### Runtime Adaptive System-on-Chip Communication Architecture

zur Erlangung des akademischen Grades eines

#### Doktors der Ingenieurwissenschaften

der Fakultät für Informatik der Universität Fridericiana zu Karlsruhe (TH)

genehmigte

#### Dissertation

von

#### Mohammad Abdullah Al Faruque

aus Tangail, Bangladesh

Tag der mündlichen Prüfung: 22.07.2009

Erster Gutachter: Prof. Dr.-Ing. Jörg Henkel

Zweiter Gutachter: Prof. Dr.-Ing. Jürgen Becker

© Copyright by Mohammad Abdullah Al Faruque, 2009

All Rights Reserved

Mohammad Abdullah Al Faruque Hans-Pfitzner-Str.7 76227, Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Mohammad Abdullah Al Faruque

## Acknowledgment

First of all, I sincerely thank my adviser, Professor Dr. Jörg Henkel, for his erudite guidance during my whole period of research. I am fortunate to have an adviser with great vision, who is always interested in exploring new research directions and ideas. He gave me complete freedom in performing research, and still made sure that my various works are neatly tied together. He has given excellent personal support to all his students and provided an enjoyable working environment.

I am also very grateful to Professor Dr. Jürgen Becker for accepting to be my co-examiner and providing valuable feedback.

I would like to thank my colleague Thomas Ebi for his continuous support in my research work. I present my gratitude to other colleagues Talal Bonny, Lars Bauer, and Muhammad Shafique for their support through discussion and positive feedback regarding my research work. I again thank all the other members of our chair, "Chair for Embedded Systems" for their help and support during my research work and thesis writing.

I am grateful to all my students for their hard and fruitful work, particularly Gereon Weiss, Xing Ye, Rudolf Krist, Manuel Hammerich, Thomas Schröder, and Thorsten Vogel.

I thank my parents for their constant love, support, and prayers. My parents always dreamed that one day I will finish my PhD. I believe this piece of work was only possible because of their prayer and wishes. I also thank my elder sister and younger sister for their loving and caring attitude throughout my student life. I would not miss the chance to thank my grandparents for their best wishes.

Finally, I present my deepest gratitude to my wife and my daughter. All of my achievements contain an invisible part of their contribution. I am grateful for all the sacrifices that my wife made to support my research. The quality of this work would not have been achieved without her priceless sacrifices.

I dedicate this thesis to all of my family members.

## **List of Publications**

### **Publications Included in This Thesis**

#### **Journal Publication**

[J.1] M. A. Al Faruque, J. Henkel: "QoS-Supported On-chip Communication for Multi-Processors", in International Journal of Parallel Programming (IJPP'08), Volume 36, Number 1, Pages: 114-139, February, 2008.

#### **Conference Publications**

- [C.1] M. A. Al Faruque, T. Ebi, J. Henkel: "Configurable Links for Runtime Adaptive On-chip Communication", in IEEE/ACM Design Automation and Test in Europe (DATE'09), Munich, Germany, Pages: 256-261, April, 2009.

- [C.2] M. A. Al Faruque, T. Ebi, J. Henkel: "ROAdNoC: Runtime Observability for an Adaptive Network on Chip Architecture", in IEEE/ACM International Conference on Computer-Aided Design (ICCAD'08), San Jose, California, USA, November, 2008.

- [C.3] M. A. Al Faruque, R. Krist, J. Henkel: "ADAM: Run-time Agent-based Distributed Application Mapping for on-chip Communication", in 45th IEEE/ACM/EDA Design Automation Conference (DAC'08), Anaheim, California, USA, Pages: 760-765, June, 2008. (Received a European Network of Excellence on High Performance and Embedded Architecture and Compilation, HiPEAC Paper Award)

- [C.4] M. A. Al Faruque, J. Henkel: "Minimizing Virtual Channel Buffer for Routers in on-chip Communication Architectures", in IEEE/ACM Design Automation and Test in Europe (DATE'08), Munich, Germany, Pages: 1238-1243, March, 2008.

- [C.5] M. A. Al Faruque, T. Ebi, J. Henkel: "Run-time Adaptive on-chip Communication Scheme", IEEE/ACM International Conference on Computer-Aided Design (ICCAD'07), San Jose, California, USA, Pages: 26-31, November, 2007.

- [C.6] M. A. Al Faruque, J. Henkel: "Transaction Specific Virtual Channel Allocation in QoS Supported On-chip Communication", IEEE International Conference on Applicationspecific Systems, Architectures and Processors (ASAP'07), Montreal, Canada, Pages: 48-53, July, 2007.

[C.7] M. A. Al Faruque, G. Weiss, J. Henkel: "Bounded Arbitration Algorithm for QoS-Supported On-chip Communication", IEEE/ACM International Conference on Hardware/-Software Co-Design and System Synthesis (Codes+ISSS'06), Seoul, South Korea, pages: 76-81, October, 2006.

#### **Workshop Publication**

[W.1] M. A. Al Faruque, X. Ye, G. Weiss, J. Henkel: "QoS-Supported Configurable Networks on Chip", Future Interconnects and Network on Chip (NOCS'06) Workshop co-located with IEEE/ACM Design Automation and Test in Europe (DATE'06), Page: 42, Munich, Germany, March, 2006 (poster, abstract).

## Abstract

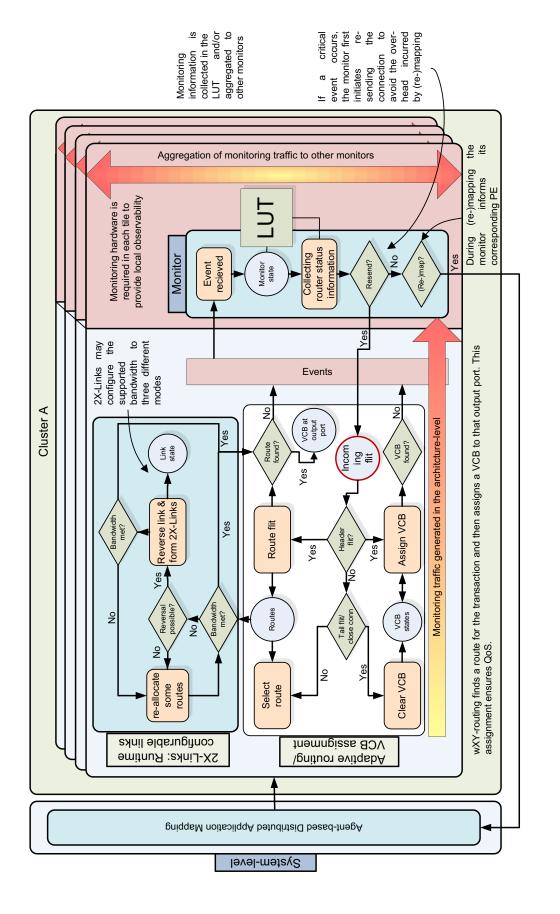

Diverse and during runtime varying workloads and/or constraints in embedded systems require runtime adaptivity to provide a high degree of efficiency during any operation mode/scenario. Design-time decisions can often only cover certain scenarios and fail in efficiency when hardto-predict system scenarios occur. Reliability concerns associated with upcoming technology nodes further strengthen the necessity towards considering runtime adaptivity in all possible parts of the future system-on-chips. In this thesis, the first approach of an adaptive system-onchip communication architecture is presented. The adaptive system provides adaptivity both in the system-level as well as in the architecture-level. The system-level adaptation is provided using a runtime application mapping. The architecture-level adaptation is implemented by using several novel methodologies to increase the resource utilization of the underlying silicon fabric, i.e. sharing the Virtual Channel Buffers (VCBs) among different output ports, changing the routing at runtime, and changing the supported bandwidth between adjacent links using configurable links at runtime. To achieve successful runtime adaptation, runtime observability is a prerequisite, as it provides necessary system information gathered on-the-fly. Therefore, a comprehensive runtime observability infrastructure for the proposed adaptive system is also presented in this thesis.

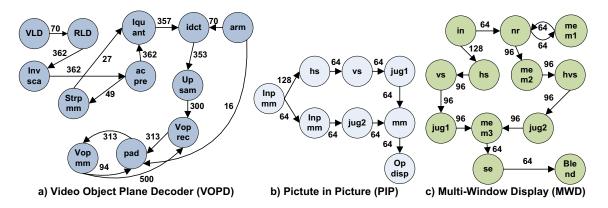

The proposed adaptive system-on-chip communication architecture is capable of supporting deadlock-free data transmission and meets required bandwidth guarantees for parallel transactions. Therefore, it is built on top of a novel *Quality-of-Service* (QoS)-supported *Networks-on-Chip* (NoC) architecture. The link arbitration algorithm, the *Bounded-Arbitration-Algorithm* (BAA) proposed in this thesis manages the flow-control mechanism at *transaction-level* and provides 100% guarantee on demanded bandwidth. The advantages of *BAA* are demonstrated by means of a complete MPEG4 video decoder case study analysis and under certain constraints it is shown that *BAA* achieves a bandwidth utilization of up to 100% (97% on an average) with a guaranteed 100% bandwidth.

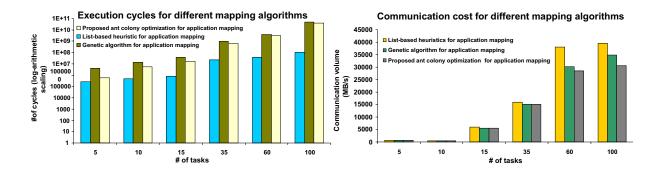

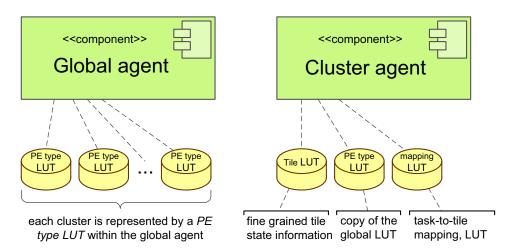

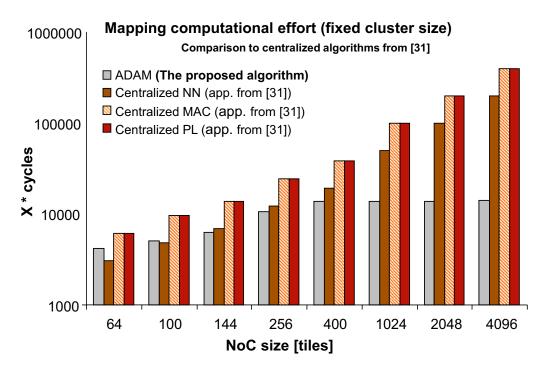

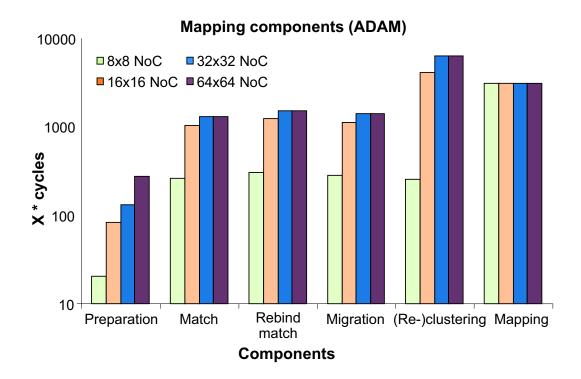

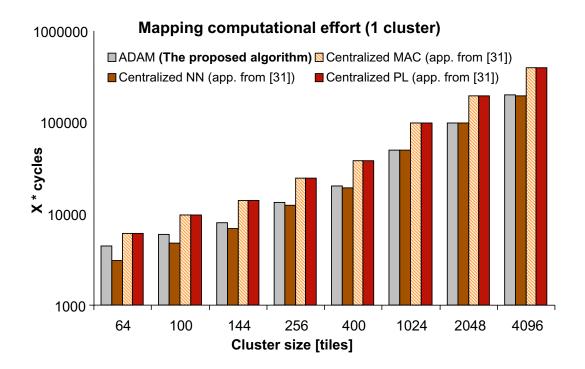

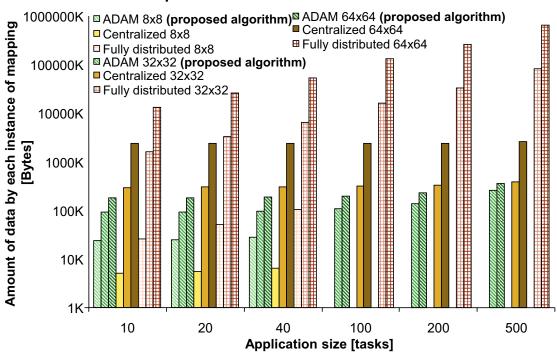

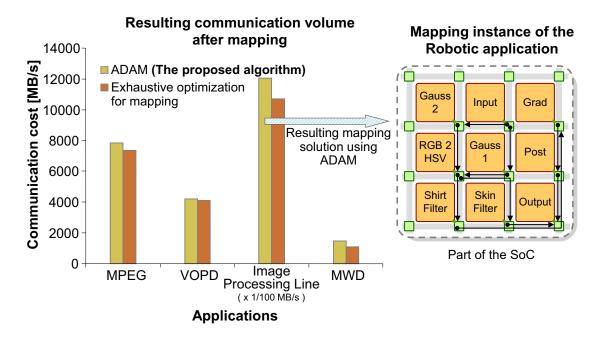

A runtime agent-based distributed application mapping is employed to achieve the *system-level* adaptation. To obtain a scalable mapping solution, the computational load is reduced by confining mapping to *clusters* which are a connected subset of NoC tiles. Exploration shows, the proposed runtime mapping obtains 10.7 times lower monitoring traffic compared to the state-of-the-art centralized mapping schemes proposed for a  $64 \times 64$  NoC. The algorithm also requires less execution cycles compared to a non-clustered centralized approach. It achieves on an average 7.1 times lower computational effort of the mapping algorithm compared to the simple *Nearest-Neighbor* (NN) heuristics in a  $64 \times 32$  NoC.

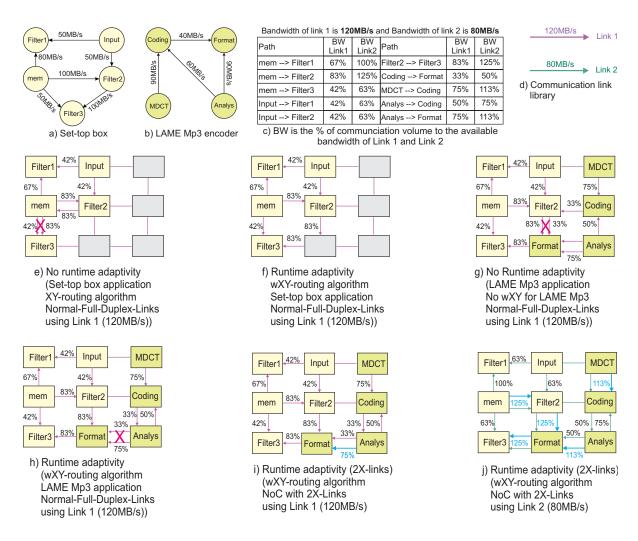

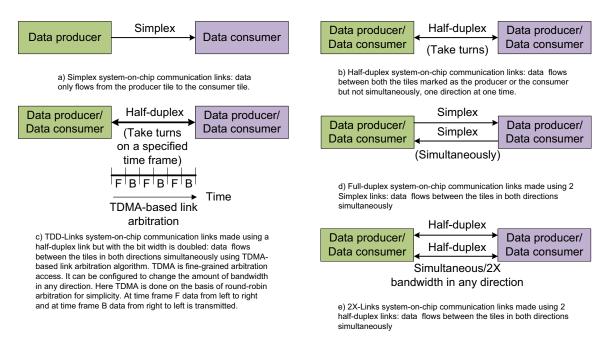

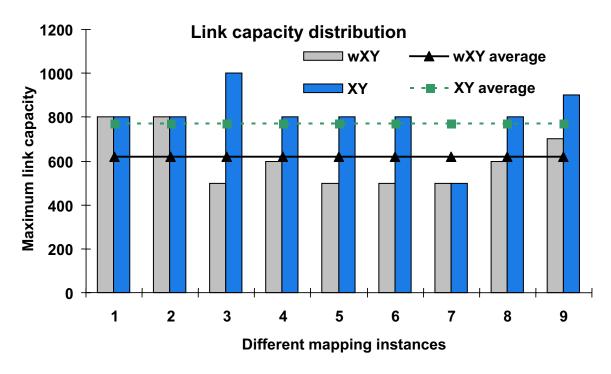

After the *system-level* has successfully set up a mapping instance, it is up to the *architecture-level* to configure each tile for the resulting transactions. The 2X-Link, a novel link for the

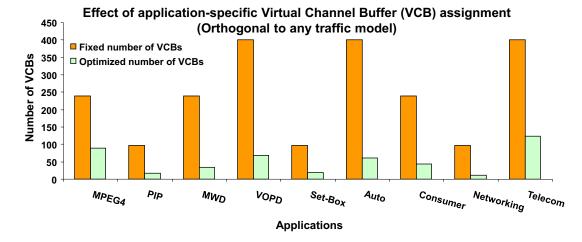

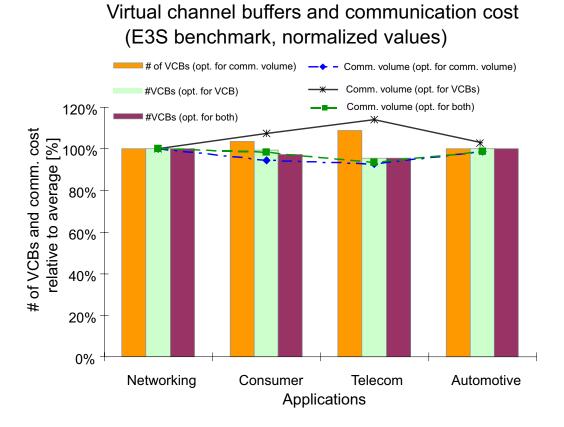

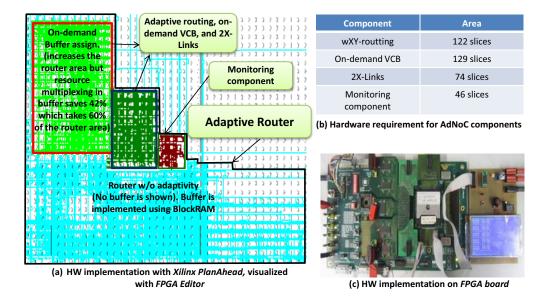

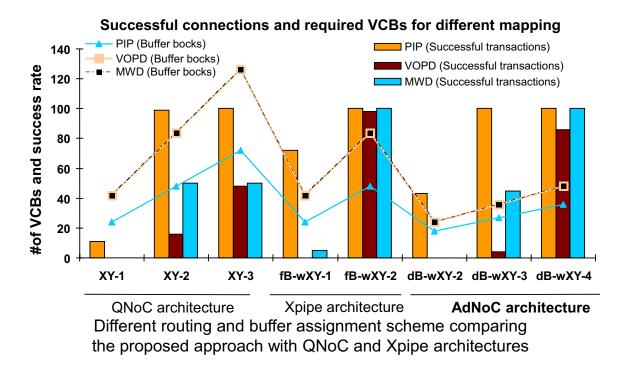

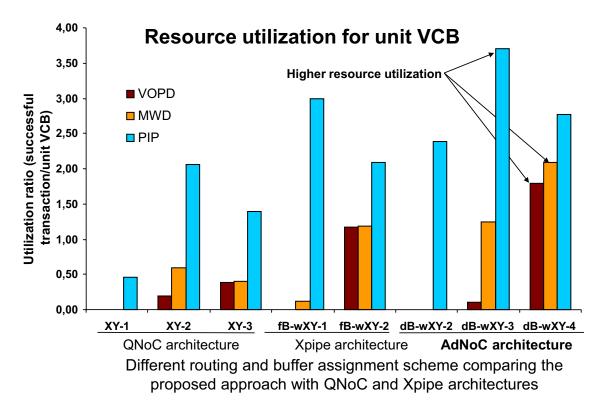

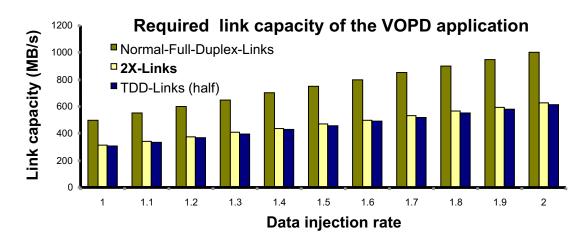

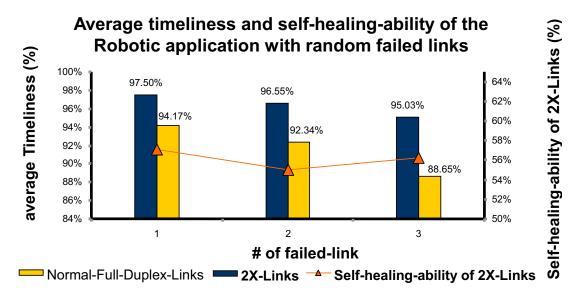

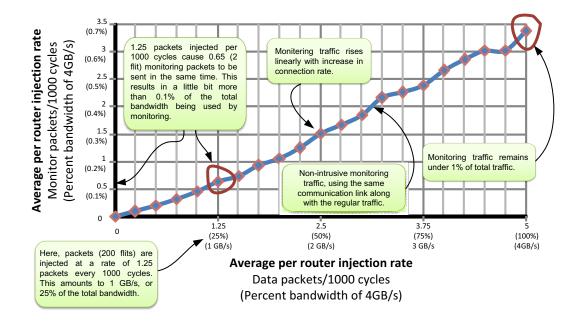

architecture-level provides a higher throughput of up to 36%, with an average throughput increase of 21.3%, compared to the Normal-Full-Duplex-Link and keeps performance-related guarantees with as low as 50% of the Normal-Full-Duplex-Link capacity. The experiments show, when some links fail randomly, the NoC with the 2X-Links may recover from those faults with an average probability of 82.2%, whereas those faults would be fatal for the Normal-Full-Duplex-Links. The on-demand buffer assignment presented as a part of the architecture-level of the adaptive system increases the buffer utilization and decreases the overall buffer use on an average of 42% in the case study analysis compared to a fixed buffer assignment. The runtime observability infrastructure that is integrated for the runtime system in the architecture-level is hardly intrusive, i.e. in worst case it may require a mere 0.7% of the total link capacity. It analyzes the communication architecture during runtime and self-adapts depending on the monitoring traffic on when and how a certain router should be configured for a certain transaction. The runtime observability infrastructure on an average increases the transaction success rate by 62% compared to having no runtime observability for the E3S benchmark suite with a hardware overhead of 46 slices in a Virtex II FPGA. The area overhead that stems from the architecturelevel adaptation may be traded-off against the flexibility to select an available route using the 2X-Links and on-demand buffer assignment (42% buffer saving) to that route for ensuring the QoS.

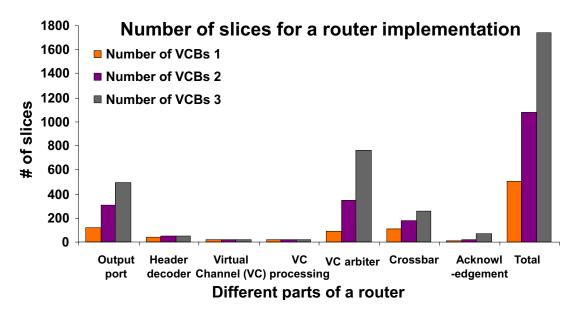

The QoS-supported NoC architecture is further explored for a case-study analysis to design an application-specific NoC. A novel methodology for design space exploration using a two-step methodology to minimize the number of *VCBs* is presented as a part of the application-specific NoC design in this thesis. On an average, 90.2% reduction in the number of *VCBs* compared to a fixed assignment for the E3S embedded application benchmark suite is achieved.

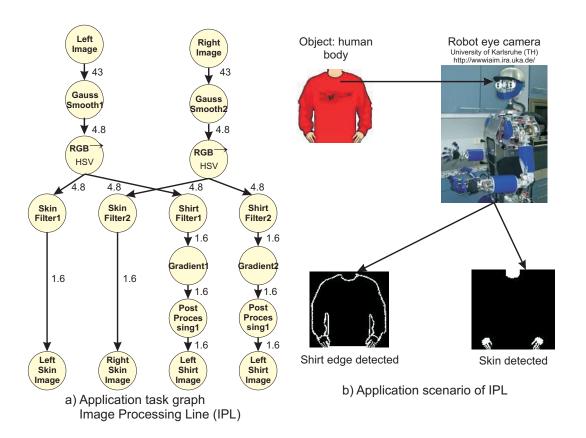

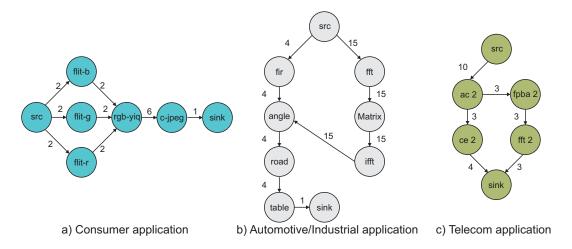

In summary, a runtime adaptive system-on-chip communication architecture on top of a QoSsupported NoC is presented in this thesis. The runtime adaptation is achieved by providing novel methodologies both in the *system-level* as well as in the *architecture-level*. The benefits of such an approach are presented with extensive experiments using representative embedded systems applications e.g. a robotic application, a set of multi-media applications, and the E3S embedded systems synthesis benchmarks suite.

## Zusammenfassung

Vielfältige und zur Laufzeit variierende Auslastungen und/oder Einschränkungen eingebetteter Systeme erfordern eine Adaption des Systems zur Laufzeit, um einen hohen Grad der Effizienz während eines beliebigen Betriebsmodus/-szenarios zu gewährleisten. Entscheidungen, welche während der Entwurfszeit getroffen werden, können oft nur gewisse Szenarien berücksichtigen und scheitern im Falle von schwer vorhersehbaren Systemszenarien daran, die Effizienz aufrecht zu erhalten. Zuverlässigkeitsprobleme, welche verstärkt mit den kommenden Generationen der Halbleitertechnologie in Verbindung gebracht werden, verstärken den Bedarf an Laufzeitadaptivität in allen Teilen zukünftiger System-on-Chip Entwürfe. Diese Arbeit präsentiert den ersten Ansatz einer adaptiven Kommunikationsarchitektur für ein solches System-on-Chip. Dieses adaptive System bietet Adaptivität sowohl auf Systemebene als auch auf Architekturebene. Die Adaption auf Systemebene wird durch eine Zuordnung der Anwendungen auf die einzelnen Rechenknoten zur Laufzeit erzielt. Die Adaptivität auf Architekturebene wird durch verschiedene, neuartige Methodologien erreicht. Sie erhöhen die Auslastung der Ressourcen des zugrunde liegenden Siliziums, z.B. durch das dynamische Verteilen des Speichers der virtuellen Kanäle (Virtual Channel Buffer, VCB) an verschiedene Ausgangsports, eine Anpassung des Routings zur Laufzeit und das Ändern der möglichen Bandbreite zwischen benachbarten Routern zur Laufzeit. Um eine erfolgreiche Adaption zur Laufzeit zu ermöglichen, ist eine ständige Beobachtung des Systems erforderlich. Daher wird eine umfassende Infrastruktur zur Beobachtung des Systems zur Laufzeit im Rahmen dieser Arbeit entworfen und vorgestellt.

Die vorgestellte adaptive System-on-Chip Kommunikationsarchitektur, realisiert als Networkson-Chip (NoC), unterstützt eine deadlock-freie Datenübertragung und garantiert benötigte Dienstgüten (*Quality-of-Service*, QoS) während paralleler Übertragungen. Das in dieser Arbeit vorgeschlagene Verfahren, der "*Bounded-Arbitration Algorithmus*" (BAA), regelt die Flusskontrolle auf Transaktionsebene und bietet eine 100-prozentige Garantie der verlangten Bandbreitenanforderungen. Die Vorteile des *BAAs* werden anhand einer umfangreicher Fallstudie eines MPEG4 Videodecoders analysiert. Hierbei wird gezeigt, dass der *BAA* unter den gegebenen Einschränkungen eine Bandbreitennutzung von bis zu 100% (im Durchschnitt 97%) erreicht, ohne an Dienstgüte zu verlieren (100% garantierte Bandbreite).

Es wird eine verteilte, agentenbasierte Zuordnung der Anwendungen auf die einzelnen Rechenknoten zur Laufzeit verwendet um die, Adaption auf Systemebene zu realisieren. Um die Zuordnung skalierbar zu halten, wird der Rechenaufwand reduziert, in dem die Zuordnung auf Cluster beschränkt wird. Ein Cluster besteht aus einer verbundenen Untermenge der Networkson-Chip-Knoten. Untersuchungen zeigen, dass das vorgeschlagene Verfahren 10,7 mal weniger Datenübertragung zur Systemüberwachung verursacht, als ein zentral gesteuertes Verfahren, wie es zum aktuellen Stand der Technik in  $64 \times 64$  NoCs verwendet wird. Hinzu kommt, dass der Algorithmus im Vergleich zu Verfahren ohne Cluster weniger Rechenzeit benötigt. In Experimenten verursacht er im Durchschnitt 7,1 mal weniger Rechenaufwand im Vergleich zur einfachen "*Nearest-Neighbor*" (NN)-Heuristik in einem  $64 \times 32$  NoC.

Nachdem auf Systemebene erfolgreich eine Anwendungszuordnung gefunden wurde, ist es eine Aufgabe auf Architekturebene, die resultierenden Verbindungen der Kacheln zu konfigurieren. 2X-Links, eine neue Art von Verbindungen für Networks-on-Chips, ermöglicht einen bis zu 36% höheren Durchsatz (im Durchschnitt 21,3%) im Vergleich zu normalen Vollduplexverbindungen. Sie garantieren Verbindungen mit bis zu 50% der Kapazität von normalen Vollduplexverbindungen. Durch Simulationen wird gezeigt, dass ein NoC mit 2X-Links mit einer durchschnittlichen Wahrscheinlichkeit von 82,2% zufällige Verbindungsausfälle umgehen kann, obwohl die Ausfälle für normale Vollduplexverbindungen unausweichlich wären. Die bedarfsabhängige Zuteilung der VCBs erhöht die Auslastung der einzelnen Buffer. In einer Fallstudie wird der Speicherbedarf im Vergleich zu einer festen Speicherzuteilungsstrategie im Durchschnitt um 42% reduziert. Die Infrastruktur zur Beobachtung des Systems zur Laufzeit, welche in die Architektur des Laufzeitsystems integriert ist, ist sehr leichtgewichtig - im schlimmsten Fall benötigt sie höchstens 0,7% der verfügbaren Verbindungskapazität. Sie analysiert die Kommunikation wären der Laufzeit und entscheidet eigenständig, wann und wie ein Router für gewisse Übertragungen konfiguriert sein sollte. Diese Maßnahme verbessert die Erfolgsquote der Übertragungen von Anwendungen aus der E3S-Benchmark-Suite um 62% im Vergleich zu einer Architektur ohne eine entsprechende Beobachtungsinfrastruktur. Sie benötigt einen Hardwareaufwand von 46 Slices in einem Virtex II FPGA. Der zusätzliche Hardwareverbrauch wird durch die Möglichkeit, verschiedene Routen - mit und ohne 2X-Links - zu nehmen, der Speicherzuteilung zur Laufzeit (42% weniger Speicherbedarf) und durch die erlangte Dienstgüte ausgeglichen.

Die QoS-bietende System-on-Chip Kommunikationsarchitektur wird mittels einer Fallstudie weiter untersucht, um ein applikations-spezifisches NoC zu entwerfen. Eine neue Vorgehensweise, um mittels einer zweistufigen Methodologie die Zahl der benötigten *VCBs* zu minimieren, wird im Rahmen dieser Arbeit vorgestellt. Im Durchschnitt wird dadurch der für die "E3S embedded application benchmark suite" benötigte Speicher im Vergleich zu einer festen Speicherzuteilung um 90,2% reduziert.

Zusammenfassend präsentiert diese Arbeit ein laufzeitadaptives NoC, welchem eine Systemon-Chip Kommunikationsarchitektur, welche QoS unterstützt, zugrunde liegt. Die Adaption zur Laufzeit wird durch neue Vorgehensweisen sowohl auf Systemebene als auch auf Architekturebene erzielt. Die Vorteile eines solchen Ansatzes werden durch zahlreiche Experimente aus repräsentativen Anwendungen für eingebettete Systeme dargestellt – z.B. einer Robotikapplikation, einer Klasse von Multimediaapplikationen und der "E3S benchmark suite".

## Contents

| Ac  | knov                     | vledge                                           | ment                                            | i                                                                                             |

|-----|--------------------------|--------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Lis | st of                    | Publica                                          | ations                                          | iii                                                                                           |

| Ab  | ostrac                   | ct                                               |                                                 | v                                                                                             |

| Zu  | Isami                    | menfas                                           | sung                                            | vii                                                                                           |

| Ab  | brev                     | iations                                          |                                                 | xiv                                                                                           |

| Lis | st of                    | Figure                                           | 3                                               | xvii                                                                                          |

| Lis | st of <sup>·</sup>       | Tables                                           |                                                 | xix                                                                                           |

| Lis | st of .                  | Algorit                                          | hms                                             | xxi                                                                                           |

| 1   | 1.1<br>1.2<br>1.3<br>1.4 | Netwo<br>Contril<br>Dissert<br>ated We<br>Bus-ba | round                                           | . 2<br>. 4<br>. 5<br>. 7<br>. 7<br>. 9<br>. 9<br>. 10<br>. 11<br>. 13<br>. 14<br>. 15<br>. 16 |

| 3   | <b>QoS</b><br>3.1<br>3.2 | Definit                                          | Orted System-on-Chip Communication         ions | . 21                                                                                          |

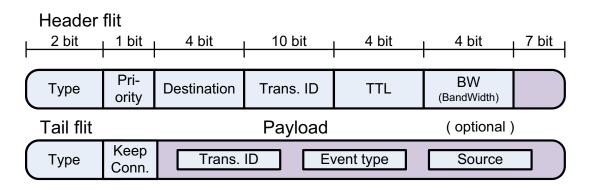

|   |     | 3.2.2 Packet Structure                                                |

|---|-----|-----------------------------------------------------------------------|

|   |     | 3.2.3 Pipeline Stages of the Router Architecture                      |

|   | 3.3 | Guaranteed Communication on Top of the Packet-switched Network        |

|   | 3.4 | Bounded-Arbitration-Algorithm                                         |

|   |     | 3.4.1 Fine-grained Quality-of-Service Specification                   |

|   |     | 3.4.2 BAA on Top of the TDMA-like Link Arbitration                    |

|   |     | 3.4.3 Bound Analysis                                                  |

|   |     | 3.4.4 Evaluation of the Bounded-Arbitration-Algorithm                 |

|   | 3.5 | Conclusion                                                            |

| 4 | Roa | d to Adaptive Networks-on-Chip 43                                     |

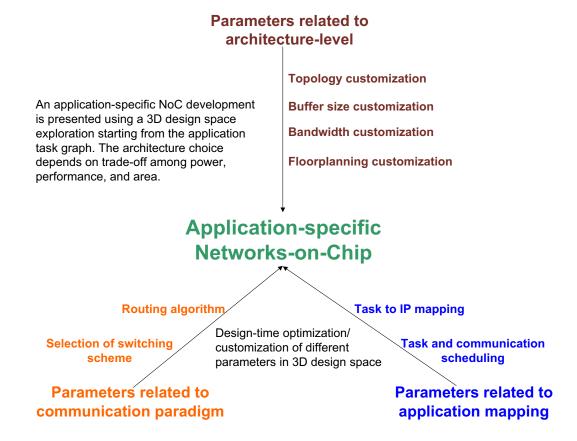

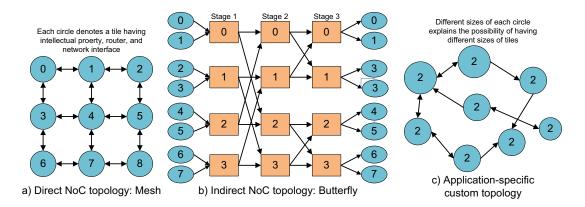

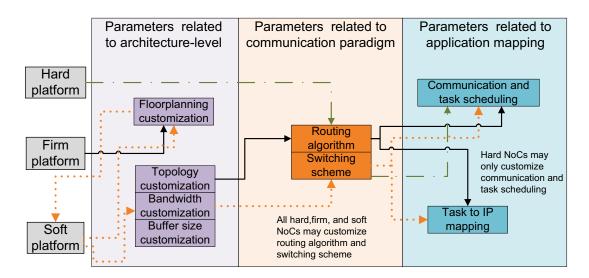

|   | 4.1 | Parameters to be Customized                                           |

|   |     | 4.1.1 Architecture-level Parameters                                   |

|   |     | 4.1.2 Communication Paradigm Customization                            |

|   |     | 4.1.3 Mapping of the Application                                      |

|   |     | 4.1.4 Design Flow for an Application-specific NoC                     |

|   | 4.2 | Novel Application-specific NoC Architecture                           |

|   | 4.3 | Application-specific Virtual Channel Buffer Assignment                |

|   |     | 4.3.1 Minimizing Virtual Channel Buffer during Application Mapping 55 |

|   |     | 4.3.1.1 The Optimization Criteria                                     |

|   |     | 4.3.1.2 Optimization Algorithm                                        |

|   |     | 4.3.1.3 Problem Formulation                                           |

|   |     | 4.3.1.4 Solution Construction                                         |

|   |     | 4.3.2 Probabilistic Analysis                                          |

|   |     | 4.3.2.1 Traffic Modeling                                              |

|   |     | 4.3.2.2 VCB Reduction Considering Quality-of-Service 62               |

|   |     | 4.3.3 Evaluation of the Proposed Methodology                          |

|   | 4.4 | Road to Runtime Adaptation: Parameters                                |

|   | 4.5 | Conclusion                                                            |

| 5 | AdN | loC: Runtime Adaptive Networks-on-Chip 69                             |

|   | 5.1 | Motivation                                                            |

|   | 5.2 | Advantages of the Adaptive NoC over the Application-specific NoC 70   |

|   | 5.3 | Runtime Adaptive Networks-on-Chip (AdNoC)                             |

|   |     | 5.3.1 AdNoC Specific Definitions                                      |

|   |     | 5.3.2 Overview of the AdNoC Architecture                              |

|   |     | 5.3.3 System-level Adaptation                                         |

|   |     | 5.3.4 Architecture-level Adaptation                                   |

|   | 5.4 | Conclusion                                                            |

| 6 | Run | time System-level Adaptation 77                                       |

| - | 6.1 | ADAM: Runtime Application Mapping Algorithm                           |

|   |     | 6.1.1 Different Parts of the ADAM Algorithm                           |

|   |     | 6.1.2   Cluster Negotiation Algorithm   81                            |

|   |     | 6.1.2.1 Data Structures for the Algorithms                            |

|   |     | $\mathcal{O}$                                                         |

|   |     |        | 6.1.2.2 Algorithm Description                                  | 84  |

|---|-----|--------|----------------------------------------------------------------|-----|

|   |     |        | 6.1.2.3 Histogram Matching during Cluster Negotiation          | 86  |

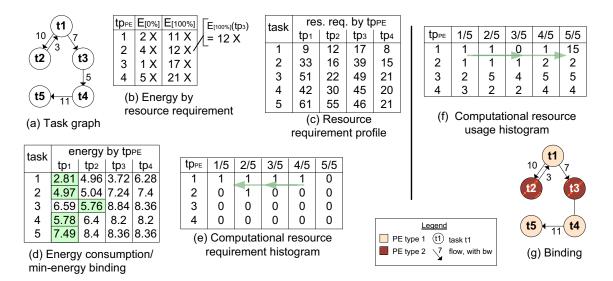

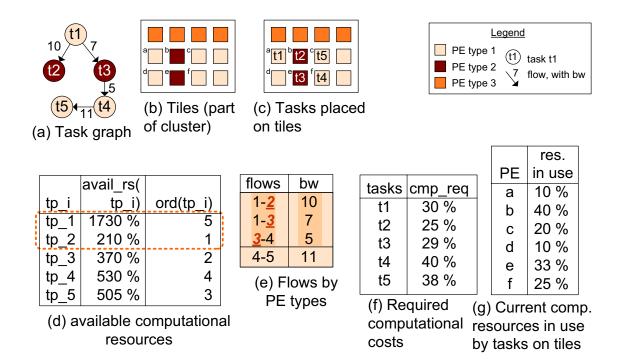

|   |     |        | 6.1.2.4 Exemplary Algorithm Execution                          | 87  |

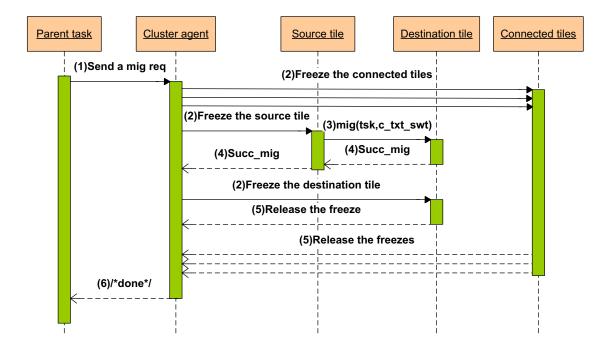

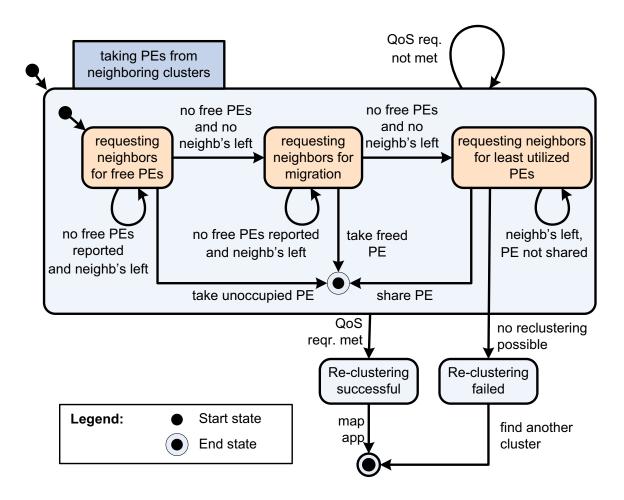

|   |     | 6.1.3  | (Re-)clustering and Task Migration for the ADAM Algorithm      | 89  |

|   |     | 6.1.4  | The Mapping Algorithm Inside a Cluster                         | 90  |

|   |     |        | 6.1.4.1 Data Structures for the Algorithm                      | 91  |

|   |     |        | 6.1.4.2 Heuristics for the Optimization                        | 94  |

|   |     |        | 6.1.4.3 Algorithm Description                                  | 95  |

|   |     |        | 6.1.4.4 Exemplary Algorithm Execution                          | 97  |

|   |     | 6.1.5  | Configuration Data for the Runtime ADAM Algorithm              | 97  |

|   |     | 6.1.6  | Persistent Configuration Data                                  | 98  |

|   |     | 6.1.7  | Collecting Status of Each Tile                                 | 101 |

|   | 6.2 | Conclu | ision                                                          | 101 |

| 7 | Run | time A | rchitecture-level Adaptation                                   | 103 |

|   | 7.1 |        | ecture-level Adaptation                                        |     |

|   |     | 7.1.1  | Motivational Example Supporting Architecture-level Adaptation  |     |

|   |     | 7.1.2  | Parameters for the Runtime Adaptation                          |     |

|   |     | 7.1.3  | Runtime Configurable Links (2X-Links)                          |     |

|   |     |        | 7.1.3.1 System-on-Chip Communication Links                     |     |

|   |     |        | 7.1.3.2 Design and Implementation of the 2X-Links              |     |

|   |     | 7.1.4  | Weighted Routing Algorithm                                     |     |

|   |     | 7.1.5  | On-demand Buffer Assignment                                    |     |

|   | 7.2 |        | ne Observability for the AdNoC Architecture (ROAdNoC)          |     |

|   |     | 7.2.1  | Monitoring Events                                              |     |

|   |     | 7.2.2  | Design and Event Collection                                    |     |

|   |     | 7.2.3  | Aggregation and Processing                                     |     |

|   |     | 7.2.4  | Monitoring Related Traffic                                     |     |

|   | 7.3 | -      | ve Router Architecture for the AdNoC                           |     |

|   | 7.4 |        | are Implementation of the AdNoC Architecture                   |     |

|   |     | 7.4.1  | The wXY-routing and the On-demand Buffer Assignment Components |     |

|   |     | 7.4.2  | Configurable Links Components                                  |     |

|   |     | 7.4.3  | Monitoring Component                                           |     |

|   | 75  | 7.4.4  | Hardware Evaluation                                            |     |

|   | 7.5 | Conclu | usion                                                          | 131 |

| 8 |     |        | and Hardware Prototyping Environment                           | 133 |

|   | 8.1 |        | ation Environment                                              |     |

|   |     | 8.1.1  | OMNeT++ Simulator                                              |     |

|   |     |        | 8.1.1.1 Implementation                                         |     |

|   |     | 010    | 8.1.1.2 Traffic Model Implementation                           |     |

|   |     | 8.1.2  | SystemC-based NoC Simulator                                    |     |

|   |     | 012    | 8.1.2.1 Configuration for the Application-specific NoC         |     |

|   | 0 2 | 8.1.3  | Application Mapping Tool                                       |     |

|   | 8.2 | Hardw  | rare Prototyping                                               | 142 |

|    | 8.3   | Conclu  | sion                                                     | 143 |

|----|-------|---------|----------------------------------------------------------|-----|

| 9  | Res   | ults an | d Case-Study Analysis                                    | 145 |

|    | 9.1   | Evalua  | tion of the Proposed AdNoC Architecture                  | 146 |

|    |       | 9.1.1   | ADAM Provides Flexibility and Reduces Computational Cost | 146 |

|    |       | 9.1.2   | On-demand VCB Assignment Increases Buffer Utilization    | 149 |

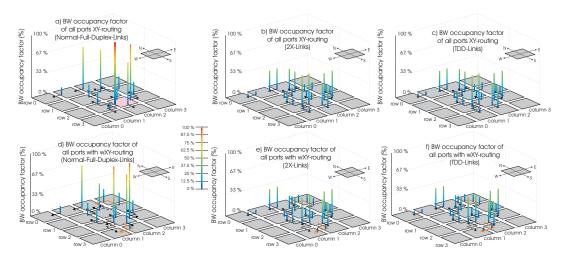

|    |       | 9.1.3   | Configurable Links Increase Resource Utilization         | 152 |

|    |       | 9.1.4   | Light-weight Monitoring Component                        | 158 |

|    | 9.2   | Summa   | ary of the Evaluation                                    |     |

| 10 | Con   | clusior | 1                                                        | 163 |

|    | 10.1  | Thesis  | Summary                                                  | 163 |

|    |       |         | Work                                                     |     |

| Re | ferer | nces    |                                                          | 180 |

# **Abbreviations**

| ACO            | Ant Colony Optimization                             |

|----------------|-----------------------------------------------------|

| AdNoC          | Adaptive Networks-on-Chip                           |

| ADAM           | Agent-based Distributed Application Mapping         |

| ASIC           | Application-Specific Integrated Circuit             |

| ROAdNoC        | Runtime Observability for Adaptive Networks-on-Chip |

| ARQ            | Automatic Repeat Request                            |

| <b>B-Frame</b> | Bidirectional-Frame                                 |

| BAA            | Bounded-Arbitration-Algorithm                       |

| BE             | Best-Effort                                         |

| BW             | BandWidth                                           |

| CA             | Cluster Agent                                       |

| CAD            | Computer-Aided Design                               |

| СМ             | Centralized Manager                                 |

| CMOS           | Complementary MetalOxideSemiconductor               |

| CPU            | Central Processing Unit                             |

| DSM            | Deep Sub Micron                                     |

| DSP            | Digital Signal Processing                           |

| E3S            | Embedded Systems Synthesis Benchmarks Suite         |

| FIFO           | First In First Out                                  |

| Flit           | Flow Control Unit                                   |

| FPGA           | Field-Programmable Gate Array                       |

| GA             | Global Agent                                        |

| GS             | Guaranteed Service                                  |

| GUI            | Graphical User Interface                            |

| HF             | Header Flit                                         |

| I-Frame        | Intra-Frame                                         |

| IP             | Intellectual Property                               |

| IPL            | Image Processing Line                               |

| ITRS           | International Technology Roadmap for Semiconductors |

| iQuant         | Inverse Quantification of the MPEG4 Decoder         |

| LB             | Lower Bound                                         |

| LC             | Link Control                                        |

| LUT            | Look-Up-Table                                       |

| MPEG4          | Moving Picture Experts Group-Standard 4             |

| MPSoC          | Multi-Processor System-on-Chip                      |

|                | Hun Processor bystem on emp                         |

| MUX     | Multiplexer                                                      |

|---------|------------------------------------------------------------------|

| MWD     | Multi-Window Display                                             |

| NACK    | Negative ACKnowledgment                                          |

| NI      | Network Interface                                                |

| NN      | Nearest-Neighbor                                                 |

| NoC     | Networks-on-Chip                                                 |

| NoCMS   | NoC Monitoring Service                                           |

| OA      | Output Arbiter                                                   |

| OCP     | Open Core Protocol                                               |

| OCIN    | System-on-Chip Interconnection Network                           |

| OD      | Output Decoder                                                   |

| PF      | Payload Flit                                                     |

| PE      | Processing Element                                               |

| P-Frame | Predicted-Frame                                                  |

| PCA     | Physical Channel Arbiter                                         |

| PDA     | Personal Digital Assistant                                       |

| PIP     | Picture in Picture                                               |

| QAP     | Quadratic Assignment Problem                                     |

| QoS     | Quality-of-Service                                               |

| QNoC    | Quality-of-Service NoC                                           |

| RAM     | Random-Access Memory                                             |

| RGB     | Red, Green, and Blue                                             |

| RR      | Round-Robin                                                      |

| SDM     | Space Division Multiplexing                                      |

| SE      | Storing Element                                                  |

| SHF     | Secondary Header Flit                                            |

| SoC     | System-on-Chip                                                   |

| TF      | Tail Flit                                                        |

| TG      | Task Graph                                                       |

| TGFF    | Task Graph For Free                                              |

| TDD     | Time-Division-Duplex                                             |

| TDMA    | Time Division Multiple Access                                    |

| TTL     | Time-To-Live                                                     |

| UB      | Upper Bound                                                      |

| UMARS   | Unified MApping, Routing, and Slot allocation                    |

| VBR     | Variable-Bit-Rates                                               |

| VC      | Virtual Channel                                                  |

| VCA     | Virtual Channel Arbiter                                          |

| VCB     | Virtual Channel Buffer                                           |

| VHDL    | Very High Speed Integrated Circuit Hardware Description Language |

| VOPD    | Video Object Plane Decoder                                       |

| wXY     | weighted XY                                                      |

|         |                                                                  |

# **List of Figures**

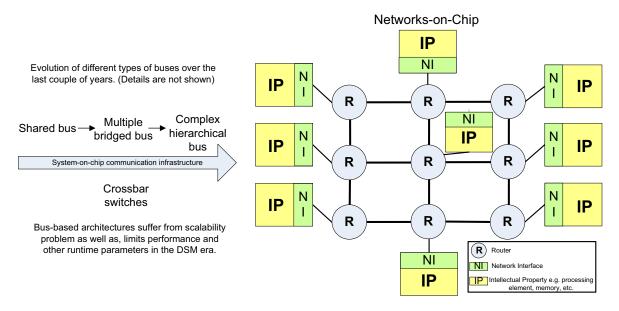

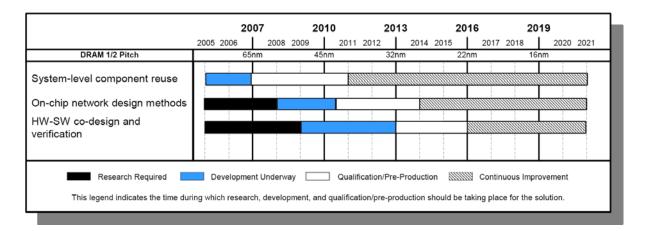

| 1.1                                                                                                   | Evolution of the Networks-on-Chip                                                                                             | 3                                      |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.1                                                                                                   | NoC as the future system-level design solution [85]                                                                           | 10                                     |

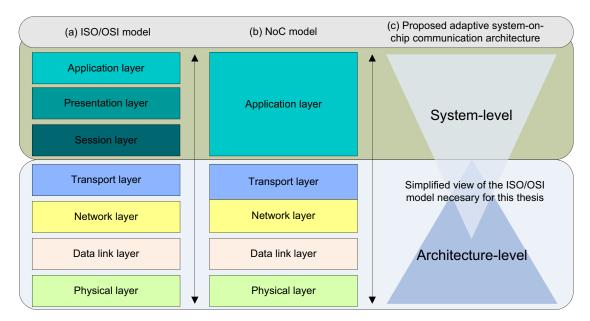

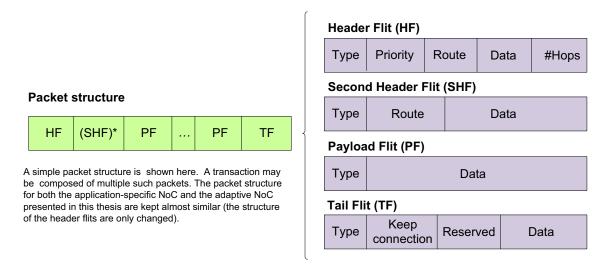

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul> | Adaptation of the ISO/OSI reference model                                                                                     | 21<br>23<br>25<br>26<br>28<br>30<br>32 |

| 3.8                                                                                                   | Proposed bounded-arbitration-algorithm                                                                                        | 33                                     |

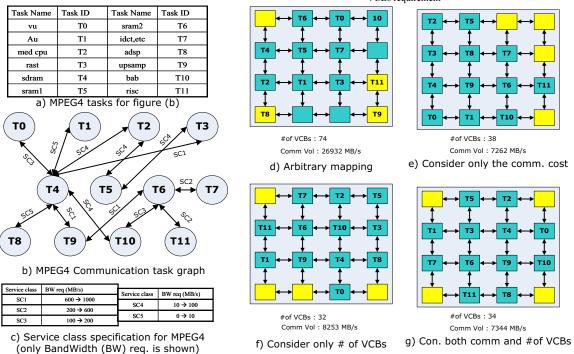

| 3.9                                                                                                   | MPEG4 video decoder and its data flow graph                                                                                   | 35                                     |

|                                                                                                       | MPEG4 video decoder mapping onto a $5 \times 4$ Mesh                                                                          | 36                                     |

|                                                                                                       | Transaction-specific bandwidth provides the lower bound guarantee                                                             | 37                                     |

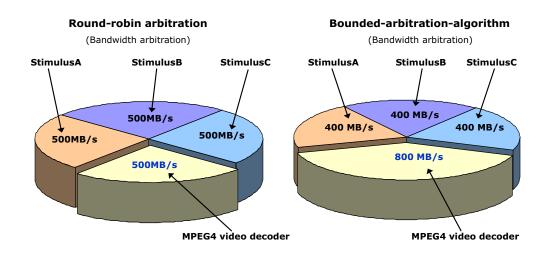

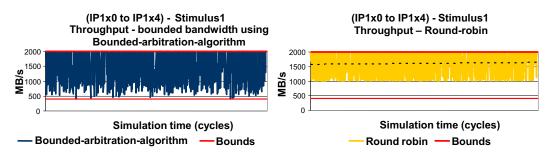

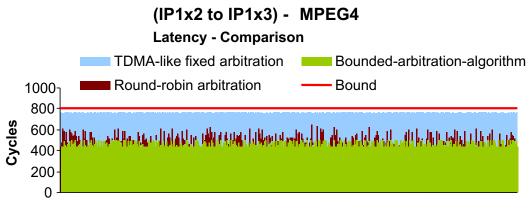

|                                                                                                       | Throughput between RR and BAA                                                                                                 | 37<br>38                               |

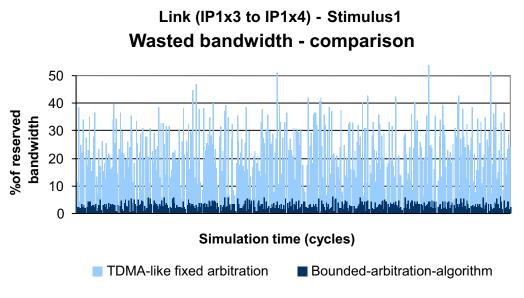

|                                                                                                       | Latency comparison for TDMA-like fixed, RR and BAA algorithms Resource utilization: TDMA-like fixed and BAA                   | - 38<br>- 38                           |

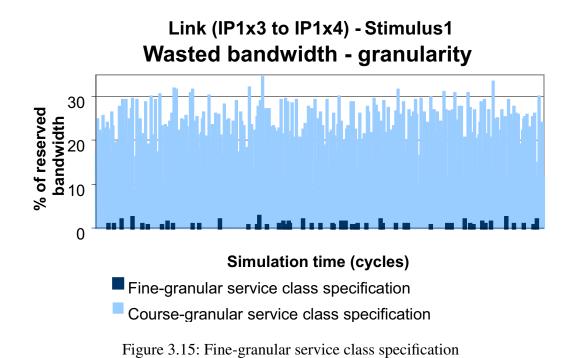

|                                                                                                       | Fine-granular service class specification                                                                                     | 39                                     |

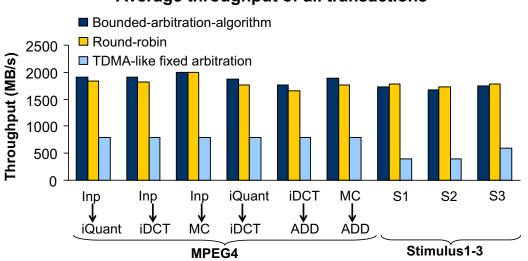

|                                                                                                       | Overall throughput comparison for MPEG4 video decoder and stimulus                                                            | 40                                     |

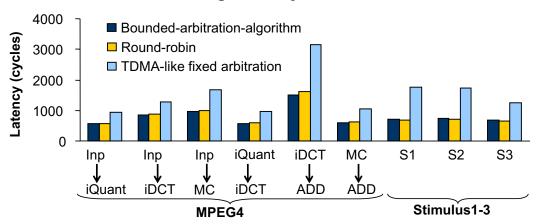

|                                                                                                       | Overall latency comparison for MPEG4 video decoder and stimulus                                                               | 41                                     |

| 4.1                                                                                                   | 3D design-space exploration for the application-specific NoC design                                                           | 44                                     |

| 4.2                                                                                                   | Different types of topology for the application-specific NoC design                                                           | 46                                     |

| 4.3                                                                                                   | Area effects of the increasing virtual channel buffers                                                                        | 47                                     |

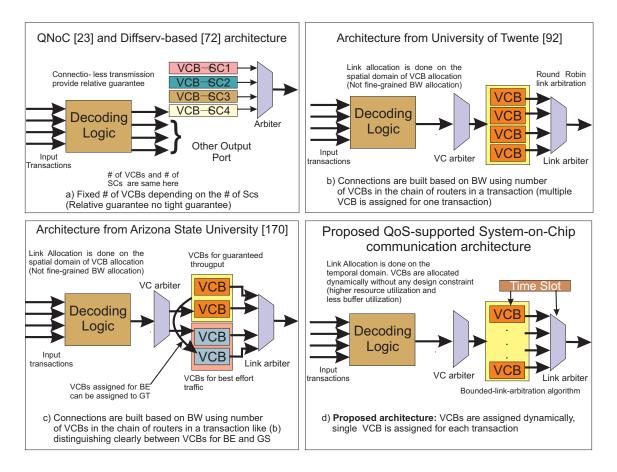

| 4.4                                                                                                   | Design flow for an application-specific NoC motivated from [122] Different state-of-the-art service-class-based architectures | 50<br>52                               |

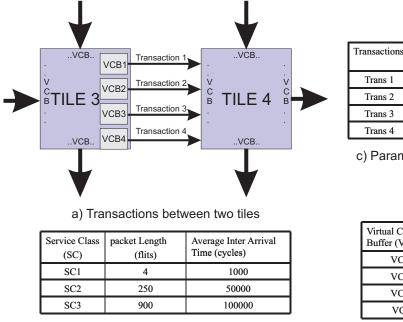

| 4.5<br>4.6                                                                                            | Motivating example: MPEG4 video decoder mapped onto a 4 x 4 NoC                                                               | 52<br>54                               |

| 4.7                                                                                                   | VCBs reduction using an analytical approach                                                                                   | 55                                     |

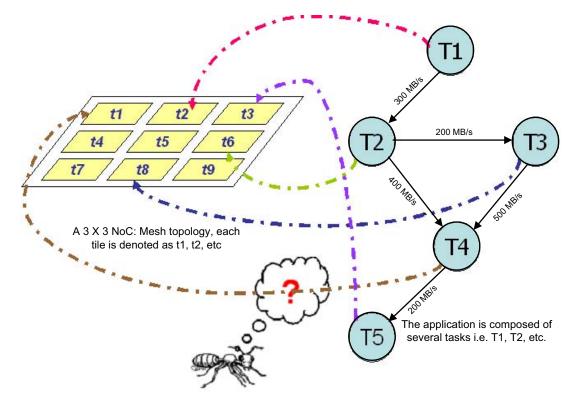

| 4.8                                                                                                   | Exemplary application mapping onto a 3 x 3 NoC using ACO                                                                      | 58                                     |

| 4.9                                                                                                   | Comparison of ACO with the GA and the LB algorithms                                                                           | 60                                     |

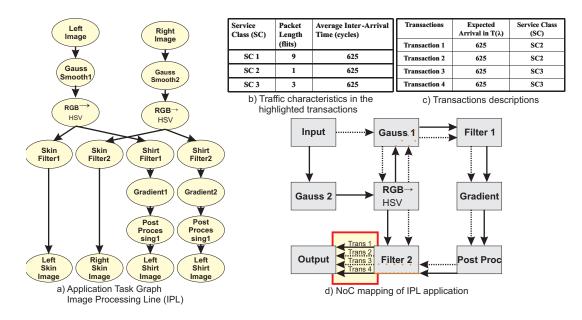

|                                                                                                       | IPL mapping and VCBs reduction through probabilistic analysis                                                                 | 64                                     |

|                                                                                                       | Effect of the application-specific VCB assignment for the E3S benchmark suite                                                 | 65                                     |

|                                                                                                       | Effect of the multi-objective goal function for the E3S benchmark suite                                                       | 66                                     |

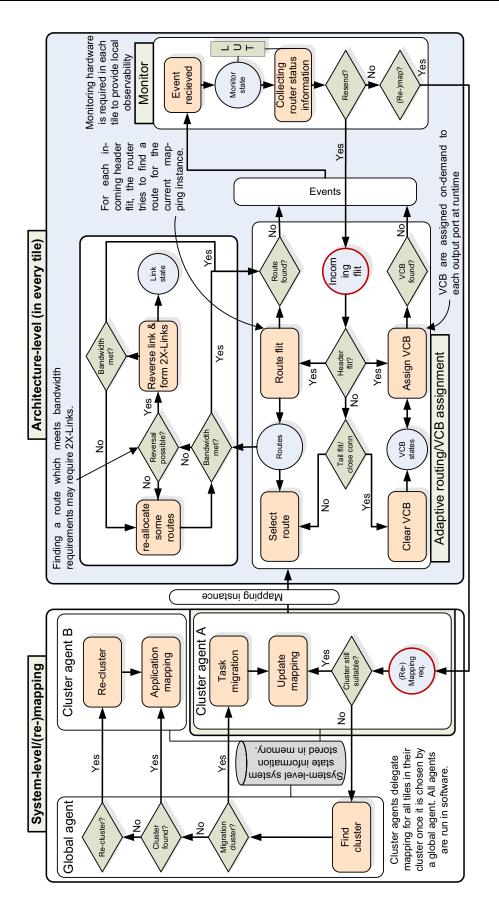

| 5.1                                                                                                   | The adaptive system-on-chip communication architecture                                                                        | 74                                     |

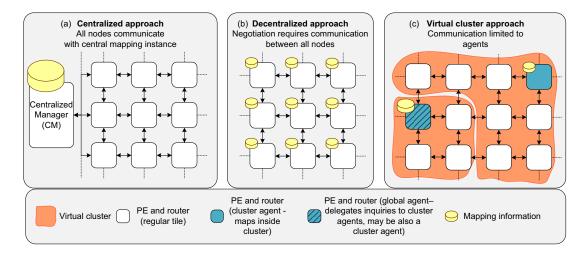

| 6.1                                                                                                   | Various options for (re-)mapping                                                                                              | 78                                     |

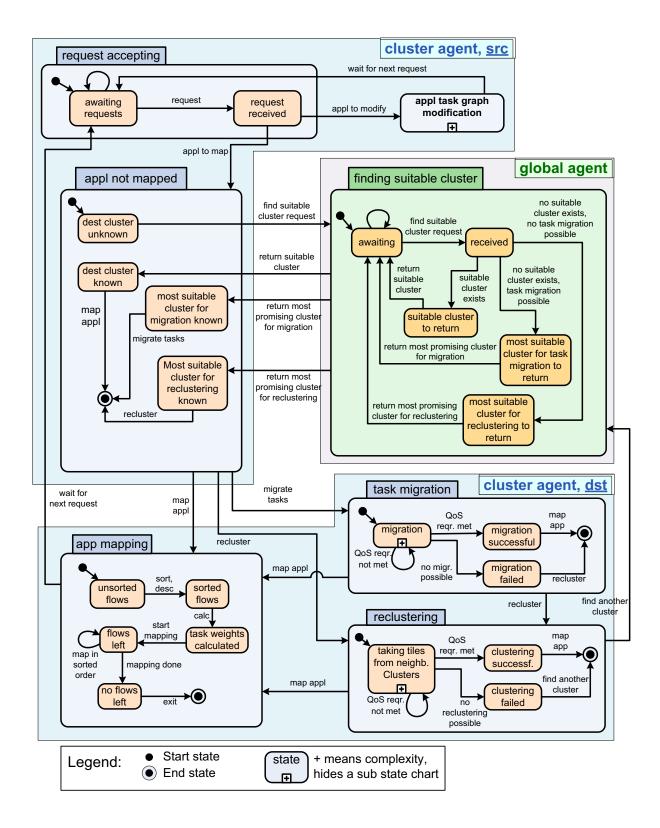

| 6.2                                                                                                                                                                                                                                       | Flow of the ADAM algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

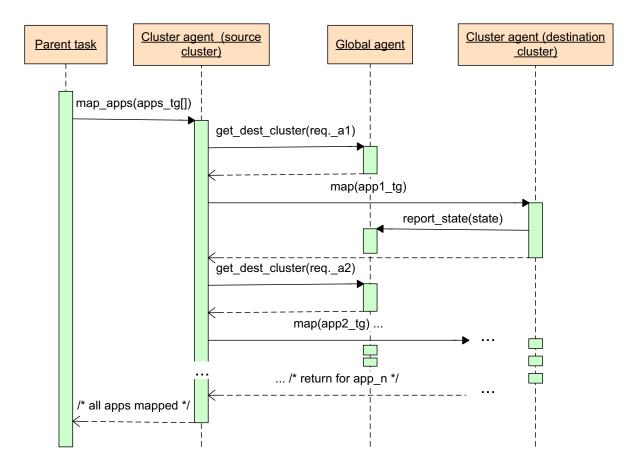

| 6.3                                                                                                                                                                                                                                       | Cluster negotiation and application mapping inside the negotiated cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81                                                                                                                                           |

| 6.4                                                                                                                                                                                                                                       | Suitable cluster and binding example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                                                                                                                           |

| 6.5                                                                                                                                                                                                                                       | Task migration to support runtime application mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89                                                                                                                                           |

| 6.6                                                                                                                                                                                                                                       | The (re-)clustering algorithm flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90                                                                                                                                           |

| 6.7                                                                                                                                                                                                                                       | Example for a runtime application mapping inside a cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96                                                                                                                                           |

| 6.8                                                                                                                                                                                                                                       | Configuration data for the runtime ADAM algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98                                                                                                                                           |

| 7.1                                                                                                                                                                                                                                       | Motivational example to show the requirement of the architecture-level adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 104                                                                                                                                          |

| 7.2                                                                                                                                                                                                                                       | Functionality during architecture-level adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107                                                                                                                                          |

| 7.3                                                                                                                                                                                                                                       | Different types of system-on-chip communication links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110                                                                                                                                          |

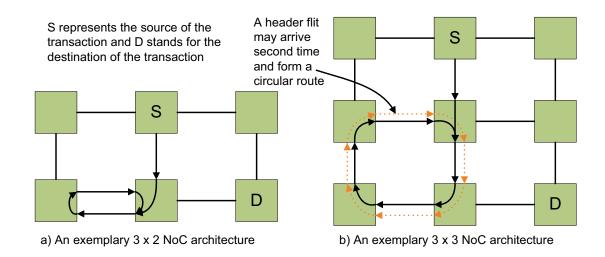

| 7.4                                                                                                                                                                                                                                       | Examples of circular routing from the source S to the destination D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114                                                                                                                                          |

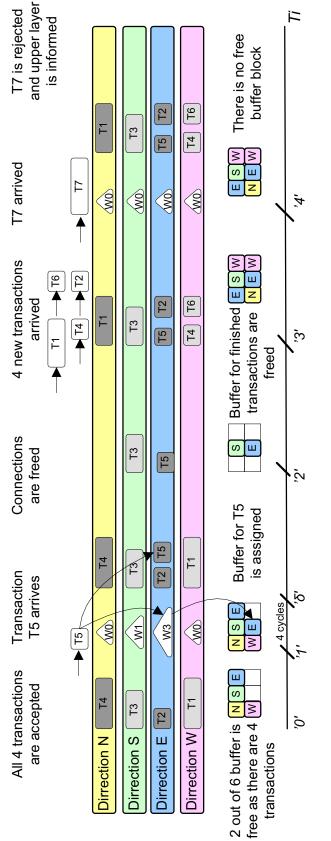

| 7.5                                                                                                                                                                                                                                       | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117                                                                                                                                          |

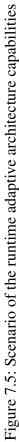

| 7.6                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 118                                                                                                                                          |

| 7.7                                                                                                                                                                                                                                       | 5 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 122                                                                                                                                          |

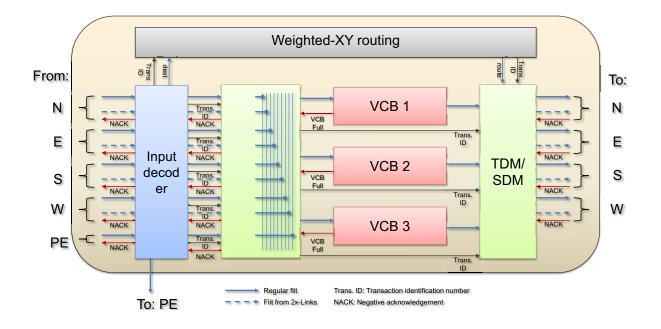

| 7.8                                                                                                                                                                                                                                       | 1 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123                                                                                                                                          |

| 7.9                                                                                                                                                                                                                                       | An overview of the AdNoC architecture-level part in each router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125                                                                                                                                          |

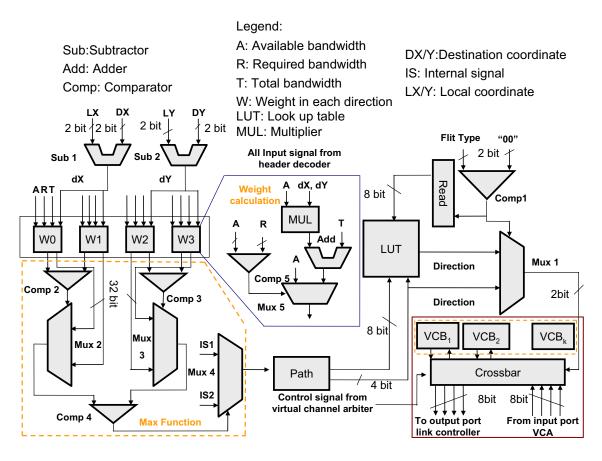

| 7.10                                                                                                                                                                                                                                      | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                                                                                          |

|                                                                                                                                                                                                                                           | Hardware implementation of the 2X-Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 128                                                                                                                                          |

|                                                                                                                                                                                                                                           | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 129                                                                                                                                          |

|                                                                                                                                                                                                                                           | Hardware for adding and analyzing monitoring events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 130                                                                                                                                          |

| 7.14                                                                                                                                                                                                                                      | Details of the hardware prototype of the proposed AdNoC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 131                                                                                                                                          |

|                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| 8.1                                                                                                                                                                                                                                       | Exemplary router module: ".ned" file with one output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134                                                                                                                                          |

| 8.1<br>8.2                                                                                                                                                                                                                                | Exemplary router module: ".ned" file with one output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134<br>135                                                                                                                                   |

|                                                                                                                                                                                                                                           | Exemplary configuration ".ini" file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| 8.2                                                                                                                                                                                                                                       | Exemplary configuration ".ini" file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 135                                                                                                                                          |

| 8.2<br>8.3                                                                                                                                                                                                                                | Exemplary configuration ".ini" file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 135<br>136                                                                                                                                   |

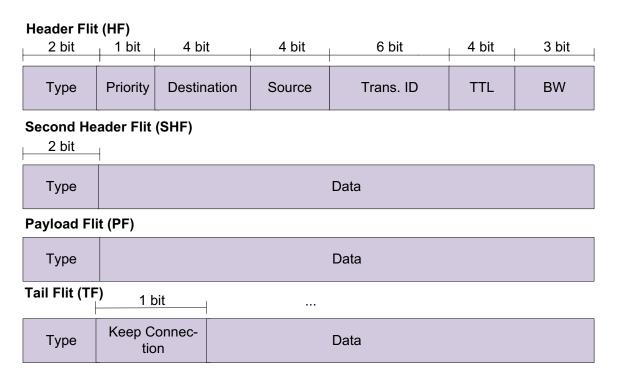

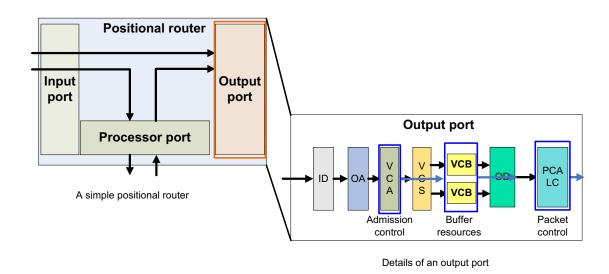

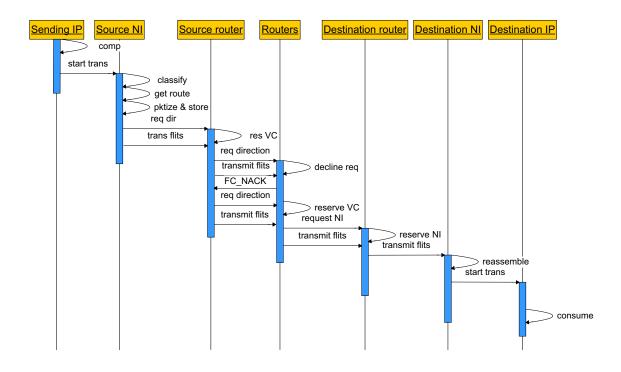

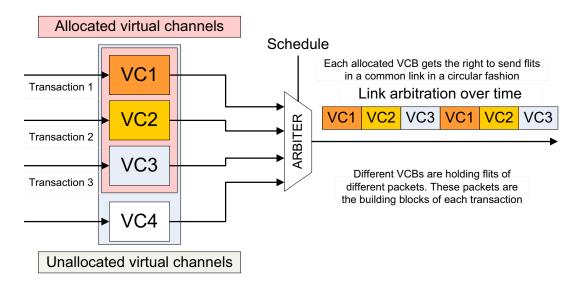

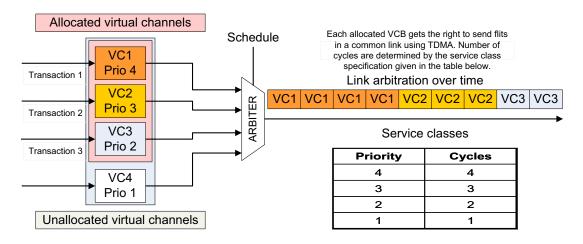

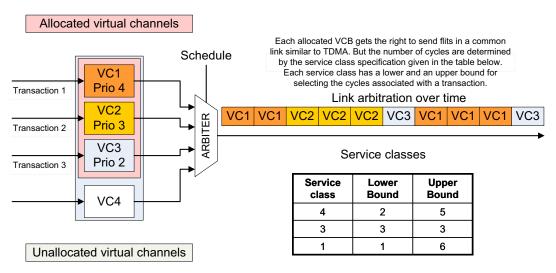

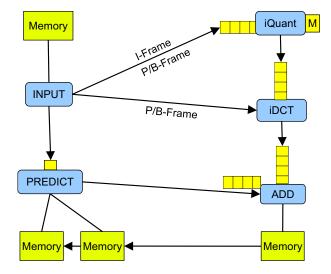

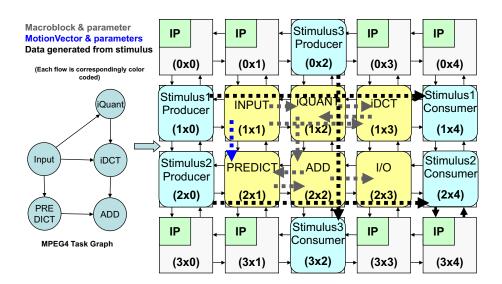

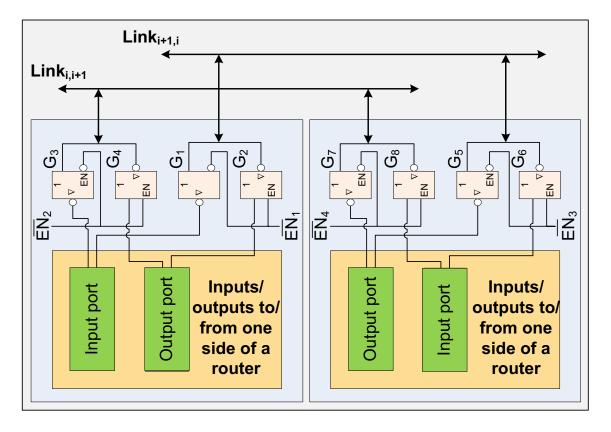

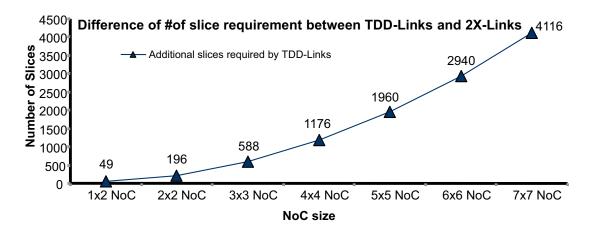

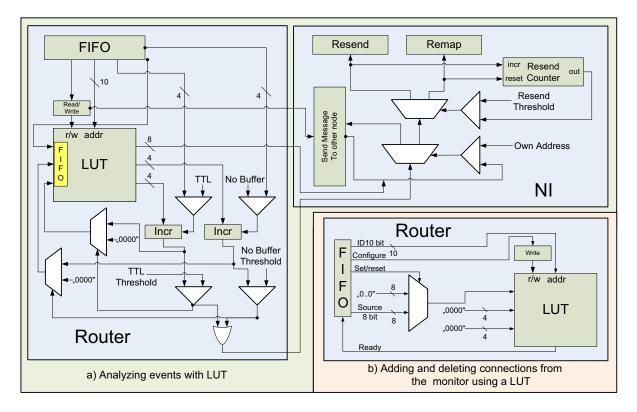

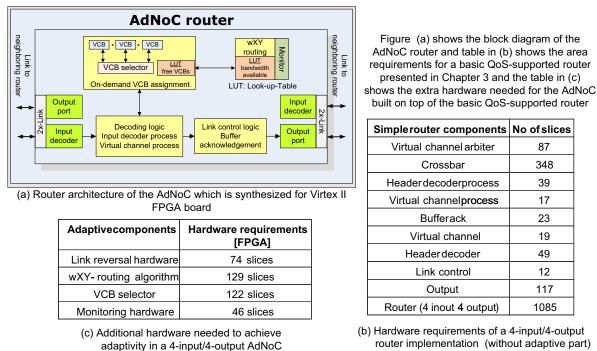

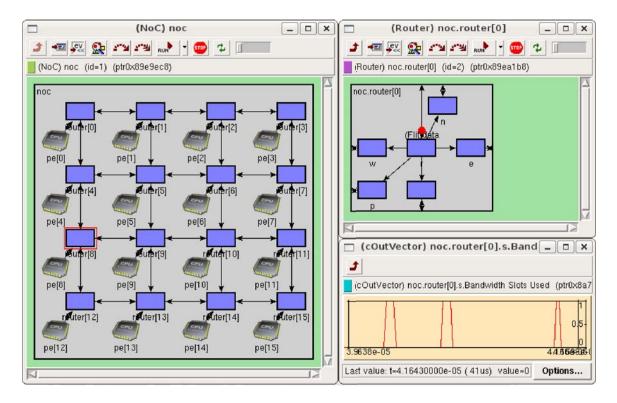

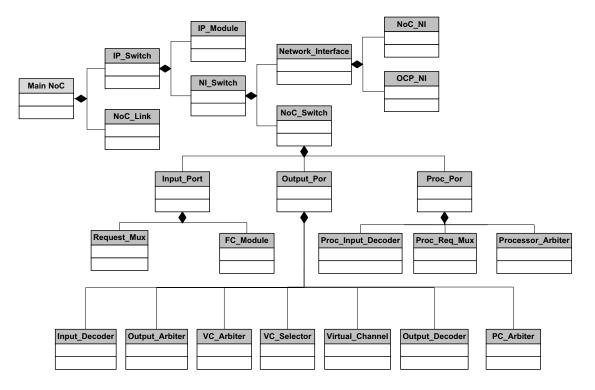

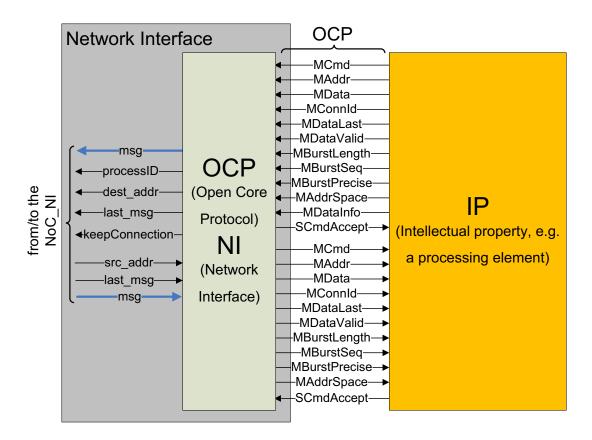

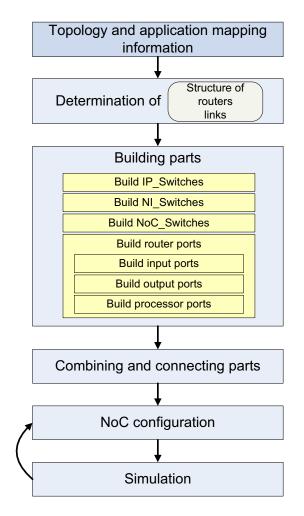

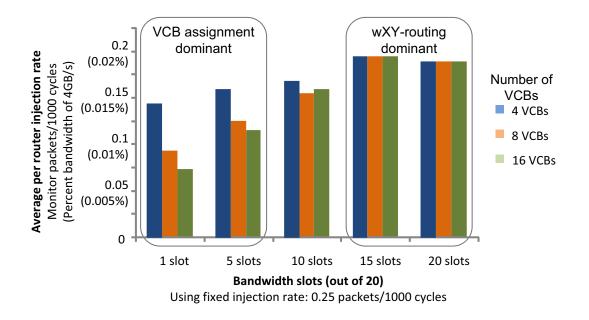

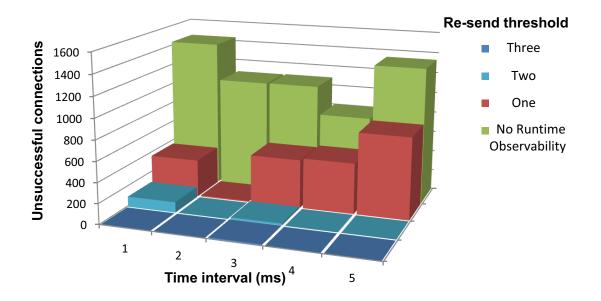

| 8.2<br>8.3<br>8.4                                                                                                                                                                                                                         | Exemplary configuration ".ini" file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 135<br>136<br>138                                                                                                                            |