## Algorithm Libraries for Multi-Core Processors

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften

> der Fakultät für Informatik des Karlsruher Instituts für Technologie

> > genehmigte Dissertation

von Dipl.-Inform. Johannes Singler aus Offenburg

Karlsruhe, Juli 2010

Tag der mündlichen Prüfung:8. Juli 2010Referent:Prof. Dr. Peter SandersKorreferent:Prof. Dr. Ulrich Meyer

Beginning in 2005, the advent of microprocessors with multiple CPU cores on a single chip has lead to a paradigm shift in computer science. Since the clock rates stagnate, there is no automatic performance increase anymore when switching to a newer processor. Instead, in order to achieve an acceleration, a program has to be executed in parallel on the multiple cores. This fact poses an immense challenge to the development of high-performance applications. Not only are multi-core processors ubiquitous nowadays, application developers are also forced to utilize them to avoid stagnation of performance.

In this thesis, we examine an approach that facilitates the development of applications that exploit parallelism. We implement parallelized variants of established algorithm libraries, which provide the same functionality as their sequential versions but execute faster by utilizing the multiple cores. This allows developers to use parallelism implicitly, encapsulated by the unaltered interface of the algorithm.

For a start, we consider a library for basic algorithms for internal (main) memory, the C++ Standard Template Library (STL). We data-parallelize its algorithms in the shared memory model, including algorithms for specific data structures, building the Multi-Core Standard Template Library (MCSTL).

Geometric algorithms are addressed next, by parallelizing selected routines of the *Computational Geometry Algorithms Library*, facilitated by the usage of MCSTL routines.

We apply MCSTL also to speed up internal computation for basic external memory algorithms, which efficiently handle large data sets stored on disks. In combination with some task parallelism for algorithmic stages on a higher level, this enables the *Standard Template Library for XXL Data Sets* (STXXL) to exploit multi-core parallelism.

The libraries had already been widely used in their sequential versions, so applications that employ them can immediately benefit from the improved speed.

We carry out experiments on the implementations, and evaluate the performance in detail, also relating to hardware limitations like the memory bandwidth and the disk bandwidth. Case studies using MCSTL and STXXL demonstrate the benefit of the libraries to algorithmic applications.

Finally, as a starting point of a generalization to distributed memory, and as an advanced application of the MCSTL and the STXXL, we design distributed external memory sorting algorithms for very large inputs. The implementation of the more practical algorithm set two performance world records in 2009.

### **Deutsche Zusammenfassung**

Beginnend mit dem Jahr 2005 hat das Aufkommen von Prozessoren mit mehreren Rechenkernen auf einem Chip zu einem Paradigmenwechsel in der Informatik geführt. Da gleichzeitig die Taktfrequenzen nicht weiter steigen, ergibt sich eine Leistungssteigerung nun nun nicht mehr automatisch beim Verwenden eines neuen Prozessors. Vielmehr muss durch die parallele Ausführung eines Programms auf mehreren Rechenkernen eine Beschleunigung erreicht werden. Diese Tatsache ist eine große Herausforderung für das Entwickeln leistungsfähiger Anwendungen. Mehrkern-Prozessoren sind inzwischen nicht nur allgegenwärtig, Software-Entwickler müssen deren Fähigkeiten auch ausschöpfen, um eine Stagnation der Rechenleistung zu verhindern.

In dieser Arbeit untersuchen wir einen Ansatz, um das Entwickeln von Anwendungen, die Parallelismus ausnutzen, zu erleichtern: Wir implementieren parallelisierte Varianten von Algorithmenbibliotheken. Diese bieten die gleiche Funktionalität wie ihre sequentiellen Versionen, ihre Routinen laufen jedoch beschleunigt, da sie mehrere Rechenkerne nutzen. Die Verwendung solcher Bibliotheken ermöglicht einem Software-Entwickler impliziten Parallelismus, gekapselt durch die gleichbleibende Schnittstelle des Algorithmus.

Wir konzentrieren uns auf etablierte C++-Bibliotheken, als Rahmenwerk zur Verwaltung von Threads wählen wir OpenMP.

Zunächst betrachten wir eine Bibliothek für grundlegende Algorithmen im Hauptspeicher, die Standard Template Library (STL), welche Teil der C++-Standardbibliothek ist. Ihre Algorithmen werden daten-parallelisiert und ergeben somit die Multi-Core Standard Template Library (MCSTL). Diese ist geeignet für Parallelrechner mit gemeinsamem Speicher, insbesondere also Mehrkern-Rechner. Sie enthält Routinen wie z. B. suchen, partitionieren, mischen, sortieren, und zufällig permutieren. Wir wählen geeignete parallele Algorithmen für die einzelnen Routinen aus, passend zu den Gegebenheiten.

Desweiteren entwerfen wir Algorithmen zur Manipulation spezieller Datenstrukturen. Für das Einfügen großer Datenmengen in ein assoziatives Feld bzw. dessen Konstruktion aus einer großen Eingabemenge betrachten wir parallele Algorithmen für Rot-Schwarz-Bäume. Um auch für Sequenzen, die nicht wahlfrei zugreifbar sind, Daten-Parallelisierung zu ermöglichen, entwerfen wir einen Algorithmus, der sie in nur einem sequentiell Durchlauf in ungefähr gleich große Teile zerteilt, ohne anfangs die Länge zu kennen.

Die Leistung aller Algorithmen und ihrer Implementierungen wird ausführlich mit Experimenten auf verschiedenen Rechnern evaluiert. Dabei werden auch Beschränkungen der Hardware berücksichtigt, z. B. die geteilte Speicherbandbreite. Es werden meist gute bis sehr gute Beschleunigungswerte erreicht, oft auch schon für relative kleine Eingaben, ab einer sequentiellen Laufzeit von 100 Mikrosekunden.

Die softwaretechnischen Aspekten der Integration der parallelisierten Routinen in eine existierende Bibliothek werden ebenfalls diskutiert. Hier ist insbesondere die Erhaltung der Semantik ein Kernthema.

Zwei Fallstudien demonstrieren die Verwendbarkeit der MCSTL-Routinen als Unterprogramme in algorithmischen Anwendungen. Zuerst betrachten wir die Konstruktion eines Suffix Arrays, einer Indexdatenstruktur für Volltextsuche. Durch Verwendung der parallelisierten Routinen als Unterprogramme wird eine existierende Implementierung um Faktor 5 beschleunigt. Außerdem wird eine Variante des Kruskal-Algorithmus zum Berechnen des minimalen Spannbaums durch die Parallelisierung mittels der MCSTL so viel schneller, dass sie andere, nicht parallelisierbare Algorithmen hinter sich lässt.

Aus dem Gebiet der algorithmischen Geometrie werden einige ausgewählte Routinen der Computational Geometry Algorithms Library (CGAL) parallel implementiert, auch unter Zuhilfenahme von MCSTL-Routinen.

Das Sortieren entlang der raumfüllenden Hilbert-Kurve dient vor allem als Vorverarbeitungsschritt anderer Algorithmen, und benötigt die Parallelisierung, um die Skalierbarkeit jener Algorithmen nicht zu gefährden.

Der Schnitt achsenparalleler (Hyper-)Quader wird oft als Heuristik in der Kollisionserkennung verwendet. Nur falls sich die einhüllenden achsenparallelen Quader zweier Objekte schneiden, muss detailliert untersucht werden, ob sich die eigentlichen Objekte tatsächlich schneiden.

Die Konstruktion der Delaunay-Triangulierung in 3 Dimensionen ist Teil vieler Verfahren zur Manipulation von 3D-Objekten. Im Gegensatz zu den bisherigen Algorithmen verwenden wir hier feingranulare Sperren zur Synchronisation während des konkurrierenden Zugriffs auf die Datenstruktur. Während für die beiden ersten Probleme gute Beschleunigungen erzielt werden, sind diese für die Delaunay-Triangulierung sogar sehr nah am Optimum.

Im weiteren werden Externspeicher-Algorithmen betrachtet, welche große Datenmengen bearbeiten, die auf Grund ihrer Größe nicht mehr in den Hauptspeicher passen, und deshalb auf Festplatte(n) gespeichert sind. Die Routinen der MCSTL werden verwendet, um die interne Rechenarbeit zu beschleunigen. In Kombination mit einem Rahmenwerk zur parallelen Ausführung von Aufgaben auf einer höheren algorithmischen Ebene wird damit auch der Standard Template Library for XXL Data Sets (STXXL) Mehrkern-Parallelismus ermöglicht.

Damit können wir die Lücke zwischen immer größerer Bandbreite der Festplatten und stagnierender Taktfrequenz der Prozessoren verkleinern. Anwendungsbeispiel ist hier wiederum

die Konstruktion eines Suffix Array, dieses Mal für noch größere Eingaben. Wir können diverse Externspeicher-Algorithmen für dieses Problem signifikant beschleunigen.

Alle erwähnten Bibliotheken hatten in ihren sequentiellen Versionen bereits eine große Verbreitung gefunden. Außerdem sind diese inklusive der parallelisierten Varianten frei verfügbar. Somit können Anwendungen, die sie verwenden, direkt von der höheren Geschwindigkeit profitieren.

Schließlich entwerfen wir Algorithmen zum Sortieren sehr großer Datenmengen auf Rechnerbündeln mit verteiltem Speicher und mehreren Festplatten pro Rechenknoten. Dies dient einerseits als Startpunkt für eine Verallgemeinerung der bisherigen Arbeit auf Systeme mit verteiltem Speicher, andererseits als ein weiteres, komplexes Anwendungsbeispiel der MCSTL und der STXXL. Die Implementierung der praktischeren Algorithmen-Variante wird wiederum ausführlich experimentell evaluiert und analysiert. Im Vergleich mit Konkurrenz-Implementierungen schneidet sie exzellent ab, sie erzielte 2009 zwei Leistungs-Weltrekorde, für ca. 1 Terabyte und 100 Terabyte an Daten. Die Leistung relativ zum Hardwareaufwand lag dabei eine Größenordnung über konkurrierenden Ansätzen.

# Contents

| 1 | Intro | oduction                                          | 1  |

|---|-------|---------------------------------------------------|----|

|   | 1.1   | Historical Development                            | 1  |

|   | 1.2   | Motivation                                        | 2  |

|   |       | 1.2.1 Basic Approach                              | 3  |

|   | 1.3   | Parallelism Available in Hardware                 | 4  |

|   | 1.4   | Models of Parallelism                             | 5  |

|   | 1.5   | Metrics                                           | 7  |

|   | 1.6   | Thesis Overview                                   | 8  |

| 2 | Rec   | urring Algorithms                                 | 9  |

|   | 2.1   | Multiway Selection/Partitioning                   | 9  |

|   | 2.2   | Multiway Merging                                  | 10 |

|   | 2.3   | Multiway Mergesort                                | 11 |

| 3 | Plat  | lform                                             | 12 |

|   | 3.1   | C++                                               | 12 |

|   | 3.2   | Platform Support for Threading                    | 12 |

|   | 3.3   | Platform Support for Distributed-Memory Computing | 16 |

|   | 3.4   | Machines for Experimental Evaluation              | 16 |

| 4 | Bas   | ic Internal Memory Algorithms                     | 19 |

|   | 4.1   | Related Work                                      | 21 |

|   | 4.2   | Algorithms                                        | 21 |

|   |       | 4.2.1 Experimental Results                        | 28 |

|   | 4.3   | Dictionary Bulk Construction and Insertion        | 42 |

|   | 4.4   | Software Engineering                              | 46 |

|   | 4.5   | Treating Sequences without Random Access          | 54 |

|   |       | 4.5.1 Single-Pass List Partitioning Algorithm     | 55 |

|   |       | 4.5.2 Experimental Results and Conclusion         | 55 |

|   | 4.6   | Case Studies                                      | 58 |

|   |       | 4.6.1 Suffix Array Construction                   | 58 |

|   |       | 4.6.2 Minimum Spanning Trees                      | 62 |

|   | 4.7   | Conclusions and Future Work                       | 64 |

| 5 | Geo   | ometric Algorithms                                | 66 |

|   | 5.1   | Spatial Sort                                      | 67 |

| 8 | 7.4<br>7.5<br>7.6<br><b>Cor</b><br>8.1<br>8.2 | 7.3.2Multiway Partitioning1037.3.3External All-to-All1037.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects109Implementation111Experimental Results112Conclusions and Future Work116Impact116Future Work117 |

|---|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 | 7.5<br>7.6<br><b>Cor</b>                      | 7.3.3External All-to-All1037.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects100Implementation11Experimental Results112Conclusions and Future Work113Inclusions116                                         |

|   | 7.5                                           | 7.3.3External All-to-All1037.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects100Implementation11Experimental Results112                                                                                    |

|   | 7.5                                           | 7.3.3External All-to-All1037.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects100Implementation11Experimental Results112                                                                                    |

|   |                                               | 7.3.3External All-to-All1007.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects100Implementation11                                                                                                           |

|   |                                               | 7.3.3External All-to-All1037.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT1007.3.6Practical Aspects100                                                                                                                           |

|   |                                               | 7.3.3External All-to-All1027.3.4Analysis Summary1007.3.5Analysis of Data Redistribution for CANONICALMERGESORT100                                                                                                                                                    |

|   |                                               | 7.3.3       External All-to-All       100         7.3.4       Analysis Summary       100                                                                                                                                                                             |

|   |                                               | 7.3.3 External All-to-All                                                                                                                                                                                                                                            |

|   |                                               | J 8                                                                                                                                                                                                                                                                  |

|   |                                               |                                                                                                                                                                                                                                                                      |

|   |                                               | 7.3.1 Internal Memory Parallel Sorting 104                                                                                                                                                                                                                           |

|   | 7.3                                           | CANONICALMERGESORT                                                                                                                                                                                                                                                   |

|   |                                               | 7.2.1 Prefetching Details                                                                                                                                                                                                                                            |

|   | 7.2                                           | Mergesort with Global Striping                                                                                                                                                                                                                                       |

|   | 7.1                                           | Related Work                                                                                                                                                                                                                                                         |

| 7 | Dist                                          | tributed External Memory Sorting 100                                                                                                                                                                                                                                 |

|   | 6.5                                           | Conclusions and Future Work                                                                                                                                                                                                                                          |

|   |                                               | 6.4.1 Application test                                                                                                                                                                                                                                               |

|   | 6.4                                           | Experiments                                                                                                                                                                                                                                                          |

|   |                                               | 6.3.3 Implementation details                                                                                                                                                                                                                                         |

|   |                                               | 6.3.2STXXL Asynchronous Pipelining8                                                                                                                                                                                                                                  |

|   | 0.5                                           | 6.3.1 STXXL Conventional Pipelining                                                                                                                                                                                                                                  |

|   | 6.3                                           | Task parallelism through asynchronous pipelining       8:                                                                                                                                                                                                            |

|   | 6.1<br>6.2                                    | Parallelizing STXXL algorithms using the MCSTL                                                                                                                                                                                                                       |

| 6 | <b>Bas</b> 6.1                                | Sic External Memory Algorithms       83         Related work       84                                                                                                                                                                                                |

|   | 5.4                                           | Conclusions and Future Work                                                                                                                                                                                                                                          |

|   |                                               | 5.3.2 Experimental Results                                                                                                                                                                                                                                           |

|   |                                               | 5.3.1 Parallel Algorithm                                                                                                                                                                                                                                             |

|   | 5.3                                           | 3D Delaunay Triangulation                                                                                                                                                                                                                                            |

|   |                                               | 5.2.3 Experimental results                                                                                                                                                                                                                                           |

|   |                                               | 5.2.2 Parallelization                                                                                                                                                                                                                                                |

|   | 0.2                                           | 5.2.1 Sequential Algorithm                                                                                                                                                                                                                                           |

|   | 5.2                                           | d-dimensional Box Intersection                                                                                                                                                                                                                                       |

|   |                                               | 5.1.1Parallel Algorithm65.1.2Experimental results6                                                                                                                                                                                                                   |

|   |                                               | 5.1.1 Parallel Algorithm                                                                                                                                                                                                                                             |

# **List of Tables**

| 1.1 | Notation used in Chapters 2 to 6                                                  | 8   |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.1 | Technical Details of the Test Machines.                                           | 17  |

| 3.2 | Memory bandwidths of the machines tested on, measured using the Stream benchmark. | 18  |

| 4.1 | Parallelization status of STL functions                                           | 22  |

| 4.2 | Executable sizes and compilation time for different algorithm variants            | 52  |

| 4.3 | Pseudocode for the SINGLEPASS list partitioning algorithm.                        | 56  |

| 6.1 | Source code for a simple linear STXXL pipeline.                                   | 89  |

| 6.2 | Pipeline with an async pull node added between two scanning nodes                 | 89  |

| 6.3 | Processing a external memory priority queue with 8 byte elements                  | 95  |

| 6.4 | Suffix array creation using different algorithm and STXXL features                | 96  |

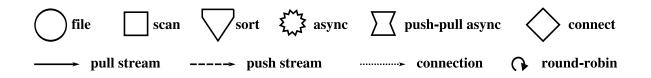

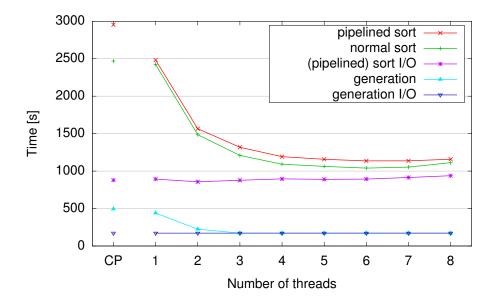

| 6.5 | Diamond flow graph running times.                                                 | 96  |

| 7.1 | Symbols used in the context of distributed memory external sorting                | 101 |

# **List of Figures**

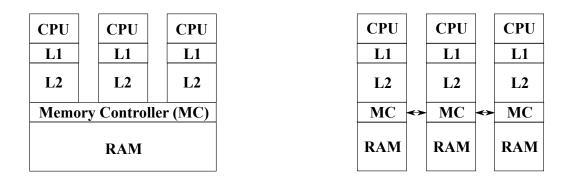

| 1.1<br>1.2 | Schema for Uniform Memory Architecture                                        | 5<br>5   |

|------------|-------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | Schema of parallel multiway merging                                           | 10<br>11 |

| 3.1        | Schema of fork-join parallelism.                                              | 13       |

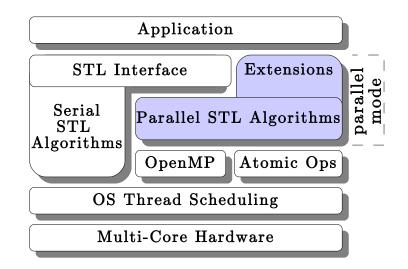

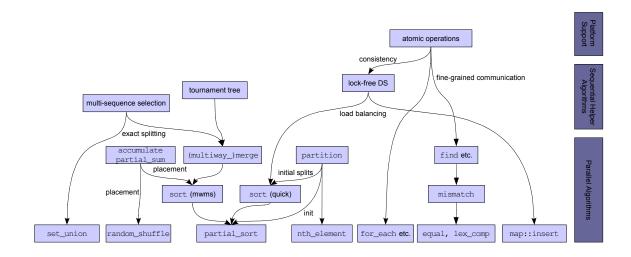

| 4.1        | Abstraction layers of the MCSTL/the libstdc++ parallel mode                   | 20       |

| 4.2        | Visualization of the parallel find algorithm                                  | 25       |

| 4.3        | Schema of parallel balanced quicksort.                                        | 27       |

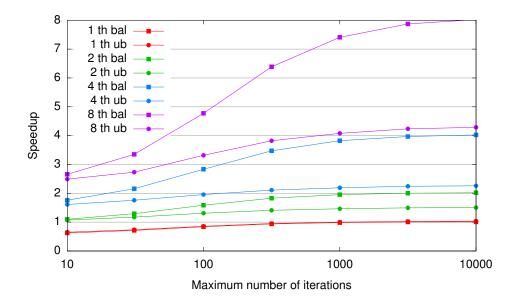

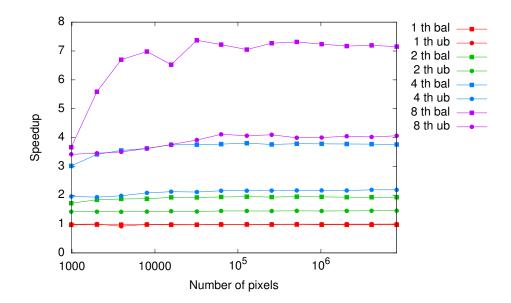

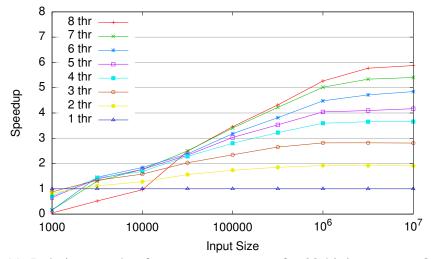

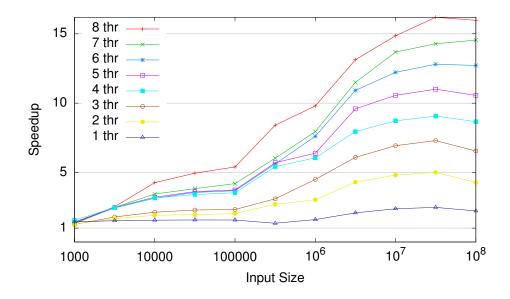

| 4.4        | Speedup for computing the Mandelbrot fractal with 1000000 pixels on           |          |

|            | OPTERON.                                                                      | 30       |

| 4.5        | Speedup for computing the Mandelbrot fractal with a maximum of 1000 itera-    |          |

|            | tions on OPTERON. bal stands for balanced, ub for unbalanced                  | 30       |

| 4.6        | Speedup for finding a 32-bit integer at uniformly random position             | 31       |

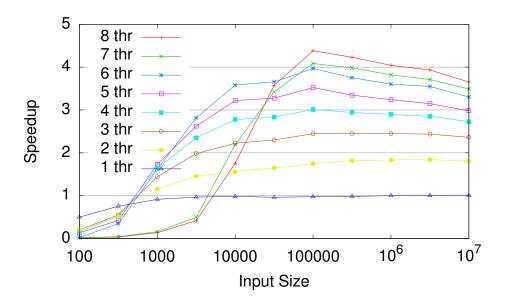

| 4.7        | Speedup for computing partial sums of 32-bit integers on XEON                 | 32       |

| 4.8        | Speedup for effectively computing partial products of floats by adding up the |          |

|            | logarithms on XEON                                                            | 32       |

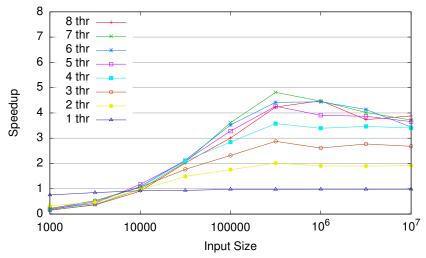

| 4.9        | Speedup for partitioning 32-bit integers on OPTERON                           | 34       |

| 4.10       | Speedup for nth_element for 32-bit integers on OPTERON                        | 34       |

| 4.11       | Relative speedup for partial_sort for 32-bit integers on OPTERON              | 34       |

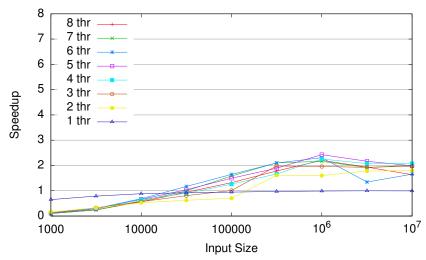

| 4.12       | Relative speedup for 2-way merging 32-bit integers on OPTERON                 | 35       |

| 4.13       | Relative speedup for 4-way merging 32-bit integers on OPTERON                 | 35       |

| 4.14       | Relative speedup for 16-way merging 32-bit integers on OPTERON                | 35       |

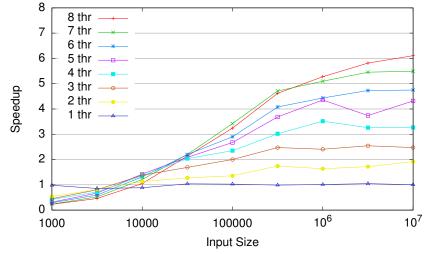

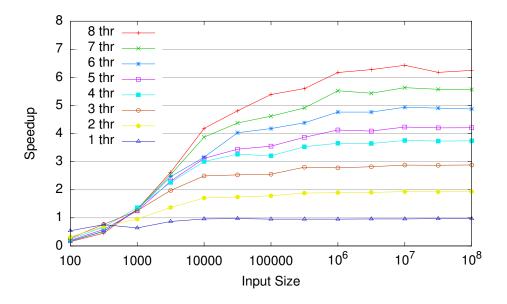

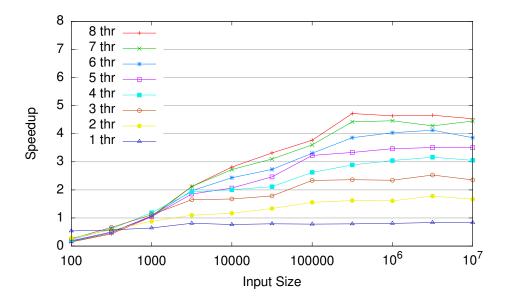

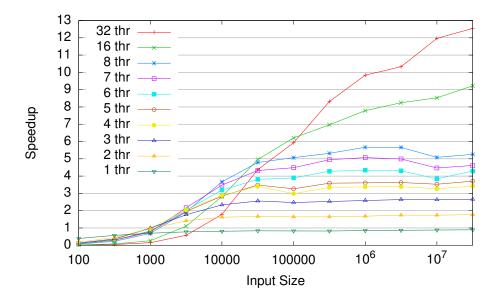

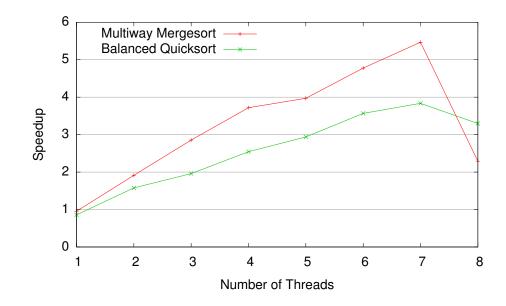

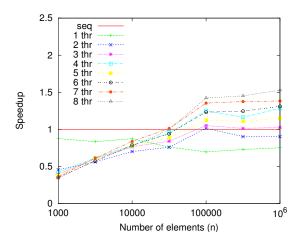

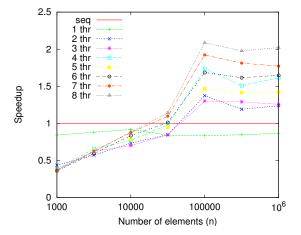

| 4.15       | Speedup for multiway mergesort on 32-bit integers on OPTERON                  | 37       |

|            | Speedup for sorting pairs of 64-bit integers on OPTERON                       | 37       |

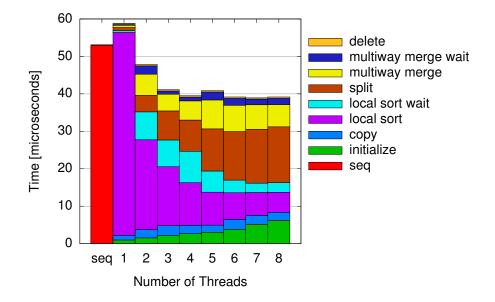

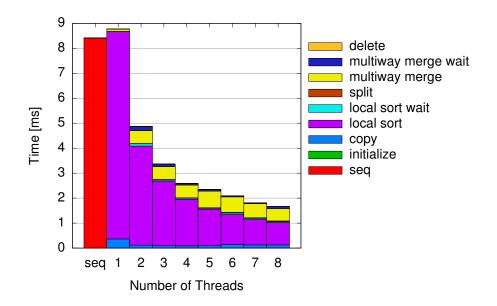

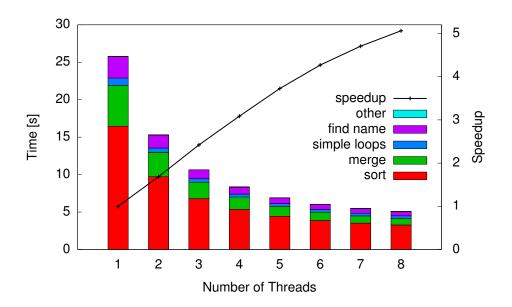

| 4.17       | Detailed timing breakdown for for multiway mergesort on 1000 32-bit integers  |          |

|            | on Opteron                                                                    | 38       |

| 4.18       | Detailed timing breakdown for for multiway mergesort on 100 000 32-bit        |          |

|            | integers on OPTERON                                                           | 38       |

|            | Speedup for sorting pairs of 64-bit integers on SUN T1                        | 39       |

| 4.20       | Speedup for multiway mergesort on equal 32-bit integers on OPTERON with       |          |

|            | sampling                                                                      | 39       |

| 4.21       |                                                                               |          |

|            | core is permanently blocked by another program.                               | 40       |

| 4.22 | Speedup for set union on 32-bit integers on OPTERON. The input size refers to    |          |

|------|----------------------------------------------------------------------------------|----------|

|      | the length of each of the two sequences.                                         | 41       |

| 4.23 | Speedup for Random shuffling 64-bit integers on OPTERON                          | 42       |

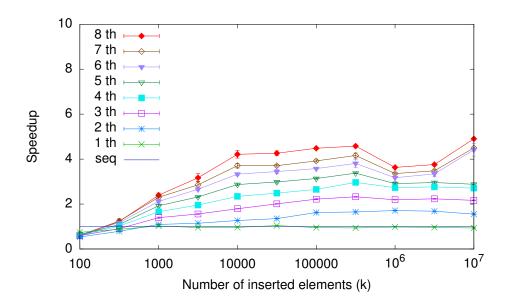

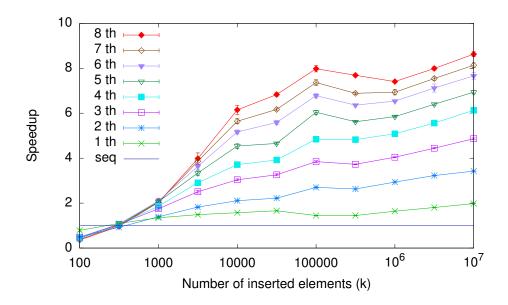

| 4.24 | Speedup for constructing a set of integers on XEON                               | 44       |

| 4.25 | Speedup for inserting integers into a set $(r = 0.1)$ on XEON                    | 45       |

| 4.26 | Speedup for inserting integers into a set $(r = 10)$ on XEON                     | 45       |

| 4.27 | Schema of code reuse inside the parallel mode.                                   | 50       |

| 4.28 | Minimal sorting code example with call stack.                                    | 51       |

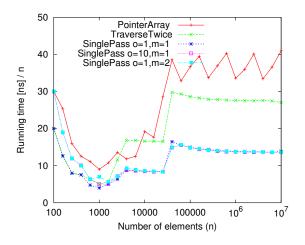

| 4.29 | Running times of the list partitioning algorithms for $p = 4$                    | 56       |

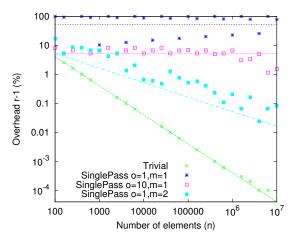

| 4.30 | Quality of the list partitioning algorithms for $p = 4$                          | 56       |

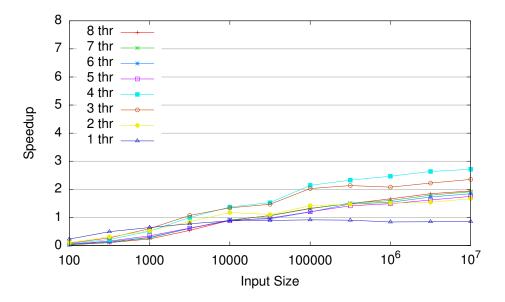

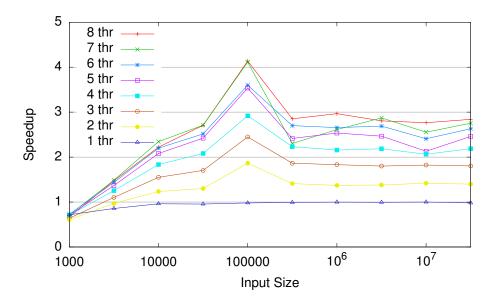

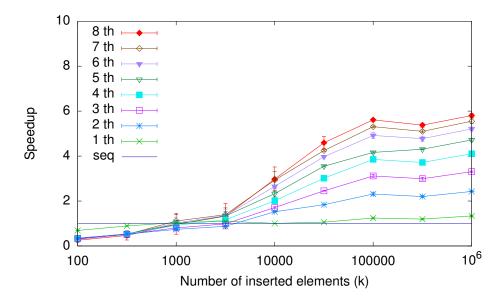

| 4.31 | Speedup for STL list sort using TRAVERSETWICE partitioning                       | 57       |

| 4.32 | Speedup for STL list sort using SINGLEPASS partitioning                          | 57       |

| 4.33 | Speedup for suffix array construction on random strings on OPTERON               | 60       |

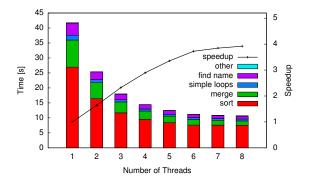

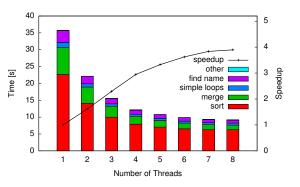

| 4.34 | Detailed timings for suffix array construction.                                  | 61       |

| 4.35 | Speedup for suffix array construction on the Gutenberg data set.                 | 61       |

| 4.36 | Speedup for suffix array construction on the Source data set on OPTERON          | 61       |

|      | Pseudocode for the Filter-Kruskal algorithm.                                     | 63       |

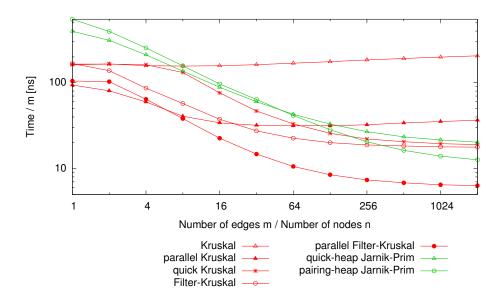

| 4.38 | MST computation for random graphs with $2^{16}$ nodes on OPTERON                 | 64       |

|      |                                                                                  |          |

| 5.1  | Speedup for 2D Hilbert sort on OPTERON                                           | 68       |

| 5.2  | Speedup for 3D Hilbert sort on OPTERON                                           | 69       |

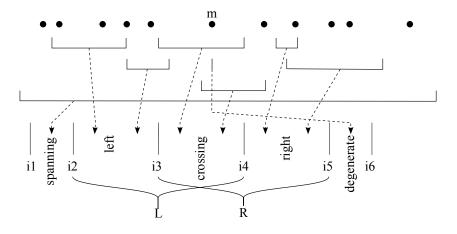

| 5.3  | Partitioning the sequence of box intervals.                                      | 70       |

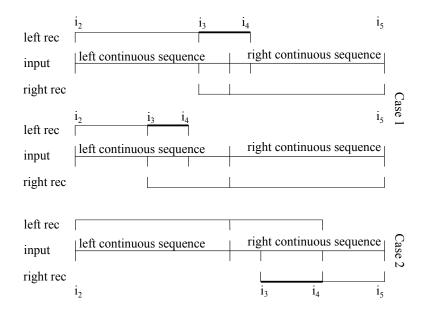

| 5.4  | Two cases for treating the split sequence of box intervals                       | 71       |

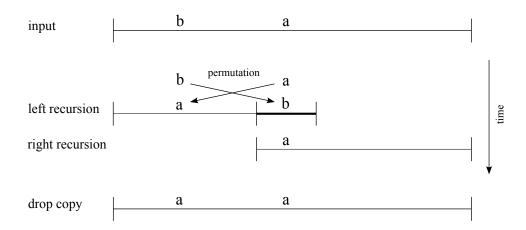

| 5.5  | Problem in copying elements for recursion.                                       | 73       |

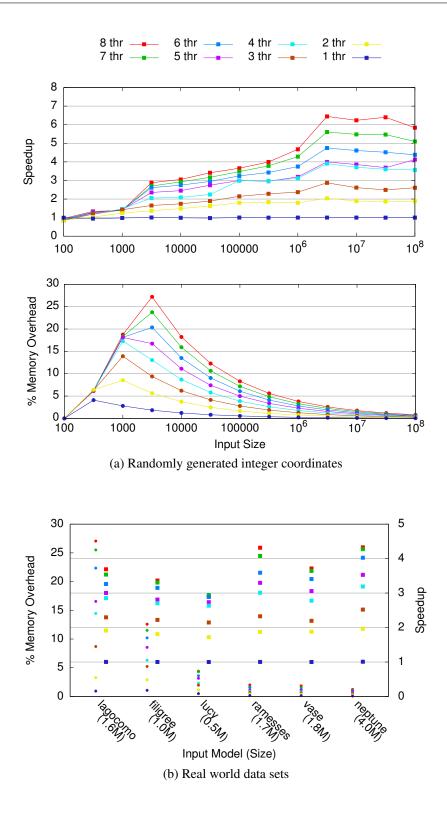

| 5.6  | Speedup and relative memory overhead for intersecting boxes on OPTERON           | 74       |

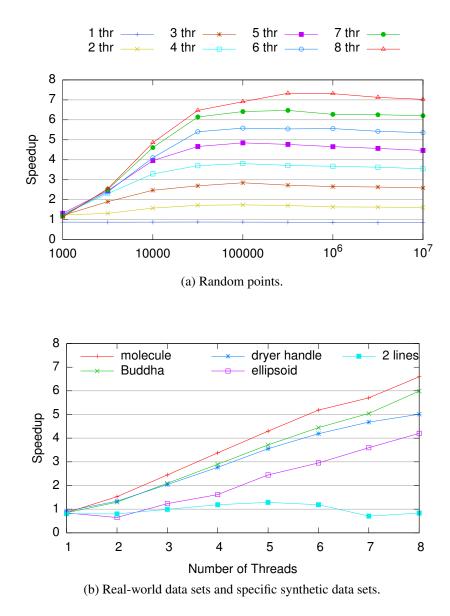

| 5.7  | Speedups for 3D Delaunay triangulation on OPTERON.                               | 80       |

| 5.8  | Breakdown of running time for sequential and parallel Delaunay construction.     | 81       |

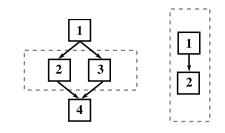

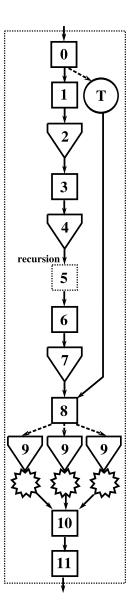

| 6.1  | Basic example for STXXL pipelining.                                              | 86       |

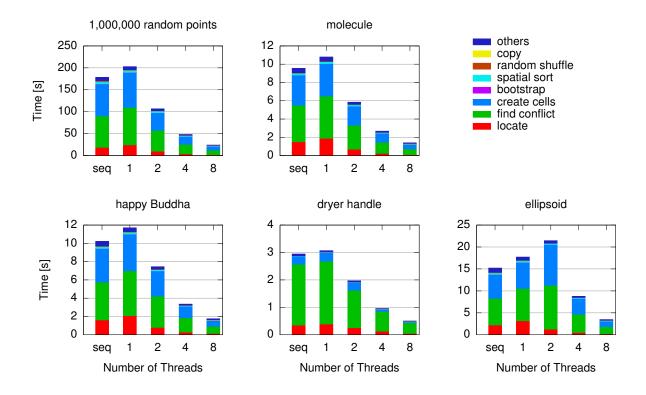

| 6.2  | Split-up sorting node in context.                                                | 80<br>87 |

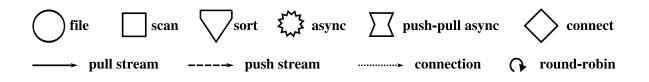

| 6.3  | Horizontal (left) and vertical (right) task parallelism for nodes 1 and 2        | 88       |

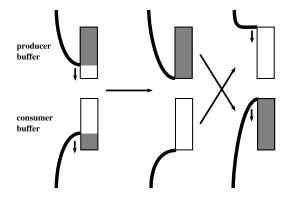

| 6.4  | Swapping pipelining buffers.                                                     | 90       |

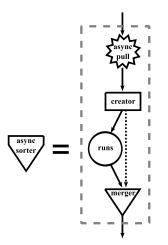

| 6.5  | Equivalent for asynchronous sorting node.                                        | 90       |

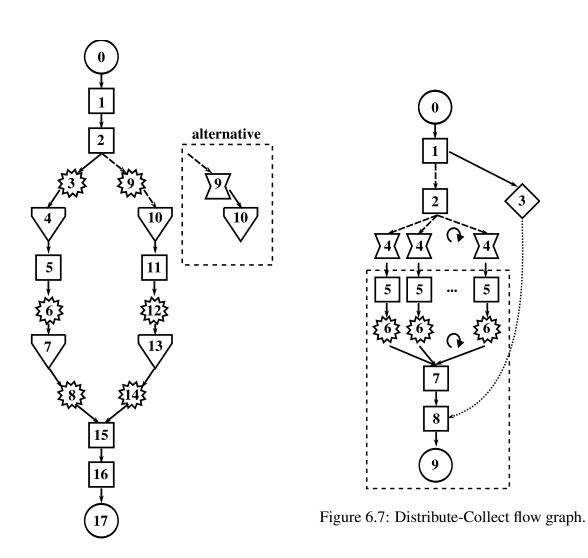

| 6.6  | Diamond flow graph.                                                              | 91       |

| 6.7  | Distribute-Collect flow graph.                                                   | 91       |

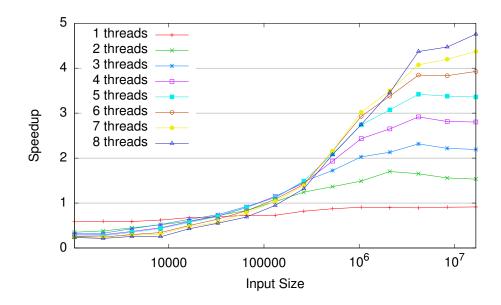

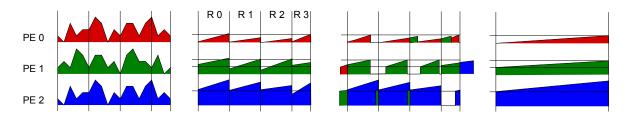

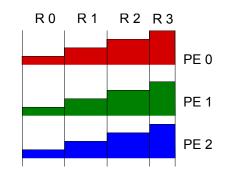

| 6.8  | Sorting 100 GiB of 64-bit unsigned integer pairs.                                | 95       |

| 6.9  | Doubling/ quadrupling flow graph.                                                | 93<br>98 |

|      | DC3 flow graph.                                                                  | 98       |

| 0.10 |                                                                                  | 90       |

| 7.1  | Schema of CANONICALMERGESORT                                                     | 104      |

| 7.2  | Bad input for CANONICALMERGESORT.                                                | 108      |

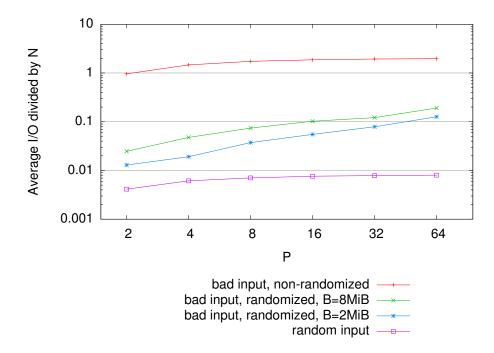

| 7.3  | I/O volume for the all-to-all phase for different inputs with/without randomiza- |          |

|      | tion, average over all nodes.                                                    | 110      |

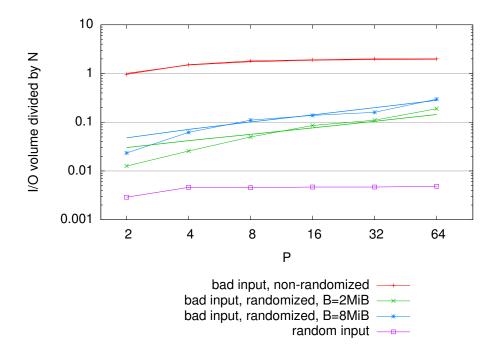

| 7.4 | I/O volume for the all-to-all phase for different inputs with/without random- |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | ization, for the likely most affected middle node. The solid lines give the   |     |

|     | theoretical estimations.                                                      | 110 |

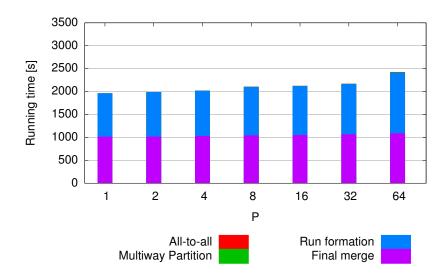

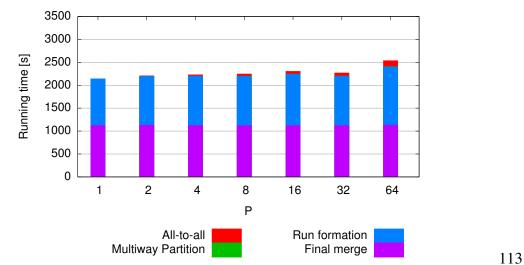

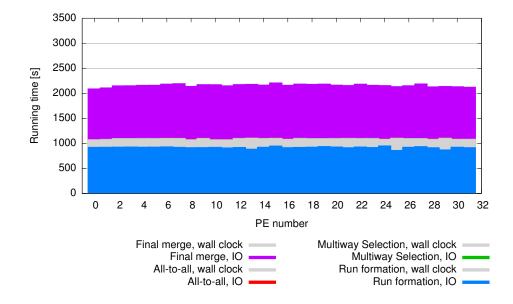

| 7.5 | Running times for random input to CANONICALMERGESORT                          | 113 |

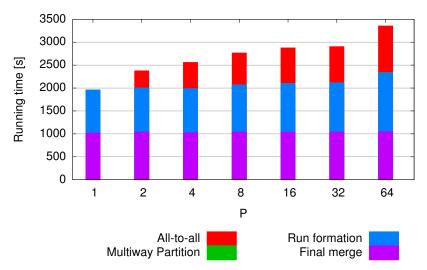

| 7.6 | Running times for worst-case input to CANONICALMERGESORT without              |     |

|     | randomization applied.                                                        | 113 |

| 7.7 | Running times for worst-case input to CANONICALMERGESORT with random-         |     |

|     | ization applied.                                                              | 113 |

| 7.8 | Running times of the different phases of CANONICALMERGESORT                   | 114 |

## **1** Introduction

### **1.1 Historical Development**

Until 2004, the clock rates of microprocessors were continuously rising. Application performance benefitted from this fact with hardly any effort from the software developers.

This development came to an end in 2005 [Ros08] for reasons stemming from semiconductor technology. Higher clock rates imply higher heat dissipation, and while the computing power grows at most linearly with the clock rate on a given design, the energy consumption grows superlinearly. This is caused by the higher voltage needed to make the transistors switching more quickly. Intel reported that underclocking a certain processor by 20% actually halves the energy consumption, but sacrifices only about 13% of performance [Ros08]. This correlation makes further clock rate increase very inefficient, also in terms of monetary cost, since more powerful cooling devices are more expensive, not to speak of the increased noise level for desktop computers. There is also the cost for the electrical energy itself, growing more important, in particular for the case of large data centers. For portable machines, a higher energy consumption lowers battery lifetime, which is unacceptable in many settings. In addition to the energy consumption problems, the speed of light limits the distance a signal can travel in a clock cycle to a few centimeters, making synchronization across the whole chip increasingly difficult.

Moore's law states that the number of transistors on a single chip doubles about every two years. *This* law does still hold true for modern semiconductor technology. Since the huge transistor budget cannot be sensibly utilized by adding functional units or caches, the major processor vendors have started to integrate multiple full processor designs on a single chip, calling them the multiple *cores* of a processor.

The first AMD dual-core processor appeared in early 2005 (Athlon 64 X2), Intel shipped its first dual-core processor around the same time, however based on the superseded and clock-rate-hungry Pentium 4 design. The first Intel processor based on the power-efficient Core micro architecture appeared in early 2006. This way, multi-core processors started to become mainstream. Before, such designs had existed only in niche markets (IBM POWER4 from 2001, Sun UltraSPARC IV from 2004). In late 2005, Sun launched the first 8-core processor (UltraSPARC T1), which featured particularly trimmed-down cores to allow for such a high number on a regular chip. These cores do not support out-of-order execution, and there is only a single floating point unit for all the cores. On the other hand, they can hide memory latency by utilizing 4 hardware threads per core, which access a comparatively powerful memory subsystem.

Nowadays, in 2010, a usual personal computer has a quad-core processor, high-end machines feature six or eight cores on a single chip, optionally supporting two hardware threads per core.

Since the clock rate is limited, the only way to increase computing power significantly is adding more and more independent cores. For CPUs with a large number of cores, the term *many-core* has been coined, although the border between multi-core and many-core is not clearly defined.

Modern graphics processing units (GPUs) could well be termed to be many-core, they contain up to several hundred primitive compute engines. However, those are not completely independent in terms of control flow, so we have a complicated programming model. Also, the amount of directly accessible memory is limited to a few gigabytes, and communication from and to the main memory is a bottleneck. GPUs can be used as offload engine for large tasks, but are inappropriate for simple tasks, they do not have direct access to peripherals, and support for multiple applications utilizing them concurrently is still very basic. So there is still a conceptual break between the work done by the general purpose processor and the GPU, which is also noticeable in programming them.

In this thesis, we focus on multi-core parallelism based on common general-purpose micro architectures.

### 1.2 Motivation

As described, multi-core processors provide increased computing power, and they are ubiquitous nowadays. However, the number of simultaneously running programs on a computer is usually limited to a very small number, in particular on non-servers machines, not able to load each core with an own process. Thus, to benefit from the increased processing power, multiple cores have to be utilized by a single program, processing its work in parallel. This has become mandatory not just for a selected number of specialized programs, but for all nontrivial applications, if they do not want to be left behind by the evolving technology. So far, most of the available computing resources are idle due to insufficiently parallelized software.

However, writing properly parallelized programs is hard. Automatic parallelization works only for simple programs, since it is too hard for a compiler to detect high-level, algorithmic parallelization opportunities. For manual parallelization, software developers not only have to think about enabling parallel execution of work, but also about how to actually parallelize the algorithms, and then do testing and debugging. This is beyond the abilities of many developers, and thus costly and error-prone.

This thesis examines a way to tackle the problem by providing software libraries of parallel algorithm implementations. While this approach has been successful in numerics for a long time, it has not yet made its way into the mainstream of non-numeric programming. Here, we consider mainly combinatorial algorithms.

But let us start from the very beginning. Users'<sup>1</sup> desire is not to run a program in parallel, it is to solve a task as quickly as possible, or to process as much data as possible in a given amount of time. This transfers one level down, to the algorithms a program consists of. The libraries presented here provide building blocks to the programmers, offering algorithms with the usual interface, but in a parallelized form, executing faster. Hence, instead of explicitly

<sup>&</sup>lt;sup>1</sup>We will refer to a person utilizing the libraries in his programs as the *developer*. The *user*, in contrast, runs the final application program.

parallelizing the program itself, it only has to call the parallelized basic algorithms. Hence, this approach raises the task of parallelizing a program to a higher level. The parallel execution becomes implicit.

Algorithm libraries play an important role in the field of *Algorithm Engineering*. Algorithm engineering is a "general methodology for algorithmic research" [San09], whose main process is a cycle of consisting of algorithm design, analysis, implementation, and experimental evaluation. Proximity to applications is kept by using realistic machine models, and doing evaluation on real-world data sets. Algorithm engineering does not replace algorithm theory, but tries to narrow the gap between theory and practice, which is sometimes quite apparent. Algorithm libraries facilitate the implementation of algorithms because they provide easily utilizable subroutines. Just as for theory, where we just cite an algorithm that solves a subtask in a certain running time, we can do the same implementation-wise if an adequate library routine is available. This foster the algorithms that are efficient in practice. In this thesis, we do not provide new algorithmic functionality, but better exploitation of the multi-core hardware, i. e. adapting the implementations to a nowadays more realistic machine model.

#### 1.2.1 Basic Approach

We base our work on already established and widely used algorithmic libraries. This ensures that we can benefit from existing code, reusing software that is widely accepted. It also establishes a performance baseline that is not made up out of thin air. Otherwise, it would be easy to achieve good speedups over slow sequential execution. Also, looking at established libraries helps the selection of algorithms worthwhile considering. Because of performance characteristics or complexity of implementation, the corpus of desired parallel functionality may shift slightly, but they are a good starting point anyway. Finally, established libraries provide an existing user base, yielding early feedback and inspiring the usage of parallelism in other software projects.

Generally, with our algorithms their implementations, we try to achieve the best possible in terms of performance, while maintaining generic usability and flexibility.

Apart from exceptions due to an increased amount of available cache, acceleration is limited by the number of processor cores used. However, the user might appreciate already speedups that are considerably below this limit. After all, the hardware is readily available, at least in terms of acquisition cost. In the worst case, the energy consumption is increased a little bit. On the other hand, utilizing multiple cores can improve the performance per Watt, namely when parallelism compensates for reduced clock speeds and less instruction level parallelism. At first sight, energy consumption is proportional to the clock rate, so increased running time due to a lower clock rate just compensate each other. But lower clock rates allow lower core voltage, and energy consumption is usually proportional to the voltage squared, so we can actually save energy. This extrapolates the approach that led to multi-core processors. Instead of leaving the cores as they are, and adding more and more, we go back to simpler cores, sometimes based on old designs, to allow for an even greater number of them.

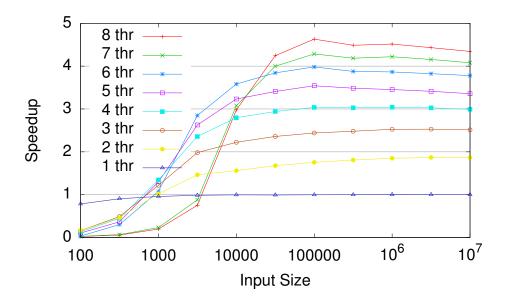

Solving a problem in parallel instead of sequentially usually involves an overhead. There is additional communication, synchronization, non-locality. So it is particularly difficult to speed up work that takes little time already sequentially. Still, we will evaluate the behavior for

small problems as well, and identify minimal time spans where parallelization is still beneficial. Repeated executions of the small problems can make the difference still noticeable to the user, improving the interactivity of the system.

#### 1.3 Parallelism Available in Hardware

Parallelism appears in computer hardware in very different ways, the most general definition being that multiple *processing elements (PE)* simultaneously process data. This can happen in a fine-grained to very coarse-grained way. The work can be divided by splitting the data (*data parallelism*) or by executing different processing steps on different PEs (*task parallelism*).

On the most fine-grained level, we have bit parallelism, a form of data parallelism. But computing with numbers of a limited bit size in one step would probably not be considered parallelism by most people, it is just to natural to handle something adequately similar to a natural number with a single step. The sequential *random access machine (RAM)* is the most common model used for analyzing sequential algorithms, and allows just that.

Next on the granularity level follows *instruction level parallelism*, which allows the processor to execute multiple machine instructions in parallel, may it be through its multiple *arithmetic logic units (ALUs)* for superscalarity, or the multiple *pipeline* stages. While pipelining clearly performs task parallelism, for superscalar execution, the classification on data or task parallelism depends on the actual instructions executed. Apart from that, modern processors provide instructions that in one call process multiple data words. After Flynn's actually more general taxonomy [Fly72], they are usually termed *SIMD instructions*.

Before the multi-core era, a processor usually was superscalar, i. e. it contained several ALUs, but those were controlled by a common control unit, coordinating a single stream of instructions. Multiple of such processors could be plugged into a mainboard, forming a *symmetric multiprocessing (SMP)* machine, where all processors access shared memory.

A multi-core processor combines multiple of the *cores* that were formerly called processors on a single chip that sits in a single socket. In either case, it is *thread-level parallelism* that exploits such an installation, again serving either data parallelism or thread parallelism.

A core can support running a limited number of threads quasi-simultaneously by providing several register files, enabling very fast switching between the threads. This method is called *Simultaneous Multithreading (SMT)* and allows for a better utilization of the arithmetic units, mostly by hiding memory latencies.

Scaling the number of sockets in a system is expensive, since this usually includes noncommodity hardware. So in the last two decades, *clusters* composed of many commodity computers became very popular. The *compute nodes* are interconnected by a network of a certain kind, having separate address spaces for the internal memories. Communication happends via *message passing*, we call such systems *distributed memory* computers. Even if a global address space is emulated and memory accesses are transparently rerouted, such machines cannot be programmed the same way as shared memory machines, since (implicit) communication is usually much slower and has a higher latency than for shared memory.

The lower levels of parallelism (bit parallelism, instruction-level parallelism) are orthogonal to the higher levels (thread parallelism, distributed memory parallelism), so they usually

Figure 1.1: Schema for Uniform Memory Architecture.

Figure1.2:SchemaforNon-Uniform Memory Architecture.

combine well. Depending on the context, the notion of a processing element can refer to anything from a switchting circuit to a fully autonomous computer. In this thesis, a PE usually relates to a thread running on a CPU core for shared memory, or a compute node for distributed memory.

On the shared memory level, to improve memory access bandwidth and latency, recent processors have an integrated memory controller. A multi-core processor typically has one to three memory controllers shared by all the contained cores. Formerly, the memory was accessed through the chipset, connected to the processor by a bus. When combining several processors with integrated memory controller on a mainboard, it is natural to associate memory with each of the sockets. To preserve the common address space and the shared view of the memory, the processors communicate data via integrated interconnects. These are *cache-coherent*, i. e. accesses to the cache always reflect a single global state of the memory. Fetching a memory word from the memory attached to a different socket requires communication, increasing the latency and lowering the bandwidth, the data possibly going through multiple hops. This non-uniform access costs lead to the notion of a *non-uniform memory architecture (NUMA)* in contrast to the formerly prevailing *uniform memory architecture (UMA)*, where the memory is accessed by one common memory controller. Schemas for UMA and NUMA are shown in Figures 1.1 and 1.2.

Since the communication including the routing is done transparently in hardware, we have a global address space, and the connecting bandwidths are very high. Thus, it would go too far to treat such a configuration as a distributed memory system with a certain interconnection topology. However, taking the properties into account qualitatively can improve performance in certain cases.

### 1.4 Models of Parallelism

Since the behavior of real hardware is usually very complex, computer scientists abstract away from too much details and use a *machine model*. A model is always a compromise between the accuracy of performance prediction, and the simplicity of the theoretical analysis.

The most basic and most established parallel model outfits the RAM with multiple ALUs, forming the *parallel random access machine (PRAM)* [J92]. All ALUs access the shared memory clock-synchronously, four variants allow or forbid concurrent read and/or write access to the same memory cell. If concurrent write access is permitted, certain rules for achieving consensus are possible (e. g. arbitrary win, all must write same, operators combining all written values). A PRAM algorithm usually assumes that there are as many ALUs as input elements, which is unrealistic for large inputs. However, a PRAM with *n* ALUs can be emulated by a PRAM with *p* ALUs with a time dilatation factor of O(n/p).

Only academic prototypes of PRAM machines have been built [BBF<sup>+</sup>96] to date, due to the hardware limitations that make clock-synchronous execution expensive and slow. Recently, the idea of constructing a PRAM has been revived by Vishkin [WV07], feasting on the high transistor density as well, putting a whole PRAM except the memory onto a single chip. Until competitive hardware is available, the absolute performance stays unclear, though. Emulating PRAM algorithms on available parallel hardware involves significant constant factors [Har94].

For message passing systems, many models haven been proposed that assume a specific connection network topology, e. g. a grid, a hypercube, or different variants of a tree. Others abstract away the interconnect, but introduce uniform communications costs between the PEs.

Valiant proposed the *Bulk Synchronous Parallel Model (BSP)* in 1990 [Val90]. The crucial concept it introduces is the *superstep*, an execution phase which consists of 1. concurrent computation, 2. communication, 3. barrier synchronization. Every BSP algorithm consists of subsequent supersteps, their number should be kept as small as possible. In the first part of each superstep, no data exchange whatsoever between PEs is allowed, the computations happen fully asynchronously. Several variables characterize the communication complexity of a superstep, *h* being the maximum number of messages a PE sends or receives. A communication is thus called an *h*-relation. The time necessary to deliver a fixed-size message is *g*. As the name says, the BSP model strives to have only few synchronization phases, which is supported by the fact that the barrier synchronization has cost *l*, penalizing fine-grained and individual synchronization. Thus, it fits distributed memory machines well.

A specialization of BSP is the *Coarse-Grained Computer (CGM)* model introduced by Dehne et al. in 1993 [DFRC93]. A coarse-grained computer consists of p processors, connected by an arbitrary connection network. Each PE has O(n/p) local memory, i. e. the local memory is explicitly restricted, and a good balance of data must be kept across the PEs. Collective communication again happens through h-relations. Algorithms proposed for this model usually need n/p > p, which is a reasonable assumption for most distributed-memory machines, at which this model is aimed.

Recently, models have been proposed that model in particular the cache hierarchy of multicore processors, establishing costs for the data transfer between hierarchy levels. Arge, Goodrich et al. propose the *Parallel External Memory (PEM)* model [AGNS08], while Valiant extends his BSP model to *Multi-BSP* [Val08].

As we want to exploit multi-core parallelism in this thesis, we use thread-level parallelism on shared memory machines for the libraries, extending it to distributed-memory parallelism for the very-large-scale sorting algorithms in Chapter 7. The parallelizations we do are usually data-parallel, some task-level parallelism is exploited for external memory in Chapter 6. Instruction level and SIMD parallelism are regarded orthogonal, and left to the compiler.

We analyze the shared memory algorithms in a PRAM-like model, but do not use clock synchronous operation or concurrent writes. Instead, many of our algorithms are inspired by the BSP model, avoiding many synchronizations, where this is too costly. This compromise leads to good performance in practice, while keeping performance guarantees under acceptable conditions.

#### 1.5 Metrics

The performance gain from parallelization can be evaluated with different goals in mind, although the always include the relation between running time and input size. There are two ways this relation can be regarded:

- 1. Parallelization makes the algorithm process more data in the same amount of time.

- 2. Parallelization makes the algorithm process the same amount of data in less time.

For both ways, we can give a factor of improvement, i. e. how much more data was processed, and how much less time was used, respectively. This factor can then be related to the number of PEs used. Of course, under bad circumstances, parallelization can make the execution even slower, or process less data in the same amount of time, so this factor can be less than 1.

In this thesis, we usually focus on the second criterion, improving responsiveness of the system with respect to the user. Generally, we specify an input, and measure the running time for processing it. For the sequential algorithm, we get  $T_{seq}$ , and for the parallel algorithm  $T_{par}(p)$ , the parallel running time depending on the number of PEs used.

We define *absolute speedup* as  $S(p) := T_{seq}/T_{par}(p)$ , where  $T_{seq}$  is the running time of the sequential reference algorithm. In contrast, the *relative speedup* refers to  $S_{rel}(p) := T_{par}(1)/T_{par}(p)$ , comparing the running times of the parallel algorithms, once utilizing only one PE, once *p* PEs. The relative and the absolute speedup usually differ. The common case is that the parallel algorithm includes overheads for handling the general case of multiple PEs, which cannot be fully avoided for the p = 1 case, so  $T_{par}(1) > T_{seq}$ .

The speedup can be related to the number of PEs used, giving the *parallel efficiency* E := S/p. The *parallel work* is the parallel running time multiplied by the number of PEs,  $W := pT_{par}$ . When the parallel work is larger than the sequential work, this inevitably harms efficiency.

If the parallel algorithm is somehow more advanced than the sequential reference algorithm, there might be absolute speedup greater 1 for only one PE, and more than p for p PEs, resulting in E > 1. However, the comparison is not fully fair then, since one could simulate the p PEs on a single one in a time-slice manner, taking only  $pT_{par}(p)$  time. In effect, this proposes a better sequential algorithm. Real super-linear speedup can only happen if not just the number of operations per second is increased by the parallelism, but also other resources are extended, such as an amount of memory with fast access (e. g. main memory instead of disk, cache instead of main memory).

Amdahl's law [Amd67] is a simple bound for the speedup of a parallel program, given that a parallelized algorithm still contains a sequential fraction s:  $S \le 1/(1-s)$ , e. g. for an algorithm having a 10% sequential fraction, the speedup is limited to 9, no matter how many PEs are

| <i>p</i> Number of threads running in parallel, numbered 0 th |                                                   |  |

|---------------------------------------------------------------|---------------------------------------------------|--|

| $\int S[0],\ldots,S[n-1]$                                     | Input sequence                                    |  |

| n                                                             | Problem/input size (number of elements)           |  |

| m                                                             | Secondary problem/input size (number of elements) |  |

Table 1.1: Notation used in Chapters 2 to 6.

used. In practice, however, the sequential part is rarely a constant fraction of the overall time, but depends on the input size and the number of PEs, making this bound not that much useful for performance prediction. However, the theorem show us quite plainly that a sequential part should be reduced as much as possible, because it cannot just make speedup worse, but impose a hard limit.

All metrics described can be applied to both theoretical running time complexity and experimentally measured running time. Unless stated otherwise, we give experimental absolute speedups comparing to the sequential library algorithm we parallelize.

The term *scalability* appears often when discussing parallelism, it is not uniquely defined though, there are several ways to interpret it. "Good" scalability may mean a linear correlation between the number of PEs and the processable input size, for the first criterion, or a good parallel efficiency in general for a large number of PEs.

#### **1.6 Thesis Overview**

In Chapter 2, we will first recapitulate algorithms that appear multiple times subsequently. The programming language and the parallelism support libraries we base our work on will be described in Chapter 3. We will consider the first library to multi-core parallelize in Chapter 4, namely the Standard Template Library (STL). It provides basic algorithms for computations in main memory. We parallelize selected algorithms from the Computational Geometry Algorithms Library (CGAL) in Chapter 5. The usage of multi-core parallelism for external memory algorithms is described in Chapter 6, building on the Standard Template Library for XXL Data Sets (STXXL). Those algorithms handle data sets that do not fit into main memory any more, but have to be stored on disks. Table 1.1 states some notation for the Chapters 2 to 6 on the mentioned libraries to be parallelized for shared memory machines. Chapter 7 presents, as continuation and application of the parallelized STXXL, sorting algorithms that combine distributed and shared memory parallelism, as well as external memory on parallel disks, including an implementation. Finally, we draw the overall conclusions and indicate future work in Chapter 8.

## 2 Recurring Algorithms

In this chapter, we recapitulate algorithms that are used multiple times in this thesis.

Multiway mergesort is an I/O- and cache-efficient sorting algorithm. For parallelizing the merge step, the work has to be split up, helped by the so-called multiway partitioning.

#### 2.1 Multiway Selection/Partitioning

Given k sorted sequences  $S_1, \ldots, S_k$  and a global rank m, we are asked to find splitting positions  $i_1, \ldots, i_k$  such that  $i_1 + \cdots + i_k = m$  and  $\forall j, j' \in 1, \ldots, k : S_j[i_j - 1] \le S_{j'}[i_{j'}]$ . This is similar to selection, although in the context of this thesis, we are usually not interested in the element of global rank m, but rather the splitting positions. We call finding the splitting positions *multiway partitioning*. Finding the respective element is trivial after multiway partitioning, just take the smallest element right of the split.

Our starting point is an asymptotically optimal algorithm by Varman et al. [VSIR91] for selecting the element of global rank *m* in a set of sorted sequences. It is fairly complicated, and to our knowledge, has been implemented before only for the case that the number of sequences is a power of two and all sequences have the same length  $|S_j| = 2^k - 1$  for some integer *k*.

The problem is solved by partitioning a more and more refined sample of the sequences. Let  $s = 2^i \ge \max_j |S_j|$ . Initially, only every  $s^{\text{th}}$  element is taken into account, then every  $(s/2)^{\text{th}}$ ,  $(s/4)^{\text{th}}$  element, and so on. Each refinement doubles the number of considered elements, until all elements are considered for  $(s/2^i) = 1$ .

Therefore, after a logarithmic number of refinements, the algorithm terminates. In each refinement step, the algorithm must determine for only O(k) elements whether they belong to the left or the right side. There is an asymptotically efficient but complicated method that achieves this goal in O(k) time. We do this using a priority queue in (slightly suboptimal) time  $O(k \log k)$  per refinement step. With each refinement step, the number of regarded elements per sequence doubles, so the maximum number of refinements<sup>1</sup> is  $\lceil \log \max_j |S_j| \rceil$ . The total running time amounts to  $O(k \log k \cdot \log \max_j |S_j|)$ .

Our implementation can handle any number of sequences of arbitrary length. Explicit care has been taken of the case of many equal elements surrounding the requested rank. To allow stable parallelized merging based on this partitioning, the splitter positions may not be in arbitrary positions in the equal subsequence. In fact, there must not be more than one sequence  $S_j$  having a splitter "inside" the equal subsequence. All  $S_i$  with i < j must have the splitter at the end of it, all  $S_i$  with i > j must have the splitter at its beginning.

<sup>&</sup>lt;sup>1</sup>Unless stated otherwise, all logarithms have base 2.

Figure 2.1: Schema of parallel multiway merging, in this case merging a specified number of elements only.

#### 2.2 Multiway Merging

*Merging* two sorted sequences  $S_1$  and  $S_2$  is usually understood as efficiently coalescing them into one sorted sequence. Its generalization to multiple sequences  $S_1, \ldots, S_k$  is called *multiway merging*.

It is often used (e. g., [San00, RKU00, DS03]) instead of repeated binary merging, since it is more I/O- and cache-efficient. The high "branching factor" allows to perform a considerable amount of work per item. This compensates for the costs of accessing the data on the (shared or external) memory.

We parallelize multiway merging using multiway partitioning. Let  $n = \sum_{i=1}^{k} |S_i|$ . In parallel, each processing element (PE) i > 1 does multiway partitioning on the set of sequences, requesting global rank  $\lceil \frac{in}{p} \rceil$ . Then, each PE *i* merges the part of the input that is determined by the locally computed splitting positions and by the splitting positions computed by PE i + 1. For i = 0 we use splitting local positions  $(0, \dots, 0)$ , and for i = p, we use local splitting positions  $(|S_1|, \dots, |S_k|)$ . The destination offset is also clear from the ranks. Figure 2.1 shows a schematic view of the algorithm.

Our implementation of sequential multiway merging is an adaptation of the implementation used for cache-efficient priority queues and external sorting in [San00, DS03]: For k = 1, we just copy, for k = 2, we use the folklore merge routine. For  $3 \le k \le 4$ , we use specialized routines that encode the relative ordering of the next elements of each sequence into the program counter, i. e. we execute a different code variant depending on the ordering, jumping around between these. For k > 4, a loser tree data structure [Knu98] keeps the next element of each sequence. The total execution time of our algorithm is  $O(\frac{n}{p} \log k + k \log k \cdot \log \max_i |S_i|)$ . Note

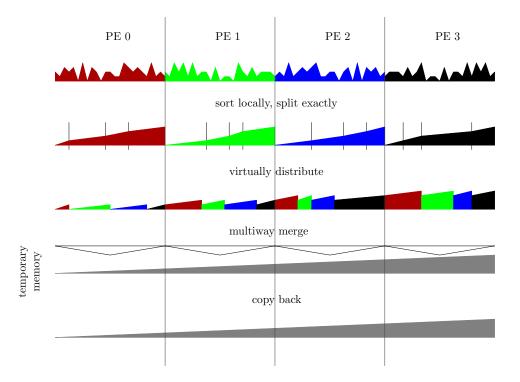

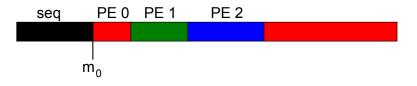

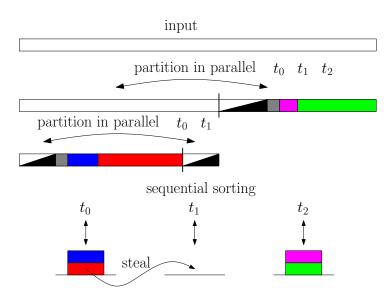

Figure 2.2: Schema of parallel multiway mergesort. For shared memory, the distribution depicted in the middle row takes place only virtually, i. e. the PEs read the data from where it is already, there is no copying. The final copying step is optional, only necessary if the result is expected in the same place as the input.

that the major first term is *p* times smaller than in sequential merging, the rest is lower-order in terms of the input size.

### 2.3 Multiway Mergesort

Based on the components explained so far, it is very easy to construct a parallel sorting algorithm. Each PE sorts about  $\frac{n}{p}$  elements sequentially, plus minus 1 due to the rounding. The resulting sorted sequences are merged using parallel multiway merging afterwards. We assume the sequential algorithm to run in time  $O(n \log n)$ , i. e.  $O\left(\frac{n}{p} \log \frac{n}{p}\right)$  per PE. Substituting k = p and  $S_i = \frac{n}{p}$  in the formula for multiway merging results in  $O\left(\frac{n}{p} \log p + p \log p \cdot \log \frac{n}{p}\right)$ . The sequential sorting and the actual merging add up to  $O\left(\frac{n}{p} \log n\right)$ , but there is still the partitioning, so we have in total  $O(\frac{n}{p} \log n + p \log p \cdot \log \frac{n}{p})$ . Figure 2.2 illustrates the algorithm.

## **3** Platform

#### 3.1 C++

C++ is a well-established programming language with a rich syntax, supporting both objectoriented programming, and generic programming via templates. It comes with no inherent performance penalty, following the "zero overhead principle", which states that it does not incur overhead for features that are not used. Since it is compiled offline, elaborate optimization routines can be applied. For languages producing executables for a virtual machine, e. g. Java or C#, this is not so clear.

This makes C++ an ideal choice for high-performance applications. The standardization [C++03] of C++ has set a common ground for language and library implementations, which are widely available and of high quality. The C++ standard is also evolving, as can be seen by the proposed upcoming standard, termed C++0x [C++10]. The Standard Template Library (STL) [PSLM00] is part of the existing C++ library specification, and provides many useful generic data structures and algorithms to its user, its design serving as a blueprint for many algorithm libraries.

#### 3.2 Platform Support for Threading

Any parallel program or library needs a foundation that enables concurrent execution. For our shared-memory parallel libraries, this foundation needs to be both efficient and platformindependent.

For the purely data-parallel libraries, for basic internal algorithms (Chapter 4) and geometric algorithms (Chapter 5), we have chosen to use *OpenMP* [Ope08]. OpenMP is a language extension supported by a run-time library. It provides a more elegant interface to parallel execution than library-style approaches like POSIX threads, and also the threading interface that will be part of the C++0x standard.

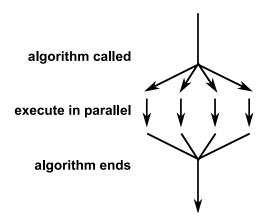

Figure 3.1: Schema of fork-join parallelism.

Its advantages include:

- OpenMP provides so-called "fork-join parallelism", which is exactly what we need for parallelizing data-parallel algorithms. The work is divided, the threads start working, they re-join, and the function call returns, as illustrated by Figure 3.1.

- OpenMP is orthogonal to the programming language, which is affirmed by a Fortran variant being available. Many programming languages with first class parallel programming support have been invented<sup>1</sup>, however, those are usually decoupled from the other developments ongoing in language design. OpenMP makes a good compromise by extending C++ through the syntax that is intended for augmentation of the language, namely pragma.

- The pragma syntax allows to intertwine parallelism specifications and actual code closely, with no need to put functor classes somewhere far into the code, outside of the current function scope. This might be partly compensated by the closures from upcoming C++0x, though.

- Low-level issues like reusing threads from a pool, and getting information about the environment, e.g. the number of cores, can be left to the OpenMP runtime. A lot of research is happening in this field, whose results can be quickly brought in because we base on such an established interface. The user can configure the runtime environment using standard procedures.

- Since OpenMP is integrated into the compiler, very efficient code can be generated that uses platform-specific functionality like atomic operations provided by the hardware.

<sup>&</sup>lt;sup>1</sup>In PPoPP 2007, a keynote speaker had counted all the parallel programming languages developed in academia over the recent years, some number  $\ell > 100$ , questioning this development. Immediately after the keynote, the next talk introduced parallel programming language number  $\ell + 1$ .

- OpenMP is platform-independent. The GNU compiler collection (GCC) supports OpenMP 2.5 from version 4.2, and OpenMP 3.0 from version 4.4. OpenMP is also supported by all major commercial C++ compilers, like the ones from Sun, Intel, and Microsoft.

- Augmented code also compiles and runs correctly (though not in parallel) with compilers not natively supporting OpenMP, adding an dummy runtime library.

- OpenMP is an open standard, supervised by the OpenMP Architecture Review Board.

It is a common misunderstanding that OpenMP is only good for parallelizing simple forloops. This impression comes from the fact that most introductory examples present this simple case.

We use OpenMP to execute a code block by a certain number of threads (called a *team*) in parallel, in a so-called *parallel region*. Splitting the work is done manually, breaking symmetry by using the omp\_get\_num\_threads and omp\_get\_thread\_num function calls. Intermediate barriers and sections that are to be executed by one thread only, are achieved by the respective pragmas. Thus, a algorithm framework looks like this:

```

void algorithm(...)

{

#pragma omp parallel

{

int num_threads = omp_get_num_threads(),

iam

= omp_get_thread_num();

#pragma single

{

//split up work sequentially

}

//do work in parallel for PE iam

#pragma omp barrier //synchronize for data exchange

//go ahead in parallel

}

}

```

A recent and very convenient addition (in version 3.0) is the task construct, which allows (nested) asynchronous processing of code blocks, scheduled by the OpenMP runtime. The tasks can be spawned at arbitrary places in the code, and the spawning thread can wait for their termination. The parallel region starts the threads, immediately suspending them to wait for tasks, as exemplified here.

```

void algorithm(...)

{

#pragma omp parallel

{

```

```

#pragma single

{

//create tasks

... //recursive, iterative

#pragma omp task

{

//spawn off as task

}

...

#pragma omp taskwait //wait for all task spawned in this thread/task

}

}

```

In addition to the actual thread control via OpenMP, we use a thin platform-specific layer that provide access to a small number of efficiently implemented primitive atomic operations like fetch-and-add and compare-and-swap. Atomic fetch-and-add increases an integer by a certain amount, with no interference from other threads possible during reading and writing the value. Since it returns the former value, it is very suitable to reserve a range for operation, namely the one between the former value and the increased value. Atomic compare-and-swap compares an integer to a given value, and if they are equal, exchanges it atomically by another given value. This function can be used to transfer one state safely to another.

The atomic operations are usually implemented in hardware, and allow for very efficient communication and synchronization in the simple cases where a single integer is sufficient. Soon, we will able to replace them by the primitives demanded by the C++0x standard, which are already available for some compilers. In case the hardware does not support atomic operations, software solutions can be used at the cost of a performance penalty.

An concurrently modifiable data structure that does not use mutual exclusion through a lock, but just atomic operations, is called *lock-free*.

A program using OpenMP can be configured by the user through different environment variables. Most important are OMP\_NUM\_THREADS and OMP\_DYNAMIC, which influence the number of threads. Although an OpenMP parallel clause takes an argument on the desired number of threads, this value poses an upper limit only, and if no explicit value is given, OMP\_NUM\_THREADS is used. If the dynamic mode is switched on, the runtime can decide to schedule a smaller number of threads to the parallel region. By default, OMP\_NUM\_THREADS is usually set to the number of cores available in the system, OMP\_DYNAMIC is switched off.

Overall, this means that the number of threads is clear only after the parallel statement, i. e. in the parallel region. The code must not make any assumptions about the number of threads beforehand. In many algorithms, this leads to a single block right after the beginning of the parallel region, in order to distribute the work appropriately. For best performance, the compiler should identify this case, and start the threads only after the single block, having fixed the number of threads in advance, and thus returning the right value from omp\_get\_num\_threads.

The environment variable OMP\_SCHEDULE only influences OpenMP parallel for loops, which are rarely used in this work.

#### CHAPTER 3. PLATFORM

Nested parallelism *is* used by some of the algorithms presented, e.g. quicksort. For those, to get best performance, OMP\_NESTED should be set to true. We also configure the OpenMP library, *libgomp*, to provide better responsiveness by threads by lowering GOMP\_SPINCOUNT to 10 000 in this case, to limit busy waiting and yield to the operating system scheduler more quickly.

In Chapter 6, we will use coarse-grained task-parallelism in addition. OpenMP is not wellsuited for this case, because threads have to synchronize in producer-consumer scheme. Since the threads work on large data sets and therefore for long times, we can admit to use regular OS threading without pooling, using the *pthread* library. As we will see, pthread for the task parallelism and OpenMP for the data parallelism combine nicely.

We do *not* make use of transactional memory [HM93]. *Transactional memory* is a concepts that is supposed to simplify concurrent programming by allowing a group of reads and writes from and to memory, usually from a code block, to execute atomically. However, competitive hardware supporting this feature is not yet available. For the case that transactions are emulated in software, it is clear that a hand-programmed transaction protocol can always be at least as fast. In fact, we do use *atomic instructions*, which can be seen as transactional memory limited to a single data word. For this granularity, hardware support is available on multi-core processors, delivering very good performance.

Anyway, the libraries considered are supposed to keep their interface in the parallelized version. So it does not make a difference to the developer whether we use transactional memory internally or not. If high-performance implementations are available one day, we could utilize it internally, without the necessity of changes by the developer. Independent of that, memory transactions on the developer level could actually improve usability by ensuring atomicity of developer-defined functions, which might be called asynchronously by a library routine.

## 3.3 Platform Support for Distributed-Memory Computing

The algorithms presented in Chapter 6 are designed for distributed memory systems, but also use shared memory parallelism locally on each node. For communication between the nodes, we use the Message Passing Interface [MPI94], which is the standard for this kind of computer. It follows a *single-program multiple-data* approach, i. e. the same program runs on every node.

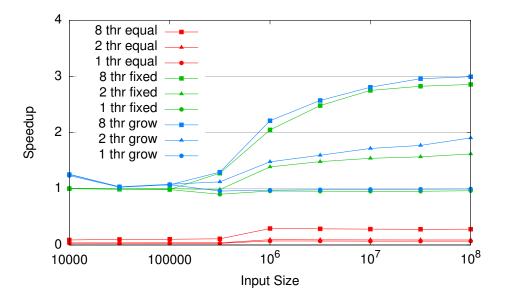

#### 3.4 Machines for Experimental Evaluation