### **Matthias Traub**

Durchgängige Timing-Bewertung von Vernetzungsarchitekturen und Gateway-Systemen im Kraftfahrzeug

#### **Matthias Traub**

Durchgängige Timing-Bewertung von Vernetzungsarchitekturen und Gateway-Systemen im Kraftfahrzeug

# Durchgängige Timing-Bewertung von Vernetzungsarchitekturen und Gateway-Systemen im Kraftfahrzeug

von Matthias Traub

Dissertation, Karlsruher Institut für Technologie Fakultät für Elektrotechnik und Informationstechnik, 2010

#### **Impressum**

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe www.ksp.kit.edu

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

Diese Veröffentlichung ist im Internet unter folgender Creative Commons-Lizenz publiziert: http://creativecommons.org/licenses/by-nc-nd/3.0/de/

KIT Scientific Publishing 2010 Print on Demand

ISBN 978-3-86644-582-6

## Durchgängige Timing-Bewertung von Vernetzungsarchitekturen und Gateway-Systemen im Kraftfahrzeug

Zur Erlangung des akademischen Grades eines

DOKTOR-INGENIEURS

an der Fakultät für

Elektrotechnik und Informationstechnik

Karlsruher Institut für Technologie (KIT)

genehmigte

DISSERTATION

von

Dipl.-Ing. Matthias Alexander Traub

geb. in: Stuttgart

Tag der mündlichen Prüfung: 29.06.2010

Hauptreferent: Prof. Jürgen Becker

Korreferent: Prof. Wolfgang Rosenstiel

#### **Danksagung**

Diese Arbeit entstand während meiner Tätigkeit als Mitarbeiter im Bereich Forschung und Vorentwicklung bei der Daimler AG. Die wissenschaftliche Betreuung der Arbeit erfolgte an der Fakultät für Elektrotechnik und Informationstechnik am Institut für Technik der Informationsverarbeitung des Karlsruher Instituts für Technologie.

An dieser Stelle möchte ich Allen, die zum Gelingen dieser Dissertation beigetragen haben, meinen persönlichen Dank aussprechen. Mein besonderer Dank gilt meinem Doktorvater Prof. Jürgen Becker für die hervorragende Betreuung und Unterstützung. Die gemeinsamen Besprechungen waren für mich von sehr großem Wert. Seine Anmerkungen und Hinweise haben mich bei der Entwicklung der Ansätze immer weitergebracht. Herrn Prof. Rosenstiel danke ich für die Übernahme des Zweitgutachtens.

Mein weiterer Dank gilt meinen Kolleginnen und Kollegen, die mir jederzeit mit Rat und Tat zur Seite standen. Mein Dank gebührt auch den zahlreichen Praktikanten und Diplomanden, die mich bei der praktischen Umsetzung meiner Ansätze tatkräftig unterstützen. Für die vielen gemeinsamen Diskussionen und Arbeiten möchte ich mich bei Dr. Kai Richter von Symtavision bedanken.

Für den moralischen Beistand bin ich meinen Freunden sehr dankbar, insbesondere Eva und Wolfgang die mir während der Endphase eine große Hilfe waren. Weiterhin möchte ich an dieser Stelle meinen Eltern ganz herzlich danken. Ihr Vertrauen bildete die Grundlage für diese Arbeit.

Mein ganz besonderer Dank gilt meiner geliebten Frau. Ihre stetige Motivation und ihr Verständnis hat mir insbesondere in schwierigen Phasen den Mut gegeben die Arbeit erfolgreich zu Ende zu bringen. Abschließend möchte ich noch meinem Sohn Lorenz danken, der in der letzten Zeit so oft zu kurz kam und mir in den wenigen gemeinsamen Stunden viel Kraft gegeben hat. Meinem im Mai geborenen Sohn Kilian danke ich für den Motivationsschub zur Vollendung dieser Arbeit.

#### Kurzfassung

Die steigende Anzahl von Elektrik-/Elektronik-Systemen im Automobil und damit verbunden das zunehmende Kommunikationsaufkommen stellen immer höhere Anforderungen an den Entwicklungsprozess. Bei der Entwicklung von zukunftsfähigen E/E-Architekturen spielt der Entwurf einer robusten Vernetzung eine zentrale Rolle. Die Auslegung und Absicherung einer solchen Vernetzungsarchitektur erfolgte bisher mittels einfacher Metriken, z.B. Berechnung der Buslast von zyklischen Botschaften. Durch die wachsende Komplexität sowie aufgrund gesetzlicher und sicherheitsrelevanter Anforderungen muss das Timing-Verhalten der Systeme zukünftig gezielt betrachtet und bewertet werden. In der vorliegenden Arbeit wird eine Methodik beschrieben, welche eine detaillierte und durchgängige Auslegung und Absicherung von Vernetzungsarchitekturen und Gateway-Systemen hinsichtlich deren Timing-Verhaltens ermöglicht.

In den letzten dreißig Jahren haben sich verschiedene Forschergruppen mit der Frage beschäftigt, wie das Timing-Verhalten von eingebetteten Systemen analytisch bestimmt werden kann. Aus diesen wissenschaftlichen Aktivitäten sind eine Vielzahl von Ansätzen und Verfahren entstanden. Ein Ziel der vorliegenden Arbeit ist es diese Verfahren auf ihre Eignung für Fragestellungen im Automobilbereich zu untersuchen. Ferner wird ein Verfahren zur Extraktion von Timing-Informationen vorgestellt, welches ein detailliertes Bild zum Stand der aktuellen E/E-Systeme im Fahrzeug liefert. Die gewonnen Daten können weiterhin für eine Modellverfeinerung in der Entwurfsphase von E/E-Architekturen verwendet werden. Um eine exakte Abbildung des Timing-Verhaltens in den entsprechenden Bewertungsverfahren zu ermöglichen, erfolgt die Definition von Modellierungsregeln. Für die Integration der Bewertungsverfahren in den existierenden E/E-Entwicklungsprozess wird eine durchgängige Bewertungsmethodik aufgezeigt. Weiterhin wird ein Konzept für die Ableitung von Routing-Testpattern auf der Basis von Timing-Analysen vorgestellt. Dieses ermöglicht eine gezielte Berücksichtigung des Timing-Verhaltens von Steuergeräten mit Gateway-Anteilen bei den Funktionstests am Komponenten-Prüfstand.

Anhand von Fallbeispielen wird die durchgängige Bewertungsmethodik validiert, um die Abdeckung der Eigenschaften und Anforderungen aus dem Vernetzungsbereich nachzuweisen. Die Ergebnisse zeigen die Tauglichkeit der Methodik für den Einsatz im Serienprozess. Der Entwurf und die Entwicklung von E/E-Architekturen werden durch die Methodik signifikant verbessert.

#### Summary

The growing number of electric-/electronic-systems in the automobile and therewith the increasing volume of communication are placing even higher demands on the development process. In the development of future electric-/electronic-architectures the design of a robust network-architecture plays a central role. The design and verification of such network-architectures has taken place up to now by means of simple metrics, for example the calculation of the bus loads of cyclic messages. Through the growing complexity and also based on legal requirements, the timing behaviour of these systems must be considered with the future in mind and evaluated accordingly. In this thesis a methodology is described, which enables a detailed design and verification of network-architectures and gateways with regard to their timing behaviour and resource demands.

In the past 30 years various researchers have focused on the question, how the timing behaviour of embedded systems can be analysed in a formal way. Several approaches and methods are created based on these scientific activities. The goal of this dissertation is to investigate the methods regarding the suitability of issues in the automobile field. Furthermore a method for the extraction of timing information will be introduced, which offers a detailed view over the actual state of the art of automotive e/e-systems. The extracted timing data can be used for a refinement of models during the early design phase. Moreover concepts of modeling rules were carried out, which guarantee an exact observation of the timing behaviour of the electric-/electronic-systems. For the integration of timing evaluation methods in the existing e/e-development process a seamless timing-evaluation will be introduced. Finally an concept for a generation of routing test patterns was developed, which allows a significant increase of the test coverage when examining gateway-control units on the hardware-in-the-loop test bench.

Based on case studies (e.g. such as CAN-bus, central gateway-control unit and distributed functions) the concepts were verified for the integrated evaluation methodology in order to prove the coverage of the typical properties and requirements from the area of network-architectures. The results of the investigation have demonstrated the suitability

of the approach for the integration into the existing development process. The use of the timing-evaluation methodology for systems in the automotive area was significantly improved and offers a large added value during the design and development of future automotive electric-/electronic-architectures.

#### Inhaltsverzeichnis

| 1 | Ein | leitung                                                            | 1  |

|---|-----|--------------------------------------------------------------------|----|

|   | 1.1 | Vernetzungsarchitekturen im Kraftfahrzeug                          | 1  |

|   | 1.2 | Zunehmende Anforderungen an die Bewertung von Vernetzungsarchitek- |    |

|   |     | turen                                                              | 3  |

|   | 1.3 | Zielsetzungen der Arbeit                                           | 5  |

|   | 1.4 | Gliederung der Arbeit                                              | 8  |

| 2 | Gru | ındlagen der Arbeit                                                | 9  |

|   | 2.1 | Eingebettete verteilte Echzeitsysteme                              | 9  |

|   | 2.2 | Begriffsdefinitionen                                               | 10 |

|   | 2.3 | Anforderungen an den Timing-Bewertungsprozess                      | 16 |

| 3 | E/E | -Architekturen und Entwicklungsprozesse                            | 19 |

|   | 3.1 | E/E-Architekturen im Kraftfahrzeug                                 | 19 |

|   |     | 3.1.1 Hardwarearchitektur von Steuergeräten                        | 20 |

|   |     | 3.1.2 Softwarearchitektur von Steuergeräten                        | 21 |

|   |     | 3.1.3 Kommunikationssysteme                                        | 27 |

|   | 3.2 | Entwicklungsprozess für E/E-Architekturen                          | 35 |

|   | 3.3 | Bewertung des Stands der Technik                                   | 38 |

|   | 3.4 | Kenngrößen für die Timing-Bewertung                                | 41 |

| 4 | Ans | sätze und Verfahren zur Timing-Bewertung                           | 47 |

|   | 4.1 | Timing-Bewertung von Steuergeräten                                 | 49 |

|   |     | 4.1.1 Simulation und Test von Steuergeräten                        | 50 |

|   |     | 4.1.2 Statische Timing-Analysen von Steuergeräten                  | 51 |

|   | 4.2 | Timing-Bewertung von Kommunikationssystemen                        | 54 |

|   |     | 4.2.1 Simulation and Test von Kommunikationssystemen               | 54 |

|   |     | 4.2.2   | Statische Timing-Analysen von Kommunikationssystemen  | 54  |

|---|-----|---------|-------------------------------------------------------|-----|

|   | 4.3 | Timin   | g-Bewertung auf Systemebene                           | 57  |

|   |     | 4.3.1   | Simulation und Test auf Systemebene                   | 58  |

|   |     | 4.3.2   | Statische Timing-Analysen auf Systemebene             | 59  |

|   | 4.4 | Einor   | dnung und Abgrenzung                                  | 71  |

| 5 | Ver | fahren  | zur Extraktion von Timing-Informationen               | 73  |

|   | 5.1 | Extral  | ktionsverfahren                                       | 75  |

|   |     | 5.1.1   | Sende- und Übertragungsjitter                         | 76  |

|   |     | 5.1.2   | Offsettabellen der Steuergeräte                       | 78  |

|   |     | 5.1.3   | Extraktion von Betriebsszenarien                      | 81  |

|   | 5.2 | Bewei   | rtung des Verfahrens                                  | 89  |

| 6 | Мос | dellier | ungsregeln zur exakten Timing-Bewertung               | 93  |

|   | 6.1 | Mode    | llierungsregeln für das Timing-Verhalten des CAN-Bus  | 93  |

|   |     | 6.1.1   | Abbildung der Sendetypen                              | 94  |

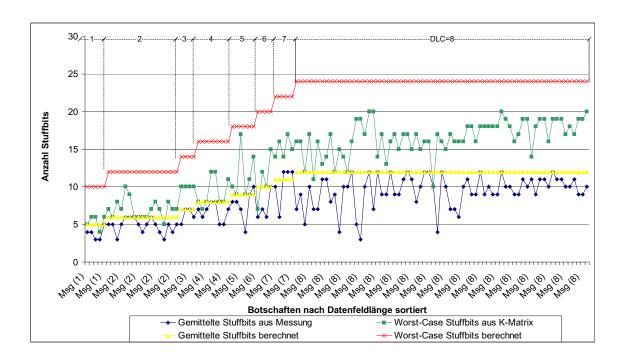

|   |     | 6.1.2   | Korrekte Berücksichtigung der Stuffbits               | 95  |

|   |     | 6.1.3   | Verfahren zur Vergabe von Offsets                     | 97  |

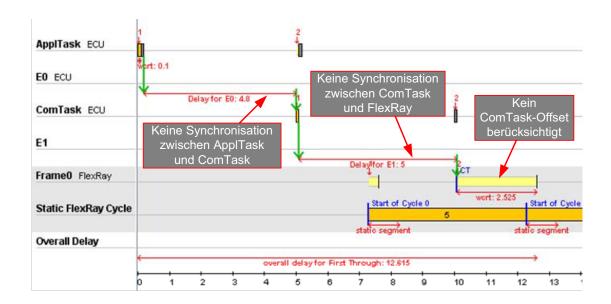

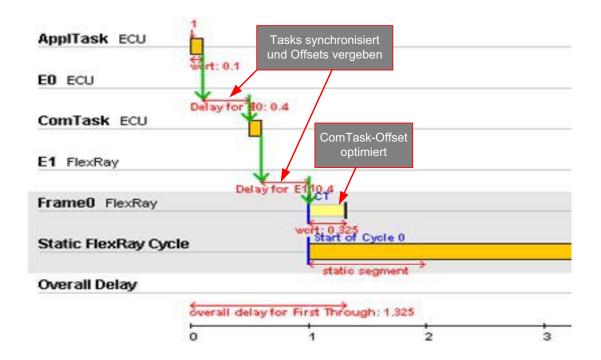

|   | 6.2 | Mode    | llierungsregeln für das Timing-Verhalten von FlexRay  | 101 |

|   | 6.3 | Mode    | llierungsregeln für Kommunikationssysteme             | 103 |

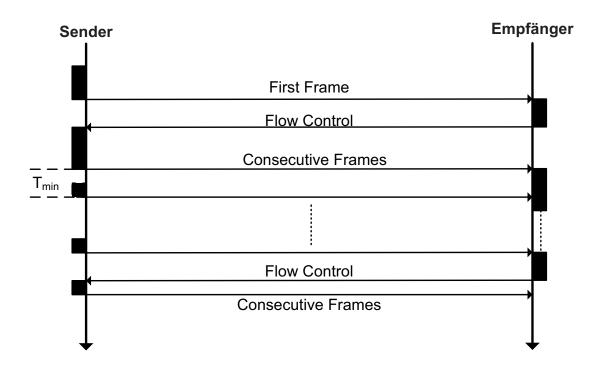

|   |     | 6.3.1   | Modellierung von Transportprotokollen                 | 103 |

|   |     | 6.3.2   | Modellierung des Netzwerkmanagements                  | 105 |

|   |     | 6.3.3   | Modellierung der dynamischen Kommunikation            | 106 |

|   |     | 6.3.4   | Modellierung des Jitters                              | 107 |

|   |     | 6.3.5   | Modellierungsregeln für die frühe Entwurfsphase       | 107 |

|   |     | 6.3.6   | Definition von Bewertungsszenarien                    | 108 |

|   |     | 6.3.7   | Bewertung der Regeln                                  | 111 |

|   | 6.4 | Mode    | llierungsregeln für das Timing-Verhalten von Gateways | 113 |

|   |     | 6.4.1   | Regeln zur Generierung von Annotationen               | 115 |

|   |     | 6.4.2   | Vollständiges Gateway-Modell für die Timing-Analyse   | 119 |

|   |     | 6.4.3   | Bewertung der Regeln und Konzepte                     | 124 |

| 7 | Met | hodik   | für eine durchgängige Timing-Bewertung                | 127 |

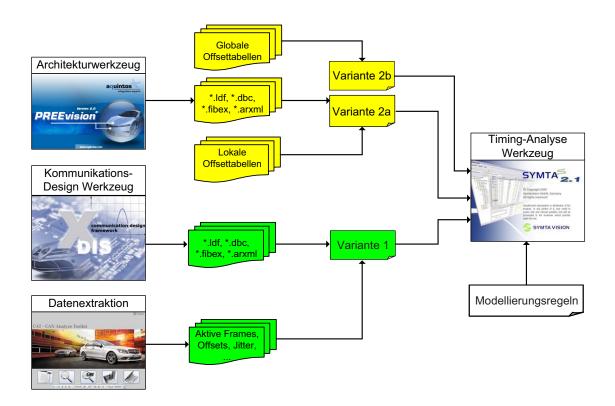

|   | 7.1 | Metho   | odik und Werkzeugkette                                | 129 |

|   | 7.2 | Konzept zur Generierung von Routing-Testpattern |                                                     |     |  |  |  |

|---|-----|-------------------------------------------------|-----------------------------------------------------|-----|--|--|--|

|   | 7.3 | Bewei                                           | rtung der Methodik und Konzepte                     | 134 |  |  |  |

|   |     | 7.3.1                                           | Bewertung der Methodik                              | 134 |  |  |  |

|   |     | 7.3.2                                           | Bewertung des Konzeptes für die Routing-Testpattern | 135 |  |  |  |

| 8 | Eva | luieru                                          | ng                                                  | 137 |  |  |  |

|   | 8.1 | Vergle                                          | eich der Timing-Bewertungsverfahren                 | 137 |  |  |  |

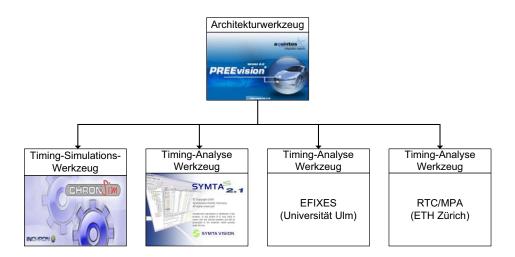

|   |     | 8.1.1                                           | Übersicht                                           | 138 |  |  |  |

|   |     | 8.1.2                                           | Verwendete Werkzeugkette                            | 140 |  |  |  |

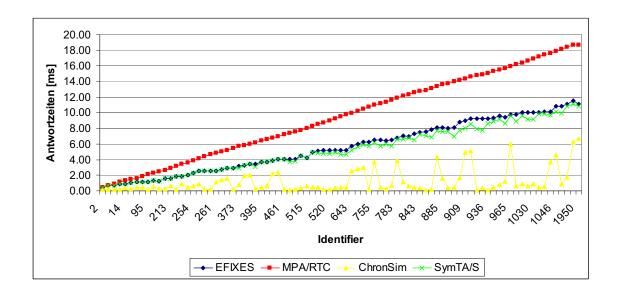

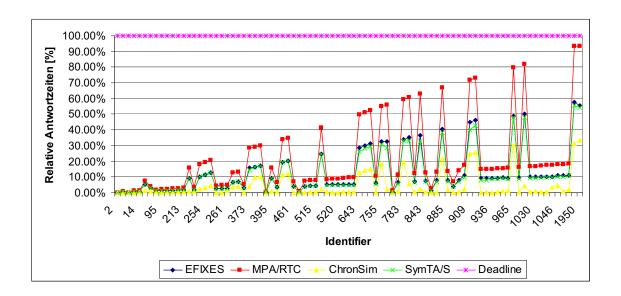

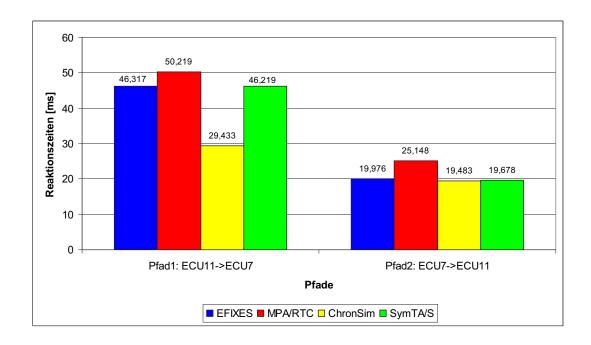

|   |     | 8.1.3                                           | Diskussion der Ergebnisse                           | 140 |  |  |  |

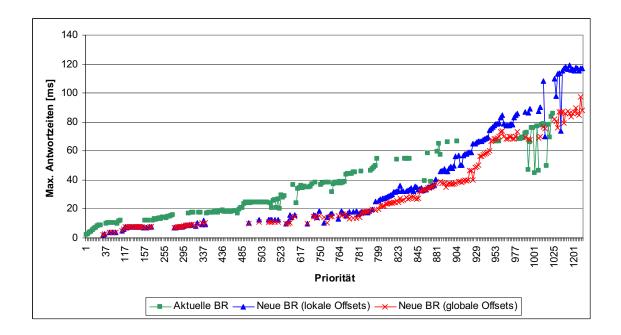

|   | 8.2 | Timin                                           | g-Bewertung eines CAN-Busses                        | 143 |  |  |  |

|   |     | 8.2.1                                           | Übersicht                                           | 143 |  |  |  |

|   |     | 8.2.2                                           | Verwendete Werkzeugkette                            | 144 |  |  |  |

|   |     | 8.2.3                                           | Diskussion der Ergebnisse                           | 145 |  |  |  |

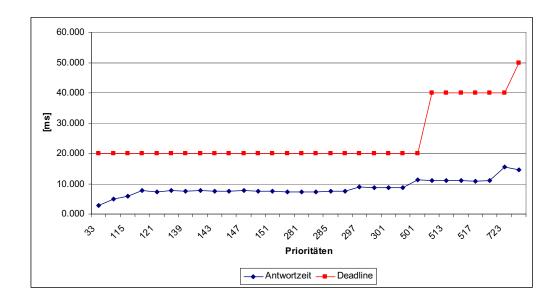

|   | 8.3 | Timin                                           | g-Bewertung eines CAN-Busses via Szenarien          | 148 |  |  |  |

|   |     | 8.3.1                                           | Übersicht                                           | 148 |  |  |  |

|   |     | 8.3.2                                           | Verwendete Werkzeugkette                            | 148 |  |  |  |

|   |     | 8.3.3                                           | Diskussion der Ergebnisse                           | 149 |  |  |  |

|   | 8.4 | Timin                                           | g-Bewertung eines AUTOSAR-basierten Gateways        | 152 |  |  |  |

|   |     | 8.4.1                                           | Übersicht                                           | 153 |  |  |  |

|   |     | 8.4.2                                           | Verwendete Werkzeugkette                            | 154 |  |  |  |

|   |     | 8.4.3                                           | Analyse der Ausführungszeiten mit aiT               | 155 |  |  |  |

|   |     | 8.4.4                                           | Messungen auf der Hardware                          | 156 |  |  |  |

|   |     | 8.4.5                                           | Diskussion der Ergebnisse                           | 159 |  |  |  |

|   | 8.5 | Timin                                           | g-Bewertung einer Vernetzungsarchitektur            | 160 |  |  |  |

|   |     | 8.5.1                                           | Übersicht                                           | 160 |  |  |  |

|   |     | 8.5.2                                           | Verwendete Werkzeugkette                            | 161 |  |  |  |

|   |     | 8.5.3                                           | Diskussion der Ergebnisse                           | 161 |  |  |  |

|   | 8.6 | Zusan                                           | nmenfassung                                         | 164 |  |  |  |

| 9 | Zus | amme                                            | enfassung und Ausblick                              | 165 |  |  |  |

|   | 9.1 |                                                 | nmenfassung                                         | 165 |  |  |  |

|   | 9.2 |                                                 | ick                                                 |     |  |  |  |

|        | 9.2.1   | Erweiterungen für die Extraktion von Timing-Informationen      | 167 |

|--------|---------|----------------------------------------------------------------|-----|

|        | 9.2.2   | Verfeinerung und Entwicklung weiterer Modellierungsregeln      | 168 |

|        | 9.2.3   | Integration der Werkzeugkette in den Serienentwicklungsprozess | 169 |

| Gloss  | ar      |                                                                | 171 |

| Abkür  | zunge   | n                                                              | 177 |

| Symb   | ole     |                                                                | 181 |

| A Lite | eraturv | rerzeichnis                                                    | 185 |

#### 1. Einleitung

#### 1.1. Vernetzungsarchitekturen im Kraftfahrzeug

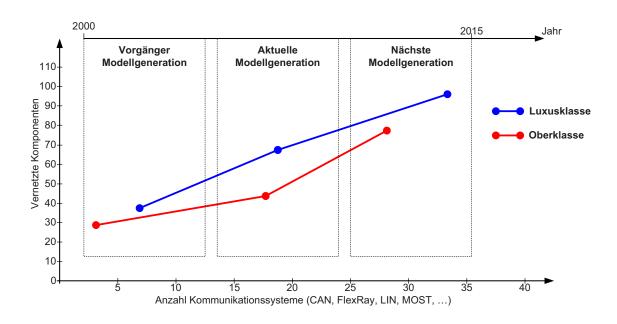

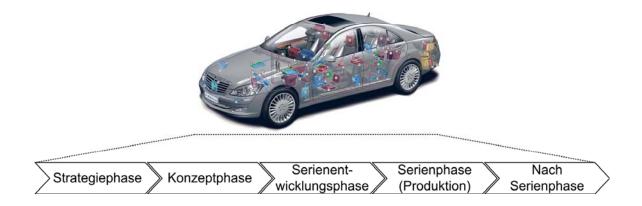

Heutige Fahrzeuge, insbesondere der Ober- und Luxusklasse, sind mit einer großen Anzahl an Funktionen ausgestattet, die dem Fahrer und den Passagieren ein hohes Maß an Komfort und Sicherheit bieten. Beispiele hierfür sind: Die fahrdynamischen Sitze, welche bei starker Querbeschleunigung den Insassen mehr Halt geben, Navigationssysteme mit 3D-Darstellung und dynamischer Routenberechnung sowie sogenannte Assistenzfunktionen wie Abstandsregeltempomat, Fahrspur- und Lichtassistenten, die dem Fahrer Routineaufgaben abnehmen (siehe z.B. [140] und [19]). Die Basis für diese Funktionen sind in zunehmendem Umfang Elektrik-/Elektronik-Systeme. Keine andere Technologie hat das Auto in den vergangenen 30 Jahren so stark verändert wie die Elektronik. Elektrik und Elektronik (E/E) machen heute rund 30 Prozent der Wertschöpfung eines Mittelklassefahrzeugs aus und sind die wesentlichen Treiber für etwa 90 Prozent aller Innovationen im Automobil [30]. In Abbildung 1.1 ist die Zunahme dieser Systeme anhand der Anzahl an vernetzten Komponenten und Bussen am Beispiel zweier Modellreihen der Ober- und Luxusklasse über eine Zeitspanne von 15 Jahren skizziert.

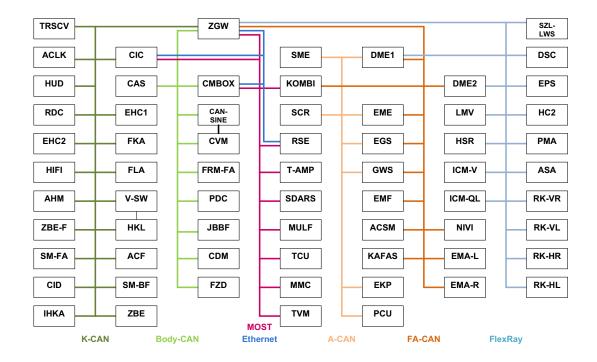

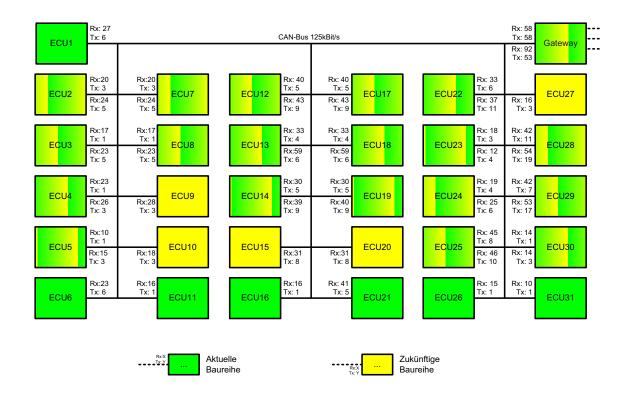

Die steigende Funktionalität und Komplexität von Elektrik-/Elektronik-Architekturen (E/E-Architekturen) und das damit verbundene zunehmende Kommunikationsaufkommen stellen immer höhere Anforderungen an den Entwicklungsprozess. Eine zentrale Rolle bei der Entwicklung spielt die Auslegung robuster und zukunftsfähiger Vernetzungsarchitekturen [131]. In bisherigen Topologien dominierten CAN- und LIN-Busse. Aktuelle und zukünftige Vernetzungsarchitekturen werden durch die notwendige Einführung von neuen Bussystemen wie FlexRay und Ethernet wesentlich heterogener. Eine Folge sind zusätzliche Herausforderungen, die sich bei der Auslegung und Absicherung der Gateway-Steuergeräte ergeben, da diese nun das Routing von Informationen zwischen unterschiedlichen Protokollen durchführen müssen. Eine derzeit typische Vernetzungsarchitektur eines Fahrzeugs der Luxusklasse ist in Abbildung 1.2 am Beispiel

Abb. 1.1.: Anstieg der Anzahl an vernetzten Komponenten und Bussen am Beispiel zweier Modellreihen mit durchschnittlicher Ausstattung

eines aktuellen Fahrzeugs von BMW dargestellt. Die Abbildung zeigt die hohe Anzahl an Steuergeräten und Kommunikationssystemen sowie welche wichtige Rolle das zentrale Gateway-Steuergerät (ZGW) einnimmt.

Zusätzliche Komplexität bringt die funktionale Hochintegration mit sich, welche das Ziel hat die Anzahl der Steuergeräte im Fahrzeug zu reduzieren bzw. konstant zu halten. Insbesondere die Auslegung und die Absicherung des Schedules werden durch die Vielzahl an Funktionen wesentlich aufwändiger. Diese Herausforderungen gilt es im Entwicklungsprozess von E/E-Architekturen zu adressieren. Die funktionalen Anforderungen werden noch durch weitere Anforderungen hinsichtlich Qualität, Testbarkeit, Diagnostizierbarkeit ergänzt [33]. Ziel des Entwurfs von E/E-Architekturen ist ein Höchstmaß an Zuverlässigkeit und dies möglichst kostenoptimal. Die Skalierbarkeit darf dabei nicht vernachlässigt werden. Erstens dient eine E/E-Architektur meist als Plattform für mehrere Baureihen, zweitens erhöht sich das Kommunikationsaufkommen durch die Integration von neuen Funktionen, zum Beispiel bei der Modellpflege, innerhalb eines Produktlebenszyklus einer Baureihe. Hierfür sind bei der initialen Entwicklung einer E/E-Architektur entsprechende Reserven einzuplanen. Die zukünftigen Anforderungen können über die Abfrage der Produktstrategie abgeleitet werden und zeigen welche Funktionalinnovationen in den nächsten Jahren zur Umsetzung anstehen. In diesem Zu-

Abb. 1.2.: Vernetzungsarchitektur eines Fahrzeugs der Luxusklasse am Beispiel von BMW [40]

sammenhang spielen der Entwurf und die Auslegung der Vernetzungsarchitektur eine zentrale Rolle. Dabei gilt es die relevanten Anforderungen der Funktionen in der Entwurfsphase zu berücksichtigen und während der Integrationsphase abzusichern.

#### 1.2. Zunehmende Anforderungen an die Bewertung von Vernetzungsarchitekturen

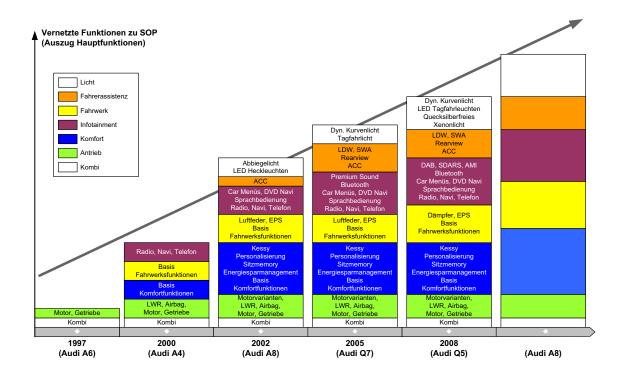

Die derzeit eingesetzten Verfahren zur Bewertung von Vernetzungsarchitekturen reichen nicht mehr aus, um eine vollständige Untersuchung der Systeme durchzuführen. Hierfür gibt es mehrere Gründe. Erstens werden die CAN-Busse immer öfter an deren Lastgrenze betrieben, so dass die bisher eingesetzten Metriken zur Buslastberechnung als einzige Absicherung nicht mehr genügen, zweitens treten durch die zunehmende Heterogenität der Vernetzungsarchitekturen Timing-Effekte auf, die es zu berücksichtigen gilt. Diese Effekte spielten in reinen CAN-Topologien keine Rolle. Drittens steigt die Anzahl der verteilten Funktionen kontinuierlich an. Ein Beispiel für den Anstieg der verteilten Funktionen ist in Abbildung 1.3 anhand verschiedener Baureihen der Audi AG dargestellt. Insbesondere im Bereich der Fahrerassistenzfunktionen wird deutlich sichtbar, dass die Verteilung stark zunimmt.

Abb. 1.3.: Steigende Anzahl an vernetzten Funktionen am Beispiel der Produktlinien der Audi AG [33]

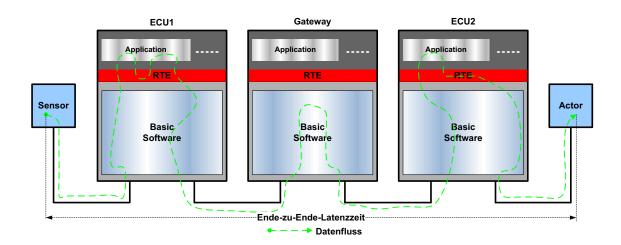

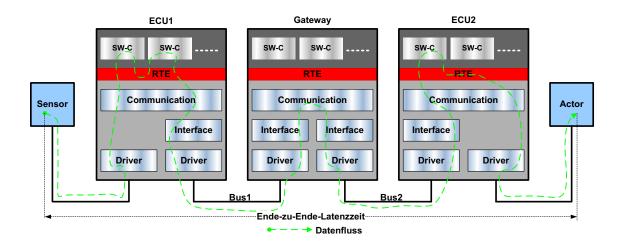

Viele dieser verteilten Funktionen sind sicherheitskritisch und müssen daher einer erweiterten Absicherung unterzogen werden. Hinsichtlich des Timing-Verhaltens stehen dabei die Latenzzeiten und Jitter der über das Netzwerk übertragenen Botschaften und Signale im Fokus. Ein exemplarischer Ende-zu-Ende-Pfad von einem Sensor bis zu einem Aktuator ist in Abbildung 1.4 skizziert. Ein solcher Pfad kann mehrere Steuergeräte und Busse enthalten. Um für so einen Pfad eine Timing-Bewertung durchführen zu können, sind die einzelnen Pfadsegmente im Detail zu untersuchen. Es müssen die Latenzzeiten, die bei der Übertragung auf den Bussen entstehen, berücksichtigt werden ebenso die Latenzzeiten, die in beteiligten Steuergeräten selber auftreten.

Ein weiterer wichtiger Punkt für den Einsatz von Timing-Bewertungsverfahren im Entwicklungsprozess sind die gesetzlichen Anforderungen und Richtlinien, welche bei der Entwicklung einer E/E-Architektur zu berücksichtigen sind. Als Beispiele kann hier die Richtlinie für die *On-Board-Diagnose (OBD)* genannt werden sowie die Norm *ISO26262*. Diese Norm ist für sicherheitskritische elektrisch/elektronische Systeme in Kraftfahrzeugen zukünftig von Relevanz.

Abb. 1.4.: Beispiel für eine Ende-zu-Ende-Latenzzeit für ein Signal vom Sensor bis zum Aktor

#### 1.3. Zielsetzungen der Arbeit

Die vorgestellten Trends und Anforderungen erfordern den Ausbau der Bewertungsmethodik für Vernetzungsarchitekturen, um auch zukünftige Fahrzeuge mit robusten und erweiterbaren E/E-Architekturen entwickeln zu können. Insbesondere bei sicherheitskritischen verteilten Funktionen müssen schon in einer frühen Entwicklungsphase Aussagen bezüglich deren Anforderungen an eine Vernetzungsarchitektur und deren Realisierbarkeit getroffen werden. Ein solches Vorgehen für eine frühzeitige und erweiterte Konzeptabsicherung führt zu einer Qualitätssteigerung und einer Reduzierung von Kosten für die Behebung von Fehlern, die ansonsten erst in einer viel späteren Entwicklungsphase zum Vorschein kämen [106].

Seit mehreren Jahren wird der Einsatz von Timing-Bewertungsverfahren im Entwicklungsprozess von E/E-Architekturen im Kraftfahrzeug vorangetrieben. Aktuell werden in verschiedenen Forschungsprojekten und Gremien die Methoden erarbeitet und die notwendigen Austauschformate spezifiziert, z.B. im *AUTOSAR-Konsortium* und im von der Europäischen Union geförderten *TIMMO-Projekt* ([15], [120]). Auch Fachzeitschriften beschäftigen sich zunehmend mit dem Thema (zum Beispiel in [57] und [58]). Einige Ansätze zur Integration der Verfahren in den Entwicklungsprozess wurden auch schon von OEMs und Zulieferern auf Konferenzen vorgestellt (zum Beispiel in [107], [95], [79] und [29]).

Die folgenden Punkte wurden in diesen Projekten und Arbeiten bisher jedoch nur unvollständig adressiert:

- Der Einsatz und die Einordnung der verschiedenen Timing-Bewertungsverfahren in den automotive E/E-Entwicklungsprozess wurden bisher nicht vollständig untersucht.

- Die Möglichkeiten der Timing-Bewertung von komplexen Vernetzungsarchitekturen, die vom OEM zu entwickeln sind, wurden bis heute nicht im Detail untersucht und aufgezeigt.

- Die detaillierte Timing-Bewertung von Gateway-Steuergeräten mit analytischen Verfahren wurde bislang nicht angegangen.

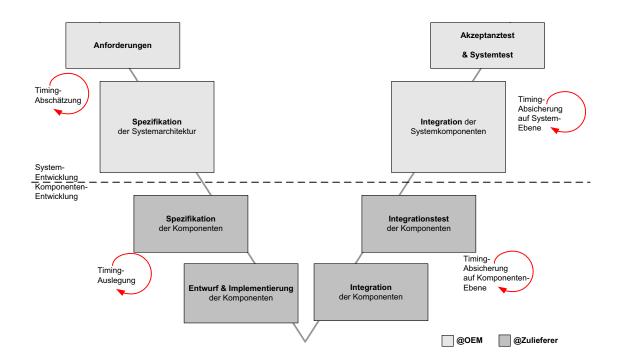

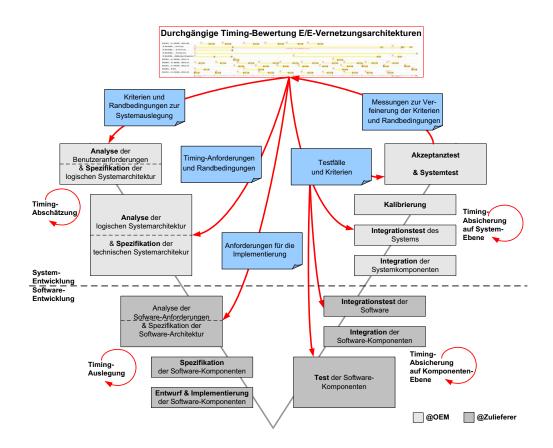

Diese offenen Punkte werden in der vorliegenden Arbeit adressiert und Lösungen hierfür erarbeitet. Der Hauptfokus dieser Dissertation liegt in der Entwicklung einer Methodik für die durchgängige Bewertung von Timing-Fragestellungen innerhalb des E/E-Entwicklungsprozesses von Vernetzungsarchitekturen und Gateway-Systemen im Kraftfahrzeug. In Abbildung 1.5 sind die wichtigsten Schritte anhand des V-Modells dargestellt. In der Entwurfsphase können erste Timing-Abschätzungen durchgeführt werden, wobei die daraus gewonnen Erkenntnisse dann als Grundlage für die Spezifikation und zur Auslegung der Systeme dienen können. Bei der anschließenden Absicherung kann das spezifizierte Timing-Verhalten verifiziert werden.

Das Ziel der Arbeit ist es, den durchgängigen Einsatz von Timing-Bewertungsverfahren im existierenden Entwicklungsprozess zu ermöglichen und die notwendige Methodik aufzuzeigen. Hierfür werden folgende Punkte in dieser Dissertation adressiert:

- Darstellung des Stands der Technik im Bereich der Bewertung von automotive Vernetzungsarchitekturen. Einordnung von Timing-Bewertungsverfahren in den existierenden E/E-Entwicklungsprozess für die Beantwortung von Fragestellungen im Bereich der Vernetzungsarchitekturen und Gateway-Systeme.

- 2. Identifikation der notwendigen Daten, die für eine aussagekräftige Timing-Bewertung notwendig sind. In diesem Zusammenhang wird ein Verfahren zur Extraktion von Timing-Informationen aus Loggingdaten entwickelt.

- 3. Untersuchung der Wiederverwendung von Timing-Informationen aus existierenden Fahrzeugen für die Modellverfeinerung in der Entwurfsphase von E/E-Architekturen.

Abb. 1.5.: Timing-Bewertungen in den einzelnen Phasen des Entwicklungsprozesses von Elektrik-/Elektronik-Architekturen

- 4. Erweiterung und Verfeinerung der Timing-Bewertungsverfahren für automotive Fragestellungen, z.B. Erarbeitung von detaillierten Modellierungsregeln und Bewertungsmöglichkeiten für Vernetzungsarchitekturen und Gateway-Steuergeräten.

- 5. Aufzeigen einer durchgängigen Bewertungsmethodik für die Timing-Fragestellungen im E/E-Entwicklungsprozess.

- 6. Entwicklung eines Konzeptes zur Ableitung von Routing-Testpattern auf der Basis von Timing-Analysen, mit dem Ziel eine gezielte Berücksichtigung des Timing-Verhaltens von Steuergeräten mit Gateway-Anteilen am Komponentenprüfstand zu ermöglichen.

Die entwickelten Konzepte und Methoden dieser Arbeit werden anschließend auf deren Tauglichkeit überprüft und anhand von repräsentativen Beispielen aus der Praxis validiert. Die Evaluierung wird mit der entstandenen prototypischen Werkzeugkette durchgeführt, die es ermöglicht eine durchgängige Bewertung des Timing-Verhaltens von Vernetzungsarchitekturen durchzuführen. Bei der Daimler AG wurden in den letzten Jahren die formale Beschreibung sowie der werkzeuggestützte Entwurf von E/E-Architekturen

eingeführt und stetig weiterentwickelt (siehe [103]). Die in dieser Arbeit entwickelte Methodik soll zukünftig Anwendung in diesem Prozess finden und in die Serie überführt werden.

#### 1.4. Gliederung der Arbeit

Die Arbeit gliedert sich wie folgt: In diesem Kapitel wurden die Motivation und die Zielsetzung für die Einführung von Timing-Analyse-Verfahren in den Entwurfsprozess von E/E-Architekturen im Kraftfahrzeug vorgestellt. In Kapitel 2 wird die Thematik der Timing-Bewertung eingeführt sowie die in dieser Arbeit verwendete Terminologie vorgestellt. Darauf aufbauend erfolgt die Herleitung der Timing-Anforderungen, die sich in diesem Bereich stellen. Kapitel 3 gibt einen Überblick über den aktuellen Stand von E/E-Architekturen. Weiterhin werden Kenngrößen eingeführt, welche für eine Timing-Bewertung von Bedeutung sind. In Kapitel 4 werden Verfahren vorgestellt, die eine Timing-Bewertung ermöglichen. Im Anschluss an die Vorstellung der einzelnen Ansätze erfolgt eine Einordnung der Verfahren sowie eine Abgrenzung dieser Dissertation von anderen aktuellen Arbeiten in diesem Themengebiet. Davon ausgehend wird in dieser Arbeit eine Methodik entwickelt, welche eine durchgängige Integration der Timing-Bewertungsverfahren in die existierende Entwicklungskette ermöglicht. Es werden dabei Timing-Fragestellung berücksichtigt, die sich sowohl im Bereich Vernetzung als auch im Umfeld der Gateway-Entwicklung ergeben. In Kapitel 5 wird ein Verfahren vorgestellt, welches die Möglichkeit bietet, Timing-Informationen aus existierenden Vernetzungsarchitekturen zu extrahieren. Weiterhin werden in Kapitel 6 Modellierungsregeln definiert, die eine präzise Abbildung des Timing-Verhaltens der Systeme ermöglichen. Basierend auf den Erkenntnissen der vorangegangenen Arbeiten, wird in Kapitel 7 die Methodik für eine durchgängige Timing-Bewertung anhand einer prototypischen Werkzeugkette aufgezeigt und deren Integration in den existierenden Entwicklungsprozess von E/E-Architekturen beschrieben. Weiterhin wird in Kapitel 7 ein Konzept für die Generierung von Routing-Testpattern vorgestellt. Die Testpattern ermöglichen eine Absicherung von Steuergeräten mit Gateway-Funktionalität am Komponenten-Prüfstand während der Integrationsphase. In Kapitel 8 erfolgt die Validierung der entwickelten Methodik anhand von Beispielen aus der Praxis. Kapitel 9 fasst die erzielten Ergebnisse der Arbeit zusammen und gibt einen Ausblick auf mögliche Erweiterungen.

#### 2. Grundlagen der Arbeit

Im vorangegangenen Kapitel wurde das Thema Timing-Bewertung von E/E-Architekturen im Kraftfahrzeug motiviert. Um bei den weiteren Ausführungen auf einer einheitlichen Terminologie aufzusetzen, werden im Folgenden die in dieser Arbeit verwendeten Begriffe eingeführt.

#### 2.1. Eingebettete verteilte Echzeitsysteme

Eingebettete verteilte *Echtzeitsysteme* (*engl. Real-Time Systems*) unterscheiden sich hinsichtlich der Zeitanforderungen grundlegend von den allgemeinen Computersystemen (z.B. Büro-Computer), sogenannten *Nicht-Echtzeitsystemen*. Bei den Nicht-Echtzeitsystemen kommt es ausschließlich auf die Korrektheit der Datenverarbeitung und der Ergebnisse an [143]. Im Gegensatz dazu spielt bei den Echtzeitsystemen neben der Korrektheit der Ergebnisse auch die Einhaltung der Zeitanforderungen eine zentrale Rolle. Zeitbedingungen, deren Nichteinhalten zu einer *Katastrophe* führen können, heißen harte Zeitbedingungen [65]. Alle anderen Zeitbedingungen heißen weiche Zeitbedingungen. Weitere wichtige Anforderungen an Echtzeitsysteme sind: *Rechtzeitigkeit*, *Gleichzeitigkeit*, *Verfügbarkeit* (siehe [143]) sowie *Vorhersagbarkeit* und *Zuverlässigkeit* [102]:

- Mit Rechtzeitigkeit ist die Anforderung gemeint, die garantiert, dass eine Ausführung auf einer CPU bzw. eine Übertragung über einen Bus innerhalb der definierten Zeitschranke abgeschlossen wird.

- Ein Echtzeitsystem muss in der Lage sein, mehrere Ereignisse gleichzeitig verarbeiten können, damit die Rechtzeitigkeit für mehrere Aktionen gleichzeitig gewährleistet ist. Zum Beispiel durch (quasi-) parallele Ausführung auf einem Prozessor oder echte parallele Ausführung auf einem Mehrprozessorsystem [114].

- Innerhalb eines spezifizierten Zeitbereichs muss ein Echtzeitsystem immer uneingeschränkt zur Verfügung stehen, d.h. ohne Unterbrechung betriebsbereit sein.

- Die Anforderung der Vorhersagbarkeit ist die Forderung, dass alle von einem System zu verarbeitenden Ereignisse und Funktionen vor der Ausführung bekannt und deterministisch sein müssen [102].

- Die Zuverlässigkeit ist die Fähigkeit eines Systems, während einer vorgegebenen Zeitdauer bei zulässigen Betriebsbedingungen die spezifizierte Funktion zu erbringen [102].

#### 2.2. Begriffsdefinitionen

Die folgenden Begriffsdefinitionen basieren zu großen Teilen auf dem Standardwerk von G. Buttazzo *Hard Real-Time Computing Systems* [21]. Generell gilt: Zeitpunkte werden immer mit *Kleinbuchstaben* annotiert, Zeiträume mit *Großbuchstaben*.

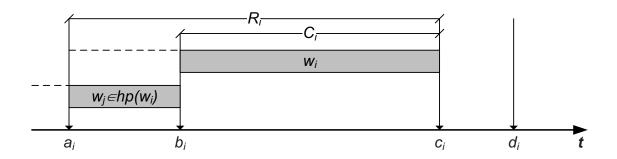

**Definition 2.1** (Ausführungszeit/Übertragungszeit) Die Ausführungszeit bzw. Übertragungszeit  $C_i$  ist die Zeit, welche benötigt wird, um einen Task  $w_i$  ohne Unterbrechung auszuführen oder eine Botschaft  $m_i$  zu übertragen.

**Definition 2.2 (Aktivierungszeitpunkt)** Der Aktivierungszeitpunkt (engl. Release)  $a_i$  ist der Zeitpunkt, an dem ein Task  $w_i$  bereit ist zur Ausführung bzw. eine Botschaft  $m_i$  zur Übertragung ansteht.

**Definition 2.3 (Startzeitpunkt)** Der Startzeitpunkt  $b_i$  ist der Zeitpunkt, an dem die Ausführung eines Tasks  $w_i$  startet bzw. die Übertragung einer Botschaft  $m_i$  beginnt.

**Definition 2.4 (Ende der Ausführung)** Das Ende der Ausführung (engl. Termination) eines Tasks  $w_i$  bzw. der Abschluss der Übertragung einer Botschaft  $m_i$  wird mit  $c_i$  angegeben.

**Definition 2.5 (Deadline)** Die Deadline  $d_i$  ist der Zeitpunkt, an dem eine Abarbeitung eines Tasks  $w_i$  oder die Übertragung einer Botschaft  $m_i$  abgeschlossen sein muss.

**Definition 2.6 (Antwortzeit)** Die Antwortzeit (engl. Response Time)  $R_i$  gibt die Zeitdauer, an die ein Task  $w_i$  bzw. eine Botschaft  $m_i$  tatsächlich für die Ausführung benötigt bzw. wieviel Zeit bei deren Übertragung ab dem Zeitpunkt der Aktivierung  $a_i$  vergangen ist.

Abbildung 2.1 zeigt ein Beispiel für ein Prioritätsscheduling. Ein Task  $w_i$ , wird zum Zeitpunkt  $a_i$  aktiviert. Die Ausführung startet erst bei  $b_i$ , da noch höherpriore Tasks  $w_j \in hp(w_i)$  aktiv sind. Nach der Ausführungszeit  $C_i$  wird der Task  $w_i$  zum Zeitpunkt  $c_i$  innerhalb der Deadline  $d_i$  beendet. Die Antwortzeit der Task ergibt sich aus der Ausführungszeit  $C_i$  und der Zeit, während der Task  $w_i$  seit dem Aktivierungszeitpunkt durch höherpriore Tasks verzögert wird. Prinzipiell kann der Task  $w_i$  auch während ihrer Ausführung durch höherpriore Tasks  $w_j \in hp(w_i)$  unterbrochen und dadurch weiter verzögert werden. Dies ist in Abbildung 2.1 nicht mit aufgezeigt, um eine einfache Darstellung zu gewährleisten.

Abb. 2.1.: Timing-Eigenschaften eines Tasks  $w_i$ , die durch höherpriore Tasks  $w_j \in hp(w_i)$  verzögert wird

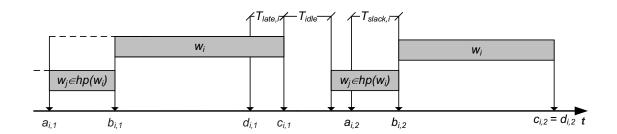

**Definition 2.7 (Idle-Zeit)** Die Idle-Zeit  $T_{idle}$  definiert die Zeitdauer, während der kein Tasks zur Ausführung oder Botschaften zur Übertragung anstehen. Die CPU bzw. das Übertragungsmedium ist in dieser Zeit nicht belegt.

**Definition 2.8 (Verspätung)** Die Verspätung (engl. Lateness)  $T_{late,i}$  ist die Zeitdauer, die ein Task  $w_i$  oder eine Botschaft  $m_i$  in Bezug auf die Deadline  $d_i$  zu spät kommt. Wird die Ausführung bzw. Übertragung innerhalb der Deadline beendet, so ist die Verspätung  $T_{late,i}$  negativ.

$$T_{late,i} = c_i - d_i [2.1]$$

**Definition 2.9** (Überschreitungszeit) Die Überschreitungszeit (Exeeding Time)  $T_{exe,i}$  definiert die Zeit, welche ein Task  $w_i$  oder eine Botschaft  $m_i$  nach Überschreitung der Deadline noch aktiv ist.

$$T_{exe,i} = max(0, T_{late,i})$$

[2.2]

**Definition 2.10 (Schlupf)** Der Schlupf (engl. slack) definiert die Zeit, die ein Task  $w_i$  oder eine Botschaft  $m_i$  nach seiner Aktivierung maximal verzögert werden darf, damit dieser noch vor der Deadline vollständig ausgeführt werden kann.

$$T_{slack,i} = d_i - a_i - C_i [2.3]$$

In Abbildung 2.2 sind die weiteren Timing-Eigenschaften am Beispiel eines Tasks  $w_i$  dargestellt.

Abb. 2.2.: Weitere Timing-Eigenschaften eines Tasks  $w_i$

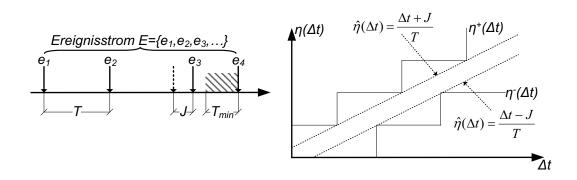

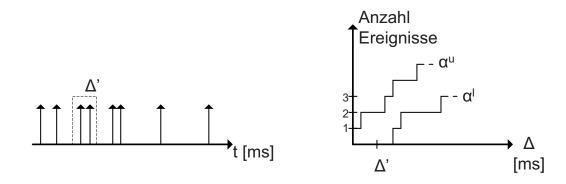

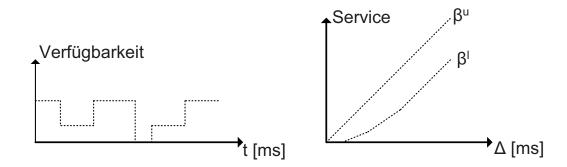

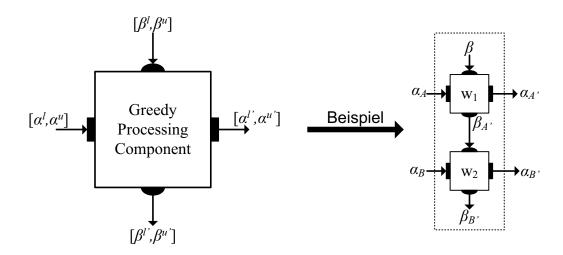

**Definition 2.11 (Ereignis, Ereignisstrom)** Ein Ereignis e ist ein Vorkommnis (z.B. ein Statuswechsel), das sich zu einem bestimmten Zeitpunkt t ereignet [65]. Ein Ereignisstrom  $E = \{e_1, e_2, e_3, ...\}$  beschreibt die Abfolge von Ereignissen. Ein Ereignisstrom ist definiert über vier charakteristische Funktionen [96]:

$$\eta^+: \mathbb{R}^+ \mapsto \mathbb{N}^+, \tag{2.4}$$

$$\eta^-: \mathbb{R}^+ \mapsto \mathbb{N}^+, \tag{2.5}$$

$$\delta^+: \mathbb{N}^+ \setminus \{0,1\} \mapsto \mathbb{R}^+ \text{ and}$$

[2.6]

$$\delta^-: \mathbb{N}^+ \setminus \{0,1\} \mapsto \mathbb{R}^+ \text{ and }$$

[2.7]

Die Funktion  $\eta^+(\Delta t)$  beschreibt die maximale Anzahl an Ereignissen innerhalb eines Zeitintervalls  $\Delta t$ . Über die Funktion  $\eta^-(\Delta t)$  wird die minimale Anzahl an Ereignissen in einem Zeitintervall  $\Delta t$  beschrieben. Die Funktionen  $\delta^+(n)$  und  $\delta^-(n)$  geben den maximalen bzw. minimalen Abstand zwischen n aufeinanderfolgenden Ereignissen an.

**Definition 2.12 (Minimaler Auftritts-/Sendeabstand)** *Der minimale Auftritts-/Sende- abstand* (engl. Minimum Distance)  $T_{min,i}$  *gibt an, welcher Mindestabstand zwischen zwei aufeinanderfolgenden Tasks*  $w_i$  *oder Botschaften*  $m_i$  *eingehalten werden muss.*

**Definition 2.13 (Jitter)** Der Jitter beschreibt die Abweichung eines Tasks  $w_i$  oder einer Botschaft  $m_i$  von dem definierten Aktivierungs-/Sendezeitpunkt (Periode). Es wird zwischen Eingangsjitter  $J_{in}$  und Ausgangsjitter  $J_{out}$  unterschieden.

In Abbildung 2.3 sind exemplarisch ein Ereignisstrom mit Jitter J und Mindestsendeabstand  $T_{min}$  sowie die resultierende Funktion  $\eta(\Delta t)$  aufgezeigt.

Abb. 2.3.: Exemplarischer Ereignisstrom und die resultierende Funktion  $\eta(\Delta t)$

**Definition 2.14 (Absoluter Jitter)** Der absolute Jitter  $J_a$  gibt die maximale Abweichung an, welche über die gesamte Zeit zwischen den Instanzen eines Tasks oder einer Botschaft auftritt. Dabei gilt für den absoluten Eingangsjitter:

$$J_{a_{in,i}} = \max_{k} (b_{i,k} - a_{i,k}) - \min_{k} (b_{i,k} - a_{i,k})$$

[2.8]

Für den relativen Ausgangsjitter gilt:

$$J_{a\_out,i} = \max_{k} (c_{i,k} - a_{i,k}) - \min_{k} (c_{i,k} - a_{i,k})$$

[2.9]

**Definition 2.15 (Relativer Jitter)** Der relative Jitter  $J_r$  gibt die Abweichung von zwei aufeinanderfolgenden Task- oder Botschaftsinstanzen an. Für den relativen Eingangsjitter gilt:

$$J_{r\_in,i} = \max_{k} \left| (b_{i,k} - a_{i,k}) - (b_{i,k-1} - a_{i,k-1}) \right|$$

[2.10]

Für den relativen Ausgangsjitter gilt:

$$J_{r\_out,i} = \max_{k} \left| (c_{i,k} - a_{i,k}) - (c_{i,k-1} - a_{i,k-1}) \right|$$

[2.11]

**Definition 2.16 (Latenzzeit)** Latenzzeit L, in unterschiedlichen Zusammenhängen auch Reaktionszeit, Verweilzeit oder Verzögerungszeit genannt, ist der Zeitraum zwischen einer Aktion (bzw. einem Ereignis) und dem Eintreten einer verzögerten Reaktion. Bei einer Latenzzeit ist die Aktion verborgen und wird erst durch die Reaktion deutlich [142].

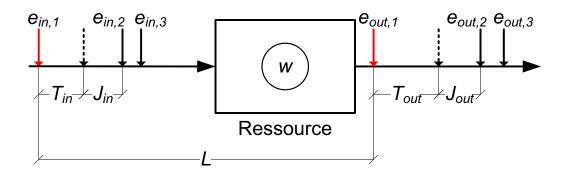

In Abbildung 2.4 ist ein gemappter Task w dargestellt sowie ein Eingangsereignisstrom  $E_{in}$  und der resultierende Ausgangsereignisstrom  $E_{out}$  inklusive der Jitter.

Abb. 2.4.: Beispiel für ein gemappter Task sowie ein Eingangsereignisstrom  $E_{in}$  und der resultierende Ausgangsereignisstrom  $E_{out}$

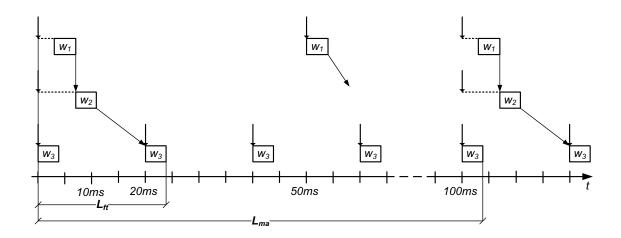

**Definition 2.17** (**Hyperperiode oder Makroperiode**) Die Hyperperiode H oder auch Makroperiode genannt, gibt die Periode an, bei der sich der Plan für das Scheduling wiederholt. Sie ist das kleinste gemeinsame Vielfache aller Perioden der im System vertretenen Jobs [117].

**Definition 2.18 (Offset)** Der Offset  $T_{off}$  beschreibt die Zeit, die nach dem Systemstart gewartet wird, bis ein Task  $w_i$  ausgeführt bzw. eine Botschaft  $m_i$  verschickt wird.

**Definition 2.19** (Auslastung) Die Auslastung U engl. Utilization beschreibt die Belegung einer Ressource. Beispielsweise kann für n unabhängige periodische Tasks  $w_i$ , für die gilt, dass deren Periode  $T_i$  gleich der Deadline  $d_i$  ist, wie folgt berechnet werden:

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i}$$

[2.12]

In der vorliegenden Arbeit wird oft der Begriff Architektur verwendet. Dessen Handhabung ist in der Literatur sehr unterschiedlich. Häufig findet sich eine starke Analogie zwischen den Begriffen Architektur und Topologie [106]. Um für die Arbeit eine einheitliche Terminologie festzulegen, wird für einige wichtige Begriffe eine eindeutige Definition gegeben, diese werden in dieser Arbeit wie folgt verwendet.

**Definition 2.20 (Architektur)** Eine Architektur ist die grundlegende Organisation eines Systems, verkörpert durch deren Komponenten, ihre Beziehungen zueinander und zur Umgebung sowie den Prinzipien, die das Design und die Evolution leiten [24].

Bei einer E/E-Architektur im Kraftfahrzeug werden die Komponenten durch die einzelnen Busse und Steuergeräte repräsentiert.

**Definition 2.21 (Topologie)** Eine Topologie (griech.: Topos = Ort) ist die Beschreibung jeglicher Art von Anordnung von Elementen und deren Verbindungen [106].

Die Topologie umfasst folglich einen Teil der Architektur. Die Architektur beschreibt nicht nur die Anordnung, sondern zusätzlich auch die verwendeten Elemente und Technologien eines Systems sowie deren Schnittstellen.

**Definition 2.22 (Vernetzungsarchitektur)** Die Vernetzungsarchitektur enthält die Netzwerktopologie, d.h. die einzelnen Busse sowie die Verbindungen/Schnittstellen der an die Busse angekoppelten Steuergeräte und enthält die verwendeten Kommunikationssysteme (Technologie).

Weiterhin werden die Begriffe Hardwarearchitektur und Softwarearchitektur für die detaillierte Beschreibung von Steuergeräten verwendet. Die Hardwarearchitektur umfasst die technische Realisierung eines Steuergerätes, z.B. CPU, Speicher, Schnittstellen. Die Softwarearchitektur beschreibt die Applikations- sowie die Basissoftware eines Steuergerätes.

#### 2.3. Anforderungen an den Timing-Bewertungsprozess

Zu jedem Zeitpunkt im E/E-Entwicklungsprozess muss eine ausreichende Menge an Timing-Informationen vorliegen, damit eine aussagekräftige Bewertung durchgeführt werden kann. Zu den Timing-Informationen zählen:

- Ausführungszeiten der Tasks und Übertragungszeiten der Botschaften

- Konfiguration des Betriebssystems und der Kommunikationssysteme

- Beschreibung des Timing-Verhaltens der Eingangsereignisse, z.B. der anwenderabhängigen Interaktion, um die entsprechenden Verhaltensmodelle abzuleiten

- Beschreibung des Sendeverhaltens der Botschaften.

- Weitere Timing-Informationen wie z.B. Jitter, Drift und Offsets

Das Ziel ist es, sowohl auf Komponentenebene (Steuergeräte und Busse) als auch auf Systemebene, eine fundierte Aussage über das Timing-Verhalten treffen zu können. Die hierfür notwendigen Timing-Informationen können bisher nur teilweise direkt aus den Spezifikationen entnommen werden. Einige Informationen sind implizit vorhanden und lassen sich über Regeln ableiten, z.B. die Übertragungszeit  $C_i$  einer Botschaft  $m_i$  kann anhand deren Länge  $p_i$  und der Übertragungsgeschwindigkeit V des Kommunikationssystems berechnet werden. Für die Beschreibung der noch fehlenden Informationen besteht meist ein direkter Zusammenhang mit der Interaktion des Fahrers und der Passagiere mit den E/E-basierten Funktionen. Dieses spontane Timing-Verhalten kann über die Beobachtung (Messung) der E/E-Systeme bestimmt werden.

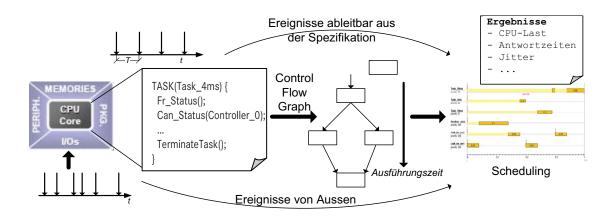

Abbildung 2.5 zeigt diese Schwierigkeit anhand eines Steuergeräts. Aus der Systembeschreibung und über Auswertungen der Code-Laufzeiten können viele Timing-Informationen ermittelt werden. Insbesondere jedoch die Ereignisse, welche von außen ausgelöst werden und direkten Einfluss auf die Ausführungszeiten haben, lassen sich nur schwer spezifizieren.

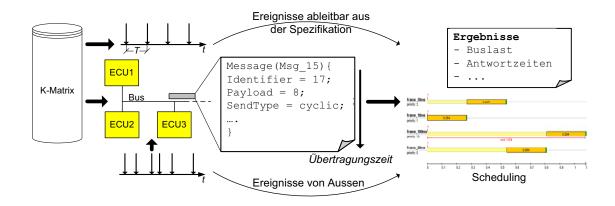

In gleicher Weise wie bei Steuergeräten verhält es sich bei der Timing-Bewertung von Kommunikationssystemen (siehe Abbildung 2.6). Ohne die Kenntnisse über das dynamische Timing-Verhalten der Busteilnehmer (Steuergeräte) ist eine sinnvolle Bewertung der Buskommunikation nicht möglich. Diese Dynamik, welche in der Versendung von

Abb. 2.5.: Einflüsse und Informationen für eine Timing-Bewertung von Steuergeräten

spontanen Botschaften resultiert, hängt in den meisten Fällen direkt mit Interaktionen der Insassen des Fahrzeugs zusammen.

Um das Problem der fehlenden Timing-Informationen zu lösen, wird in der vorliegenden Arbeit eine Methodik vorgestellt, die eine durchgängige und aussagekräftige Timing-Bewertung innerhalb des Entwicklungsprozesses von E/E-Architekturen ermöglicht und Wege aufzeigt, die dafür notwendigen Timing-Informationen bereitzustellen. Ferner können die ermittelten Informationen schrittweise als zusätzliche Attribute (Kriterien oder Anforderungen) in die Spezifikationen der E/E-Systeme einfließen. Auf deren Basis ist dann zukünftig eine genauere Auslegung der Systeme möglich. Ferner sind die ermittelten Timing-Informationen für eine Modellverfeinerung in der Entwurfsphase von E/E-Architekturen verwendbar.

Abb. 2.6.: Einflüsse und Informationen für eine Bewertung von Kommunikationssystemen

# 3. E/E-Architekturen und Entwicklungsprozesse

In diesem Kapitel werden die Grundlagen der E/E-Architekturen im Kraftfahrzeug eingeführt, welche im Kontext der Timing-Bewertungen relevant sind. Weiterhin erfolgt die detaillierte Beschreibung der einzelnen Komponenten. Im Anschluss daran wird auf den aktuellen E/E-Entwicklungsprozess eingegangen und es werden die detaillierten Anforderungen für die Timing-Bewertungen abgeleitet. Abschließend erfolgt die Ableitung der hierfür wesentlichen Kenngrößen.

## 3.1. E/E-Architekturen im Kraftfahrzeug

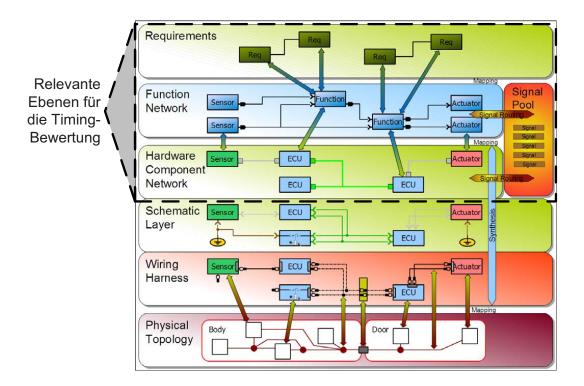

Die Begriffsdefinitionen für Architektur, Topologie, etc. wurden in Abschnitt 2.2 gegeben. Eine E/E-Architektur im Kraftfahrzeug umfasst das Funktionsnetzwerk, das Netzwerk der Hardwarekomponenten, den Leitungssatz und die physikalische Topologie. Die Unterteilung in die verschiedenen Ebenen ist in Abbildung 3.1 dargestellt. *Top-Down* betrachtet werden die Anforderungen (*Requirements*) formuliert. Diese Anforderungen sind durch ein Netz kooperierender Funktionen realisiert (*Functional Network*). Die Software-Anteile der Funktionen sind auf den einzelnen Steuergeräten integriert. Die Verbindung der Steuergeräte ist über verschiedene Kommunikationssysteme realisiert. Weiterhin sind Sensoren und Aktoren an die Steuergeräte gekoppelt. Dieser Verbund bildet das Hardwarekomponentennetzwerk (*Hardware Component Network*). Der sogenannte *Schematic Layer* beinhaltet die Anschlüsse und Leitungen zwischen den einzelnen Komponenten sowie die Energieversorgung. Der Leitungssatz (*Wiring Harness*) ist in der nächsten Ebene zu finden. Die physikalische Topologie (*Physical Topology*) umfasst die Einbauorte und Kabeldurchführungen.

Die oberen drei Ebenen sind bei der Timing-Bewertung relevant. Dazu zählen die Hardware- und Software-Architektur der Steuergeräte sowie die Kommunikationssysteme. Die Topologieaspekte, wie Signallaufzeiten auf physikalischer Ebene und die hierfür notwendige Berücksichtigung der Leitungslängen, spielen bei der Betrachtung des

Timing-Verhaltens auf logischer Ebene keine Rolle und sind nicht Gegenstand dieser Arbeit. Die für die Timing-Bewertung relevanten Eigenschaften der Komponenten werden im Folgenden näher ausgeführt.

Abb. 3.1.: Die einzelnen Ebenen einer E/E-Architektur und die für die Timing-Bewertung relevanten Abschnitte [131]

# 3.1.1. Hardwarearchitektur von Steuergeräten

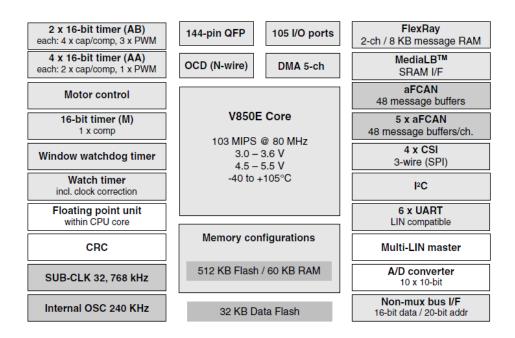

Die Hardware-Architektur von Steuergeräten umfasst die Steckerpins, das Gehäuse, die Platine sowie die elektronischen Baugruppen wie Spannungsversorgung, Leistungstreiber für die Ein- und Ausgänge und die Transceiver-Bausteine sowie die Recheneinheit, typischerweise ein Mikrocontroller. Ein Beispiel für einen heute eingesetzten 32-Bit Mikrocontroller ist in Abbildung 3.2 dargestellt. Der Baustein beinhaltet neben dem Rechenkern (hier: *V850E Core*) den flüchtigen und festen Speicher (*RAM* und *Flash*). Weiterhin werden diverse Schnittstellen zur Ankopplung von Sensorik und Aktorik sowie zur Anbindung verschiedener Kommunikationssysteme bereitgestellt.

Abb. 3.2.: Blockdiagramm eines aktuellen Microkontrollers V850/CAG4-M von NEC [84]

Für das Timing-Verhalten eines Steuergerätes bzw. der Software ist die Auswahl eines für die jeweiligen Aufgaben geeigneten Mikrocontrollers von zentraler Bedeutung. Für ein Gateway-Steuergerät beispielsweise ist eine homogene Ankoppelung der Peripherie an die CPU sehr wichtig, d.h. die Peripherie, z.B. die Buscontroller sollten nicht eine vielfach kleinere Frequenz als die CPU haben, damit möglichst wenig *Wait States* von der CPU bei der Datenübertragung zu dem Controller eingefügt werden müssen.

Ein weiteres wichtiges Thema im Zusammenhang mit der Timing-Bewertung werden zukünftig die Multicore-Architekturen von Mikrocontrollern sein, welche in naher Zukunft vermehrt in Steuergeräten eingesetzt werden. Das Verhalten und die Bewertung solcher Multicore-Systeme ist nicht Bestandteil dieser Arbeit. Die weiteren Ausführungen beziehen sich immer auf Single-Core Architekturen. Viele der entwickelten Konzepte sind jedoch auf Multicore-Architekturen übertragbar.

## 3.1.2. Softwarearchitektur von Steuergeräten

Die Softwarearchitektur eines Steuergerätes umfasst neben der Laufzeitumgebung auch die Applikationssoftware. Die Laufzeitumgebung beinhaltet das Betriebssystem, die Treiber für die Ansteuerung der Peripherie sowie Basisdienste. In der Applikationssoftware sind die kundenerlebbaren Funktionen gekapselt.

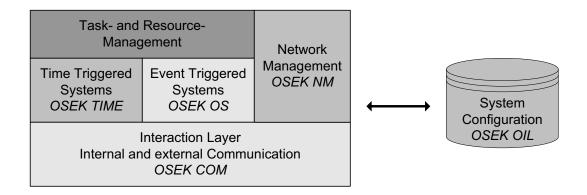

Da über den Einsatz einer OEM-eigenen Laufzeitumgebung kein signifikanter Wettbewerbsvorteil erzielt werden kann, wird seit vielen Jahren an herstellerübergreifenden Standards gearbeitet. Die wichtigsten Gremien sind OSEK/VDX (Offene Systeme für die Elektronik im Kraftfahrzeug/Vehicle Distributed Executive), die Herstellerinitiative Software (HIS) und AUTOSAR (Automotitve Open Systems Architecture) [87],[17]. Mit der Arbeit an OSEK/VDX wurde im Jahre 1995 begonnen und es ist aktuell in fast allen Steuergeräten aktueller Fahrzeuge zu finden. Mit dem Zusammenschluss vieler OEMs, Zulieferer und Toolhersteller im AUTOSAR-Konsortium erfolgte ein weiterer Schritt hin zu einer umfassenden Standardisierung. In AUTOSAR sind große Teile der Konzepte von OSEK eingeflossen.

### OSEK/VDX

Das OSEK/VDX-System besteht aus mehreren Modulen. In Abbildung 3.3 sind die einzelnen Module dargestellt.

Abb. 3.3.: Grundkomponenten des OSEK/VDX-Systems [144]

- 1. *OSEK-OS (Operating System)* ist ein ereignisgesteuertes Echtzeit-Multitasking Betriebssystem, welches die Möglichkeit zur Task-Synchronisation und Ressourcenverwaltung bietet [53].

- 2. *OSEK-TIME* ist die zeitgesteuerte Variante.

- 3. *OSEK-COM (Communication)* beschreibt die Interaktionsschicht zum internen Datenaustausch zwischen den Tasks eines Steuergerätes und zum externen Datenaustausch mit anderen Steuergeräten über die entsprechenden Schnittstellen.

- 4. Über das *OSEK-NM (Networkmanagement)* wird die Überwachung und Verwaltung der Kommunikation mit anderen Steuergeräten realisiert, die über ein Kommunikationssystem stattfindet.

- 5. *OSEK-OIL (OSEK Implementation Language)* ist eine Beschreibungssprache zur Konfiguration der aufgeführten Module.

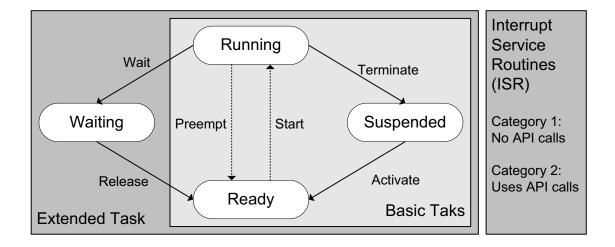

Die stärksten Einflüsse auf das Timing-Verhalten eines Steuergerätes hat das Betriebssystem und dessen Konfiguration. Aus diesem Grund werden im Folgenden die wichtigsten Eigenschaften des OSEK-OS diskutiert. Das OSEK-OS ist eingeteilt in vier Konformitätsklassen. Diese ermöglichen es je nach Anforderungen einen bestimmten Funktionsumfang des OSEK-OS für ein Steuergerät zu verwenden. Als Ausführungseinheiten für den Programmcode dienen die *Tasks*. Bei OSEK-OS wird zwischen *Basic Tasks* und *Extended Tasks* unterschieden. Basic-Tasks hängen nicht von äußeren Ereignissen ab, während Extended-Tasks auf Ereignisse von außen warten. Abbildung 3.4 zeigt das Zustandsmodell der OSEK-OS-Tasks.

Abb. 3.4.: Betriebssystemezustände für Basic Tasks und Extended Tasks des OSEK-OS[88]

Nach der Aktivierung einer Task (Suspended  $\rightarrow$  Ready) ist diese bereit zur Ausführung. Eine Task kann ausgeführt (Ready  $\rightarrow$  Running) werden, falls: 1) Die CPU nicht belegt ist, 2) ein preemptiver Task mit niederer Priorität gerade ausgeführt wird und 3) keine Interrupts ausgelöst wurden.

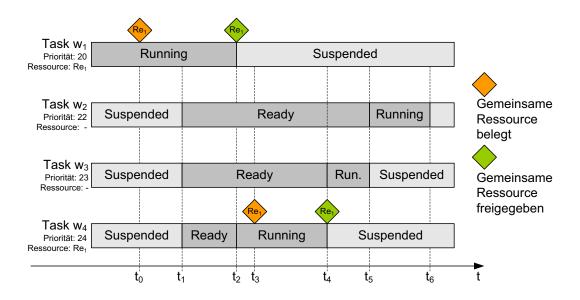

Beim OSEK-OS wird über den Scheduler die CPU-Zeit den Tasks über statische Prioritäten zugewiesen [61]. Im Gegensatz dazu arbeitet das OSEK-TIME über das TDMA-Verfahren. Alle Tasks beim OSEK-OS können durch Interrupts unterbrochen werden. Preemptive Tasks sind auch von höherprioren Tasks unterbrechbar. Bei gemeinsam genutzten Ressourcen wird der korrekte Zugriff über das *Priority-Ceiling-Protokoll* gesteuert. Ein Beispiel für ein Deadlock-freies Task-Scheduling des OSEK-OS ist in Abbildung 3.5 dargestellt.

Abb. 3.5.: Beispiel für das Scheduling von Tasks unter Berücksichtigung des Priority-Ceiling-Protokolls

Der Task  $w_1$  wird aktuell ausgeführt. Zum Zeitpunkt  $t_0$  wird die Ressource  $Re_1$  verwendet. Task  $w_4$  steht ab dem Zeitpunkt  $t_1$  zur Ausführung bereit. Trotz der höheren Priorität wird über das Priority-Ceiling-Protokoll dessen Ausführung erst bei  $t_2$  gestartet, nachdem Task  $w_1$  die Ressource wieder freigegeben hat (die Priorität von Task  $w_1$  wird von 20 auf 24 angehoben).

### **AUTOSAR**

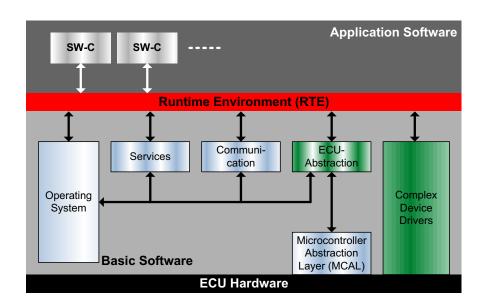

Die AUTOSAR-Initiative definiert eine Softwarearchitektur für Steuergeräte. Diese entkoppelt die Software von der Hardware eines Gerätes. Weiterhin beinhaltet die Softwarearchitektur Funktionsmodule, die sogenannten Softwarekomponenten. Diese können unabhängig voneinander und durch verschiedene Hersteller entwickelt und dann in einem weitgehend automatisierten Konfigurationsprozess zu einem konkreten Projekt zusammengebunden werden [144]. In Abbildung 3.6 ist die Softwarearchitektur von AUTOSAR mit deren wichtigsten Modulen abgebildet. Die sogenannte Basissoftware enthält die Hardware-Schnittstellen (Treiber), die Services, das Betriebssystem und die Interaktionsschicht. Das Betriebssystem *AUTOSAR-OS* ist aufwärtskompatibel zu OSEK-OS und wurde zusätzlich um Konzepte aus OSEK-TIME erweitert [16]. Über diese Schicht wird eine klare Trennung auf der Basis standardisierter Schnittstellen realisiert. Dadurch ist der Austausch oder die Ergänzung von Applikationen leicht möglich, ohne dass der komplette Software-Stack geändert werden muss.

Abb. 3.6.: AUTOSAR Software-Architektur [8]

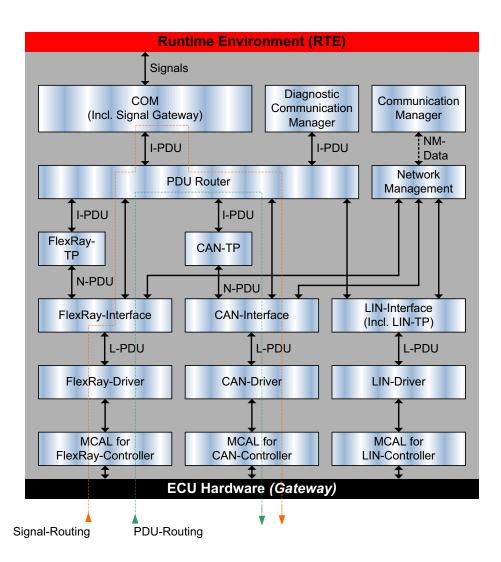

Innerhalb der Arbeit ist das Timing-Verhalten von Gateway-Steuergeräten ein wichtiger Bestandteil. Diese Komponenten sind die zentralen Elemente einer Vernetzungsarchitektur, deren Timing-Verhalten maßgeblich die Latenzzeiten der zu routenden Signale

und Botschaften beeinflusst. Aus diesem Grund werden im Folgenden die Module des AUTOSAR-Software-Stack näher beschrieben, welche für die Gateway-Funktionalität von Bedeutung sind. Abbildung 3.7 zeigt die relevanten Anteile für das Routing. Hierzu zählen die Treiber (*Drivers*), die sogenannten *Interfaces*, der *PDU-Router*, das *COM-Modul* und das Netzwerkmanagement (*Networkmanagement*). Der Treiber und das Interface kapseln die busspezifischen Eigenschaften. Im PDU-Router erfolgt das Weiterleiten von ganzen Datenpaketen, der sogenannten *PDUs* (*Protocol Data Unit*). Das COM-Modul ist für das Routing einzelner Signale zuständig. Über das Netzwerkmanagement steuert das Gateway-Steuergerät das Schlaf- und Weck-Verhalten des gesamten Netzes.

Abb. 3.7.: Detaillierte Sicht auf die einzelnen Module der AUTOSAR-Basis-Software, welche für das Routing relevant sind

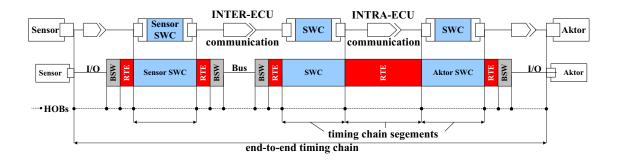

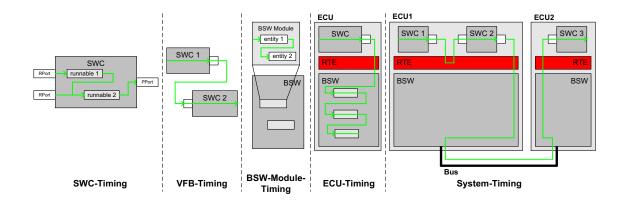

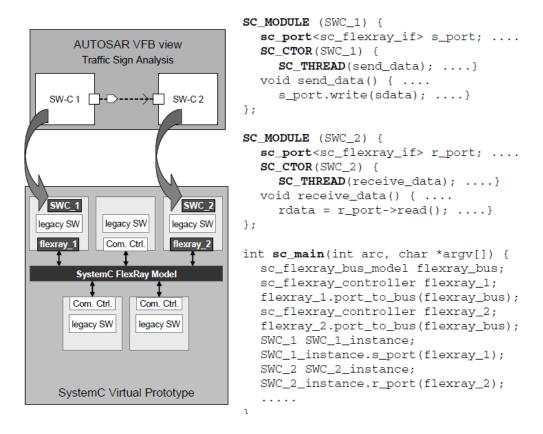

Ab der Projektphase für das AUTOSAR-Release 4 wird das Timing-Thema in einer Arbeitsgruppe bearbeitet und in einer eigenen Spezifikation *Specification of Timing-Extensions* beschrieben [15]. Der Hauptfokus richtet sich auf die Bereitstellung einer konsolidierten und konsistenten Timing-Beschreibung. Diese bietet die Möglichkeit in den verschiedenen Schritten des Entwicklungsprozesses Timing-Informationen und deren Anforderungen zu beschreiben sowie eine Bewertung auf Basis dieser Daten durchzuführen. Ein Beispiel für die Beschreibung eines Systems ist in Abbildung 3.8 dargestellt.

Abb. 3.8.: Beispiel für eine Ende-zu-Ende-Timingkette, von Abfrage des Sensors bis zur Auslösung des Aktors [15]

Über die Notationsmöglichkeiten der AUTOSAR-Timing-Spezifikation kann eine solche sogenannte Timing-Kette (*End-to-end timing-chain*) von der Abfrage eines Sensors bis zum Aktor beschrieben werden. Die Timingkette teilt sich in mehrere Untersegmente auf, die sogenannten *Timing chain segments*. Die Segmentierung ermöglicht eine Timing-Beschreibung auf verschiedenen Abstraktionsebenen. Die hierfür notwendige Deadline kann über die *AUTOSAR Timing-Extensions* beschrieben werden, ebenso die Latenzzeiten und Ausführungszeiten der einzelnen Segmente.

## 3.1.3. Kommunikationssysteme

In einer E/E-Architektur im Kraftfahrzeug kommen unterschiedliche Kommunikationssysteme zum Einsatz. Der Fokus liegt dabei auf den Kommunikationssystemen CAN und FlexRay, da diese in aktuellen und zukünftigen Vernetzungsarchitekturen die zen-

trale Rolle einnehmen. In den folgenden Abschnitten werden die für die Arbeit relevanten Aspekte erläutert. Für eine umfassende Beschreibung wird auf die wichtigsten Dokumente verwiesen.

### **Controller Area Network**

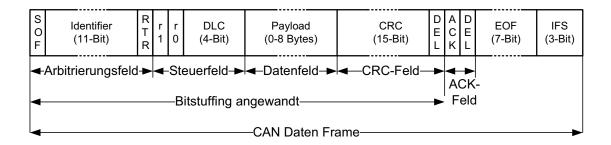

Das Controller Area Network (CAN) ist das am häufigsten eingesetzte Kommunikationssystem im Kraftfahrzeug. Der CAN-Bus wurde Anfang der 90er Jahre von der Robert Bosch GmbH entwickelt. Die Spezifikation definiert eine maximale Übertragungsgeschwindigkeit V von 1MBit/s. In aktuellen Vernetzungsarchitekturen liegt die Übertragungsgeschwindigkeit auf den CAN-Bussen zwischen 100kBit/s und 500kBit/s. Höhere Übertragungsgeschwindigkeiten als 500kBit/s führen zu teilweise starken Topologieeinschränkungen im Kraftfahrzeug. Aufgrund des steigenden Kommunikationsaufkommens werden mittlerweile mögliche Topologien mit Übertragungsraten bis zu ein 1MBit/s untersucht. Die Busarbitrierung beim CAN-BUS erfolgt mittels des CSMA/CR-Verfahrens (Carrier Sense Multiple Access/Collision Resolution). Über den Identifier wird die Nachrichtenpriorisierung geregelt, d.h. der niedrigste Wert hat die höchste Priorität. Der CAN-Bus arbeitet ereignis-getrieben, d.h. die Spezifikation sieht keine festen Sendezeitpunkte für bestimmte Botschaften vor. Es ist jedem Busteilnehmer erlaubt, zu einer beliebigen Zeit auf den Bus zuzugreifen. Pro Nachricht können maximal acht Byte Nutzdaten übertragen werden. In Abbildung 3.9 ist der Aufbau eines CAN-Datenframes dargestellt. Die Daten werden NRZ-codiert (Non-Return to Zero). Weiterhin wird für einen Teilbereich der Botschaft Bitstuffing angewandt. Dieses wird zur fortlaufenden Synchronisation der CAN-Knoten verwendet.

Abb. 3.9.: Aufbau eines Daten- oder Datenanforderungsframes im CAN-Standardformat [45]

Sowohl für die Berechnung der Buslast U als auch für die Ermittlung der Übertragungszeit einer Botschaft  $m_k$  müssen deren Stuffbits mit berücksichtigt werden. Die maximalen Stuffbits  $n_{stuff,k}$  einer Botschaft  $m_k$  berechnen sich wie folgt:

$$n_{stuff,k} = \left| \frac{34 + 8 \cdot p_k - 1}{4} \right|$$

[3.1]

Für die Berechnung der Übertragungszeit  $C_k$  einer CAN-Botschaft  $m_k$  sind alle Steuerbits (*Header und Trailer*) und deren Payload  $p_k$  (Anzahl der Nutzdatenbytes) zu berücksichtigen. Für die Berechnung der Busauslastung ist zusätzlich noch noch der *Interframe-Space*  $T_{ifs} = 3Bit$  den Steuerbits hinzuzufügen.

$$C_k = \frac{8 \cdot p_k + 44 + n_{stuff}}{B}$$

[3.2]

Da eine schon gestartete Botschaftsübertragung nicht unterbrechbar ist, kann eine weitere Botschaft  $m_k$  erst mit dem Buszugriff beginnen, wenn im schlechtesten Fall die längste niederpriore Botschaft vollständig übertragen ist. D.h. beim Sendevorgang findet eine Umkehr der Prioritäten statt. Der Sender, der den Bus belegt, hat bis zum Abschluss seiner Übertragung die höchste Priorität. Weitere wichtige Parameter des CAN-Busses, die eine Auswirkung auf das Zeitverhalten der Botschaften haben, sind:

- Die Offsets der CAN-Botschaften, oft auch als *StartDelayTime* (siehe *Specification of DBKOM-Attributes* [138]) oder *ComTxModeTimeOffsetFactor* (siehe *Specification of Communication* in AUTOSAR [10]) referenziert. Über die Offsets wird das Versenden der zyklischen Botschaften eines Steuergerätes entzerrt, so dass es zu keiner blockweisen Übertragung kommt.

- Die Sendetypen der Botschaften beschreiben, wie eine Botschaft von deren jeweiligem Sender verschickt wird. Die Sendetypen sind OEM-spezifisch. In Tabelle 3.1 sind die Sendetypen der CAN-Botschaften beschrieben, so wie diese bei der Daimler AG zum Einsatz kommen.

Tab. 3.1.: Sendetypen der CAN-Botschaften, so wie diese bei der Daimler AG zum Einsatz kommen [138]

| Sendetyp                   | Zeitliches Verhalten                                  |  |  |

|----------------------------|-------------------------------------------------------|--|--|

| zyklisch <i>cyclicX</i>    | immer aktiv mit fester Periode $T_{cycle}$            |  |  |

| spontan                    | spontanes Auftreten, relevant für die                 |  |  |

| spontanous                 | Modellierung ist der Mindestsendeabstand $T_{min}$    |  |  |

| bei aktiver Funktion (BAF) | zeitweise aktiv (wenn Funktion aktiviert)             |  |  |

| cyclicIfActive             | mit fester Periode                                    |  |  |

| zyklisch und spontan (csx) | immer aktiv mit fester Periode $T_{cycle}$ zusätzlich |  |  |

| cyclicAndSpontanWithDelay  | kann die Botschaft auch noch spontan                  |  |  |

|                            | innerhalb der Periode unter Berücksichtigung des      |  |  |

|                            | Mindestsendeabstandes $T_{min}$ verschickt werden     |  |  |

| schnell                    | immer aktiv mit zwei festen Perioden: Lang-           |  |  |

| cyclicIfActiveFast         | same Periode $T_{slow}$ bei nicht aktiver Funktion    |  |  |

|                            | und schnelle Periode $T_{fast}$ bei aktiver Funktion  |  |  |

| geändert                   | werden abhängig von der Anzahl der definierten        |  |  |

| cyclicWithRepeatOnDemand   | Wiederholungen zyklisch gesendet                      |  |  |

| Keine none                 | Kein Verhalten definiert                              |  |  |

Für weiterführende Literatur zum Thema CAN-Bus wird auf die folgende Literatur verwiesen [34], [104] und [69].

# **FlexRay**

Das Kommunikationssystem *FlexRay* wurde ab 2001 innerhalb eines Konsortiums verschiedener OEMs, Zulieferer und Halbleiterhersteller entwickelt. In den neuen Fahrzeuggenerationen ist das System mittlerweile auch im Einsatz. Auf physikalischer Ebe-

ne erlaubt FlexRay den ein- oder zweikanaligen Betrieb. Es kann eine Umsetzung in Linien- oder Sterntopologie sowie in einer Mischform erfolgen. Die maximale Übertragungsgeschwindigkeit liegt bei V = 10MBit/s.

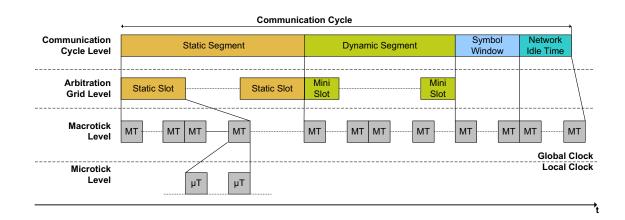

FlexRay ist wie CAN ein nachrichtenorientiertes Kommunikationssystem. Der Zugriff auf den Bus erfolgt jedoch bei FlexRay zeitgesteuert über das sogenannte *Time Division Multiple Access (TMDA)* Verfahren. Jedes Steuergerät erhält zu festgelegten Zeitpunkten den exklusiven Buszugriff. Das TDMA-Verfahren macht es notwendig, dass eine Synchronität zwischen allen Busknoten vorliegt. Hierzu sind verschiedene Verfahren zur Uhrensynchronisation (Raten- und Offsetkorrektur) notwendig. Die Zeit ist bei FlexRay auf der Basis von *Makroticks* und *Microticks* definiert. Ein Makrotick ist global für das gesamte Netz festgelegt. Die Microticks sind knotenspezifisch. Abbildung 3.10 zeigt die Timing-Ebenen von FlexRay. Oberhalb der Makrotick-Ebene befindet sich die *Arbitration Grid* Ebene, hier erfolgt die Abbildung der Makroticks auf die Slots des statischen Segmentes sowie auf die Minislots des dynamischen Segmentes. Auf der obersten Ebene ist der Kommunikationszyklus (Zyklus) definiert. Dieser beinhaltet ein statisches und optional ein dynamisches Segment für die Datenübertragung. Zusätzlich sind die *Network Idle Time* und das optionale *Symbol Window* Bestandteile eines Zyklus.

Abb. 3.10.: FlexRay-Timing-Ebenen [37]

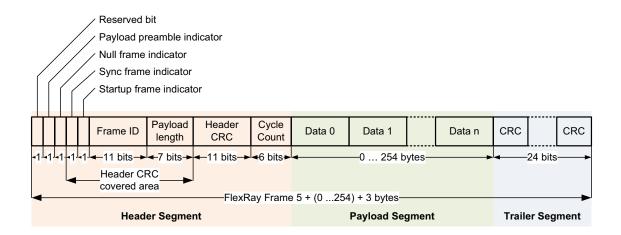

Der Aufbau eines FlexRay-Frames (Botschaft) ist in Abbildung 3.11 dargestellt. Diese besteht aus einem Header und einem Trailer sowie einem Datenfeld mit maximal 254Byte.

Abb. 3.11.: Aufbau eines FlexRay-Frames [37]

Die Übertragungszeit  $C_k$  einer Botschaft  $m_k$  hängt von der Übertragungsgeschwindigkeit V und der Länge der Botschaft ab. Im statischen Segment von FlexRay haben alle Botschaften dieselbe Länge. Die Botschafts- bzw. Framelänge aFrameLenght in Bit berechnet sich wie folgt (siehe FlexRay-Specification 3.0 auf Seite 293 [37]:

$$aFrameLength[Bit] = gdTSSTransmitter[Bit] + cdFSS[Bit] + 80Bit +$$

$$aPayloadLength[two - byteword]$$

$$\cdots 20Bit/two - byteword + cdFES[Bit]$$

[3.3]

Dabei ist *gdT SST ransmitter* die sogenannte *Transmission Start Sequence*, diese kann im Wertebereich zwischen 3...5*Bit* liegen. Der Parameter *cdFSS* steht für die Dauer der Startsequenz, diese hat die Länge von 1*Bit*. Die Endsequenz *cdFES* hat eine Länge von 2*Bit*. Da jedes übertragene Byte auf dem FlexRay 10*Bit* entspricht, kommen noch für den 8*Byte* großen Header 80*Bit* hinzu sowie die entsprechende Payload. Daraus ergibt sich für die Übertragungszeit:

$$C_k = \frac{aFrameLength}{V}$$

[3.4]

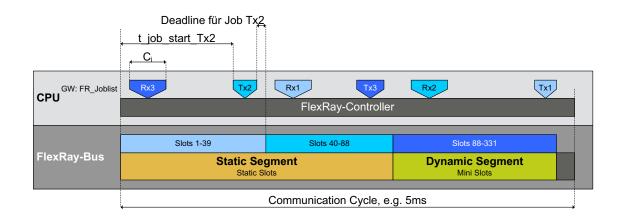

Im dynamischen Segment ergibt sich die Übertragungsdauer aus der Botschaftslänge. Die entsprechende Formel ist in der *FlexRay-Specification 3.0* auf Seite 321 zu finden [37]. Ein weiterer wichtiger Punkt bei FlexRay-Steuergeräten ist die korrekte Konfiguration der FlexRay-Jobs (siehe auch [11]). Diese sind in der Art zu definieren, dass

das Schreiben eines Frames in den *Message Ram* des FlexRay-Controllers unmittelbar vor dem nächsten Sendezeitpunkt des Frames stattfindet. Gleiches gilt für das Lesen aus dem Message Ram. Dieses Vorgehen ist notwendig, um eine optimale Übermittlung der Daten sicherzustellen und Wartezyklen zu vermeiden. In Abbildung 3.12 ist beispielhaft ein solches Zusammenspiel zwischen FlexRay-Jobs und -Schedule dargestellt. Beispielsweise bedient der FlexRay-Job Tx2 die Slots 40-88. Um die zeitlich optimale Übergabe der Daten zu gewährleisten, muss der Job vor dessen Deadline mit der Ausführung fertig sein.

Für weiterführende Literatur zum Thema FlexRay wird auf die folgenden Dokumente verwiesen [94], [37] und [38].

Abb. 3.12.: Zusammenspiel zwischen den FlexRay-Jobs im Steuergerät und dem FlexRay-Schedule

# Weitere Kommunikationssysteme

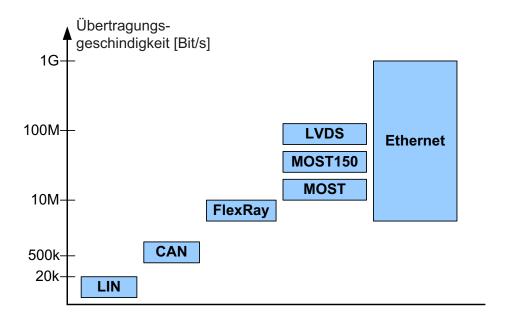

Weitere Kommunikationssysteme, welche in aktuellen Vernetzungsarchitekturen von Kraftfahrzeugen zum Einsatz kommen, sind in Abbildung 3.13 dargestellt.

• Das *Local Interconnect Network (LIN)*, ein serielles Bussystem, welches nach dem Master/Slave-Prinzip arbeitet. Die maximale Übertragungsgeschwindigkeit des LIN-Bus liegt bei 20kBit/s [71],[72].

- Der *Media Oriented System Transport (MOST)*, dieser ist für Multimedia-Anwendungen konzipiert und hat eine maximale Übertragungsgeschwindigkeit von 150MBit/s. Der MOST-Bus ist in Ringtopologie ausgeführt [82], [83].

- Das *Low Voltage Differential Signaling (LVDS)* wird zur Hochgeschwindigkeitsdatenübertragung verwendet, beispielsweise für die Übertragung von Rohdaten von Kameras.

- Das *Ethernet-IP* (*Internet Protocol*), das derzeit als schneller Flash-Zugang eingesetzt wird und bei BMW für die Anbindung des *Rear Seat Entertainments*. Aktuell wird an weiteren Einsatzmöglichkeiten geforscht (z.B. für Kameravernetzung und als Backbone-Bus) [110], [93].

Abb. 3.13.: Gegenüberstellung der Kommunikationssysteme im Kraftfahrzeug anhand deren Übertragungsgeschwindigkeiten

Die folgende Tabelle 3.2 stellt die wichtigsten Eigenschaften der einzelnen Kommunikationssysteme gegenüber.

Tab. 3.2.: Gegenüberstellung der wichtigsten Eigenschaften der Automotive-Kommunikationssysteme

| Eigenschaften             | LIN         | CAN         | FlexRay     | MOST        |

|---------------------------|-------------|-------------|-------------|-------------|

| Max. Brutto-Übertragungs- |             |             |             |             |

| geschwindigkeit [MBit/s]  | 0.02        | 1.0         | 10.0        | 150.0       |

| Max. Payload [Byte]       | 8           | 8           | 254         | 384         |

| Zugriffsverfahren         | Token       | CSMA/CR     | TDMA        | Token       |

|                           | Passing     |             |             | Passing     |

| Topologie                 | Bus         | Bus/Stern   | Bus/Stern   | Ring        |

| Synchronisation           | Master      | Keine       | Verteilte   | Master      |

|                           | Slave       |             |             | Slave       |

| Kanäle                    | 1           | 1           | 1-2         | 1           |

| Max. Knoten               | 60          | keine       | 64          | keine       |

| Physical Layer            | half duplex | half duplex | half duplex | full duplex |

# 3.2. Entwicklungsprozess für E/E-Architekturen

Durch den hohen Anteil an E/E-Systemen im Kraftfahrzeug ist die Existenz eines durchgängigen und konsistenten Entwicklungsprozesses von zentraler Bedeutung für die Qualität der Produkte. Die Entwicklung eines Kraftfahrzeugs lässt sich grob in fünf Phasen einteilen (siehe auch Abbildung 3.14):

- In der *Strategiephase* wird die Entscheidung über die Entwicklung einer neuen Baureihe getroffen. Hierfür werden Marktanalysen durchgeführt und die Eckpunkte für die grobe strategische Ausrichtung festgelegt sowie die Leitplanken (Meilensteine) für die Entwicklung vorgegeben.

- Während der Konzeptphase erfolgt die Evaluierung unterschiedlicher Alternativen einer Realisierung des Fahrzeugs. Dabei bilden die vorgegebenen Randbe-

dingungen aus der Strategiephase die Grenzen des Entwurfsraumes. Für die E/E-Architektur wird in dieser Phase ein Gesamtkonzept erarbeitet, welches die Grundlage für die nächste Entwicklungsphase bildet.

- Die Entwicklung des eigentlichen Fahrzeugs wird in der gleichnamigen *Entwicklungsphase* durchgeführt. Die einzelnen Artefakte eines Fahrzeugs werden vom Prototypenstadium bis hin zur Serienreife entwickelt.

- Die Serienphase beschreibt den Zeitraum, in dem ein Fahrzeug produziert wird. Während dieser Zeit werden meist noch kleinere Verbesserungen am Fahrzeug vorgenommen. In der Mitte der Serienphase erfolgt fast immer die sogenannte Modellpflege, welche teilweise größere Änderung am Fahrzeug zur Folge hat.

- Die *Nach Serienphase* ist der Zeitraum, in dem das Fahrzeug nicht mehr produziert wird, aber noch entsprechende Ersatzteile für die Wartungen und Reparaturen verfügbar sein müssen.

Abb. 3.14.: Phasen innerhalb des Lebenszyklus eines Automobils

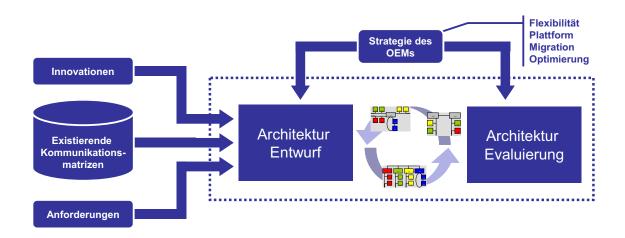

Die eigentliche Entwicklung einer E/E-Architektur beginnt in der Konzeptphase. In diesem Zeitraum werden verschiedene Architekturvarianten anhand definierter Kriterien miteinander verglichen. Der Einsatz neuer Technologien wird bewertet und die Innovationen werden integriert. In Abbildung 3.15 ist der grobe Ablauf für die Konzeptphase dargestellt. Über das sogenannte *Frontloading* wird auf der Basis existierender Architekturen ein initiales Modell erstellt. Dieses wird um die Innovationen erweitert. Der

Trend zum Frontloading hat zum Ziel, die Zahl der Änderungen innerhalb einer E/E-Architektur zu reduzieren oder zumindest in eine frühere Phase im Entwicklungsprozess zu verschieben. Frühzeitig wird versucht, Erkenntnisse über die Fahrzeugentwicklung zu gewinnen und die entworfenen Konzepte, z.B. auf digitaler Basis, abzusichern [141].

Abb. 3.15.: Vorgehensweise beim Entwurf von E/E-Architekturen während der Konzeptphase [129]

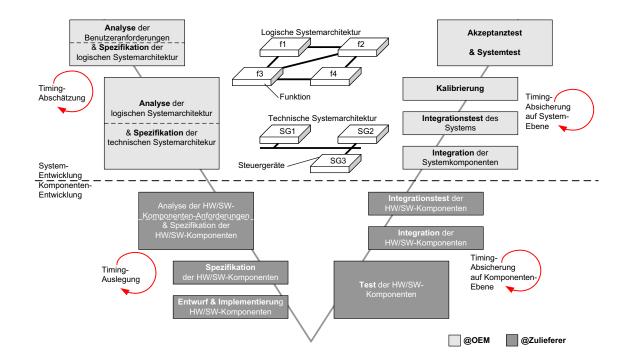

Da sich diese Arbeit auf die Bewertung von Vernetzungsarchitekturen fokussiert, wird im Folgenden auf die hierfür relevanten Prozessschritte eingegangen. Die Entwicklungsschritte der Komponenten sowie des Gesamtsystems einer Vernetzungsarchitektur orientiert sich am sogenannten *V-Modell*. In Abbildung 3.16 sind die einzelnen Schritte aufgezeigt.

Nach der Analyse der Anforderungen erfolgt die Spezifikation der logischen Systemarchitektur, d.h. in diesem Schritt wird das Funktionsnetzwerk festgelegt sowie die Schnittstellen der Funktionen und der Kommunikation zwischen den Funktionen der gesamten logischen Systemarchitektur beschrieben. Anschließend wird die logische Systemarchitektur analysiert und die Spezifikation der technischen Systemarchitektur abgeleitet. In dieser Phase des Entwicklungsprozesses sind erste Timing-Abschätzungen möglich. Nach erfolgreicher Spezifikation der technischen Systemarchitektur erfolgt die Ableitung der Spezifikation für die einzelnen Komponenten (Busse und Steuergeräte). In dieser Phase ist auch die Timing-Auslegung für die Systeme durchzuführen. Im Anschluss daran werden die Komponenten anhand der Spezifikation entworfen, implemen-

Abb. 3.16.: V-Modell für die Entwicklungsschritte von Vernetzungsarchitekturen im Kraftfahrzeug, ergänzt mit relevanten Timing-Bewertungsschritten (in Anlehnung an *Automotive Software Engineering* [111])

tiert und getestet. Im nächsten Schritt werden die einzelnen Komponenten auf Systemebene integriert und getestet. Im kompletten rechten Arm des V-Modells können in den einzelnen Schritten die Module, Komponenten und Systeme auf deren Timing-Verhalten abgesichert werden.

# 3.3. Bewertung des Stands der Technik

Durch die stetige Zunahme der E/E-Systeme im Kraftfahrzeug sind dementsprechend auch die Anforderungen an den Entwicklungsprozess gestiegen. Weiterhin sind Themen bezüglich Produkthaftung zukünftig mit zu berücksichtigen, z.B. die Norm *ISO26262*. Im aktuellen Entwicklungsprozess ist meist folgende Aufteilung anzutreffen: Der OEM entwirft das Gesamtsystem, spezifiziert die Einzelsysteme, integriert die einzelnen Komponenten und testet den Verbund [39]. Die Zulieferer übernehmen den Entwurf, die Implementierung und den Test der einzelnen Komponenten. Dabei kann der OEM auch einzelne Anteile an den Komponenten mit beisteuern, z.B. wird ein Teil der Applikationen (Software-Komponenten) vom OEM entwickelt. Durch die zunehmende Vernetzung

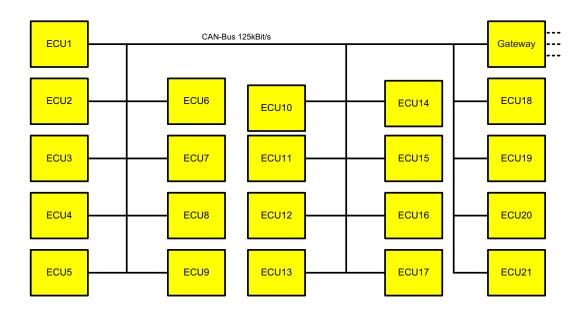

von Funktionen sowie aufgrund der immer höheren Auslastung der Systeme reichen die bisher eingesetzten Verfahren für eine vollständige Absicherung des Timing-Verhaltens nicht aus. Abbildung 3.17 zeigt ein typisches Beispiel für ein verteiltes System.

Abb. 3.17.: Beispiel für einen typischen Ende-zu-Ende-Pfad vom Sensor bis zum Aktor

Um einen solchen Ende-zu-Ende Pfad bewerten und absichern zu können, ist das Timing-Verhalten der beteiligten Komponenten im Detail zu berücksichtigen. Insbesondere für die Evaluierung der Kommunikationssysteme wurden bisher rein kapazitive Untersuchungsmethoden verwendet. Um hier zukünftig eine detaillierter Aussage treffen zu können, wird in dieser Arbeit eine durchgängige Methodik für die Timing-Bewertung aufgezeigt. In diesem Zusammenhang sind folgende Fragestellungen von Bedeutung:

- 1. Wie kann das Timing-Verhalten von Software- und Hardware Systemen und deren Subsysteme im Kraftfahrzeug gezielt vorhergesagt und abgesichert werden?

- 2. Welche Daten sind für eine aussagekräftige Timing-Bewertung notwendig und stehen zu welchem Entwicklungszeitpunkt zur Verfügung?

- 3. Inwieweit sind Timing-Aussagen in der frühen Entwurfsphase möglich?

- 4. Wie ist eine exakte Abbildung des Timing-Verhaltens in den entsprechenden Bewertungsverfahren umzusetzen?

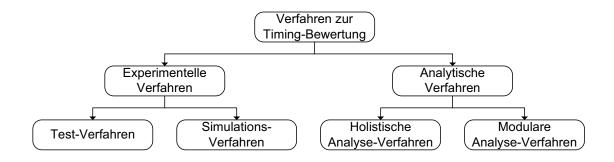

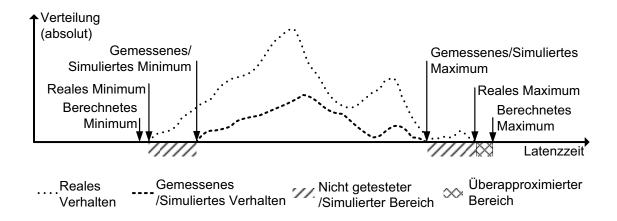

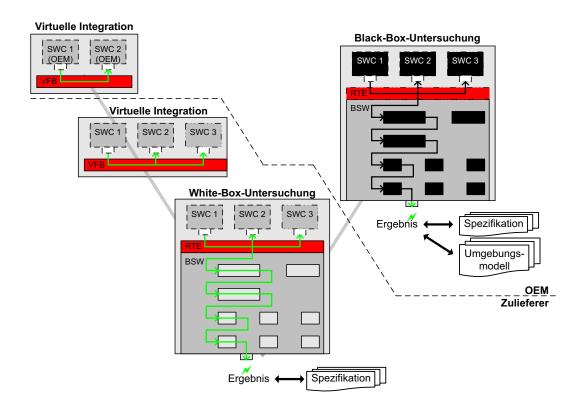

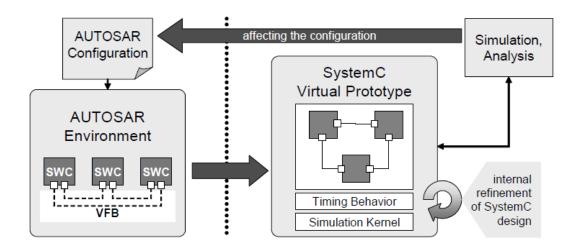

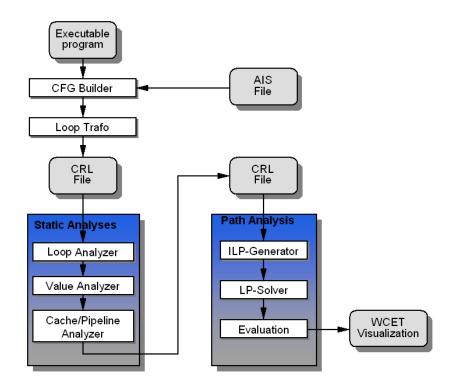

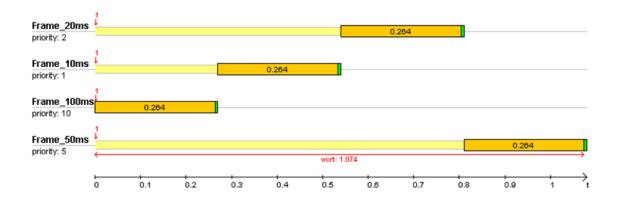

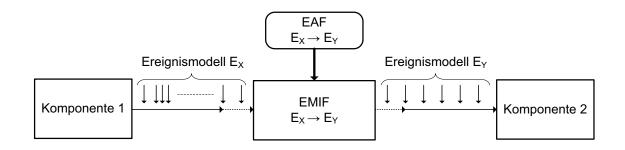

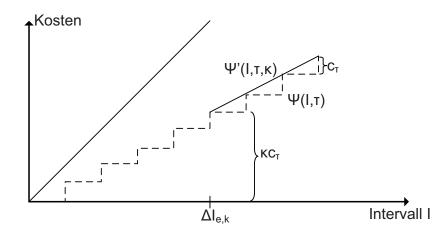

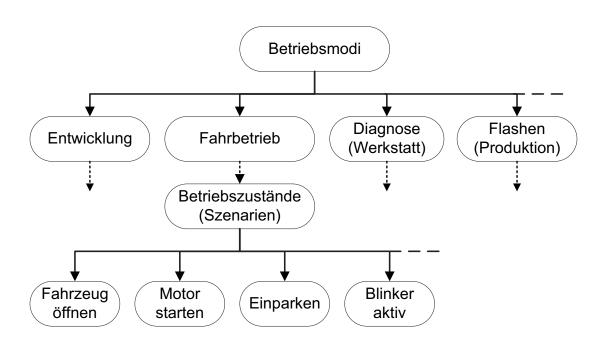

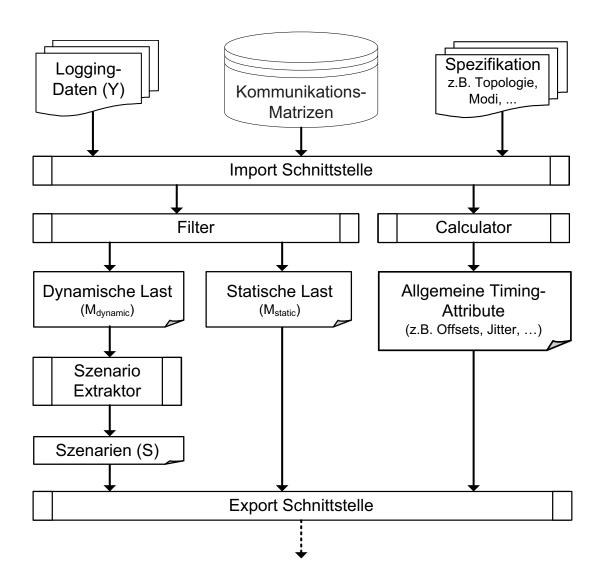

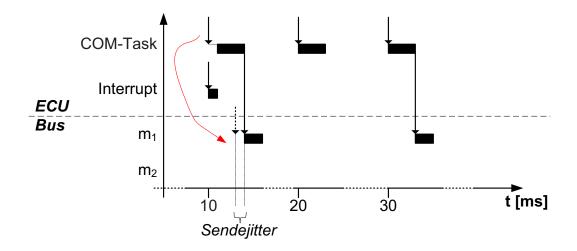

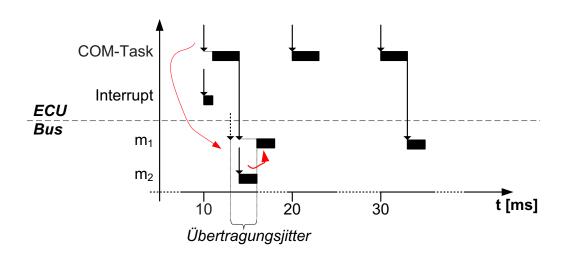

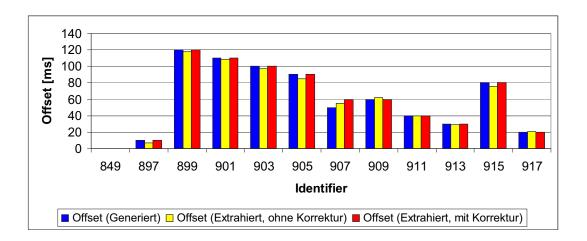

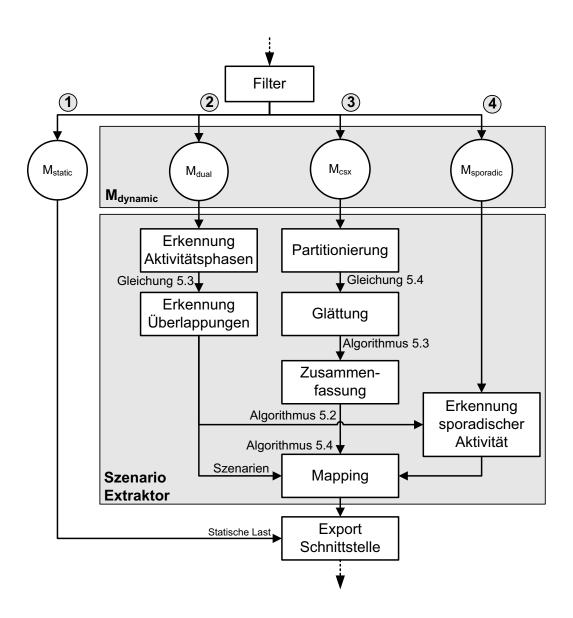

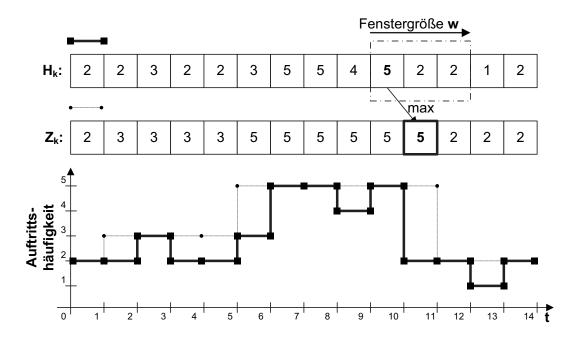

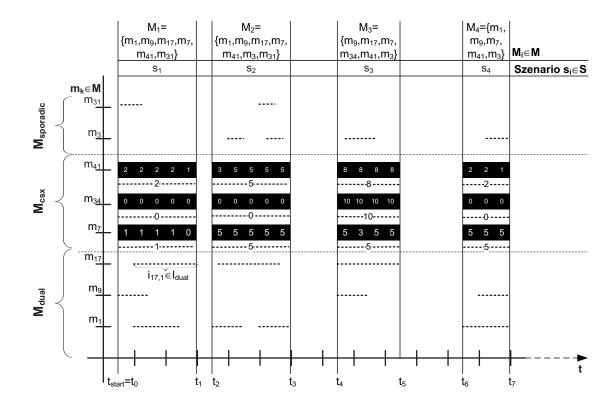

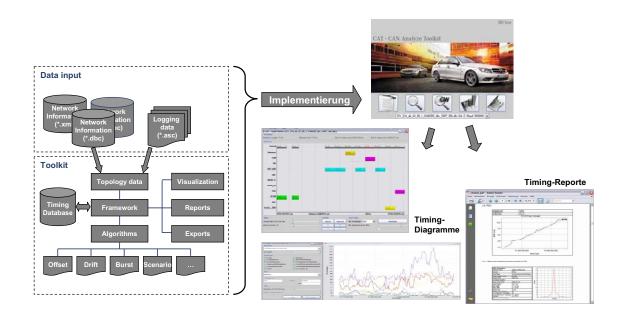

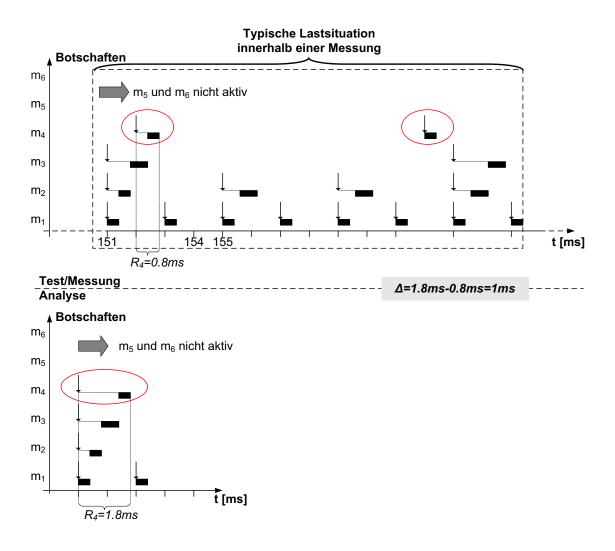

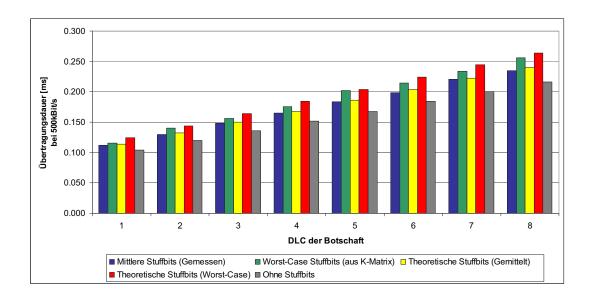

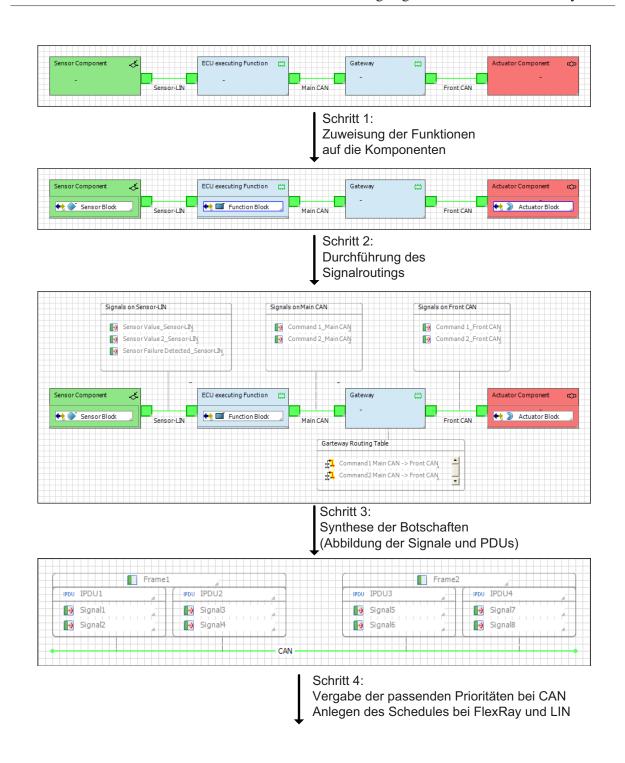

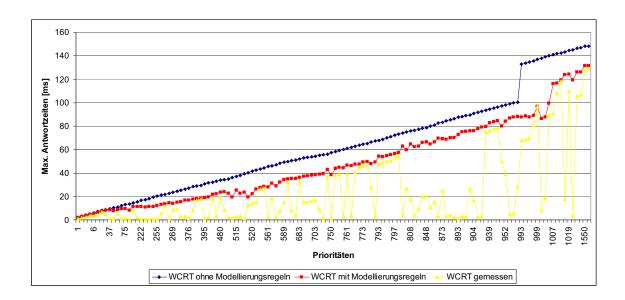

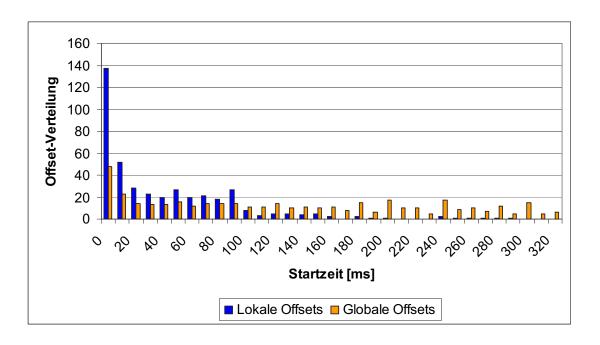

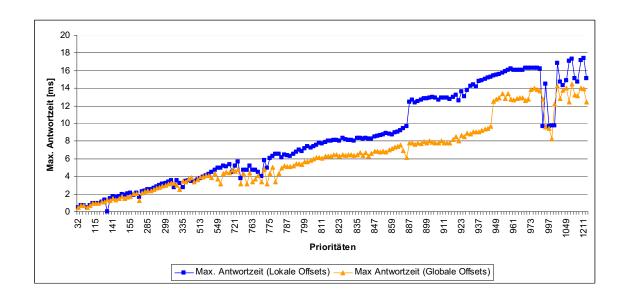

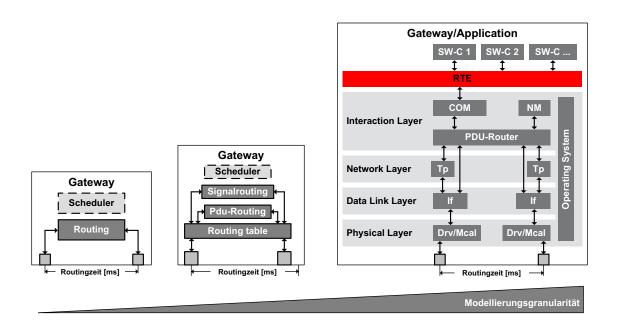

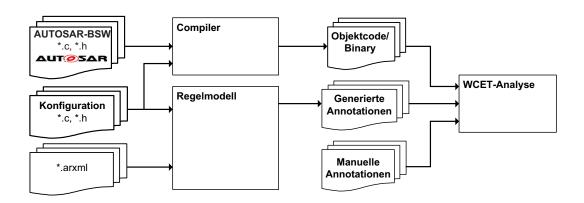

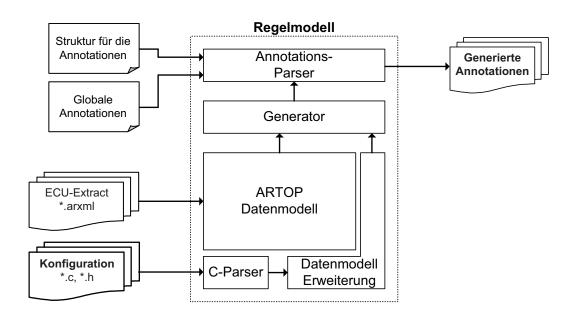

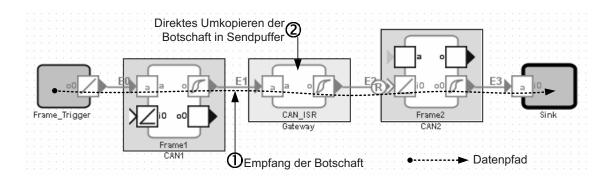

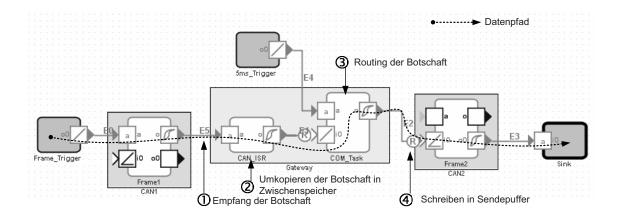

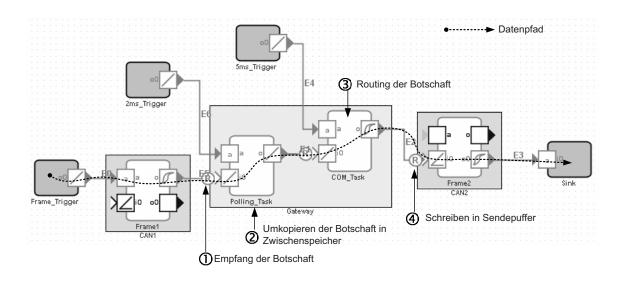

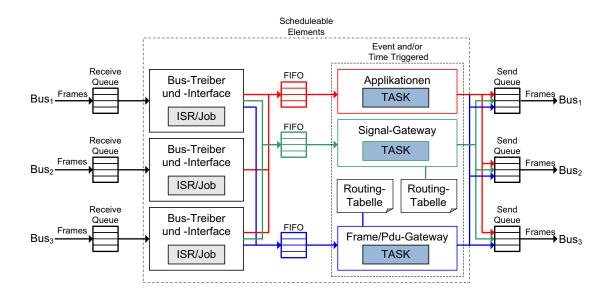

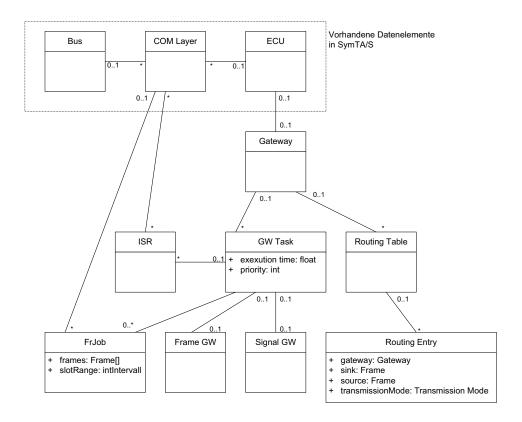

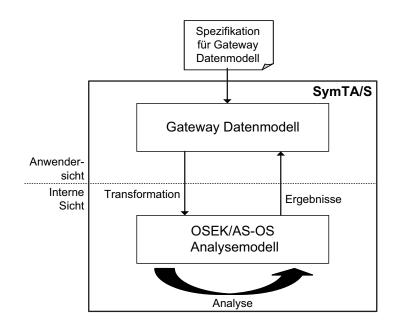

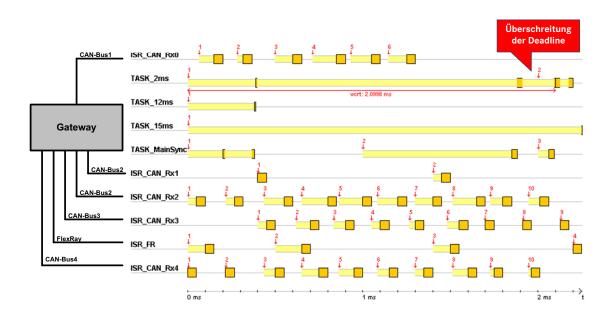

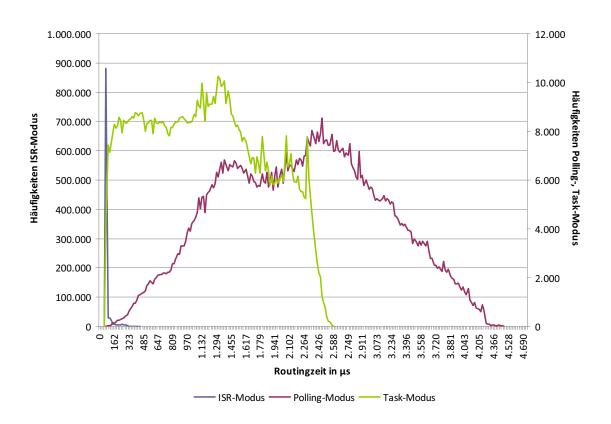

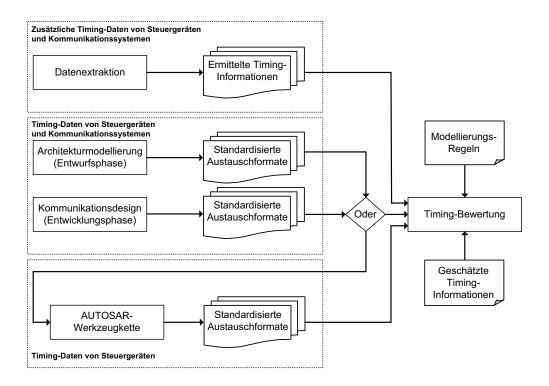

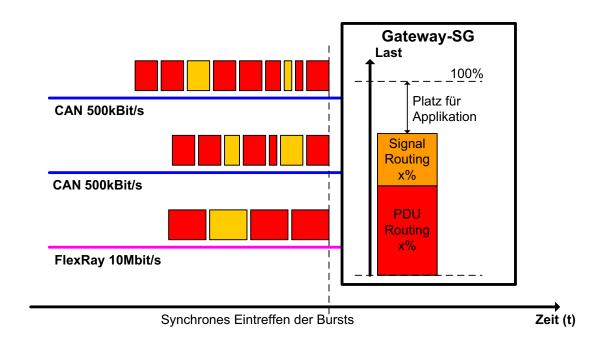

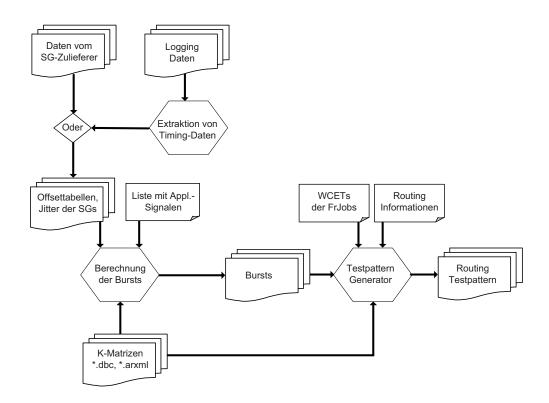

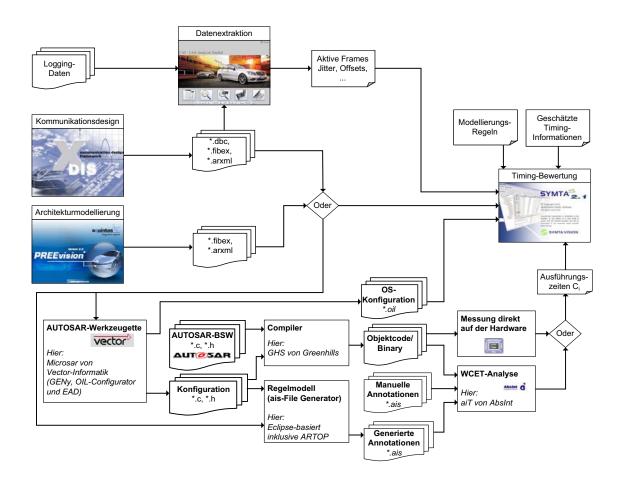

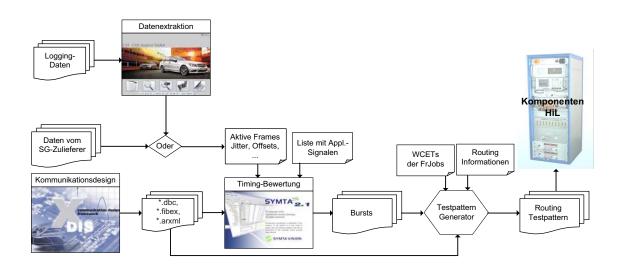

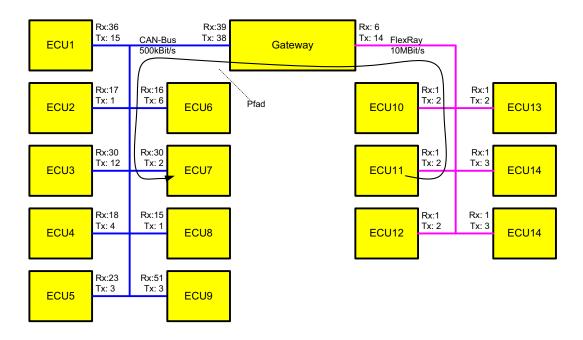

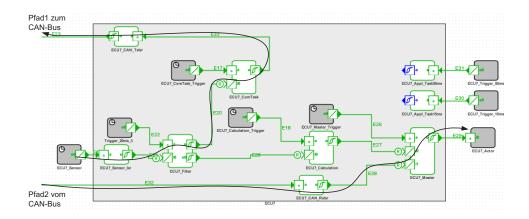

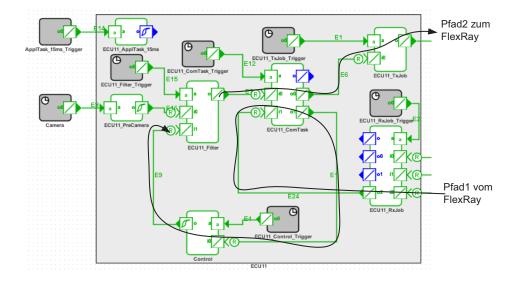

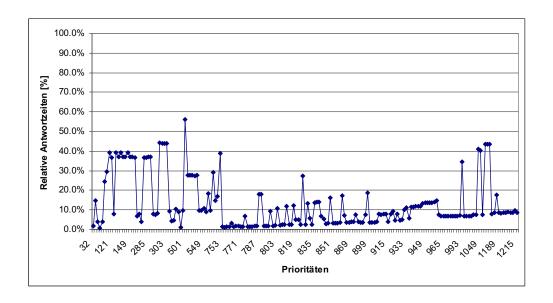

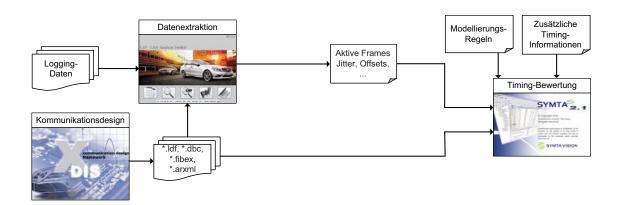

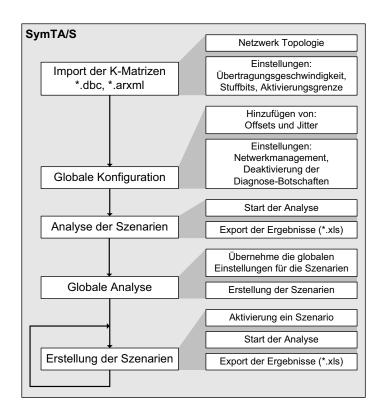

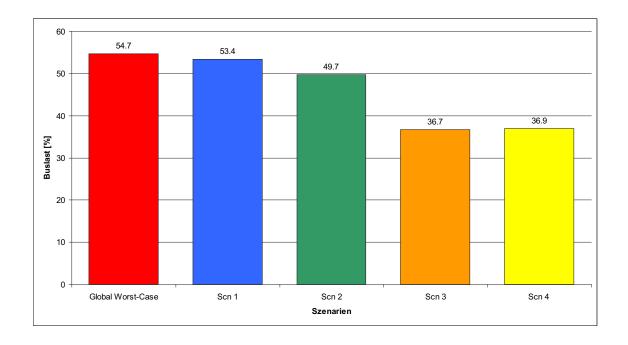

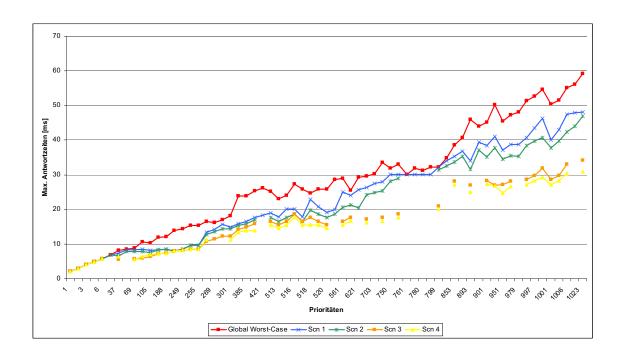

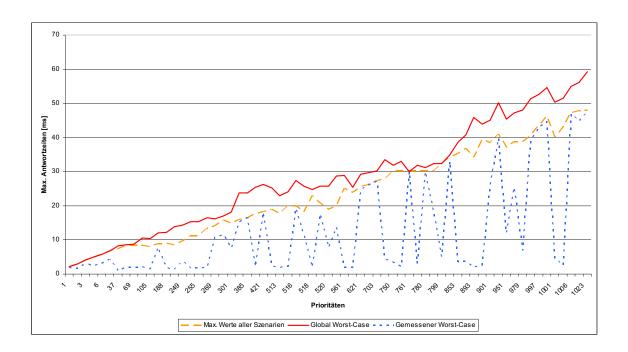

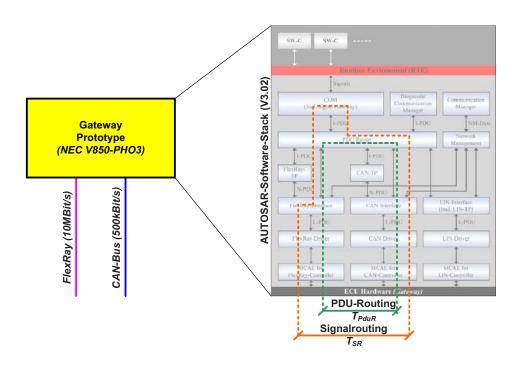

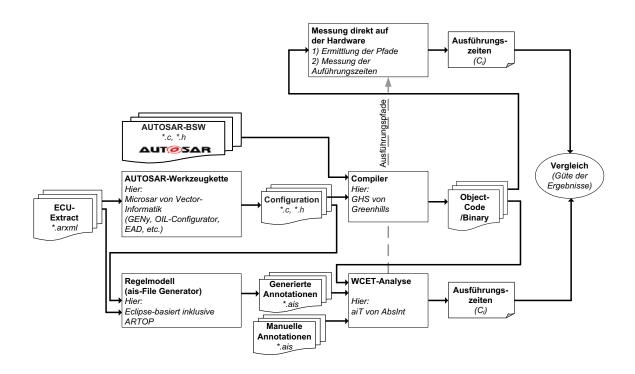

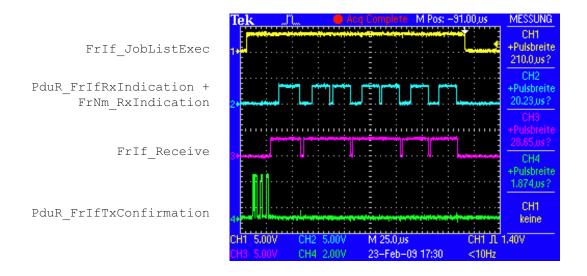

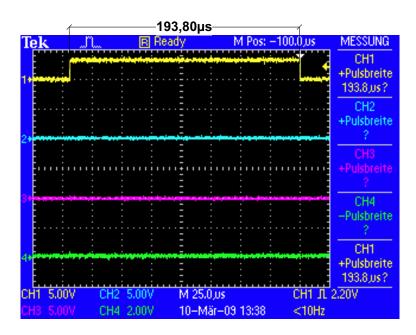

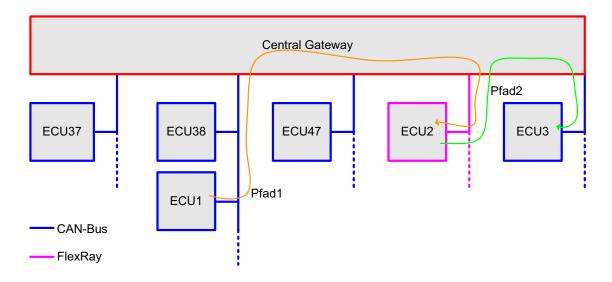

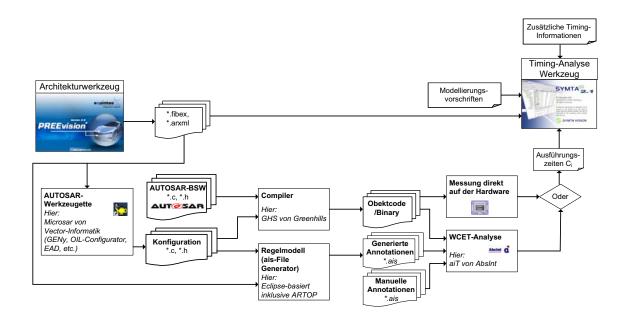

5. Wie lassen sich die Timing-Bewertungsverfahren optimal in den existierenden E/E-Entwicklungsprozess integrieren?