## **RISPP: A Run-time Adaptive Reconfigurable Embedded Processor**

zur Erlangung des akademischen Grades eines

### Doktors der Ingenieurwissenschaften

der Fakultät für Informatik der Universität Fridericiana zu Karlsruhe (TH)

#### genehmigte

### **Dissertation**

von

### Lars Bauer

Tag der mündlichen Prüfung: 15. Dezember 2009

Referent: Prof. Dr.-Ing. Jörg Henkel, Universität Karlsruhe (TH), Fakultät für Informatik, Lehrstuhl für Eingebettete Systeme (CES)

Korreferent: Prof. Dr.-Ing. Jürgen Becker, Universität Karlsruhe (TH), Fakultät für Elektrotechnik und Informationstechnik, Institut für Technik der Informationsverarbeitung (ITIV)

Lars Bauer Adlerstr. 3a 76133 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

## Acknowledgements

I want to thank my advisor Prof. Jörg Henkel for the inspirations, discussions, and opportunities he provided and shared with me. He managed to guide and to challenge me while giving me all freedom to follow my ideas and interests. Working with him was a nice experience and it definitely had a strong influence on my independent approach to work.

I also want to thank all colleagues from the Chair for Embedded Systems for the nice discussions and the good time. In the last two month before submitting my thesis, especially Thomas Ebi and Sebastian Kobbe provided consistent support by helping me managing the daily workload and by sharing their coffee machines, which I cannot appreciate enough. Additionally, it is especially due to the secretaries and technicians that we can research in a good working environment and I explicitly want to acknowledge their work during all the time.

Special thanks go to my colleague and room mate Muhammad Shafique. Without him, the work would not have been what it became. The technical discussions on application- and architecture-aspects improved the quality of this work more than once. I also want to thank the Master students that I supervised in the scope of this thesis.

It was a nice experience to collaborate with colleagues from the groups (in alphabetical order) of Prof. Jürgen Becker (ITIV), Prof. Jörg Henkel (CES), and Prof. Wolfgang Karl (CA) from the University of Karlsruhe in different projects. In particular, I want to thank (in alphabetical order): Waheed Ahmed<sup>CES</sup>, Mohammad Abdullah Al Faruque<sup>CES</sup>, Talal Bonny<sup>CES</sup>, Rainer Buchty<sup>CA</sup>, Thomas Ebi<sup>CES</sup>, Dominic Hillenbrand<sup>CES</sup>, Michael Hübner<sup>ITIV</sup>, Florian Kaiser<sup>CES</sup>, Ralf König<sup>ITIV</sup>, David Kramer<sup>CA</sup>, Christian Schuck<sup>ITIV</sup>, Muhammad Shafique<sup>CES</sup>, and Timo Stripf<sup>TTV</sup>.

I had the honor to participate at the (semi-) annual colloquia of the priority programs from the German Research Foundation (DFG) about Reconfigurable Computing Systems (SPP-1148) and Organic Computing (SPP-1183). The presentations and the discussion with colleagues from other Universities broadened my horizon and created contact with many excellent researchers. I want to thank the coordinators of these priority programs for this great experience (in alphabetical order): Prof. Hartmut Schmeck and Prof. Jürgen Teich.

The hardware prototype and simulation environment would not have been possible without support of various different companies, i.e. (in alphabetical order) ACE by, Agilent GmbH, Avnet Inc., Digilent Inc., Samsung, and Xilinx Inc. I especially want to thank Parimal Patel from Xilinx for his consistent support and his hints according the Early Access Partial Reconfiguration tools.

Finally, I want to thank my family and in particular my parents Heidrun and Dieter. They all supported me whenever I needed it. Not only during my Ph.D. study but actually since ever. This strong foundation certainly helped looking forward.

"In a nutshell, ingenuity combined with very hard work is the key. Never lean back. Always look forward. Identify and face new challenges. Be very self-critical. And honest." Jörg Henkel

Email conversation after DAC'08 acceptance notification, 8<sup>th</sup> February 2008

## List of Own Publications Included in This Thesis

#### **Transactions (blind peer reviewed)**

[T.1] L. Bauer, M. Shafique, J. Henkel, "Efficient Resource Utilization for an Extensible Processor through Dynamic Instruction Set Adaptation", IEEE Transaction on Very Large Scale Integration (TVLSI'08), Special Section on Application-Specific Processors, Volume 16, Issue 10, pp. 1295-1308, October 2008.

#### **Conferences (double-blind peer reviewed)**

- [C.1] L. Bauer, M. Shafique, J. Henkel, "MinDeg: A Performance-guided Replacement Policy for Runtime Reconfigurable Accelerators", IEEE International Conference on Hardware-Software Codesign and System Synthesis (CODES+ISSS'09), Grenoble, France, pp. 335-342, October 2009.

- [C.2] L. Bauer, M. Shafique, J. Henkel, "Cross-Architectural Design Space Exploration Tool for Reconfigurable Processors", IEEE/ACM 12<sup>th</sup> Design Automation and Test in Europe Conference (DATE'09), Nice, France, pp. 958-963, April 2009.

- [C.3] L. Bauer, M. Shafique, J. Henkel, "A Computation- and Communication-Infrastructure for Modular Special Instructions in a Dynamically Reconfigurable Processor", IEEE 18th International Conference on Field Programmable Logic and Applications (FPL'08), Heidelberg, Germany, pp. 203-208, September 2008.

- [C.4] L. Bauer, M. Shafique, J. Henkel, "Run-time Instruction Set Selection in a Transmutable Embedded Processor", ACM/IEEE/EDA 45th Design Automation Conference (DAC'08), Anaheim, CA, USA, pp. 56-61, June 2008.

Received a "European Network of Excellence on High Performance and Embedded Architecture and Compilation" (HiPEAC) Paper Award

- [C.5] L. Bauer, M. Shafique, S. Kreutz, J. Henkel, "Run-time System for an Extensible Embedded Processor with Dynamic Instruction Set", IEEE/ACM 11<sup>th</sup> Design Automation and Test in Europe Conference (DATE'08), Munich, Germany, pp. 752-757, March 2008.

Received the DATE'08 Best Paper Award for Track D (Design Methods, Tools, Algorithms and Languages)

- [C.6] L. Bauer, M. Shafique, D. Teufel, J. Henkel, "A Self-Adaptive Extensible Embedded Processor", IEEE/ACM First International Conference on Self-Adaptive and Self-Organizing Systems (SASO'07), Boston, MA, USA, pp. 344-347, July 2007.

- [C.7] L. Bauer, M. Shafique, S. Kramer, J. Henkel, "RISPP: Rotating Instruction Set Processing Platform", ACM/IEEE/EDA 44<sup>th</sup> Design Automation Conference (DAC'07), San Diego, CA, USA, pp. 791-796, June 2007.

### Workshops (double-blind peer reviewed)

[W.1] L. Bauer, M. Shafique, J. Henkel, "Efficient Resource Utilization for an Extensible Processor through Dynamic Instruction Set Adaptation", 5<sup>th</sup> Workshop on Application Specific Processors (WASP'07), Salzburg, Austria, pp. 39-46, October 2007.

## List of Supervised Student Projects that Contributed to the Simulation and Prototype

#### **Master Thesis (Diplomarbeiten)**

- [D.1] Frank Birkle "Designing and prototyping a partially reconfigurable processor framework with a HW/SW Co-Designed run-time system", August 2009.

- [D.2] Roman Sinawski "Design and implementation of an extensible ASIP for an H.264 Video Encoder", August 2009.

- [D.3] Artjom Grudnitsky "Extending the RISPP Simulator with Floorplan-Aware Special Instruction Management and Execution", May 2009.

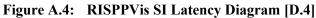

- [D.4] Patrick Koffler "Visualisierung ereignisbasierter interner Abläufe in rekonfigurierbaren Prozessoren", May 2009.

- [D.5] Hongzhang Chen "Extending an application specific processor towards dynamic partial reconfiguration", December 2008.

- [D.6] Weiwei Cheng "Simulation und Messung des Energieverbrauchs eines Rekonfigurierbaren Eingebetteten Prozessors", October 2008.

- [D.7] Christian Krämer "Design and Implementation of a Reconfigurable Processor with Adaptive Reconfiguration Management", September 2007.

- [D.8] Stephanie Kreutz "Konzeption und Evaluierung einer Methodik zur Rekonfigurationsentscheidung eines dynamischen ASIPs", August 2007.

- [D.9] Simon Kramer "Graphenanalyse zur Bestimmung von Vorhersagepunkten für Spezialbefehle", January 2007.

- [D.10] Francois Blassmann "Implementierung eines Prototypen zur partiellen Laufzeitrekonfiguration", May 2006.

- [D.11] Dirk Teufel "Entwicklung eines Rekonfigurationsmanagers für einen Applikationsspezifischen Prozessor", May 2006.

### Semester Thesis (Studienarbeiten)

- [S.1] Jan Micha Borrmann "Entwicklung eines IP-Cores zur Erfassung und Vorverarbeitung von Videodaten auf einem FPGA", May 2009.

- [S.2] Ekrem Karaman "Untersuchung verschiedener Implementierungen von Spezialbefehlen für dynamisch rekonfigurierbare Prozessoren", July 2008.

- [S.3] Artjom Grudnitsky "Designing a customizable framework with exchangeable modules for partially reconfigurable hardware", May 2008.

- [S.4] Roland Sedler "A simulation environment for reconfigurable processor architectures", April 2008.

- [S.5] Christoph Brückner "Evaluierung von Debuggingwerkzeugen für Xilinx FPGAs", September 2007.

- [S.6] Andreas Becker "Messen des Leistungsverbrauches beim partiellen Rekonfigurieren eines FPGAs", June 2007.

- [S.7] Christian Krämer "Implementierung einer I2C Schnittstelle für ein FPGA Prototyping Board und Anbindung eines Touch Screen LCDs zur Steuerung von ASIPs", February 2007.

- [S.8] Florian Fetz "Entwicklung eines Designs zur partiellen Selbstrekonfiguration mit PlanAhead", December 2006.

## Abstract

Reconfigurable embedded processors are a special class of processors comprising an extended instruction set that is implemented using a reconfigurable fabric. The instruction-set extension is typically application specific, but it is not required to finalize it when designing the processor. The reconfigurable fabric (e.g. a field-programmable gate array (FPGA)) allows that the accelerators that are used to implement the instruction-set extension may be reconfigured during run time without affecting the functionality of the working processor. Therefore, the accelerators – and thus the instruction-set extension – may be adapted according to the requirements of a running application.

State-of-the-art reconfigurable processors require that the application programmer (or compiler) determines during compile time 'which' reconfigurations shall be performed and 'when' they shall be performed, i.e. which accelerators shall be loaded to a particular part of the reconfigurable fabric at a certain time. The problem is that it is typically not known during compile time which applications execute at the same time (i.e. in a multi-tasking environment), demanding the reconfigurable fabric. Additionally, it is not necessarily known, which accelerators are demanded frequently and which are demanded rather seldom, because this may depend on the input data for the application. Here, it would be desirable that this information – that is only available during run time – would be used to determine which reconfigurations should be performed. A further problem is the reconfiguration time, that ranges in the area of milliseconds for FPGAs (1 ms = 100,000 cycles of a 100 MHz CPU). The reconfiguration time of an accelerator grows approximately linear with the share of the reconfigurable fabric that needs to be reconfigured. This means, that an accelerator that exploits more parallelism (and thus demands a larger area) requires a longer reconfiguration time. Therefore, it becomes usable at a later time (in comparison with a smaller accelerator), which implies that some potential performance improvement is lost due to longer reconfiguration time.

In this thesis, concepts, strategies, and implementations are presented to solve the discussed problems of long reconfiguration times and missing run-time adaptivity. As foundation, a novel hierarchical composition of instruction set extensions was developed that allows to provide the instruction set extensions in multiple versions. These versions differ according their parallelism and reconfiguration time and allow switching from one version to another efficiently. 'Efficiently' means that it is not required to reconfigure a new version (e.g. exploiting more parallelism) from scratch. Instead, it may build on top of an existing version (typically exploiting less parallelism). This makes it possible to replace an existing instruction set extension by a faster one by reconfiguring the additionally required accelerators. This means, a stepwise upgrade of the instruction set extension becomes now possible. This addresses the effect of long reconfiguration time and it allows choosing different implementations of the instruction set extension at different points in time, depending on execution frequency of the instruction set extension set extensions and depending on the available amount of reconfigurable fabric. In comparison with state-of-the art instruction set extension, the application does not need to be changed to benefit from this novel concept, just the performance of the instruction set extension changes over time.

To exploit the provided run-time flexibility, multiple algorithms were developed and implemented to solve the following problems during run time:

- Application requirement analysis (using online monitoring) and prediction of the required instruction set extensions (i.e. which extension is required how often) to start the corresponding reconfigurations in time.

- Selecting the specific version of the instruction set extension for a given size of the reconfigurable fabric (similar to a knapsack problem).

- Scheduling the demanded reconfigurations (this is required because at most one reconfiguration can be performed at a time).

- Replacing currently available accelerators to be able to reconfigure further accelerators.

The resulting system was implemented and evaluated using a simulation and an FPGA prototype. Additionally, it was compared with state-of-the-art processors with a reconfigurable / and a non-reconfigurable instruction set (so-called application-specific instruction set processors). Due to the run-time adaptivity, the concept of upgrading instruction set extensions, and the reduced reconfiguration overhead problem, significant performance improvements were observed for a complex H.264 video encoder application:

- up to 2.38x in comparison with the reconfigurable Molen processor,

- up to 7.19x in comparison with the reconfigurable Proteus processor,

- up to 3.06x in comparison with a non-reconfigurable application-specific processor, and

- up to 25.7x in comparison with a non-reconfigurable general-purpose processor without instruction set extension.

## Zusammenfassung

Rekonfigurierbare Eingebettete Prozessoren sind eine spezielle Klasse von Prozessoren, die über eine Befehlssatzerweiterung verfügen, welche durch rekonfigurierbare Hardware realisiert wird. Die Befehlssatzerweiterung ist häufig anwendungsspezifisch, muss aber nicht zur Entwurfszeit des Prozessors festgelegt werden. Die rekonfigurierbare Hardware (z.B. ein feldprogrammierbares Gatterarray (FPGA)) erlaubt es, die Beschleunigerschaltkreise, die die Befehlssatzerweiterung implementieren, zur Laufzeit des Systems auszutauschen, ohne dabei die übrige Funktionalität des arbeitenden Prozessors zu beeinträchtigen. Dadurch können die Beschleunigerschaltkreise – und somit die Befehlssatzerweiterung – abhängig von den Bedürfnissen einer laufenden Anwendungen angepasst werden.

Dem Stand der Kunst entsprechende rekonfigurierbare Prozessoren erwarten vom Anwendungsprogrammierer (bzw. vom Übersetzer), das er zur Übersetzungszeit der Anwendung festlegt, welche Rekonfigurationen wann ausgeführt werden sollen, sprich: welche Beschleunigerschaltkreise zu welchem Zeitpunkt an welche Stelle der rekonfigurierbaren Hardware geladen werden sollen. Das Problem daran ist, dass zur Übersetzungszeit typischerweise nicht bekannt ist, welche Anwendungen gleichzeitig (d.h. im Zeitscheibenverfahren eines Multi-Tasking Systems) laufen und die rekonfigurierbare Hardware beanspruchen. Außerdem ist nicht immer zur Übersetzungszeit bekannt, welche Beschleunigerschaltkreise besonders häufig und welche eher selten benötigt werden, weil das von Eingabedaten der Anwendung abhängen kann. Hier wäre es wünschenswert, wenn diese Informationen - die erst zur Laufzeit der Anwendung bekannt sind – benutzt würden, um zu entscheiden welche Rekonfigurationen durchgeführt werden sollen. Ein weiteres Problem ist die Rekonfigurationszeit, die sich bei FPGAs im Bereich mehrerer Millisekunden bewegt (1 ms = 100.000 Takte einer 100 MHz CPU). Die Rekonfigurationszeit eines Beschleunigerschaltkreises wächst annäherungsweise linear mit der Fläche, die auf dem FPGA rekonfiguriert werden soll. Das bedeutet, dass ein Beschleuniger der mehr Parallelität ausnutzt (und damit eine größere Fläche belegt) eine längere Rekonfigurationszeit hat. Dadurch wird er erst später verfügbar, was dazu führt, dass ein Teil der erwarteten Beschleunigung (Ausnutzung von mehr Parallelität) durch die längere Rekonfigurationszeit verloren geht.

In der vorliegenden Arbeit werden Konzepte, Strategien und Implementierungen vorgestellt, um die beschriebenen Probleme der langen Rekonfigurationszeit und der fehlenden Laufzeitadaptivität zu lösen. Als Grundlage wurde eine neuartige hierarchische Komposition von Befehlssatzerweiterungen entworfen, die es ermöglicht, die Befehlssatzerweiterung in mehreren Versionen anzubieten. Diese Versionen unterscheiden sich bezüglich ihrer Parallelität und Rekonfigurationszeit und erlauben es, effizient von einer Version zu einer anderen zu wechseln. Effizient bedeutet hier, dass eine Version die z.B. mehr Parallelität nutzt nicht komplett neu rekonfiguriert werden muss, sondern auf einer vorhandenen Version (die dann typischerweise weniger Parallelität nutzt) aufbauen kann. Dadurch ist es möglich, eine vorhandene Befehlssatzerweiterung durch eine schnellere zu ersetzt, wobei nur die zusätzlich benötigten Teile der Beschleuniger rekonfiguriert werden müssen, sprich: ein schrittweises Aufrüsten der Befehlssatzerweiterung wird möglich. Dadurch wird der Effekt der langen Rekonfigurationszeit angegangen und es ist außerdem möglich, zur Laufzeit zu verschiedenen Zeitpunkten verschiedene Implementierungen der Befehlssatzerweiterung auszuwählen, abhängig davon, welche Erweiterung wie häufig benötigt wird und wie viel Hardware dafür verfügbar ist. Die Anwendung selbst muss dafür nicht angepasst werden, nur die Ausführungsgeschwindigkeit der Befehlssatzerweiterung ändert sich.

Zum Erreichen der Laufzeitadaptivität wurden mehrere Algorithmen entworfen und implementiert, welche die folgenden Problemstellungen zur Laufzeit lösen:

- Bedarfsanalyse der Anwendung und Vorhersage der benötigten Befehlssatzerweiterung (welcher Beschleunigerschaltkreis wird wie häufig gebraucht), um frühzeitig mit der Rekonfiguration beginnen zu können.

- Auswahl von konkreten Versionen der Befehlssatzerweiterungen für eine gegebene Hardwarefläche (ähnlich dem Rucksackproblem).

- Zeitliche Ablaufplanung der notwendigen Rekonfigurationen (notwendig, da immer nur eine Rekonfiguration gleichzeitig durchgeführt werden kann, die anstehenden Rekonfigurationen also in eine Reihenfolge gebracht werden müssen).

- Verdrängung existierender Beschleunigerschaltkreise, um neue zu laden.

Das resultierende Gesamtsystem wurde in einem Simulator und einem FPGA Prototypen implementiert und evaluiert. Außerdem wurde es mit dem Stand der Kunst entsprechenden Prozessoren mit rekonfigurierbarer Befehlssatzerweiterung, wie auch mit nicht rekonfigurierbarer Befehlssatzerweiterung (sog. anwendungsspezifische Prozessoren) verglichen. Durch die Laufzeitadaptivität und die Aufrüstbarkeit der Befehlssatzerweiterung (und die damit einhergehende Verringerung der Rekonfigurationswartezeit) wurden für eine komplexe H.264 Video Encoder Anwendung deutliche Performanzgewinne beobachtet:

- bis zu 2,38x im Vergleich zum rekonfigurierbaren Molen Prozessor,

- bis zu 7,19x im Vergleich zum rekonfigurierbaren Proteus Prozessor,

- bis zu 3,06x im Vergleich zu nicht rekonfigurierbaren anwendungsspezifischen Prozessoren und

- bis zu 25,7x im Vergleich zu nicht rekonfigurierbaren Standardprozessoren ohne Befehlssatzerweiterung.

# Contents

| Acknow  | vledgements                                                      | i     |

|---------|------------------------------------------------------------------|-------|

| List of | Own Publications Included in This Thesis                         | V     |

| List of | Supervised Student Projects that Contributed to the Simulation a |       |

|         | Prototype                                                        | vii   |

| Abstr   | a c t                                                            | ix    |

| Zusam   | menfassung                                                       | xi    |

| Conte   | nts                                                              | xiii  |

| List of | Figures                                                          | xvii  |

| List of | Tables                                                           | xxiii |

| List of | Algorithms                                                       | XXV   |

| Abbrev  | viations                                                         | xxvii |

| Chapte  | r 1 Introduction                                                 | 1     |

| 1.1     |                                                                  |       |

| 1.2     | Reconfigurable Processors                                        | 2     |

| 1.3     | Thesis Contribution                                              | 3     |

| 1.4     | Thesis Outline                                                   | 5     |

| Chapte  | r 2 Background and Related Work                                  | 7     |

| 2.1     | Extensible Processors                                            |       |

| 2.2     |                                                                  |       |

|         | 2.2.1 Granularity of the Reconfigurable Fabric                   | 8     |

|         | 2.2.2 Using and Partitioning the Reconfigurable Area             |       |

|         | 2.2.3 Coupling Accelerators and the Processor                    |       |

|         | 2.2.4 Reconfigurable Instruction Set Processors                  |       |

| 2.3     | Summary of Related Work                                          |       |

| Chapte  | r 3 Modular Special Instructions                                 | 21    |

| 3.1     | Problems of State-of-the-art Monolithic Special Instructions     |       |

| 3.2     | Hierarchical Special Instruction Composition                     |       |

| 3.3     | Example Special Instructions for the ITU-T H.264 Video Encoder   |       |

|         | Application                                                      | 31    |

| 3.4    | Formal Representation and Combination of Modular Special           |    |

|--------|--------------------------------------------------------------------|----|

|        | Instructions                                                       | 36 |

| 3.5    | Summary of Modular Special Instructions                            | 39 |

| Chapte | r 4 The RISPP Run-time System                                      | 41 |

| 4.1    | RISPP Architecture Overview                                        |    |

| 4.2    | Requirement Analysis and Overview                                  | 43 |

| 4.3    | Online Monitoring and Special Instruction Forecasting              |    |

|        | 4.3.1 Fine-tuning the Forecast Values                              | 52 |

|        | 4.3.2 Evaluation of Forecast Fine-tuning                           | 55 |

|        | 4.3.3 Hardware Implementation for Fine-tuning the Forecast Values  | 58 |

| 4.4    | Molecule Selection                                                 | 60 |

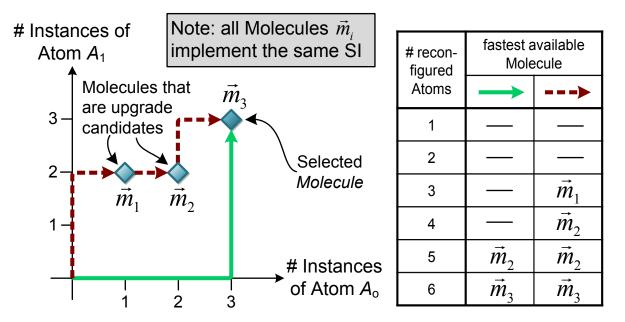

|        | 4.4.1 Problem description for Molecule Selection                   | 61 |

|        | 4.4.2 Parameter Identification for the Profit Function             | 64 |

|        | 4.4.3 Heuristic Solution for the Molecule Selection                | 66 |

|        | 4.4.4 Evaluation and Results for the Molecule Selection            | 69 |

| 4.5    | Reconfiguration-Sequence Scheduling                                | 74 |

|        | 4.5.1 Problem Description for Reconfiguration-Sequence Scheduling. | 76 |

|        | 4.5.2 Determining the Molecule Reconfiguration Sequence            | 78 |

|        | 4.5.3 Evaluation and Results for the Reconfiguration-Sequence      |    |

|        | Scheduling                                                         | 82 |

| 4.6    | Atom Replacement                                                   | 84 |

|        | 4.6.1 Motivation and Problem Description of State-of-the-art       |    |

|        | Replacement Policies                                               | 84 |

|        | 4.6.2 The MinDeg Replacement Policy                                | 87 |

|        | 4.6.3 Evaluation and Results                                       | 89 |

| 4.7    | Summary of the RISPP Run-time System                               | 95 |

| Chapte | r 5 RISPP Architecture Details                                     | 97 |

| 5.1    | Special Instructions as Interface between Hardware and Software    | 97 |

| 5.2    | Executing Special Instructions using the core Instruction Set      |    |

|        | Architecture (cISA)                                                | 01 |

| 5.3    | Data Memory Access for Special Instructions                        |    |

| 5.4    | Atom Infrastructure                                                | 08 |

|        | 5.4.1 Atom Containers and Bus Connectors                           | 11 |

|        | 5.4.2 Load/Store- and Address Generation Units 1                   | 15 |

| 5.5    | RISPP Prototype Implementation and Results 1                       | 19 |

| 5.6    | Summary of the RISPP Architecture Details                          | 27 |

| Chapte  | r 6 Benchmarks and Comparisons                              | 129 |

|---------|-------------------------------------------------------------|-----|

| 6.1     | Benchmarking the RISPP approach for different architectural |     |

|         | parameters                                                  | 129 |

| 6.2     | Comparing Different Architectures                           | 132 |

|         | 6.2.1 Assumptions and Similarities                          | 133 |

|         | 6.2.2 Dissimilarities                                       |     |

|         | 6.2.3 Fairness of Comparison                                | 134 |

| 6.3     | Comparing RISPP with Application-Specific Instruction Set   |     |

|         | Processors (ASIPs)                                          |     |

| 6.4     | Comparing RISPP with Reconfigurable Processors              | 141 |

| 6.5     | Summary of Benchmarks and Comparisons                       | 145 |

| Chapte  | r 7 Conclusion and Outlook                                  | 147 |

| 7.1     | Thesis Summary                                              | 147 |

| 7.2     | Future Work                                                 | 148 |

| Append  | lix A RISPP Simulation                                      | 151 |

| Append  | lix B RISPP Prototype                                       | 157 |

| Bibliog | raphy                                                       | 161 |

# **List of Figures**

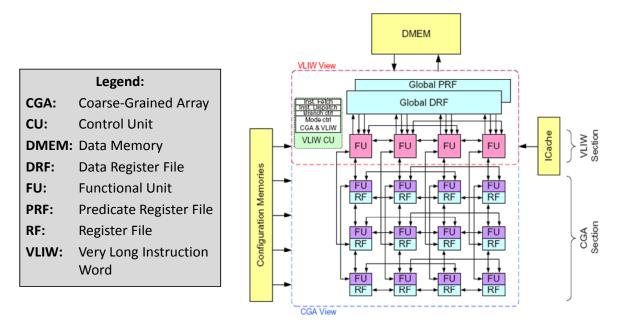

| Figure 2.1: | Connecting Coarse-Grained Reconfigurable Functional Units [BBKG07]                                                                                                                           | 9  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

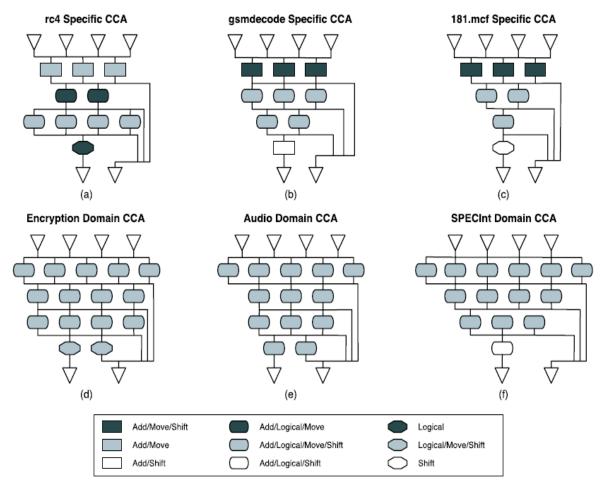

| Figure 2.2: | Application Specific and Domain Specific CCA Design Examples<br>[CBC+05]                                                                                                                     | 10 |

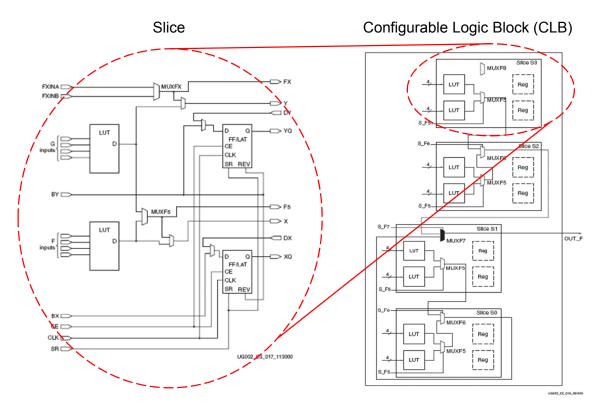

| Figure 2.3: | Connecting LUTs as the Basic Building Blocks of Fine-grained<br>Reconfigurable Logic to Slices and Configurable Logic Blocks [Xil07b]                                                        |    |

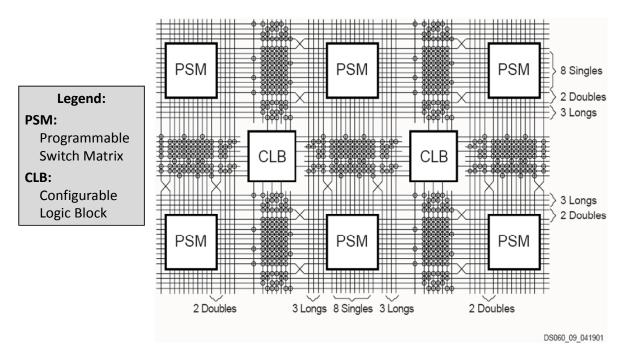

| Figure 2.4: | Two-Dimensional Array of Fine-grained Reconfigurable CLBs that are<br>Connected With Fine-grained Reconfigurable Switching Matrices<br>[Xil08b]                                              | 11 |

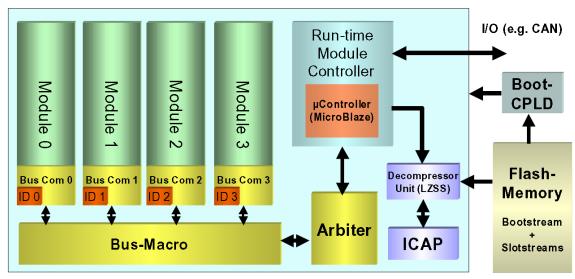

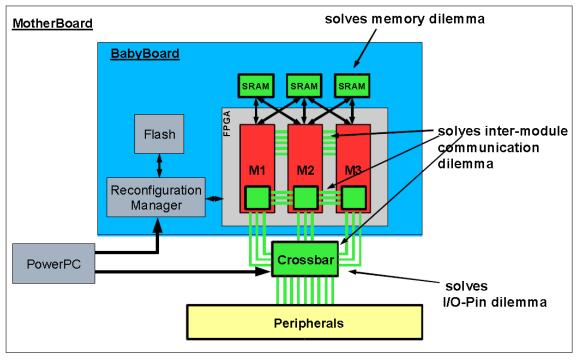

| Figure 2.5: | Example for a General Framework for Partially Reconfigurable Modules that Comprise Dedicated IP-Cores or Tasks [UHGB04b]                                                                     | 13 |

| Figure 2.6: | Erlangen Slot Machine (ESM) Architecture Overview [MTAB07]                                                                                                                                   | 14 |

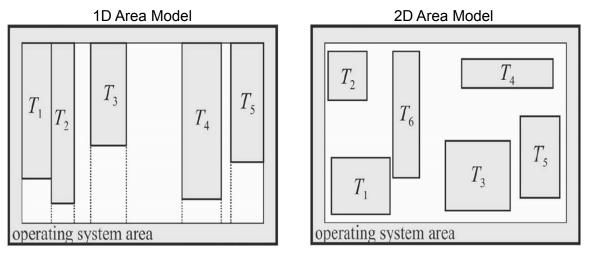

| Figure 2.7: | Different Area Models for Fine-grained Reconfigurable Fabric [SWP04]                                                                                                                         | 15 |

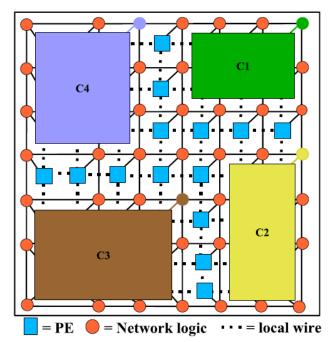

| Figure 2.8: | 2D Area Model Using a Dynamic Network on Chip Architecture to<br>Establish Communication [BAM+05]                                                                                            | 16 |

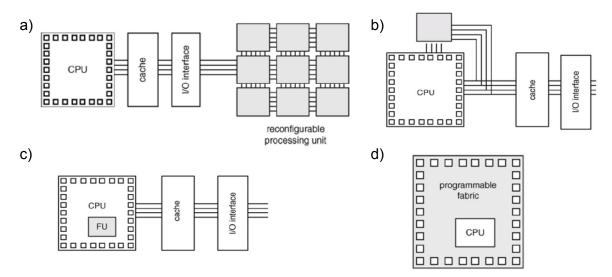

| Figure 2.9: | Coupling Reconfigurable Accelerators with the Core Processor [CH02, TCW+05]                                                                                                                  | 17 |

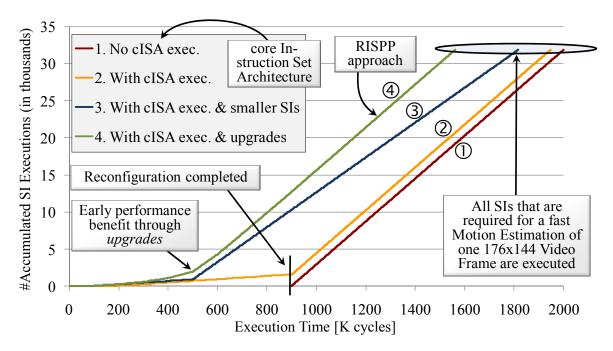

| Figure 3.1: | Comparing Different Performance vs. Reconfiguration Overhead Trade-<br>Offs                                                                                                                  | 24 |

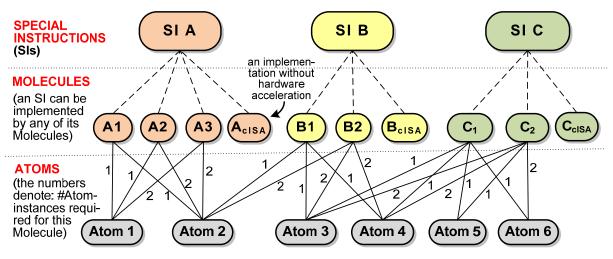

| Figure 3.2: | Hierarchical Composition of Special Instructions: Multiple<br>Implementation Alternatives – So-called Molecules – Exist per Special<br>Instruction and Demand Atoms for Realization          | 25 |

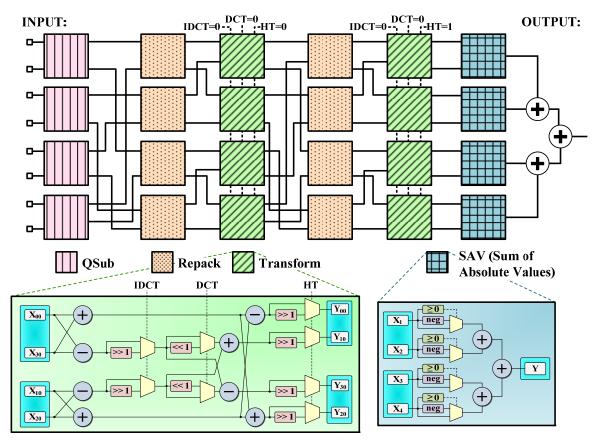

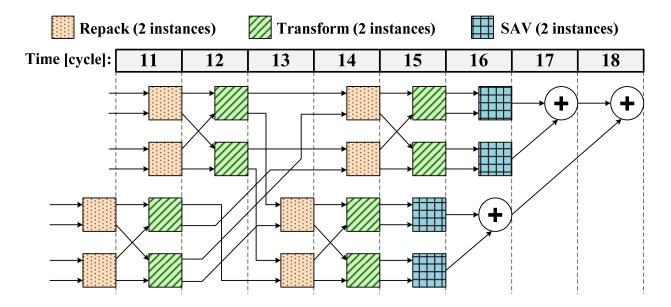

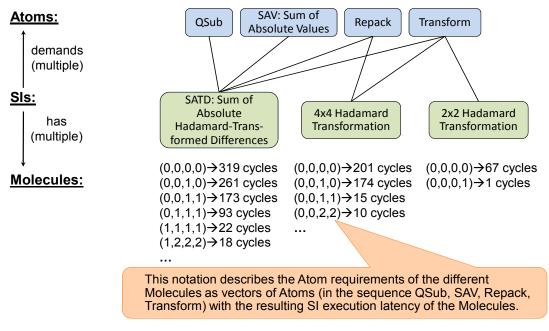

| Figure 3.3: | Example for the Modular Special Instruction SATD (Sum of Absolute (Hadamard-) Transformed Differences), Showing the Details for the Transform Atom and the SAV (Sum of Absolute Values) Atom | 27 |

| Figure 3.4: | Example Schedule for a Molecule of the SATD Special Instruction, Using<br>Two Instances of Each Atom                                                                                         |    |

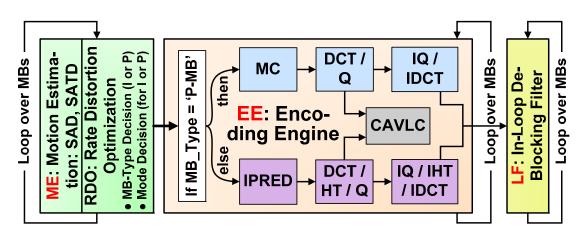

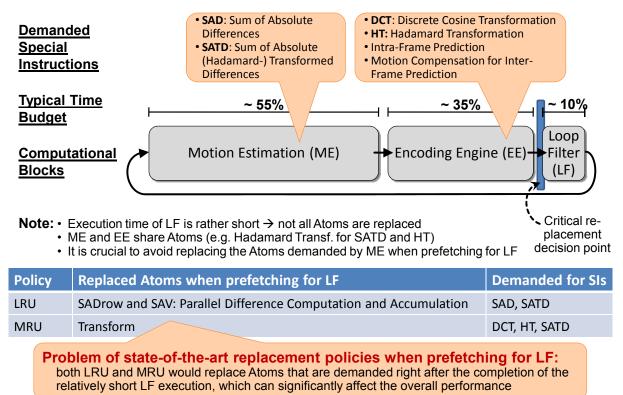

| Figure 3.5: | H.264 Application Flow, Highlighting the Three Main Computational<br>Blocks (ME, EE, LF) and their Embedded Kernels                                                                          |    |

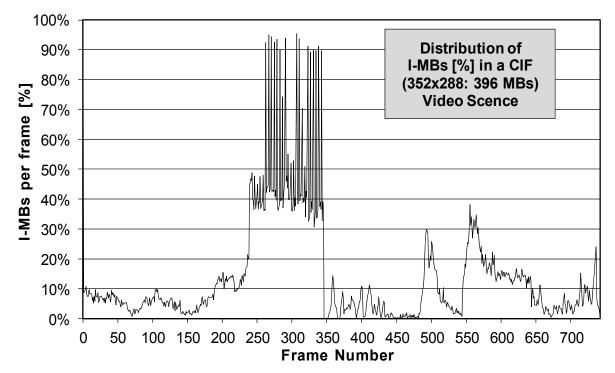

| Figure 3.6: | Relative Frequency of Intra-Prediction Macroblocks (I-MBs) in a Video<br>Sequence                                                                                                            | 33 |

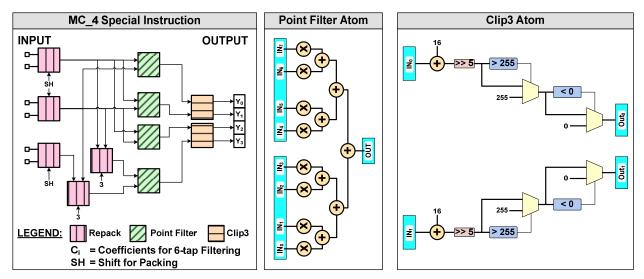

| Figure 3.7: | Example of a Motion Compensation Special Instruction with Three<br>Different Atoms and the Internal Data Path of the Point Filter Atom<br>[SBH09a]                                           | 34 |

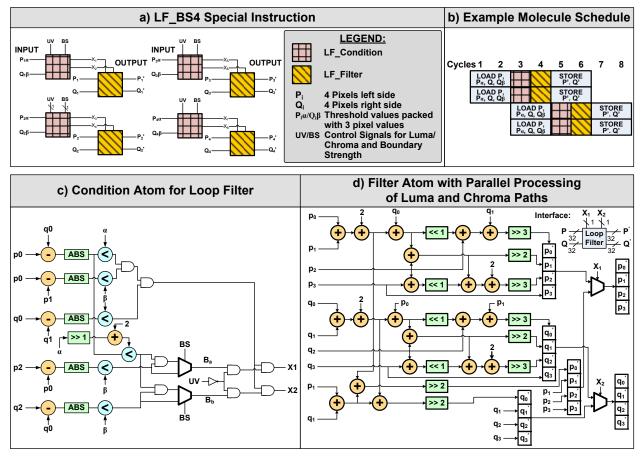

| Figure 3.8: | Special Instruction for In-Loop De-blocking Filter with Example Schedule<br>and Constituting Atoms for Filtering Conditions and Filtering Operation<br>[SBH09a]                              |    |

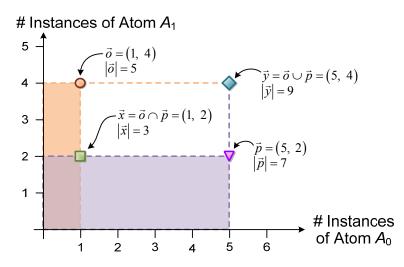

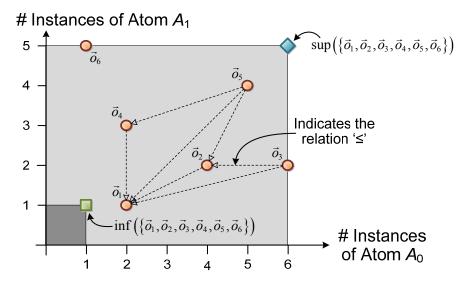

| Figure 3.9:  | Example for Union, Intersection, and Determinant Operation on Molecules                                                                                                                             | 37 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

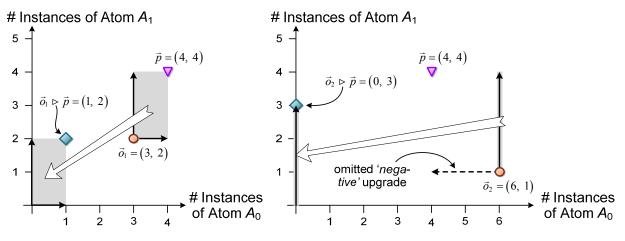

| Figure 3.10: | Example for Upgrade Operation on Molecules                                                                                                                                                          | 37 |

| Figure 3.11: | Example for Relation, Supremum, and Infimum of Molecules                                                                                                                                            | 38 |

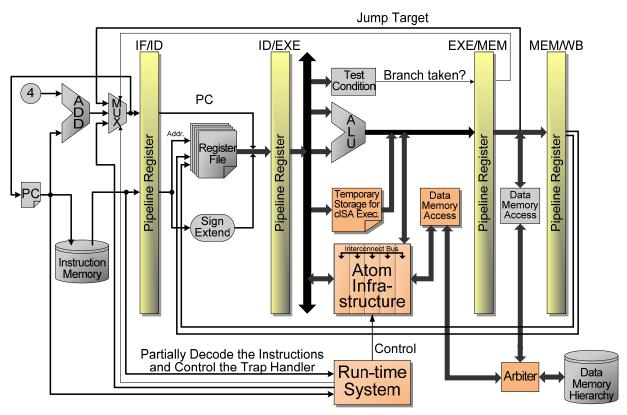

| Figure 4.1:  | Extending a Standard Processor Pipeline toward RISPP                                                                                                                                                | 42 |

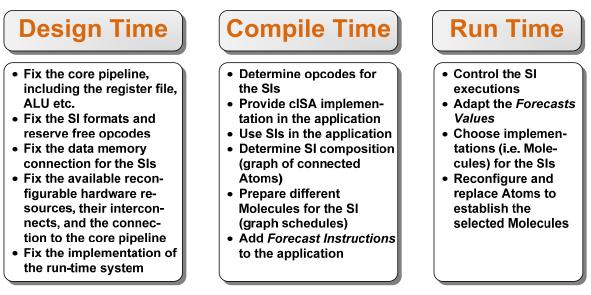

| Figure 4.2:  | Fix at Design-/Compile Time and Adapt at Run Time                                                                                                                                                   | 44 |

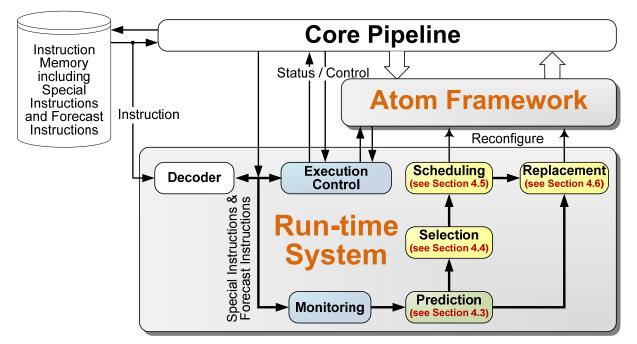

| Figure 4.3:  | Overview of the RISPP Run-time System                                                                                                                                                               | 46 |

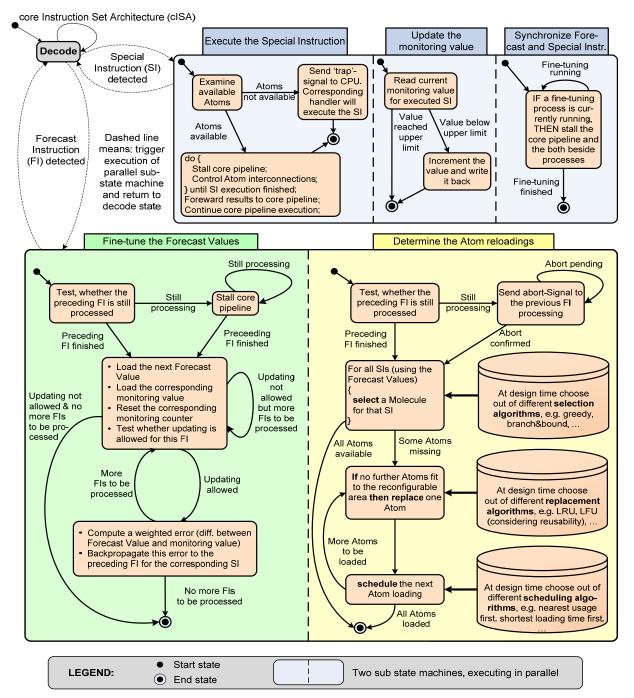

| Figure 4.4:  | State-Transition Diagram of the Run-time System                                                                                                                                                     | 48 |

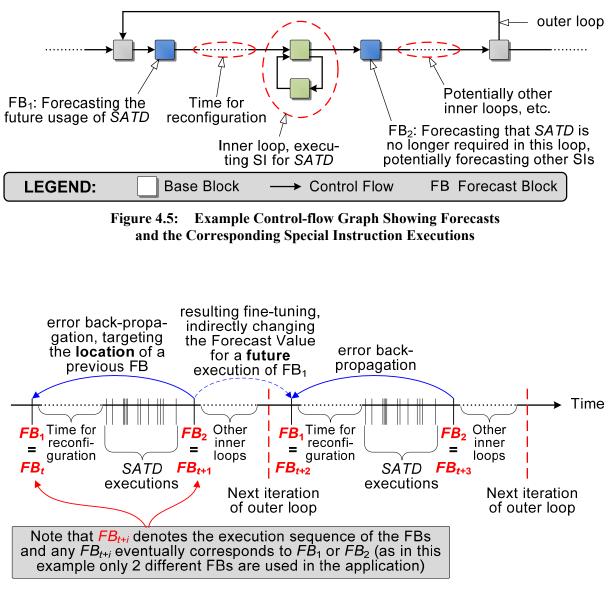

| Figure 4.5:  | Example Control-flow Graph Showing Forecasts and the Corresponding<br>Special Instruction Executions                                                                                                | 51 |

| Figure 4.6:  | Execution Sequence of Forecast and Special Instructions with the<br>Resulting Error Back Propagation and Fine-tuning                                                                                | 51 |

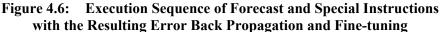

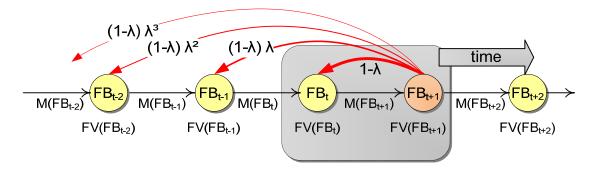

| Figure 4.7:  | A Chain of Forecast Blocks, Showing How the Information in a Sliding<br>Window is Used to Determine a Forecast Error that is Back Propagated                                                        | 52 |

| Figure 4.8:  | A Chain of Forecast Blocks, Showing How Multiple Previous Forecast Blocks may be Updated, Depending on Parameter $\lambda$                                                                          | 54 |

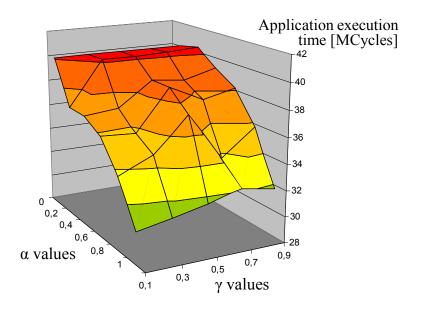

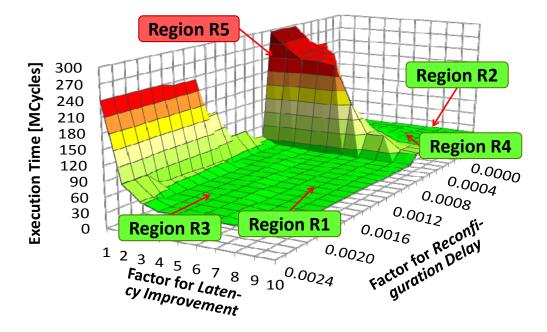

| Figure 4.9:  | Parameter Evaluation for $\alpha$ and $\gamma$ for $\lambda$ =0, Showing the Resulting Application Run Time                                                                                         | 56 |

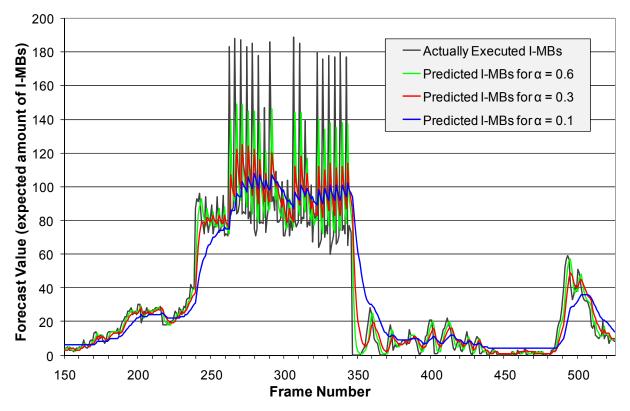

| Figure 4.10: | Evaluation of the Forecast Value for Different Values of $\alpha$ , Showing the Actual and Predicted SI Execution                                                                                   | 57 |

| Figure 4.11: | Accumulated Absolute Forecast Error                                                                                                                                                                 | 57 |

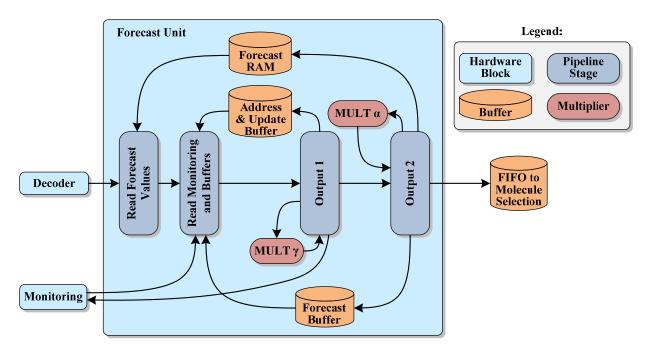

| Figure 4.12: | Pipelined Implementation for Fine-tuning the Forecasts [D.7]                                                                                                                                        | 58 |

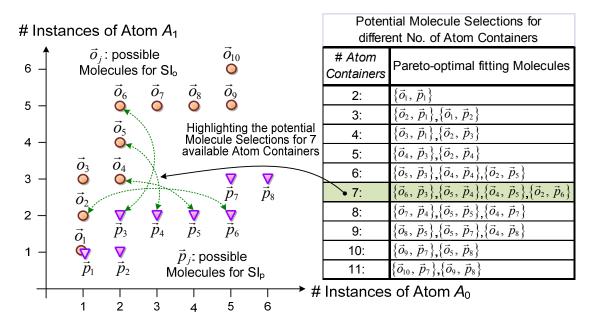

| Figure 4.13: | Different Showcase Molecules for Two Special Instructions with the<br>Corresponding Selection Possibilities for Different Numbers of Available<br>Atom Containers                                   | 61 |

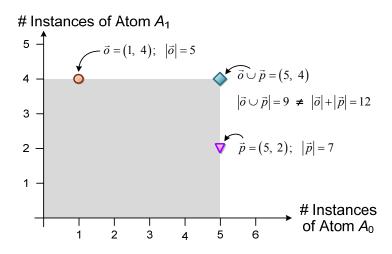

| Figure 4.14: | Atom Sharing, Leading to a Size of the Combined Molecule that is<br>Smaller than the Accumulated Size of the Two Individual Molecules                                                               | 63 |

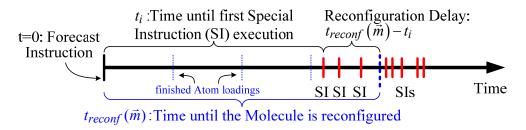

| Figure 4.15: | Comparing the Reconfiguration Time and the First Execution Time of a Special Instruction                                                                                                            | 65 |

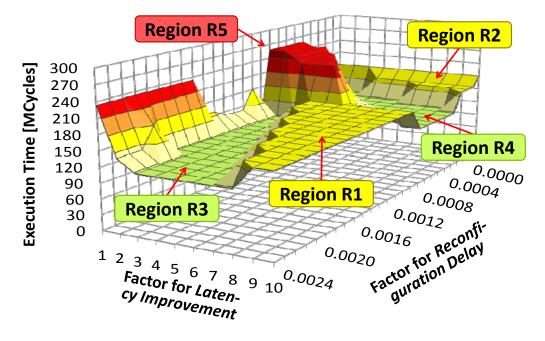

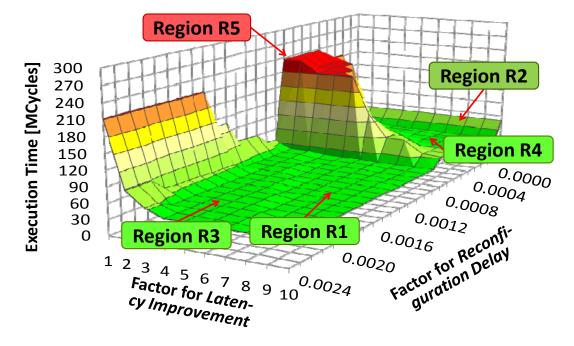

| Figure 4.16: | Impact of the Profit-Function Parameters on the Application Execution<br>Time for Four Atom Containers                                                                                              | 70 |

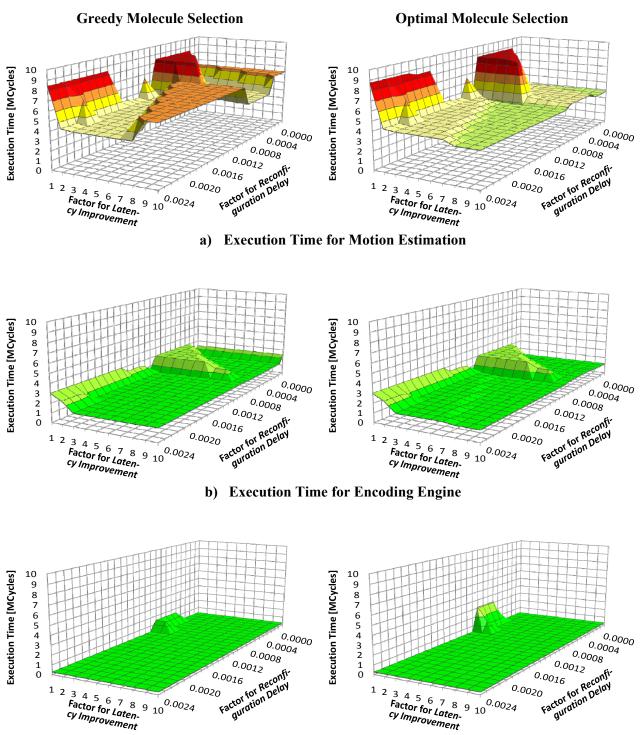

| Figure 4.17: | Detailed Analysis of the Application Execution Time for the Three<br>Individual Computational Blocks Motion Estimation, Encoding Engine,<br>and In-Loop De-blocking Filter for Four Atom Containers | 71 |

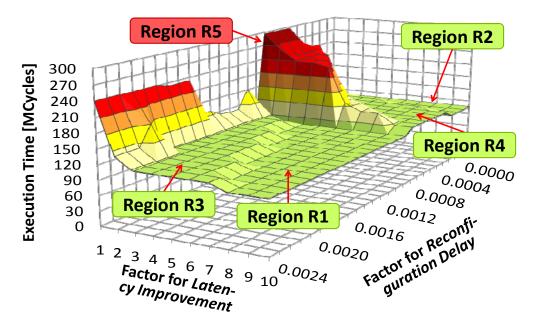

| Figure 4.18: | Impact of the Profit Function Parameters on the Application Execution<br>Time for Seven Atom Containers                                                                                             | 72 |

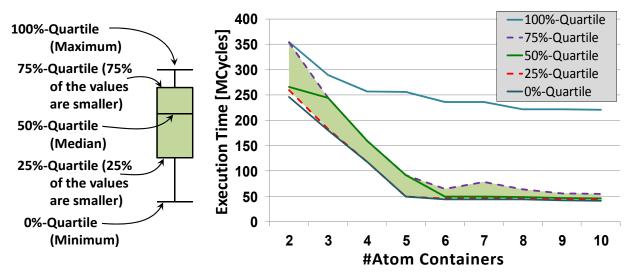

| Figure 4.19: | Statistical Analysis of Greedy Selection for Different Numbers of Atom<br>Containers                                                                                                                | 73 |

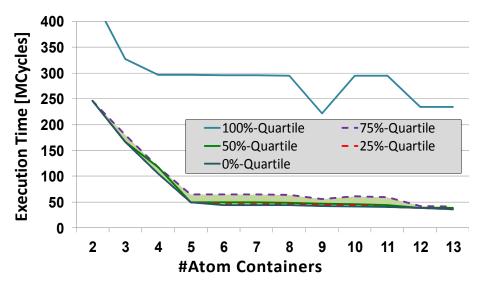

| Figure 4.20: | Statistical Analysis of Optimal Selection for Different Numbers of Atom<br>Containers                                                                                              | 74  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.21: | Different Atom Schedules with the Corresponding Molecule Availabilities                                                                                                            | 75  |

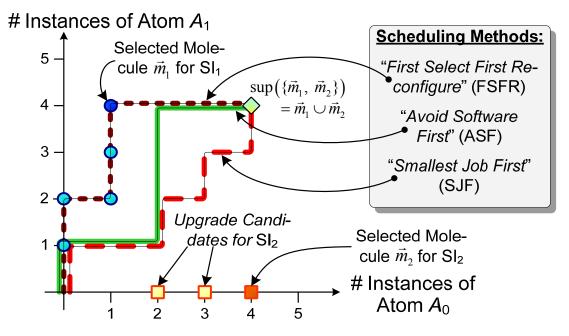

| Figure 4.22: | Comparing Different Scheduling Methods for Two Selected Molecules of Different SIs                                                                                                 | 78  |

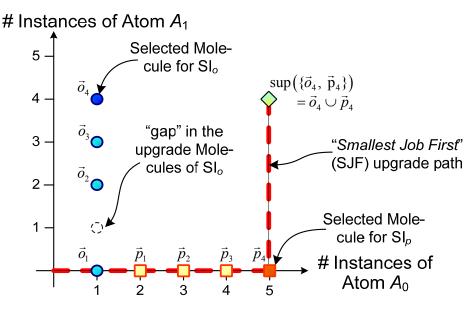

| Figure 4.23: | The Problem of Upgrade 'Gaps' for the SJF Scheduler                                                                                                                                | 81  |

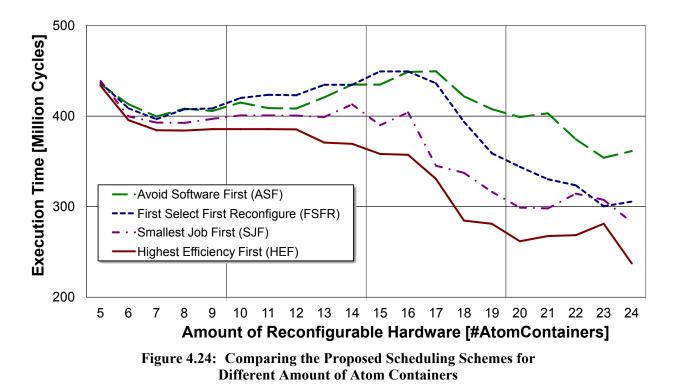

| Figure 4.24: | Comparing the Proposed Scheduling Schemes for Different Amount of Atom Containers                                                                                                  | 82  |

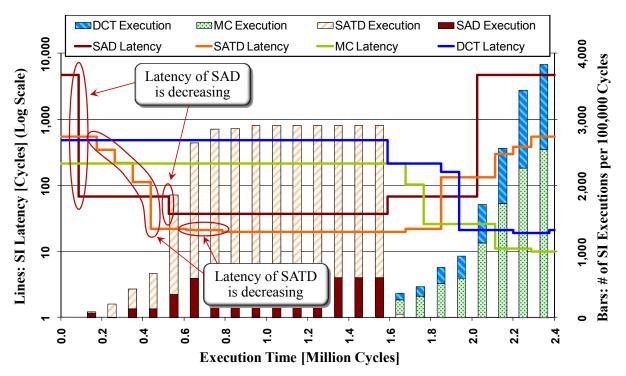

| Figure 4.25: | Detailed Analysis of the HEF Scheduler for the Motion Estimation and<br>Encoding Engine, Showing how the SI Latencies (Lines) and Execution<br>Frequencies (Bars) Change Over Time | 83  |

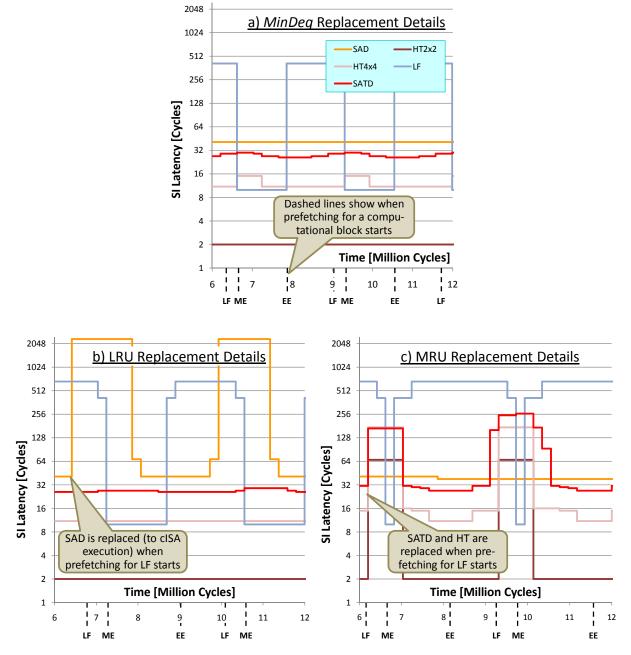

| Figure 4.26: | High-level H.264 Video Encoder Application Flow, Showing a Typical Use Case and Presenting the Different Replacement Decisions of LRU and MRU in Detail                            | 84  |

| Figure 4.27: | Examples for Atoms and their Utilization in SIs, Showing Different<br>Implementation Alternatives (i.e. Molecules) and their Execution<br>Latencies                                |     |

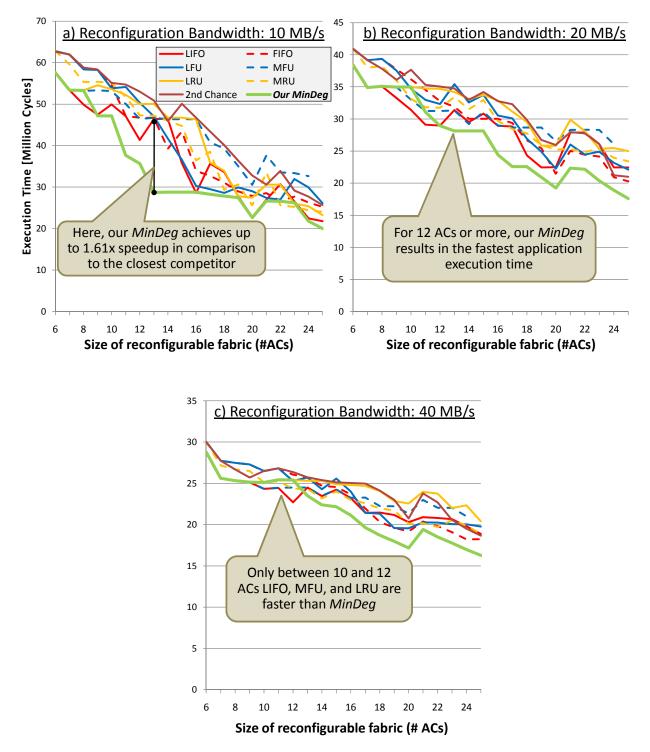

| Figure 4.28: | Comparing the MinDeg Replacement Policy with State-of-the-art Policies<br>for Different Reconfiguration Bandwidths (a-c) and Size of the<br>Reconfigurable Fabric (x-axis)         | 90  |

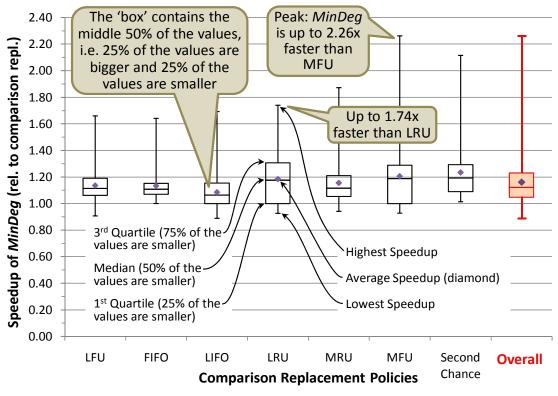

| Figure 4.29: | Summarizing the Performance Improvement of MinDeg in Comparison with State-of-the-art Replacement Policies                                                                         | 92  |

| Figure 4.30: | Detailed Replacement Analysis for 20 MB/s Reconfiguration Bandwidth and 15 ACs                                                                                                     | 93  |

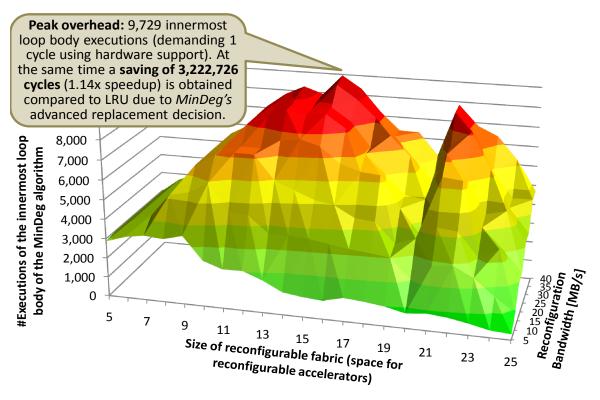

| Figure 4.31: | Algorithm Execution Time (Accumulated Number of Innermost Loop<br>Body Executions when Encoding 10 Frames)                                                                         | 94  |

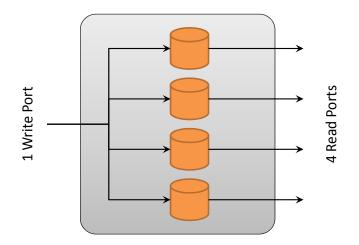

| Figure 5.1:  | Using Dual-Ported BlockRAMs to Implement a General Purpose Register<br>File (GPR) with One Write and Four Read Ports                                                               | 98  |

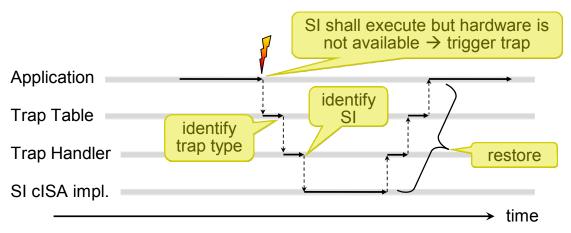

| Figure 5.2:  | Levels and Contexts to reach the cISA Implementation of an SI                                                                                                                      | 102 |

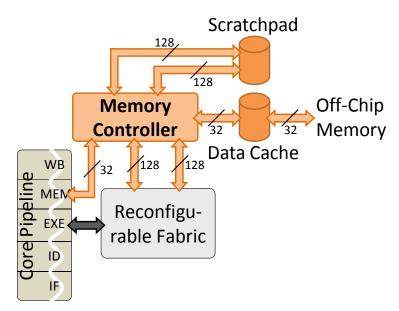

| Figure 5.3:  | Memory Controller, Connecting the Memory Stage of the Core Pipeline<br>and Both 128-bit Ports for SIs with the Data Cache and an On-Chip<br>Scratchpad Memory                      | 107 |

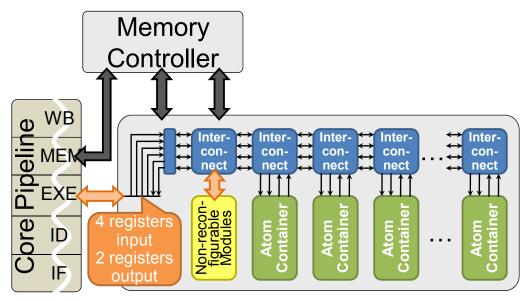

| Figure 5.4:  | Overview of the Atom Infrastructure and its Connection to the Core<br>Pipeline and the Memory Controller                                                                           |     |

| Figure 5.5:  | Overview of the Non-reconfigurable Modules within the Atom<br>Infrastructure                                                                                                       | 110 |

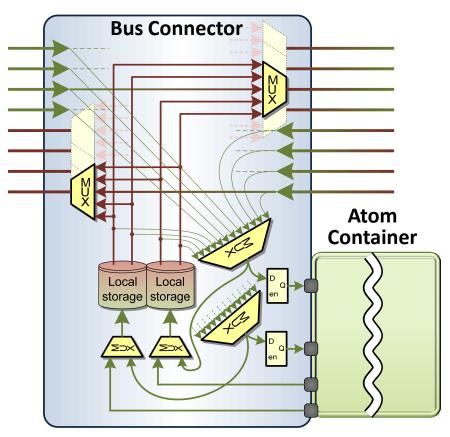

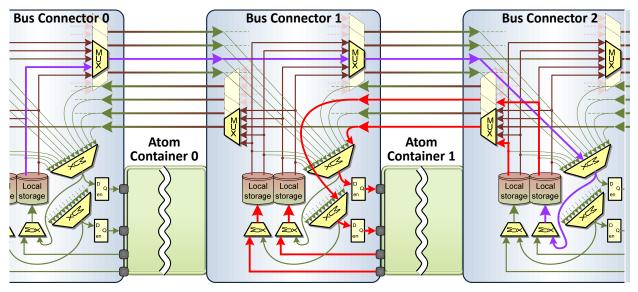

| Figure 5.6:  | Internal Composition of a Bus Connector, Showing the Connection to its<br>Atom Container and the Neighboring Bus Connectors                                                        | 112 |

| Figure 5.7:  | Atom Infrastructure with three Bus Connectors, Highlighting two<br>Example Communication Patterns for Typical Atom Computation and<br>Data Copying                                                            | 113 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

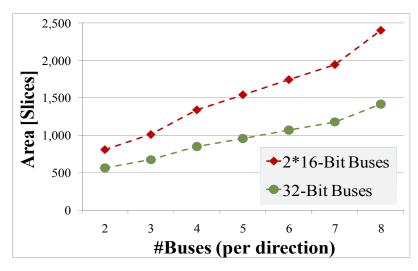

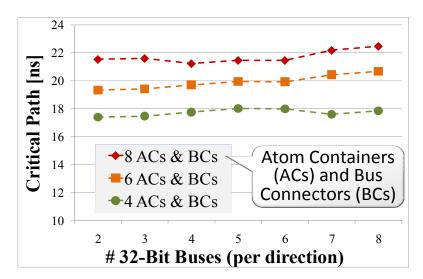

| Figure 5.8:  | Area Requirements per Bus Connector for More Buses and Finer Access<br>Granularity                                                                                                                            |     |

| Figure 5.9:  | Latency Changes for Increasing Amount of Buses and Bus Connectors                                                                                                                                             | 114 |

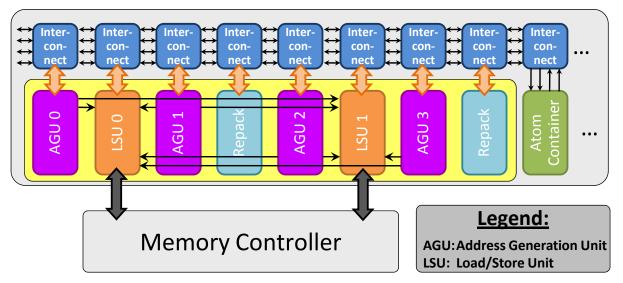

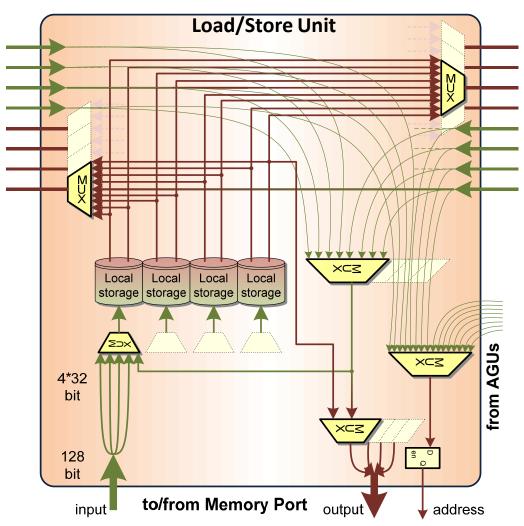

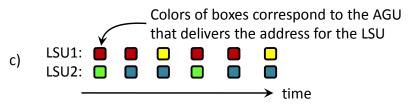

| Figure 5.10: | Internal Composition of a Load/Store Unit, Showing the Connection to the Memory Port and the Address Generation Units                                                                                         | 115 |

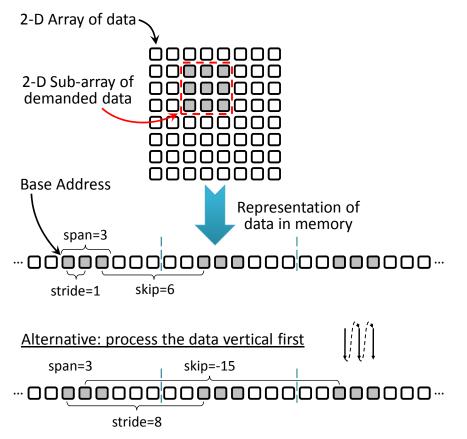

| Figure 5.11: | Memory Streams, Described by Base Address, Stride, Span, and Skip                                                                                                                                             |     |

| Figure 5.12: | Problems, if one Memory Stream shall be accessed with both LSUs in Parallel                                                                                                                                   | 117 |

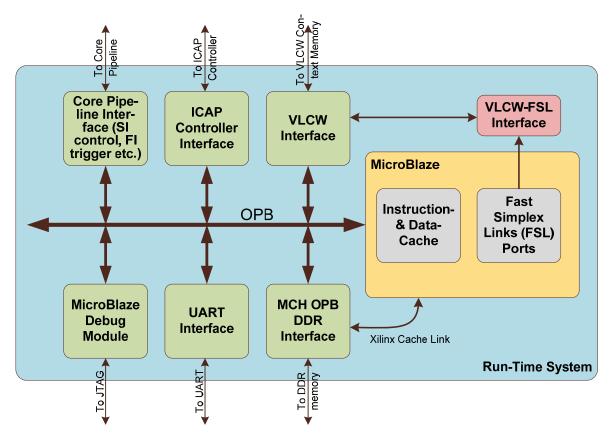

| Figure 5.13: | Overview of the MicroBlaze System that Implements the Algorithms of the Run-time System and Controls the Reconfigurations [D.1]                                                                               | 119 |

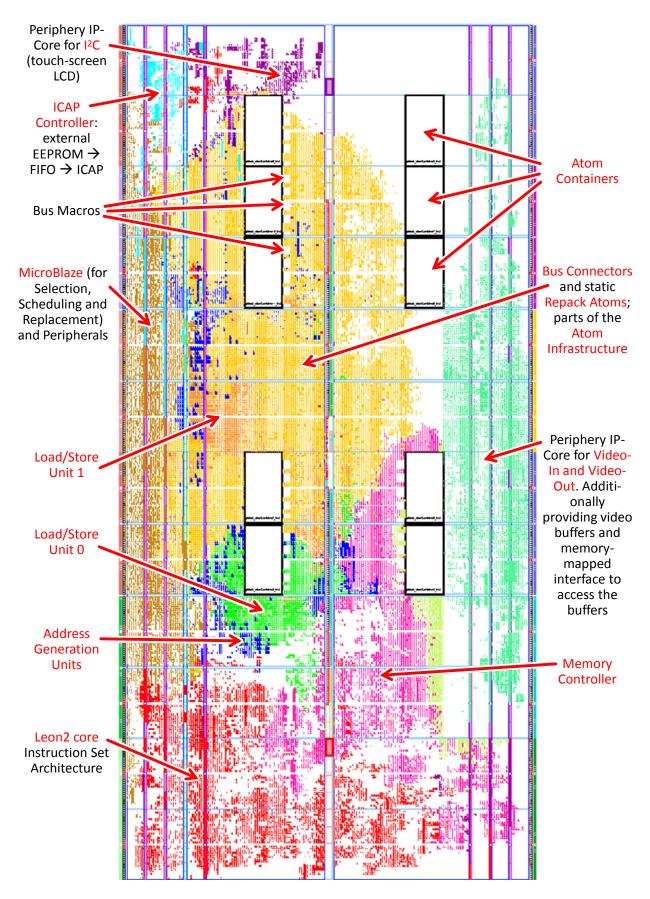

| Figure 5.14: | Floorplan of the RISPP Prototype Implementation, Showing the<br>Placement of the Different Components on the Xilinx Virtex-4 LX 160<br>FPGA [D.1]                                                             | 122 |

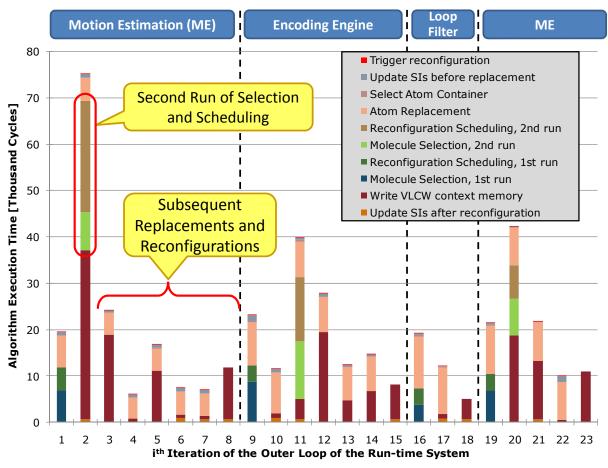

| Figure 5.15: | Execution Time Analysis of the RISPP Run-time System's Algorithms that Execute on the MicroBlaze Part of the RISPP Prototype [D.1]                                                                            | 126 |

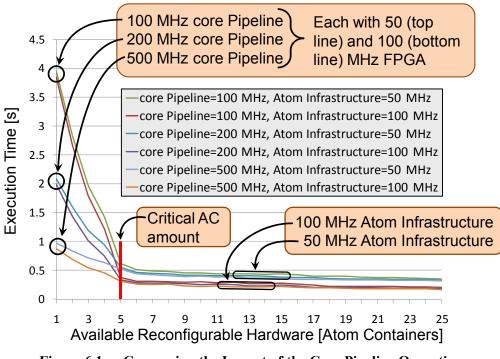

| Figure 6.1:  | Comparing the Impact of the Core Pipeline Operating Frequency and the Atom Infrastructure Operating Frequency                                                                                                 | 130 |

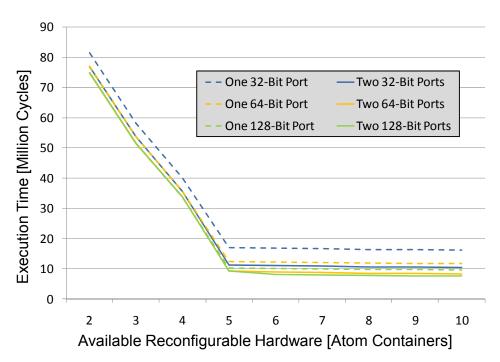

| Figure 6.2:  | Investigating the Effect of Different Data Memory Connections                                                                                                                                                 | 131 |

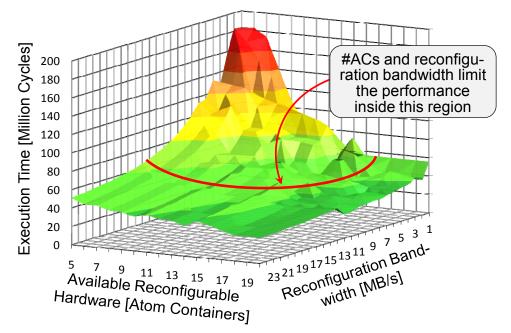

| Figure 6.3:  | Impact of the Reconfiguration Bandwidth and the Number of Atom Containers                                                                                                                                     | 132 |

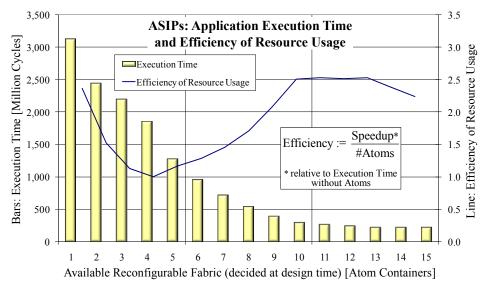

| Figure 6.4:  | Analyzing the Execution Time and the Resource Usage Efficiency Using Different Area Deployments when Processing 140 Video Frames with an ASIP                                                                 | 136 |

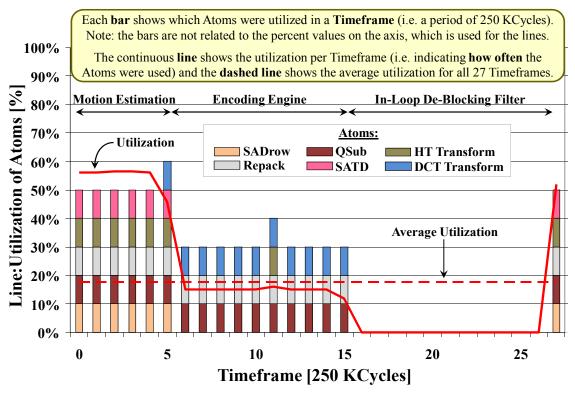

| Figure 6.5:  | Detailed ASIP Utilization Variations for Six Available Atoms                                                                                                                                                  | 137 |

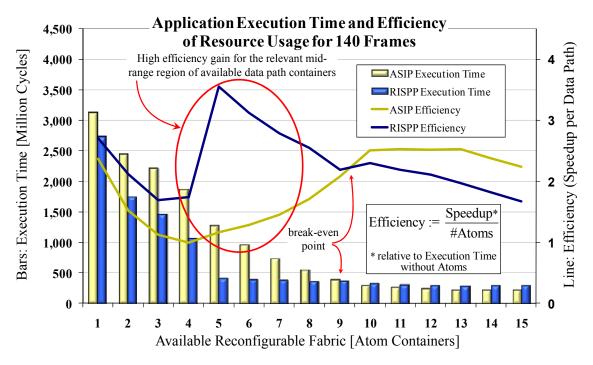

| Figure 6.6:  | Application Execution Time and Efficiency of Resource Usage for<br>Encoding 140 Video Frames on ASIP and RISPP                                                                                                | 138 |

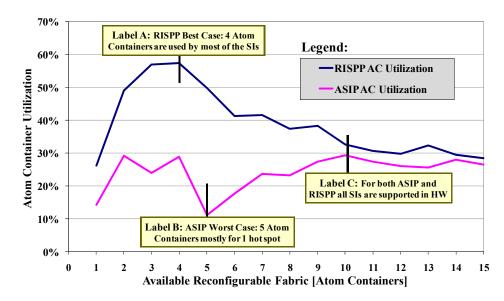

| Figure 6.7:  | Atom Utilization for ASIP and RISPP                                                                                                                                                                           |     |

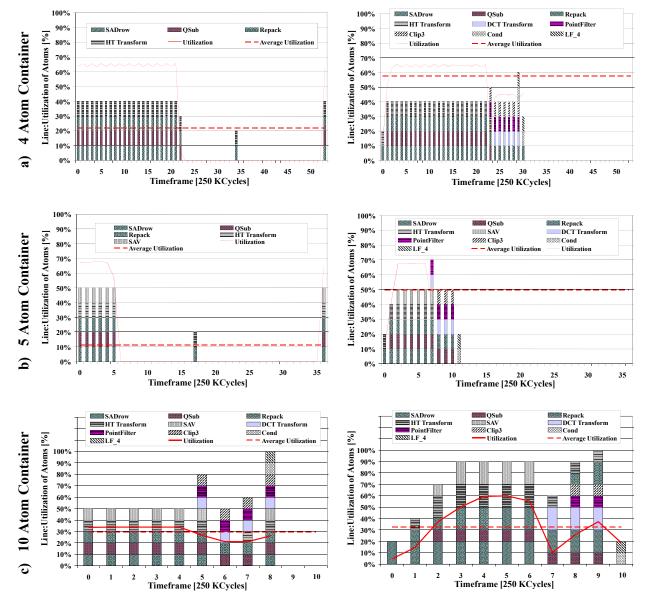

| Figure 6.8:  | Detailed Atom Utilization Variations for 4, 5, and 10 Available Atom<br>Containers (AC), Used by ASIP (AC Content Determined at Design Time)<br>and RISPP (AC Content Reconfigured at Run Time); Respectively | 140 |

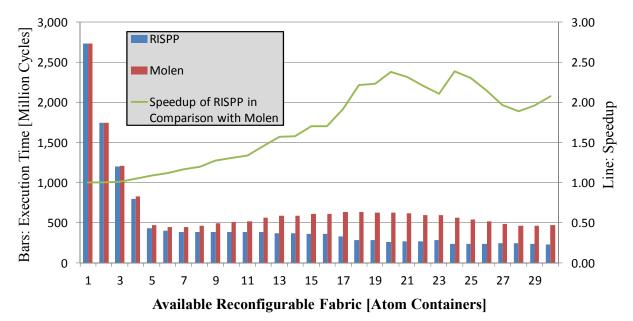

| Figure 6.9:  | Comparison of RISPP and Molen, Showing the Execution Time of the<br>H.264 Video Encoder Benchmark (Encoding 140 Frames in CIF<br>Resolution, i.e. 352x288) and the Speedup                                    | 142 |

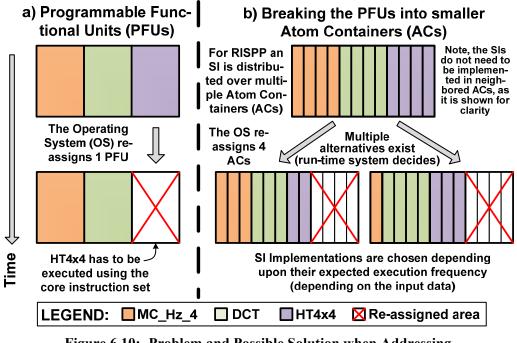

| Figure 6.10: | Problem and Possible Solution when Addressing Reconfigurable<br>Hardware as Monolithic RFUs                                                                                                                   | 144 |

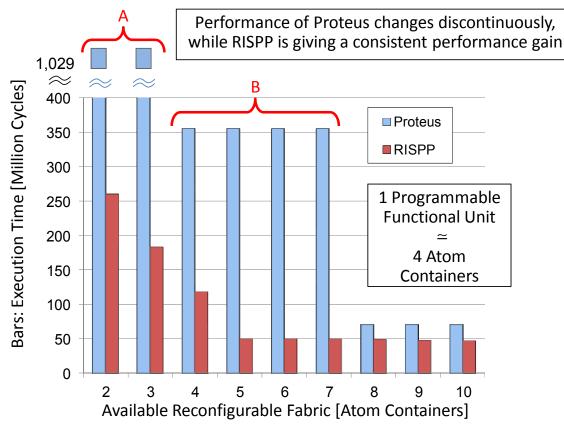

| Figure 6.11: | Comparing the RISPP Approach with Proteus, Executing an H.264 Video<br>Encoder and Showing the Impact of RFUs vs. Atom Containers                                                                             | 145 |

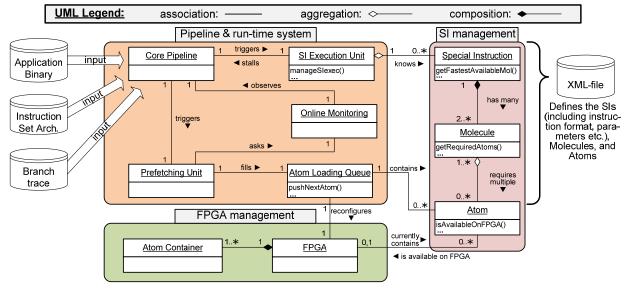

| Figure A.1: | Internal Composition of the Design Space Exploration Tool, Showing                                                                                                     |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | Module Interactions                                                                                                                                                    | 151 |

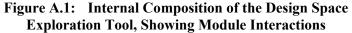

| Figure A.2: | Overview of the RISPP Simulation Visualization: RISPPVis [D.4]                                                                                                         | 153 |

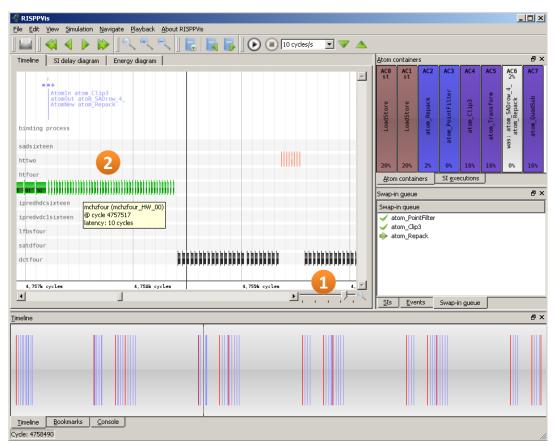

| Figure A.3: | RISPPVis Zooming into SI Execution Latency Changes [D.4]                                                                                                               | 153 |

| Figure A.4: | RISPPVis SI Latency Diagram [D.4]                                                                                                                                      | 155 |

| Figure A.5: | RISPPVis Design Rule Check [D.4]                                                                                                                                       | 155 |

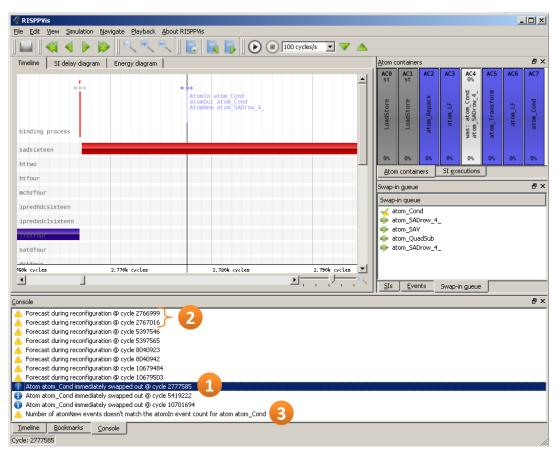

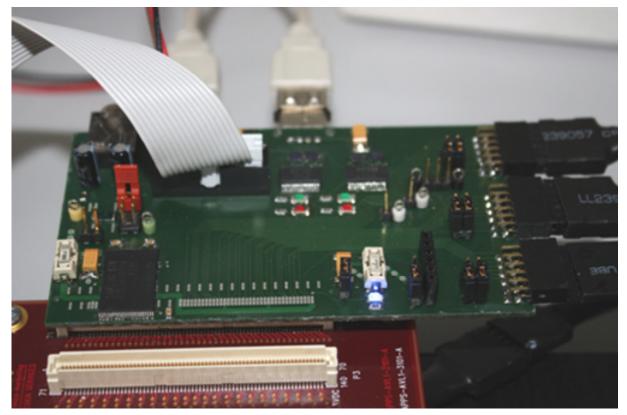

| Figure B.1: | Picture of the Avnet Xilinx Virtex-4 LX160 Development Kit with<br>Periphery for SRAM, SDRAM, Reconfiguration EEPROM, Audio/Video<br>Module, and (Touch Screen) LCDs   | 158 |

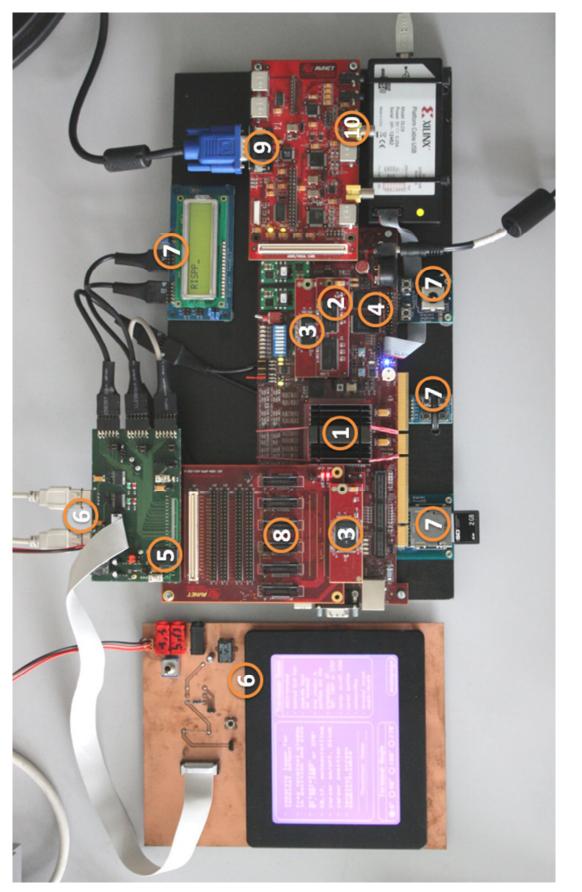

| Figure B.2: | Schematic of the Four Layers for the PCB for EEPROM, USB, Audio,<br>Touch-Screen LCD, and General-purpose Connectors that was Developed<br>in the Scope of this Thesis | 159 |

| Figure B.3: | Picture of the Developed PCB                                                                                                                                           | 159 |

# List of Tables

| Table 3.1:  | Overview of Different SATD Molecule Alternatives                                                                                                 | 28  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2:  | Overview of Implemented SIs and their Required Atoms [SBH09a]                                                                                    | 35  |

| Table 3.3:  | Overview of High-level Molecule and Special Instruction Properties                                                                               |     |

| Table 4.1:  | Hardware Requirements for Monitoring and Forecast Unit                                                                                           | 60  |

| Table 4.2:  | Speedup due to HEF Scheduling                                                                                                                    | 83  |

| Table 4.3:  | Relevant History-based Replacement Policies, Used for Evaluating the Performance-guided MinDeg Policy                                            | 88  |

| Table 5.1:  | SPARC V8 Instruction Formats [SPA]                                                                                                               | 99  |

| Table 5.2:  | SPARC V8 Instruction Format 2 with RISPP Extensions [D.7]                                                                                        | 99  |

| Table 5.3:  | SPARC V8 Format 2 Used for UNIMP and Helper Instructions (HIs)                                                                                   | 100 |

| Table 5.4:  | Overview of Implemented Helper Instructions [D.7]                                                                                                | 100 |

| Table 5.5:  | Instruction Format for Special Instructions as Part of SPARC V8<br>Instruction Format 2                                                          | 101 |

| Table 5.6:  | Hardware Implementation Results for the RISPP Prototype; all FPGA<br>Utilization Numbers are Relative to the Used Xilinx Virtex-4 LX 160<br>FPGA | 102 |

| Table 5.7:  | Atom Implementation Results                                                                                                                      |     |

| Table 5.8:  | Individually Constraint Parts of the Critical Path in the Atom                                                                                   | 124 |

| 1 abic 5.8. | Infrastructure and their Processing Sequence [D.1]                                                                                               | 124 |

| Table 6.1:  | Investigated Architectural Parameters                                                                                                            |     |

| Table 6.2:  | Selected Atoms for ASIPs for the Computational Blocks of H.264 Video Encoder                                                                     |     |

| Table 6.3:  | Summary of Comparison of RISPP and ASIP                                                                                                          |     |

| Table 6.4:  | Speedup Compared with Molen, a State-of-the-art Reconfigurable                                                                                   |     |

|             | Processor with Monolithic SIs                                                                                                                    | 143 |

| Table B.1:  | Resources Provided by the FPGA of the Prototype [Xil07a]                                                                                         | 157 |

# **List of Algorithms**

| Algorithm 4.1: | Pseudo Code of a Greedy Knapsack Solver                                                                    | 66  |

|----------------|------------------------------------------------------------------------------------------------------------|-----|

| Algorithm 4.2: | Pseudo Code of the Molecule Selection                                                                      | 68  |

| Algorithm 4.3: | The Implemented Scheduling Method "Highest Efficiency First" (HEF)                                         | 80  |

| Algorithm 4.4: | The Performance-guided Minimum Degradation (MinDeg) Replacement<br>Policy                                  | 89  |

| Algorithm 5.1: | Trap Handler to Implement Special Instructions with the cISA and the<br>Support of the Helper Instructions | 104 |

| Algorithm 5.2: | Examples for Implicit and Explicit cISA Execution of SIs                                                   | 104 |

# Abbreviations

| AC     | Atom Container: a part of the reconfigurable fabric that can be dynamically reconfigured to contain an Atom, i.e. an elementary data path                                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGU    | Address Generation Unit                                                                                                                                                                                              |

| ALU    | Arithmetic Logic Unit                                                                                                                                                                                                |

| ASF    | Avoid Software First: A reconfiguration-sequence scheduling algorithm, as presented in Sec-<br>tion 4.5                                                                                                              |

| ASIC   | Application Specific Integrated Circuit                                                                                                                                                                              |

| ASIP   | Application Specific Instruction Set Processor                                                                                                                                                                       |

| BC     | Bus Connector: Connecting an $\rightarrow$ AC to the Atom Infrastructure                                                                                                                                             |

| BRAM   | Block $\rightarrow$ RAM: An on-chip memory block that is available on Virtex $\rightarrow$ FPGAs                                                                                                                     |

| cISA   | core Instruction Set Architecture: the part of the instruction set that is implemented using the (non-reconfigurable) core pipeline; can be used to implement $\rightarrow$ SIs as well, as presented in Section 5.2 |

| CLB    | Configurable Logic Block: part of an $\rightarrow$ FPGA, contains multiple $\rightarrow$ LUTs                                                                                                                        |

| CPU    | Central Processing Unit                                                                                                                                                                                              |

| DCT    | Discrete Cosine Transformation: a computational kernel that is used in H-264 video encoder                                                                                                                           |

| EEPROM | Electrically Erasable Programmable Read Only Memory                                                                                                                                                                  |

| FB     | Forecast Block: indicated by an $\rightarrow$ FI, containing a set of $\rightarrow$ SIs with a $\rightarrow$ FV per SI                                                                                               |

| FI     | Forecast Instruction: a special $\rightarrow$ HI that indicates an $\rightarrow$ FB                                                                                                                                  |

| FIFO   | First-In First-Out buffer                                                                                                                                                                                            |

| FPGA   | Field Programmable Gate Array: a reconfigurable device that is composed as an array of $\rightarrow$ CLBs, $\rightarrow$ BRAMs, and further components                                                               |

| FPS    | Frames Per Second                                                                                                                                                                                                    |

| FSFR   | First Select, First Reconfigure: a reconfiguration-sequence scheduling algorithm, as presented in Section 4.5                                                                                                        |

| FSL    | Fast Simplex Link: A special communication mechanism for a MicroBlaze processor                                                                                                                                      |

| FSM    | Finite State Machine                                                                                                                                                                                                 |

| FV     | Forecast Value: the expected number of $\rightarrow$ SI executions for the next computational block, part of the information in an $\rightarrow$ FB                                                                  |

| GPP    | General Purpose Processor                                                                                                                                                                                            |

| GPR    | General Purpose Register file                                                                                                                                                                                        |

| GUI    | Graphical User Interface                                                                                                                                                                                             |

| HEF    | Highest Efficiency First: reconfiguration sequence-scheduling algorithm, as presented in Sec-<br>tion 4.5                                                                                                            |

| HI     | Helper Instruction: an assembly instruction that is dedicated to system support (e.g. an $\rightarrow$ FI); not part of the $\rightarrow$ cISA and not an $\rightarrow$ SI                                           |

| HT     | Hadamard Transformation: a computational kernel that is used in H-264 video encoder                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA    | Instruction Set Architecture                                                                                                                                                                                                                         |

| ISS    | Instruction Set Simulator                                                                                                                                                                                                                            |

| IP     | Intellectual Property                                                                                                                                                                                                                                |

| KB     | Kilo Byte (also KByte): 1024 Byte                                                                                                                                                                                                                    |

| LSU    | Load/Store Unit                                                                                                                                                                                                                                      |

| LUT    | Look-Up Table: smallest element in an $\rightarrow$ FPGA, part of a $\rightarrow$ CLB; configurable as logic or memory                                                                                                                               |

| MB     | Mega Byte (also MByte): 1024 →KB                                                                                                                                                                                                                     |

| MinDeg | Minimum Degradation: an Atom replacement algorithm, as presented in Section 4.6                                                                                                                                                                      |

| MUX    | Multiplexer                                                                                                                                                                                                                                          |

| NOP    | No Operation: an assembly instruction that does not perform any visible calculation, memory access, or register manipulation                                                                                                                         |

| NP     | Non-deterministic Polynomial: A complexity class that contains all decision problems that can be solved by a non-deterministic Turing machine in polynomial time                                                                                     |

| OS     | Operating System                                                                                                                                                                                                                                     |

| PCB    | Printed Circuit Board                                                                                                                                                                                                                                |

| PRM    | Partially Reconfigurable Module                                                                                                                                                                                                                      |

| PSM    | Programmable Switching Matrix                                                                                                                                                                                                                        |

| RAM    | Random Access Memory                                                                                                                                                                                                                                 |

| RISPP  | Rotating Instruction Set Processing Platform                                                                                                                                                                                                         |

| RFU    | Reconfigurable Functional Unit: denotes a reconfigurable region that can be reconfigured to-<br>ward an SI implementation                                                                                                                            |

| SI     | Special Instruction                                                                                                                                                                                                                                  |

| SJF    | Shortest Job First: a reconfiguration sequence-scheduling algorithm, as presented in Section 4.5                                                                                                                                                     |

| SPARC  | Scalable Processor Architecture: processor family from Sun Microsystems; used for the $\rightarrow$ RISPP prototype                                                                                                                                  |

| VLC    | Variable Length Coding: a computational kernel that is used in H-264 video encoder                                                                                                                                                                   |

| VLCW   | Very Long Control Word: configuration bits for the coarse-grained reconfigurable Atom Infra-<br>structure, i.e. determining the operation mode and connection of the $\rightarrow$ ACs, $\rightarrow$ BC, $\rightarrow$ AGUs, and $\rightarrow$ LSUs |

# **Chapter 1** Introduction

Embedded processors are the heart of embedded systems. They perform the calculations that are required to make a set of components eventually appear as a system. For instance, they receive input data from cameras, microphones, and/or many further sensors, perform the calculations that the user of the embedded system expects (e.g. video compression/transmission, feature extraction, etc., i.e. the actual functionality of the system) and present the corresponding results. Therefore, embedded processors are the key components for rapidly growing application fields ranging from automotive to personal mobile communication/entertainment etc.

Designing an embedded system typically starts with an analysis of the requirements. Afterwards, some standard components (e.g. periphery or processors provided as chips or IP cores) may be selected and combined with some specifically created components to realize the desired system either as a single chip or as a board with multiple chips. For some tasks that the system shall be able to perform (e.g. decoding a video stream) the question arises whether a general-purpose processor (GPP) or an applicationspecific integrated circuit (ASIC) shall perform that task. Choosing a GPP has the advantage that it provides a very high flexibility, i.e. it is programmable by software. This allows that the GPP can be used to perform further tasks (when the video decoder is not required at a certain time or in parallel to it, using a multi-tasking environment). Additionally, it also allows changing the specification of the tasks (e.g. a new video decoding standard or a bug fix) by changing the software, e.g. via firmware upgrades. The advantage of an ASIC is its efficiency (e.g. 'performance per area' or 'performance per power consumption') that it achieves because it is particularly optimized for the specific task. Using an ASIC typically introduces rather high initial cost for creating that ASIC, but the higher efficiency may overcome the initial monetary drawback. However, an ASIC does not provide flexibility, i.e. it cannot be used to perform any tasks that were not considered when designing it, and changes of the initial task specification/implementation are not possible without a rather costly re-design. Depending on the projected work area (e.g. selling volume, required possibility for upgrades, reusability for further products etc.), GPPs or ASICs may be used.

### 1.1 Application Specific Instruction Set Processors

The term 'ASIP' (Application Specific Instruction Set Processor) was introduced in the early 1990s and denoted then processors that are application specific. They provide an alternative to GPPs and ASICs when designing an embedded system as they – to some degree – combine both approaches. Designing an ASIP involves analyzing (e.g. profiling) an application, a set of applications, or even a whole application domain (e.g. multi-media) and then creating an instruction set that performs very efficient for that application domain compared with a GPP. The implementation of this instruction set extension correspond to ASIC parts that are dedicated to a particular application and that are embedded into to core of a GPP. The application can use these ASIC parts by so-called Special Instructions (SIs). An ASIP may provide the same functionality as a GPP, but depending on the optimization targets, also parts of the GPP functionality (e.g. a floating-point unit) may be removed, thus potentially reducing the flexibility. Altogether, an ASIP provides a trade-off between GPPs and ASICs. Since the late 1990s / early 2000s, the term ASIP is far more expanded. Since major vendors like Tensilica [Tena], ARC [ARC], CoWare [CoW], etc. offer their tool suites and processors cores, the user can now create a very specific instruction set (instead of buying/licensing a predetermined one) that is tailor-made for a certain application. Typically, these tool suites come with a whole set of retargetable tools such that code can easily be generated for that specific extensible processor. As a result, extensible processors are more efficient than the first generation of ASIPs.

Nowadays, the landscape of embedded applications is rapidly changing and it can be observed that today's embedded applications are far more complex and offer a far wider set of functionality than a decade ago. This makes it increasingly difficult to estimate a system's behavior sufficiently accurate at design time. In fact, after exploration of complex real world embedded applications (most of them from the multimedia domain) it became apparent that it is hard or even impossible to predict the performance and other criteria accurately during design time. Consequently, the more critical decisions are fixed during design time, the less flexible an embedded processor can react to non-predictable application behavior. This not only results in a reduced efficiency but also leads to an unsatisfactory behavior when it comes to the absolute design criteria 'performance' and 'power consumption'. However, the ASIP approach assumes that customizations are undertaken during design time with little or no adaptation possible during run time. Additionally, for large applications that feature many diverse computational hot spots and not just a few exposed ones, current ASIP concepts struggle. According our studies with truly large and inherently diverse applications, customization for many hot spots introduces a non-negligible overhead and may significantly bloat the initial small processor core, because rather many different SIs need to be provided and implemented. Then, a designer needs to answer the question whether more powerful processor architectures would not have been the better choice. Since often only one hot spot is executed at a certain time, the major hardware resources reserved for other hot spots are idling. This indicates an inefficiency that is an implication of the extensible processor paradigm.

### 1.2 Reconfigurable Processors

Reconfigurable computing provides adaptivity by using a fabric that can be reconfigured at run time (see Section 2.2). This reconfigurable fabric can be used to implement application-specific accelerators, similar to those that are used by ASIPs. Great efforts were spend in investigating how such a reconfigurable fabric can be connected with a processor and used by an application efficiently. Recent approaches allow coupling the reconfigurable fabric into to the pipeline of the processor as reconfigurable functional units (RFUs). They allow providing implementations of multiple SIs (like the SIs that are developed and used for ASIPs), by loading reconfigurable accelerators into the RFUs. However, the RFUs provide the conceptual advantage that they can be reconfigured and thus it is not predetermined which SI implementations shall be available in the RFUs at which time. Therefore, such a reconfigurable processor is no longer specific for a particular application or application domain. Even after the reconfigurable processor is fabricated and deployed, the reconfigurable accelerators can be modified (similar to the above-discussed firmware update) to support extended application standards and even new application domains. This is done by providing modified or additional configuration data that is used to reconfigure the RFUs. This increases the flexibility in comparison with ASIPs as now the software and parts of the hardware can be changed at run time. Additionally, the application-specific reconfigurable accelerators provide the efficiency of an ASIC implementation. Therefore, reconfigurable processors present a promising trade-off between ASICs and GPPs that goes beyond the concept of ASIPs.

However, the process of reconfiguration also comes with some drawbacks. Performing a reconfiguration is a rather slow process (multiple milliseconds) and thus the potential benefit of run-time reconfiguration may be diminished. If an application requires rather few SIs and all of them fit into the RFUs at the same time, then the reconfiguration overhead only occurs when the application starts, i.e. all accelerators are reconfigured into the RFUs once. In this case, the reconfiguration overhead will typically amortize over time. However, if a more complex application demands more SIs than fit into the RFUs at the same time, then frequent run-time reconfigurations of the RFUs are required to exploit the performance of a reconfigurable processor maximally. In such a case, the overall application performance may be affected by the reconfiguration time. Actually, when an SI implementation provides more parallelism, then this leads to larger area requirements and the reconfiguration time becomes correspondingly longer. In general: a trade-off between provided parallelism and reconfiguration overhead needs to be determined. Here, the performance of an ASIP is not bound by the parallelism of an SI implementation, but rather its area efficiency is bound by it, because SI implementations that provide more parallelism leads to a larger ASIP footprint.

Another important aspect of reconfigurable processors is that, even though the hardware can be reconfigured at run time, typically it is determined at compile time 'what' shall be reconfigured and 'when' the reconfiguration shall be performed. Certainly, this limits the run-time adaptivity, as the deployment of the run-time adaptive RFUs is predetermined at compile time. However, run-time adaptivity is important to use the RFUs most efficiently. For instance, our exploration of real world applications points out that the execution time of some computational hot spots may highly depend on input data. As this input data (e.g. an input video from camera) is not known at compile time, it cannot be predicted, which out of multiple hot spots in an application will be executed for how long? However, this information affects, which application-specific accelerators will provide which performance improvement for the overall application execution. Still, the decision which accelerators shall be reconfigured to the RFUs is determined at compile time, i.e. without the demanded run-time knowledge. Given that not all accelerators fit to the RFUs at the same time, the full performance potential cannot be exploited. Especially in multi-tasking scenarios, it is typical that not all demanded accelerators fit to the RFUs, because they need to be shared among the executing tasks. Often it is not even known at compile time, which applications will execute at the same time. For instance, if a user downloads and starts additional applications on his cell phone or handheld device, then it is impossible to consider all potential execution scenarios when compiling a particular application. Therefore, it is not known which share of the RFUs is available for a particular application and thus, the design and implementation of SIs cannot be optimized for it. A concept and strategy to shift these decisions to a run-time system that is aware of the run-time specific scenario (i.e. which applications execute and which input data they process) can improve the efficiency of run-time reconfigurable processors significantly.

#### **Summary of Reconfigurable Processors:**

Performance and efficiency are key targets already for today's embedded systems and thus in particular for embedded processors. Reconfigurable processors can be adapted to different applications and application domains after fabrication without redesign, which provides a fast time-to-market and reduced non-recurring engineering cost in comparison with ASIPs. However, their performance may be limited by the reconfiguration overhead and – due to compile-time determined reconfiguration decisions – they do not exploit their full potential for run-time adaptivity. Especially compile-time unpredictable scenarios would benefit from improved adaptivity. For instance, the execution time of a computational hot spot may depend on input data, and the utilization of the RFUs depends on the number and priority of the executing tasks. These are the major challenges for future embedded processors that have to face rather complex applications, various application domains, and compile-time unpredictable scenarios, e.g. in cell phones or handheld devices.

### 1.3 Thesis Contribution