## **Architectures for Adaptive Low-Power Embedded Multimedia Systems**

zur Erlangung des akademischen Grades eines

## Doktors der Ingenieurwissenschaften

der Fakultät für Informatik

Karlsruhe Institute of Technology (KIT)

(The cooperation of the Universität Fridericiana zu Karlsruhe (TH) and the national research center of the Helmholtz-Gemeinschaft)

#### genehmigte

#### **Dissertation**

von

### **Muhammad Shafique**

Tag der mündlichen Prüfung: 31.01.2011

Referent: Prof. Dr.-Ing. Jörg Henkel, Karlsruhe Institute of Technology (KIT),

Fakultät für Informatik, Lehrstuhl für Eingebettete Systeme (CES)

Korreferent: Prof. Dr. Samarjit Chakraborty, Technische Universität München (TUM),

Fakultät für Elektrotechnik und Informationtechnik, Lehrstuhl für Realzeit-

Computersysteme (RCS)

Muhammad Shafique Adlerstr. 3a 76133 Karlsruhe Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Muhammad Shafique

## **Acknowledgements**

I would like to present my cordial gratitude to my advisor Prof. Dr. Jörg Henkel for his erudite and invaluable supervision with sustained inspirations and incessant motivation. He guided me to explore the challenging research problems while giving me the complete flexibility, which provided the rationale to unleash my ingenuity and creativity along with an in-depth exploration of various research issues. His encouragement and meticulous feedback wrapped in constructive criticism helped me to keep the impetus and to remain streamlined on the road of research that resulted in the triumphant completion of this work.

I am also grateful to my co-advisor Prof. Dr. Samarjit Chakraborty for his erudite feedback and profound discussion on my research work. Furthermore, I will present my gratitude to (in alphabetical order) Dr. Jian-Jia Chen, Prof. Dr. Ralf H. Reussner, Prof. Dr. Peter Sanders, Prof. Dr. Mehdi B. Tahoori, and Prof. Dr. Walter F. Tichy for their valuable feedback during the *Professorenrunde* phase.

I will present my special thanks to my colleague and project partner Dr. Lars Bauer for his technical discussions on various reconfigurable computing aspects and continuous support during the paper submissions. He has always been very critical with me in scrutinizing the research issues to deliver a thorough and quality work. Without him, the work of this quality would have been exceptionally difficult.

I would like to pay my thanks to all of the colleagues from the Chair for Embedded Systems (CES) for their discussions and feedback. In particular, I want to thank (in alphabetical order): Waheed Ahmed, Mohammad Abdullah Al Faruque, Lars Bauer, Talal Bonny, Thomas Ebi, Artjom Grudnitsky, Florian Kaiser, Semeen Rehman, and Bruno Zatt. In the last six months of my thesis writing, especially Semeen Rehman and Bruno Zatt provided consistent support in managing my workload and sharing their food, that was a great help in keeping me focused to timely finish my thesis. I also want to thank my Master students (especially Bastian Molkenthin and Florian Kriebel) whom I supervised in the scope of this thesis. Furthermore, I want to acknowledge the support of secretaries and technicians to provide a good working environment.

I am also grateful to the Higher Education Commission of Pakistan (HEC) and Deutscher Akademischer Austausch Dienst (DAAD) for financially supporting my research work.

My utmost gratitude to Mr. Azeemullah who motivated and encouragement me throughout my Ph.D. studies. At the time of each failure, he was there to fuel my energies to perform and deliver even much better than earlier and to constantly improve my work.

Finally, I would like to pay my deepest gratitude to my parents (Muhammad Siddique Wahlah and Razia Sultana) and my siblings (Anwar-us-Saeed, Riffat Shahid, Tasneem Kauser, Muhammad Aqeel Wahlah, Naseem Kauser) for their unconditional love, never-ending support, sincere prayers, and exceptional sacrifices throughout my Ph.D. studies and since ever. My father saw the dream of my Ph.D. and I am grateful to my ex-team lead Dr. Jamil Raza who ignited the fire inside me (during my job at Streaming Networks Pvt. Ltd.) to make this dream come true.

I dedicate this thesis to all of my family members and my advisor Prof. Jörg Henkel.

# "Great things cast shadows. Imagination and creativity are the essence of research." Jörg Henkel

### **List of Own Publications Included in This Thesis**

#### **Transactions/Journals (blind peer reviewed)**

[T.1] M. Shafique, L. Bauer, J. Henkel, "Optimizing the H.264/AVC Video Encoder Application Structure for Reconfigurable and Application-Specific Platforms", Journal of Signal Processing Systems (JSPS), volume 60, issue 2, pp. 183-210, August 2010 (online-published November 2008).

#### **Conferences (double-blind/blind peer reviewed)**

- [C.1] M. Shafique, L. Bauer, J. Henkel, "Selective Instruction Set Muting for Energy-Aware Adaptive Processors", IEEE/ACM 28<sup>th</sup> International Conference on Computer-Aided Design (ICCAD'10), San Jose, California, USA, November 2010. Nominated for the IEEE/ACM WILLIAM J. MCCALLA ICCAD Best Paper Award 2010.

- [C.2] M. Shafique, L. Bauer, J. Henkel, "enBudget: A Run-Time Adaptive Predictive Energy-Budgeting Scheme for Energy-Aware Motion Estimation in H.264/MPEG-4 AVC Video Encoder", IEEE/ACM 13<sup>th</sup> Design Automation and Test in Europe Conference (DATE'10), Dresden, Germany, pp. 1725-1730, March 2010.

- [C.3] M. Shafique, B. Molkenthin, J. Henkel, "An HVS-based Adaptive Computational Complexity Reduction Scheme for H.264/AVC Video Encoder using Prognostic Early Mode Exclusion", IEEE/ACM 13<sup>th</sup> Design Automation and Test in Europe Conference (DATE'10), Dresden, Germany, pp. 1713-1718, March 2010.

- [C.4] M. Shafique, L. Bauer, J. Henkel, "REMiS: Run-time Energy Minimization Scheme in a Reconfigurable Processor with Dynamic Power-Gated Instruction Set", IEEE/ACM 27<sup>th</sup> International Conference on Computer-Aided Design (ICCAD'09), San Jose, California, USA, pp. 55-62, November 2009.

- [C.5] M. Shafique, B. Molkenthin, J. Henkel, "Non-Linear Rate Control for H.264/AVC Video Encoder with Multiple Picture Types using Image-Statistics and Motion-Based Macroblock Prioritization", IEEE 16th International Conference on Image Processing (ICIP'09), Cairo, Egypt, pp. 3429-3432, November 2009.

- [C.6] M. Shafique, L. Bauer, J. Henkel, "A Parallel Approach for High Performance Hardware Design of Intra Prediction in H.264/AVC Video Codec", IEEE/ACM 12<sup>th</sup> Design Automation and Test in Europe Conference (DATE '09), Nice, France, pp. 1434-1439, April 2009.

- [C.7] M. Shafique, L. Bauer, J. Henkel, "3-Tier Dynamically Adaptive Power-Aware Motion Estimator for H.264/AVC Video Encoding", ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED'08), Bangalore, India, pp. 147-152, August 2008.

#### Workshops (blind peer reviewed)

[W.1] M. Shafique, L. Bauer, J. Henkel, "An Optimized Application Architecture of the H.264 Video Encoder for Application Specific Platforms", 5<sup>th</sup> IEEE Workshop on Embedded Systems for Real-Time Multimedia (ESTIMedia '07), Salzburg, Austria, pp. 119-124, October 2007.

## List of Supervised Student Projects that Contributed to the Simulation, Prototype, and Encoder Demonstration

#### **Master Theses (Diplomarbeiten)**

- [D.1] Bastian Molkenthin "Development of a Power-Aware Rate Controller for H.264 Video Encoder". (Received the Forschungszentrum Informatik Award for Best Master Thesis)

- [D.2] Weiwei Cheng "Simulation und Messung des Energieverbrauchs eines Rekonfigurierbaren Eingebetteten Prozessors".

#### **Semester Theses (Studienarbeiten)**

- [S.1] Orcun Tüfek, "Developing Entropy Coding Framework and Optimized Hardware Accelerators for CAVLC in H.264 Video Encoder".

- [S.2] Saraswathi Devi Thupakula "Porting and Optimizing the Functional Blocks of H.264 Video Encoder on a VLIW-based Digital Signal Processor".

- [S.3] Florian Kriebel "Developing Special Instructions and Hardware Accelerators for Multimedia and Communication Application Suites Targeting Dynamically Reconfigurable Processors".

## **Abstract**

The continuously increasing user demands for advanced services lead to the evolution of new multimedia standards. As a result the next generation mobile multimedia applications exhibit high complexity and consume high energy to fulfill the end-user requirements. This stimulates the need for high-performance *embedded multimedia systems with low power/energy consumption*. Besides the context-aware processing in the emerging multimedia standards, the need for user-interactivity introduces a new dimension of *runtime adaptivity* to the overall system requirements in order to react to the run-time changing scenarios (e.g., quality and performance constraints).

State-of-the-art multimedia solutions typically employ heterogeneous multimedia Multi-Processor System-on-Chip (MPSoC) that integrate several programmable processors, domain-specific weakly programmable co-processors, and application-specific hardware accelerators. The selection of cores in an MPSoC is determined at design time depending upon the requirements of a certain set of applications. Therefore, such an MPSoC does not provide the demanded efficiency when executing applications from different domains. Moreover, with a change in the application standard (e.g., a different video encoding) the currently-used MPSoC becomes obsolete (as it may not fulfill the required performance and power design constraints for the end-product). Therefore, when using state-of-the-art multimedia embedded processors, the performance or power constraints may be achieved in a certain context, but the inability to react to the above-mentioned uncertainties (i.e., changing standards, unpredictable scenarios, and application behavior) and the resulting efficiency issues remain. A more efficient approach to target these issues is dynamically reconfigurable processor that embeds a reconfigurable fabric within a core pipeline. These processors provide a high adaptivity and flexibility (due to their hardware reconfigurability and programmability) combined with the performance and efficiency of dedicated hardware accelerators (by exploiting a high degree of parallelism using an embedded FPGA). Previous approaches in reconfigurable processors have mainly concentrated on improving the performance by reconfiguring application-specific hardware accelerators at run time to meet applications' demands and constraints. This reconfiguration process may consume a noticeable amount of energy. Consequently, the major shortcoming of these reconfigurable processors is their high energy consumption compared to ASICs and lack of efficient energy management features. Moreover, with the evolution of sub-micron fabrication technologies, the consideration of leakage power/energy has become imperative in the energy-aware design of reconfigurable processors.

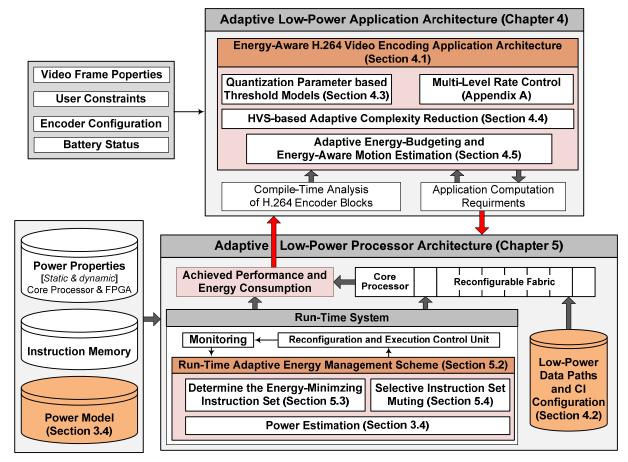

The **goals** of this thesis are to exploit the available potential of energy reduction and to achieve high energy efficiency while meeting the performance constraint and keeping the video quality degradation unnoticeable, under run-time varying scenarios (due to changing video properties, available energy resources, user-defined constraints etc.). Therefore, adaptive energy management needs to be considered *jointly at both processor architecture and application architecture levels*, such that both hardware and software adapt together in order to react to the design-/compile-time unpredictable scenarios.

In this thesis concept, strategies, and implementations are developed targeting both processor and application architectures that enable run-time configurability of energy consumption and video quality for adaptive low-power embedded multimedia systems.

1) Low-power Processor Architecture: In order to enable the run-time adaptivity at the processor level, dynamically reconfigurable processors are deployed as the target platform. State-of-the-art low-power schemes employ power-shutdown considering the state/usage of the hardware (i.e., a hardware-oriented shutdown) to reduce the leakage power/energy. When targeting reconfigurable processors, it cannot be determined at compile time which parts of the instruction set will be reconfigured on which part of the reconfigurable fabric. Therefore, unlike state-of-the-art, the proposed work raises the abstraction level of shutdown to the instruction set level. It enables a far higher potential for leakage

energy savings. At the processor level, a run-time adaptive energy management scheme is employed that performs the following steps.

- a) Determine an Energy Minimizing Instruction Set: A tradeoff between leakage, dynamic, and reconfiguration energy is investigated and an energy-minimizing instruction set is selected for a dynamically reconfigurable processor under run-time varying performance and area constraints. To enable this, a comprehensive power model for the reconfigurable processors was developed, which is based on power measurements. The benchmarks for two state-of-the-art reconfigurable processors (Molen [PBV07, VWG+04] and RISPP [BSH08b, BSH08c, BSKH07]) demonstrate an energy reduction of more than 40% compared to when not using the proposed scheme.

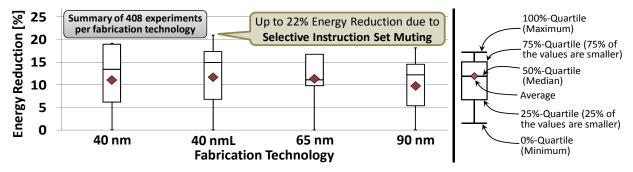

- b) Selective Instruction Set Shutdown: A decision about the shutdown mode is determined for the temporarily unused subset of the instruction set by considering the requirements and execution lengths of the compute-intensive parts of an application (i.e., the execution context of an application). It is determined at run time which subset of instruction set should be put into which muting mode at which time by evaluating at run time the possible associated energy benefit (a joint function of leakage, dynamic, and reconfiguration energy). In addition to the above-mentioned energy savings, a further 30% energy reduction is achieved.

The information about the actual energy consumption is transmitted to the application layer for application-level energy management.

- 2) **Low-power Application Architecture:** Video coding is the key component of the current and emerging embedded multimedia systems as it consumes a significant amount of processing time and energy. Therefore, at the application level, the adaptivity and energy reduction are demonstrated using an advanced video encoder (like H.264). An optimized application architecture is proposed for video encoders targeting the reconfigurable processors. To reduce the computation requirements of different processing blocks of a low-power video encoder at run time, different algorithms have been developed. These algorithms address the following issues:

- Need for an analysis of spatial and temporal video properties with consideration of important Human-Visual System properties to categorize different video frames and their Macroblocks.

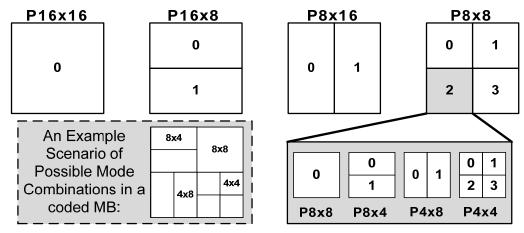

- Adaptive complexity reduction to reduce energy requirements of encoder by excluding improbable

coding modes from the mode-decision process. It solves the issue of choosing the final coding

mode out of hundreds of possible combination (without exhaustively searching the design space) by

considering the spatial and temporal video properties.

- To adaptively predict the energy quota for the energy-aware Motion Estimation (that may consume up to 65% of the total encoding energy). It chooses a certain Motion Estimation configuration for different video frames considering the available energy, video frame characteristics, and user-defined coding constraints while keeping a good video quality.

The proposed low-power video encoder provides a dynamic energy reduction of more than 60% with an insignificant quality loss (0.2dB). For the blocks that are fixed by the standard and adaptivity is not possible, low-power hardware accelerators were designed.

In addition to the above-discussed scientific contribution, following has been developed in the scope of this work:

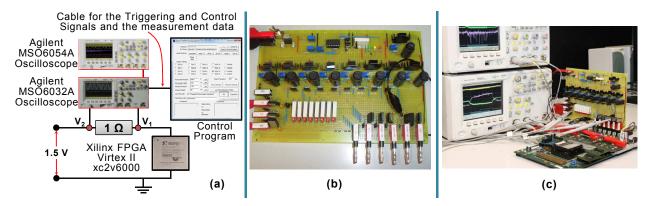

- A complete power-measurement setup for dynamically reconfigurable processors that consists of a power supply board, two oscilloscopes, an FPGA based prototyping board, and a control program (running on a PC) for capturing the measurements from the oscilloscopes.

- A complete H.264 video encoder application with the proposed run-time algorithms and low-complexity data flow. The in-house developed H.264 encoder is currently executing on an in-house dynamically reconfigurable processor prototype, Texas Instruments' multimedia processor, and laptop/desktop PCs.

- A video analysis tool with an easy-to-use graphical user interface for quick and in-depth analysis of video sequences.

## Zusammenfassung

Die kontinuierlich steigenden Nutzerwünsche nach fortgeschrittenen Diensten führen zur Evolution neuer Multimediastandards. Als eine Folge besitzen die mobilen Multimediaanwendungen der nächsten Generation eine hohe Komplexität und konsumieren eine große Menge an Energie, um die Anforderungen der Endbenutzer zu erfüllen. Dies stimuliert den Bedarf nach hochperformanten eingebetteten Multimediasystemen mit geringem Leistungs-/Energiebedarf. Neben den kontextbewussten Berechnungen in den aufkommenden Multimediastandards, führt der Bedarf nach Benutzerinteraktivität zu einer neuen Dimension von Laufzeitadaptivität für die gesamten Systemanforderungen, um auf Szenarien reagieren zu können, die sich zur Laufzeit ändern (z.B. Qualitäts- und Performanzanforderungen).

Dem Stand der Technik entsprechende Multimedialösungen verwenden heterogene Multimedia-Mehrkernprozessor Systeme (MPSoC), die mehrere programmierbare Prozessoren, domänenspezifische schwach programmierbare Koprozessoren und anwendungsspezifische Hardwarebeschleuniger integrieren. Die Auswahl an Kernen in einem MPSoC wird zur Entwurfszeit abhängig von den Anforderungen einer gewissen Menge an Anwendungen bestimmt. Deswegen liefert solch ein MPSoC nicht die geforderte Effizienz, wenn Anwendungen einer anderen Domäne ausgeführt werden. Des Weiteren wird das momentan eingesetzte MPSoC bei einer Änderung des Anwendungsstandards (z.B. Videokodierung) geforderten Performanzeine anderen obsolet (weil es die Leistungsverbrauchsanforderungen des Endprodukts möglicherweise nicht mehr erfüllen kann). Deswegen können bei Verwendung von eingebetteten Multimediaprozessoren des Stands der Technik die Performanz- oder Leistungsverbrauchsanforderungen vielleicht in einem bestimmten Kontext erreicht werden, aber die Unfähigkeit auf die oben genannten Unsicherheiten (d.h. sich ändernde Standards, unvorhersagbare Szenarien und Anwendungsverhalten) reagieren zu können und die daraus resultierenden Effizienzprobleme bleiben. Ein effizienterer Ansatz um diese Probleme anzugehen ist ein dynamisch rekonfigurierbarer Prozessore, der eine rekonfigurierbare Fläche in eine Kernpipeline integriert. Diese Prozessoren liefern eine hohe Adaptivität und Flexibilität (durch ihre Hardwarerekonfigurierbarkeit und Programmierbarkeit), kombiniert mit der Performanz und Effizienz Hardwarebeschleunigern (durch die Ausnutzung eines hohen Grades an Parallelität durch den eingebetteten FPGA). Frühere Ansätze bei rekonfigurierbaren Prozessoren haben sich darauf konzentriert, die Performanz durch die Rekonfiguration von anwendungsspezifischen Hardwarebeschleunigern zur Laufzeit zu erhöhen, um die Bedürfnisse und Anforderungen der Anwendungen zu erfüllen. Diese rekonfigurierbaren Prozessoren können eine beachtliche Menge an Energie verbrauchen. Folgerichtig ist ein Hauptnachteil dieser rekonfigurierbaren Prozessoren ihr hoher Energieverbrauch im Vergleich zu ASICs und ihr Mangel an Energieverwaltungsmöglichkeiten. Des Weiteren ist durch die Evolution von sub-micron Herstellungstechnologien die Berücksichtigung von Leckströmen ein Gebot für den energiebewussten Entwurf von rekonfigurierbaren Prozessoren geworden.

Das **Ziel** dieser Doktorarbeit ist es, das vorhandene Potential zur Energieverbrauchsreduzierung zu nutzen und eine hohe Energieeffizienz zu erzielen, während bei Situationen die zur Laufzeit variieren (durch sich ändernde Videoeigenschaften, die verfügbaren Energieressourcen und anwenderdefinierte Anforderungen etc.) die Performanzanforderung eingehalten und die Verringerung der Videoqualität unbemerkbar gehalten wird. Dafür muss eine adaptive Energieverwaltung sowohl bei der Prozessor-, wie auch bei der Anwendungsarchitektur berücksichtigt werden, so dass sich Hardware und Software gemeinsam anpassen, um auf Situationen zu reagieren, die zur Entwurfs- und Übersetzungszeit nicht vorhergesagt werden können.

In dieser Doktorarbeit werden Konzepte, Strategien und Implementierungen sowohl für die Prozessorwie auch die Anwendungsarchitektur entwickelt, welche die Laufzeitkonfigurierbarkeit von

Energieverbrauch und Videoqualität für adaptive low-power eingebettete Multimediasysteme ermöglichen.

- 1) Low-power Prozessorearchitektur: Um die Laufzeitadaptivität auf der Ebene des Prozessors möglich zu machen, werden dynamisch rekonfigurierbare Prozessoren als Zielplattform verwendet. Dem Stand der Technik entsprechende low-power Schemata verwenden Power-Abschaltung unter Berücksichtigung vom Status und dem Zustand der Hardware (d.h. eine hardwareorientierte Abschaltung), um den durch Lechströme verursachten Leistungs-/Energieverbrauch zu verringern. Bei rekonfigurierbaren Prozessoren kann nicht zur Übersetzungszeit festgelegt werden, welche Teile des Befehlssatzes in welchen Bereich der rekonfigurierbaren Hardware rekonfiguriert werden. Deswegen hebt die vorgestellte Arbeit im Gegensatz zum Stand der Technik den Abstraktionsgrad auf ein Abschalten auf der Befehlssatzebene. Dies eröffnet ein deutlich größeres Potential zum Reduzieren der Leckströme. Auf der Prozessorebene wird ein laufzeitadaptives Energieverwaltungssystem eingesetzt, das die folgenden Schritte durchführt.

- c) Bestimmung eines energieminimierenden Befehlssatzes: Ein Kompromiss zwischen Leckströmen, dynamischen- und Rekonfigurationsenergieverbrauch wird untersucht und ein energieminimierender Befehlssatz wird für einen dynamisch rekonfigurierbaren Prozessor unter zur sich zur Laufzeit ändernden Performanz- und Flächenbedingungen ausgewählt. Um dies zu ermöglichen wurde ein umfassendes Powermodell für den rekonfigurierbaren Prozessor entwickelt, das auf Leistungsverbrauchsmessungen basiert. Die Benchmarks für dem Stand der Technik entsprechende rekonfigurierbare Prozessoren (Molen [PBV07, VWG+04] und RISPP [BSH08b, BSH08c, BSKH07]) demonstrieren eine Verringerung des Energieverbrauches um mehr als 40% im Vergleich zum Betrieb ohne das vorgeschlagene System.

- d) Ausgewählte Befehlssatzabschaltung: Eine Entscheidung über den Abschaltungsmodus wird für die temporär nicht benutze Teilmenge des Befehlssatzes getroffen, wobei die Anforderungen und die Ausführungslänge der rechenintensiven Teile einer Anwendung berücksichtigt werden (d.h., der Ausführungskontext einer Anwendung). Es wird zur Laufzeit bestimmt, welche Teilmenge des Befehlssatzes zu welcher Zeit in welchen Abschaltungsmodus versetzt werden soll, indem zur Laufzeit die möglichen assoziierten Energievorteile (eine gemeinsame Funktion aus Leckstrom, dynamischer- und Rekonfigurationsenergie) evaluiert wird. Zusätzlich zu den oben genannten Energieeinsparungen wird eine weitere Energiereduktion um 30% erreicht.

Die Informationen über den momentanen Energieverbrauch werden für die Energieverwaltung auf der Anwendungsschicht in die Anwendungsebene transportiert.

- 2) Low-power Anwendungsarchitektur: Videokodierung ist die Schlüsselkomponente für momentane und entstehende eingebettete Multimediasysteme, weil sie einen signifikanten Teil der Rechenzeit und der Energie verbraucht. Deswegen werden Adaptivität und die Energieeinsparungen auf Seiten der Anwendungsarchitektur durch einen fortgeschrittenen Videokodierer (wie H.264) demonstriert. Eine optimierte Anwendungsarchitektur für Videokodierer die für rekonfigurierbare Prozessoren ausgelegt ist wird vorgeschlagen. Um die Rechenanforderungen der verschiedenen Rechenblöcke eines low-power Videokodierers zur Laufzeit zu verringern, sind verschiedene Algorithmen entwickelt worden. Diese Algorithmen adressieren die folgenden Probleme:

- Bedarf einer Analyse von räumlichen und zeitlichen Videoeigenschaften unter Berücksichtigung der wichtigen Eigenschaften des menschlichen Sehsystems, um verschiedene Videobilder und deren Makroblöcke zu kategorisieren.

- Adaptive Komplexitätsreduzierung, um den Energieverbrauch durch Ausschluss unwahrscheinlicher Kodierungsmodi aus dem Modusentscheidungsprozess zu verringern. Dies löst das Problem den finalen Kodierungsmodus aus hunderten von möglichen Kombinationen zu wählen (ohne den Entwurfsraum erschöpfend zu durchsuchen), indem räumliche und zeitliche Videoeigenschaften berücksichtigt werden.

- Adaptiv das Energiekontingent für die energiebewusste Bewegungsabschätzung (die bis zu 65% der Gesamtenergie der Enkodierung brauchen kann) vorherzusagen. Dies wählt eine gewisse

Bewegungsabschätzungskonfiguration für verschiedene Videobilder unter Berücksichtigung der verfügbaren Energie, der Videobildcharakteristiken und der nutzerdefinierten Kodierungsanforderungen aus, wobei eine gute Videoqualität gewahrt wird.

Der vorgeschlagene low-power Videokodierer bietet bei einem unbedeutenden Qualitätsverlust (0,2dB) eine Verringerung des dynamischen Energieverbrauchs um mehr als 60%. Für die Blöcke, die durch den Standard festgelegt sind und für die keine Adaptivität möglich ist, wurden low-power Hardwarebeschleuniger entworfen.

Zusätzlich zu dem oben diskutierten wissenschaftlichen Beitrag wurde im Rahmen dieser Doktorarbeit Folgendes entwickelt:

- Eine komplette Umgebung zur Messung des Leistungsverbrauches von dynamisch rekonfigurierbaren Prozessoren, das aus einem Stromversorgungsboard, zwei Oszilloskopen, einem FPGA basierten Prototypen und einem Kontrollprogramm (auf einem PC ausgeführt, um die Messergebnisse der Oszilloskope zu empfangen) besteht.

- Eine komplette H.264 Videokodieranwendung mit den vorgeschlagenen Laufzeitalgorithmen und einem Datenfluss geringer Komplexität. Der intern entwickelte H.264 Kodierer wird momentan auf einem intern entwickelten dynamisch rekonfigurierbaren Prozessorprototypen, einem Multimediaprozessor von Texas Instruments und auf Laptop/Desktop PCs ausgeführt.

- Ein Videoanalyse Tool mit einer leicht zu bedienenden grafischen Benutzerschnittstellt für eine schnelle und gründliche Analyse von Videosequenzen.

## **Contents**

| Acknov  | wledge  | ments                                                    | i      |

|---------|---------|----------------------------------------------------------|--------|

| List of | Own P   | ublications Included in This Thesis                      | V      |

| List of | Superv  | vised Student Projects that Contributed to the Simulatio | n,     |

|         | Pro     | ototype, and Encoder Demonstration                       | vii    |

| Abstr   | act     |                                                          | ix     |

| Zusam   | menfas  | ssung                                                    | xi     |

| Conte   | ents    | •••••••••••••••••••••••••••••••••••••••                  | XV     |

| List of | Figure  | S                                                        | xxi    |

| List of | Tables  |                                                          | xxvii  |

| List of | Algori  | thms                                                     | xxix   |

|         | _       | s and Definitions                                        |        |

|         |         | roduction                                                |        |

| 1.1     |         | Is and Requirements of Advanced Multimedia Systems       |        |

| 1.2     | Trend   | ls and Options for Multimedia Processing                 | 3      |

| 1.3     | Sumn    | nary of Challenges and Issues                            | 6      |

| 1.4     | Thesi   | s Contribution                                           | 6      |

| 1.5     | Thesi   | s Outline                                                | 8      |

| Chapte  | er 2 Ba | ckground and Related Work                                | 11     |

| 2.1     | Video   | Coding: Basics and Terminology                           | 11     |

| 2.2     | The H   | H.264 Advanced Video Codec: A Low-Power Perspective      | 12     |

|         | 2.2.1   | Overview of the H.264 Video Encoder and its Functional   |        |

|         |         | Blocks                                                   | 12     |

|         | 2.2.2   | Low-Power Architectures for H.264/AVC Video Encoder      | 16     |

|         | 2.2.3   | Adaptive and Low-Power Design of the Key Functional E    | Blocks |

|         |         | of the H.264 Video Encoder: State-of-the-art and Their   |        |

|         |         | Limitations                                              | 17     |

| 2.3     | Recor   | nfigurable Processors                                    |        |

|         | 2.3.1   | Fine-Grained Reconfigurable Fabric                       |        |

|         | 2.3.2   |                                                          |        |

|         |         | Power-Shutdown Infrastructure                            |        |

|    |      | 2.3.3   | Custom Instructions (CIs): A Reconfigurable Processor        |      |

|----|------|---------|--------------------------------------------------------------|------|

|    |      |         | Perspective                                                  | . 23 |

|    |      | 2.3.4   | Reconfigurable Instruction Set Processors                    | . 24 |

|    |      | 2.3.5   | Rotating Instruction Set Processing Platform (RISPP)         | . 25 |

|    | 2.4  | Low-I   | Power Approaches in Reconfigurable Processors                | . 32 |

|    | 2.5  | Summ    | nary of Related Work                                         | . 33 |

| Ch | apte | r 3 Ada | aptive Low-Power Architectures for Embedded Multimedia       |      |

|    | -    |         | tems                                                         | . 35 |

|    | 3.1  | Analy   | zing the Video Coding Application for Energy Consumption and |      |

|    |      | Adapt   | ivity                                                        | . 35 |

|    |      | 3.1.1   | Advanced Video Codecs: Analyzing the Tool Set                | . 36 |

|    |      | 3.1.2   | Energy and Adaptivity Related Issues in H.264/AVC Video      |      |

|    |      |         | Encoder                                                      | . 38 |

|    | 3.2  | Energ   | y- and Adaptivity Related Issues for Dynamically             |      |

|    |      |         | figurable Processors                                         |      |

|    | 3.3  | Overv   | iew of the Proposed Architectures and Design Steps           | . 42 |

|    | 3.4  |         | Model for Dynamically Reconfigurable Processors              | 45   |

|    |      | 3.4.1   | Power Consuming Parts of a Computation- and                  |      |

|    |      |         | Communication-Infrastructure in a Dynamically                |      |

|    |      |         | Reconfigurable Processor                                     |      |

|    |      |         | The Proposed Power Model                                     |      |

|    | 3.5  | Summ    | nary of Adaptive Low-Power Embedded Multimedia System        | . 48 |

| Ch | apte | r 4 Ada | aptive Low-Power Video Coding                                | 49   |

|    | 4.1  | H.264   | Encoder Application Architectural Adaptations for            |      |

|    |      | Recon   | figurable Processors                                         | . 49 |

|    |      | 4.1.1   | Basic Application Architectural Adaptations                  | 49   |

|    |      | 4.1.2   | Application Architectural Adaptations for On-Demand          |      |

|    |      |         | Interpolation                                                | . 51 |

|    |      | 4.1.3   | Application Architectural Adaptations for Reducing the       |      |

|    |      |         | Hardware Pressure                                            | . 53 |

|    |      | 4.1.4   | 11                                                           |      |

|    |      |         | Reduced Hardware Pressure.                                   | . 55 |

|    | 4.2  | Design  | ning Low-Power Data Paths and Custom Instructions            | . 57 |

|    |      | 4.2.1   | Designing the Custom Instruction for In-Loop Deblocking      |      |

|    |      |         | Filter                                                       |      |

|    |      | 4.2.2   | Designing the Custom Instructions for Motion Estimation      | 61   |

|    |      | 423     | Designing the Custom Instruction for Motion Compensation     | 61   |

|    |      | 4.2.4   | Area Results for the Custom Instruction of H.264 Encoder     | 62  |

|----|------|---------|--------------------------------------------------------------|-----|

|    | 4.3  | Spatia  | al and Temporal Analysis of Videos Considering Human Visual  |     |

|    |      | Syster  | n                                                            | 63  |

|    |      | 4.3.1   | HVS-Based Macroblock Categorization                          | 67  |

|    |      |         | QP-Based Thresholding                                        |     |

|    | 4.4  | An H    | VS-based Adaptive Complexity Reduction Scheme                | 69  |

|    |      | 4.4.1   | Prognostic Early Mode Exclusion                              | 70  |

|    |      | 4.4.2   | Hierarchical Fast Mode Prediction                            | 71  |

|    |      | 4.4.3   | Sequential RDO Mode Elimination                              | 73  |

|    |      | 4.4.4   | Evaluation of the Complexity Reduction Scheme                | 73  |

|    | 4.5  | Energ   | y-Aware Motion Estimation with an Integrated Energy-         |     |

|    |      | Budge   | eting Scheme                                                 | 77  |

|    |      | 4.5.1   | Adaptive Motion Estimator with Multiple Processing Stages    | 78  |

|    |      | 4.5.2   | enBudget: The Adaptive Predictive Energy-Budgeting Scheme.   | 82  |

|    |      | 4.5.3   | Evaluation of Energy-Aware Motion Estimation with an         |     |

|    |      |         | Integrated Energy-Budgeting Scheme                           | 87  |

|    | 4.6  | Summ    | nary of Low-Power Application Architecture                   | 90  |

| Ch | apte | r 5 Ada | aptive Low-Power Reconfigurable Processor Architecture       | 93  |

|    | _    |         | rational Scenario and Problem Identification                 |     |

|    | 5.2  | Run-T   | Time Adaptive Energy Management with the Novel Concept of    |     |

|    |      | Custo   | m Instruction Set Muting                                     | 95  |

|    |      | 5.2.1   | Concept of Muting the Custom Instructions                    | 95  |

|    |      | 5.2.2   | Power-Shutdown Infrastructure for the Muted Custom           |     |

|    |      |         | Instructions                                                 | 97  |

|    |      | 5.2.3   | Run-Time Adaptive Energy Management                          | 98  |

|    | 5.3  | Deter   | mining an Energy-Minimizing Instruction Set                  | 100 |

|    |      | 5.3.1   | Formal Problem Modeling and Energy Benefit Function          | 100 |

|    |      | 5.3.2   | Algorithm for Choosing CI Implementation Versions            | 102 |

|    |      | 5.3.3   | Evaluation and Results for Energy-Minimizing Instruction Set | 105 |

|    | 5.4  | Select  | tive Instruction Set Muting                                  | 110 |

|    |      | 5.4.1   | Problem Description and Motivational Scenarios               | 111 |

|    |      | 5.4.2   | Operational Flow for Selective Instruction Set Muting        | 112 |

|    |      | 5.4.3   | Analyzing the Energy Benefit Function of Muting              | 114 |

|    |      | 5.4.4   | Hot Spot Requirement Prediction: Computing Weighting         |     |

|    |      |         | Factors for CIs                                              | 115 |

|    |      | 5.4.5   | Evaluation of Selective Instruction Set Muting               | 116 |

|    | 5.5   |         | nary of Adaptive Low-Power Reconfigurable Processor            |       |

|----|-------|---------|----------------------------------------------------------------|-------|

|    |       | Archi   | tecture                                                        | . 118 |

| Cł | napte | r 6 Pov | ver Measurement of the Reconfigurable Processors               | . 119 |

|    | 6.1   | Power   | Measurement Setup                                              | . 119 |

|    | 6.2   | Measu   | uring the Power of Custom Instructions                         | . 120 |

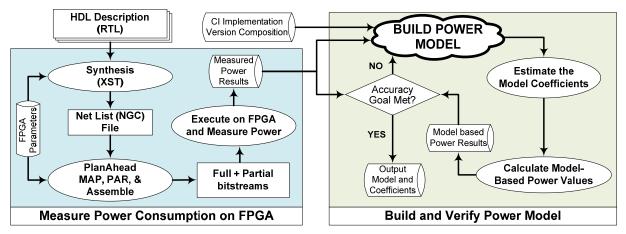

|    |       | 6.2.1   | Flow for Creating the Power Model                              | . 120 |

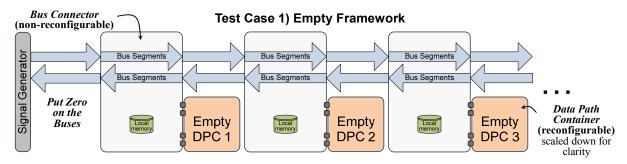

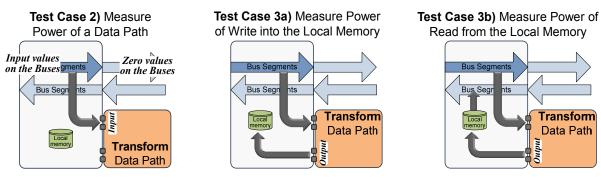

|    |       | 6.2.2   | Test Cases for Power Measurements                              | . 121 |

|    |       | 6.2.3   | Results for Power Measurement and Estimation                   | . 123 |

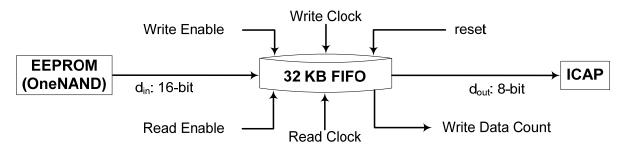

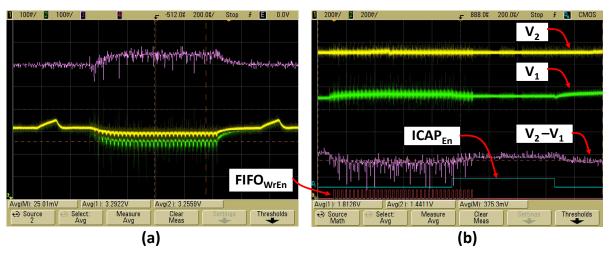

|    | 6.3   |         | uring the Power of the Reconfiguration Process                 |       |

|    |       | 6.3.1   | Power Consumption of EEPROM                                    | . 124 |

|    |       | 6.3.2   | Power Consumption of the Reconfiguration via ICAP              | . 125 |

|    | 6.4   | Summ    | nary of the Power Measurement of the Reconfigurable Processor  | :s125 |

| Cł | napte | r 7 Ber | nchmarks and Results                                           | . 127 |

|    | •     |         | Simulation Conditions and Fairness of the Comparison           |       |

|    | 7.2   |         | ive Low-Power Application Architecture                         |       |

|    |       | 7.2.1   | Comparing Complexity Reduction Scheme to State-of-the-art      |       |

|    |       |         | and the Exhaustive RDO-MD                                      | . 128 |

|    |       | 7.2.2   | Comparing the Energy-Aware Motion Estimation with              |       |

|    |       |         | Integrated Energy Budgeting Scheme to State-of-the-art         | . 131 |

|    | 7.3   | Adapt   | ive Low-Power Processor Architecture                           | . 133 |

|    |       | 7.3.1   | Comparing the Adaptive Energy Management Scheme (without       |       |

|    |       |         | Selective Instruction Set Muting) to RISPP with Performance    |       |

|    |       |         | Maximization [BSH08c]                                          | . 133 |

|    |       | 7.3.2   | Applying the Adaptive Energy Management Scheme (without        |       |

|    |       |         | Selective Instruction Set Muting) to Molen [VWG+04]            |       |

|    |       |         | Reconfigurable Processor                                       | . 134 |

|    |       | 7.3.3   | Comparing the Adaptive Energy Management Scheme (with          |       |

|    |       |         | Selective Instruction Set Muting) to State-of-the-Art Hardware |       |

|    |       |         | Oriented Shutdown                                              |       |

|    | 7.4   | Sumn    | nary of the Benchmarks and Comparisons                         | . 137 |

| Cł | napte | r 8 Coi | nclusion and Outlook                                           | . 139 |

|    | 8.1   | Thesis  | s Summary                                                      | . 139 |

|    | 8.2   | Future  | e Work                                                         | . 142 |

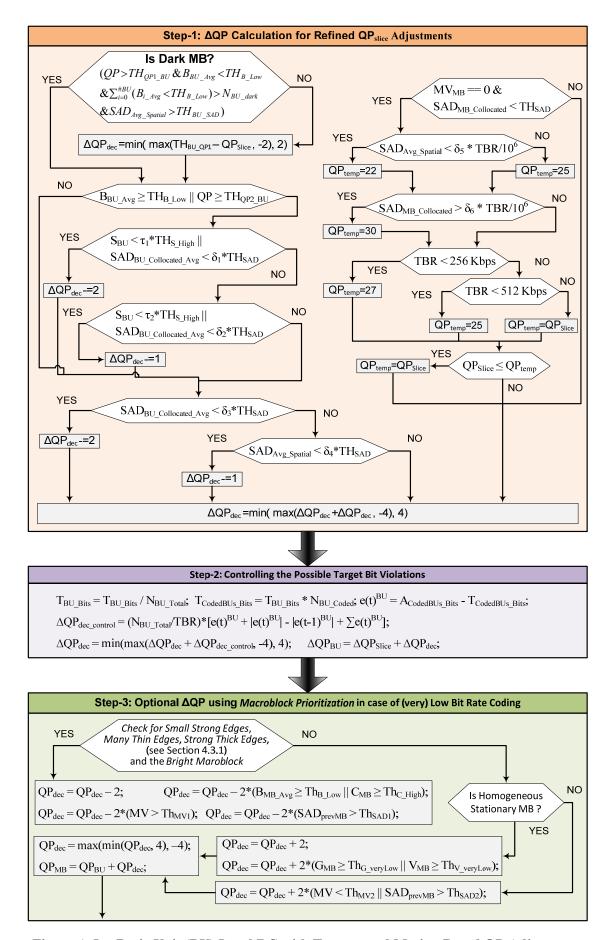

| Ar | pend  | lix A   | A Multi-Level Rate Control                                     | . 145 |

| 1  | _     |         | e Control Algorithm                                            |       |

|    |       |         | roposed Multi-Level Rate Control                               |       |

|    |       | P       |                                                                |       |

| A.3 Evalu    | A.3 Evaluation and Results                               |     |

|--------------|----------------------------------------------------------|-----|

| Appendix B   | Simulation Environment the H.264 Video Encoder           |     |

|              | Demonstration                                            | 155 |

| B.1 Impl     | ementation and Simulation Environment                    | 155 |

| B.2 H.26     | 4 Video Encoder on the RISPP Hardware Prototype          | 157 |

| B.3 H.26     | 4 Video Encoder on the Texas Instruments' DM6437 Digital |     |

| Medi         | a Processor                                              | 158 |

| Appendix C   | The CES Video Analyzer Tool                              | 161 |

| Bibliography |                                                          | 163 |

## **List of Figures**

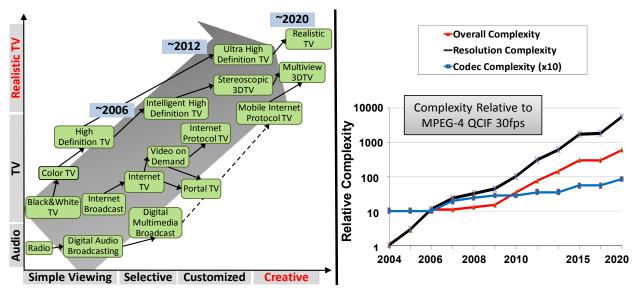

| Figure 1.1:  | (a) Video Services Over Time [Hui10]; (b) Video Complexity Over Time [MBNN10]                                                                                               | 2  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

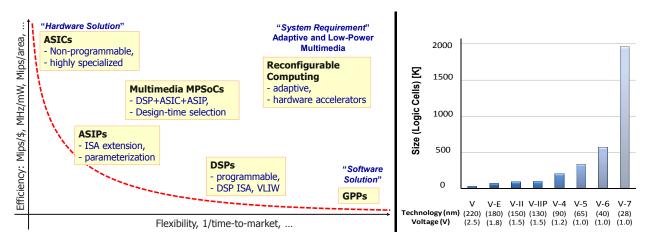

| Figure 1.2:  | (a) Flexibility vs. Efficiency Comparison of Different Architectural Options (inspired from [Hen03]); (b) Evolution Trend of Xilinx Virtex FPGAs [Xil10a]                   | 4  |

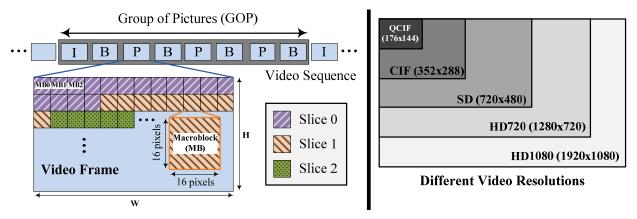

| Figure 2.1:  | An Overview of the Digital Video Structure (showing Group of Pictures, Frame, Slice, MB) and Different Video Resolutions                                                    | 12 |

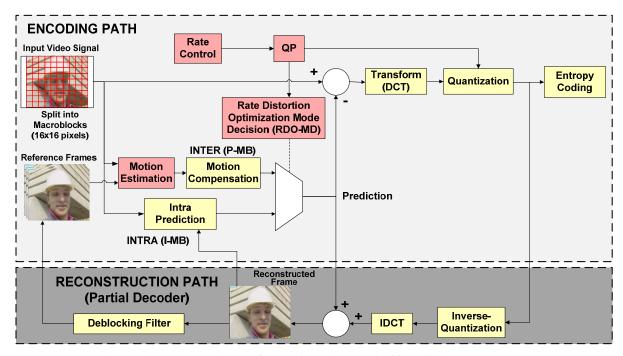

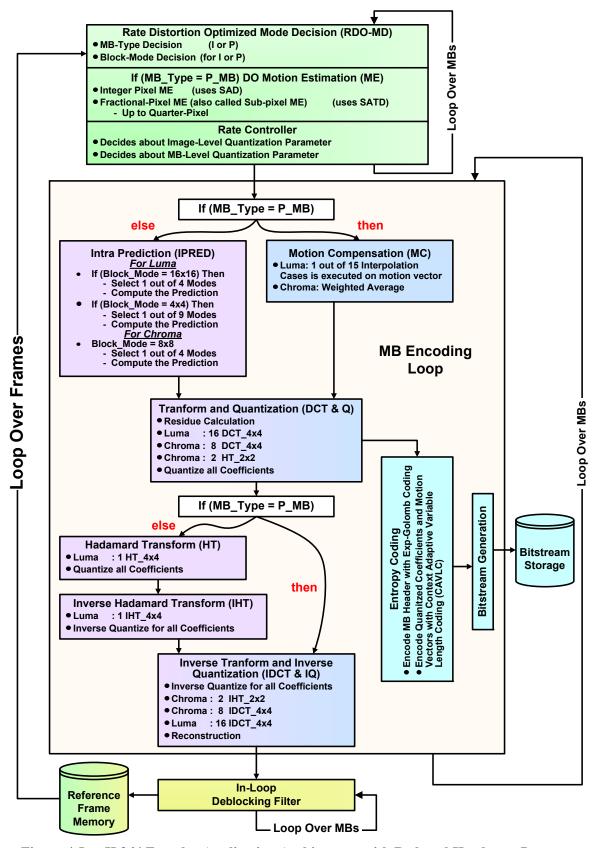

| Figure 2.2:  | Functional Overview of the H.264/AVC Video Encoder                                                                                                                          | 13 |

| Figure 2.3:  | Variable Block Sizes for Inter-Predicted MBs (P-MBs) in H.264/AVC                                                                                                           | 13 |

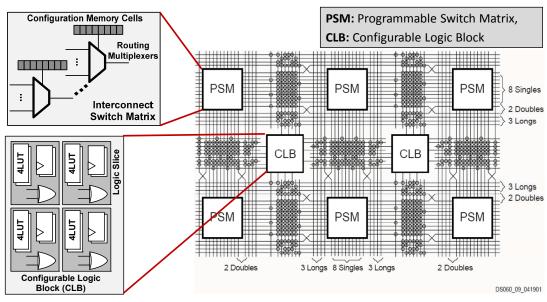

| Figure 2.4:  | A Typical Composition of a Fine-Grained Reconfigurable Fabric with a 2D-Array of CLBs and PSMs along with the Internal Details of a Spartan-3 Tile [Te06, Xil08a]           | 21 |

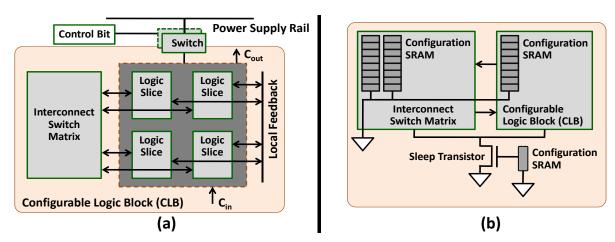

| Figure 2.5:  | State-of-the-Art in Power-Shutdown Infrastructure (a) by [Ge04] (b) by [Te06]                                                                                               | 22 |

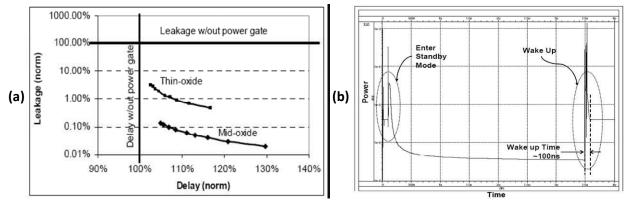

| Figure 2.6:  | (a) Sizing of Thin- & Mid-Oxide Power Gate showing Leakage-Delay Tradeoffs [Te06]; (b) Power Consumption for Activating and Deactivating a single tile [Te06]               | 23 |

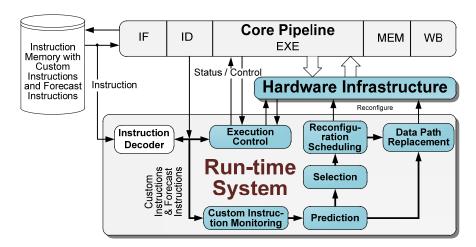

| Figure 2.7:  | Extending a Standard Processor Pipeline towards RISPP and the Overview of the RISPP Run-time System [BSTH07]                                                                | 26 |

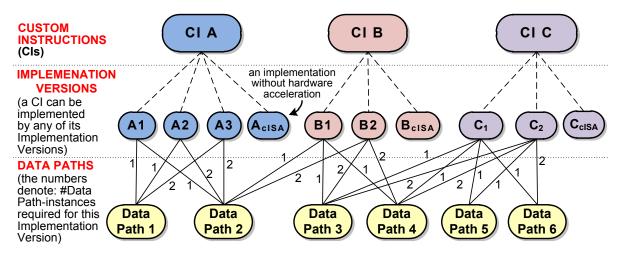

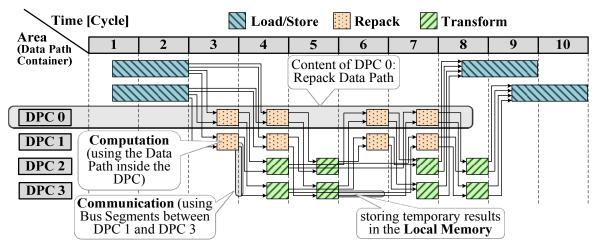

| Figure 2.8:  | Hierarchical Composition of Custom Instructions: Multiple Implementation Versions Exist per Custom Instruction and Demand Data Paths for Realization [BSKH07, BSTH07]       | 27 |

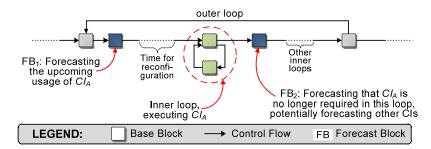

| Figure 2.9:  | Example Control-flow Graph Showing Forecasts and the Corresponding Custom Instruction Executions [Bau09]                                                                    | 30 |

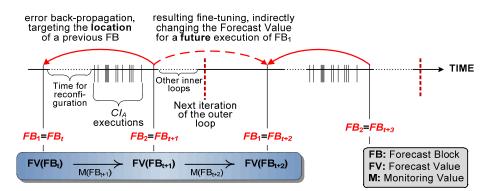

| Figure 2.10: | Execution Sequence of Forecast and Custom Instructions with the Resulting Error Back Propagation and Fine-tuning [Bau09]                                                    | 30 |

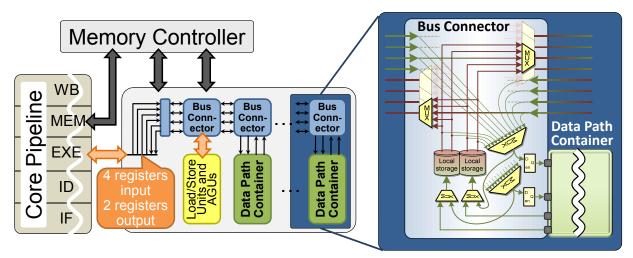

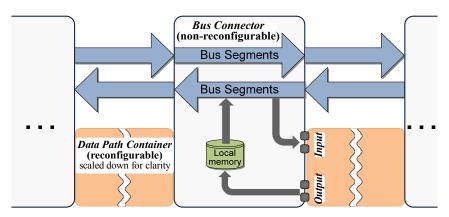

| Figure 2.11: | Overview of the Hardware Infrastructure for Computation (Data Path Container) and Communication (Bus Connector) showing the Internal Composition of a Bus Connector [Bau09] | 31 |

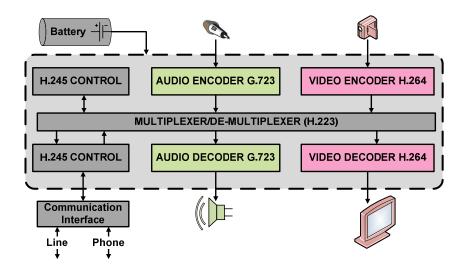

| Figure 3.1:  | Overview of an H.324 Video Conferencing Application with H.264/AVC Codec                                                                                                    | 35 |

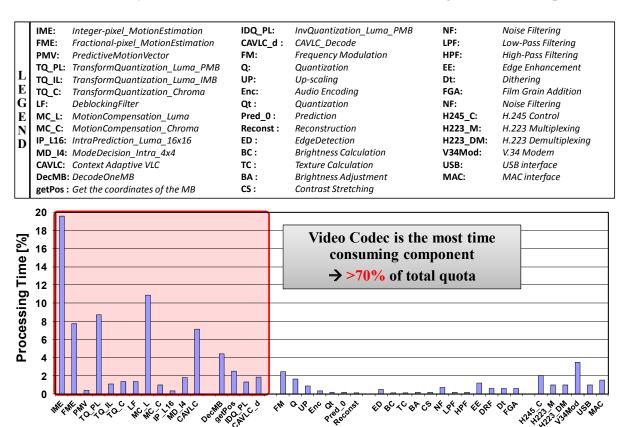

| Figure 3.2:  | Processing Time Distribution of Different Functional Blocks in the H.324 Video Conferencing Application                                                                     | 36 |

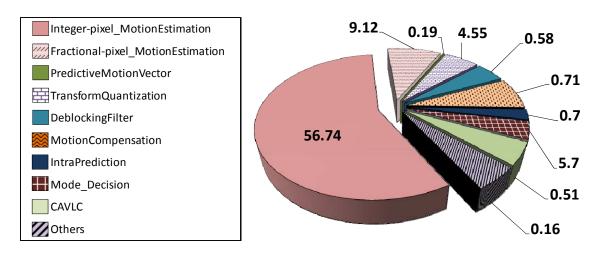

| Figure 3.3:  | Percentage Distribution of Energy Consumption of Different Functional Blocks in the H.264 Video Encoder                                                                     |    |

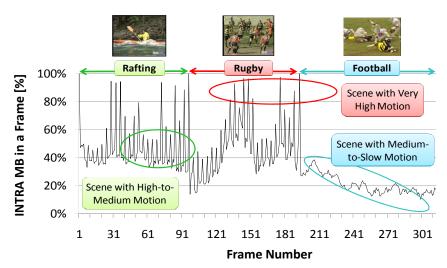

| Figure 3.4:  | Distribution of I-MBs in Slow-to-Very-High Motion Scenes (Test Conditions: Group of Pictures=IPPP, CAVLC, Quantization Parameter = 28, 30fps)       | 40 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.5:  | Overview of the Adaptive Low-Power Application and Processor Architectures                                                                          | 42 |

| Figure 3.6:  | Highlighting Different Steps to be Performed at Design, Compile, and Run Time at both Application and Processor Levels                              | 44 |

| Figure 3.7:  | Power-Relevant Components of the Computation- and Communication Infrastructure to Execute CI Implementation Versions [BSH08a]                       | 46 |

| Figure 3.8:  | Example for a Custom Instruction (CI) Implementation Version                                                                                        | 46 |

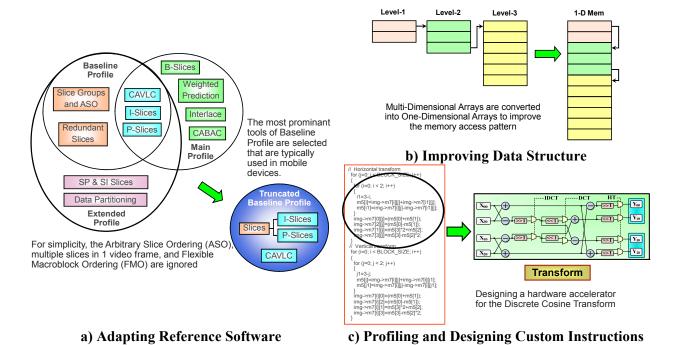

| Figure 4.1:  | Basic Application Architectural Adaptations to Construct the Benchmark Application                                                                  | 50 |

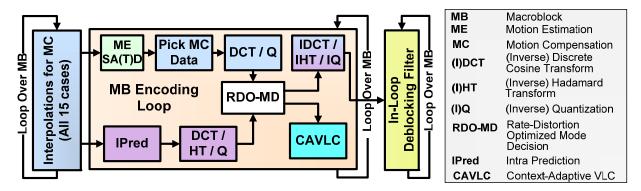

| Figure 4.2:  | Arrangement of Functional Blocks in the H.264 Encoder Benchmark Application                                                                         | 51 |

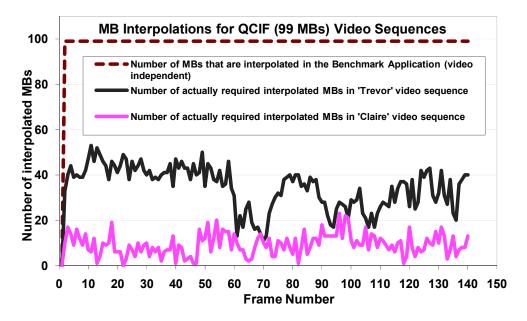

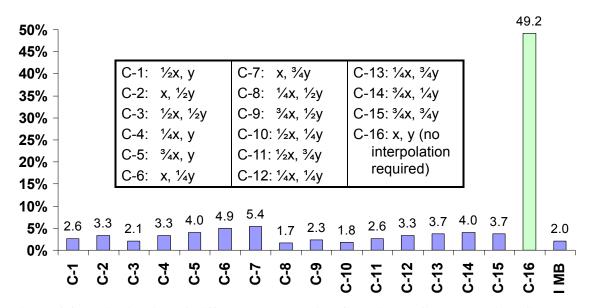

| Figure 4.3:  | Number of Computed vs. Required Interpolated MBs for two Standard Test Sequences for Mobile Devices                                                 | 51 |

| Figure 4.4:  | Distribution of Different Interpolation Cases in the Carphone Video Sequence                                                                        | 52 |

| Figure 4.5:  | H.264 Encoder Application Architecture with Reduced Hardware Pressure                                                                               | 54 |

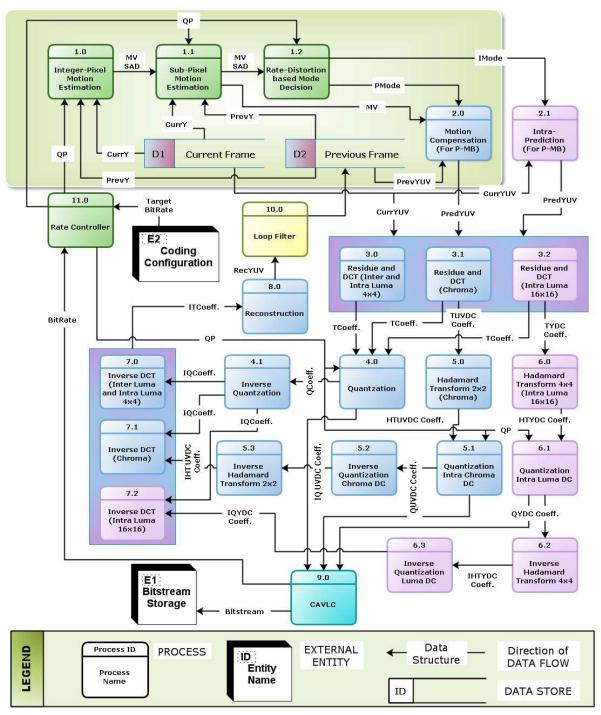

| Figure 4.6:  | Data Flow Diagram of the H.264 Encoder Application Architecture with Reduced Hardware Pressure                                                      | 55 |

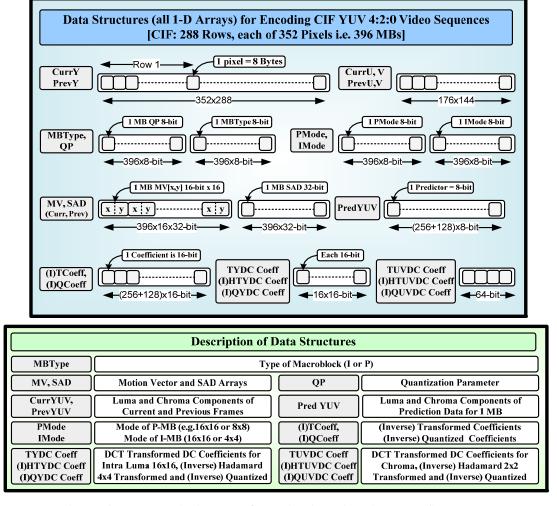

| Figure 4.7:  | Description and Organization of Major Data Structures                                                                                               | 56 |

| Figure 4.8:  | Steps to Create Optimized Data Paths from the Standard Formulae                                                                                     | 58 |

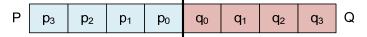

| Figure 4.9:  | Pixel Samples Across a 4x4 Block Horizontal or Vertical Boundary [ITU05]                                                                            | 59 |

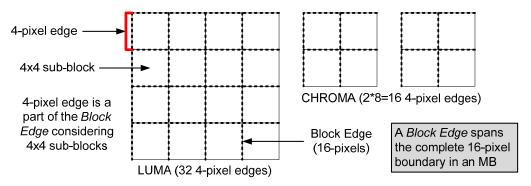

| Figure 4.10: | 4-Pixel Edges in one Macroblock [ITU05]                                                                                                             | 59 |

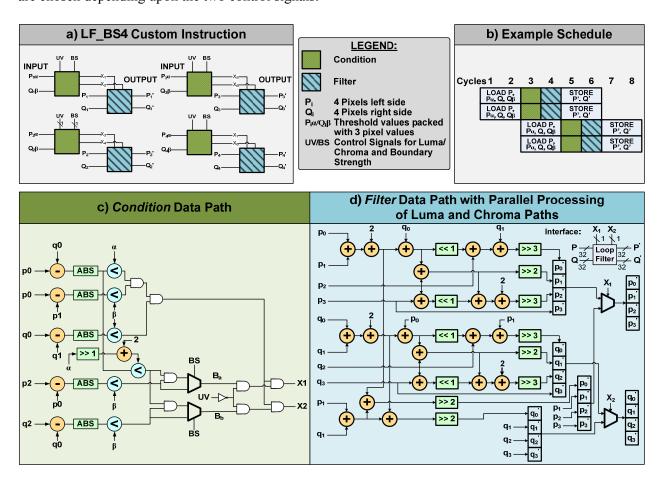

| Figure 4.11: | Custom Instruction for In-Loop Deblocking Filter with Example Schedule and Constituting Data Paths for Filtering Conditions and Filtering Operation | 60 |

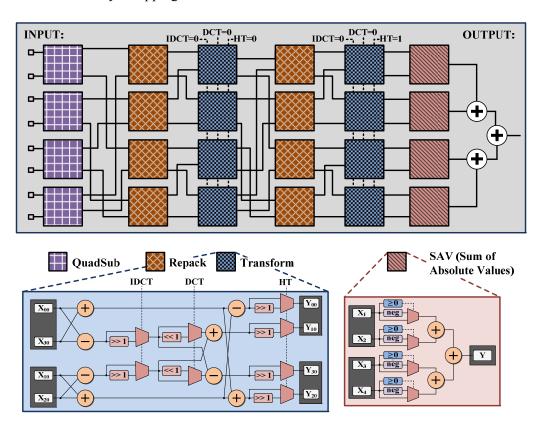

| Figure 4.12: | Custom Instruction for SATD4x4 showing the Transform and SAV Data Paths                                                                             |    |

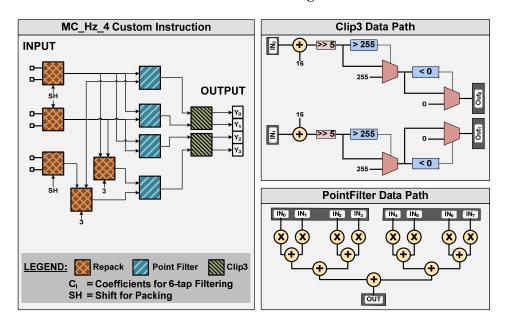

| Figure 4.13: | Custom Instruction for Motion Compensation showing Different Data Paths                                                                             | 62 |

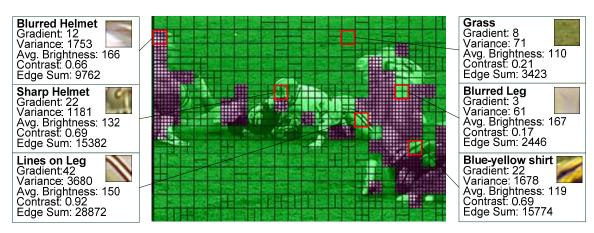

| Figure 4.14: | Mode Distribution and Video Statistics in the 7th Frame of American Football                                                                        | 64 |

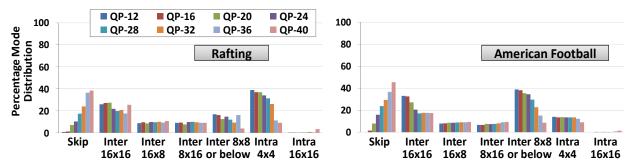

| Figure 4.15: | Optimal Coding Mode Distribution in Rafting and American Football Sequences at different Quantization Parameter (QP) values                         | 65 |

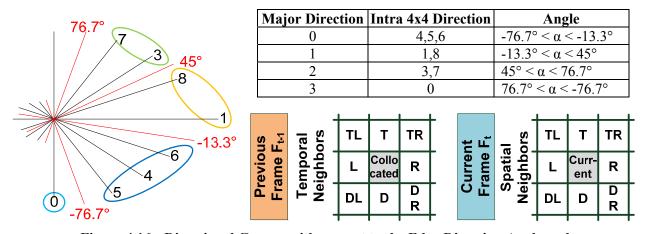

| Figure 4.16: | Directional Groups with respect to the Edge Direction Angle and Notion of Spatial and Temporal Neighboring Macroblocks                              | 66 |

| Figure 4.17: | Mode Distribution of Frame 4 in Rafting Sequence using the Exhaustive RDO-MD for two different QP values: Left: QP = 16 and Right: QP = 38                                   | 68 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

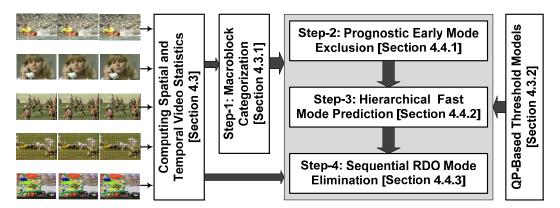

| Figure 4.18: | Overview of the Adaptive Computational Complexity Reduction Scheme (ACCoReS) showing Different Processing Steps and MB Categorizations                                       | 70 |

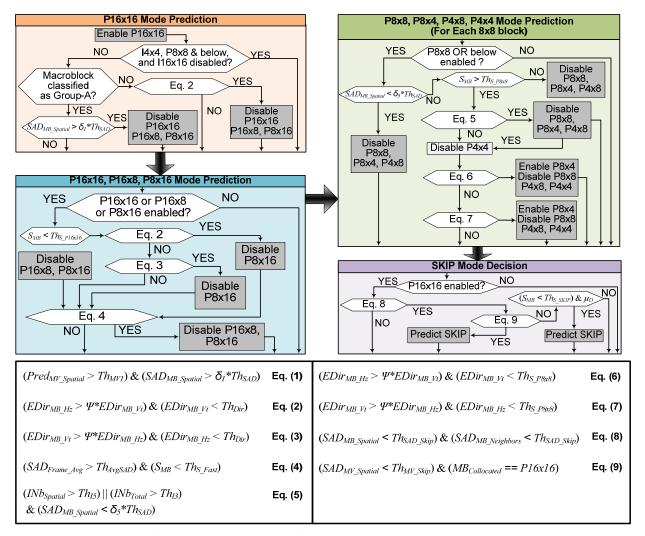

| Figure 4.19: | Processing Flow of the Hierarchical Fast Mode Prediction                                                                                                                     |    |

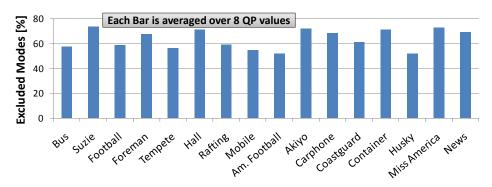

| Figure 4.20: | Percentage Mode Excluded in ACCoReS for Various Video Sequences                                                                                                              |    |

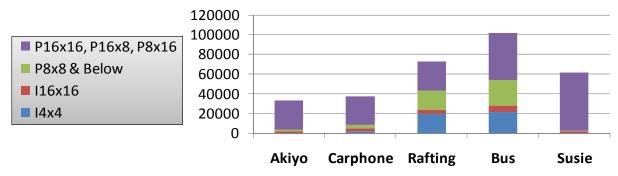

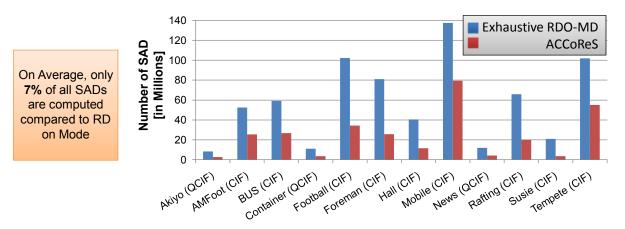

| Figure 4.21: | Distribution of Mode Processing for QP=28                                                                                                                                    | 75 |

| Figure 4.22: | Comparison of Total SAD Computations for various video sequences                                                                                                             |    |

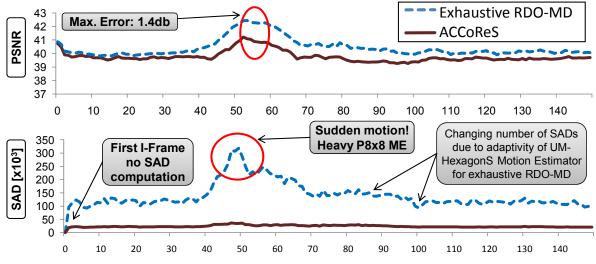

| Figure 4.23: | Frame-Level in-depth Comparison for Susie Sequence                                                                                                                           |    |

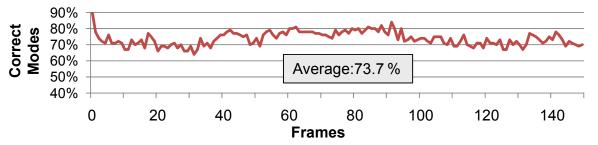

| Figure 4.24: | Frame-Level in-depth evaluation of correct mode prediction                                                                                                                   |    |

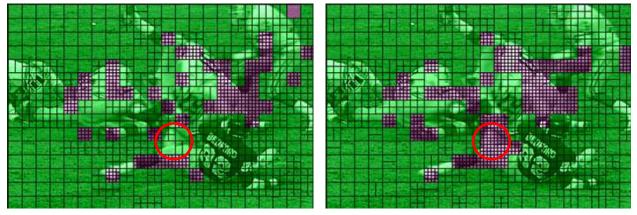

| Figure 4.25: | MB-level Mode Comparison with the Exhaustive RDO-MD: Frame 17 of American Football. Left: ACCoReS [PSNR=33.28 dB], Right: Exhaustive RDO-MD [PSNR=34.52 dB]                  |    |

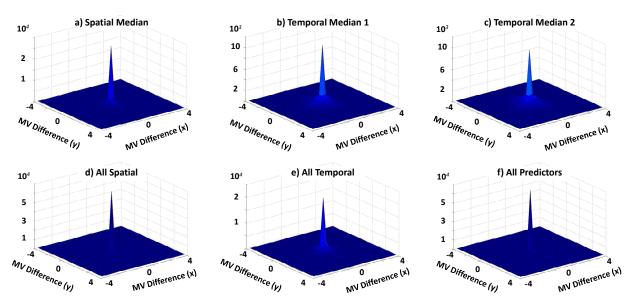

| Figure 4.26: | Motion Vector Difference Distribution in Foreman Sequence (256 kbps) for Various Predictors Compared to the Optimal Motion Vector (obtained using the Full Search algorithm) | 78 |

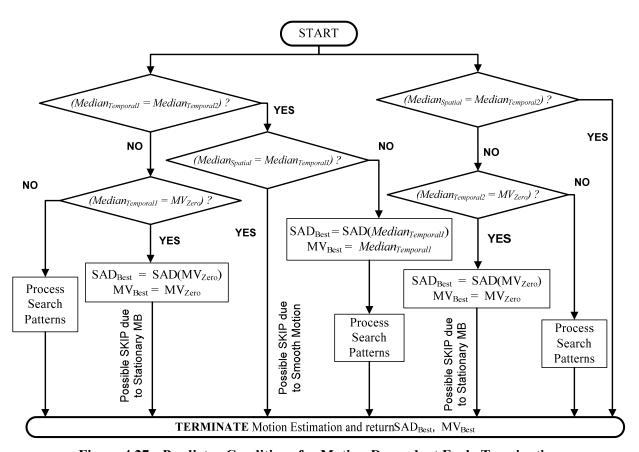

| Figure 4.27: | Predictor Conditions for Motion-Dependent Early Termination                                                                                                                  | 79 |

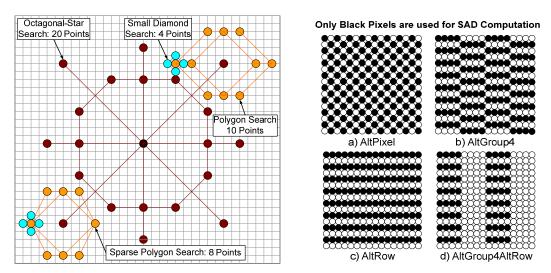

| Figure 4.28: | Four Search Patterns used in the Adaptive Motion Estimator and the Pixel-Decimation Patterns for SAD Computation                                                             | 81 |

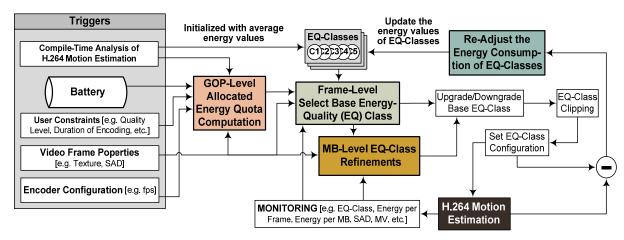

| Figure 4.29: | Flow of the enBudget Scheme for Energy-Aware Motion Estimation                                                                                                               | 83 |

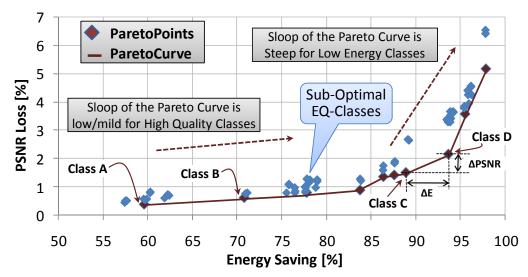

| Figure 4.30: | Energy-Quality (EQ) Classes: Energy-Quality Design Space Exploration showing various Pareto Points and the Pareto Curve                                                      | 84 |

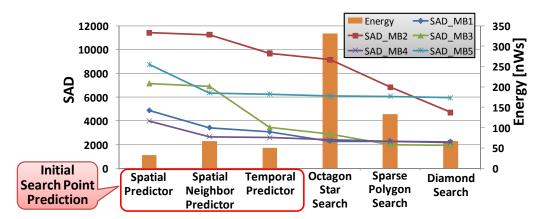

| Figure 4.31: | SAD vs. Energy Consumption Comparison of different Motion Estimation Stages for Foreman Sequence                                                                             | 84 |

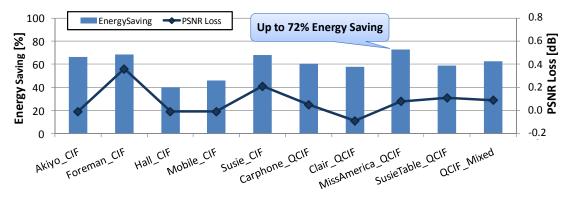

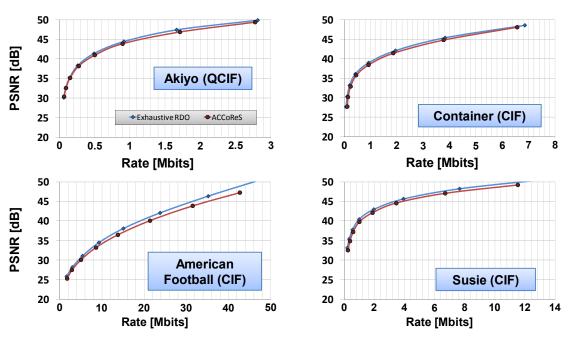

| Figure 4.32: | Energy and Quality Comparison for the Adaptive Motion Estimator With and Without the enBudget for Various Video Sequences                                                    | 88 |

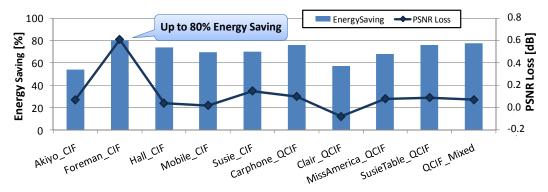

| Figure 4.33: | Energy and Quality Comparison for the UMHexagonS [CZH02] With and Without the enBudget for Various Video Sequences                                                           | 88 |

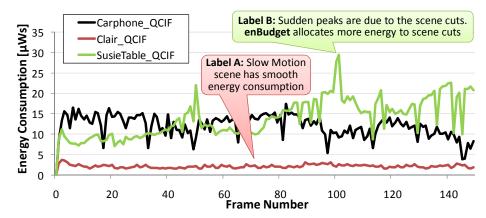

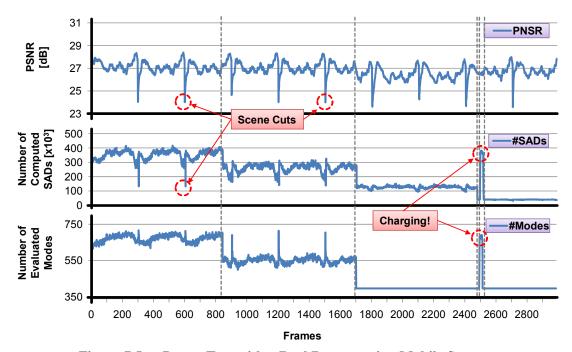

| Figure 4.34: | Frame-wise Energy Consumption of the Energy-Aware Motion Estimation                                                                                                          | 89 |

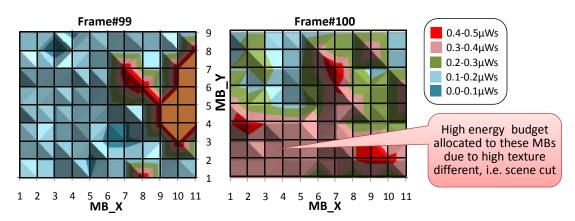

| Figure 4.35: | Macroblock-Wise Energy Consumption Map of two Exemplary Frames in the SusieTableMix_QCIF Sequence for a 90nm Technology                                                      | 89 |

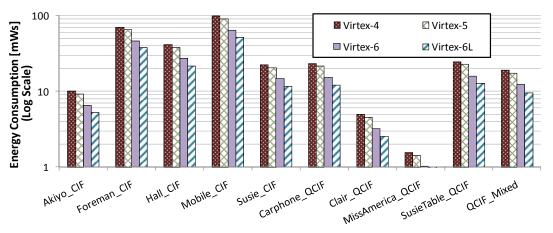

| Figure 4.36: | Energy Consumption of the Energy-Aware Motion Estimation for Various FPGA Fabrication Technologies for Various Video Sequences                                               | 89 |

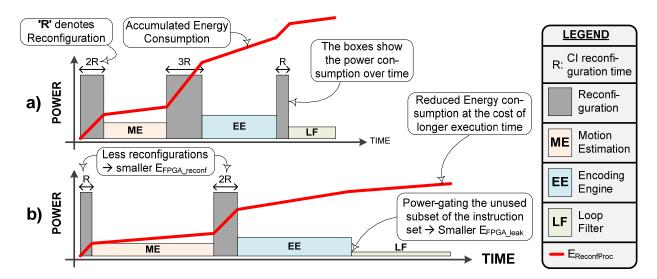

| Figure 5.1:  | Simplified Comparison of Energy Consumption, Highlighting the Effects of Different Reconfiguration Decisions                                                                 | 94 |

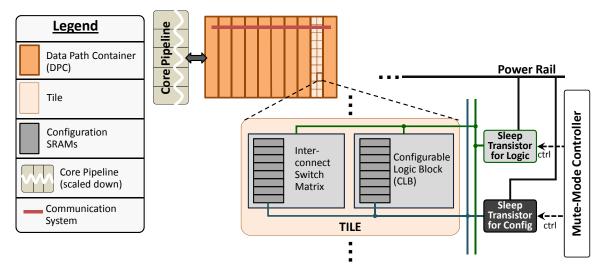

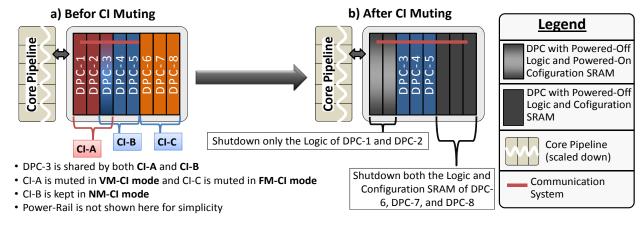

| Figure 5.2:  | Infrastructure Necessary to Exert the Proposed CI Muting Technique                                                                                                           | 97 |

| Figure 5.3:  | Muting the Temporarily Unused Instruction Set                                                                                                                                | 97 |

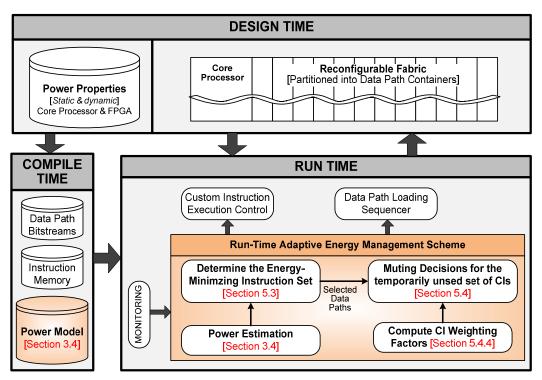

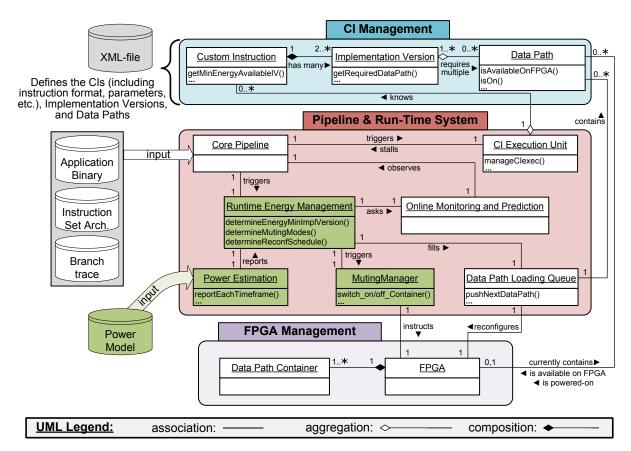

| Figure 5.4:  | Overview of the Proposed Adaptive Low-Power Reconfigurable Processor with Run-Time Adaptive Energy Management along with the Design-, Compile-, and Run-Time Steps                                                                                                                                                                  | 99  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

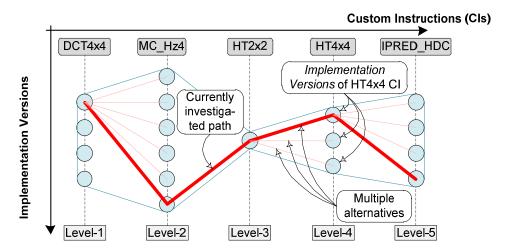

| Figure 5.5:  | Search Space of Five CIs with Their Implementation Versions at the Corresponding Levels and The Path of the Energy-Minimizing Instruction Set                                                                                                                                                                                       | 103 |

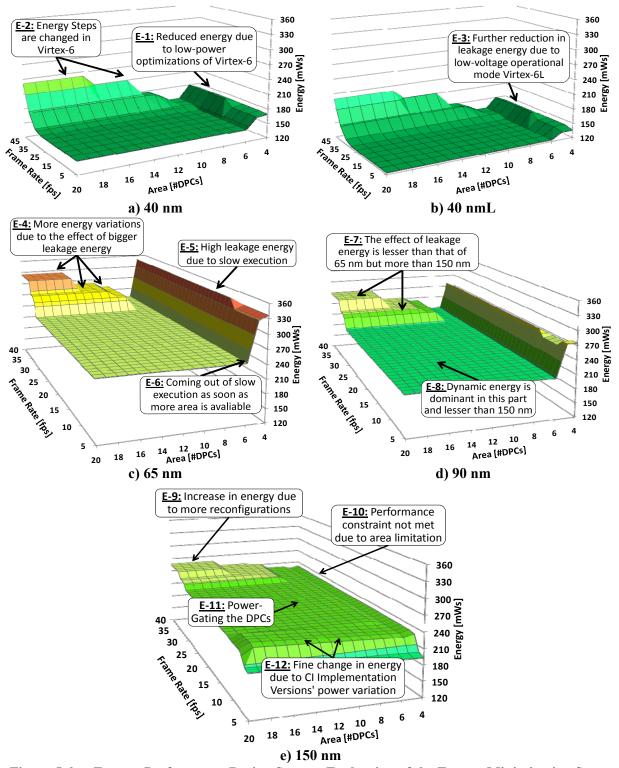

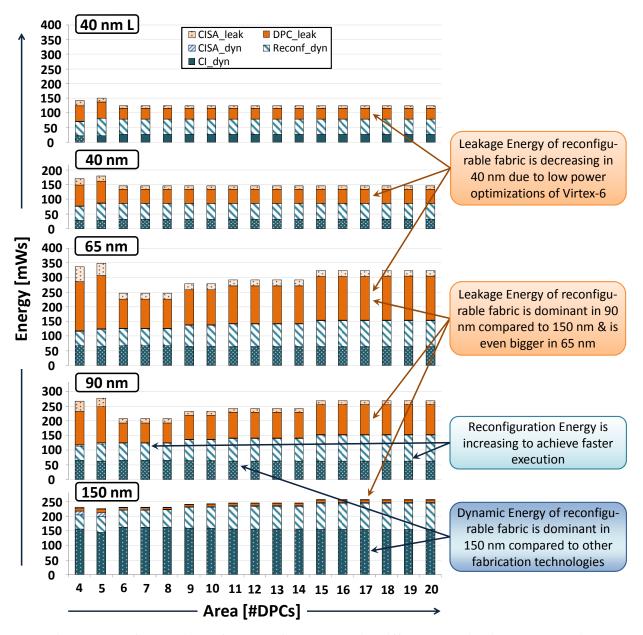

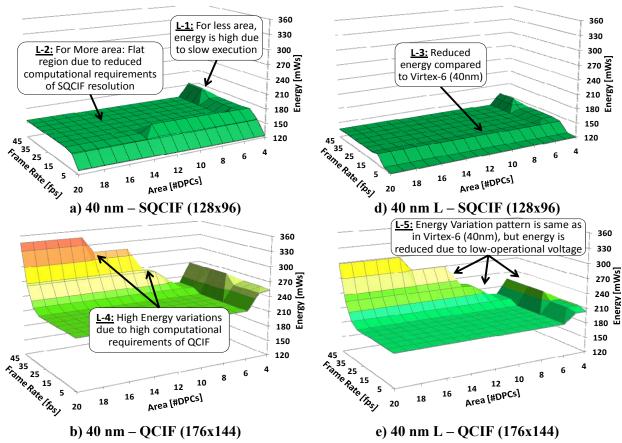

| Figure 5.6:  | Energy-Performance Design Spaces: Evaluation of the Energy Minimization Space Using the Adaptive Energy Management Scheme under Various Area and Performance Constraints for Four Fabrication Technologies for an Encoding of 40 QCIF (176x144) Frames                                                                              | 106 |

| Figure 5.7:  | Comparison of Energy Components in Different Fabrication Technologies under Various Area Constraints                                                                                                                                                                                                                                |     |

| Figure 5.8:  | Comparing Energy-Performance Design Spaces for Different Video<br>Resolutions when using the Energy Management Scheme under Various<br>Area and Performance Constraints for an Encoding of 60 Video Frames                                                                                                                          | 108 |

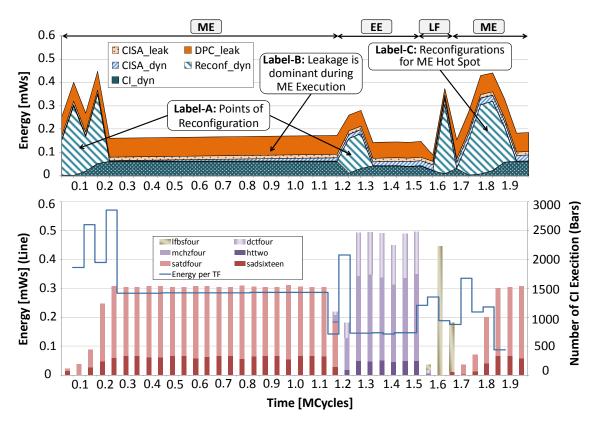

| Figure 5.9:  | CI Execution Results for 30 fps on 65 nm Showing a Detailed Breakdown of Energy Components Highlighting the Contribution of Reconfiguration and Leakage Energy. The Lower Graph Shows the Detailed Execution Pattern of Various CIs Executing in Different Hot Spots of the H.264 Video Encoder Along With Total Energy Consumption | 109 |

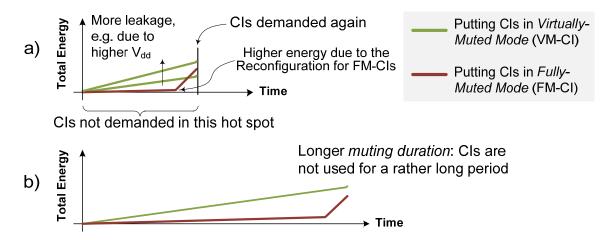

| Figure 5.10: | Comparing the Energy Requirements of Virtually- & Fully-Muted CIs for 2 Scenarios                                                                                                                                                                                                                                                   |     |

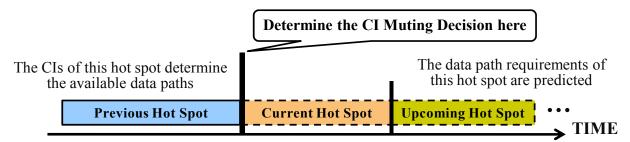

| Figure 5.11: | Time-line showing the execution sequence of hot spots and the situation for a CI Muting decision                                                                                                                                                                                                                                    | 112 |

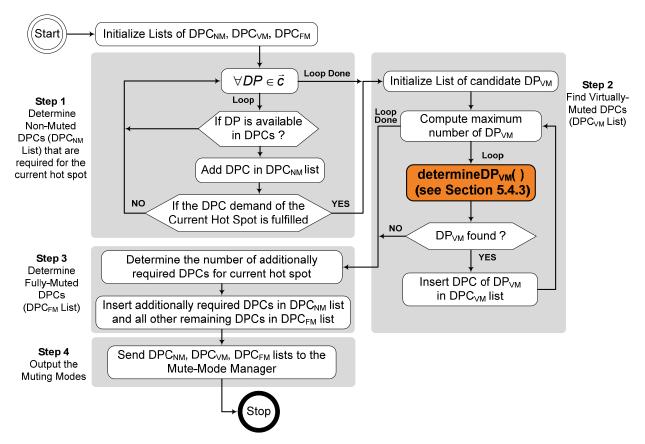

| Figure 5.12: | Flow for Selecting a Muting Mode for the Custom Instruction (CI) Set                                                                                                                                                                                                                                                                | 113 |

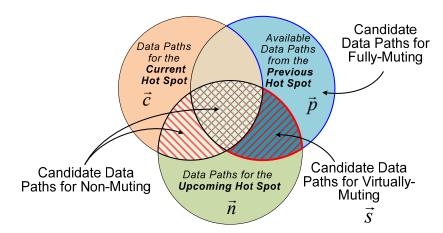

| Figure 5.13: | Venn Diagram Showing the Data Path Requirements of Previous, Current, Upcoming Hot Spots                                                                                                                                                                                                                                            | 114 |

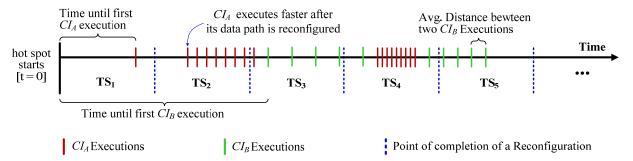

| Figure 5.14: | Calculating the Weighting Factor for Custom Instructions w.r.t. the Application Context                                                                                                                                                                                                                                             | 116 |

| Figure 5.15: | Summary of Energy Benefit of using Selective Instruction Set Muting                                                                                                                                                                                                                                                                 | 117 |

| Figure 6.1:  | a) Measurement setup, b) the in-house Developed Power Supply board                                                                                                                                                                                                                                                                  | 119 |

| Figure 6.2:  | Flow for Creating the Measurement-based Power Model                                                                                                                                                                                                                                                                                 | 120 |

| Figure 6.3:  | Test Case and Setup for Measuring the Power of An Idle (Empty) Framework                                                                                                                                                                                                                                                            | 121 |

| Figure 6.4:  | Different Test Cases for Measuring the Power of Different Components of a Custom Instruction (CI) Implementation Version                                                                                                                                                                                                            | 122 |

| Figure 6.5:  | Connection of FIFO between FEPROM and ICAP                                                                                                                                                                                                                                                                                          | 124 |

| Figure 6.6:  | (a) EEPROM Voltage Drop while Loading one Data Path Bitstream from EEPROM to FPGA. (b) VCC <sub>INT</sub> Voltage Drop for Transferring one Data Path Bitstream to ICAP and Performing the Corresponding                    |     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | Reconfiguration                                                                                                                                                                                                             | 125 |

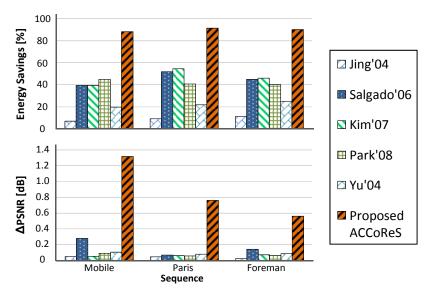

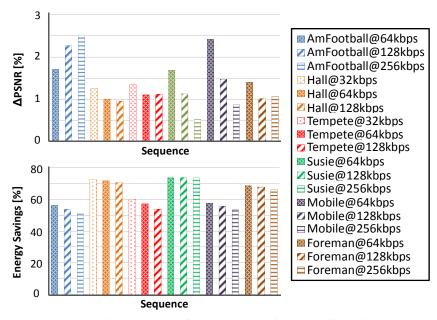

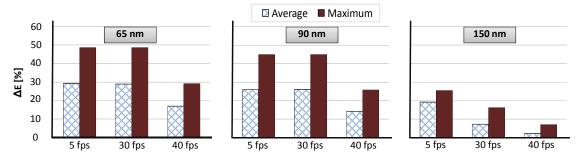

| Figure 7.1:  | Comparing the Energy Savings and Quality Loss of the ACCoReS with Several State-of-the-Art Fast Mode Decision Schemes                                                                                                       | 129 |

| Figure 7.2:  | Energy Savings and Quality Loss of the ACCoReS compared to the Exhaustive RDO-MD for CIF Resolution Video Sequences                                                                                                         | 129 |

| Figure 7.3:  | Energy Savings and Quality Loss of the ACCoReS compared to the Exhaustive RDO-MD for QCIF Resolution Video Sequences                                                                                                        | 130 |

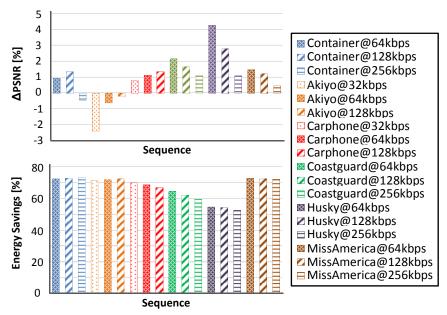

| Figure 7.4:  | Comparing the Rate Distortion Curves for QCIF and CIF Sequences                                                                                                                                                             | 130 |

| Figure 7.5:  | Power Test with a Real Battery using Mobile Sequence                                                                                                                                                                        | 131 |

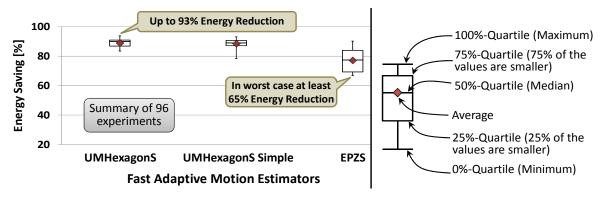

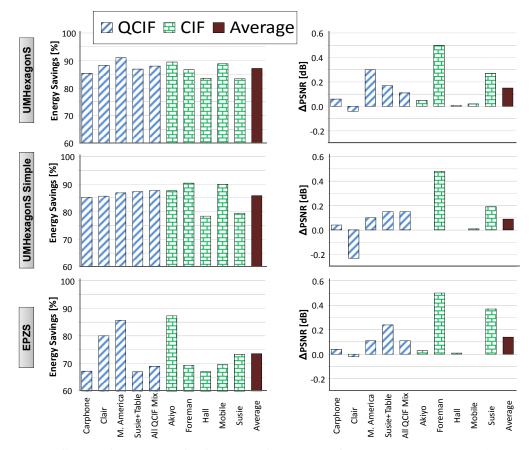

| Figure 7.6:  | Summary of Energy Savings of the enBudget Scheme Compared to Various Fast Adaptive Motion Estimation Schemes                                                                                                                | 132 |

| Figure 7.7:  | Comparing Energy Saving and PSNR Loss of the Proposed Energy-Aware Motion Estimation and the enBudget Scheme with Various Fast Adaptive Motion Estimators [* negative PSNR loss actually shows the PSNR gain of the Scheme] | 132 |

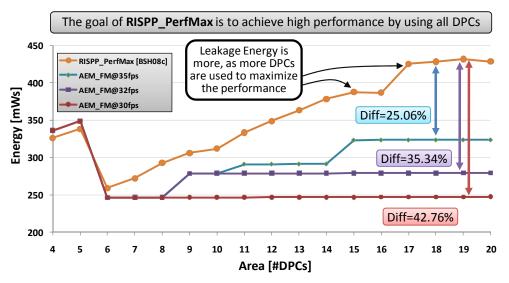

| Figure 7.8:  | Energy Comparison of the AEM_FM and RISPP_PerfMax schemes for 65 nm                                                                                                                                                         | 133 |

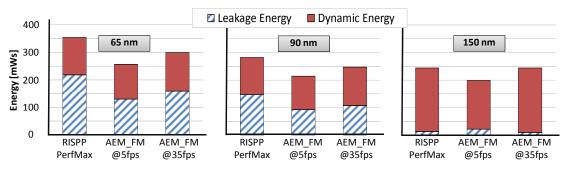

| Figure 7.9:  | Average Energy Comparison of the AEM_FM and RISPP_PerfMax for 3 Technologies                                                                                                                                                | 134 |

| Figure 7.10: | Percentage energy saving of Molen [VWG+04] plus AEM_FM over Molen without AEM_FM for three technologies                                                                                                                     | 134 |

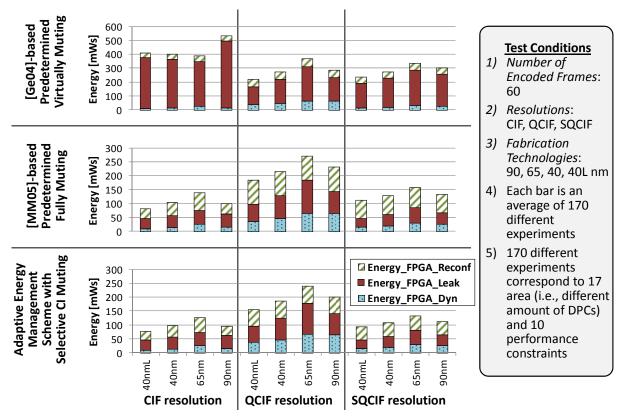

| Figure 7.11: | Comparing the Energy Breakdown of the Adaptive Energy Management Scheme (with Selective Instruction Set Muting) to [Ge04]-based Pre-VM and [MM05]-based Pre-FM.                                                             | 135 |

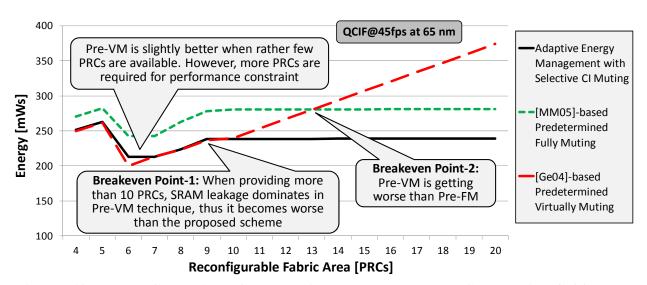

| Figure 7.12: | Energy Comparison of the Adaptive Energy Management Scheme with [Ge04]-based Pre-VM and [MM05]-based Pre-FM Techniques for Varying Amount of Reconfigurable Fabric                                                          | 136 |

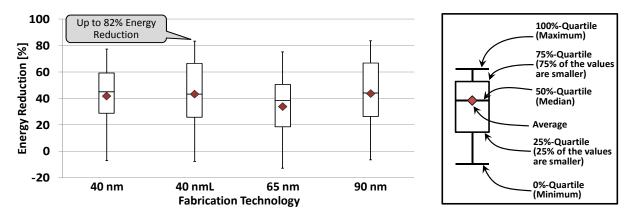

| Figure 7.13: | Energy Savings of the Adaptive Energy Management Scheme Compared to the [Ge04]-based Pre-VM technique                                                                                                                       |     |

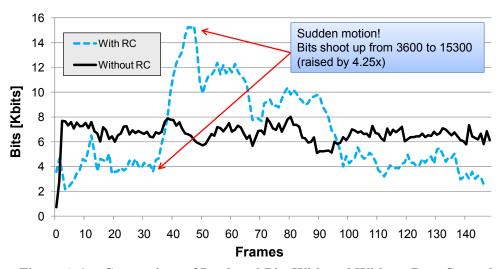

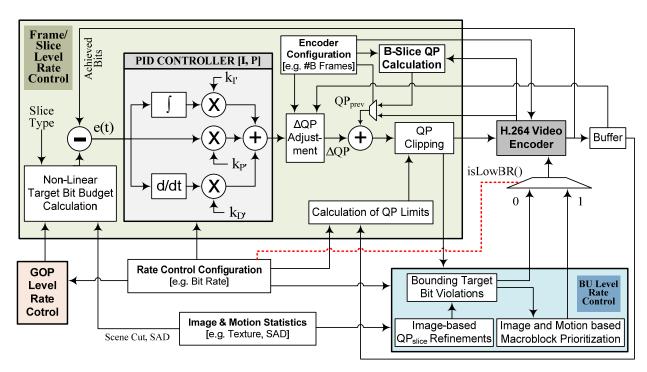

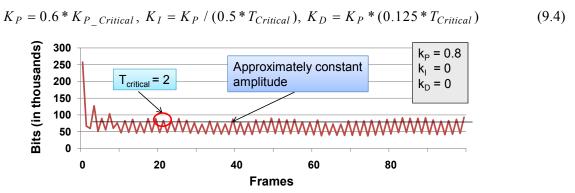

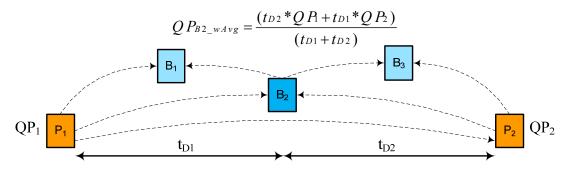

| Figure A.1:  | Comparison of Produced Bits With and Without Rate Control                                                                                                                                                                   | 145 |

| Figure A.2:  | The Multi-Level Rate Control Scheme covering GOP, Frame/Slice, & BU Levels along with Image and Motion Based Macroblock Prioritization                                                                                      |     |

| Figure A.3:  | Critical Ziegler-Nichols-Point for American Football                                                                                                                                                                        |     |

| Figure A.4:  | Temporal Distance based QP Calculation for B Frames/Slices                                                                                                                                                                  | 149 |

| Figure A.5:  | Basic Unit (BU) Level RC with Texture and Motion Based QP                                                                                                                                                                   |     |

|              | Adjustments                                                                                                                                                                                                                 | 151 |

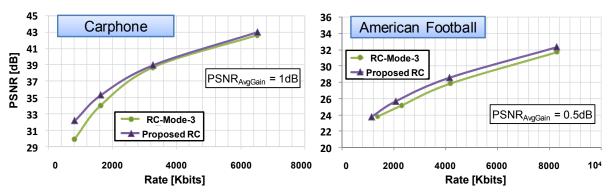

| Figure A.6:  | RD-Curves Comparison of the Proposed Multi-Level RC with RC-Mode-<br>3 for Carphone (QCIF, IPPP) and American Football (SIF, IBBP)                       | 152 |

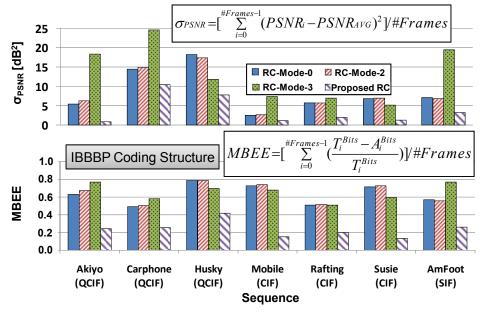

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure A.7:  | MBEE Comparison of the Multi-Level RC with Three Different RC Modes                                                                                      | 152 |

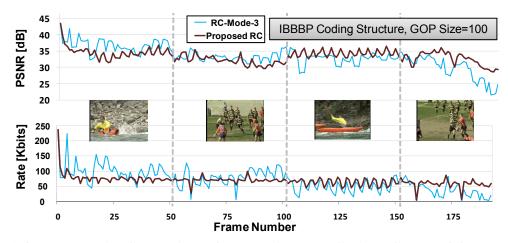

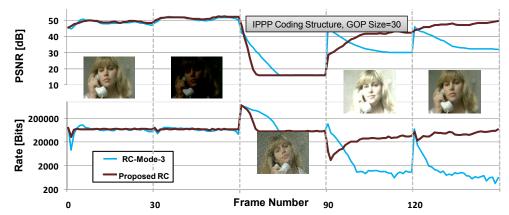

| Figure A.8:  | Frame-wise Comparison of the Multi-Level RC with RC-Mode-3 for Fast Motion Combined CIF Sequences Encoded at 2Mbps@30fps                                 | 153 |

| Figure A.9:  | Frame-wise Comparison of the Multi-Level RC with RC-Mode-0 for Susie Mixed CIF Sequence (Bright, Dark, Noisy) at 2Mbps@30fps                             | 153 |

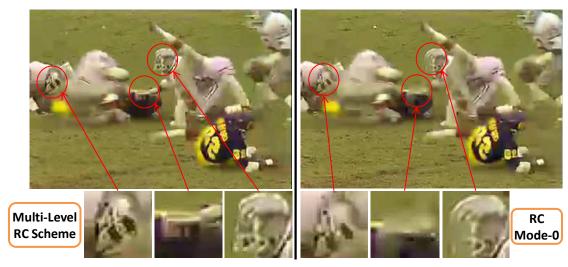

| Figure A.10: | Evaluating the Image and Motion Based MB Prioritizations (Note: All excerpts are 2x zoomed using nearest neighbor interpolation)                         | 153 |

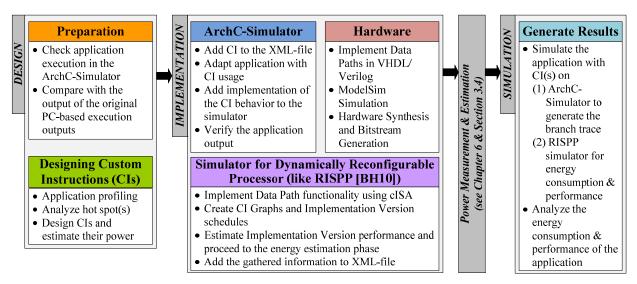

| Figure B.1:  | Simulation Methodology Showing Various Steps of the Simulation Procedure [S.3]                                                                           | 156 |

| Figure B.2:  | Reconfigurable Processor Simulator [BSH09a] with the Extensions Implemented in the Scope of this Thesis for Run-Time Adaptive Energy- Management         | 157 |

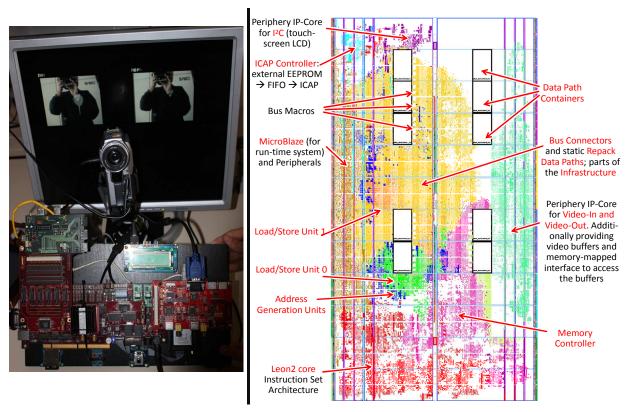

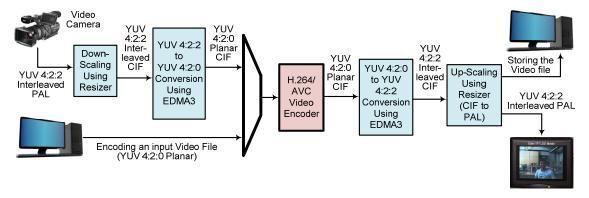

| Figure B.3:  | (A) H.264 Video Encoder Executing on the RISPP Prototype; (B) Floorplan of the RISPP Prototype Implementation on the Xilinx Virtex-4 LX 160 FPGA [Bau09] | 158 |

| Figure B.4:  | H.264 Video Encoder Executing on the TI' DM6437 DSP Board [S.2]                                                                                          | 159 |

| Figure B.5:  | Flow for porting H.264 Encoder on DM6437 Digital Signal Processor [S.2]                                                                                  | 159 |

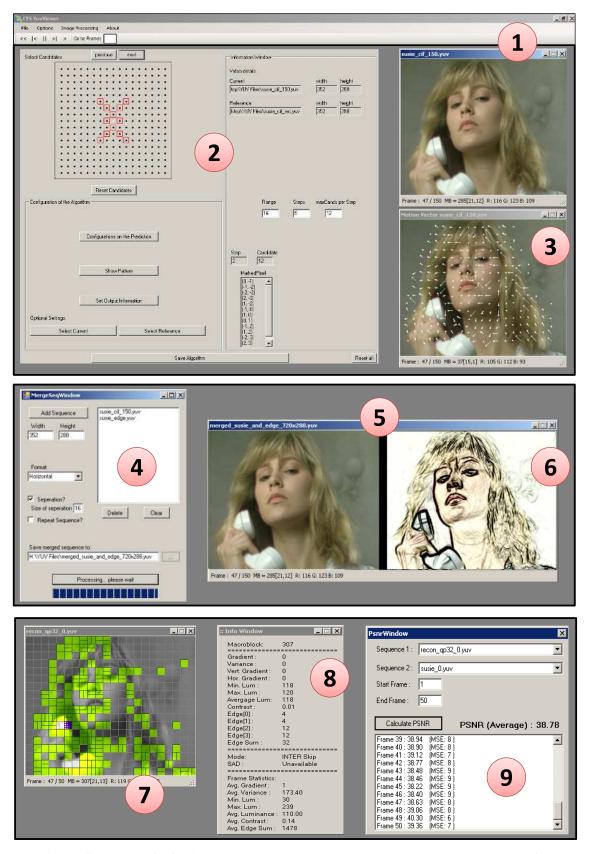

| Figure C.1:  | The CES Video Analyzer Tool showing the Research Framework for Motion Estimation, Video Merging, and Texture Analysis [D.1]                              | 162 |

## **List of Tables**

| Table 2.1: | High-level Properties of Implementation Version and Custom Instruction [Bau09]                                                                                                                                                                                             | 28  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1: | Comparing the Coding Tool Set of Various Video Encoding Standards [ITU05, ITU09, Joi08, Joi10, KL07, Mic10a, Mic10b, Ric03, Ric10, YCW09]                                                                                                                                  | 37  |

| Table 4.1: | Custom Instructions and Data Paths for the H.264 Video Encoder                                                                                                                                                                                                             |     |

| Table 4.2: | Implementation Results for Various Data Paths of the H.264 Video Encoder                                                                                                                                                                                                   | 63  |

| Table 4.3: | Thresholds and Multiplying Factors Used in ACCoReS                                                                                                                                                                                                                         | 69  |

| Table 4.4: | Summary of PSNR, Bit Rate, and Speedup Comparison for Various Video Sequences (Each encoded using 8 different QPs)                                                                                                                                                         | 74  |

| Table 4.5: | Comparing the Video Quality of Different SAD Decimation Patterns for Encoding of Susie CIF video sequence (30fps@256 kbps)                                                                                                                                                 | 81  |

| Table 4.6: | Configuration and Energy Consumption for the chosen Energy-Quality (EQ) Classes [*Averaged over various test video sequences for 90 nm ASIC]                                                                                                                               | 85  |

| Table 4.7: | Coefficients and Thresholds used by the algorithm of enBudget in Algorithm 4.4                                                                                                                                                                                             | 87  |

| Table 4.8: | Performance, Area, and Energy Overhead of enBudget                                                                                                                                                                                                                         | 90  |

| Table 5.1: | Various Custom Instruction (CI) Muting Modes                                                                                                                                                                                                                               | 96  |

| Table 5.2: | Parameters and Evaluation Conditions with their Corresponding Reference<br>Sources * the Virtex-5/6 internal CLB Composition is Different Compared<br>to Previous FPGAs                                                                                                    | 105 |

| Table 5.3: | Hardware Implementation Results for the Energy Management Scheme on the RISPP Prototyping Platform (see Figure 6.1 in Section 6.1)                                                                                                                                         | 109 |

| Table 6.1: | Different Placement Combinations of two Transform Data Paths for Power Measurement                                                                                                                                                                                         | 122 |

| Table 6.2: | Measured Power Results for Various Data Paths & HT4x4 Implementation Versions [* showing the effect of changing communication requirements, ** power for a single toggling bus segment; many bus segments are used for communication to realize an Implementation Version] | 123 |

| Table 6.3: | Parameters of Power Model for the CI Implementation Versions                                                                                                                                                                                                               | 123 |

| Table 6.4: | Power Consumption and Latencies of Different Implementation Versions (using Different Amount of DPCs) for Various Custom Instructions for 65                                                                                                                               | 100 |

|            | nm and 40 nm Technologies                                                                                                                                                                                                                                                  | 123 |

## **List of Algorithms**

| Algorithm 4.1: The Filtering Process for Boundary Strength=4                           | 59  |

|----------------------------------------------------------------------------------------|-----|

| Algorithm 4.2: Pseudo-Code of Group-A for Prognostic Early Mode Exclusion              | 71  |

| Algorithm 4.3: Pseudo-Code of Group-B for Prognostic Early Mode Exclusion              | 72  |

| Algorithm 4.4: Pseudo code of the Run-Time Adaptive Predictive Energy-Budgeting Scheme | 86  |

| Algorithm 5.1: Pseudo code of Determining the Energy Minimizing Instruction Set        | 104 |

| Algorithm 5.2: Pseudo Code for Finding a Data Path for Virtually-Muting Mode           | 114 |

## **Abbreviations and Definitions**

ACCoReS Adaptive Computational Complexity Reduction Scheme

ADI Arbitrary Directional Intra

ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

ASIP Application Specific Instruction Set Processor

AVC Advanced Video Coding AVS Advanced Visual Systems

B-MB Bi-directionally predicted →MB (i.e., a prediction is performed from the previous and

future reference frames)

BC Bus Connector: Connecting a →DPC to the Computation and Communication

Infrastructure

BOPF Buffer Overflow Prevention Factor

BU Basic Unit, it is a group of →MBs; it defines the granularity at which the rate controller

computes a new QP value

CABAC Context-Adaptive Binary Arithmetic Coding

CAVLC Context-Adaptive Variable Length Coding

CBR Constant Bit Rate

CI Custom Instruction

CIF Common Intermediate Format (Resolution: 352x288)

CIP Combined Intra Prediction

cISA core Instruction Set Architecture: the part of the instruction set that is implemented

using the core processor pipeline (i.e., non-reconfigurable); it can be used to implement

can be used to implement →Custom Instructions

CLB Configurable Logic Block: part of an →FPGA, contains multiple →LUTs

CPU Central Processing Unit

DCSS Dynamic Clock Supply Stop

DCT Discrete Cosine Transform

DPC Data Path Container: a part of the reconfigurable fabric that can be dynamically

reconfigured to contain a Data Path, i.e., an elementary hardware accelerator

DVFS Dynamic Voltage and Frequency Scaling

EAPR Early Access Partial Reconfiguration

EE Encoding Engine

EEPROM Electrically Erasable Programmable Read Only Memory

enBudget The run-time adaptive Energy Budgeting Scheme

EPZS Enhanced Predictive Zonal Search

EQ Energy-Quality

FI Forecast Instruction: a trigger instruction that indicates a Forecast Block containing a set

of  $\rightarrow$ CIs with an information of the compile-time analysis (e.g., expected number of

executions)

FIFO First-In First-Out buffer FIR Finite Impulse Response

FME Fractional-pixel Motion Estimation

FMO Flexible Macroblock Ordering

FM-CI Fully-Muted Custom Instruction

FPGA Field Programmable Gate Array: a reconfigurable device that is composed as an array of

→CLBs and switching matrices

FPS Frames Per Second

FS Full Search

GOP Group of Pictures with one I-Frame followed by a series of P- and/or B-Frames

GPP General Purpose Processor HDTV High Definition Television

HD720p High Definition 720 Lines Progressive Scan (Resolution: 1280 x 720)

HEVC High Efficiency Video Coding

HT Hadamard Transform HVS Human Visual System

I-MB Intra-predicted →MB (i.e., a prediction is performed from the reconstructed pixels of

→MBs from the current frame; it is also called *spatial* prediction

I4x4 Macroblock is encoded as Intra with prediction is done at 4x4 block sizes

I16x16 Macroblock is encoded as Intra where the whole 16x16 block is predicted

ICAP Internal Configuration Access Port

IDCT Inverse Discrete Cosine Transform

IEC International Electrotechnical Commission

IHT Inverse Hadamard Transform

ILP Integer Linear Programming

IME Integer-pixel Motion Estimation

IP Intellectual Property

IPred Intra Prediction

IQ Inverse Quantization

ISA Instruction Set Architecture

ISO International Organization for Standardization

ISS Instruction Set Simulator

ITU International Telecommunication Union

JVT Joint Video Team

KB Kilo Byte (also KByte): 1024 Byte

KD Derivative GainKI Integral Gain

KP Proportional Gain

LF Loop Filter

LUT Look-Up Table: smallest element in an →FPGA, part of a →CLB; configurable as logic

or memory

MAD Mean of Absolute Differences

MB Mega Byte (also MByte): 1024 → KB

MB Macroblock, a 16x16 pixel block of a video frame

MBEE Mean Bit Estimation Error

MC Motion Compensation

MD Mode Decision

ME Motion Estimation

MIPS Microprocessor without Interlocked Pipeline Stages

MPEG Motion Picture Experts Group MPSoC Multiprocessor System-on-Chip

MSE Mean Square Error

MV Motion Vector

MVC Multiview Video Coding

NM-CI Non-Muted Custom Instruction

NMOS N-type Metal-Oxide-Semiconductor Logic