# Performance Optimization Strategies for Transactional Memory Applications

zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

Martin Otto Schindewolf

aus Eschwege

Tag der mündlichen Prüfung: 19. April 2013

Erster Gutachter:

Zweiter Gutachter:

19. April 2013Prof. Dr. Wolfgang KarlProf. Dr. Albert Cohen

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum der Helmholtz-Gesellschaft

Ich versichere hiermit wahrheitsgemäß, die Arbeit bis auf die dem Aufgabensteller bereits bekannte Hilfe selbständig angefertigt, alle benutzten Hilfsmittel vollständig und genau angegeben und alles kenntlich gemacht zu haben, was aus Arbeiten anderer unverändert oder mit Abänderung entnommen wurde.

Karlsruhe, den 4. März 2013

Martin Schindewolf

#### Abstract

Transactional Memory (TM) has been proposed as an architectural extension to enable lock-free data structures. With the ubiquity of multi-core systems, the idea of TM gains new momentum. The motivation for the invention of TM was to simplify the synchronization of parallel threads in a shared memory system. TM features optimistic concurrency as opposed to the pessimistic concurrency with traditional locking. This optimistic approach lets two transactions execute in parallel and assumes that there is no data race. In case of a data race, e.g., both transactions write to the same address, this conflict must be detected and resolved. Therefore a TM run time system monitors shared memory accesses inside transactions. These TM systems can be implemented in software (STM), hardware (HTM) or as a hybrid combination of both. Most of the research in TM focuses on language extensions, compiler support, and the optimization of algorithmic details of TM systems. Each of the resulting TM systems has a different performance characteristic and comes with a number of parameters that can be tuned. This optimization space overwhelms the application developer who has been the target audience for the invention of TM. In contrast to other research activities, this thesis proposes TM tools that are candidates to bridge the gap between the application developer and the designer of the TM system. These tools for TM provide insights in the run time behavior of the TM application and guide the application developer to optimize the TM application.

In contrast to related work presenting tools for a specific TM system coupled with a programming language, this thesis presents solutions that cover multiple TM systems (Software, Hardware, and hybrid TM) and account for different parameter settings in each of the TM systems. Moreover, the proposed methods and strategies use information of all different layers of the TM software stack. Therefore, static information, information about the run time behavior, and expert-level knowledge need to be extracted to develop these new methods and strategies for the optimization of TM applications. Extracting and using this information poses the following challenges that need to be addressed.

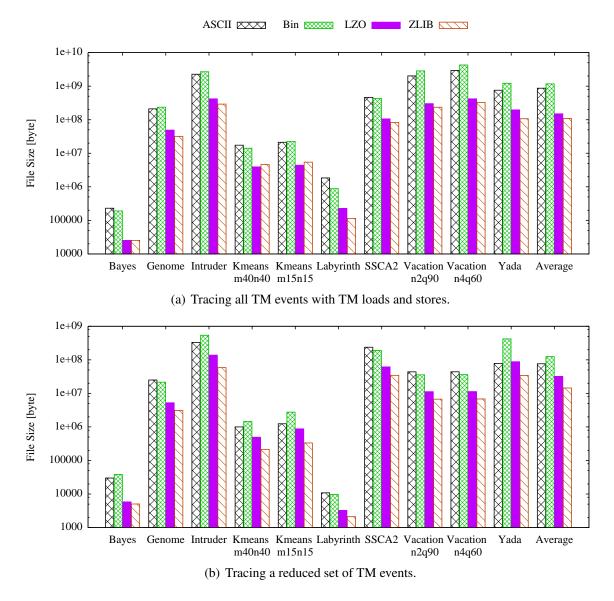

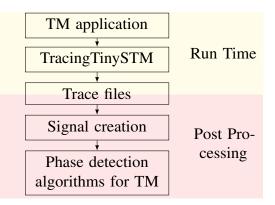

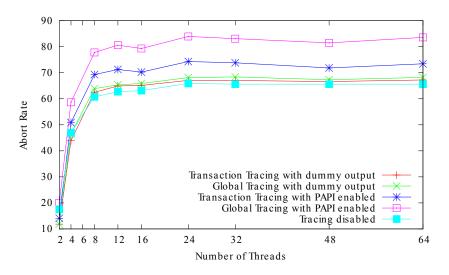

The first challenge is to capture the genuine TM application's behavior at run time. This is especially important because transactions are sensitive to artificially introduced delays of a thread which may cause an introduced TM conflict. This may lead to a recorded application's behavior that is biased through the tracing machinery. Therefore, a lightweight trace generation scheme with a small probe-effect needs to be developed and evaluated. This thesis presents similar solutions for STM and hybrid TM that generate event traces. For STM, the logging of frequently occurring events, such as TM loads and stores, quickly saturates the write bandwidth of the hard disk. Thus, a reduction of the amount of data to be written to hard disk needs to be achieved. Therefore, we research how these events can be compressed online without disturbing the application. A multi-threaded trace compression scheme is designed, implemented, and evaluated. We enhance the TinySTM, a word-based open source STM, with tracing facilities. Due to the lightweight and compressing tracing

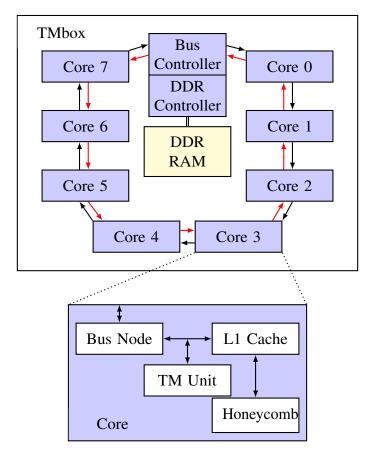

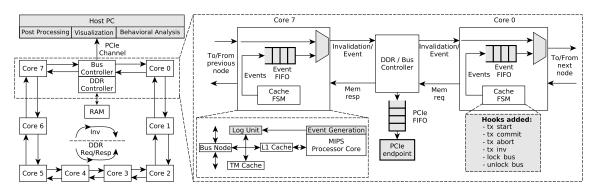

scheme, the resulting TracingTinySTM generates event traces that capture the genuine TM application's behavior. For an FPGA-based hybrid TM system, called TMbox, a low-overhead tracing solution is shown. Each processing element is enhanced with an event generation unit for monitoring. When an instruction of interest is encountered, a corresponding time-stamped event is generated and passed on to the log unit. This unit uses idle times on the bus to transfer it to the memory of the host machine. Although all methods are tailored to and applied in the context of TM, they are universally applicable in a different context. Example application areas are the monitoring of arbitrary events in an FPGA-based processor prototype or the logging and compressing of events in a math library.

The second challenge arises with the release of IBM's new Blue Gene/Q architecture with HTM support. We establish a set of best practices for the new architecture so that the application developer can exploit the full potential of the architecture including the TM subsystem. For this purpose, we introduce a new benchmark, CLOMP-TM, that has a series of parameters that allow us to explore varying transaction granularities and conflict rates, coupled with typical computational kernels found in scientific codes. This enables new insights through evaluating the TM system and comparing the performance with other synchronization primitives of OpenMP. Further, this new BG/Q architecture also requires tool support to enable optimizations of scientific applications. A trace-based solution to capture the run time behavior on a per event basis is not feasible for this proprietary HTM system. This HTM system requires a complete software stack, including compiler and run time system. Thus, we design, implement and evaluate three different tools for TM that enable programmers to explore the subtleties of TM execution and contribute the following to the state-of-the-art:

- the first tool that profiles applications using MPI and OpenMP with TM on BG/Q,

- a tracing tool for TM that enables in-depth inspection of thread-level execution and utilization of the architecture through visualization with the state-of-the-art visualization tool Vampir,

- a tool that measures overheads associated with TM, designed to dissect these overheads and direct optimization efforts for the TM stack.

These tools uncover the subtle interaction of the TM system and the prefetching on BG/Q and help to study the implications for designing applications and choosing the TM mode of execution. Moreover, these tools enable to obtain a comprehensive understanding of the performance of synchronization mechanisms in *LULESH*, a Lagrange hydrodynamics proxy application, and find the cause for the missing performance with TM.

The third challenge is to correlate the gathered TM characteristics with microarchitecture events for the optimization of TM applications using STMs. Although this correlation is not new by itself, it is extremely helpful and has not been researched extensively in this context. Besides choosing well-suited parameters to monitor the microarchitecture, the correct interpretation of the obtained values is of key importance. To simplify the optimization for humans, the Visualization Of TM Applications (VisOTMA) framework is developed that visualizes these traces and enables the programmer to identify frequently conflicting transactions and the corresponding values of microarchitecture parameters in a post-processing step.

The visualization of this aggregated data needs to be achieved in a way that an inexperienced as well as an experienced programmer can identify pathological execution patterns – posing

the fourth challenge. So far optimizations have been carried out by TM experts with excellent knowledge of the underlying TM system. An inexperienced programmer does not have or may not be willing to acquire the knowledge of the TM system. Thus, the inexperienced programmer follows a trial-and-error strategy to optimize the TM application. To speedup this process, we invent EigenOpt – an exploration tool based on EigenBench – as part of the VisOTMA framework. With the help of EigenOpt, any programmer can capture the TM characteristic of the application in terms of parameters for Eigenbench. These parameters combined with Eigenbench are straightforwardly used to explore the space available through optimizations. With this tool, unrewarding optimization directions can be excluded without modifying the application. In this thesis, we will research how to identify and avoid optimization attempts with diminishing returns. This will speedup the optimization process for an inexperienced programmer and also yield new insights for an experienced one.

The fifth challenge is to detect and exploit a potential phase behavior of TM applications and integrate this analysis in the VisOTMA framework. In case the behavior of the TM application has periods with high and low conflict probability, this behavior of the application can be detected and exploited. Exploiting these phases is motivated through the different proposed TM designs: optimistic conflict detection schemes detect conflicts at commit-time whereas pessimistic schemes check for conflicts at encounter-time. In the optimistic case, a conflict early in the execution of a transaction is noticed at commit time so that computations are performed that have to be undone. The wasted work in this transaction can be reduced, when switching from the optimistic to the pessimistic scheme. In this thesis, we transfer algorithms, Signal Analysis and Wavelet-based classification, that have been proposed for phase detection in other contexts, to TM. These enable the offline detection of a TM phase behavior.

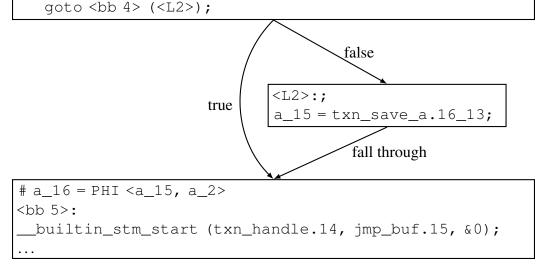

To complement the information retrieved in the above challenges, we gather and interpret static information. First, we design and implement initial support for Transactional Memory in GCC. This freely available support may provide the baseline for a wide-spread adoption of TM. The original GTM design, a design for the integration of TM in the programming language C with GCC, is presented, implemented, and evaluated. Second, we research how to exploit static information inside of a compiler to select suited STM parameters to project the run time behavior of that TM application and give advice to the application developer. This approach is called MAPT for analysis of Memory Access Patterns in Transactions and helps to select an STM parameter at compile-time.

In short the main contributions of this thesis are the following:

- a tracing methodology for STM that captures the genuine TM application's behavior

in a way that generating traces has a lower influence on the TM application and a

higher throughput than a comparable Pin tool while at the same time optionally

employing compression algorithms,

- a low-overhead tracing solution for hybrid TM that exploits the properties of the TMbox architecture to achieve low-intrusiveness and enables a guided optimization process through visualization that yields a relative performance gain of 24.1 % when moving from STM-only to a hybrid-ETL variant on TMbox,

- a set of best practices that describes how to use TM on IBM's new Blue Gene/Q architecture with HTM support. Applying these practices yields a speedup of 1.22 over a simple transactional version of a Monte Carlo Benchmark and a speedup of

4.4 for an optimized TM version of a Smoothed Particle Hydrodynamics method from the PARSEC suite over a simple TM version. Additionally three tools are specifically designed for the evaluation and optimization of TM performance that highlight the interaction of TM and prefetching on BG/Q and help to identify the cause for the missing performance with TM in a Lagrange hydrodynamics proxy application,

- a novel framework for the optimization of STM applications (VisOTMA) that provides the following additional features

- visualization of TM applications to identify pathological behavior that can help to tune the transaction's size in a way that the tuned TM version of a simulated fluid flow benchmark, implemented with a smoothed particle hydrodynamics method, yields a speedup of 1.43 over the initial TM version,

- correlation of TM characteristics with microarchitecture events to better steer the optimization process and gain insights in the run time behavior and the applicability of STM to two variants of the method of Conjugate Gradients and reveal details whether the changed utilization of the microarchitecture is due to an altered convergence behavior or the choice of a different algorithmic formulation while at the same time comparing TM to other means of synchronization,

- EigenOpt, an exploration tool that speeds up the optimization process for inexperienced programmers and excludes directions with diminishing returns which also helps experienced programmers,

- algorithms for the detection of phase behavior in TM applications uncovering the additional potential of exploiting the resulting phase changes through adaptation of the TM system,

- design, implementation, and evaluation of inital support for TM in the GCC compiler,

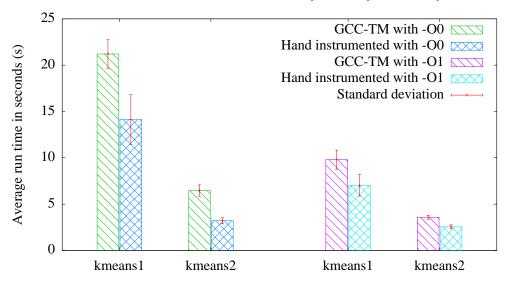

- a new approach that gathers and exploits static information to select suited STM parameters and speedup the run time of the application yielding a relative improvement in execution time of 14.7% for a transactional K-means clustering algorithm and 16.9% for learning a Bayesian network implemented with transactions.

#### Zusammenfassung

Transactional Memory (TM) wurde als eine Architekturerweiterung vorgeschlagen, die die Verwendung von Datenstrukturen ohne Sperren ermöglichen soll. Durch die Allgegenwart von heutigen Mehrkernsystemen bekommt diese Idee neuen Schwung. Als Motivation für die Erfindung von TM diente die zu vereinfachende Synchronisation von mehreren parallel ablaufenden Fäden in einem System mit gemeinsam verwendetem Speicher. TM unterstützt hierbei einen optimistischen Ablauf der Transaktionen, welcher im Gegensatz zum pessimistischen Ablauf keinen wechselseitigen Ausschluss der Fäden erzwingt und somit eine parallele Abarbeitung unter der Bedingung, dass keine Wettlaufsituation auftritt, ermöglicht. Im Fall einer solchen Wettlaufsituation, die zum Beispiel dadurch entstehen kann, dass zwei Transaktionen auf die gleiche Speicherstelle schreiben, führt dies zu einem Konflikt der beiden Transaktionen, der erkannt und aufgelöst werden muss. Hierfür gibt es ein TM-Laufzeitsystem, welches die Zugriffe auf gemeinsam verwendeten Speicher innerhalb von Transaktionen überwacht. Diese Laufzeitsysteme für TM können in Software, kurz STM, Hardware, kurz HTM, oder als Hybridsystem realisiert werden. Die meisten der Forschungssysteme im Bereich von TM sind spezialisiert auf Spracherweiterungen, Unterstützung durch Übersetzer oder die Optimierung von algorithmischen Details des TM-Systems. Jedes der resultierenden TM-Systeme besitzt eine unterschiedliche Leistungscharakteristik und eine Vielzahl von Parametern, die abgestimmt werden können. Der hieraus resultierende Optimierungsraum überwältigt den Anwendungsprogrammierer, der jedoch das Zielpublikum für die Einführung von TM darstellte. Im Gegensatz zu anderen Forschungsaktivitäten beschäftigt sich diese Arbeit mit Werkzeugen für TM, welche die Lücke zwischen dem Anwendungsprogrammierer und dem Entwickler des TM-Systems überbrücken sollen. Diese Werkzeuge ermöglichen Einblicke in das Laufzeitverhalten einer Anwendung mit TM und leiten den Anwendungsentwickler zur Optimierung der TM-Anwendung an.

Im Gegensatz zu anderen verwandten Arbeiten, die die Werkzeuge auf eine bestimmte Kombination von Programmiersprache und TM-System zuschneiden, präsentiert diese Arbeit Lösungen für mehrere TM-Systeme (Software, Hardware und hybride) und bezieht das Setzen von unterschiedlichen Parametern für jedes dieser TM-Systeme mit ein. Zudem verwenden die vorgeschlagenen Methoden und Verfahren zur Optimierung von TM-Anwendungen Informationen von allen Schichten des Software-Systems. Statische Informationen, Informationen über das Laufzeitverhalten der Anwendung, sowie Expertenwissen müssen extrahiert und gesammelt werden, um diese neuen Methoden und Strategien zur Optimierung von TM-Anwendungen zu entwickeln. Das Erheben und Verwenden der benötigten Informationen verlangt nach der Bewältigung der folgenden Herausforderungen.

Als erste Herausforderung muss das unverfälschte Laufzeitverhalten der TM-Anwendung festgehalten werden. Dieses ist von hoher Bedeutung, weil Transaktionen sehr empfindlich auf eingeführte Verzögerungen eines Fadens reagieren, wodurch künstliche Konflikte mit anderen Transaktionen ausgelöst werden können. Hierdurch kann das aufgezeichnete Anwendungsverhalten durch die Aufzeichnungsmechanismen selbst verfälscht werden. Folglich muss eine leichtgewichtige Lösung für das Erstellen von Spurdateien, verbunden mit einer geringen Verfälschung der Anwendung, entwickelt und ausgewertet werden. Diese Arbeit präsentiert ähnliche Lösungen für STM- und hybride TM-Systeme, welche Spurdateien der Ereignisse der TM-Anwendung erzeugen. Für das STM-System wird für die Aufzeichnung der häufig vorkommenden Ereignisse, wie beispielsweise transaktionale Lese- und Schreibzugriffe, die Bandbreitenbeschränkung der Festplatte schnell zum Flaschenhals. Um diesem entgegenzuwirken, muss eine Reduktion der Daten, die auf die Festplatte geschrieben werden, erreicht werden. Hierfür erforschen wir wie diese Ereignisse zur Laufzeit komprimiert werden können, ohne die Anwendung damit zu stören. Ein mehrfädiges Kompressionsschema für Spuren von TM-Ereignissen wird entworfen, implementiert und ausgewertet. Wir erweitern TinySTM, eine Wort-basierte, quelloffene STM-Implementierung mit der Infrastruktur zum Erstellen von TM-Ereignisspuren. In Folge des leichtgewichtigen und komprimierenden Schemas für Spuren von TM-Ereignissen, generiert die resultierende TracingTinySTM Ereignis-Dateien, die das unverfälschte Verhalten der TM-Anwendung wiedergeben. Eine Lösung zur Spurerstellung mit geringem Mehraufwand wird für ein FPGA-basiertes hybrides TM-System, genannt TMbox, demonstriert. Jedes Rechenelement wird um eine Überwachungseinheit erweitert, die bei der Ausführung interessanter Instruktionen ein entsprechendes Ereignis generiert. Falls eine überwachte Instruktion auftritt, wird ein Zeitstempel generiert und gemeinsam mit dem Ereignis an die Aufzeichnungseinheit weitergegeben. Diese Einheit benutzt Leerzeiten auf dem Bus, um diese Ereignisse an den Speicher des Hauptcomputers zu schicken. Obwohl diese Methoden auf den speziellen Kontext von TM zugeschnitten sind und dort angewendet werden, sind sie universell und könnten auch in einem anderen Kontext angewendet werden. Andere Anwendungsgebiete sind das Überwachen von beliebigen Ereignissen in einem FPGA-basierten Prozessor-Prototypen oder das Aufzeichnen und Komprimieren von Ereignissen in einer Mathematikbibliothek.

Die zweite Herausforderung entsteht mit der Veröffentlichung der Blue Gene/Q Architektur, welche eine Unterstützung für HTM besitzt, durch IBM. Wir erstellen eine Menge an bewährten Vorgehensweisen, die es dem Anwendungsentwickler ermöglichen, das volle Potential der Architektur inklusive des TM-Systems zu nutzen. Zu diesem Zweck führen wir einen neuen Benchmark, genannt CLOMP-TM, ein, welcher über eine Vielzahl an Parametern verfügt, die es ermöglichen Transaktionen mit unterschiedlichen Granularitäten, Konfliktraten und verschiedenen Rechenkernen, welche im wissenschaftlichen Rechnen Verwendung finden, zu erforschen. Dieses ermöglicht neue Einsichten durch die Evaluation des TM-Systems und den Vergleich der Leistung mit anderen Synchronisationprimitiven, welche von OpenMP unterstützt werden. Zudem benötigt diese neue BG/Q Architektur auch TM-spezifische Werkzeugunterstützung, um die Optimierung von wissenschaftlichen Anwendungen zu ermöglichen. Eine Lösung, die auf der Erzeugung von Spuren von TM-Ereignissen basiert, um das Laufzeitverhalten festzuhalten, ist für dieses proprietäre System nicht bzw. nur eingeschränkt durchführbar. Das HTM-System benötigt eine vollständige Softwareunterstützung, die Übersetzer und Laufzeitsystem umfasst. Folglich entwerfen, implementieren und bewerten wir drei verschiedene Werkzeuge für TM, welche es Programmierern ermöglichen, die Feinheiten der Ausführung mittels TM zu ergründen und tragen damit Folgendes zum Stand der Forschung bei:

• das erste Werkzeug, welches das Erstellen von Laufzeitprofilen von Anwendungen mit MPI, OpenMP und TM auf der BG/Q Architektur ermöglicht,

- ein Werkzeug für TM, welches durch Ereignisspuren von TM Statistiken in Kombination mit der Auslastung der Architektur, welche auf der Granularität des ausführenden Fadens erhoben werden, eine detaillierte Analyse mittels des Visualisierungswerkzeugs Vampir, das dem Stand der Technik entspricht, ermöglicht und

- ein Werkzeug, das den Mehraufwand, der mit TM einhergeht, misst, den jeweiligen Ausführungsphasen einer Transaktion zuordnet und damit ermöglicht, dass Optimierungsversuche direkt auf die relevanten Teile der Softwareschichten abzielen können.

Diese Werkzeuge enthüllen die Wechselwirkung zwischen TM-System und dem Vorabladen von Werten aus dem Speicher auf der BG/Q Architektur und helfen dabei, die Auswirkungen von Entwurfsentscheidungen für die Anwendung und die Auswahl des TM Ausführungsmodus zu verstehen. Darüber hinausgehend ermöglichen diese Werkzeuge ein umfassenderes Verständnis der Synchronisationsmechanismen in *LULESH*, einer Lagrange-Hydrodynamik-Stellvertreter-Anwendung und identifizieren den Grund für die fehlende Leistung mit TM.

Die dritte Herausforderung ist die Korrelation der gesammelten TM-Charakteristiken mit Ereignissen, die das Verhalten der Mikroarchitektur beschreiben, um dieses zur Optimierung von STM-Anwendungen zu verwenden. Obwohl diese Art der Korrelation selbst nicht neu ist, ist sie extrem hilfreich und wurde in diesem Kontext noch nicht weitergehend untersucht. Die korrekte Interpretation der erhobenen Werte ist neben der Auswahl von geeigneten Parametern der Mikroarchitektur, welche dann überwacht werden, von höchster Bedeutung. Um die Optimierung für Menschen zu vereinfachen, entwickeln wir das Rahmenwerk VisOTMA zur Visualisierung von TM-Anwendungen. Dieses ermöglicht es in einem Nachbearbeitungsschritt dem Programmierer häufig konfligierende Transaktionen und die zugehörigen Werte der Mikroarchitekturparameter zu identifizieren.

Die Visualisierung dieser aggregierten Daten muss so erfolgen, dass sogar ein unerfahrener Programmierer pathologische Ausführungsmuster erkennen kann. Dies stellt die vierte Herausforderung dar. Bisher wurden Optimierungen von TM-Experten vorgenommen, die ein ausgezeichnetes Wissen über das zugrundeliegende TM-System hatten. Ein unerfahrener Programmierer hat dieses Wissen über das TM-System nicht oder will es sich nicht aneignen. Folglich verfolgt dieser bei der Optimierung der TM-Anwendung eine Strategie, die auf Versuch und Irrtum beruht. Um diesen Prozess zu beschleunigen, führen wir EigenOpt ein. EigenOpt ist ein Erkundungswerkzeug, welches auf EigenBench beruht und in das VisOTMA-Rahmenwerk integriert wird. Mit der Hilfe von EigenOpt kann jeder Programmierer das charakteristische TM-Laufzeitverhalten in Form von Parametern für EigenBench festhalten. Diese Parameter in Verbindung mit EigenBench werden kanonisch verwendet, um den Raum für Optimierungen zu erforschen. Mit diesem Werkzeug können Optimierungsansätze, die keinen Erfolg versprechen, ausgeschlossen werden, ohne die Anwendung zu modifizieren. In dieser Arbeit werden wir erforschen, wie man das charakteristische TM-Anwendungsverhalten automatisiert festhält und Optimierungsansätze ohne Aussicht auf Gewinn identifiziert und vermeidet. Dies wird den Optimierungsvorgang für einen unerfahrenen Programmierer beschleunigen und neue Einsichten für einen erfahrenen Programmierer bereithalten.

Die fünfte Herausforderung besteht in der Detektion und dem Ausnutzen eines potentiellen Phasenverhaltens der TM-Anwendung und in der Integration dieser Analyse in das bestehende Rahmenwerk VisOTMA. Für den Fall, dass das TM-Anwendungsverhalten Perioden mit hohem und niedrigem Konfliktpotential aufweist, kann dieses Anwendungsverhalten erkannt und eventuell ausgenutzt werden. Die Ausnutzung dieses Phasenverhaltens wird motiviert durch die verschiedenen TM-Entwürfe: eine optimistische Konflikterkennung erkennt Konflikte erst zur Zeit des Abschlusses der Transaktion, während eine pessimistische Konflikterkennung beim Zugriff auf die Daten bereits Konflikte erkennt. Wenn im optimistischen Fall ein Konflikt früh in der Ausführung einer Transaktion auftritt und erst beim Abschluss der Transaktion erkannt wird, werden weitere Berechnungen angestellt, die zum Ende der Transaktion wieder rückgängig gemacht werden müssen. Diese verschwendete Arbeit in dieser Transaktion kann verringert werden, wenn man von dem optimistischen zum pessimistischen Schema wechselt. In dieser Arbeit übertragen wir Algorithmen wie die Signal Analyse und eine Klassifikation basierend auf Wavelets, welche für die Phasenerkennung in anderen Bereichen vorgeschlagen wurden, auf TM. Diese Algorithmen ermöglichen die Erkennung eines Phasenverhaltens in TM.

Um die Informationen, die in den vorhergehenden Herausforderungen erhoben wurden zu ergänzen, sammeln und interpretieren wir auch statische Informationen. Zuerst entwerfen und implementieren wir eine Unterstützung von Transactional Memory im GCC. Diese frei verfügbare Unterstützung, genannt GTM, kann als Basis für einen weitverbreiteten Einsatz von TM dienen. Der ursprüngliche Entwurf von GTM wird präsentiert, implementiert und ausgewertet. Zweitens erforschen wir, wie man statische Informationen innerhalb des Übersetzers verwenden kann, um geeignete Parameter einer STM-Bibliothek anhand des erwarteten Laufzeitverhaltens der TM-Anwendung auszuwählen und den Anwendungsprogrammierer damit zu unterstützen. Dieser Ansatz wird von uns MAPT genannt, da er die Speicherzugriffsmuster in Transaktionen analysiert und bei der Selektion eines STM-Parameters zur Übersetzungszeit unterstützt.

Zusammengefasst sind die Hauptbeiträge dieser Arbeit die folgenden:

- eine Methodik zur Spurerstellung von STM-Ereignissen, die das unverfälschte TM-Anwendungsverhalten in einer Form festhält, so dass diese einen geringeren Einfluss auf die TM-Anwendung und einen höheren Durchsatz zur Folge hat als ein vergleichbares Werkzeug, welches auf dem dynamischen Binärinstrumentierer Pin basiert, wobei bei unserem Ansatz optional Kompressionsalgorithmen zum Einsatz kommen,

- eine Lösung zur Spurerstellung von Ereignissen in hybriden TM-Systemen, die wenig Overhead erzeugt und Eigenschaften der TMbox Architektur ausnutzt, um eine geringe Beeinflussung und eine Anleitung zum Optimierungsprozess mittels Visualisierung bereitstellt, die einen relativen Leistungsgewinn von 24.1 % zur Folge hat, wenn man von einer Ausführung in STM zu einer hybrid-ETL Variante auf TMbox wechselt,

- eine Menge an bewährten Vorgehensweisen, die beschreiben, wie man das neue HTM-System der Blue Gene/Q Architektur verwendet. Die Anwendung dieser Vorgehensweisen zeigt einen Gewinn von 1.22 im Vergleich zu einer einfachen transaktionalen Version eines Monte-Carlo-Benchmarks und einen Gewinn von 4.4 für eine optimierte TM-Version einer geglätteten Partikelmethode der Hydrodynamik aus der PARSEC-Sammlung. Zusätzlich werden drei Werkzeuge speziell für die Auswertung und Optimierung der Leistung von TM entworfen, so dass diese die Interaktionen zwischen TM-System und dem Vorabladen von Werten aus dem Speicher auf der BG/Q beleuchten und helfen den Grund für die fehlende Leistung von TM in einer Lagrange-Hydrodynamik-Stellvertreter-Anwendung zu identifizieren,

- ein neues Rahmenwerk zur Optimierung von STM-Anwendungen (VisOTMA), welches die folgenden zusätzlichen Eigenschaften besitzt:

- die Visualisierung des TM-Anwendungsverhaltens ermöglicht, um pathologisches Verhalten der TM-Anwendung identifizieren zu können und zusätzlich hilft die Transaktionsgröße in einer Art und Weise anzupassen, dass die optimierte STM-Variante einer geglätteten Partikelmethode der Hydrodynamik aus der PARSEC-Sammlung einen Laufzeitgewinn von 1.43 gegenüber der initialen TM-Version erzielt,

- die Korrelation von TM-Charakteristika und Ereignissen der Mikroarchitektur, welche es ermöglicht, den Optimierungsprozess besser zu steuern und hierfür Einblicke in das Laufzeitverhalten und die Anwendbarkeit von STM gewährt. Diese Methode wird auf zwei Varianten des mathematischen Verfahrens der konjugierten Gradienten angewendet und gibt detailliert Aufschluss darüber, welche Veränderungen der Nutzung der Mikroarchitektur durch ein verändertes Konvergenzverhalten und welche durch andere Effekte der Umformulierung des Verfahrens bedingt sind, wobei zusätzlich TM mit anderen Möglichkeiten zur Synchronisation verglichen wird,

- EigenOpt, ein Erkundungswerkzeug, welches die Optimierung sogar f

ür unerfahrene Entwickler beschleunigt und Optimierungsans

ätze, die keinen Erfolg versprechen, ausschlie

ßt, ohne dass die Anwendung modifiziert werden muss,

- Algorithmen f

ür die Erkennung eines Phasenverhaltens in TM-Anwendungen, die zus

ätzliches Potential zur Ausnutzung der Phasenwechsel durch die Anpassung des TM-Systems aufzeigen,

- den Entwurf, die Implementierung und die Auswertung der initialen Unterstützung des Übersetzers für TM im GCC,

- einen neuen Ansatz, der statische Informationen sammelt und ausnutzt, um einen passenden Parameter der STM-Bibliothek auszuwählen und einen Laufzeitgewinn der Anwendung mit einer relativen Steigerung von 14.7 % für einen transaktionalen K-means Bündelungsalgorithmus und 16.9 % für das Lernen eines Bayes'schen Netzwerks mittels Transaktionen erzielt.

### Contents

| 1 | Mot  | ivation for Tools targeting Transactional Memory                      | 1  |

|---|------|-----------------------------------------------------------------------|----|

|   | 1.1  | Transactional Memory for Parallel Programming                         | 1  |

|   | 1.2  | The Missing Performance with TM                                       | 2  |

|   | 1.3  | Tool Support for Simplifying the Optimization of TM Programs          | 2  |

|   | 1.4  | Organization of this Thesis                                           | 6  |

| 2 | Fun  | damentals                                                             | 9  |

|   | 2.1  | Transactional Memory Concept and Properties                           | 9  |

|   | 2.2  | Realization of Transactional Memory                                   | 11 |

|   |      | 2.2.1 Software Transactional Memory                                   | 12 |

|   |      | 2.2.2 Hardware Transactional Memory                                   | 16 |

|   |      | 2.2.3 Hybrid Transactional Memory                                     | 18 |

|   | 2.3  | Memory Model for Transactional Memory                                 | 19 |

| 3 | Rela | ated Work                                                             | 23 |

|   | 3.1  | Compiler Support for TM                                               | 24 |

|   | 3.2  | Information Retrieval in TM Systems                                   | 28 |

|   | 3.3  | Tools for the Optimization of TM Applications                         | 30 |

|   | 3.4  | FPGAs and Hybrid TM                                                   | 34 |

|   | 3.5  | Programming with TM                                                   | 35 |

|   | 3.6  | Performance, Energy, and Modeling of TM                               | 38 |

|   | 3.7  | Adaptive STMs                                                         | 39 |

|   | 3.8  | Phase Detection and Prediction                                        | 41 |

|   | 3.9  | Open Questions with the State-of-the-Art                              | 42 |

| 4 | Con  | ncept and Overview                                                    | 45 |

|   | 4.1  | Concept for the Optimization of TM Applications                       | 46 |

|   | 4.2  | Components that Implement the Concept                                 | 47 |

|   | 4.3  | Experimental Setup                                                    | 48 |

| 5 | TM-  | specific Trace Generation for STM and Hybrid TM Systems               | 51 |

|   |      | Augmenting TinySTM with Trace Generation Facilities                   | 51 |

|   |      | 5.1.1 Minimizing Application Disturbances                             | 52 |

|   |      | 5.1.2 Implication of Lightweight Trace Generation on Offline Analysis | 53 |

|   |      | 5.1.3 The Influence of Tracing on the Runtime                         | 53 |

|   |      | 5.1.4 Online Trace Compression                                        | 56 |

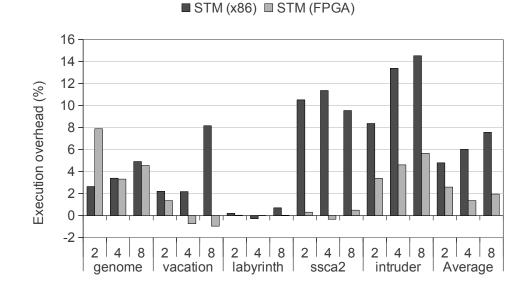

|   |      | 5.1.5 Impact of Trace Generation on STAMP Benchmarks                  | 58 |

|   | 5.2  | Event Logging in a Hybrid TM System (TMbox)                           | 60 |

|   |      | 5.2.1 Design of the Event Logging Extensions                          | 62 |

|   |      | 5.2.2     | Implementation Details                                        | 63      |

|---|------|-----------|---------------------------------------------------------------|---------|

|   | 5.3  | Compa     | arison of SW- and HW-based Monitoring of TM Events            | 64      |

|   | 5.4  | Summ      | arizing the Trace Generation                                  | 66      |

| 6 | Vier | valizati  | on and Tool Support for TM Applications in Unmanage           | Ч       |

| 0 |      | guage     |                                                               | u<br>69 |

|   | 6.1  |           | clear contraction Cycle of TM Applications                    |         |

|   | 011  | 6.1.1     | Studying the Influence of Transaction Size on the Performance |         |

|   |      | 6.1.2     | Retrieving TM Events and Memory Requests                      |         |

|   |      | 6.1.3     | Visualization with Paraver                                    |         |

|   | 6.2  | Revea     | ling Optimization Potential                                   |         |

|   |      | 6.2.1     | Transaction Size                                              | 82      |

|   |      | 6.2.2     | Visualization of Pathological TM Cases                        | 84      |

|   |      | 6.2.3     | Evaluation of a Transactified PARSEC Benchmark                | 86      |

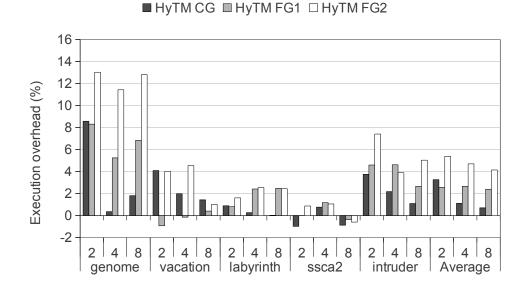

|   |      | 6.2.4     | Optimization of Hybrid TM with TMbox                          | 88      |

|   | 6.3  | Conju     | gate Gradients Solver                                         | 90      |

|   |      | 6.3.1     | Pipelined Conjugate Gradients Solver                          |         |

|   |      | 6.3.2     | Comparison of CG and Pipelined CG                             | 97      |

|   |      | 6.3.3     | Findings with Normal and Pipelined CG                         |         |

|   | 6.4  |           | Detection in TM Applications                                  |         |

|   |      | 6.4.1     | Comparison with Related Work                                  |         |

|   |      | 6.4.2     | Design of the TM Phase Detector                               |         |

|   |      | 6.4.3     | Applying Phase Detection Algorithms to the STAMP Suite        |         |

|   |      | 6.4.4     | Discussion of Phase Detection for TM                          |         |

|   | 6.5  | Eigen(    |                                                               |         |

|   |      | 6.5.1     | Parameters of Eigenbench                                      |         |

|   |      | 6.5.2     | Changes to the TracingTinySTM                                 |         |

|   |      | 6.5.3     | Adjustments to Post-Processing Tools                          |         |

|   |      | 6.5.4     | Intrusiveness with EigenOpt                                   |         |

|   |      | 6.5.5     | Results with EigenOpt                                         | 127     |

|   | 6.6  | 6.5.6     | Outlook for EigenOpt                                          |         |

|   | 0.0  | Concio    |                                                               | 129     |

| 7 | Con  | npiler \$ | Support for TM and Guidance Through Static Information        | 131     |

|   | 7.1  | Towar     | ds TM for GCC                                                 | 131     |

|   |      | 7.1.1     | Design                                                        | 132     |

|   |      | 7.1.2     | Expansion                                                     | 133     |

|   |      | 7.1.3     | Checkpointing                                                 | 133     |

|   |      | 7.1.4     | Optimizations and Extensions                                  | 134     |

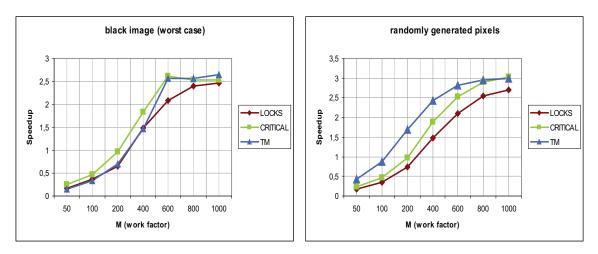

|   |      | 7.1.5     | Parallelization of Irregular Reductions                       |         |

|   |      | 7.1.6     | Overinstrumentation with GCC                                  | 138     |

|   |      | 7.1.7     | Improvements with GCC-4.7                                     |         |

|   |      | 7.1.8     | Concluding Remarks for TM in GCC                              |         |

|   | 7.2  |           | ion of the Conflict Detection Granularity in an STM           |         |

|   |      | 7.2.1     | Detection of Memory Access Patterns in Transactions           |         |

|   |      | 7.2.2     | Evaluation                                                    |         |

|   |      | 7.2.3     | Conclusion and Outlook for MAPT                               | 151     |

| 8  | First | Experience with BG/Q Performance                           | 153 |

|----|-------|------------------------------------------------------------|-----|

|    | 8.1   | Demands on Transactional Memory in HPC                     | 153 |

|    | 8.2   | Comparison with Related Work                               | 154 |

|    | 8.3   | Experimental Setup with BG/Q                               |     |

|    |       | 8.3.1 Overview of BG/Q's TM Hardware                       | 155 |

|    |       | 8.3.2 Application Perspective in BG/Q's TM Software Stack  | 156 |

|    |       | 8.3.3 The CLOMP-TM Benchmark                               | 156 |

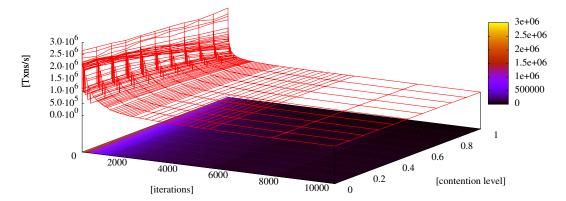

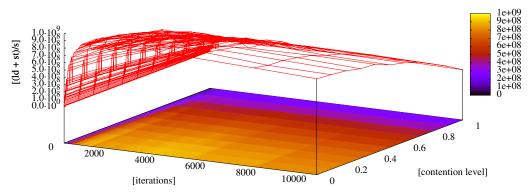

|    | 8.4   | Characterizing TM Performance using CLOMP-TM               | 158 |

|    |       | 8.4.1 Synchronization Overhead                             | 160 |

|    |       | 8.4.2 Conflict Probability                                 | 162 |

|    |       | 8.4.3 Tuning the BG/Q TM Runtime Environment               | 162 |

|    |       | 8.4.4 CLOMP-TM with Mixed Scatter Modes                    | 166 |

|    |       | 8.4.5 Using TM in the Context of MPI Applications          | 166 |

|    |       | 8.4.6 Finding a Competitive Task to Thread Ratio           | 168 |

|    | 8.5   | Lessons Learned                                            | 168 |

|    | 8.6   | Application Case Studies                                   | 169 |

|    |       | 8.6.1 MCB: A Proxy Application for Monte Carlo Simulations | 169 |

|    |       | 8.6.2 Fluidanimate from the PARSEC Suite                   | 170 |

|    | 8.7   | Summarizing the First Experience with BG/Q                 | 171 |

| 9  | Tool  | Support for TM on BG/Q                                     | 173 |

|    | 9.1   | Introduction and Motivation for Tools on BG/Q              | 173 |

|    | 9.2   | Design of a TM Tool for IBM's Run Time Stack               |     |

|    |       | 9.2.1 A Profiling Tool for TM                              |     |

|    |       | 9.2.2 A Tracing Tool for TM                                |     |

|    |       | 9.2.3 A Tool for Measuring TM Overheads                    |     |

|    |       | 9.2.4 Common Implementation Details for the Tools          |     |

|    | 9.3   | TM Tools: Experimental Setup and Measurements              |     |

|    |       | 9.3.1 Experimental Setup: BG/Q                             |     |

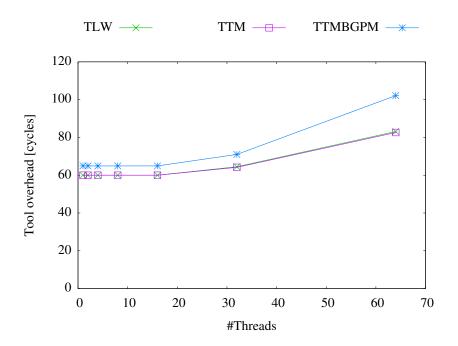

|    |       | 9.3.2 Tool Overhead of the Overhead Tool                   |     |

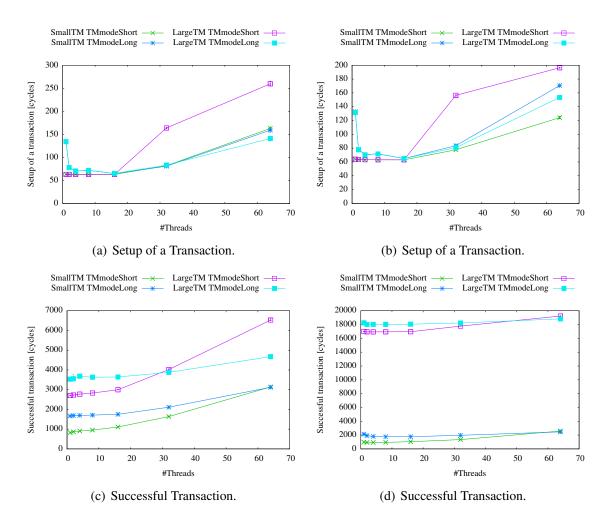

|    |       | 9.3.3 Break Down of TM Overheads                           |     |

|    |       | 9.3.4 Influence of Scrub Rate on Application's Behavior    |     |

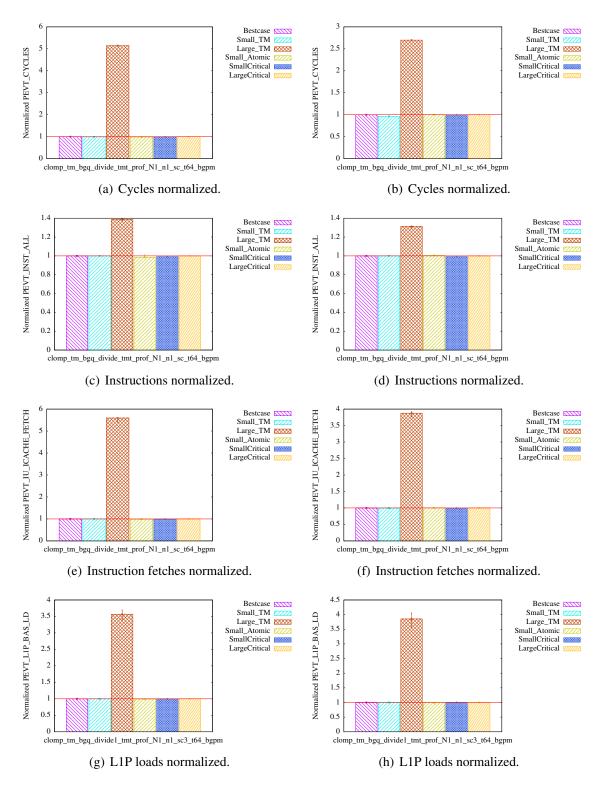

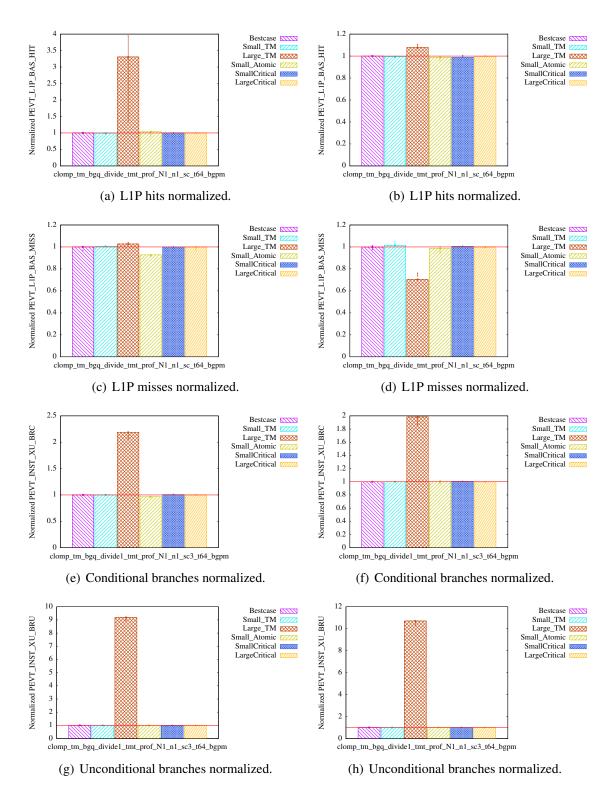

|    |       | 9.3.5 Implications of the TM Mode on the Microarchitecture |     |

|    |       | 9.3.6 Long Transactions at Any Cost?                       |     |

|    | 9.4   | Profiling LULESH                                           |     |

|    | 9.5   | A Case Study with Vampir Visualizing TM Performance Data   |     |

|    | 9.6   | State of the Art                                           |     |

|    | 9.7   | Conclusion                                                 |     |

| 10 | Con   | clusion and Future Work                                    | 203 |

|    |       | Summary and Conclusion                                     |     |

|    |       | 10.1.1 Information Retrieval for Hybrid TM and STM         |     |

|    |       | 10.1.2 Optimization of TM Applications                     |     |

|    |       | 10.1.3         Hybrid TM                                   |     |

|    |       | 10.1.4 Compilation and Static Information                  |     |

|    |       | 10.1.5 HTM of BG/Q from an Application's Perspective       |     |

|    |       | 10.1.6 Tool Support for TM on BG/Q                         |     |

|    | 10.2  | Outlook and Future Work                                    |     |

209

231

| xiv          | C |

|--------------|---|

| Bibliography |   |

| Appendix | Curriculum | Vitae |

|----------|------------|-------|

|----------|------------|-------|

### List of Publications Relevant for this Thesis

- [HJK<sup>+</sup>13] Vincent Heuveline, Sven Janko, Wolfgang Karl, Björn Rocker, and Martin Schindewolf. Software Transactional Memory, OpenMP and Pthread Implementations of the Conjugate Gradients Method – A Preliminary Evaluation. In Michel Daydé, Osni Marques, and Kengo Nakajima, editors, *High Performance Computing for Computational Science - VECPAR 2012*, volume 7851 of *Lecture Notes in Computer Science*, pages 300–313. Springer Berlin / Heidelberg, July 2013.

- [KSS<sup>+</sup>12] Philipp Kirchhofer, Martin Schindewolf, Nehir Sonmez, Oriol Arcas, Osman S. Unsal, Adrian Cristal, and Wolfgang Karl. Enhancing an HTM System with Monitoring, Visualization and Analysis Capabilities. In *Euro-TM Workshop on Transactional Memory (WTM 2012)*, April 2012. Abstract available at http://www.eurotm.org/action-meetings/wtm2012/ program/abstracts#Kirchhofer.

- [SAK<sup>+</sup>12] Nehir Sonmez, Oriol Arcas, Philipp Kirchhofer, Martin Schindewolf, Osman S. Unsal, Adrián Cristal, and Wolfgang Karl. A low-overhead Profiling and Visualization Framework for Hybrid Transactional Memory. In FCCM 2012: The 20th Annual IEEE International Symposium on Field-Programmable Custom Computing Machines, pages 1–8, 2012. http: //fccm12.cse.sc.edu/4699a001.pdf.

- [SBG<sup>+</sup>12] Martin Schindewolf, Barna Bihari, John Gyllenhaal, Martin Schulz, Amy Wang, and Wolfgang Karl. What Scientific Applications Can Benefit from Hardware Transactional Memory? In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, SC '12, pages 90:1–90:11, Los Alamitos, CA, USA, 2012. IEEE Computer Society Press.

- [SCK<sup>+</sup>09] Martin Schindewolf, Albert Cohen, Wolfgang Karl, Andrea Marongiu, and Luca Benini. Towards Transactional Memory Support for GCC. In *First International Workshop on GCC Research Opportunities*, GROW '09, January 2009. Held in conjunction with: the fourth International Conference on High-Performance Embedded Architectures and Compilers (HiPEAC).

- [SEK11] Martin Schindewolf, Alexander Esselson, and Wolfgang Karl. Compiler-Assisted Selection of a Software Transactional Memory System. In Mladen Berekovic, William Fornaciari, Uwe Brinkschulte, and Cristina Silvano, editors, Architecture of Computing Systems - ARCS 2011, volume 6566 of Lecture

Notes in Computer Science, pages 147–157. Springer Berlin / Heidelberg, 2011.

- [SK09] Martin Schindewolf and Wolfgang Karl. Investigating Compiler Support for Software Transactional Memory. In Proceedings of ACACES 2009 Poster Abstracts: Advanced Computer Architecture and Compilation for Embedded Systems, pages 89–92, Terrassa, Spain, July 2009. Academia Press, Ghent.

- [SK12] Martin Schindewolf and Wolfgang Karl. Capturing Transactional Memory Application's Behavior – The Prerequisite for Performance Analysis. In *International Conference on Multicore Software Engineering, Performance and Tools (MSEPT 2012)*, volume 7303 of *Lecture Notes in Computer Science*, pages 30–41. Springer Verlag, May 31–June 1, 2012.

- [SRKH13] Martin Schindewolf, Björn Rocker, Wolfgang Karl, and Vincent Heuveline. Evaluation of two Formulations of the Conjugate Gradients Method with Transactional Memory. In Felix Wolf, Bernd Mohr, and Dieter an Mey, editors, 19th International European Conference on Parallel and Distributed Computing Euro-Par 2013, volume 8097 of Lecture Notes in Computer Science. Springer Berlin / Heidelberg, 2013. Accepted for publication.

- [SSB<sup>+</sup>12] Martin Schindewolf, Martin Schulz, Barna Bihari, John Gyllenhaal, Amy Wang, and Wolfgang Karl. Performance Analysis of and Tool Support for Transactional Memory on BG/Q. In Euro-TM Workshop on Transactional Memory (WTM 2012), April 2012. Abstract available at http://www.eurotm.org/action-meetings/wtm2012/ program/abstracts#Schindewolf.

# **List of Figures**

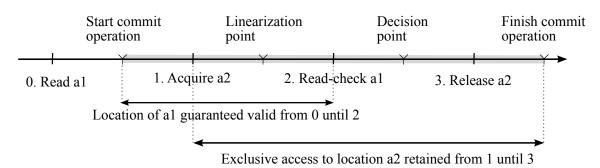

| 2.1                                                                                                                             | Commit phases in an STM system                                                                                                               | 13                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

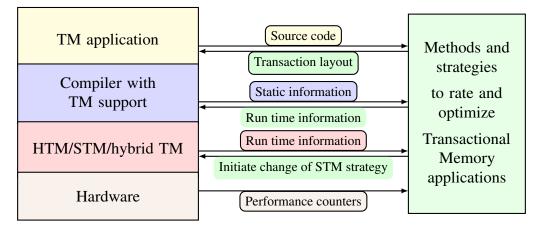

| 4.1<br>4.2                                                                                                                      | Schematic interaction of components in a system with TM software stack.<br>Overview and relationship of components presented in this thesis. | 46<br>47                                                       |

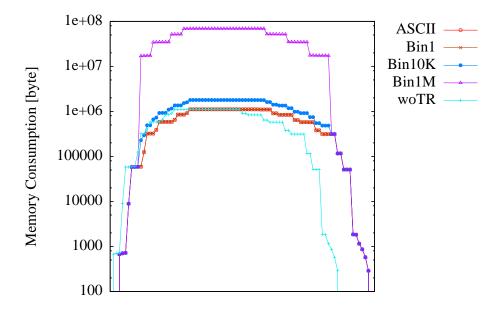

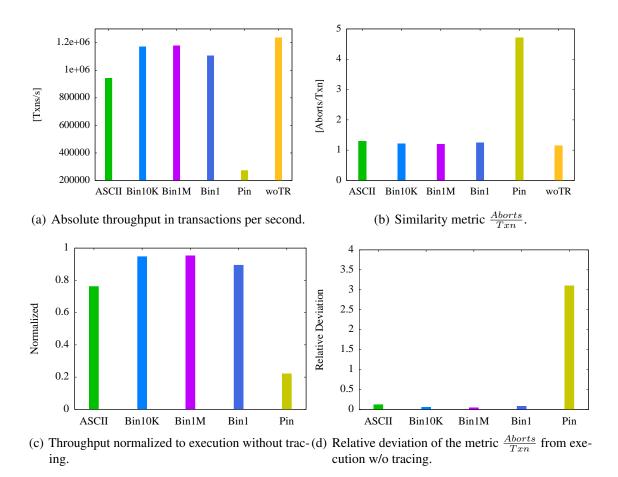

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                     | Heap size of the bank application                                                                                                            | 54<br>55<br>56<br>57<br>57<br>58<br>59<br>61<br>62<br>65<br>66 |

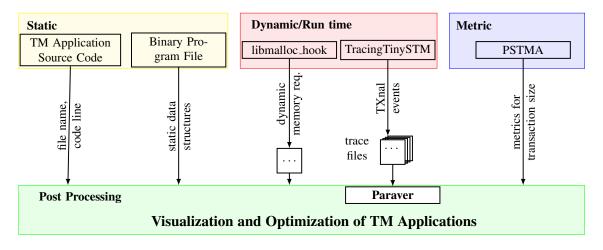

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.2</li> </ul> | Components and interplay in the VisOTMA framework                                                                                            | 71<br>74<br>75<br>78<br>79<br>85<br>85<br>85                   |

| 6.9<br>6.10                                                                                                                     | Pathological TM behavior of the intruder benchmark on TMbox Optimizing the execution times of the intruder benchmark on TMbox.               | 88<br>89                                                       |

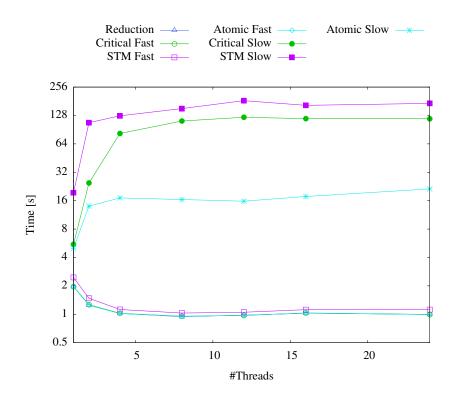

|                                                                                                                                 | Execution time of normal CG.                                                                                                                 | 92                                                             |

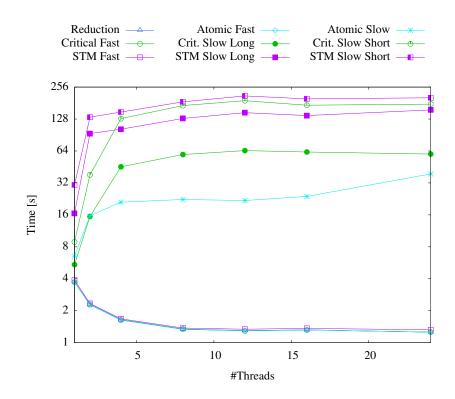

| 6.12<br>6.13                                                                                                                    | Execution time of pipelined CG                                                                                                               | 96<br>98                                                       |

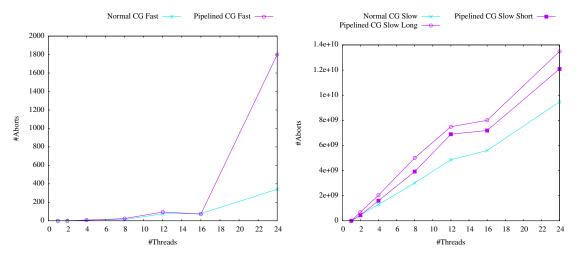

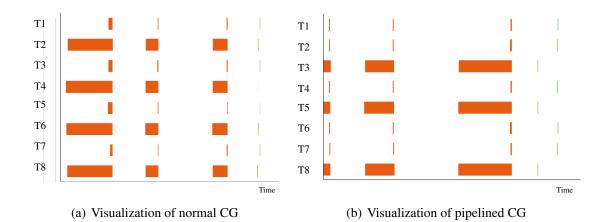

| 6.14<br>6.15                                                                                                                    | Visualization of normal and pipelined CG                                                                                                     | 99<br>100                                                      |

| 6.16                                                                                                                            | Load and store instructions.                                                                                                                 | 100                                                            |

|                                                                                                                                 | Level 1 instruction and data cache misses.                                                                                                   | 102                                                            |

|                                                                                                                                 | Data cache misses in L2.                                                                                                                     | 105                                                            |

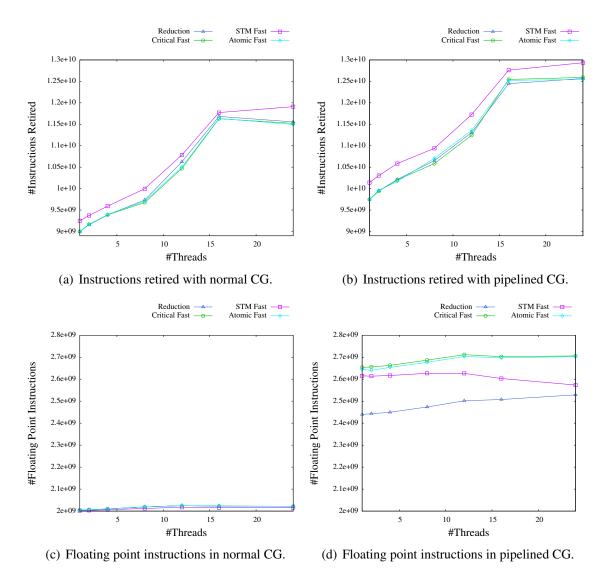

|                                                                                                                                 | Instructions retired and floating point instructions.                                                                                        | 106                                                            |

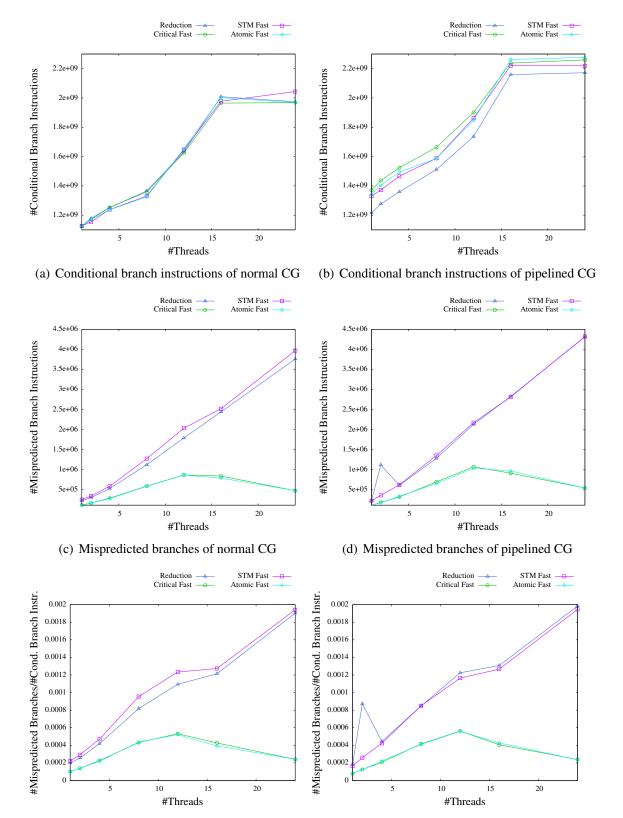

|                                                                                                                                 | Conditional branch and mispredicted branch instructions                                                                                      | 107                                                            |

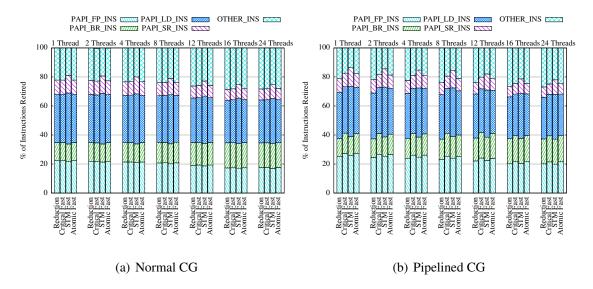

|                                                                                                                                 | Break down of instructions.                                                                                                                  | 108                                                            |

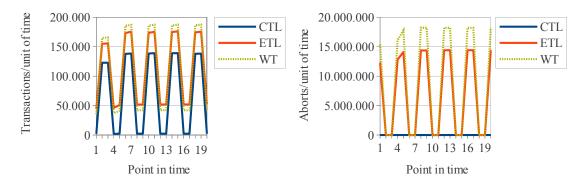

| 6.22                                                                                                                            | Comparison of three STM strategies.                                                                                                          | 110                                                            |

| <ul> <li>6.24</li> <li>6.25</li> <li>6.26</li> <li>6.27</li> <li>6.28</li> <li>6.29</li> <li>6.30</li> </ul> | Workflow for phase detection in TM applications                                                                                                                                                                                                                                                                                                                                        | <ol> <li>113</li> <li>114</li> <li>115</li> <li>117</li> <li>119</li> </ol> |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9                                                  | Checkpointing mechanism after the gtm_checkpoint pass Speedup over sequential execution                                                                                                                                                                                                                                                                                                | 138<br>139<br>140<br>141<br>142<br>145<br>146                               |

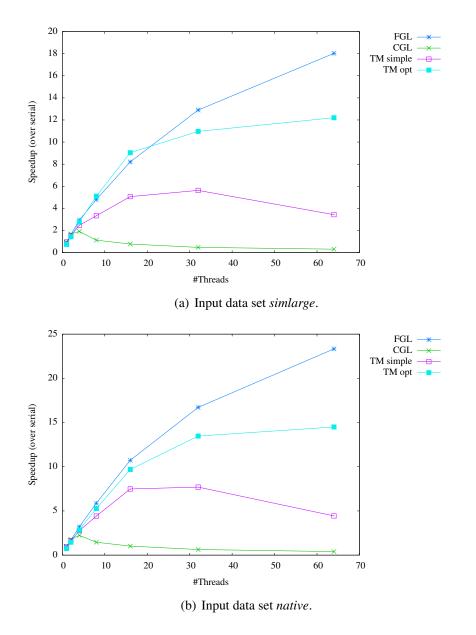

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10                                          | Excellent speedups with <i>Large TM</i> over <i>Small Atomic</i>                                                                                                                                                                                                                                                                                                                       | 161<br>161<br>163<br>164<br>165<br>165<br>167                               |

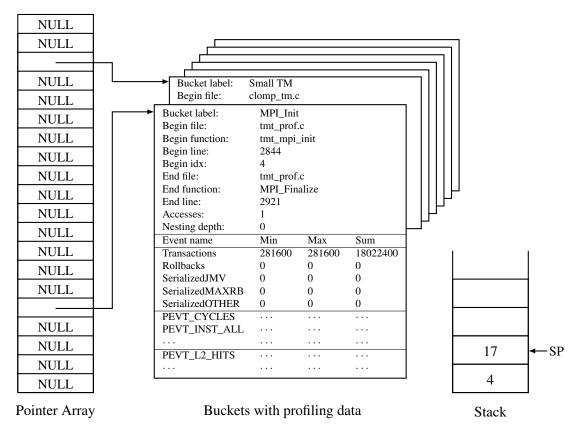

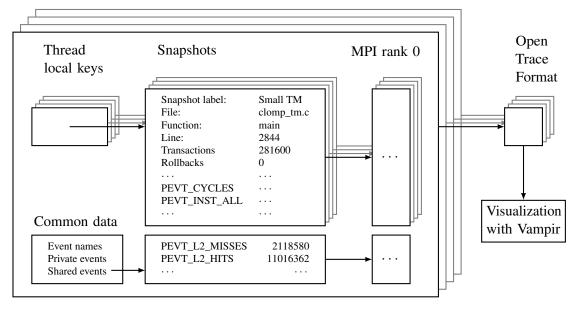

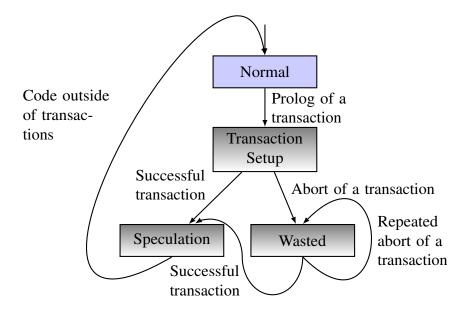

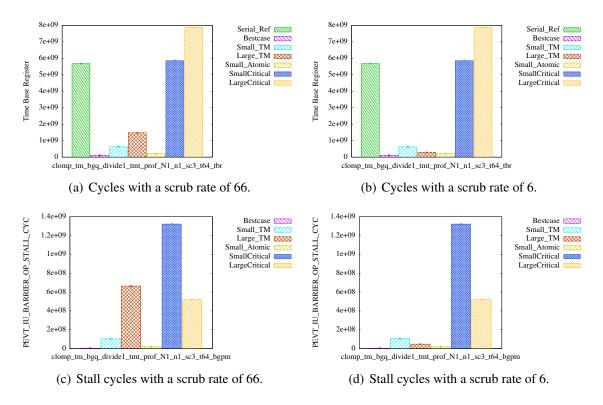

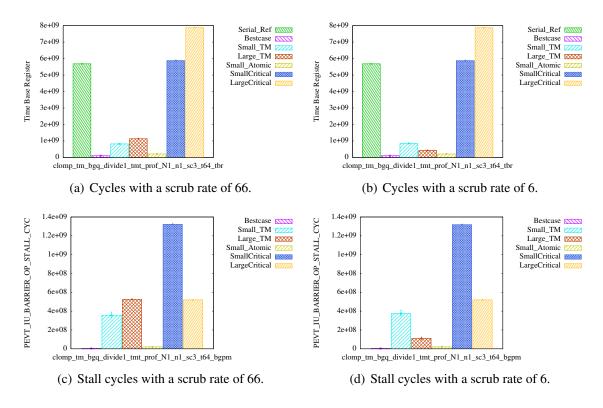

| 9.11<br>9.12                                                                                                 | Data structures of the profiling tool for TM                                                                                                                                                                                                                                                                                                                                           | 177<br>179<br>182<br>184<br>186<br>187<br>188<br>189<br>189<br>190<br>191   |

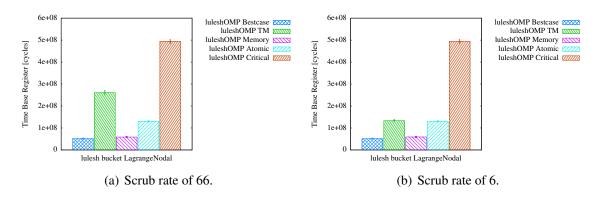

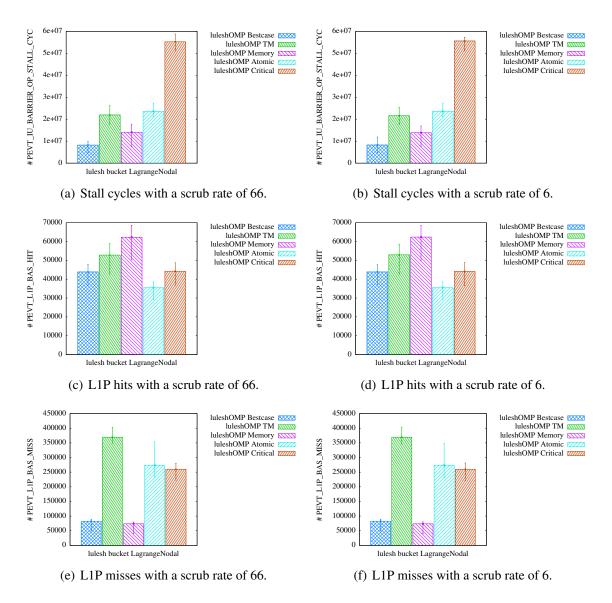

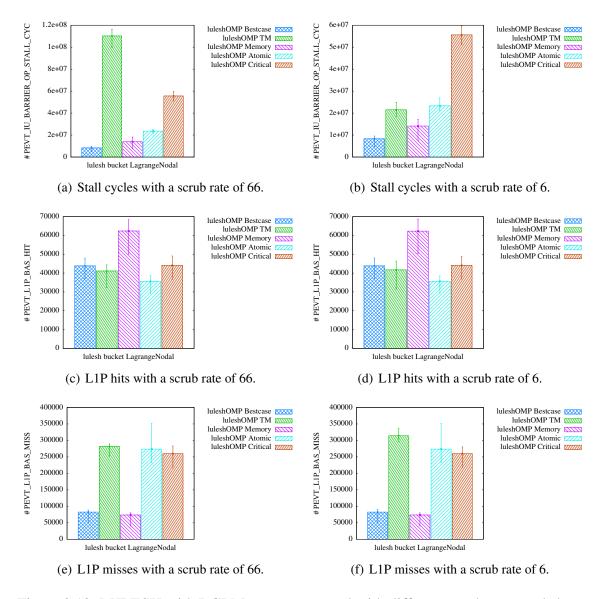

| 9.14<br>9.15<br>9.16<br>9.17<br>9.18                                                                         | Influence of moving the computation inside the transaction Computation inside the transaction in the long-running mode Influence of the scrub rate on the stall cycles in long-running mode LULESH executed with different scrub rates and long-running TM mode. LULESH executed with different scrub rates and short-running TM mode. BGPM events of LULESH with long-running TM mode | 192<br>193<br>193<br>195<br>195<br>195<br>196<br>197                        |

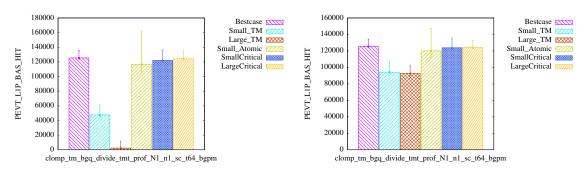

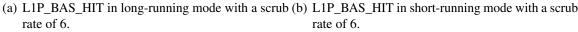

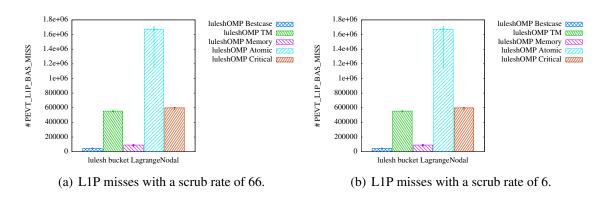

| 9.20 | L1P misses with LULESH and 16 threads in short-running mode | 197 |

|------|-------------------------------------------------------------|-----|

| 9.21 | L1P misses with LULESH and 16 threads in long-running mode  | 198 |

| 9.22 | L1P hits and stall cycles with LULESH and 16 threads        | 198 |

| 9.23 | Vampir visualizing the application's behavior.              | 200 |

## **List of Tables**

| 3.1  | Design space of phase detection.                                       | 41 |

|------|------------------------------------------------------------------------|----|

| 4.1  | Experimental platform ExpX5670                                         | 49 |

| 5.1  | Format of timing and transactional events in x86_64 binary trace files | 53 |

| 5.2  | L3 cache misses for labyrinth                                          | 60 |

| 5.3  | Format of the events that are transferred as packets                   | 63 |

| 5.4  | Area overhead per processor core in different tracing configurations   | 64 |

| 6.1  | Relation of contention parameter and ApT.                              | 82 |

| 6.2  | Parameter settings for the example problem                             | 97 |

| 6.3  | STAMP input parameter sets                                             | 16 |

| 6.4  | Parameters used in EigenBench                                          | 22 |

| 6.5  | Orthogonal TM characteristics                                          | 22 |

| 6.6  | Additional event types required for EigenOpt                           | 23 |

| 6.7  | Cases InTxn and NonTxn with known inputs                               | 26 |

| 6.8  | Transactional characteristics of the intruder benchmark 1              |    |

| 6.9  | Parameters obtained from traces with Case1                             | 27 |

| 6.10 | Test case with high contention and one and two transactions            |    |

| 6.11 | Test case with low contention                                          | 29 |

| 7.1  | Read barriers with two optimization levels                             |    |

| 7.2  | Write barriers with two optimization levels                            |    |

| 7.3  | Throughput of two conflict detection variants                          |    |

| 7.4  | Throughput of three test cases                                         |    |

| 7.5  | Run times of STAMP benchmarks                                          | 50 |

| 8.1  | Different contention levels in the CLOMP-TM benchmark                  |    |

| 8.2  | Description of synchronization constructs used in CLOMP-TM 1           |    |

| 8.3  | Parameters for CLOMP-TM                                                |    |

| 8.4  | MCB with one MPI task and 64 threads (strongScaling)                   | 70 |

## Listings

| 2.1        | Example of two threads executing transactions.                        | 10  |

|------------|-----------------------------------------------------------------------|-----|

| 6.1        | Algorithmic design of a parameterizable synthetic TM application      | 72  |

| 6.2        | Proposed optimization algorithm for TM applications based on PSTMA    | 73  |

| 6.3        | Example logs of dynamic memory requests with malloc                   | 76  |

| 6.4        | Trace format for logging dynamic memory requests with free            | 77  |

| 6.5        | Detecting communication patterns between transactions                 | 78  |

| 6.6        | Global statistics of transactional execution.                         | 80  |

| 6.7        | Statistics per transaction.                                           | 80  |

| 6.8        | Sorted list of addresses with number of contentious accesses          | 81  |

| 6.9        | Transactional version of fluidanimate with <i>small Txns</i>          | 83  |

| 6.10       | Transactified fluidanimate with the <i>long Txns</i> version          | 84  |

| 6.11       | Mapping of CG to OpenMP for parallelization.                          | 90  |

|            | <i>Fast</i> version of a reduction that is implemented with TM macros | 91  |

| 6.13       | Implementation of the pipelined CG with OpenMP Reduction              | 94  |

| 7.1        | C extension with a pragma to specify transactions                     |     |

| 7.2        | Example of a reduction pattern with nested loops.                     | 137 |

| 8.1        | Use of MPI barriers for CLOMP-TM with MPI                             | 166 |

| 9.1<br>9.2 | Application programming interface for the TM profiling tool           |     |

## 1. Motivation for Tools targeting Transactional Memory

#### **1.1 Transactional Memory for Parallel Programming**

With multi-core processors becoming the norm for desktop as well as server machines, parallel programming gains importance in everyday software development. Due to the difficulties associated with conventional locking, Herlihy and Moss proposed Hardware Transactional Memory (HTM) to facilitate the synchronization in applications using shared memory [91]. The concept of transactions is borrowed from database systems and releases the programmer from the burden of managing low-level primitives e.g., locks to synchronize concurrent threads of execution.

For programmers, Transactional Memory offers the convenient abstraction of an atomic block, also called transaction, to synchronize concurrent accesses to shared memory. A transaction may contain a finite sequence of instructions that execute with the following properties: Atomicity, Consistency, and Isolation (ACI) [83]. These ACI properties provide a convenient abstraction for coordinating concurrent accesses to shared data and herewith simplify parallel programming. TM delivers the means to overcome most of the shortcomings of traditional lock-based synchronization, such as priority inversion, deadlock, livelock, and convoying.

Moreover, TM features optimistic concurrency that replaces the mutual exclusion of traditional synchronization. This enables to execute transactions in parallel and detect conflicting memory accesses of different threads. A run time system, implemented in hardware (HTM), software (STM) or both (hybrid TM), implements the conflict detection and maintains speculative versions of the data.

The optimistic concurrency with TM nourishes the hope for an increased scalability compared with pessimistic synchronization. Scalability improvements gain importance with the ever increasing core counts of the new multi-core generations. Another advantage of TM is the composability of independently developed parallel libraries. This may facilitate the integration of third party libraries in the development cycle of parallel software.

Moreover, the transaction simplifies to reason about the correctness of the parallel code because transactions are simple to understand and insert. Thus, TM improves parallel

programming over lock-based synchronization, which especially attracts programmers new to the development of parallel software.

#### 1.2 The Missing Performance with TM

The target audience judges whether TM is a success or not. This audience may have more demands on TM than the expected gains in usability. For developers who start to program in parallel, a convenient abstraction that simplifies synchronization may be convincing. For experts in high performance computing (HPC), this may not suffice. In this use case, the composability of parallel modules and the expected gains when maintaining the software are advantageous but the performance of TM is also a very important factor.

The performance of TM depends on the implementation of the run time system. STM comes with known performance deficiencies that originate from the overhead due to the instrumentation of the memory accesses, executing the algorithm for conflict detection, lock acquisition and release, and validation of the read and write sets. HTMs often have limitations e.g., in the number of memory locations that can be accessed inside of a transaction or the type of instructions that can be executed. Otherwise the transaction fails and retries. Hybrid TM inherits the performance of both systems so that a transition from hardware to software execution yields a performance degradation.

Although these overheads and limitations are known, the application developer does not necessarily know whether overheads cause the unexpectedly low performance or an execution pattern that results in repeated rollbacks of a transaction. The issue is that the application developer is unaware of the TM application's behavior and has no profound basis to take counter measures e.g., to reorganize the transactions, choose a better suited TM run time system or reorganize the data structures to achieve a better utilization of the microarchitecture.

Moreover, there has been little research on the human factor in TM programming so that the granularity of transactions and the introduced costs through inappropriate use of transactions have not been quantified. Tools for TM can detect and help ameliorate these cases so that even inexperienced programmers can detect pathological execution patterns in their TM application and judge whether this behavior negatively influences the performance of the TM application.

#### **1.3 Tool Support for Simplifying the Optimization of TM Programs**

So far tool support for TM has been proposed to support STM [7, 191, 127, 123, 220, 29, 76] or HTM [31, 71]. While these solutions are tailored to a specific TM system and programming language, we present the first holistic approach that considers multiple TM systems (Software, Hardware, and hybrid TM) as well as includes information from more than two layers of the TM software stack. Information from the TM application, TM compiler, TM run time system, and hardware pose the inputs for the novel methods and strategies for the optimization of TM applications presented in this thesis. We collect information from these different layers of the TM software stack in order to obtain a broader view on the performance of the application and advance the state-of-the-art. The additional information is expected to yield higher performance gains and enable optimizations beyond

that of previous tools for TM that consider only one or two layers of the TM software stack. In particular we identify the following possibilities to improve the state-of-the-art in tools for TM.

The following related works use profiling or sampling information from the TM run time system that is retrieved during run time and combine it with information from the source code [7, 191, 127, 220, 123, 29, 76]. The combination of information from the TM run time and source code is important and valuable for the programmer, but cannot explain performance deficiencies in the presence of a TM behavior that shows very few rollbacks. In order to sufficiently explain the performance of the TM system in these cases and provide complementary information from the microarchitecture for all cases, we research how to use information from the hardware performance counters of the microarchitecture. These counters enable to rate and compare the utilization of resources of the microarchitecture e.g., L1 caches and help to identify the sources for performance degradation with TM even for a TM application with very few rollbacks. Moreover, readings from these performance counters also help to compare synchronization using TM with other synchronization constructs e.g., with OpenMP primitives and enable new insights into the interaction of the TM system with the microarchitecture that have not been possible with previous tools for TM.

Optimization of TM applications with the mentioned tools is a trial-and-error process that takes the following steps: first, profile the TM application, then find the data structures that are heavily contended and identify the corresponding transactions, use the profiling information to determine the wasted work caused by transactions that abort and either rearrange or substitute the data structures or change the reordering of statements in the transaction to reduce the amount of wasted work [220]. Hence, an application developer must invest time and effort to refactor the data structures and/or transactions of the TM application in order to reduce the amount of wasted work. A new version of the application must be tested for correctness, executed and compared with the previous profile in order to find out whether the code changes yield the expected performance gains. Often this a disappointing and tiring process that yields diminishing returns. We seek to alleviate this process through providing a set of best practices for the programming with TM. These practices enable the programmer to design the TM application according to criteria that incorporate transactional length and conflict potential. With these practices an application developer easily sees whether a transaction meets the requirements or not and can direct the optimization efforts so that the transactions in the TM application meet the requirements formulated in the best practices. A second approach researches how to use hardware performance counters to extract the characteristic parameters of the TM application behavior. With these characteristic parameters, a tool such as the EigenBench microbenchmark [94] helps to simulate the effects of possible optimizations on the target application and helps to exclude optimization directions with diminishing returns. This approach may help application developers to simulate a set of optimizations and select and transfer the most promising one to the actual TM application.

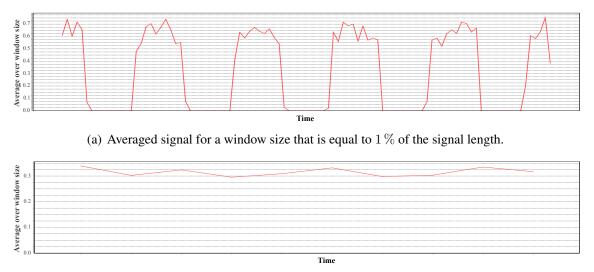

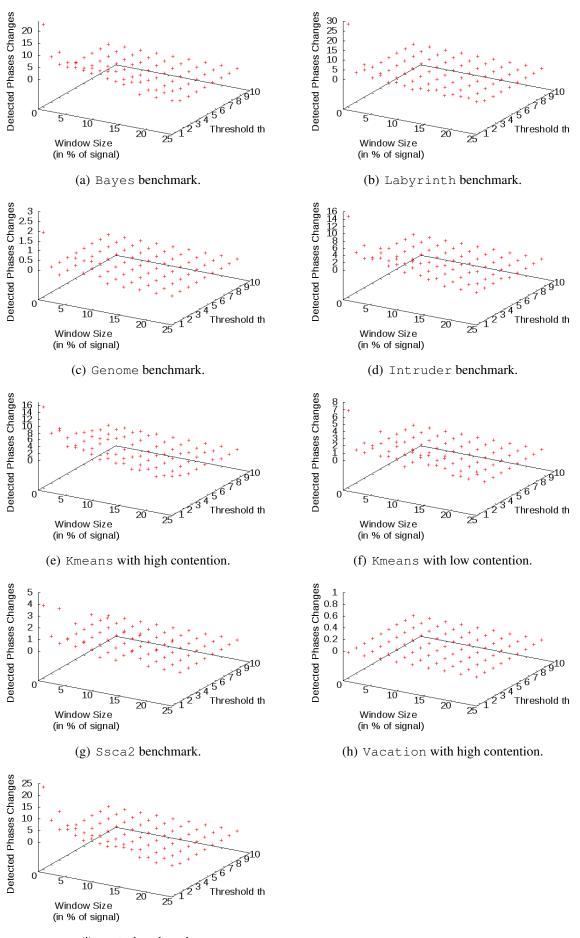

Moreover, the existing tools do not account for the time varying behavior of TM applications. In order to make the time varying behavior of a TM application easily accessible for an inexperienced as well as an experienced application developer, transitions between execution phases with low and high contention between transactions must be recognized automatically with a tool. This approach helps to assess the potential of optimizations that exploit the transition between optimistic and pessimistic conflict detection modes of an STM system. In order to identify a possible optimization possibility and to answer the question whether phases exist in current TM applications, we develop a post-processing tool that analyzes the execution phases of a TM application and detects phase changes. This tool enables even inexperienced application developers to identify execution phases in the application and determine the number of phase changes to judge the optimization potential.

Until now, tools for TM do not take advantage of the static information from the TM application that is available throughout the compilation process. This may lead to missed optimization opportunities and result in selecting a standard parameter setting of the STM system that may not be the best for this particular application. Hence, incorporating static information in the flow of the optimization of TM applications seems an idea worth to research in this thesis.

Therefore, static information, information about the run time behavior and best practices, that condense the knowledge of experts, need to be extracted to develop these new methods and strategies for the optimization of TM applications. The practical result of researching these methods and strategies are tools for TM that can be easily applied even by inexperienced application developers. These tools extract the run time behavior of a TM application, provide means, e.g., a representative application with a multitude of input parameters, to find best practices, support the visualization of the run time behavior, and thus help experienced as well as inexperienced application developers to optimize the TM application. Extracting and combining information from TM systems implemented in hardware, software or both in a suitable way poses the following six challenges that we address in this thesis.

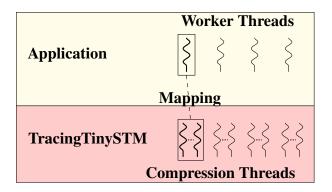

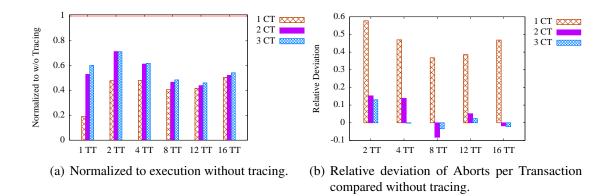

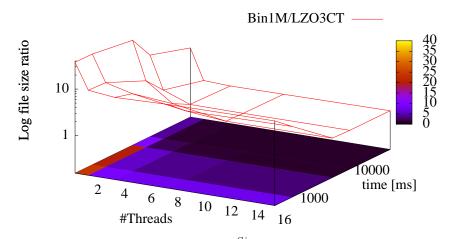

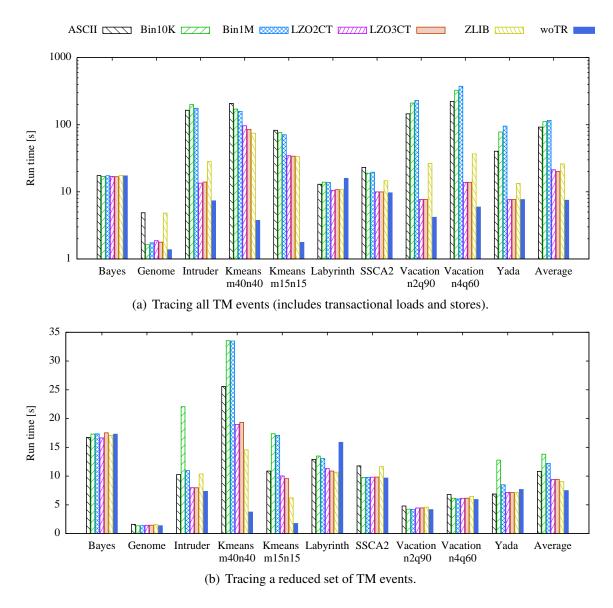

The first challenge is to capture the genuine TM application's behavior at run time. This is especially important because transactions are sensitive to artificially introduced delays of a thread which may lead to an introduced TM conflict. This may lead to a recorded application behavior that is biased through the tracing machinery. Therefore, a lightweight trace generation scheme with a small probe-effect needs to be developed and evaluated. This thesis presents similar solutions for STM and hybrid TM that generate event traces. For STM, the logging of frequently occurring events, such as TM loads and stores, quickly saturates the write bandwidth of the hard disk. Thus, a reduction of the amount of data to be written to hard disk needs to be achieved. Therefore, we research how these events can be compressed online without disturbing the application. A multi-threaded trace compression scheme is designed, implemented, and evaluated. We enhance the TinySTM, a word-based open source STM, with tracing facilities. Due to the lightweight and compressing tracing scheme the resulting TracingTinySTM generates event traces that capture the genuine TM application's behavior. For an FPGA-based hybrid TM system, called TMbox, a low-overhead tracing solution is shown. Each processing element is enhanced with an event generation unit for monitoring. When an instruction of interest is encountered, a corresponding time-stamped event is generated and passed on to the log unit. This unit uses idle times on the bus to transfer it to the memory of the host machine. The event tracing methodology captures transactions that utilize the HTM part of the hybrid TM system as well as transactions using the STM part. Our approach is the first to capture the behavior of a TM application in a hybrid TM system. Although all methods are tailored to and applied in the context of TM, they are universally applicable in a different context. Example application areas are the monitoring of arbitrary events in an FPGA-based processor prototype or the logging and compressing of events in a math library.

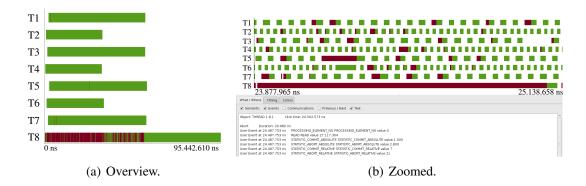

The second challenge arises with the release of IBM's new Blue Gene/Q architecture with HTM support. We establish a set of best practices for the new architecture so that the application developer can exploit the full potential of the architecture including the TM subsystem. For this purpose, we introduce a new benchmark, CLOMP-TM, that has a series of parameters that allow us to explore varying transaction granularities and conflict rates, coupled with typical computational kernels found in scientific codes. This enables new insights through evaluating the TM system and comparing the performance with other synchronization primitives of OpenMP. Further, this new BG/Q architecture also requires tool support to enable optimizations of scientific applications. A trace-based solution to capture the run time behavior on a per event basis is not feasible for this proprietary HTM system. This HTM system requires a proprietary software stack, including compiler and run time system. Thus, we design, implement and evaluate three different tools for TM that enable programmers to explore the subtleties of TM execution. We contribute the first tool that profiles applications using MPI and OpenMP with TM on BG/Q, a tracing tool for TM that enables in-depth inspection of thread-level execution and utilization of the architecture through visualization with the state-of-the-art visualization tool Vampir, and a tool that measures overheads associated with TM, designed to dissect these overheads and direct optimization efforts for the TM stack. These tools incorporate the use of BG/Q specific hardware performance counters in order to uncover the subtle interaction of the TM system and the prefetching on BG/Q and help to study the implications for designing applications and choosing the TM mode of execution. Moreover, these tools enable to obtain a comprehensive understanding of the performance of synchronization mechanisms in LULESH, a Lagrange hydrodynamics proxy application, and find the cause for the missing performance with TM.

The third challenge is to correlate the gathered TM characteristics with microarchitecture events for the optimization of TM applications using STMs. Although this correlation is not new by itself, it is extremely helpful and has not been researched extensively in this context. Besides choosing well-suited parameters to monitor the microarchitecture, the correct interpretation of the obtained values is of key importance. To simplify the optimization for humans, the Visualization Of TM Applications (VisOTMA) framework is developed that visualizes these traces and enables the programmer to identify frequently conflicting transactions and the corresponding microarchitecture parameters in a post-processing step.

The visualization of this aggregated data needs to be achieved in a way that an inexperienced as well as experienced programmer can identify pathological execution patterns – posing the fourth challenge. So far optimizations have been carried out by TM experts with excellent knowledge of the underlying TM system. An inexperienced programmer does not have or may not be willing to acquire the knowledge of the TM system. Thus, the inexperienced programmer follows a trial-and-error strategy to optimize the TM application. To speedup this process, we invent EigenOpt – an exploration tool based on EigenBench – as part of the VisOTMA framework. With the help of EigenOpt, any programmer can capture the TM characteristic of the application in terms of parameters for Eigenbench. These parameters combined with Eigenbench are straightforwardly used to explore the space available through optimizations. With this tool, unrewarding optimization directions can be excluded without modifying the application. In this thesis, we will research how to identify and avoid optimization attempts with diminishing returns. This will speedup the optimization process for an inexperienced programmer and yield new insights for an experienced one.

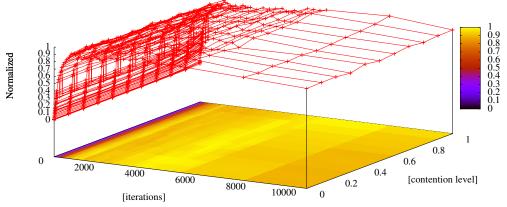

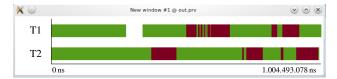

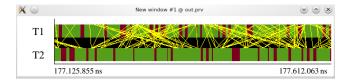

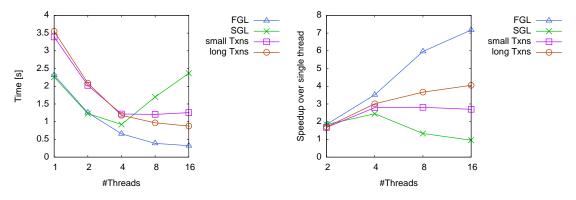

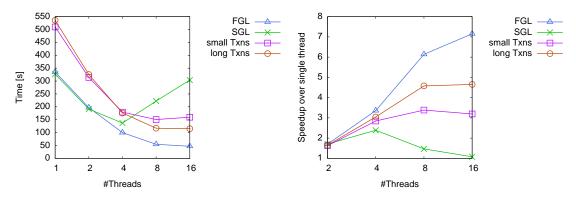

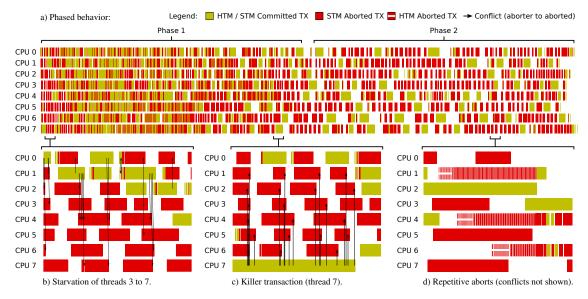

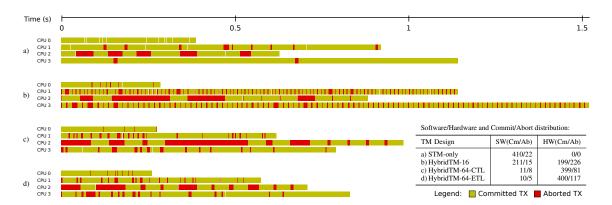

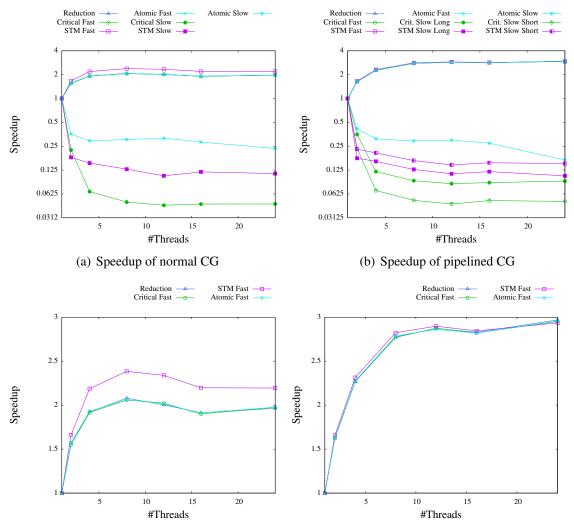

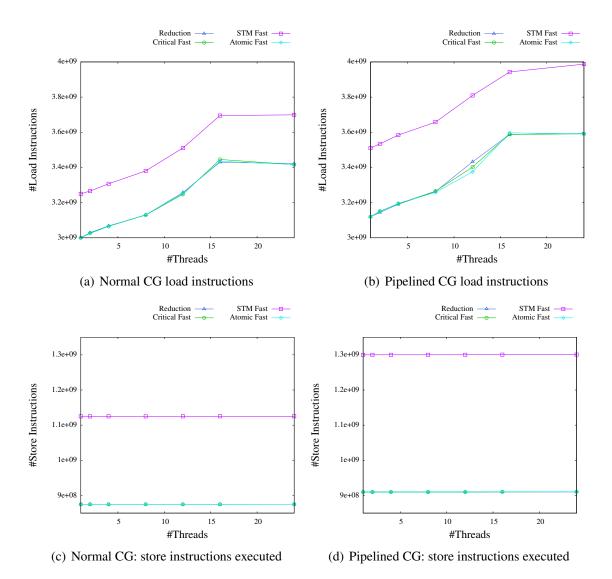

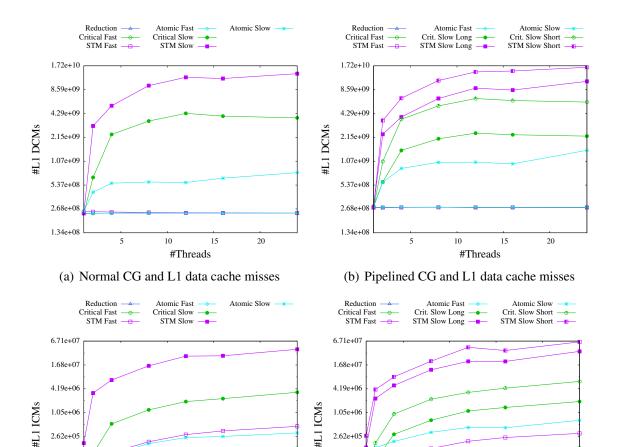

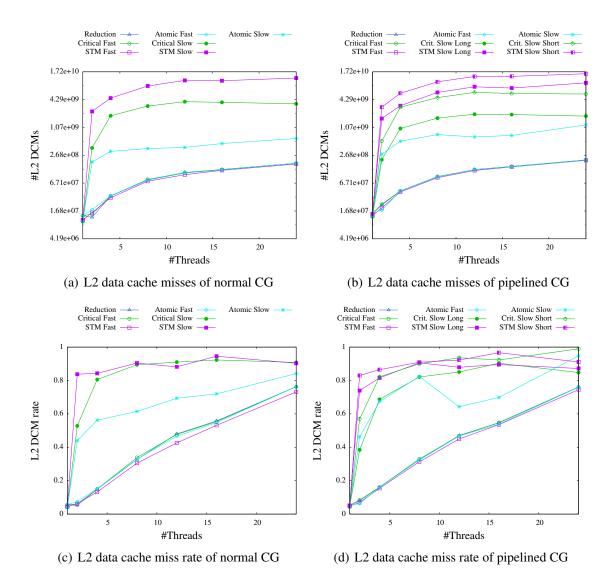

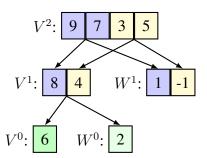

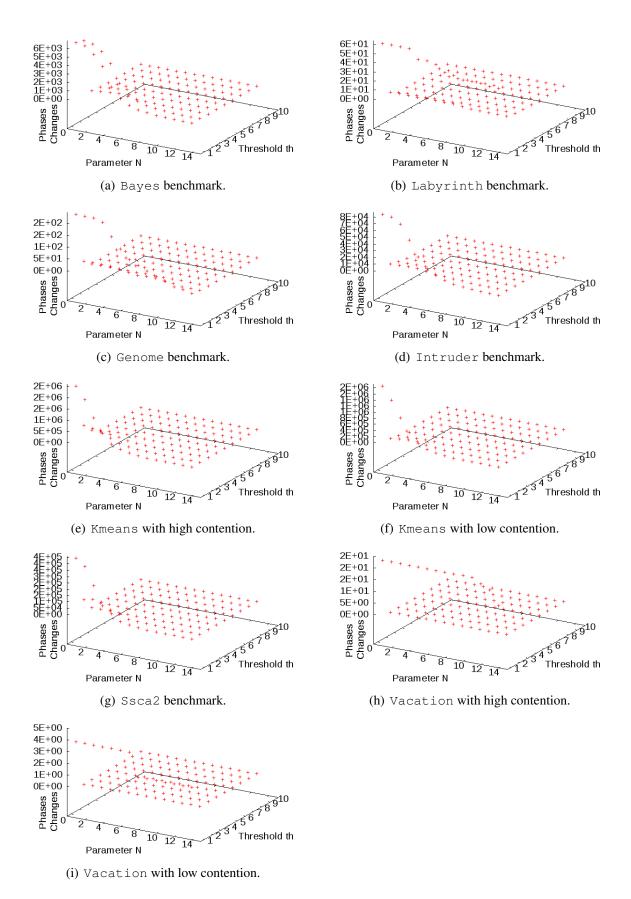

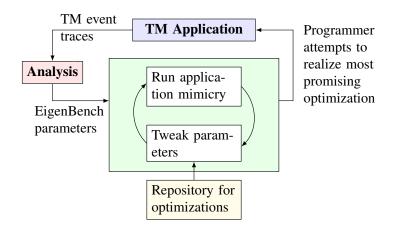

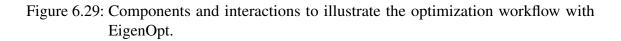

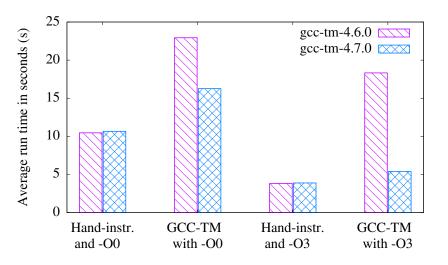

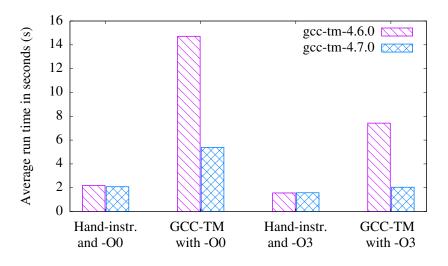

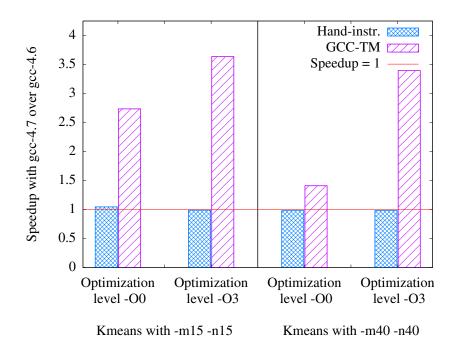

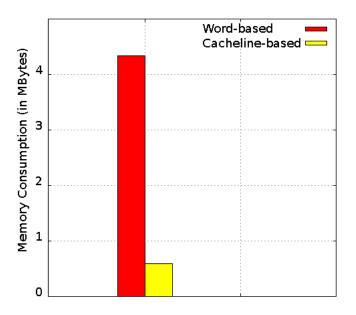

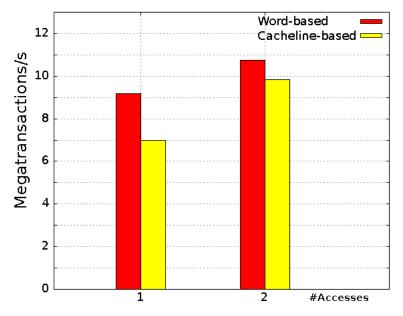

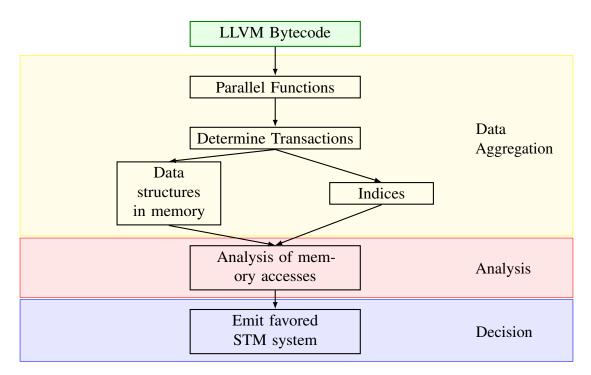

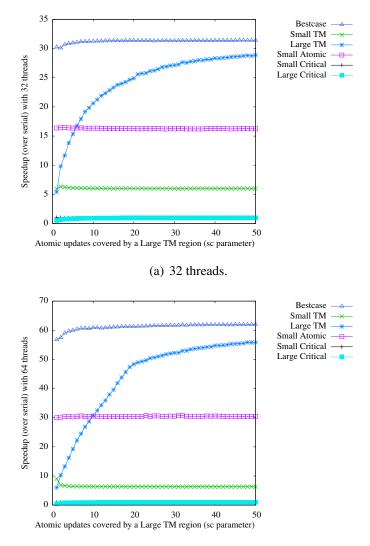

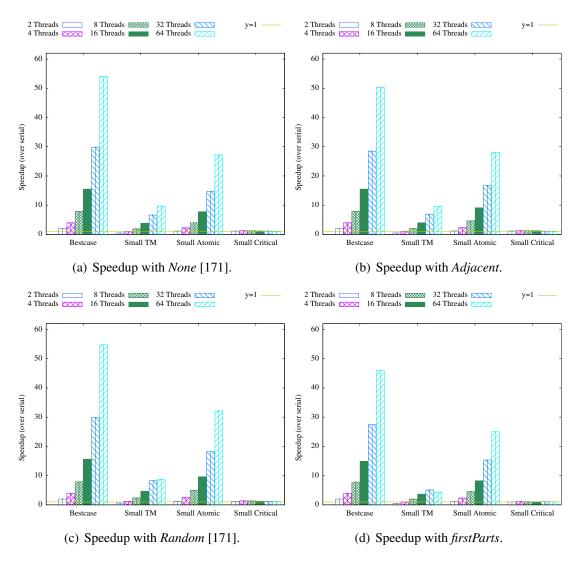

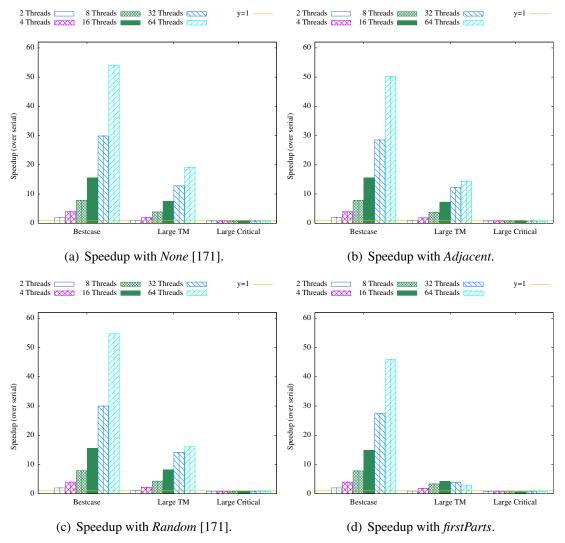

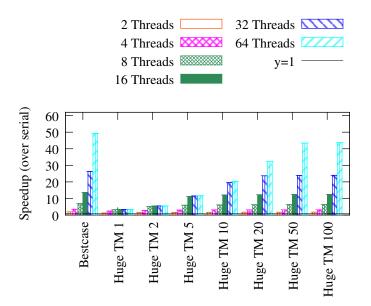

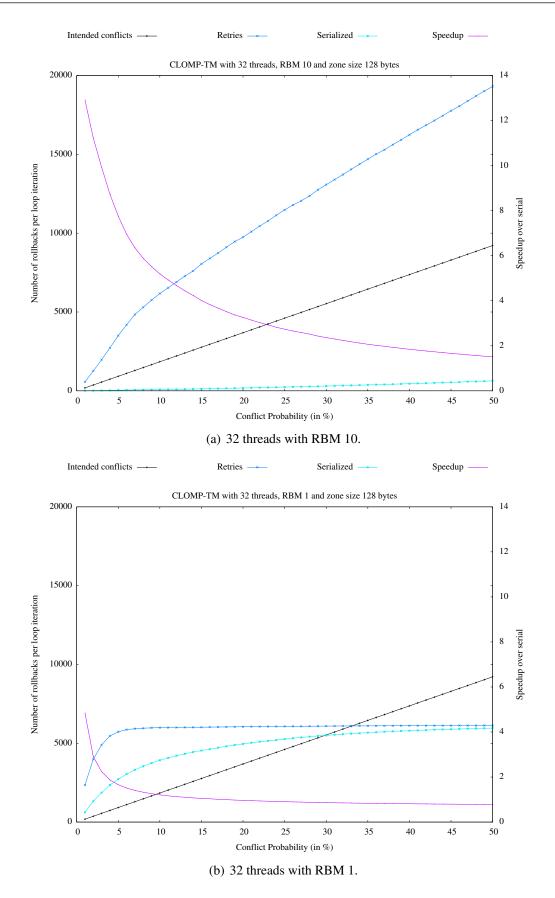

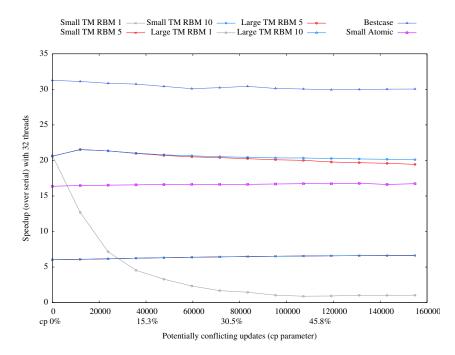

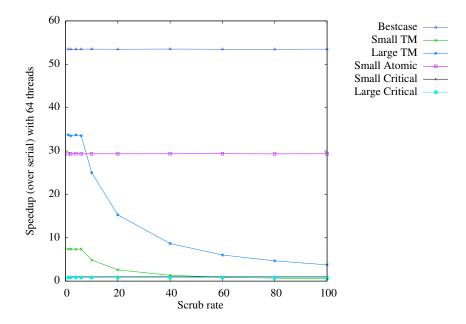

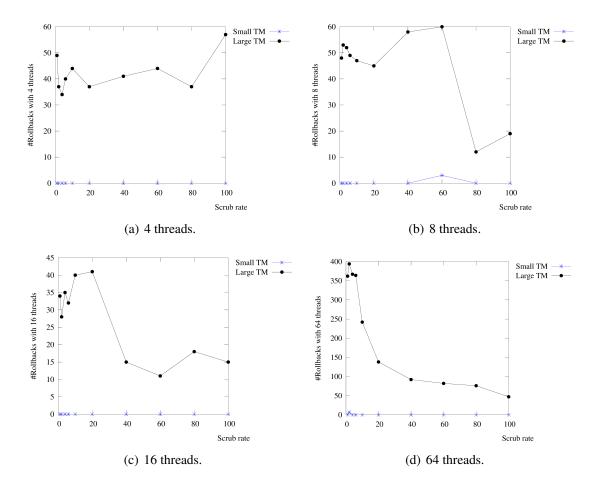

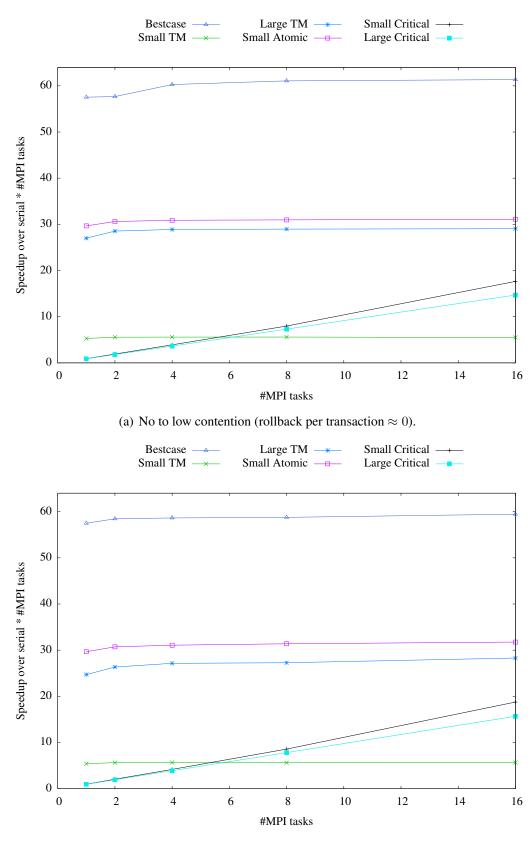

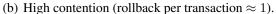

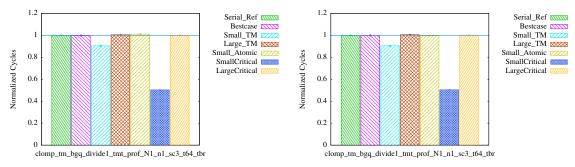

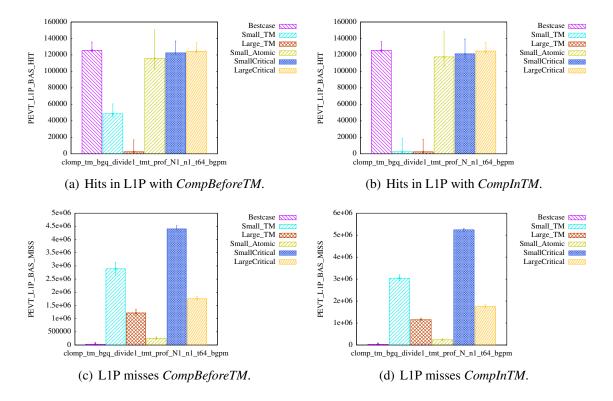

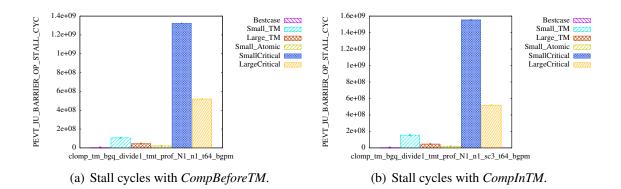

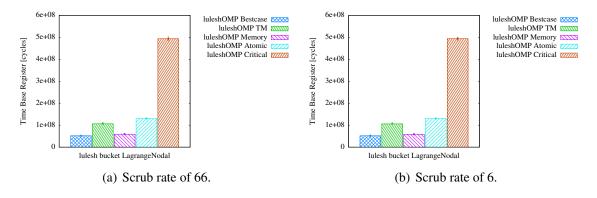

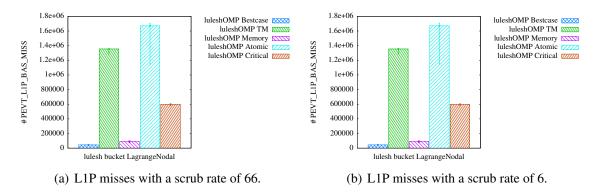

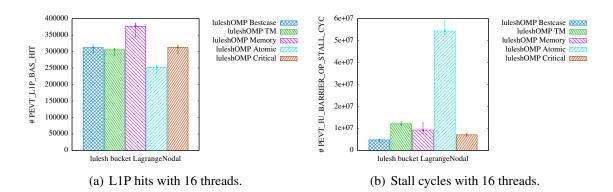

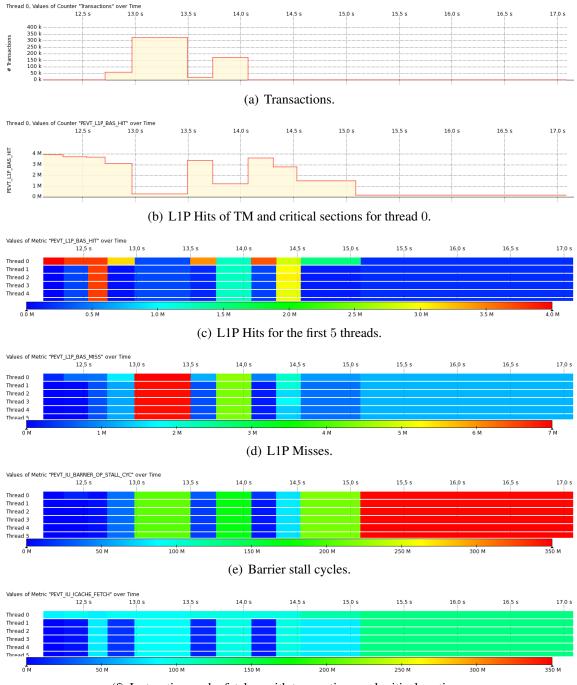

The fifth challenge is to detect and exploit a potential phase behavior of TM applications and integrate this analysis in the VisOTMA framework. In case the behavior of the TM application has periods with high and low conflict probability, this behavior of the application can be detected and exploited. Exploiting these phases is motivated through the different proposed TM designs: optimistic conflict detection schemes detect conflicts at commit-time whereas pessimistic schemes check for conflicts at encounter-time. In the optimistic case a conflict early in the execution of a transaction is noticed at commit time so that the programs performs computations that have to be undone. The wasted work in this transaction can be reduced, when switching from the optimistic to the pessimistic scheme. In this thesis, we transfer algorithms, Signal Analysis and Wavelet-based classification, that have been proposed for phase detection in other contexts, to TM. These enable the offline detection of a TM phase behavior.