# ERANCISCO MENROZA CERVANTES

A PROBLEM-ORIENTED APPROACH

FOR DYNAMIC VERIFICATION OF

HETEROGENEOUS EMBEDDED SYSTEMS

### Francisco Mendoza Cervantes

A Problem-Oriented Approach for Dynamic Verification of Heterogeneous Embedded Systems

# A Problem-Oriented Approach for Dynamic Verification of Heterogeneous Embedded Systems

by Francisco Mendoza Cervantes

Dissertation, Karlsruher Institut für Technologie (KIT) Fakultät für Elektrotechnik und Informationstechnik

Tag der mündlichen Prüfung: 15. Juli 2013

Referent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Korreferent: Prof. Dr.-Ing. Michael Hübner

#### Impressum

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe

KIT Scientific Publishing is a registered trademark of Karlsruhe Institute of Technology. Reprint using the book cover is not allowed. www.ksp.kit.edu

This document – excluding the cover – is licensed under the Creative Commons Attribution-Share Alike 3.0 DE License

(CC BY-SA 3.0 DE): http://creativecommons.org/licenses/by-sa/3.0/de/

The cover page is licensed under the Creative Commons Attribution-No Derivatives 3.0 DE License (CC BY-ND 3.0 DE):

http://creativecommons.org/licenses/by-nd/3.0/de/

Print on Demand 2014

ISBN 978-3-7315-0169-5 DOI: 10.5445/KSP/1000038209

# A Problem-Oriented Approach for Dynamic Verification of Heterogeneous Embedded Systems

Zur Erlangung des akademischen Grades eines

**DOKTOR-INGENIEURS**

von der Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) genehmigte

### DISSERTATION

von

M. Sc. Francisco Mendoza Cervantes aus Mexiko Stadt

Hauptreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Korreferent: Prof. Dr.-Ing. Michael Hübner

Tag der mündlichen Prüfung: 15.07.2013

# Acknowledgments

The work presented ahead was carried out while I was working as a Research Scientist at the FZI Forschungszentrum Informatik in Karlsruhe. I would like to thank my former colleagues from the Embedded Systems and Sensors Engineering (ESS) group for their support and motivation. There are good memories and friendships from that time that I will always cherish.

There are also people from ABB Corporate Research that I would like to thank. Dr.-Ing. Philipp Nenninger for his trust and continuous support for my research. Dr.-Ing. Dirk John for believing in the benefits of this work in the industrial domain. Dr. Joris Pascal for providing an interesting industrial case study for this work and for his further collaboration on it. Finally, my colleagues from the Intelligent Devices group for their feedback on this work and for the multiple discussions regarding model based design approaches.

From the academic side, I want to thank my mentor and main advisor Prof. Dr.-Ing. Dr. h. c. Jürgen Becker for his support and for giving me the opportunity to carry out my research as part of the Karlsruhe Institute of Technology (KIT). Special thanks to Prof. Dr.-Ing. Michael Hübner for being co-advisor for this work and for supporting its application in the industrial domain.

My deepest appreciation goes to my family who provided me the determination to complete this dissertation. My parents for teaching me the values of honesty and hard work. My brother for always having an open ear for me. My wife for her love and patience, and for enduring the sleepless nights and weekends I invested in front of the computer. Without her none of this work would have been possible.

## **Abstract**

Industrial devices in the industrial automation domain have undergone a steep increase in their complexity during the last 20 years. They have evolved from simple acquisition devices with point-to-point communication up to complex processing units with multiple computation and communication functionalities. This has given rise to a new series of design challenges for the embedded systems used to implement them.

Simulation based techniques are widely used for the design and verification of embedded systems for industrial devices. These systems are heterogeneous from a system level perspective due to the combination of digital systems, analog and mixed-signal systems and multi-domain physical systems. Various domain-specific modeling languages and simulation tools are available for this purpose. However, these tools focus on specific aspects of a design, which makes it very challenging to predict the behavior of full systems. This is done in late design stages, namely in the integration and tests phase, and often leads to time-consuming redesign cycles that affect the cost and time-to-market of a product.

This dissertation presents a virtual prototyping methodology for the design and verification of heterogeneous embedded systems. The targeted applications are industrial device such as sensor, actuators and close-loop controllers used to interact with physical processes in the field level of industrial automation systems. This methodology provides multidisciplinary team members with enhanced modeling and simulation capabilities in order to identify and solve design problems during early development stages. It also provides supporting modeling guidelines and a problem-oriented verification approach which can be applied in different development stages.

The virtual prototypes described in this work provide a pragmatic solution for emulating the behavior of hardware prototypes and experimental setups. The underlying simulation models used can be described in varying granularities according to the development stage, and using different modeling formalisms and simulation tools. This work

demonstrates that virtual prototypes can help increase the confidence in the correctness of a design thanks to a deeper understanding of the complex interactions between hardware, software, analog and mixed-signal components of embedded systems and the physical processes they interact with.

# Kurzfassung

Industrielle Geräte in der Automatisierungstechnik sind in den letzten 20 Jahren deutlich komplexer geworden. Sie haben sich von einfachen Messgeräten mit Punktzu-Punkt Kommunikation zu Einheiten mit mehreren Kommunikations- und Verarbeitungsfunktionen entwickelt. Ihre zunehmende Komplexität führt zu neuen Herausforderungen in der Entwicklung derartiger eingebetteter Systeme.

Diese eingebetteten Systeme werden auf Systemebene als heterogen bezeichnet, da digitale, analoge und mixed-Signal Komponenten mit Multidomain-physikalischen Systemen zusammenwirken. Zur Entwicklung und Verifikation solcher Systeme werden häufig simulationsbasierte Verfahren eingesetzt. Diese Verfahren erfolgen durch mehrere domain-spezifische Modellierungssprachen und Werkzeuge, die auf spezifischen Teilen des Systems ausgerichtet sind. Das Gesamtverhalten kann daher erst in einer späteren Entwicklungsphase, nämlich der Integrationsphase, getestet werden. Dabei kommt es oft zu zeitaufwendigen Redesign-Zyklen, die sich auf Kosten und time-to-market eines Produkts auswirken.

In dieser Dissertation wird eine auf Virtual Prototyping basierende Vorgehensweise für die Entwicklung und Verifikation heterogener eingebetteter Systeme vorgeschlagen. Gezielte Anwendungen sind industrielle Geräte wie Sensoren, Aktoren und Regler, die mit physikalischen Prozessen auf der Feldebene von industriellen Automatisierungssystemen zusammenwirken. Die entwickelte Methode gibt multidisziplinären Arbeitsgruppen verbesserte Modellierungs- und Simulationsfähigkeiten zur Identifizierung und Lösung von Entwicklungsproblemen in frühen Entwicklungsphasen an die Hand. Dabei werden auch Modellierungsrichtlinien und ein problem-basiertes Verifikationsverfahren, welches in verschiedenen Entwicklungsphasen anwendbar ist, beschrieben.

Die in dieser Arbeit dargestellten virtuellen Prototypen bieten eine pragmatische Lösung für die Simulation von Hardwareprototypen und Testaufbauten. Die zugrunde liegenden Simulationsmodelle werden, entsprechend der Entwicklungsphase, mit verschiedenen Modellierungssprachen in variierendem Detaillierungsgrad beschrieben. Diese Arbeit zeigt, dass virtuelle Prototypen das Vertrauen in die Richtigkeit eines Designs stärken können, da sie zu einem tieferen Verständnis für die Wechselwirkungen zwischen der Komponenten von heterogenen eingebetteten Systemen und den physikalischen Systemen, mit denen sie zusammenwirken, führen.

# Contents

| 1 | Intr | oduction        |                                 |  |  |  | 1  |

|---|------|-----------------|---------------------------------|--|--|--|----|

|   | 1.1  | Industrial dev  | ices in automation systems      |  |  |  | 1  |

|   | 1.2  | Design challes  | nges for industrial devices     |  |  |  | 2  |

|   | 1.3  | Goals of this v | vork                            |  |  |  | 5  |

|   | 1.4  | Outline of this | work                            |  |  |  | 7  |

| 2 | Indi | ıstrial Devices |                                 |  |  |  | 9  |

|   | 2.1  | Industrial dev  | ices in automation systems      |  |  |  | ç  |

|   |      | 2.1.1 Indust    | rial processes                  |  |  |  | 10 |

|   |      | 2.1.2 Indust    | rial devices                    |  |  |  | 12 |

|   |      | 2.1.3 Indust    | rial controllers                |  |  |  | 13 |

|   |      | 2.1.4 Indust    | rial communication              |  |  |  | 15 |

|   | 2.2  | Embedded sys    | tems for industrial devices     |  |  |  | 17 |

|   |      | 2.2.1 Hardy     | vare platforms                  |  |  |  | 19 |

|   |      | 2.2.2 Device    | e firmware                      |  |  |  | 19 |

|   | 2.3  | Design approa   | ches for industrial devices     |  |  |  | 20 |

|   | 2.4  | Identification  | of requirements for this work   |  |  |  | 22 |

| 3 | Mod  | lel Based Desi  | gn of Embedded Systems          |  |  |  | 25 |

|   | 3.1  | System level o  | esign                           |  |  |  | 25 |

|   |      | 3.1.1 Overv     | iew                             |  |  |  | 26 |

|   |      | 3.1.2 Design    | n methodologies                 |  |  |  | 27 |

|   |      | 3.1.3 System    | n level design languages        |  |  |  | 29 |

|   |      | 3.1.4 Verific   | ation and validation approaches |  |  |  | 30 |

|   | 3.2  | SystemC         | <br>                            |  |  |  | 34 |

|   |      | 3.2.1 Struct    | ural modeling                   |  |  |  | 35 |

viii Contents

|   |     | 3.2.2   | Behavioral modeling                          | 38 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 3.2.3   | Simulation semantics                         | 40 |

|   |     | 3.2.4   | TLM-2.0                                      | 42 |

|   | 3.3 | Virtua  | ıl prototypes                                | 45 |

|   |     | 3.3.1   | Processor models                             | 46 |

|   |     | 3.3.2   | Open Virtual Platforms (OVP)                 | 49 |

|   | 3.4 | Analo   | g and Mixed-Signal (AMS) modeling            | 50 |

|   |     | 3.4.1   | Physical domain modeling                     | 50 |

|   |     | 3.4.2   | Analog and mixed-signal modeling languages   | 53 |

|   |     | 3.4.3   | Verification and validation approaches       | 55 |

| 4 | Het | erogen  | eous Embedded Systems                        | 59 |

|   | 4.1 | _       | ls of computation                            | 59 |

|   | 4.2 | Comb    | ining models of computation                  | 60 |

|   |     | 4.2.1   | Formal-based approaches                      | 61 |

|   |     | 4.2.2   | Co-simulation based approaches               | 63 |

|   | 4.3 | Scope   | and definition of this work                  | 67 |

| 5 | Gui | delines | s for the Construction of Virtual Prototypes | 71 |

|   | 5.1 |         | considerations                               | 71 |

|   |     | 5.1.1   | Modeling requirements                        | 71 |

|   |     | 5.1.2   | Modeling domains                             | 72 |

|   | 5.2 | Role o  | of virtual prototypes in the design flow     | 74 |

|   |     | 5.2.1   | System specifications                        | 75 |

|   |     | 5.2.2   | Algorithmic modeling                         | 75 |

|   |     | 5.2.3   | System level modeling                        | 76 |

|   |     | 5.2.4   | Specialized design flows                     | 79 |

|   |     | 5.2.5   | Implementation                               | 80 |

|   | 5.3 | Struct  | ure of a virtual prototype                   | 80 |

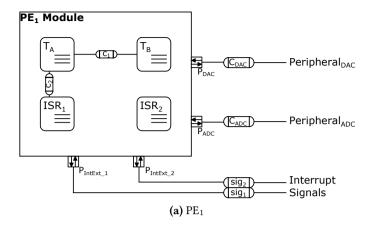

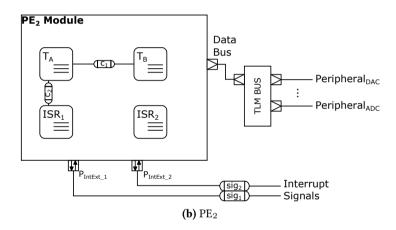

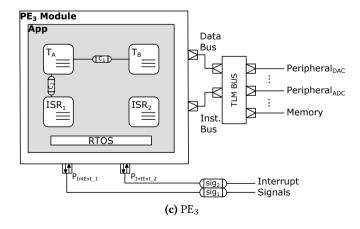

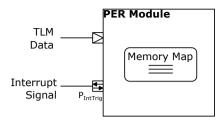

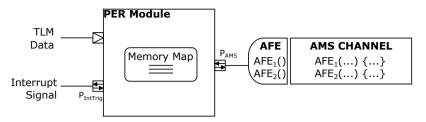

|   |     | 5.3.1   | Processing elements                          | 82 |

|   |     | 5.3.2   | SoC buses                                    | 85 |

|   |     | 5.3.3   | Peripherals                                  | 85 |

|   |     | 5.3.4   | AMS channel                                  | 86 |

|   |     | 5.3.5   | Analog Front Ends                            | 87 |

Contents ix

| 6 | Des | ign Me | thodology and Problem-Oriented Verification | 89  |

|---|-----|--------|---------------------------------------------|-----|

|   | 6.1 | Design | n and verification methodology              | 89  |

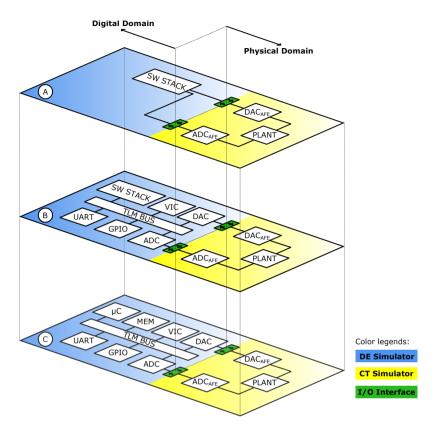

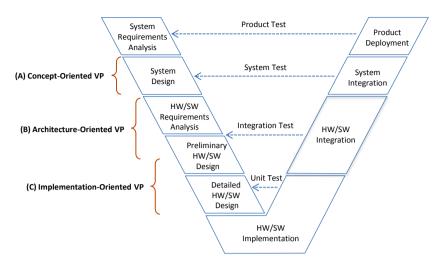

|   |     | 6.1.1  | Modeling abstractions                       | 90  |

|   |     | 6.1.2  | Concept-Oriented virtual prototype          | 90  |

|   |     | 6.1.3  | Architecture-Oriented virtual prototype     | 92  |

|   |     | 6.1.4  | Implementation-Oriented virtual prototype   | 93  |

|   | 6.2 | Suppo  | ort for the development life-cycle          | 96  |

|   |     | 6.2.1  | System tests                                | 97  |

|   |     | 6.2.2  | Integration tests                           | 97  |

|   |     | 6.2.3  | Unit tests                                  | 97  |

| 7 | Co- | Simula | tion Framework                              | 99  |

|   | 7.1 | Overv  | riew                                        | 99  |

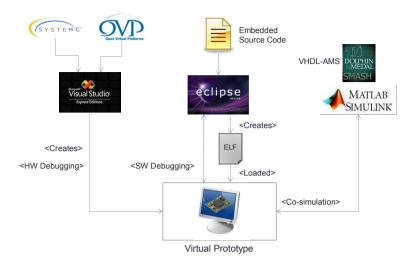

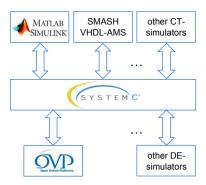

|   |     | 7.1.1  | Supported modeling and simulation tools     | 100 |

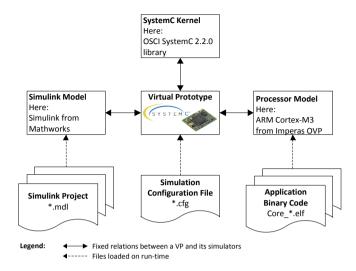

|   |     | 7.1.2  | Tool flow description                       | 101 |

|   | 7.2 | Model  | ling formalisms and their simulators        | 102 |

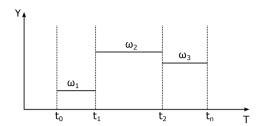

|   |     | 7.2.1  | Discrete-Event (DE) simulation              | 102 |

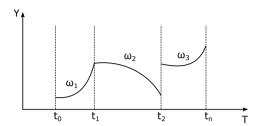

|   |     | 7.2.2  | Continuous-Time (CT) simulation             | 103 |

|   | 7.3 | DE/C   | Γ co-simulation                             | 104 |

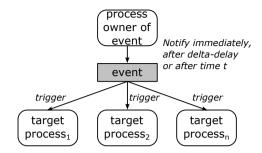

|   |     | 7.3.1  | Principles of simulation coupling           | 105 |

|   |     | 7.3.2  | Implementation requirements                 | 107 |

|   |     | 7.3.3  | Simulation cycle                            | 107 |

|   |     | 7.3.4  | State event detection                       | 110 |

|   | 7.4 | Syster | nC backplane                                | 111 |

|   |     | 7.4.1  | Event queue introspection                   | 112 |

|   |     | 7.4.2  | Time advance detection                      | 115 |

|   |     | 7.4.3  | Simulation control                          | 115 |

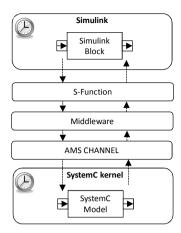

|   | 7.5 | Syster | nC/Simulink co-simulation                   | 116 |

|   |     | 7.5.1  | Overview                                    | 117 |

|   |     | 7.5.2  | Implementation                              | 118 |

|   |     | 7.5.3  | Simulation configuration                    | 119 |

|   |     | 7.5.4  | Simulation execution                        | 123 |

|   | 7.6 | Syster | nC/VHDL-AMS co-simulation                   | 129 |

|   |     | 7.6.1  | Overview                                    | 129 |

|   |     | 7.6.2  | Implementation                              | 129 |

|   |     | 7.6.3  | Simulation configuration                    | 131 |

**x** Contents

|    |       | 7.6.4   | Simulation execution         | 131 |

|----|-------|---------|------------------------------|-----|

| 8  | Eval  | luation |                              | 137 |

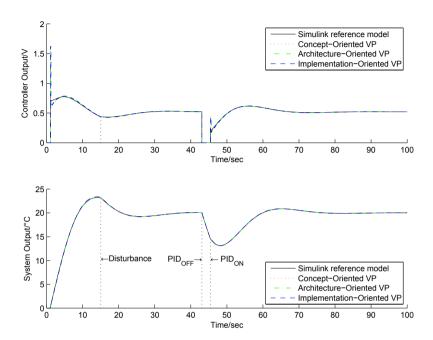

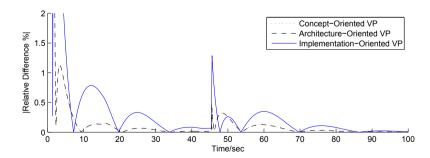

|    | 8.1   | PID clo | ose-loop control system      | 137 |

|    |       | 8.1.1   | Simulation models            | 138 |

|    |       | 8.1.2   | Simulation results           | 140 |

|    |       | 8.1.3   | Evaluation                   | 140 |

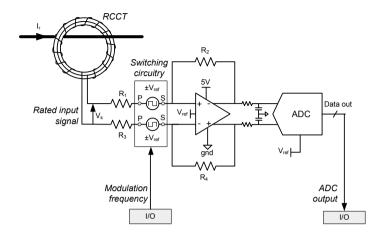

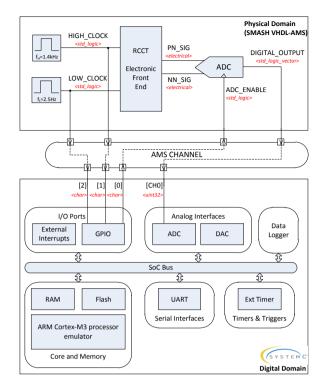

|    | 8.2   | Rogow   | rski Coil Current Transducer | 142 |

|    |       | 8.2.1   | Operation principle          | 142 |

|    |       | 8.2.2   | Simulation models            | 142 |

|    |       | 8.2.3   | Simulation results           | 144 |

|    |       | 8.2.4   | Evaluation                   | 146 |

| 9  | Con   | clusion | as and Outlook               | 149 |

|    | 9.1   | Conclu  | isions                       | 149 |

|    | 9.2   | Outloo  | k                            | 151 |

| Ac | crony | ms      |                              | 153 |

| Bi | bliog | raphy   |                              | 157 |

## Introduction

### 1.1 Industrial devices in automation systems

The day-to-day operations of most production and manufacturing plants are possible thanks to industrial automation systems. They form part of many industry sectors, including chemical and petrochemical, food and beverage, pulp and paper, oil and gas, power generation, mining, among many others. Their goal is to make production processes more efficient, cost effective and fast enough to keep up with market demands.

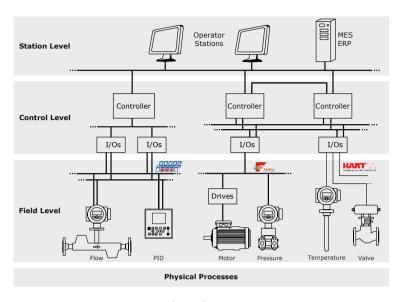

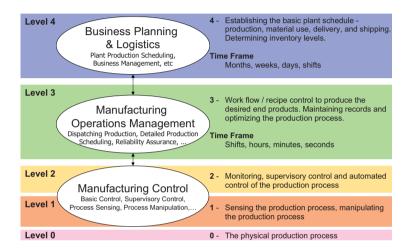

The primary activities performed by industrial automation systems are the monitoring and control of industrial processes. A wide range of industrial devices, interconnected by industrial networks and field buses, are used for this purpose. Figure 1.1 illustrates a typical example in the process automation domain. It also shows the different levels of an industrial automation system and its interconnection topology. The station level is responsible for monitoring and process optimization tasks, the control level is responsible, as its name specifies, for control tasks, and the field level is responsible for sensing and actuation tasks. This clear separation of tasks, in hand with available means for sharing information between them, makes it possible to automate even the most complex industrial processes.

Industrial devices, also called industrial instruments or field devices, are highly reliable and robust sensors, actuators and controllers located in the field level of industrial automation systems. Some examples in the process automation domain are illustrated

2 1 Introduction

Figure 1.1: Industrial automation system

in the bottom part of Figure 1.1. They are sensing devices such as temperature sensors, flow sensors and pressure sensors. They are also actuators such as valves and motor drives, as well as local controllers such as industrial PID controllers. Another example from a different application domain are IEDs (Intelligent Electronic Devices) used in power systems. They are highly complex sensing devices for electric measurements and are used in electrical substations for monitoring and protection purposes. All these devices act as the eyes and hands of higher level control and monitoring systems. Their communication with upper levels of automation networks is implemented by a variety of field buses and communication protocols.

### 1.2 Design challenges for industrial devices

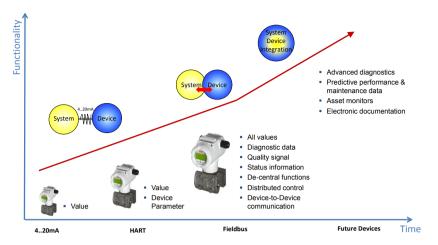

During the last 20 years, the amount of computation and communication functionalities embedded into industrial devices has considerably increased [100]. Figure 1.2 helps to illustrate the evolution of industrial devices during this time. Devices that where once point-to-point transmitters of process variables are now intelligent devices capable of performing multiple additional functionalities. For instance, they are equipped with advanced signal processing capabilities, they perform multiple self-diagnostic functionalities, they perform distributed control functions and they are able to communicate independently with other devices.

Figure 1.2: Increasing functionality of industrial devices

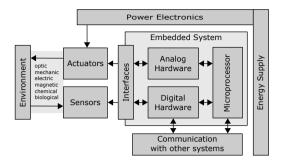

The design of embedded systems for industrial devices is a multidisciplinary activity that requires domain experts on digital and physical aspects of a design. Digital aspects refer to hardware and software components. Meanwhile, physical aspects refer to the physics behind the plant or process involved, as well as the analog and mixed-signal components used to interact with it. This combination of digital, mixed-signal, analog and physical systems lead to their classification as heterogeneous embedded system.

Certain assumptions must be done to separate digital and physical aspects of a design. The purpose of this separation is to reduce the complexity of a system by breaking it down into smaller and more manageable parts. For instance, a common approach in HW/SW (Hardware/Software) co-design of digital systems is the use of test benches. A common simplification is to consider test benches as static elements, such as sinks and sources. This is not valid when the execution of HW/SW components being developed is dependent on the behavior of physical processes they interact with. Physical processes are dynamic systems sensitive to a number of factors, such as feedback control, disturbances and particular operation points. Ignoring the intrinsic dynamic characteristics of physical processes in test benches is commonly a reason for integration problems that happen in later design stages. This results in unforeseen interactions between physical processes and components of embedded systems that can lead to costly and time-consuming redesign cycles.

A similar premise is used by authors such as *Branicky* [23] for describing hybrid systems, as well as *Lee* [82] and *Karsai* [75] for describing CPS (Cyber-Physical Systems). Their premise states that from a system level perspective, the execution of computation

4 1 Introduction

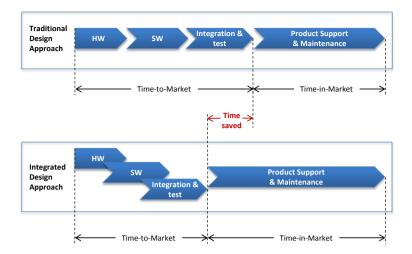

Figure 1.3: Example of an integrated design approach for embedded systems

and communication tasks performed by an embedded system are directly affected by the behavior of the physical process it interacts with and vice versa.

Industrial devices evidently fall into the classification of hybrid or cyber-physical systems since heterogeneous embedded systems are used for the measurement and control of physical processes. Similar examples can be found in other industries such as automotive, avionics, medicine technology, etc. The design challenges are to ensure the predictability and reliability of such systems, while at the same time keeping up with constraining time-to-market requirements. These challenges arise when digital and physical domains are closely coupled.

The assumptions made on early design stages due to the partitioning and simplification of digital and physical domains may not always be valid. They lead to inconsistencies in the specifications by which embedded systems are designed. The result is an increased number of iterative redesign cycles, which consequently leads to long times-to-market and costly development processes.

An improved design approach is needed. This is exemplary illustrated in Figure 1.3. It is an integrated design approach that envisions design teams working in parallel and being able to share and test their results together at different design stages. The advantage with respect to traditional design approaches is the possibility to perform verification and validation of complete systems at different designs stages. Higher quality results, in a shorter time-to-market, can be obtained thanks to the identification and resolution of design errors in earlier design stages.

1.3 Goals of this work 5

In practice, an ideal design flow such as the one illustrated in Figure 1.3 does not exist. Many technical tradeoffs must be considered, for example, the type of embedded systems being designed, their complexity, and the tools and modeling formalisms used. External factors must also be considered, such as the acceptance of development teams to adopt new design approaches and the overhead that this might bring.

### 1.3 Goals of this work

Traditional design approaches for embedded systems are characterized by their dependency on hardware prototypes and experimental setups for verification and validation purposes. More recent approaches such as Rapid Prototyping and Hardware-in-the-Loop testing are available that can help make this verification and validation process more reliable and efficient. A third and more recent approach is Virtual Prototyping. Virtual prototyping stands for the verification and validation of embedded systems using system level simulation models that emulate (mimic) the behavior of hardware prototypes and experimental setups.

Simulation techniques are an established aid during the development of embedded systems. They are used by various domains experts (hardware engineers, embedded software developers, physicist, etc.) for understanding and designing particular parts of a system. However, the impact of crossing simulation boundaries is rarely considered. Virtual prototypes offer the possibility to bridge the simulation boundaries between digital, analog and physical domains in order to have a better understanding of the systems being developed and of the complex interactions among them.

Related work on virtual prototyping include Ptolemy II [38, 44], the CODIS cosimulation framework [21, 51], the work from *Kirchner et al.* [77, 78] and the dissertation from *Verhoef* [134]. In these, the following points have not been fully addressed:

- The use of virtual prototypes for supporting various stages of the development life-cycle of heterogeneous embedded systems have not been investigated

- The possibility to reuse and test existing device firmware inside virtual prototypes

has not been considered. This includes embedded legacy code and hardware

dependent software (drivers and real time operating systems).

- The simulation of overall systems, which includes digital and physical domains, using processor emulation tools has not been addressed until now

6 1 Introduction

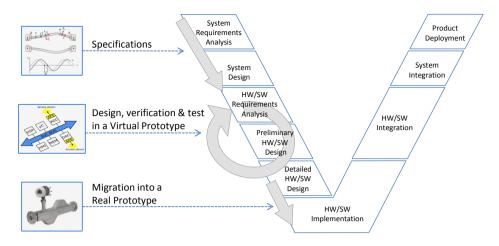

Figure 1.4: Virtual prototyping in the design of industrial devices

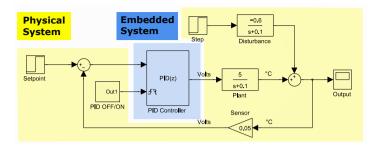

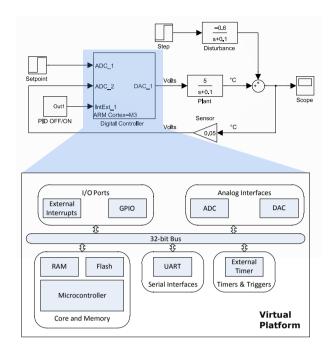

These points and their appropriate solutions will be addressed in this dissertation. This work proposes a virtual prototyping methodology for the design and verification of heterogeneous embedded systems. Its role in the design flow of industrial devices is illustrated in Figure 1.4. It is a model-based design approach that brings together hardware, software, analog and mixed-signal component models of embedded systems with physical models of their environment. It enables a new dimension of testing and verification capabilities by considering the effects that functional, structural and physical specifications have in the behavior of full systems. It also speeds up the design process since iterative design cycles are performed in a virtual environment, which is much faster than with real hardware prototypes and experimental setups.

The goal of this dissertation is to enable the use of overall system simulation approaches throughout the development process of heterogeneous embedded systems for industrial devices and to provide a supporting methodology for it. This work is intended to provide multidisciplinary team members with enhanced verification capabilities to identify and solve design problems during early development stages. This is possible by coupling the execution of different simulators, each one responsible for obtaining the behavior of part of a system. The combined execution of simulators can help increase the understanding of interdependencies between different system components. This eventually helps increase the confidence in the correctness of a design, thereby reducing risks in a project and leading to hardware prototypes and experimental setups that are built right the first time. Thereby, the following points will be addressed in this work:

1.4 Outline of this work 7

A multi-domain simulation framework where digital and physical system level

models can interact in a correct and reproducible manner. The selected tools and

modeling formalisms must be compatible with best-practices used in the industrial

automation domain.

- 2. A set of modeling guidelines intended to decrease the implementation effort of the proposed design methodology. The guidelines must provide a set of rules for the construction of consistent and meaningful virtual prototypes. They should ease the creation of virtual prototypes and help increase the reusability of designs.

- 3. A problem-oriented verification methodology for identifying and solving design problems before they propagate into further development stages. It should allow for top-down or bottom-up verification approaches in order to target specific verification goals. This should help increase the confidence in the correctness of heterogeneous embedded system designs.

### 1.4 Outline of this work

Chapter 2 gives an overview of the applications of industrial devices, their embedded systems and some of the best-practices used during their design. The initial requirements are identified and used as driving force for the work presented in the following chapters.

Chapter 3 and Chapter 4 describe the state-of-the-art on model based design approaches for heterogeneous embedded systems. This includes approaches for describing digital systems, analog and mixed-signal systems and physical systems. The state-of-the-art is evaluated regarding requirement for the design of industrial devices in order to define the scope of this dissertation.

Chapter 5 and Chapter 6 describe the proposed virtual prototyping methodology for the design, verification and test of industrial devices. These chapters define modeling guidelines for creating virtual prototypes and a problem-oriented verification methodology applicable to different design stages.

Chapter 7 describes a multi-domain simulation framework that enables the verification strategies of the above-mentioned virtual prototypes. It describes a generic and efficient co-simulation algorithm for coupling continuous-time and discrete-event simulators. It also describes its implementation for coupling SystemC/Simulink and SystemC/VHDL-AMS simulation engines.

8 1 Introduction

Chapter 8 describes the evaluation of the work presented in this dissertation. Two application examples are presented: the first one is based on an academic example and the second on an ongoing industrial project.

Chapter 9 presents the conclusions of this work and an outlook for further research on applications for virtual prototyping methodologies in the industrial automation domain.

## **Industrial Devices**

This chapter provides the necessary background for understanding the challenges encountered during the design of industrial devices used in the field level of industrial automation systems. These devices are complex heterogeneous embedded systems responsible for the monitoring, measurement and manipulation of physical processes in the field level. This chapter gives an overview of the applications of industrial devices, their embedded systems and some of the best-practices used during their design. The initial requirements for this dissertation are identified and are used as driving force for the work presented in the following chapters.

## 2.1 Industrial devices in automation systems

The overall goal of industrial automation systems is to optimize processes and assets in all levels of an organization. This is archived by various electronic systems that gather information from physical processes in order to control them in a safe, reliable and efficient manner. Industrial automation systems can be found in any major industrial sector. Some examples are listed in Table 2.1.

Industrial automation systems are distributed across all layers of an organization as shown in Figure 2.1. This helps identify the different levels of an industrial automation system, as well as the main activities performed in each of them. Since the scope of this dissertation is on industrial devices on the field level, only the three bottom levels of

10 2 Industrial Devices

| Sector                 | Industries                                |

|------------------------|-------------------------------------------|

| Power generation       | coal, gas, wind, solar                    |

| Distribution           | water, gas, oil, electricity              |

| Process manufacturing  | food & beverage, chemical, pharmaceutical |

| Discrete manufacturing | automotive, electronic appliances         |

| Buildings              | HVAC, lighting                            |

| Transportation         | railways, maritime ports, airports        |

**Table 2.1:** Example of industries relying on industrial automation systems

Figure 2.1: Hierarchy of industrial automation system according to ISA-95 [19]

Figure 2.1, corresponding to manufacturing control activities, will be described ahead.

### 2.1.1 Industrial processes

This section describes in more detail the physical production processes corresponding to Level-0 of Figure 2.1. According to the DIN19222 [39] control technology terminology, a process is defined as a set of concurrent operations acting upon a system in which mater, energy or information is transformed, transported or stored. The definition applies to any type of industrial process, e.g. a petrochemical process in a refinery plant or an assembly process in the automotive industry. Moreover, the ISA-95 standard [74] further classifies processes into three types: continuous, discrete and batch processes.

### Continuous processes

Continuous processes are associated with the transformation of raw materials into products. The transformation process results in a product that cannot be separated into its raw materials, e.g. oil refinement, electricity generation, food and beverage products. Such systems require sensors and actuators that determine and regulate physical properties of raw materials, and control systems that monitor and control the overall transformation process. Continuous control systems are used extensively in industrial applications such as: food & beverage, pulp & paper, oil & gas, chemical processing, power generation and distribution, etc.

From a mathematical point of view, the behavior of continuous processes is described by continuous states and state transitions. They are monotone and reversible [95], which makes them controllable by techniques such as feedback control. Thereby, control tasks for continuous processes focus mainly on the regulation of measurable physical properties.

### Discrete processes

Discrete processes are associated with the assembly of parts into a final product. The transformation process is reversible, thus individual parts can be identified in the final product. Such systems require sensors and actuators that can determine and alter the state of a system according to commands from a control system. Discrete control systems are used extensively in the automotive industry, for example, to assemble parts in a car and to transport it to different locations inside a plant. Many industries rely on discrete control systems for activities such as printing, sorting, packing and transport of materials or products via conveyor belts or cranes.

From a mathematical point of view, the behavior of discrete processes is described by discrete states and abrupt state transitions from one state to the next caused by input events. They are reversible and not monotone [95], meaning that the removal of an input stimuli will not necessarily bring a process back to its previous state. Thereby, control tasks for discrete processes focus mainly on the calculation of discrete sets of commands that can bring a process to a desired state.

### **Batch processes**

Batch processes are systems with continuous and discrete processes. Pharmaceutical and chemical industries are classical examples of applications with dominantly batch processes. In this context, a control task is represented by a sequence of discrete steps

12 2 Industrial Devices

needed to carry out a recipe, while each step is described by a continuous process particular to the assigned resource (e.g. heating, filling, mixing). For example, in a bottle-filling application a discrete process describes the sequence of events for bottles transported on a conveyor belt, while a continuous process describes the filling process (pour a certain volume of liquid into each bottle).

### 2.1.2 Industrial devices

This section describes in more detail the industrial devices used for sensing and manipulation activities corresponding to Level-1 of Figure 2.1. Industrial devices are highly specialized electronic devices responsible for the measurement and control of industrial processes. They are further classified as discrete and continuous instruments, according to the type of industrial processes they interact with.

#### Discrete instruments

Discrete instrumentation devices are sensors and actuators used to identify and manipulate discrete states of a process. Examples of such devices are proximity detectors. They are micro-switches, optical sensors or magnetic sensors that communicate binary values about the presence or absence of an object. Further examples are pushbuttons, position encoders and identification solutions (bar code scanners, RFID detectors, machine vision, etc.).

#### Continuous instruments

Instrumentation devices for continuous processes are responsible for the measurement, manipulation and local control of continuous processes. Figure 2.2 shows classical examples of industrial devices for continuous process in the process automation market. They correspond to one of the categories listed below:

- Sensors.- Measurement devices that extract process variables and transmit them to

control and automation systems. Such variables are related to physical properties

of a system, thereby requiring specialized sensing elements and measurement

principles. Some examples are sensors for temperature, pressure, flow and level.

- Actuators.- Responsible for executing manipulation tasks coming from control and automation systems. Some examples of actuators in industrial applications are electric contactors, heating elements, pneumatic and hydraulic positioners and electric motors.

Recorders and controllers.- They provide data visualization and control capabilities

of continuous processes. They are installed directly in the field level, in proximity

with sensing devices and actuators. The most common example are PID process

controllers.

Figure 2.2: Examples of continuous instruments offered by ABB

### 2.1.3 Industrial controllers

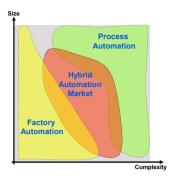

This section describes in more detail the industrial controllers used for monitoring, supervision and control activities corresponding to Level-3 of Figure 2.1. The distinction between continuous, discrete and batch processes has led to the specialization of industrial automation systems. Figure 2.3 illustrates the classification of industrial automation systems according to the type of process they interact with. Each market specializes on specific type of processes: factory automation on discrete processes, hybrid automation on batch processes and process automation on continuous processes. It is also interesting to notice that not only the type of processes determines the most adequate control system, but also the size and complexity of a process.

In the factory automation market, monitoring and control tasks are carried out by the combination of SCADA (Supervisory Control and Data Acquisition) systems and PLC (Programmable Logic Controller) systems. PLC controllers are affordable industrial controllers specializing on medium to low complexity tasks related with discrete processes. Various PLC controllers may be utilized in a plant according to its size and control requirements. An example of a PLC controller, the AC500 from ABB, is presented in Figure 2.4a. SCADA systems provide an overview of the control operations carried out by PLC controllers. Their task is the supervision and collection of all data coming from PLC controllers. Often, they are accompanied with data visualization solutions useful to present the state of a process in real-time.

14 2 Industrial Devices

Figure 2.3: Classification of markets for industrial automation systems [3]

In the process automation market, monitoring, data acquisition and control tasks are carried out by DCS (Distributed Control Systems) systems. DCS systems are more complex than their SCADA/PLC counterparts in factory automation. In comparison to SCADA/PLC combinations, DCS systems centralize distributed control operations, provide advanced functionalities and can handle more I/O modules. Another difference to SCADA/PLC combinations is that DCS systems provide diagnosis information of processes and enable remote access to field devices from an operator console. This is possible thanks to more intelligent field devices and more advanced communication protocols. The application market of DCS control systems are plants with complex continuous and batch processes. An example of a DCS controller is the 800M controller from ABB showed in Figure 2.4c.

The hybrid automation market offers monitoring and control solutions for continuous/discrete and batch processes of middle complexity. Such solutions may include SCADA/PLC and DCS combinations or dedicated systems such as the Freelance controller from ABB showed in Figure 2.4b.

Figure 2.4: Examples of industrial automation systems offered by ABB

### 2.1.4 Industrial communication

The communication requirements for each level of an automation system are very different. For instance, at the field level hundreds or thousands of instruments communicate data via dedicated lines or shared fieldbuses. This requires robust communication networks with various data rates and real-time constraints. Data is then gathered in the control level where new commands are issued. This requires communication networks that support high data rates and real-time constraints. Finally, communication networks in the station level have even higher data rates, but no real-time constraints since mainly monitoring activities are performed.

Various communication standards are available in the industrial automation domain. Some of the most significant industrial communication standards are listed in Table 2.2. The most relevant of these are described ahead.

#### 4-20mA

The simplest industrial communication standard available is the 4-20mA hardwire communication. It has been used for decades in the process automation market and is still widely implemented. It enables the transmission of primary process variables encoded as a 4-20mA analog current. Basic error signalization is possible by transmitting current values on defined ranges outside the 4-20mA range [43]. The physical mediums are point-to-point 2-wire or 4-wire cables between field devices and I/O modules of a controller. This creates a current loop for the transmission of analog data. The key elements of current loops are analog transmitters. These can be sensing elements, such as temperature transmitters, or I/Os from a controller. The advantage of 4-20mA current loops is that they provide a simple and robust communication medium for transferring analog data. Since the information is an electrical current value, it is insensitive to the line resistance or voltage variations. The disadvantages are the amount of cabling required for their installation, the limited amount of information that can be transferred (only

| Field Level          | 4-20mA, HART, FOUNDATION Fieldbus, Profibus DP/PA, PROFINET IO, Modbus RTU, CANopen, IEC 61850-9-2 |

|----------------------|----------------------------------------------------------------------------------------------------|

| <b>Control Level</b> | FOUNDATION Fieldbus, PROFINET, Modbus TCP,                                                         |

|                      | IEC 61850-8                                                                                        |

| Station Level        | Ethernet TCP/IP                                                                                    |

**Table 2.2:** Examples of industrial communication networks

16 2 Industrial Devices

one process variable), and that the communication is unidirectional (sensor-controller or controller-actuator).

### **HART**

The HART (Highway Addressable Remote Transducer) industrial communication protocol is widely used in the process automation market. It is backwards compatible with 4-20mA communication standard in order to reuse available cabling from existing installations. The HART communication protocol uses a frequency shift keying principle to modulate digital signals onto a 4-20 mA DC analog current [58]. Physical connections between field devices and I/Os of controllers can be point-to-point or multi-drop. In point-to-point connections, primary process variables are transmitted as analog currents and secondary process variables from intelligent field devices are transmitted as modulated digital signals. In multi-drop connections, multiple field devices can be connected to the same current loop. Since all devices share the same physical medium, primary and secondary process variables from intelligent field devices are transmitted digitally upon polling requests from a controller.

#### **Fieldbuses**

A variety of fieldbus communication standards from different standardization organizations are available. In the factory automation market, simple fieldbuses are required since the data transferred are discrete values. Examples of fieldbuses with low overhead and small data packets are Seriplex, Interbus-S, and AS-I (AS-Interface), which are sometimes called sensor buses or bit level buses [16]. Other more advanced fieldbuses are DeviceNet, ControlNet, and PROFIBUS DP, which are referred to as device buses or byte-level buses [16].

In the process automation market, digital communication protocols such as FOUN-DATION Fieldbus and Profibus are widely used. In comparison to HART, they are fully digital and are not backwards compatible with 4-20mA installations. Instead, they rely on a bus topology where instrumentation devices and controllers are connected to.

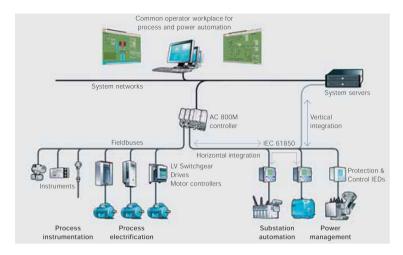

The substation automation market uses industrial communication standards which are similar to fieldbuses in the process automation market. Since 2002, various device manufacturers have started to follow a new Ethernet-based communication standard called IEC 61850 [22]. The IEC 61850 solves interoperability problems between devices developed by different manufacturers and enables the use of more intelligent devices called IEDs (Intelligent Electronic Devices). They are used for protection, control and

Figure 2.5: Integrated process and power automation [56]

electrical metering. They connect to instrument transformers and primary equipment in switchyards, such as switchgear and power transformers. IEDs are similar in terms of computation and communication capabilities to field devices in the process automation market. Figure 2.5 shows an example of how fieldbuses for process automation and the IEC 61850 for substation automation are able to coexist in a plant thanks to advanced DCS control systems.

# 2.2 Embedded systems for industrial devices

Each level of an industrial automation system relies on different underlying technologies. They are selected according to requirements such as processing power, memory, communication data rates and real-time behavior. For instance, in the station level, tasks are highly data oriented. Large amounts of information, generated by the control and field levels, need to be stored, transferred and monitored. The underlying technologies are typically general purpose, such as PCs, data servers and high bandwidth networks. In the case of the control level, multiple industrial processes, sometimes strictly dependent on each other, need to be carefully orchestrated and synchronized. This requires the execution of multiple control cycles with real-time processing and communication constraints. The underlying technologies are industrial computers relying on powerful processor architectures, as well as various types of industrial networks. Lastly, in the field level, highly specialized sensing, manipulation and local control tasks need to be

18 2 Industrial Devices

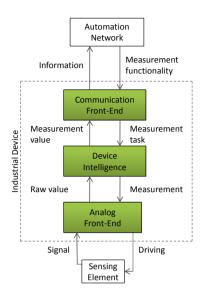

Figure 2.6: Basic structure and functionality of an industrial measurement device

performed. Real-time processing and communication constraints apply here as well. The underlying technologies are embedded systems with strict limitations regarding their processing and communication capabilities, memory and power consumption.

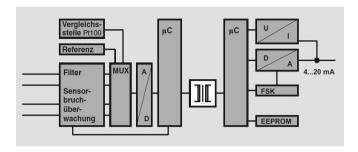

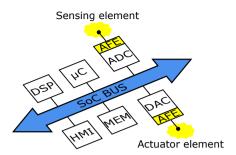

Figure 2.6 shows the basic structure and functionality of an industrial measurement device. It relies on three main components for its operation: an analog front-end, a device intelligence module and a communication front-end. The analog front-end is responsible for interacting with transducers and other sensing/actuating elements. It performs function such as signal adaption, filtering and quantization. The device intelligence is responsible for the execution of measurement tasks and for performing data analysis on acquired data sets. It may also be responsible for the execution of communication stacks. Finally, the communication front-end is responsible for the communication with higher levels of an automation system using industrial communication standards such as 4-20mA, HART or some digital fieldbus.

The structure and functionality of modern industrial devices is in reality more complex. In general, they all rely on the three basic modules explained above (analog front-end, device intelligence and communication front-end). However, each of these modules must be tailored according to particular applications and requirements. They also support a number of additional functionalities which are constantly evolving in new product lines. Such increase in functionality is intended to provide a better handling of industrial devices themselves (e.g. useful during commissioning, maintenance, diagnosis) and

to make the operation of an industrial automation system more efficient (e.g. higher accuracy, better transient response, lower power consumption).

## 2.2.1 Hardware platforms

Industrial devices are designed for particular measurement and control applications. They are also designed according to particular hardware safety requirements such as SIL (Safety Integrity Level) certification and explosion safety protection. Therefore, the complexity and heterogeneity of hardware platforms for industrial devices can vary significantly. They may include a variety of software programmable components (e.g. microcontrollers, DSPs, hard/soft cores in FPGAs), hardware programmable components (e.g. FPGAs), digital and mixed-signal off-the-shelf components (e.g. memories, A/D and D/A converters, transceivers) and analog circuitry (e.g. protection circuits, filters, multiplexers, voltage regulators, transducers).

Figure 2.7 shows an example of a hardware platform of an industrial temperature transmitter. It is a 2-wire platform, where a device is powered by the same two wires used for 4-20mA communication. The block diagram shows in a simplified way the digital, analog and mixed-signal components that make up its structure. The analog front-end is implemented by analog and mixed-signal components such as analog filters, a multiplexer, an A/D converter and other analog circuitry. The device intelligence is implemented by digital components, in this case two microcontrollers due to the galvanic isolation between circuitry on the process side and circuitry on the automation network side. The communication front-end is implemented by further mixed-signal components such as a voltage-to-current converter, a D/A converter and a frequency shift keying signal modulator for HART communication. In this example, a typical distribution of tasks are signal adaption and sensing tasks in the in the left side of the galvanic isolation, whereas signal processing and communication tasks are assigned to the right side of the galvanic isolation.

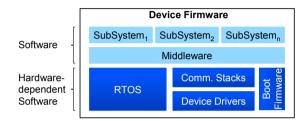

#### 2.2.2 Device firmware

The device firmware of an industrial device is composed of hardware-dependent and hardware-independent software components as illustrated in Figure 2.8. Hardware dependent software is shown in the bottom part of Figure 2.8 and includes boot firmware, device drivers, communication protocol stacks and real-time operating systems. Hardware independent software, or simply software as depicted in the top part of Figure 2.8, includes middleware, adapters and subsystems for application software.

20 2 Industrial Devices

Figure 2.7: Block diagram of an industrial temperature transmitter circuitry [43]

Figure 2.8: Device firmware of an industrial device

Software is the primary mean for implementing communication and computation functionalities in industrial devices. Application software is encapsulated in subsystems derived from component based approaches [100]. In component based approaches, subsystems are defined as sets of related functions and data objects that are able to communicate with each other through well-known interfaces. This is vital for maintaining software architectures of industrials devices and for reusing software components throughout different product line.

# 2.3 Design approaches for industrial devices

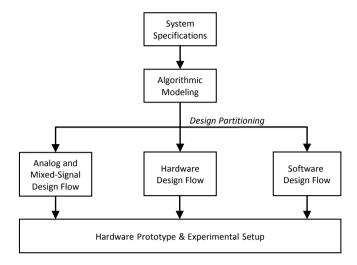

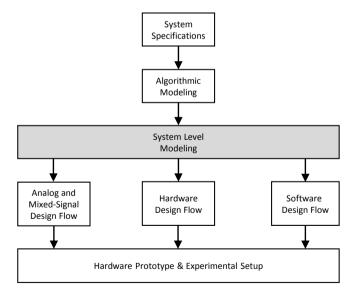

Figure 2.9 illustrates the initial stages of the design of embedded systems for industrial devices. It corresponds to the left side of the V-Model. A similar design flow is followed in most applications where embedded systems are used to interact with physical processes. It starts with the definition of the system specifications and ends with the creation of a hardware prototype and an experimental setup. Further steps in the design include integration and testing phases, corresponding to the right side of the V-Model, and are not shown in the figure.

Figure 2.9: Design flow of embedded systems

System specifications are based on functional and non-functional requirements. Functional requirements describe the particular measurement or control principles that need to be implemented in an embedded system, as well as boundary conditions for its operation. Non-functional requirements include things like operation temperature range, safety considerations, robustness considerations, the desired power consumption, footprint and cost, etc.

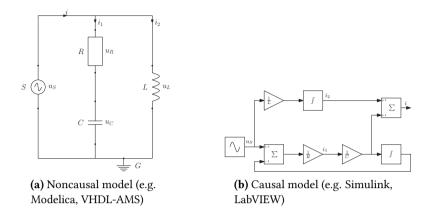

Algorithmic models are derived from functional system specifications. They are behavioral models described using formalisms such as mathematical equations, lumped models or transfer functions. Within the algorithmic modeling stage, measurement and control algorithms, which will be later executed in an embedded system, are verified and validated together with plant models. Commercial modeling and simulation tools for dynamic systems such as MATLAB/Simulink and LabVIEW are commonly used during this stage. Further examples are multi-body system dynamics simulation tools such as Modelica, ADAMS, RecurDyn or Simpack.

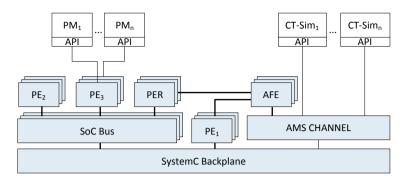

Once enough knowledge of a system's behavior has been gathered during the algorithm modeling phase, a complete paradigm shift occurs. This is depicted in Figure 2.9 as design partitioning. It refers to the partitioning of embedded system functionality into hardware, software, analog and mixed-signal components. Afterwards, each of them is independently designed using specialized tools and formalisms. These are, for instance, software compilers and debuggers for the software design flow, synthesis and place-and-route tools for the hardware design flow, and circuit schematics tools for the analog design flow.

22 2 Industrial Devices

Hardware, software, analog and mixed-signal components of a system are brought together in the integration phase for the construction of a first hardware prototype. Experimental setups are also constructed in test laboratories equipped with appropriate test equipment. For instance, a typical test setup for a flow meter requires test labs equipped with water tanks, pipes, heaters, pumps, etc. Within this stage, design iterations on hardware prototypes must be performed to correct possible design errors. This results in the creation of further versions of hardware prototypes and may involve performing changes in experimental setups. Solving design problems in such late design stages implies costly and time consuming redesign cycles that may take months to complete. This can severely increase a project's risk, delaying times-to-market and increasing the overall cost of a project.

# 2.4 Identification of requirements for this work

During the design of industrial devices, a considerable amount of time and effort is invested in the integration phase. Within this phase, the identification of design errors typically means going back to previous design stages and, in some cases, performing subsequent redesign of a hardware prototype. The reasons of such problems include:

- Inconsistencies in the specifications

- Misunderstanding of specifications by different team members

- · Lack of specification follow-up throughout the design phase

- Unexpected interactions between internal components of embedded systems

- Unexpected interactions between components of embedded system and their physical environment

Virtual prototypes make it possible to identify and correct the problems listed above using overall system level simulations. Such problems might otherwise appear in later design stages, where the cost of solving them increases. Overall system level simulation refer to the combined simulation of hardware, software, analog and mixed-signal components of embedded systems together with physical models of the plants or processes they interact with. A methodology is required that can help guide the generation of such virtual prototypes and their subsequent use for the resolution of possible design problems.

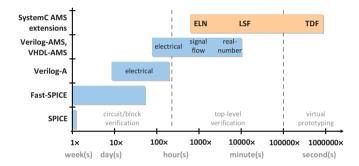

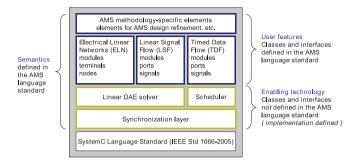

Simulation techniques are extensively used during the design of industrial devices. They are highly specialized, thereby used for the design of particular parts of a system, which can be hardware, software, analog or mixed-signal components. Overall simulations are possible by bringing together different parts of a system and their respective simulation engines. This is not a trivial task and requires a deep understanding of the models of computation behind each simulation engine. Therefore, the following issues have been identified and will be addressed in this dissertation:

- 1. How to describe the structure and behavior of embedded systems (including hardware, software, analog and mixed signal components) and the physical models of their environment?

- 2. Which information is necessary for the creation of meaningful models of embedded systems and their environment and at what point of the development process are they available?

- 3. Which problems can be addressed by overall system level simulation of embedded systems and physical models and at what stages of the development process can they be used?

- 4. How can overall system level simulation approaches be integrated into existing development processes of industrial devices?

Point 1 is addressed in Chapter 3 and Chapter 4 with appropriate models of computation for describing and simulating embedded system components and physical processes. Point 2 is addressed in Chapter 5 with modeling guidelines that define the amount of detail permitted in a model and define how simulation results must be accordingly interpreted. Point 3 is addressed in Chapter 6 with a problem-oriented design methodology that correlates the type of models that must be used according to particular problems that need to be solved during different design stages. Point 4 is addressed in Chapter 7 with a generic co-simulation framework for coupling continuous-time and discrete-event simulators. Such co-simulation framework is required by the previously mentioned models and verification methodology.

# Model Based Design of Embedded Systems

This chapter gives a background on model based design approaches for embedded systems. The focus is on system level design methodologies for digital systems, analog and mixed-signal systems and physical systems. These systems are initially separated since they describe different aspects of a design. In Chapter 4 they are brought together for describing heterogeneous embedded systems.

# 3.1 System level design

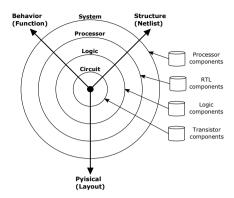

The fundamental principles for modeling digital systems were described by *Gajski* [47] with the diagram shown in Figure 3.1 called the Y-Chart. The axis of the Y-Chart corresponds to three different design concerns and their respective abstractions are represented by four concentric circles. According to the Y-Chart, any embedded system, no matter its complexity, can be described using three types of models. These are behavioral models (also called functional models), structural models (also called net lists or block diagrams) and physical models (also called layout or board design). In addition, models can be described in four main abstractions, represented as concentric circles around the axis origin. The names of the abstraction layers correspond to the type of components generated on each level: transistors on the circuit level, flip-flops and logic

**Figure 3.1:** Y-Chart [47]

gates on the logic level, ALUs (Arithmetic and Logic Unit) and hardware multipliers on the processor level, and processors, memories and buses on the system level.

#### 3.1.1 Overview

System level design approaches describe embedded systems with models corresponding to the highest abstraction level depicted in the Y-Chart. The separation of design concerns, represented by the three axis of the Y-Chart, makes it possible to independently describe behavioral, structural and physical aspects of a design. The advantages of system level design with respect to lower abstraction design levels such as RTL (Register Transfer Level) are faster simulation speed and increased model reuse. The tradeoff is a lower accuracy due to the high abstraction in which models are described.

System level design methodologies are intended to cope with the increasing complexity of embedded systems and to enhance the productivity of their designers [80]. They are model based design approaches used for the design, refinement and verification of embedded systems. The goals of system level design methodologies can be summarized as follows:

- Enable HW/SW co-design and design space exploration

- Provide effective means for design and reuse

- Facilitate the refinement of models into implementation solutions such as software binaries or RTL models

## 3.1.2 Design methodologies

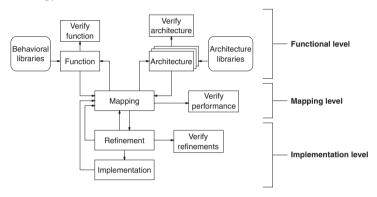

The basic components of a system level design methodology are presented in Figure 3.2. An essential part is the orthogonalization of design concerns, i.e., the separation of various aspects of a design to allow more effective exploration of alternate solutions [76]. The most common separations are done between functionality and architecture, and between communication and computation. The different levels of a system level design methodology are described ahead.

Figure 3.2: System level design methodology for embedded systems [80]

#### **Functional level**

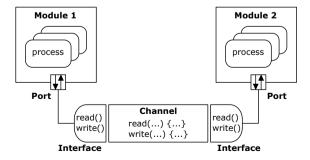

The first form of orthogonalization of design concerns is the separation between functionality and architecture. Functionality is described via behavioral models whose execution semantics are described by a particular Models of Computation (MoC). Common MoCs used to describe functional models are Finite State Machine (FSM) or Synchronous Data Flow (SDF) [81] models. They can also be described with imperative MoCs such as sequential programing language like C/C++.

Architectures are system level models of hardware components endowed with I/O ports. Ports are interconnected via signals in order to form net lists. Architectural models are intended to describe the operation of hardware implementation solutions such as software programmable components (DSPs and microcontrollers), fixed hardware components (buses, peripherals and other ASICs) and custom hardware components (FPGAs).

The second form of orthogonalization of design concerns is the separation between communication and computation. This is essential for the reuse of models and for their refinement into lower abstraction models. This is possible by defining the communication semantics between models independent to their performed computations. The separation is done using common design patterns such as interfaces whose implementation is defined by the communication channel they connect to [50]. Communication channel enable the interoperability between models by using things such as adapters, protocols and payloads that define how information is shared.

#### Mapping level

The process of assigning a function to an architecture is called mapping. For example, a signal processing algorithm corresponding to a functional model can be mapped as a software component in a an architectural model of a microcontroller or it can be mapped as a hardware accelerator in an architectural model of an FPGA.

HW/SW co-design is possible since SW models, corresponding to functional models, and HW models, corresponding to architectural models, can be mapped and tested together. HW/SW co-design can be used to explore the design space in order to optimize a design according to particular metrics and constraints. Such constraints are estimated values of performance and costs in terms of resource usage obtained by analytic, simulation or hybrid based methods (refer to Section 3.1.4).

#### Implementation level

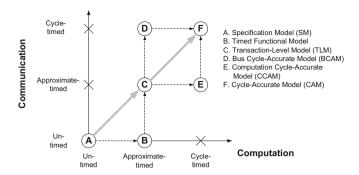

The refinement of system level designs down to the processor level consists of a series of intermediate levels. This process has been described by various authors [25, 34, 42] and vary mainly in the terminology used. Figure 3.3 shows such process according to *Cai and Gajski* [25]. A system level design starts with untimed functional and architectural models mapped into a Specification Model (SM). Following the separation of communication and computation aspects, specification models are refined into approximately-timed models, corresponding to Transaction Level Models (TLM), and finally into Cycle-Accurate Models (CAM). The transformation of computation and communication models does not necessarily need to be done at the same time, which gives rise to models *B*, *D* and *E* from Figure 3.3.

System level design methodologies such as the one shown in Figure 3.2 define how specification models must be described in order to be transformed into Transaction Level Models (TLM) and Cycle-Accurate Models (CAM) models. Each of these models is useful for different design purposes: specification models for conceptual design, TLM models for embedded software programming and CAM models for hardware design. In the end,

Figure 3.3: Refinement of system level models [25]

regardless of the system level design methodology, the desired implementation result are software binaries ready to be directly loaded into a target processor or synthesizable RTL models for an FPGA target.

#### Further design methodologies

System level design methodologies had been restricted to the academic domain [10, 28, 36, 61] during the last ten years. Some of the most relevant are the Metro II framework [36] from Prof. Alberto L. Sangiovanni-Vicentelli and his team at Berkley University and the ESE (Embedded Systems Environment) [28] framework from Prof. Daniel D. Gajski and his team at the University of California Irvine. The Metro II framework is an implementation of Platform Based Design [76] premises and focuses on the automatic mapping of high level behavioral descriptions into architectural models. The ESE framework focuses on the automatic refinement of system level models into RTL descriptions.

The EDA (Electronic Design Automation) market has started to adopted principles from system level design. This has triggered the offering of commercial tools that focus on particular aspects of system level design. Available commercial tools for system level design focus primarily on modeling and simulation using virtual platforms.

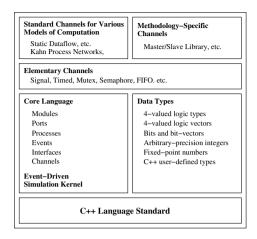

## 3.1.3 System level design languages

Hardware designers for integrated circuits are familiar with models based on the RTL level. The hardware description languages used are VHDL or Verilog. RTL abstractions are adequate for describing hardware and their inherent timing and concurrency, but lack expressiveness to describe embedded software. In contrast, embedded software designers

are familiar with programming languages such as C/C++ and assembly languages. These languages are ideal for describing sequential execution of instructions, but lack support for describing timing and concurrency of hardware components.

Languages for system level design describe hardware and software components of embedded system in a high abstraction. They rely on high level programing languages that support modeling concepts from hardware description languages and embedded software programing languages. They support key aspects for describing the behavior and structure of hardware components, such as timing, hierarchy, synchronization and concurrency. They also support embedded software descriptions, which are commonly given as sequential code or using higher models of computation such as state machines or static data flow models.

Some example of system level design languages are SpecC [48], SystemC [55], and SystemVerilog [119]. SpecC and SystemC are based on C and C++ respectively. These are natural languages for describing software components, but not for hardware descriptions. Hardware modeling capabilities are added using extensions (SpecC) or libraries (SystemC). Further details on SystemC are given in Section 3.2. On the other hand, SystemVerilog originates from the Verilog hardware modeling language. SystemVerilog is an extension to Verilog that enables the description of software components.

## 3.1.4 Verification and validation approaches

In the software engineering community, the terms verification and validation are defined according to the IEEE 1012-2004 standard as follows:

- Verification: "The process of evaluating a system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase." [72]

- Validation: "The process of evaluating a system or component during or at the end of the development process to determine whether it satisfies specified requirements." [72]

The definitions also apply to system level design with the difference that the end products are models of HW/SW components. Verification is used to check that models are constructed according to their specification (*am I building the model right?*). Validation concentrates on the bigger picture, on whether the constructed model is suitable for the intended application (*am I building the right model?*). Combined, verification and

validation provide a certain degree of confidence that a system will behave as expected once it is implemented in a real prototype.

System level design methodologies such as the one showed in Figure 3.2 specify a series of verification steps that may be done in each stage of the design. In each step, a designer needs to make sure that models behave according to their specifications and that they do so in an efficient, safe and deterministic manner. Various verification techniques are available for such purpose and are classified as analytic or dynamic techniques. Analytic techniques rely on formal verification methods and dynamic techniques rely on simulation based methods. This dissertation focuses on simulation based methods for verification purposes. Formal verification methods are not implemented in the work, but they propose an interesting alternative and are thus described ahead.

#### Formal verification methods

In formal verification methods, the accordance of a model to its specifications is statically checked using a series of mathematical formulations. Instead of requiring a designer to manually check simulation traces for their compliance, formal verification approaches can be automated. They are able to determine all possible states of a model and check for the compliance of specifications accordingly. Unlike simulation approaches, which are limited to checking specifications using a defined set of stimulus, formal approaches are able to check for scenarios which may not have been considered by a designer.

There are three main components to any formal verification method: a *modeling language* in which the system can be described, a *specification language* for the formulation of properties, and a deductive *calculus* or *algorithm* for the verification process [33]. Formal methods rely on mathematical formulations to verify the correctness of a model against formal specifications described in some logical language. They are also able to verify the equivalence between models which have gone through a refinement stage, in which case specifications from an abstract model should be true for a refined model as well. In either case, the process of verification involves the application of the rules of inference of the logic system [9] which provide an absolute answer to a verification problem.

The modeling language must provide a defined set of modeling formalisms, also known as MoCs (Models of Computation). MoCs define available constructs and rules that can be used to describe a system. Typically these MoCs are finite state machines or imperative programing languages. Such rules make it possible to automatically translate models into some sort of abstract mathematical representation which will be used together with formal specifications as an input to the verification process.

Formal specifications use logical languages to describe system properties with precise mathematical notations. Specifications are predicates, meaning that they are evaluated as *true* or *false* by the verification process. Temporal logic descriptions such as linear temporal logic (LTL) and computation tree logic (CTL) are the most widely used type of formal specifications. They enable to express properties such as the occurrence of an event and its properties (event A must occur at least once or infinitely many times), the causal dependency between events (if event A occurs, event B must also occur) and the ordering of events (after every occurrence of event A, event B must follow). They are also able to express many safety and liveness properties of systems. Safety properties are specifications in which "nothing bad happens" during execution. Similarly, liveness properties specify that "something good will happen" during the execution. More details on formal specification languages can be found in [33].

The key difference between formal and dynamic verification approaches is the absence of test patterns. This is possible since the verification process checks for the compliance of specifications over all possible states of a model. The verification process is done using an automatic technique called model checking. Other techniques such as equivalence checking and theorem proving are available and can be found in [49]. Model checking [32] is an algorithmic method for determining whether a system satisfies a formal specification expressed as a temporal logic formula. All reachable states of a model are represented as a Kripke structure, which itself should be a model of the specification formula in order to declare the correctness of a model. The main technical challenge in model checking is the state space explosion problem, addressed by state space reduction techniques. Further details on model checking are out of the scope of this work and can be found in [31–33].

Formal verification methods are adequate for design stages that require some level of automation. This is the reason why they are widely implemented by hardware synthesis back-end tools and by static code analyzers used for software development. Despite their evident benefits, formal verification methods for system level design are not yet widely available in the EDA market, where simulation-based verification is still dominant. Further drawbacks of formal methods are that they limit the expressiveness in which models can be described and, since engineers are not commonly familiar with the mathematical background required to describe formal specifications, these methods are still limited to a small group of design experts.

SPIN [65] and UPAAL [12] are well known model checkers used in both industry and research communities. There are few applications of these in system level design methodologies. Specifically, they are used for checking safety and liveness properties of

SystemC models. In [131], SystemC models were automatically translated into PROMELA language used by SPIN. In [12], SystemC models were automatically translated into timed automata models used by UPAAL. In both cases, safety and liveness properties could be verified. However, the SystemC kernel had to be previously described in PROMELA or timed automata formalisms before SystemC models could be verified. A further application is the Satya framework, which according to their authors [79] can be used for detecting deadlocks, write-conflicts and safety property violation of SystemC models.

#### Dynamic verification methods

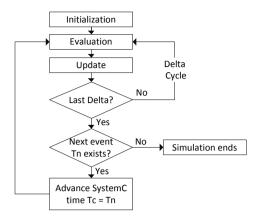

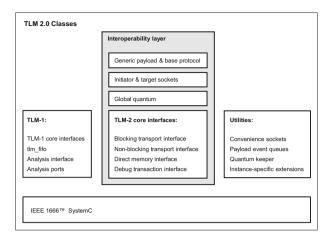

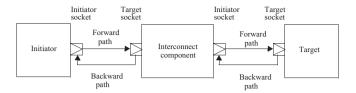

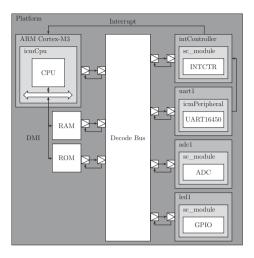

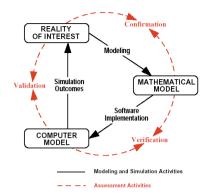

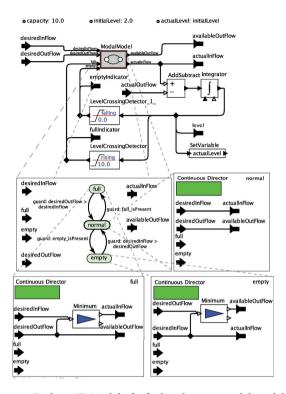

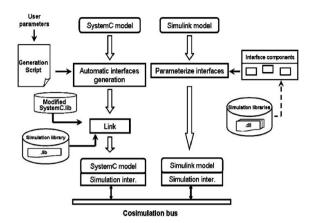

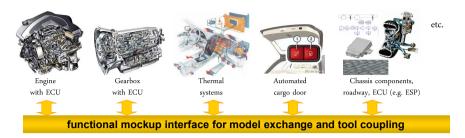

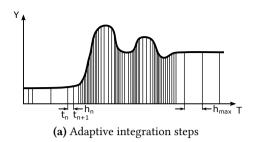

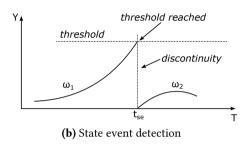

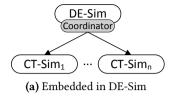

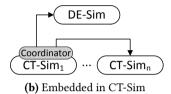

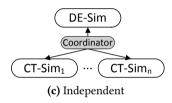

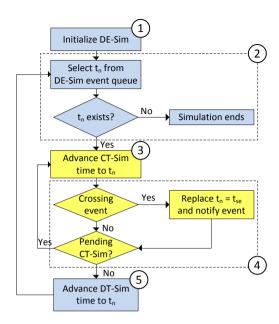

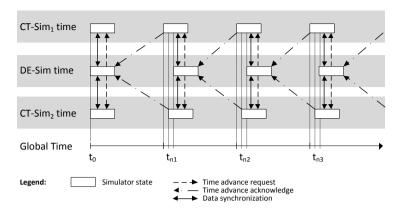

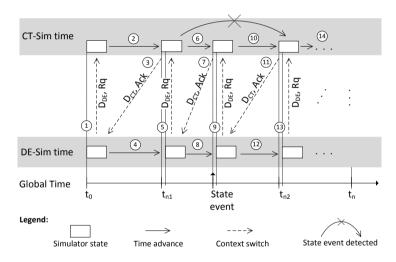

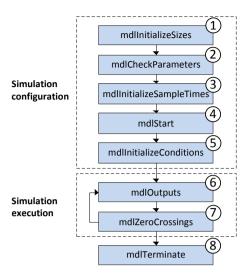

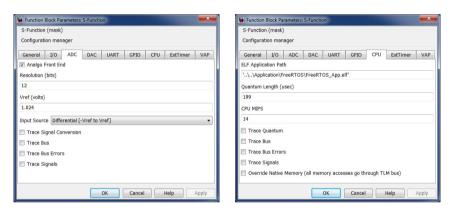

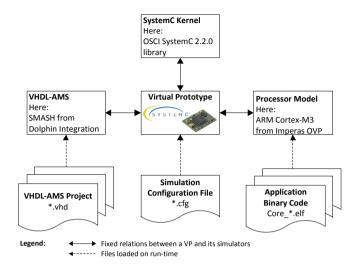

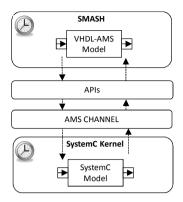

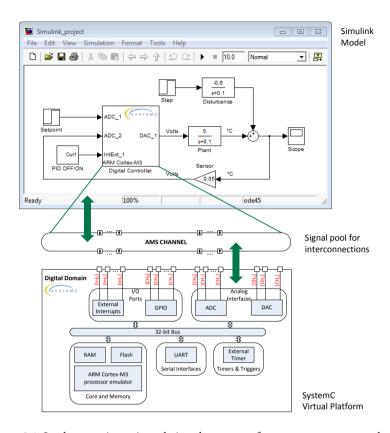

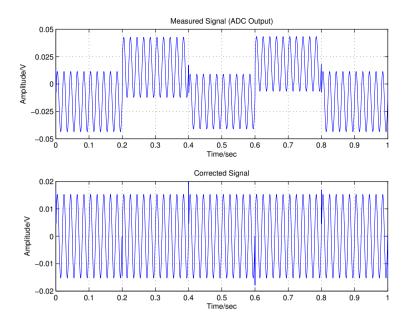

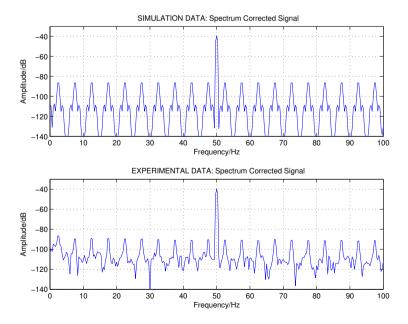

In simulation-based approaches, specifications are checked by executing multiple simulation runs. This process can be done manually or automated via scripts that define test benches and their expected behavior. Specifications are commonly given in terms of behavioral properties that can be verified dynamically during the execution of one or multiple simulation runs. Structural properties do not necessarily need to be verified via simulation. However, since they are mapped together with behavioral specifications, they can also be tested this way.