### Master's Thesis

# An in depth look at LU-decomposition on modern multi-socket hardware.

Tobias Maier

date of submission: 20. March 2015

Supervisor: Prof. Dr. Peter Sanders

Dipl.-Inform., Dipl.-Math. Jochen Speck

Institute of Theoretical Informatics, Algorithmics

Department of Informatics

Karlsruhe Institute of Technology

Hiermit versichere ich, dass ich diese Arbeit selbständig verfasst und keine anderen, als die angegebenen Quellen und Hilfsmittel benutzt, die wörtlich oder inhaltlich übernommenen Stellen als solche kenntlich gemacht und die Satzung des Karlsruher Instituts für Technologie zur Sicherung guter wissenschaftlicher Praxis in der jeweils gültigen Fassung beachtet habe.

Karlsruhe, den 20.03.2015

### Zusammenfassung

Moderne Hardware stellt neue Herausforderungen an Algorithmen. Um Rechnerarchitekturen mit mehreren Sockeln und komplexen Cachehierarchien gut auszulasten, müssen Algorithmen mit den Stärken und Schwächen der Hardware im Blick entworfen werden. Richtig eingesetzt kann moderne Hardware auch neue und interessante Optimierungsansätze bieten. In dieser Arbeit präsentieren wir einen neuen Ansatz zur Arbeitsverteilung, anhand einer LU-Zerlegung. Bei der Arbeitsverteilung betrachten wir Möglichkeiten gemeinsame Daten zwischen verschiedenen Teilaufgaben wiederzuverwenden. Sofern dies möglich ist werden die entsprechenden Teilaufgaben so auf Rechenkerne zugewiesen, dass sie gemeinsame Eingaben über den L3 Cache teilen können.

Das bestimmen der LU-Zerlegung einer Matrix ist eine der wichtigsten numerischen Aufgaben. Die LU-Zerlegung wird verwendet, um Matrizen zu invertieren, ihre Determinante zu bestimmen und um lineare Gleichungssysteme zu lösen. Der Algorithmus zur LU-Zerlegung ist außerdem repräsentativ für viele weitere numerische Berechnungen. Dies ist auch der Grund, weshalb er der Hauptbestandteil des berühmten LINPACK Benchmarks ist, welcher verwendet wird, um die stärksten Supercomputer für die TOP500 Liste zu bestimmen.

Es ist wichtig, die Laufzeit der LU-Zerlegung zu verbessern ohne die numerische Genauigkeit zu verschlechtern. Deshalb verwenden wir den selben numerischen Algorithmus wie die anerkannte PLASMA (Parallel Linear Algebra for Scalable Multi-core Architectures) Bibliothek. Durch unsere Anpassungen an die Arbeitsverteilung, die es uns ermöglichen Teilaufgaben mit gemeinsam genutzten Daten besser zu verteilen, erreichen wir eine Performanzsteigerung, zwischen 15% und 29%.

### Abstract

Modern hardware makes new demands on algorithms. To properly utilize multi-socket architectures with non-trivial cache hierarchies, algorithms have to be designed with the hardware's strengths, and weaknesses in mind. If properly addressed, modern hardware offers new, and interesting optimization possibilities. In this thesis we present a new scheduling approach, using the example of an LU-decomposition. Our scheduler considers data reuse opportunities between different subtasks, and schedules these subtasks in a way that lets them share common inputs through the L3 cache.

The LU-decomposition of matrices is one of the most important numerical algorithms. It is used for matrix inversion, to compute the determinant of a matrix, and to solve systems of linear equations. The algorithm for LU-decomposition is also representative for many other numerical computations. This is the reason, why it is part of the famous LINPACK benchmark, that is used to rank the most powerful supercomputers in the TOP500 list.

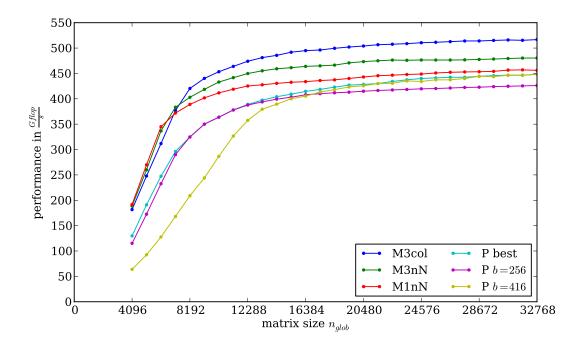

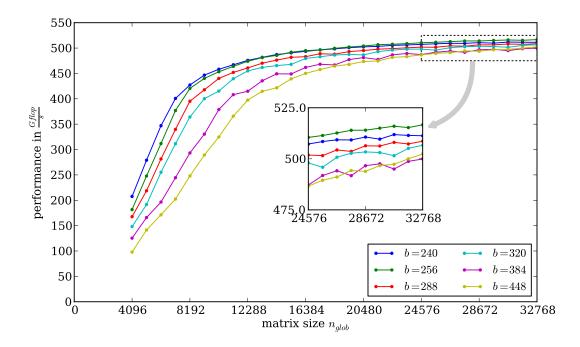

It is important, to improve the performance of the LU-decomposition, without decreasing its numerical accuracy. Therefore, we use the same numerical algorithm for the LU-decomposition as PLASMA (Parallel Linear Algebra for Scalable Multi-core Architectures), which is a current state of the art implementation. By adapting the scheduling scheme, to take better advantage of data sharing, we achieve performance increases between 15%, and 29%.

# Contents

| 1 | intro | Dauction                                          | 5       |  |  |  |  |

|---|-------|---------------------------------------------------|---------|--|--|--|--|

|   | 1.1   | Motivation                                        | (       |  |  |  |  |

|   | 1.2   | Related Work                                      | 1(      |  |  |  |  |

|   | 1.3   | Overview                                          | 12      |  |  |  |  |

| 2 | Prel  | Preliminaries                                     |         |  |  |  |  |

|   | 2.1   | Matrix Layout                                     | 12      |  |  |  |  |

|   | 2.2   | LU-Decomposition                                  | 13      |  |  |  |  |

|   | 2.3   | DAG-Scheduling                                    | 21      |  |  |  |  |

|   | 2.4   | Task-DAG of the LU-decomposition                  | $2^{2}$ |  |  |  |  |

|   | 2.5   | Modern Multi-Socket Machines                      | 24      |  |  |  |  |

| 3 | Our   | ·                                                 | 26      |  |  |  |  |

|   | 3.1   | Tile-Cache Model                                  | 26      |  |  |  |  |

|   | 3.2   | Data co-use Hypergraph                            | 27      |  |  |  |  |

|   | 3.3   | ±                                                 | 29      |  |  |  |  |

|   | 3.4   | Targeted NUMA-Scheduling                          | 3(      |  |  |  |  |

|   | 3.5   | Merging Cache and NUMA-Strategies                 | 31      |  |  |  |  |

| 4 | Ove   | rview of our Solution                             | 32      |  |  |  |  |

|   | 4.1   | Meta-Tasks                                        | 33      |  |  |  |  |

|   | 4.2   | Architecture of our Scheduler                     | 37      |  |  |  |  |

|   | 4.3   | Execution Order of Subtasks                       | 38      |  |  |  |  |

| 5 | lmp   | Implementation Details 4                          |         |  |  |  |  |

|   | 5.1   |                                                   | 4(      |  |  |  |  |

|   | 5.2   | Description of a Meta-Task's Lifetime             | 43      |  |  |  |  |

|   | 5.3   | V                                                 | 44      |  |  |  |  |

|   | 5.4   | Panel Algorithm                                   | 46      |  |  |  |  |

| 6 | Exp   | eriments                                          | 49      |  |  |  |  |

|   | 6.1   | Hardware and Environment                          | 49      |  |  |  |  |

|   | 6.2   | Tested Variations and Inputs                      | 5(      |  |  |  |  |

|   | 6.3   | Overview of our Test Results                      | 52      |  |  |  |  |

|   | 6.4   | Breakdown of our Improvements                     | 57      |  |  |  |  |

|   | 6.5   | Using the Tile-Cache Model to Analyze Experiments | 62      |  |  |  |  |

|   | 6.6   | Different Performance Metrics                     | 65      |  |  |  |  |

| 7 | Con   | clusion                                           | 67      |  |  |  |  |

|   | 7.1   | Overview                                          | 6       |  |  |  |  |

|   | 7.2   | Future Work                                       | 68      |  |  |  |  |

| Α | Den   | sity Maps for other Parametrizations              | 71      |  |  |  |  |

|   | A.1   |                                                   | 7       |  |  |  |  |

|   | A.2   | IvyBridge16                                       | 73      |  |  |  |  |

|   | A.3   | Haswell24                                         |         |  |  |  |  |

# List of Figures

| 1  | Different Data Layouts for Storing Matrices                 |

|----|-------------------------------------------------------------|

| 2  | Description of Partial Pivoting                             |

| 3  | Representation of $L$ , and $U$ in One Matrix               |

| 4  | LU-Decomposition via Gaussian Elimination                   |

| 5  | LU-Decomposition of a Tiled Matrix                          |

| 6  | Task Naming Example                                         |

| 7  | Spatial Representation of Tasks                             |

| 8  | Incoming Dependencies of each Class of Tasks                |

| 9  | Task-DAG of the Tile-Based LU-Decomposition                 |

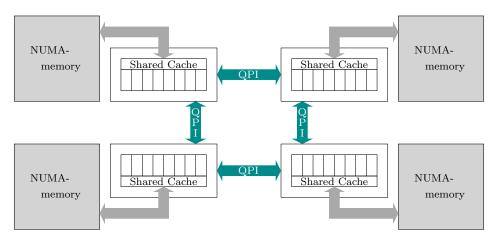

| 10 | Multi-Socket Machine Model                                  |

| 11 | Data co-use Hyperedges                                      |

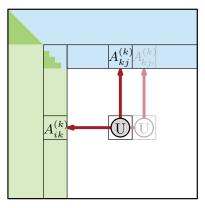

| 12 | U-tasks Sharing Input Tiles                                 |

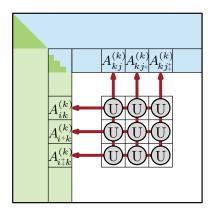

| 13 | Meta-Tiles and NUMA-Distribution of the Matrix              |

| 14 | Using Meta-Tiles to Create Meta-Tasks                       |

| 15 | Meta-Task-Graph                                             |

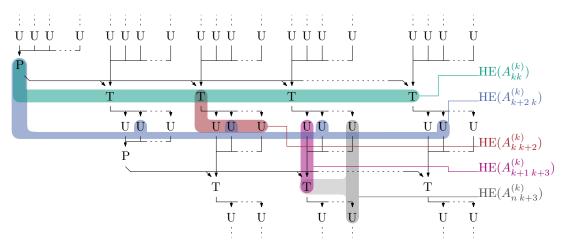

| 16 | Task-DAG with priorities                                    |

| 17 | Priorities within the Spatial Representation                |

| 18 | Pulling a new Task                                          |

| 19 | Task Execution Order with Tile-Cache Status                 |

| 20 | Thread Work Cycle                                           |

| 21 | Panel Algorithm Recursion                                   |

| 22 | Panel Algorithm Terminating Case                            |

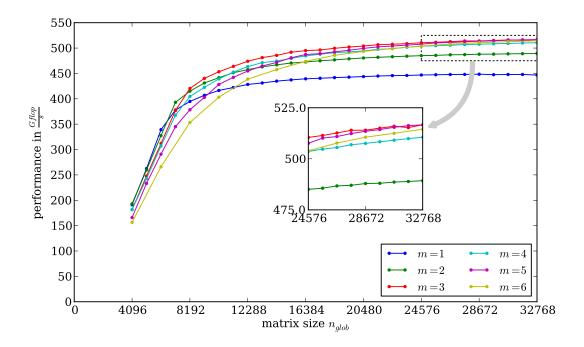

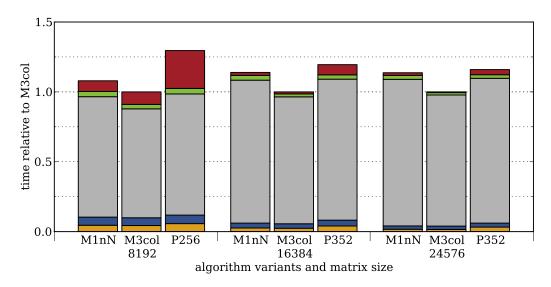

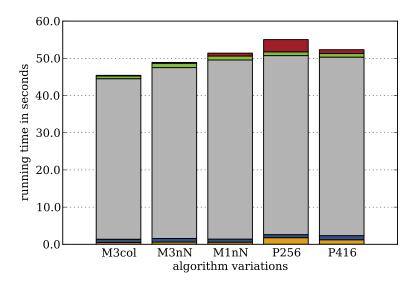

| 23 | Main Performance Plot                                       |

| 24 | Varying Tile Sizes                                          |

| 25 | Varying Meta-Tile Sizes                                     |

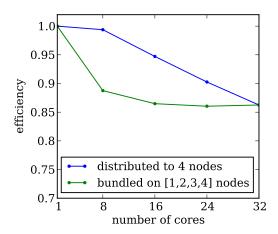

| 26 | Relative Efficiency                                         |

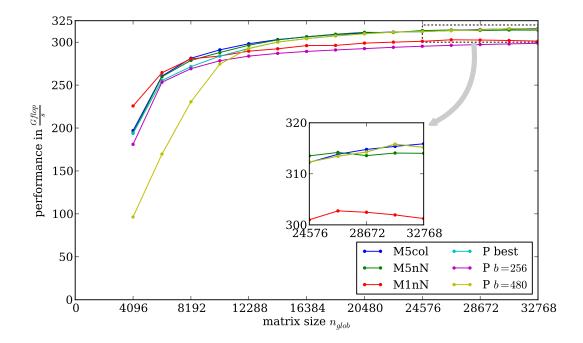

| 27 | Performance on IvyBridge16                                  |

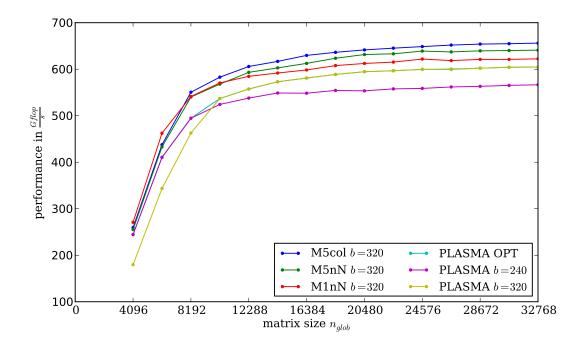

| 28 | Performance on Haswell24                                    |

| 29 | Relative Running Time Ratios                                |

| 30 | Running Time Ratio                                          |

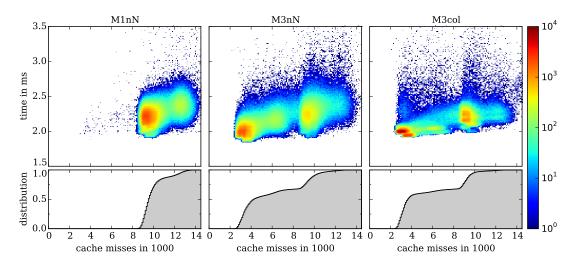

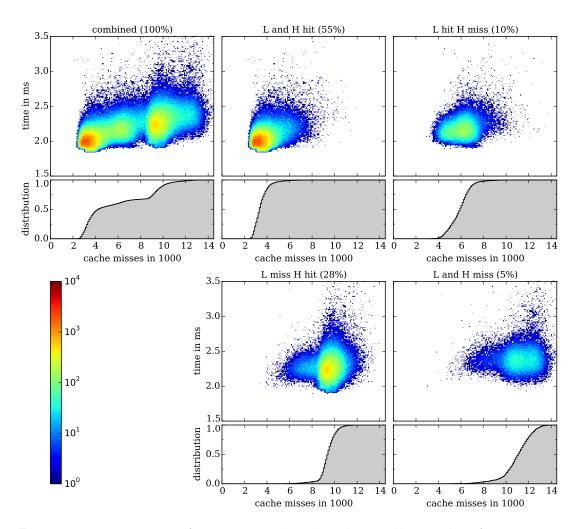

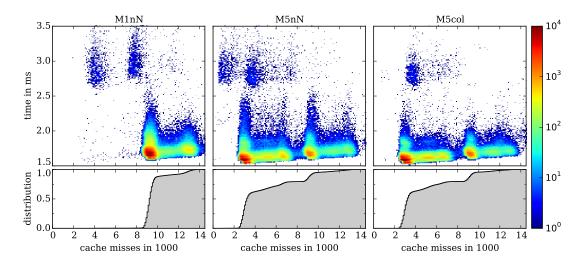

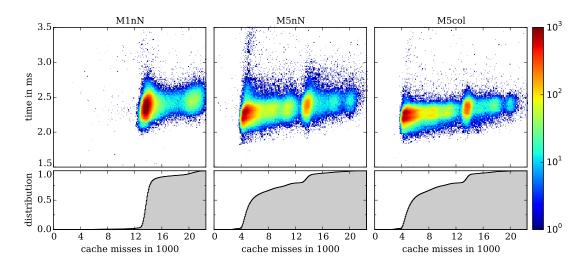

| 31 | U-Task Cache-Misses versus Execution Time as Density Map 61 |

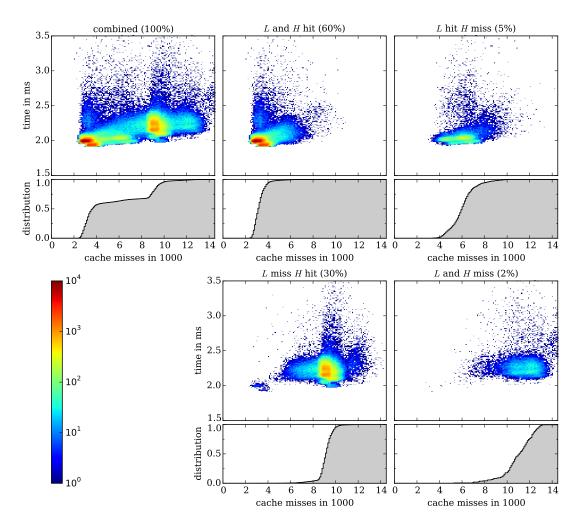

| 32 | U-Tasks Categorized with the Tile-Cache Model               |

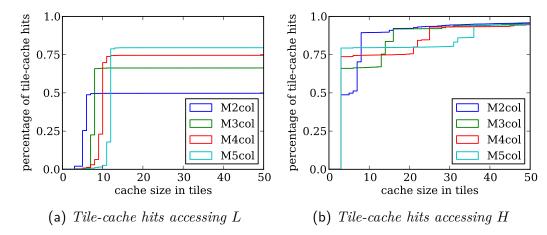

| 33 | Number of Tile-Cache Hits on Varying Tile-Cache Sizes 65    |

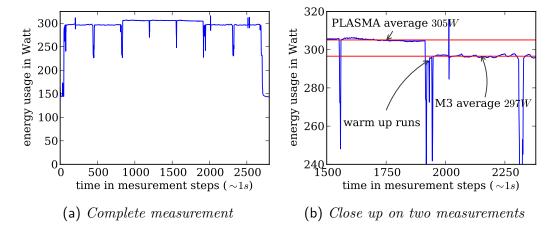

| 34 | Power Measurements                                          |

| 35 | Density Map for M3nN                                        |

| 36 | Density Map for M4col                                       |

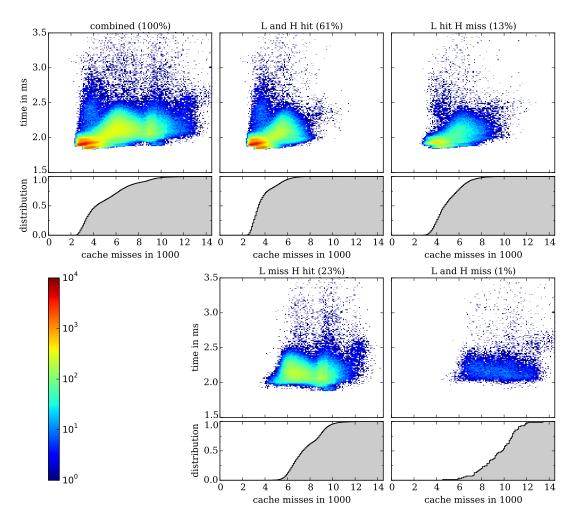

| 37 | Density Map for Different Variations on IvyBridge16         |

| 38 | Density Map for Different Variations on Haswell24           |

# **List of Tables**

| 1<br>2<br>3 | Tasks with corresponding Dependencies | 60 |

|-------------|---------------------------------------|----|

| List        | of Algorithms                         |    |

| 1           | Gaussian Elimination with Pivoting    | 16 |

| 2           | Tiled LU-Decomposition with Pivoting  | 18 |

| 3           | Panel Algorithm (parallel, recursive) | 47 |

## 1 Introduction

### 1.1 Motivation

Modern computers become faster, and faster. Today, there are two main factors that cause the increase in computing power, the increase in the number of cores per processor, and the fact that modern cores can perform more and more computations per cycle. Through Advanced Vector Extensions (AVX and AVX2), cores can compute up to eight floating point operations per cycle (16 with AVX2). At this rate of computation, memory access becomes an important bottleneck. Especially the latency of uncached memory accesses can be detrimental for high performance computations. This trend is further intensified on multi socket-hardware by non-uniform memory access (NUMA). A single memory access can slow down computations significantly. To counteract this problem, manufacturers use complex cache hierarchies. Modern processors have multiple levels of caches, some of which are shared between cores. It has become an important, and difficult task, for programmers to optimally use these complex cache architectures.

We chose the LU-decomposition problem to show that even problems which were long believed to be compute bound can profit from dedicated cache optimizations. LU-decomposition is interesting in this context for multiple reasons. (1) It is one of the most important numerical algorithms. LU-decompositions are the main tool to solve systems of linear equations, which is an important subtask for many applications. Systems of linear equations are used in many different areas, for example in engineering, physics, chemistry, computer science, and economics. The LU-decomposition can also be used to invert matrices, and to compute determinants. (2) The algorithm for LU-decomposition is characteristic for many dense linear algebra computations. If our methods succeed at accelerating the LU-decomposition, it is very likely that similar ideas can be used to accelerate other numerical linear algebra computations. (3) Because of its importance, there are already optimized implementations of LU-decomposition algorithms, like the one used in the PLASMA [11, 1] library (Parallel Linear Algebra for Scalable Multi-core Architectures). Therefore, even small improvements can be worthwhile, and show the novelty of our approach. Well optimized solutions can not only be used as competitors in our experiments, we can also use them as a starting point for our own solution. (4) LU-decomposition is the core of the famous LINPACK [12] benchmark. This benchmark is used to rank the worlds most powerful supercomputers in the TOP500 list [9].

For large numerical computations like the LU-decomposition it is common to generate parallelism by dividing the computation into small sequential subtasks. Oftentimes, many subtasks can be executed independently creating parallelism. This execution method is often called DAG-scheduling (Directed Acyclic Graph), because one can construct a graph with the subtasks as vertices, and the dependencies between subtasks as edges (see Section 2.3). In the context of numerical linear algebra computations, subtasks are often routines of highly optimized BLAS libraries (Basic Linear Algebra Subprograms). Therefore, it is more interesting to optimize the scheduling of subtasks than to optimize the subtasks themselves.

Even in modern, state of the art libraries like PLASMA very little care is taken to optimize data sharing between independent subtasks. Our approach is to take into account, when multiple subtasks access the same input data. We show, that scheduling subtasks with data sharing opportunities in mind, can greatly reduce the number of cache misses, and in turn improve the running time of the algorithm. To reduce the number of cache misses, we exploit the fact that modern processors use shared caches, which connect multiple cores of one processor. Scheduling tasks, that read the same memory regions, onto cores that share a common cache, can lead to significant speedups, because the common memory region will only be cached once.

In addition to our cache optimizations, we explicitly address, and optimize the NUMA-behavior of our implementation. By controlling the NUMA-distribution of the matrix, we are able to schedule tasks in a way, that minimizes the access to non-local memory. Tasks are scheduled on the node, that holds the majority of their input tiles. This accelerates data accesses even in case of cache faults.

What we propose, can be described as a data-computation-co-scheduling. Algorithms can only reach their optimal performance, if data flow, and work flow are considered together. To analyze the data flow and the usage of shared caches during the computation we develop a theoretical cache model. This cache model predicts the contents of shared caches during the computation depending on the order, and placement of executed subtasks. Using this theoretical model, we optimize the scheduling process that is used for our algorithm's subtasks.

An important aspect for all numerical linear algebra computations is accuracy. There are papers, that propose a trade-off between the speed, and the accuracy of a computation. We aim to achieve the best possible accuracy. Therefore, we use the same numerical algorithm that is used within PLASMA to compute the LU-decomposition. This algorithm was described by Dongarra et al. [10], and we use it as a starting point for our implementation. Most of our code is taken directly from PLASMA, and nearly all of our changes are part of the scheduling process. Notably, all of our numerical computations are exactly the same operations as in PLASMA, and therefore produce the same result with the same accuracy. An analysis of the algorithm's accuracy can be found in the original description [10].

Through our changes in the scheduling strategy, we achieve a performance improvement of 15% on big matrices (32768 rows/columns), and up to 29% on smaller matrices (8192 rows/columns).

### 1.2 Related Work

In principle, there are two fields of work, that we consider to be related to our findings. The first field is related through the common topic of LU-decomposition, while the second field is related through similar optimization methods.

As described in Section 1.1, LU-decompositions are a very important for common problems like solving systems of linear equations. For that reason, there are already many publications on the efficient computation of LU-decompositions. Over the last decades a lot of work has gone into the efficient parallelization of the LU-decomposition.

It has become clear, that LAPACK [2], which has been the standard library for linear algebra computations for a long time, has performance issues on modern

multi-core machines. The reason for this is, that LAPACK creates parallelism with a fork-join based approach. Instead of splitting the computation into small subtasks, that can be computed independently. LAPACK uses bigger subtasks, that are executed in parallel. This results in a significant synchronization overhead. Modern contributions to the area of dense matrix computations rely on the dynamic scheduling of fine grained, (mostly) sequential subtasks. Through this approach, the synchronization between different threads is reduced significantly.

As we already mentioned, the algorithm for LU-decomposition can be split into subtasks, that can be executed somewhat independently. There are different kinds of subtasks, within the LU-decomposition. The most complex type of subtasks is called a panel task (see Section 2.2.3). These panel tasks, are considered too big, to be executed sequentially. Therefore, it has been a focus of many papers to improve their execution. Buttari et al. [7], and Quintana-Ortí et al. [17] seek to improve the panel parallelization, by changing the pivoting scheme (see Section 2.2) such that the panel factorization can be split into smaller subtasks. They use what they call *incremental pivoting* to parallelize panel tasks more efficiently. This method is also employed by Kurzak et al. [14] in their work on dynamically scheduling dense linear algebra workloads.

But, changing the pivoting scheme comes at a cost in numerical stability. Dongarra et al. [10] show that the loss of precision over the more commonly used partial pivoting can be significant. Dongarra et al. also show a recursive variant of the panel algorithm – using partial pivoting – that can be parallelized. This algorithm combines high accuracy with high performance. It is the algorithm that is used within the PLASMA [11] library, and because we used PLASMA as a starting point, for our implementation, this is also the algorithm that we use for this thesis.

Related works, that use similar optimization, and scheduling techniques can be found in the field of DAG-scheduling. A lot of work has been done in the context of DAG-scheduling, as it is applicable to many problems. Kwok, and Ahmad [15] give a good overview of many aspects of DAG-scheduling.

Bosilca et al. [5] present a framework for high performance computations on distributed hardware, using DAG-scheduling. Their goal is to simplify development by offering a run-time system, which schedules tasks, and data-flows. This framework has already been used by Bosilica et al. [6] to implement some distributed numerical linear algebra functions, including a LU-decomposition.

One technique, that we are using for our optimizations is to manipulate the execution order of subtasks in a way that allows subtasks to reuse cached memory slots. Cheng et al. [8] show that parallel depth first traversal of the task-DAG can reduce the number of cache misses compared to more traditional work stealing methods. While this method shows large improvements for many problems, they did not reach significant improvement for the LU-decomposition.

Apart from application level scheduling, there are also more indirect methods, to improve the cache locality of parallel work loads. Tam et al. [18] use an approach, where they change the operating systems scheduling mechanisms. With this method, they try to optimize the allocation of threads to processors. This is done, by monitoring the memory accesses of applications with performance counters, and rescheduling threads appropriately.

### 1.3 Overview

We begin this thesis with the Preliminaries in Section 2. In this section, we describe the background of our work. It contains theoretical backgrounds, like the definition of an LU-decomposition, and a short introduction to DAG-scheduling as well as the high level description of the numerical algorithm that we use for our factorization.

In Section 3 we explain our optimization techniques from a theoretical point of view. There, we develop the theoretical cache model, that we base our cache optimizations on, and we describe the the cache, and NUMA-optimizations that we implemented.

After this theoretical view on our optimizations, we use Section 4 to detail the architecture of our scheduler, and the scheduling process. Here we also describe how we incorporate the ideas – developed in Section 3 – into the scheduling approach. In Section 5 we describe the detailed implementation, of our scheduling process. There, we describe details, that are important for the scheduling of tasks within our implementation. This includes the data structures of our scheduler, the sequence of a threads work cycle, and the process of readying, and scheduling subtasks.

To validate our findings, we conducted the performance experiments shown in Section 6. There we compare the performance of our implementation to that from the PLASMA library. We also conduct a detailed analysis, of our optimization techniques, and their influence on the running time of different subtasks of the algorithm. In the end, we summarize our findings in Section 7.

# 2 Preliminaries

This section contains some theoretical background for this thesis. We begin with Section 2.1 where we explain different matrix layouts. Then we use Section 2.2 to define the problem of LU-decomposition. Within this section, we also introduce the numerical algorithm that we use to compute the decomposition. It works by splitting the work of the computation into small subtasks. These subtasks can either be executed sequentially – one after the other – or they can be reordered. Many subtasks are independent from one another. They can be executed in parallel.

In Section 2.3 we describe DAG-scheduling which is a method to schedule independent subtasks. Subsequently, we use Section 2.4 to show the task structure of the algorithm for LU-decomposition when it is scheduled with a DAG-scheduler.

Then, we describe the architecture of modern computers in Section 2.5. There, we describe the hardware properties that we exploit to achieve better running times.

# 2.1 Matrix Layout

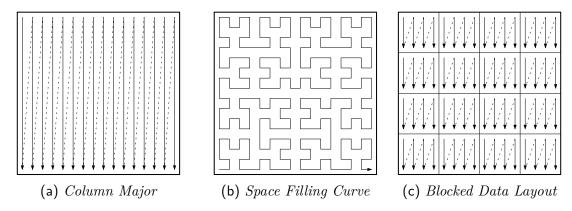

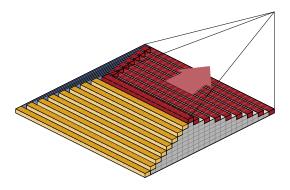

There are multiple ways to efficiently store matrices. Classically matrices are stored in the column-major format. This means that all elements of the matrix are stored in one consecutive piece of memory, in a column by column ordering (see Figure 1a). This data layout is very popular, because it is the native format

used in Fortran, and therefore LAPACK [2], which is a widely-used linear algebra interface written in Fortran.

There are other data layouts which are designed for better data locality. Such layouts have proven effective especially for matrix multiplication. Examples for this are hierarchical storage options and layouts that store matrices along space-filling curves [3, 13] (see Figure 1b). Layouts of this kind can often lead to *cache oblivious* algorithms – algorithms that effectively use caches without being tuned to specific cache sizes.

We are using a blocked data layout [7]. This means, that the matrix is stored in square blocks, which we call tiles. Each tile is stored in a column major format (see Figure 1c). This layout is used in modern linear algebra software like PLASMA [11]. It improves data locality, but submatrices are still stored in the column major format. This enables us to use common BLAS libraries like Intel's MKL (Math Kernel Library) for subtasks of our computation.

In this thesis we are handling a lot of tiled matrices, therefore we want to specify some naming conventions.

**Definition 2.1** (Matrix Layout). All matrices used in this paper are square matrices of size  $n_{glob} \times n_{glob}$  (unless specified otherwise). A tiled matrix is a matrix that is subdivided into  $n \times n$  tiles of size  $b \times b$ .

$$n = \left\lceil \frac{n_{glob}}{b} \right\rceil$$

If  $n_{glob} \neq n \cdot b$  then there are offsets in the lowest tile-row (rightmost tile-column).

We call the tile in matrix A at position (i, j)  $A_{ij}$ . The top left tile is  $A_{11}$ , and the bottom right tile is  $A_{nn}$ . We also use  $A_{i...kj}$  as a shorthand, for the tiles  $A_{ij}$ ,  $A_{i+1j}$ , ...,  $A_{kj}$  (part of a column), and  $A_{ij...k}$  for  $A_{ij}$ ,  $A_{ij+1}$ , ...,  $A_{ik}$  (part of a row).

As previously mentioned, this data layout combines good data locality with the ability to use existing libraries. It can also facilitate the parallelization of matrix algorithms. An algorithm that operates on a matrix can often be split into different subtasks that only work on certain tiles of the matrix. Two subtasks that work on different parts of the same matrix can usually be executed in parallel. This facilitates parallel execution without unnecessary synchronizations (or data locking).

# 2.2 LU-Decomposition

The LU-decomposition is a factorization of a matrix into a *lower triangular* matrix (zeros above the diagonal) and an upper triangular matrix (zeros below the diagonal). These two matrices can in turn be used to solve linear systems of equations or to invert the original matrix.

There are different varieties of LU-decompositions. Before we describe the version that is commonly used (also used for this thesis), we begin by defining the most basic variation of LU-decomposition.

Figure 1: Different data layouts for storing matrices.

### Strict LU-Decomposition

**Definition 2.2** (Strict LU-Decomposition). The matrix A is said to have an LU-decomposition, if there exists a factorization  $A = L \cdot U$  where:

- L is a lower triangular matrix (only zeros above the diagonal) with ones on the diagonal.

- U is an upper triangular matrix (only zeros below the diagonal).

If there exists such a decomposition for a matrix A then it is unique. This is forced through the constraint that L must have ones on its diagonal.

There are two problems with this general definition of LU-decompositions. The first problem is that an LU-decomposition of this form is not possible for some matrices. Especially singular matrices (not invertible) and permutation matrices (exactly one "1" per row, and column) often do not have an LU-decomposition. The second problem is the numerical stability of such a decomposition. This kind of decomposition is only guaranteed to be numerically stable in certain special cases, for example for diagonally dominant matrices (diagonal elements are greater than the sum of other elements in the same row).

LU-Decomposition with Row Pivoting (partial pivoting) To reduce the problems of strict LU-decompositions, it is very common to allow row pivoting for the decomposition. Row pivoting means that rows of the original matrix A are permuted during the decomposition. This can improve the numerical stability because it can prevent that large numbers are divided by very small numbers. Rows are usually exchanged according to a pivoting scheme. We use the partial pivoting scheme, which is the most common pivoting scheme, that in practice leads to good numerical stability.

**Definition 2.3** (LU-Decomposition with Row Pivoting). An LU-decomposition of A with row pivoting is a decomposition where  $P \cdot A = L \cdot U$  and:

- $L \cdot U$  is a strict LU-decomposition of  $P \cdot A$  (as described in Definition 2.2).

- P is a permutation matrix  $(P \cdot A = A \text{ with permuted rows})$ .

If we allow row pivoting, then every squared matrix has an LU-decomposition. Throughout this thesis LU-decomposition will always mean an LU-decomposition with partial pivoting (unless specifically mentioned otherwise).

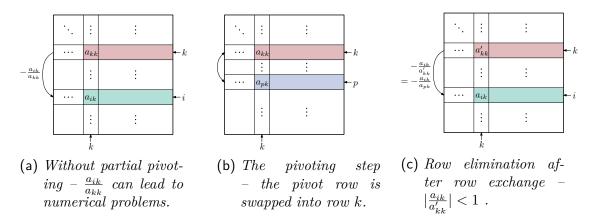

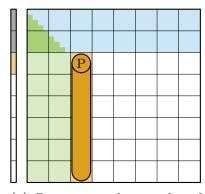

Figure 2: Description of partial pivoting. The elimination of values below the diagonal with, and without partial pivoting.

**Partial Pivoting** During the algorithm used for the decomposition, we eliminate values in column k (below the diagonal) by subtracting a multiple of row k (see Figure 2a). If the entry  $a_{kk}$  is zero, this leads to a division by zero. This is the reason why not every matrix has a strict LU-decomposition. Even if  $|a_{kk}| > 0$ , there can be numerical problems if  $a_{kk}$  is small compared to other entries in column k. These numerical problems can reduce the overall accuracy of the computation significantly.

Partial pivoting reduces these inaccuracies by choosing a pivot row and swapping that row into row k (see Figure 2b). The pivot row is chosen as the row that has the highest absolute value in column k. This way  $\left|\frac{a_{ik}}{a_{kk}}\right| \leq 1$  can be guaranteed for every "elimination factor"  $\frac{a_{ik}}{a_{kk}}$  (see Figure 2c). In this thesis we do not go into further detail on the numerical accuracy of our

In this thesis we do not go into further detail on the numerical accuracy of our LU-decomposition. The numerical accuracy of our LU-decomposition should be equal to the accuracy of any similar implementation using partial pivoting. Since our implementation is closely related to the implementation used in PLASMA, we expect our accuracy to be the same. Results on the accuracy of PLASMA's LU-decomposition can be found in [10].

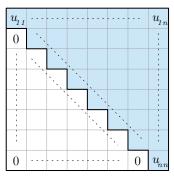

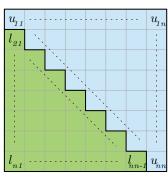

### 2.2.1 Representation of the LU-Decomposition in one Matrix

Memory is a concern when factoring big matrices. Therefore, it is preferable not to allocate multiple matrices at once. Especially, if two of these matrices will be triangular (one half of all elements are zero). Luckily, L and U can be stored together in one matrix. This is possible, because L is a lower triangular matrix and U is an upper triangular matrix. The only positions where non-zero elements of L and U collide are on the diagonal, but all diagonal entries of L are one. Thus, both triangular matrices can be stored in one matrix, in which the zero entries and L's diagonal are stored implicitly (see Figure 3).

The LU-decomposition can even be computed in place without allocating any new matrices. Both algorithms that we present throughout this section are examples for in-place LU-decompositions (see Section 2.2.2, and Section 2.2.3).

Only the permutations have to be stored externally. However, storing a permutation matrix can be done a lot less memory consuming than a regular matrix. The permutation matrix is used to create a row permutation of the original ma-

- (a) lower triangular (with ones on diagonal)

- (b) upper triangular

- (c) combined (lower diagonal stored implicitly)

Figure 3: Representation of L, and U in one matrix.

### **Algorithm 1:** Gaussian Elimination with Pivoting

0

```

Input: matrix A \in \mathbb{R}^{n_{glob} \times n_{glob}}

1 for 1 \leq k \leq n_{glob} do

// find pivot row with partial pivoting

q_k \leftarrow \arg\max_{k \le i \le n} |a_{ik}|

exchange_rows(k, q_k)

// Figure 4a

\begin{array}{l} \text{for } k+1 \leq i \leq n_{glob} \text{ do} \\ \bigsqcup a_{ik} \ \leftarrow \frac{a_{ik}}{a_{kk}} \end{array}

// Figure 4b

4

// generates entry of L

5

for k+1 \leq j \leq n_{glob} do

// Figure 4c

6

\begin{array}{l} \text{for } k+1 \leq i \leq n_{glob} \text{ do} \\ \bigsqcup a_{ij} \ \leftarrow a_{ij} - a_{ik} \cdot a_{kj} \end{array}

7

// update matrix with row operations

```

Output: matrix A containing L and U, and the pivoting vector  $Q = (q_1, \ldots, q_n)$

trix A. So instead of saving all permutations in the form of a matrix, we are storing permutations in the form of an integer vector. Every value  $q_i$  of this vector denotes that row i was exchanged with row  $q_i$  (compare Algorithm 1 line 2, and 3). Saved like this, the permutation matrix only uses memory space linear in the matrix size  $n_{glob}$ .

### 2.2.2 Gaussian Elimination

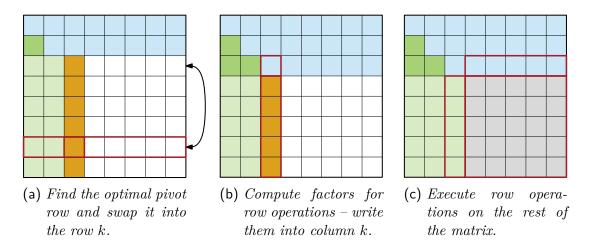

Originally the LU-decomposition was computed via the Gaussian Elimination algorithm that can be seen in Algorithm 1 and Figure 4. This is the same algorithm that is commonly used when manually solving linear systems of equations. The matrix is triangulated – from top left to bottom right – by eliminating entries under the diagonal.

For this algorithm, we assume that we work on a matrix with tile size b = 1. So  $n_{glob} = n$  and  $A_{ij}$  is the element in position (i, j) of A. As it is customary to use lower case letters for individual matrix elements, we use lower case letters while b = 1.

There is one global loop (Algorithm 1 line 1 to 8) over k. Each global iteration k works in three steps:

Figure 4: One iteration of the LU-decomposition via Gaussian Elimination

- 1. (lines 2-3) We find a pivot row. This is the row with which values under the diagonal are eliminated. Then, the pivot row is exchanged with row k. We call this a row exchange (see Figure 4a).

- 2. (lines 4-5) Afterwards, we compute all factors which are later used to eliminate values under the diagonal. These factors make up the k-th column of L (see Figure 4b). Hence, L can be seen as a history of all used elimination factors.

- 3. (lines 6-8) At last, we subtract multiples of the right side of the pivot row (row k right of column k) from each lower row. The corresponding factors for each row were computed in step two and are stored in the k-th column of L. We call these subtractions row operations (see Figure 4c).

Each iteration of this loop finalizes row k of matrix U. It also computes all values that are in column k of matrix L. The values of column k might still be reordered through row exchanges of future iterations. All values above row k are final.

In step one the pivot row is chosen according to the pivoting scheme. Partial pivoting is the most commonly used pivoting scheme. It is a method that in practice achieves good numerical stability while still being fast, and easy to implement. Partial pivoting means that we always use the row with the biggest absolute value in column k as the pivot row. Therefore,  $a_{kk}$  is be the biggest value in column k. This makes the computation of  $a_{ik}/a_{kk}$  more numerically stable.

The problem with this algorithm is that it heavily uses matrix-vector products (level 2 BLAS operations), these cannot fully take advantage of modern hardware. Especially the matrix update (see Figure 4c), which is by far the biggest portion of the algorithm's work, could be executed more efficiently if it consisted of matrix-matrix products (level 3 BLAS operations). Therefore, modern libraries (for example PLASMA) use a slightly different version of this algorithm.

### Algorithm 2: Tiled LU-Decomposition with Pivoting

```

Input: a tiled matrix A \in (\mathbb{R}^{b \times b})^{n \times n}

1 for 1 \leq k \leq n do

2 A_{k...n\,k}, Q_k \leftarrow \text{PANEL}(A_{k...n\,k}) // finds pivots + column updates

3 for k+1 \leq j \leq n do

4 A_{k(..n)\,j} \leftarrow \text{TOP}(A_{k(..n)\,j}, A_{kk}, Q_k) // exchange rows + computation

5 for k+1 \leq i \leq n do // update the rest of the matrix

6 A_{ij} \leftarrow \text{SUBMATRIX\_UPDATE}(A_{ij}, A_{ik}, A_{kj})

7 for 1 \leq i < k do // exchange rows left of the panel

8 A_{k...n\,i} \leftarrow \text{BEHIND\_PANEL\_PERMUTATION}(A_{k...n\,i}, Q_k)

Output: matrix A that now contains L and U, and the pivoting vector Q = (Q_1, \dots, Q_n)

```

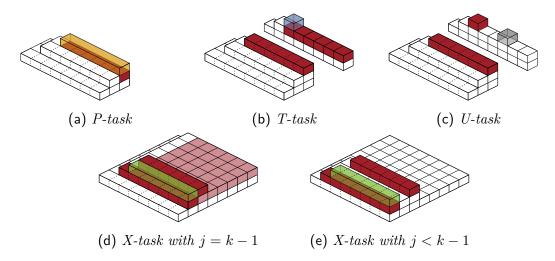

### 2.2.3 Algorithm for Tiled Matrix Layouts

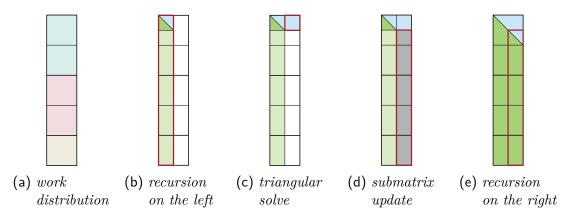

The LU-decomposition algorithm for tiled matrices, that can be seen in Algorithm 2 and Figure 5, effectively recreates Gaussian Elimination on a matrix of tiles. The main difference is that it combines row exchanges and row operations from multiple columns (one tile-column) before applying them to the rest of the matrix. For each global iteration over k (lines 1-8 in Algorithm 2), we call tile-column k the panel of iteration k ( $A_{k..nk}$ ; orange in Figure 5a). The panel is comparable to column k of iteration k during the Gaussian algorithm. At the beginning of each iteration, all permutations and elimination factors within the panel are computed. Afterwards, the rest of the matrix is updated with all row exchanges and row operations made within the panel. The algorithm splits its work load into four major classes of subtasks:

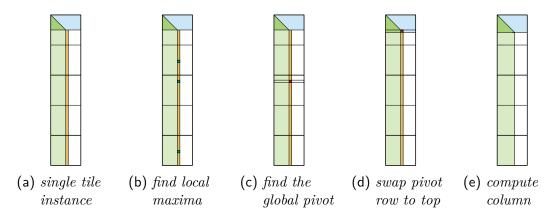

**PANEL-tasks** (or P-tasks): In each global iteration, there is exactly one P-task. It computes the LU-decomposition of the panel and the corresponding subsection of the permutation vector Q (see Figure 5a). In Section 5.4 we go into further detail about the implementation of the panel algorithm that we use. At this point it is only important to know that the panel algorithm is parallelized which means that there are multiple cores that work on each P-task cooperatively.

The P-task can be implemented very similar to the Gaussian Elimination algorithm from Section 2.2.2. The P-task finds the pivot row for each column within its tile-column and computes the corresponding tile-column of matrix L. A single P-task has an asymptotic complexity of  $\mathcal{O}((n-k+1) \cdot b^3)$  flops. All n P-tasks combined have an asymptotic complexity of

$$complexity(P-tasks) = \mathcal{O}(n^2 \cdot b^3)$$

.

**TOP**-tasks (or T-tasks): They are the tasks that execute row exchanges on the right side of the panel. In each global iteration, there is one T-task per tile-column on the right side of the panel. They also compute the effects of row operations within the topmost tile-row (see Figure 5b). The row exchanges execute  $\mathcal{O}(b^2)$  reads and writes (no flops), while the row operations have an

(a) Decompose the panel and compute the corresponding part of Q.

(c) Update the rest of the matrix with all row operations made in the panel.

(b) Execute row exchanges and finalize the topmost tile-row.

(d) Execute the row exchanges on the left side of the panel.

Figure 5: One iteration of the LU-decomposition on a tiled matrix  $(k = 3 \text{ on a } matrix \text{ with } 8 \times 8 \text{ tiles}).$

asymptotic complexity of  $\mathcal{O}(b^3)$  flops. All T-tasks combined have a complexity of

$$complexity(T-tasks) = \frac{n \cdot (n-1)}{2} \cdot \mathcal{O}(b^3) = \mathcal{O}(n^2 \cdot b^3).$$

**SUBMATRIX\_UPDATE-tasks** (or *U-tasks*): These are the tasks that update most of the matrix. In every iteration, there is one U-task for each tile that has to be updated (see Figure 5c). Every U-task operates on one tile. It computes the effects of row operations – made within the panel – on its tile. This is done with a simple matrix multiplication. The U-task operating on tile  $A_{ij}$  during iteration k computes  $A_{ij} = A_{ij} - A_{ik} \cdot A_{kj}$ . This is very similar to the matrix update of the Gaussian Elimination seen in Algorithm 1 (line 6-8) and Figure 4c. The difference is that matrix-matrix products are significantly better to use a processor at full capacity than vector-matrix products. One U-task consists of  $2b^3$  flops. All U-tasks together have a complexity of

$$complexity(U-tasks) = \frac{n \cdot (n-1) \cdot (2n-1)}{6} \cdot 2b^3$$

.

**BEHIND\_PANEL\_PERMUTATION**-tasks (or *X-tasks*): An X-task executes row exchanges made within the panel on a tile-column left of the panel (see Figure 5d). In each iteration, there are as many X-tasks as there are tile-columns

left of the panel. X-tasks fulfill a special role in the algorithm. They do not compute any flops. Because of this, it is beneficial to omit X-tasks from certain considerations or images. Instead of computing any values X-tasks exchange values from the topmost matrix tile with values from the corresponding pivot rows. Therefore, they cause  $\mathcal{O}(b^2)$  reads/writes without having any computational complexity.

**In Conclusion** U-tasks are the only class of tasks which has a cubic complexity (cubic in the matrix size  $n_{glob}$ ). They dominate the running time of the algorithm. Therefore, we will be paying a lot of attention to optimizing the execution of U-tasks. The LU-decomposition with this algorithm takes

$$\begin{aligned} complexity(tiled\ algorithm) &= \frac{n \cdot (n-1) \cdot (2n-1)}{6} \cdot 2b^3 + \mathcal{O}\Big(n^2b^3\Big) \\ &= \frac{2}{3}n^3b^3 - \frac{1}{2}n^2b^3 + \frac{1}{6}nb^3 + \mathcal{O}\Big(n^2b^3\Big) \ . \end{aligned}$$

The theoretical flop count taken from LAPACK working note 41 [4] (with m = n for square matrices) is

$$complexity(LU\text{-}decomposition) = \frac{2}{3}n_{glob}^3 - \frac{1}{2}n_{glob}^2 + \frac{5}{6}n_{glob} \ .$$

This is also the flop count that we use to compute the performance (Gflop/s) of our algorithm in Section 6.

### 2.2.4 Spatial View on the Tiled LU-decomposition

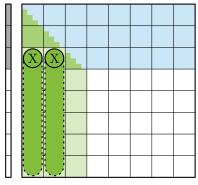

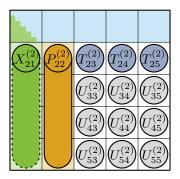

In this section, we want to introduce a geometrical view on all subtasks of the numerical algorithm for tiled matrices. We identify each subtask with one tile that it operates on (even if it changes multiple tiles). This allows us to spatially arrange subtasks in a grid (see Figure 6). This grid structure simplifies the formulation of dependencies between subtasks.

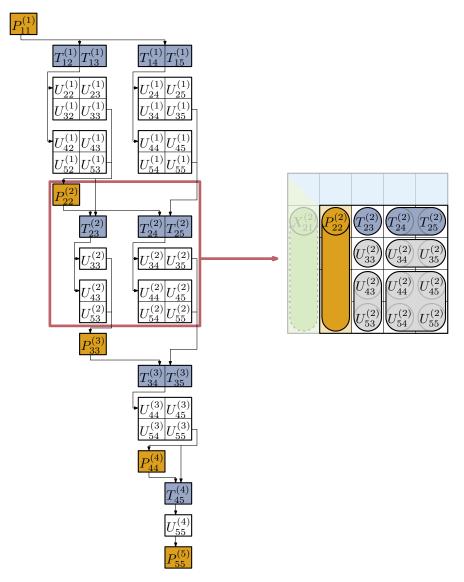

At first we introduce new version numbers for all tiles of the matrix. We call the tile at position (i,j) after iteration k of the algorithm  $A_{ij}^{(k)}$ . With each iteration we finish the k-th tile row. This means that  $A_{ij}^{(i)}$  is the final version of tile  $A_{ij}$  ( $A_{ij}^{(i)} = A_{ij}^{(n)}$ ) because in future iterations there are no tasks that change  $A_{ij}$ .

With the definition of version numbers, we can introduce a new naming system to easily differentiate all subtasks of the algorithm. Each task is indexed with the global iteration that it belongs to and with the position of one matrix tile that it works on (See Figure 6):

- $P_{kk}^{(k)}$  is the P-task of iteration k.

- $T_{kj}^{(k)}$  is the T-task that operates on column j during iteration k.

- $U_{ij}^{(k)}$  is the U-task that operates on the tile  $A_{ij}$  during iteration k.

- $X_{kj}^{(k)}$  is the X-task that operates on column j during iteration k.

Figure 6: Task naming example (k = 2 on  $5 \times 5$  matrix)

Figure 7: Spatial representation of subtasks from three iterations of the tiled LU-algorithm (without X-tasks).

If we start working on a square matrix then the part of the matrix that is actively worked on (through P-, T-, and U-tasks) remains a square at the bottom right corner of the matrix (each iteration finishes one tile-row and one tile-column). We can arrange all tasks of one iteration according to the matrix tiles that the task operates on (see task indices), an example of this can be seen in Figure 6. Additionally, we can stack the tasks of consecutive iterations on top of each other – creating a time axis. This generates a pyramid structure of tasks, part of which can be seen in Figure 7.

In this structure, the task occupying position (i, j, k) is responsible for the computation of tile  $A_{ij}^{(k)}$ . This view on the algorithm's subtasks is beneficial because we can use it to describe relations between subtasks more easily.

# 2.3 DAG-Scheduling

DAG-Scheduling is a very important computation model to expose opportunities for parallelization within an algorithm. An algorithm is divided into a set V of subtasks  $(t_1...t_{|V|})$ . Where each subtask has to be executed sequentially.

Some of these subtasks might be independent from one another. Hence, they may be scheduled simultaneously. Other tasks might not be independent, for example if task  $t_b$  uses task  $t_a$ 's result then  $t_b$  cannot be scheduled until  $t_a$  is finished. We call this a *precedence constraint* or we say  $t_b$  depends on  $t_a$ . Such precedence constraints can be denoted by tuples  $(t_a, t_b)$ . We say E is the set of all precedence constraints which are implicitly given by the algorithm  $(E \subset V \times V)$ .

We can visualize all tasks and dependencies as a directed graph G = (V, E). The vertices of the graph are the subtasks of the algorithm, and the edges of the graph are the dependencies between subtasks. In the example above  $t_b$  depends on  $t_a$ . Therefore, the graph contains an edge from vertex  $t_a$  to vertex  $t_b$ . Every valid algorithm that is parallelized through subtasks implies such a graph. There cannot be any directed cycles in this graph because a cycle would imply a task that transitively depends on itself (This task could never be ready for execution). Thus, we call this graph the task-DAG (Directed Acyclic Graph) of an algorithm. There are four basic states a task can have during the computation:

- (not ready) A task is not ready as long as it depends on at least one unfinished task.

- (ready) Ready tasks are ready to be scheduled and executed. A task is ready if it has no dependency to an unfinished task and it is not already working or finished.

- (working) This means that the task is currently being executed. Each task t has a running time w(t).

- (finished) Finished tasks are tasks that have already been executed.

In the beginning of an algorithm's execution, there are usually only a few ready tasks and many more tasks that are not ready. Once a ready task is finished other dependent tasks may become ready. These ready tasks are also scheduled until every task is finished. An execution of the algorithm can be compared to a traversal of the task-DAG. The target of DAG-scheduling is usually to find a schedule that minimizes the time needed for the computation.

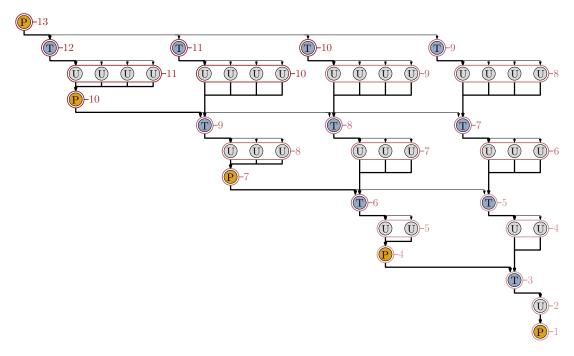

# 2.4 Task-DAG of the LU-decomposition

The algorithm from Section 2.2.3 is already separated in small subtasks which we indexed in Section 2.2.4. Now, we analyze the precedence constraints between these subtasks to see which of them can be executed in parallel. A summary of all precedence constraints can be seen in Table 1 and a visualization can be seen in Figure 8:

**P-task:** (see Figure 8a) During each iteration  $P_{kk}^{(k)}$  works on the panel $(A_{k...n\,k})$ . It reads tiles  $A_{k...n\,k}^{(k-1)}$  and transforms them to version  $A_{k...n\,k}^{(k)}$ . The tiles  $A_{k...n\,k}^{(k-1)}$  are usually written by the tasks  $U_{k...n\,k}^{(k-1)}$  (except for k=1). Therefore,  $P_{kk}^{(k)}$  cannot be started until  $U_{k...n\,k}^{(k-1)}$  are finished.  $P_{kk}^{(k)}$  also generates the k-th part of the pivoting vector  $(Q_k)$ .

**T-task:** (see Figure 8b) The T-task  $T_{kj}^{(k)}$  performs row exchanges on column j. Therefore, it reads tiles  $A_{k...nj}^{(k-1)}$  and the k-th part of the pivot vector  $Q_k$ . It changes the tiles  $A_{k...nj}^{(k-1)}$  into intermediate tile versions  $\widetilde{A}_{k...nj}^{(k-1)}$  where permutations are already performed but row operations are not. Row operations of all previous iterations have to be completed to do this, therefore,  $T_{kj}^{(k)}$  depends on the tasks  $U_{k...nj}^{(k-1)}$ . After all row permutations,  $T_{kj}^{(k)}$  performs the row operations on all rows of the uppermost tile  $\widetilde{A}_{kj}^{(k-1)}$  to create tile  $A_{kj}^{(k)}$ . Hence,  $T_{kj}^{(k)}$  needs tile  $A_{kk}^{(k)}$  which

| Task t         | Inputs $IN(t)$                                                | Outputs $OUT(t)$                                                  |

|----------------|---------------------------------------------------------------|-------------------------------------------------------------------|

|                | Dependencies In                                               | Dependencies Out                                                  |

| $P_{kk}^{(k)}$ | $A_{k\dots n \ k}^{(k-1)}$                                    | $A_{k\dots n\ k}^{(k)}, Q_k$                                      |

|                | $U_{k\dots nk}^{(k-1)}$                                       |                                                                   |

| $T_{kj}^{(k)}$ | $A_{knj}^{(k-1)}, A_{kk}^{(k)}, Q_k$                          | $\widetilde{A}_{kj}^{(k)}, \widetilde{A}_{k+1\dots n}^{(k-1)}$    |

|                | $U_{knj}^{(k-1)}, P_{kk}^{(k)}$                               | $U_{k+1\dots nj}^{(k)}$                                           |

| $U_{ij}^{(k)}$ | $\widetilde{A}_{ij}^{(k-1)}, A_{ik}^{(k)}, A_{kj}^{(k)}$      | $A_{ij}^{(k)}$                                                    |

|                | $P_{kk}^{(k)}, T_{kj}^{(k)}$                                  | $[X_{k+1}^{(k+1)}], P_{k+1}^{(k+1)} \text{ or } T_{k+1}^{(k+1)}]$ |

| $X_{kj}^{(k)}$ | $A_{k\dots n\ j}^{(k-1)}, Q_k$                                | $A_{k\dots n j}^{(k)}$                                            |

|                | $P_{kk}^{(k)}, X_{k-1j}^{(k-1)} \text{ or } [U_{**}^{(k-1)}]$ | $X_{k+1j}^{(k+1)}$                                                |

Table 1: Tasks with corresponding input and output tiles, and the resulting dependencies. Square brackets [\*] denote read before write dependencies.

Figure 8: Incoming dependencies of each class of tasks. The examined task is drawn transparent and highlighted in its color (see Figure 5). Direct dependencies are highlighted in red (read before write in brighter red). All white tasks are indirect dependencies.

at this point was last written by  $P_{kk}^{(k)}$  (as was  $Q_k$  which was needed for the row permutations). Therefore,  $T_{kj}^{(k)}$  is also dependent on  $P_{kk}^{(k)}$ .

**U-task:** (see Figure 8c) The U-task  $U_{ij}^{(k)}$  performs all row operations of the k-th iteration on tile  $\tilde{A}_{ij}^{(k-1)}$ . Therefore, it reads the tiles  $\tilde{A}_{ij}^{(k-1)}$ ,  $A_{ik}^{(k)}$  (for the elimination factors) and  $A_{kj}^{(k)}$  (for the pivot row elements). This makes  $U_{ij}^{(k)}$  dependent on  $T_{kj}^{(k)}$  (who writes  $\tilde{A}_{ij}^{(k-1)}$  and  $A_{kj}^{(k)}$ ), and on  $P_{kk}^{(k)}$  (who writes  $A_{ik}^{(k)}$ ). The dependence on  $P_{kk}^{(k)}$  can be ignored, since  $U_{ij}^{(k)}$  is already dependent on  $T_{kj}^{(k)}$  which in turn is also dependent on  $P_{kk}^{(k)}$ .

**X-task:** (see Figure 8d and 8e) The X-task  $X_{kj}^{(k)}$  performs row interchanges on column j (left of the panel). Thus, it reads the permutation vector  $Q_k$  which makes it dependent on  $P_{kk}^{(k)}$ . It also reads the tiles  $A_{k...nj}^{(k-1)}$  and changes them to

$X_{53}^{(5)}$

$X_{52}^{(5)}$

$X_{54}^{(5)}$

Figure 9: task-DAG of the tile based algorithm on a  $5 \times 5$  tile matrix.

version k. These tiles were previously written by either task  $P_{k-1 \ k-1}^{(k-1)}$  (if j=k-1 this means  $A_{k...n \ j}^{(k-1)}$  is the previous panel) or task  $X_{k-1 \ j}^{(k-1)}$  (if j < k-1).

If  $A_{k...nj}^{(k-1)}$  was written by  $P_{k-1j}^{(k-1)}$ , then it was part of the panel from the last iteration (k-1) which means many tasks of that iteration read its contents. Therefore, we have to make sure that each of those tasks is finished before  $X_{kj}^{(k)}$  can change the panel. Thus,  $X_{kj}^{(k)}$  is dependent on each U-task of the previous iteration (k-1). We call this kind of precedence constraint a write after read constraint.

Write after read constraints can generally be circumvented by duplicating the affected memory. This is not important here since X-tasks only make up an insignificant amount of the algorithm's running time. Hence, it is no problem to wait for all dependencies and postpone X-tasks until later in the computation. This is the only instance of a write after read precedence constraint within the algorithm.

With the help of these precedence constraints we can build the task-DAG (see Figure 9). One can see that there is a lot of structure to this graph. This makes it easy to pre-compute the incoming and outgoing dependencies when the subtasks are created.

### 2.5 Modern Multi-Socket Machines

Modern processors become increasingly complicated. They get more cores, deeper cache hierarchies, and they have more advanced arithmetic units. Most of our experiments were done on a Sandy Bridge system, where each core can compute up to four double precision multiplications and four double precision additions per cycle (AVX). Newer machines, that support AVX2 instructions, can even com-

Figure 10: Schematic sketch of a four socket architecture. It shows the NUMAmemory, shared caches, as well as QPI-links connecting the sockets.

pute eight combined multiply and add functions per cycle, resulting in a peak performance of 16 flop per cycle. Luckily modern processors are also equipped with bigger and bigger caches to hide long latencies when accessing slow off-core memory.

Properly using these big caches is becoming an important issue for programmers. Especially the last level of on-chip cache (L3) is crucial for the performance of many algorithms because it is the largest cache that can hide long load times from off-chip memory. Since the L3-cache is commonly shared between all cores of one processor, we can decrease the number of L3-cache-misses by reusing cache-lines that were originally loaded by another core of the same processor. This makes the L3-cache even more interesting from an algorithmic point of view. We call all cores sharing one L3-cache a cache-node.

Another aspect of modern multi-socket machines is that they are usually NUMA-machines (Non Uniform Memory Access). This means that there are different memory sections and the access rate of each memory section depends on the processor that it is accessed from. In practice, every socket has its own "local" memory. Local memories are shared between sockets, but accesses are significantly faster when accessing local memory. Everything that is accessed remotely has to be shared through QPI links (QuickPath Interconnect) connecting all sockets (see Figure 10).

NUMA-machines accentuate the importance of caches even further because there can be longer latencies when accessing memory remotely. Memory controllers are usually shared between all cores of one processor. Thus, cache-nodes and NUMA-nodes usually correspond with each other. Therefore, we use the terms node, cache-node, and NUMA-node somewhat interchangeably.

In the following, we will also use the terms thread and core interchangeably. At the beginning of the execution, we start one thread per core. Every thread is pinned to one corresponding core. Even though every machine that we used supports hyper-threading, we create only one thread per physical core. Hyper-threading does not actually improve the performance of the LU-decomposition since the two hardware-threads that are executed on the same core share a common floating-point unit.

# 3 Our Concepts for Performance Improvements

In this section, we present the ideas and concepts that we used to optimize the scheduling of subtasks. As described in Section 2.2.3, U-tasks represent the most work among all task classes. They are the only task class that performs  $\Theta(n_{glob}^3)$  floating point operations. In our experiments, U-tasks take up to 95% of the running time especially on large matrices (see Section 6.4.1). Therefore, we concentrate our efforts on improving the performance of U-tasks.

At first we will describe how the scheduling of subtasks can influence the cache status, and thereby, the performance of a subtask. To do this we first define a cache model that will simplify the cache behavior during the computation (Section 3.1). Then we point out why classical DAG-scheduling (Section 3.2) might not be the best option to schedule the LU-decomposition. After this introduction, we go into further detail on our approach to improve the cache performance (Section 3.3) and NUMA-behavior (Section 3.4) of our implementation.

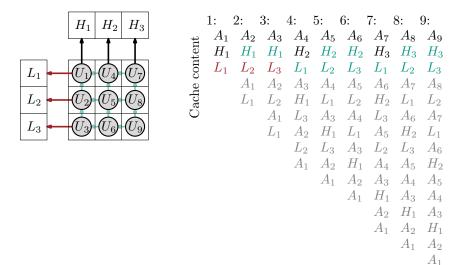

### 3.1 Tile-Cache Model

To be able to predict the cache performance of a potential schedule, we developed the following theoretical machine model. It is supposed to replicate the conditions described in Section 2.5 while still being easy to work with.

For our purposes a modern multi socket machine consists of s nodes  $(node_0, \ldots, node_{s-1})$ . Each node consists of p cores, a shared tile-cache, and local memory. The cores are labeled globally,  $core_0, \ldots, core_{p-1}$  are the cores of  $node_0$  (subsequently  $node_i$  consists of  $core_{i cdot p}, \ldots core_{(i+1) cdot p-1}$ ). Each node's shared cache can contain a constant number c of matrix tiles (see Section 2.1 Blocked Data layout) depending on the tile size  $(b \times b)$  and the physical cache size.

When a task t is executed on  $core_i$  all input tiles  $A_{in} \in IN(t)$  have to be read. There are three different memory locations where  $A_{in}$  could be read from:

- (Cache Hit) If tile  $A_{in}$  is already loaded into the shared cache of the corresponding node, then it can be read from this cache reducing the loading time significantly.

- (Locally Solvable Cache Miss) The tile is not cached and has to be read from the local memory.

- (NUMA-Miss)  $A_{in}$  is not cached and is not stored locally thus it has to be loaded from another node's local memory. We call this a NUMA-miss.

Every tile, that is read this way, is stored in  $core_i$ 's shared cache. After the execution of t, each output tile  $A_{out} \in OUT(t)$  replaces the corresponding input tile in the local cache. Eventual copies of the old version in other caches are invalidated (removed).

T- and X-tasks are the only tasks that read partial tiles. Therefore their input tiles have to be treated differently. T- and X-tasks perform row exchanges on non-panel tiles. A T-task  $T_{kj}^{(k)}$  swaps rows of the tile-column  $A_{k...nj}$  into its uppermost tile  $A_{kj}$ . Therefore, it reads/changes  $A_{kj}$  completely and only reads/changes single rows of all other tiles within the column. Hence, we approximate that for cache modeling purposes a T-task (or X-task) only reads and writes the topmost

tile of its column. To represent the additional data that is read from the rest of the column, we load another tile into the local tile cache. This tile is not part of the actual matrix. It is loaded into the cache to "waste" space, therefore, it cannot be used for future cache hits. Since all other tiles of the column are not changed significantly, they are not invalidated or cached.

Each local cache can store up to c different tiles. When the tile  $A_{in}$  is loaded and the local cache is already at its capacity, an old tile will be replaced. In our model we replace the tile that has not been used for the longest time.

This cache model is meant to simulate the behavior of modern L3-caches during the computation of the LU-decomposition. There are some key differences between our model and actual hardware caches. The biggest difference is that the model only represents complete matrix tiles. In reality a tile consists of thousands of different cache lines. We think that this simplification is justifiable because most subtasks accesses their input tiles as a whole. This means that their cache lines enter the cache succinctly and are probably also replaced somewhat succinctly.

The simulation assumes a fully associative "least recently used" cache (the oldest tile of the cache is replaced) when in reality caches are not fully associative. This means, that a new cache line can only replace a cache line from a subset of all cache lines. Hence, it might not always be the oldest cache line which is replaced. Cache lines might even be evicted although the cache is not full yet. This happens if the corresponding subset of the cache is full.

We think that in our case the assumption of a fully associative cache is valid. The machine, that we used for testing (see Section 6.1 SandyBridge32), has a 20-way set associative cache. This means, the cache can simultaneously store up to 20 cache lines associated with one *cache group*. If we assume that no two cache lines of one matrix tile share the same cache group (This assumption is guaranteed if a tile is stored consecutively within the physical memory) then there can be at least 20 different tiles in the shared cache of one node and replacement should work as expected.

Our model only counts the number of "tile-cache hits" (and misses). We do this because reading one tile produces significantly less cache misses than the number of cache lines that the tile consists of. Therefore, we believe that in practice a lot of work is done by the prefetcher. We also assume that a matrix tile is big in comparison to all other data which is loaded during the execution of a task. Therefore, we ignore all data that is not part of the matrix in our cache simulation. Reloading parts of other data structures should not evacuate significant parts of a tile from the cache.

This cache model simplifies the complex behaviors of modern hardware caches good enough to predict the effectiveness of our following optimization techniques. In Section 6.5, we show that it also holds up in real experiments and measurements.

# 3.2 Data co-use Hypergraph

One major problem with using classical DAG-scheduling for the LU-decomposition is that all relations between subtasks are expressed through precedence constraints. Two tasks that are not directly or indirectly dependent have no con-

(a) Some examples of hyperedges drawn into a section of the task-DAG (consisting of two iterations and no X-tasks).

(b) Hyperedges connecting tasks from one iteration. The different types of hyperedges (panel tile, tile from topmost tile row) are color coded as in Figure 11a. Bright edges do not reappear in Figure 11a.

Figure 11: Data co-use hyperedges.

nection. Therefore, they are scheduled completely independent from one another even if they share common input tiles. This makes expressing data reuse between different tasks difficult. But since our subtask implementation basically uses the same code as our competitors (mostly BLAS library calls), cleverly scheduling different subtasks becomes the only way to improve running times.

To improve the global schedule, we analyze not only the obvious precedence constraints of the task-DAG. We also review data reuse possibilities. Therefore, we introduce new *hyperedges* (edges connecting more than two tasks) between tasks that read (write) the same version of a memory section.

$$HE(mem^{(v)}) = \{t_i \in V \mid task \ t_i \ reads \ or \ writes \ into \ mem^{(v)}\}$$

In our case the memory sections correspond to matrix tiles. Each version of a matrix tile  $A_{ij}^{(k)}$  implicitly defines a hyperedge  $\text{HE}(A_{ij}^{(k)})$  which contains all subtasks that read (or write) tile  $A_{ij}^{(k)}$ .

$$HE(A_{ij}^{(k)}) = \{t_i \in V \mid task \ t_i \ reads \ or \ writes \ into \ tile \ A_{ij}^{(k)}\}$$

In Figure 11 we show examples of hyperedges within the task-DAG (Figure 11a) and within the spatial representation of one iteration (Figure 11b). One can easily see that each hyperedge  $HE(A_{ij}^{(k)})$  contains exactly one task that writes  $A_{ij}^{(k)}$ . All other tasks read  $A_{ij}^{(k)}$ . Each precedence constraint edge  $(t_a, t_b)$

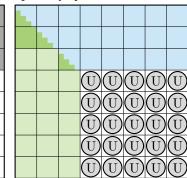

(a) One U-task and its input tiles (the neighboring Utask shares an input tile).

(b) Square group of nine Utasks sharing multiple input tiles.

Figure 12: *U-tasks sharing input tiles*.

can be found within such a hyperedge. The constraint is caused by  $t_b$  using the results of  $t_a$ . In the context of our computation results are matrix tiles. Therefore, the constraint is caused by a tile which  $t_a$  writes to that  $t_b$  reads. But not all connections of such a hyperedge follow precedence constraints.

If we look at hyperedge  $\operatorname{HE}(A_{k+1\,k}^{(k)})$  (the second panel tile of iteration k), the hyperedge contains all tasks that handle  $A_{k+1\,k}^{(k)}$  namely  $P_{kk}^{(k)}$  (the panel task),  $U_{k+1\,(k+1)\dots n}^{(k)}$  (the topmost row of U-tasks), and  $X_{k+1\,k}^{(k+1)}$ . The tasks  $U_{k+1\,(k+1)\dots n}^{(k)}$  have no connection in the original task-DAG. Hence, a classical DAG-scheduler would not know that all these tasks share an input tile, let alone schedule them appropriately.

Our target is to schedule tasks in such a way that these data reuse possibilities are exploited. Scheduling multiple tasks of one data reuse hyperedge appropriately can often lead to an improved cache performance and even reduce the amount of node to node communication.

# 3.3 Cache Improvements

When a core works on a U-task  $U_{ij}^{(k)}$ , there are three input tiles that have to be loaded into the local cache: the topmost tile of the tile column  $A_{kj}^{(k)}$ , the panel tile  $A_{ik}^{(k)}$ , and the original tile  $\widetilde{A}_{ij}^{(k-1)}$  (see Figure 12a). If the same core would also compute the neighboring tile update  $U_{ij+1}^{(k)}$ ,  $A_{ik}^{(k)}$  might still be in the cache. This produces a cache hit in our machine model (see Section 3.1), thus, there would only be the need to load two new matrix tiles.

As described in Section 3.1, caches are shared between all cores of one node. Therefore, we can also reduce the amount of tile loads by scheduling neighboring tasks simultaneously on two cores of the same node. This can be even more beneficial because it reduces the amount of tiles that have to be cached simultaneously. If we schedule all U-tasks that operate on one tile-row i to a node, then we only need to store two tiles per core plus the shared tile  $A_{ik}^{(k)}$ . Thus, tiles can remain inside the cache longer because less tiles are actively needed for the

computation.

With that said, we need to figure out how to group and schedule U-tasks such that we reuse as many cached tiles as possible. To do this we analyze the data reuse hyperedges described in Section 3.2. The hyperedges between U-tasks of one iteration k have a grid structure (see Figure 11b). All U-tasks working on one column j are connected through the common use of the topmost tile  $A_{kj}^{(k)}$  ( $U_{(k+1)\dots nj}^{(k)} \in \operatorname{HE}(A_{kj}^{(k)})$ ), and all U-tasks operating on the same row i are connected through the common use of the same panel tile  $A_{ik}^{(k)}$  ( $U_{i(k+1)\dots n}^{(k)} \in \operatorname{HE}(A_{ik}^{(k)})$ ).

Therefore, we propose to group tasks that operate on a square of tiles. This exploits horizontal and vertical data reuse opportunities equally (see Figure 12b). If we group all U-tasks working on a  $3 \times 3$  square of tiles, then computing all nine U-tasks in parallel loads a total of 15 distinct tiles (three panel tiles, three tiles of the first row, and the nine tiles that are operated on). This way, we can save twelve loaded tiles compared to unoptimized execution (three tiles per U-task = 27 loaded tiles) and four loaded tiles compared to row/column-wise groups (two tile loads per task plus one commonly used tile = 19 loaded tiles). The savings increase even more when we increase the number of tile updates that are grouped together  $(4 \times 4 \Rightarrow 24$  tile loads  $\Rightarrow 24$  tiles saved).

There are upper limits to the size that groups of U-tasks should have. If a group is too big, cached tiles might be replaced while the node still works on the same group. In this case cache benefits might be lost because tiles are replaced before they can be reused.

# 3.4 Targeted NUMA-Scheduling

In Section 3.3, we introduce a possibility to reduce the number of tile loads throughout our matrix update tasks. Our next goal is to accelerate the tile loads that are still needed. As described in Section 3.1, there are three different memory locations a read tile can come from, the cache, the local memory node, and a foreign node. We want to make sure that our implementation of the LU-decomposition loads as few tiles as possible from foreign nodes. At first we want to describe what parameters we can influence to achieve this.

The first influence that we have on the NUMA-performance is that we can influence the way in which the matrix is distributed on different nodes of the machine. We store the matrix separated in tiles with a blocked data layout (see Section 2.1). Each tile is stored on one node in a consecutive area of memory. To be able to improve the locality of data reads, we can control the distribution of the matrix tiles to nodes. This distribution can be described as a mapping.

$$t2n: Tiles \rightarrow |Nodes|$$

We chose to keep this mapping constant within one computation. This means that we will not move tiles from one node to another. Moving a tile during the computation would require copying an existing tile. We believe that the time needed for this copy is greater than the time that can be saved through NUMA-hits on this tile. Therefore, all different versions of one tile will always remain on the same node (at the same global position).

The second influence that we have on the NUMA-behavior of our implementation is the placement of subtasks. Our implementation will work on each core of the machine in parallel. Therefore, we can control which core of the machine executes a certain subtask. This can be described as a mapping comparable to t2n. Note, that we do only map to nodes (not to specific cores). The specific core does not matter from a NUMA standpoint and this mapping leaves us more freedom for the specific scheduling.

$$s2n: Subtasks \rightarrow |Nodes|$$

If we schedule a subtask on the node that contains all its input tiles, then that subtask will not lead to any NUMA-misses. It is not possible to place all matrix tiles such that all input tiles of each U-task are located on the same node.

Instead, we have to optimize t2n and s2n together to achieve the best possible NUMA-behavior. To do this, we look at the different tiles that are accessed by each task. What sticks out to us is that all tasks access multiple tiles from one tile column. P-tasks access the whole panel, T- and X-tasks exchange lines within one tile column, and even U-tasks access two tiles from one column  $(U_{ij}^{(k)})$  accesses  $A_{ij}$  as well as  $A_{kj}$ .

Therefore, we propose to distribute the matrix tile-column-wise. This means that all tiles of one tile-column are stored in the local memory of the same node. Subsequently, subtasks are scheduled to be executed on a core that belongs to the node where most of their input tiles are stored.

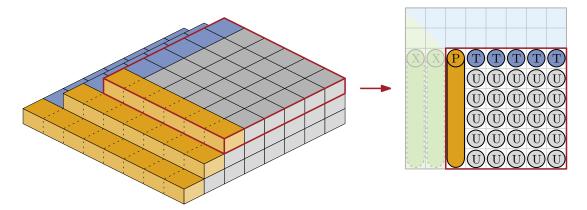

# 3.5 Merging Cache and NUMA-Strategies

On first glance our cache and NUMA-strategies work against each other. In Section 3.4 we proposed to store the matrix distributed tile-column-wise and to schedule subtasks on the node that holds their input tiles. For our proposed cache optimizations, introduced in Section 3.3, we suggest to execute square groups of tasks on one node to exploit opportunities for cache co-use.

If we distribute the matrix in a round robin tile-column-wise pattern, the two tasks  $U_{ij}^{(k)}$  and  $U_{ij+1}^{(k)}$  are supposed to be scheduled on two different nodes (according to the NUMA-optimization). For cache purposes they are two neighboring tasks which could benefit from being scheduled on one node (simultaneously).

Another mistake would be to partition the matrix into |Nodes| vertical sections. This would cause an imbalanced work placement. With each iteration the area of the matrix that is worked on by P-, T-, and U-tasks shrinks by one tile-column. Hence, the node that is responsible for the leftmost section will have less tasks to execute (apart from X-tasks, which do not perform any floating point operations).

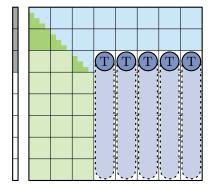

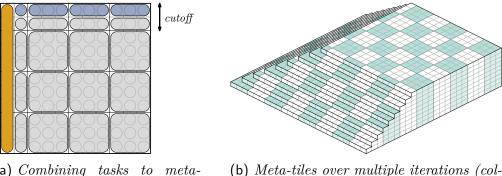

Our solution to this problem is to distribute m neighboring tile-columns to one node. This allows us to group tasks that work on  $m \times m$  squares of tiles for "simultaneous" execution on one node. It also roughly balances the work load of different nodes. To further simplify the grouping of tasks for cache purposes, we introduce meta-tiles. Meta-tiles are  $m \times m$  squares of tiles. In our implementation we group tasks depending on the meta-tile that they operate on (see Section 4.1.2).

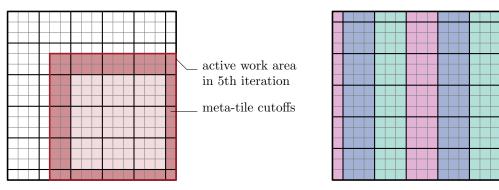

The most obvious way to combine tiles to meta-tiles is to combine the  $m \times m$  tiles on the upper left side of the matrix and to continue from there. This is really easy if n is a multiple of m, because then every meta-tile has the same size. But if this is not the case, then tiling the matrix from the upper left side will lead to cutoffs in the last row/column of meta-tasks (cutoffs = smaller meta-tiles; see Figure 13a).

As described in Section 2.2.4, the area of the matrix that is actively being worked on is a shrinking square on the bottom right side of the matrix. Each iteration shrinks this square by one tile row/column. Therefore, the top left border of this square can cut across meta-tiles (see Figure 13a). Hence, there can also be cutoffs on the top left side of the square. So instead of creating meta-tiles from the top left side of the matrix, we start tiling the matrix from the bottom right corner of the matrix (see Figure 13b). This reduces the absolute number of possible borders with cutoffs (there can never be cutoffs on the bottom/right side of the matrix).

With these considerations we can define t2n and s2n as:

```

off = m - (n \mod m)

t2n: A_{ij} \mapsto ((j + off) \operatorname{div} m) \operatorname{mod} |Nodes|

s2n: Y_{ij}^{(k)} \mapsto ((j + off) \operatorname{div} m) \operatorname{mod} |Nodes| = t2n(A_{ij})

```

In Section 2.2.3 we describe that P-tasks use a parallelized algorithm. Thus, there can be multiple cores cooperating on one P-task. In this case, we enforce that all cores working on one P-task belong to one node. This creates an upper bound to the number of cores working on one P-task. In Section 5.4 we describe why this restriction is not problematic.

Even with this distribution the workload is not fully balanced between nodes. Therefore, s2n(t) should only be used as the preferred node for task t (no strict allocation). There has to be a system which prioritizes the execution of t on the preferred node but also ensures that no core is idling while there are ready tasks that can be executed. This form of work-stealing or work-rebalancing is important because the time that can be saved through proper NUMA-placement of one task is too small to justify waiting for a more appropriate task while other tasks are ready.

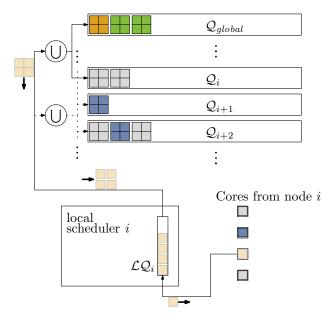

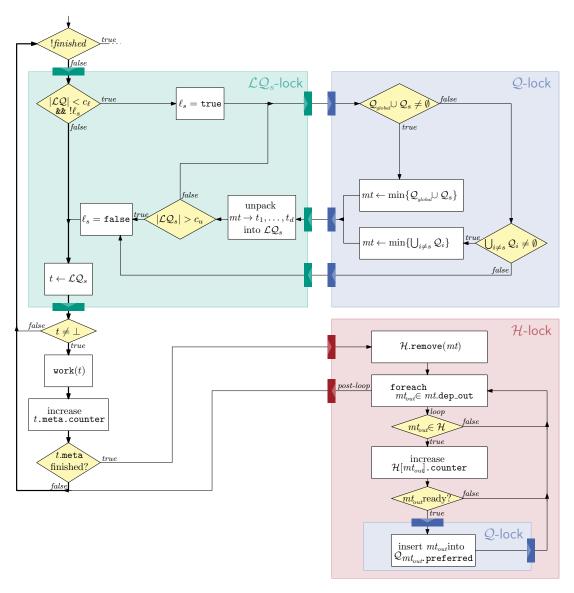

# 4 Overview of our Solution

Our Scheduler works on a two level hierarchical approach. On the *global level* groups of tasks which we call *meta-tasks* are scheduled to nodes. On the *local level* meta-tasks are unpacked into individual subtasks and then scheduled to cores. This two level approach – with meta-tasks – has a lot of benefits. It reduces creation and scheduling overheads of tasks because we will never handle individual tasks on the global scheduling level. It also simplifies the treatment of parallelized subtasks (P-tasks) and the implementation of our cache improvements described in Section 3.3.

We begin this section by describing the concept and the creation of metatasks (in Section 4.1). Then, we describe the architecture of our scheduler (in

- (a) When we start tiling from the top left corner, there are iterations with metatile-cutoffs on each side of the matrix.

- (b) A matrix with 3 × 3 meta-tiles and NUMA-distribution on three nodes. Tiling from the lower right corner reduces cutoffs.

Figure 13: Meta-tiles and NUMA-distribution of the matrix.

Section 4.2). This scheduler uses methods of DAG-scheduling (see Section 2.3), which we refined with our cache and NUMA-concepts (see Section 3), to schedule tasks.

### 4.1 Meta-Tasks

The task-generation is done sequentially in the beginning of the execution. One core creates all meta-tasks and inserts them into the data structures of the scheduler. This is done in a way that allows other cores to start working as soon as the first task is fully created (see Section 5.2.1).

The DAG that we schedule during the execution is not exactly the task-DAG that we presented in Section 2.4. On the global scheduling level we work only with meta-tasks. Therefore, we will be scheduling a DAG that has meta-tasks as its vertices.

### 4.1.1 Meta-Task Definition

Formally, A meta-task is a set of subtasks. For scheduling purposes, we can extend the definitions of dependency and readiness (see Section 2.3) on meta-tasks. A meta-task  $mt_2$  depends on another meta-task  $mt_1$  if there is a task  $t_2 \in mt_2$  that depends on a task  $t_1 \in mt_1$ . A meta-task is ready to be executed if there are no unfinished meta-tasks that it depends on.

With these preliminary definitions we can define the meta-task-graph. The meta-task-graph is the graph that we get by contracting all tasks belonging to one meta-task within the task-DAG. More formally, it is the graph  $\overline{G} = (\overline{V}, \overline{E})$  where  $\overline{V}$  is the set of all meta-tasks and  $\overline{E}$  is the set of all meta-task dependencies

$$\overline{V} = \{mt_1, \dots mt_\ell\} \qquad mt_i \subset V \qquad V = \bigcup_{mt \in \overline{V}} mt$$

$$\overline{E} = \{ (mt_1, mt_2) \in \overline{V} \times \overline{V} \mid \exists t_1 \in mt_1, \ t_2 \in mt_2 \quad (t_1, t_2) \in E \}$$