# Soft Error Analysis and Mitigation at High Abstraction Levels

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

## Dissertation

von

## Liang Chen

aus Henan, China

Tag der mündlichen Prüfung: June 19, 2015

Referent:

Korreferent:

Prof. Dr. Mehdi Baradaran Tahoori, KIT Dr. Dan Alexandrescu, iRoC Technologies

## Acknowledgments

Completing the PhD is a long expedition for me, during which I underwent unforgettable life experience: from daunting and discouraging periods after bitter frustrations on research and publications, to the comforting and reassuring moments after fruitful project progress and final acknowledgment from the research community. Standing at the destination point and looking back at the old times, I want to express my deepest gratitude to all the people accompanying me in this journey.

First and foremost I want to give the sincere thanks to my advisor Prof. Mehdi Tahoori. During the more than 4 years PhD period, his visionary advice on my research directions, his continuous care of my research progress as well as his patient efforts to improve my research capabilities are the prerequisites for my successful completeness of this dissertation today. In addition, his encouragement after research difficulties and paper rejections, the valuable opportunities he provided for communications with scientific experts as well as industry leaders during international conferences or workshops, are other indispensable factors for my professional and personal development. In particular, during the internship at iRoC I met Dr. Dan Alexandrescu and had impressive working experience with him. His extraordinary expertise in my research period, the inspiring discussion with him on the cutting edge industry progress, and the efforts he spent as the second advisor during the graduation progress are all highly appreciated.

Furthermore, I want to thank all the colleagues in our Chair of Dependable Nano Computing (CDNC). Their responsible and kind-hearted help in both working and personal aspects facilitated my research activities in CDNC, as well as my living experience in Karlsruhe. Among them I would like to give special gratitude to Mojtaba Ebrahimi, with whom I had very close research collaborations in the past years. His inspiring advices during idea formulation, his consistent help in the implementations, paper writing and polishing have made significant contributions to my PhD achievements.

In addition, I gratefully acknowledge the funding sources that made my PhD work possible: the DFG SPP1500 Priority Program "PERICES: Providing Efficient Reliability in Critical Embedded Systems".

I am also very grateful to my friend and senior Dr. Bing Li from Technical University Munich, who gave me essential advices and encouragement to go through the toughest period during my PhD study. Last but not least, I want to thank my parents and sister who are accompanying me with endless love all the time. No matter what happens, they are always supporting me and standing on my side, which is the root source of all my power and passion in the life.

Liang Chen Haid-und-Neu Str. 62 76131 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen - die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Karlsruhe, Juli 2015

Liang Chen

## ABSTRACT

With the rapid advance of semiconductor technology in the past several decades, computing systems already become indispensable parts of our society. The main driving forces behind the prevalent usage of these systems are their boosting performance and continuous integration of sophisticated functionalities. However, alongside with the aggressive downscaling of the transistor feature size in these systems, the current and future technologies are facing serious reliability challenges, which mandate a new paradigm to take reliability into consideration during the entire system design flow to achieve cost-efficient reliable computing.

One of the major reliability issues is radiation-induced soft error, which is a type of transient fault during the system operation, and it is caused by charge collection after the transistor is struck by the energetic particles from packaging materials or cosmic rays. Soft errors are not reproducible and can severely corrupt the system data integrity. The previous soft error mitigation solutions at low abstraction levels are very costly, because they stay at the end of the design stack and the useful high level application semantics for error abstraction and the corresponding error masking effects are totally ignored. In contrast, at high abstract levels there are significant potentials for cost-effective solutions, because the reliability metric are considering earlier in the design phase, and the larger flexibility in the design space exploration can be leveraged.

This thesis presents several novel and efficient techniques for soft error evaluation and mitigation at high abstract levels, i.e. from register transfer level up to behavioral algorithmic level. For error evaluation, first we perform sophisticated correlation analysis during the propagation process of multiple errors, which enables the appropriate error abstraction from logic level to register transfer level. Then at register transfer level, according to different error propagation properties, the data and control paths are carefully analyzed with analytical and formal techniques, respectively. Finally at the algorithmic level, the soft error evaluation is comprehensively performed by considering branch probabilities and functional semantics using the probabilistic model checking technique.

Based on previous detailed soft error evaluation, cost-efficient error mitigation solutions based on selective protection are investigated during the high level synthesis process. We develop a versatile reliability-aware synthesis framework regarding the allocation and binding of hardware modules (in the spatial domain), and the scheduling of behavioral operations (in the temporal domain), which can generate low-cost reliability-enhanced hardware implementations at register transfer level. This synthesis framework features the comprehensive consideration of the reliability metrics at both low and high abstraction levels, i.e. intrinsic soft error rates of hardware modules and algorithmic error vulnerabilities of behavioral variables and operations. The effectiveness of the proposed techniques is demonstrated with extensive synthesis experiments, which show that compared with the state-of-the-art solutions, our techniques can achieve much higher system reliability with the same hardware overhead, i.e. more cost-efficient reliability enhancement.

## ZUSAMMENFASSUNG

Bedingt durch die schnell voranschreitende Entwicklung der Halbleitertechnologie in den vergangenen Jahrzehnten sind Computersystem mittlerweile essentielle Bestandteile unserer Gesellschaft. Der Hauptgründe für diesen Erfolg und die gängige Nutzung solcher Systeme ist die kontinuierlich wachsende Leistungsfähigkeit und die Integration von immer mehr sowie immer ausgeklügelteren Funktionen. Um dies zu ermöglichen werden die Transistordimensionen mit jeder Generation weiter verkleinert. Dies bringt allerdings auch zahlreiche Herausforderungen mit sich. So sind aktuelle und zukünftige Technologiegenerationen grossen Zuverlässigkeitsherausforderungen ausgesetzt, weshalb die Zuverlässigkeit von Computersystemen als Paradigma in allen Phasen des gesamten Entwicklungszyklus solcher Systeme beachtet werden muss.

Eine der wichtigsten Zuverlässigkeitsherausforderungen sind "Soft Errors" verursacht durch Strahlung. Dabei handelt es sich um transiente Fehler, die während des Betriebs auftreten, und durch Treffer von hochenergetischen Teilchen aus dem Verpackungsmaterial oder aus kosmischer Strahlung hervorgerufen werden. "Soft Errors" können daher nicht reproduziert werden. Darüber hinaus können sie die Datenintegrität des betroffenen Systems stark beeinträchtigen. Die bisherigen Lösungsansätze konzentrieren sich auf die untersten Abstraktionsschichten und sind daher sehr kostspielig, da in solchen Methoden "Soft Errors" nur am Ende des Designzyklus beachtet werden und nützliche Informationen von höheren Abstraktionsebenen nicht berücksichtigt werden. Dennoch haben höhere Abstraktionsebenen ein grosses Potential um zu einer effektiven Problemlösung beizutragen, da die Zuverlässigkeitsprobleme bereits in frühen Phasen des Entwicklungszyklus betrachtet werden können und zudem ein grösserer Suchraum für Lösungsansätze besteht.

In dieser Dissertation werden neue Ansätze zur Modellierung und zur Problemlösung für "Soft Errors" auf höheren Abstraktionsebenen (von Register-Transfer-Ebene bis zur Algorithmen-Ebene) vorgestellt. Um eine geeignete Abstraktion der Fehlermechanismen zu erreichen, müssen dazu die Korrelationen von diversen Fehlerursachen auf Logikebene untersucht werden. Anschliessend folgt eine weitere Abstraktion auf Register-Transfer-Ebene, auf der die Daten- und Kontrollpfade mit Hilfe von analytischen sowie formalen Methoden analysiert werden. Schlussendlich wird eine "Soft Error" Evaluierung auf noch höheren Abstraktionsebenen unter der Berücksichtigung der Verhaltensbeschreibung des Designs durchgeführt. Hierzu wird ein probabilitischer Model-Checker-Ansatz entwickelt, der Sprungwahrscheinlichkeiten und semantischen Aussagen des Designs in die Analyse miteinbezieht.

Basierend auf der detaillierten "Soft Error" Analyse können dann kostengünstige Ansätze entwickelt werden um die Fehlerrate zu verringen, in dem selektive Schutzmöglichkeiten währen der High-Level Synthese ausgenutzt werden. Zu diesem Zweck haben wir eine Synthese-Plattform auf Register-Transfer-Ebene entwickelt, die die Zuverlässigkeit der Schaltung berücksichtigt. Mit dieser Plattform ist es möglich, eine optimale Strategie hinsichtlich der Zuverlässigkeit für die Allokierung und Bindung der Hardware-Ressourcen (örtliche Domäne) sowie für das Scheduling der Operationen (zeitlich Domäne) zu finden, um auf diese Weise die Zuverlässigkeit der Schaltung zu verbessern. Dafür baut die Plattform auf ausführlich beschriebenen Zuverlässigkeitsmetriken auf. Die Effektivität der vorgestellten Ansätze während der High-Level Synthese wird in ausführlichen Experimenten beleuchtet und mit State-of-the-Art Lösungen verglichen. Diese Vergleiche zeigen dabei, dass unsere Methoden wesentlich effizienter die Zuverlässigkeit verbessern können, d.h. mit den gleichen Kosten kann die Zuverlässigkeit des Systems deutlich gegenüber gängigen Lösungen gesteigert werden.

# Contents

| Glossary       |          |                                                    |    |

|----------------|----------|----------------------------------------------------|----|

| Lis            | st of    | Figures                                            | ix |

| List of Tables |          |                                                    |    |

| 1              | oduction | 1                                                  |    |

|                | 1.1      | Scope and Contributions                            | 2  |

|                | 1.2      | Outline                                            | 5  |

| 2              | Prel     | liminaries and State of the Art                    | 7  |

|                | 2.1      | Soft Error Basics                                  | 7  |

|                |          | 2.1.1 Origins                                      | 7  |

|                |          | 2.1.2 Models and Metrics                           | 9  |

|                |          | 2.1.3 Scaling Trends                               | 10 |

|                | 2.2      | Soft Error Analysis and Mitigation                 | 11 |

|                |          | 2.2.1 Design Views and Abstraction Levels          | 11 |

|                |          | 2.2.2 Low Level Error Analysis and Mitigation      | 14 |

|                |          | 2.2.3 High Level Error Analysis and Mitigation     | 17 |

|                |          | 2.2.4 Summary of State of the Art                  | 20 |

| 3              | Erro     | or Correlation Analysis at Logic Level             | 21 |

|                | 3.1      | Introduction                                       | 21 |

|                | 3.2      | Related Work                                       | 22 |

|                | 3.3      | Correlation Model                                  | 23 |

|                |          | 3.3.1 Correlation Coefficient Method               | 24 |

|                |          | 3.3.2 Error Correlation                            | 26 |

|                | 3.4      | Proposed Error Estimation Methodology              | 26 |

|                |          | 3.4.1 Error Propagation Model                      | 27 |

|                |          | 3.4.2 Error Cone Extraction                        | 29 |

|                |          | 3.4.3 Super-gate Correlation Formulas              | 29 |

|                |          | 3.4.4 Dynamic Blocking of Error Propagation        | 31 |

|                |          | 3.4.5 Limited Depth Correlation Analysis           | 31 |

|                | 3.5      | Extensions of the Proposed Method                  | 34 |

|                |          | 3.5.1 Multiple Errors Propagation with Correlation | 34 |

|                |          | 3.5.2 Block-level Error Estimation                 | 34 |

|                | 3.6      | Experimental Results                               | 35 |

|                |          | 3.6.1 Experimental Setup                           | 35 |

|                |          | 3.6.2 Benchmark Results                            | 39 |

|                |          | 3.6.3 Case Study of OpenRISC 1200 ALU              | 40 |

|                | 3.7      | Conclusion and Summary                             | 43 |

| 4 | Vulr | nerability Analysis at Register Transfer and Behavioral Levels | 47 |

|---|------|----------------------------------------------------------------|----|

|   | 4.1  | Introduction                                                   | 47 |

|   | 4.2  | Preliminary and Problem Statements                             | 49 |

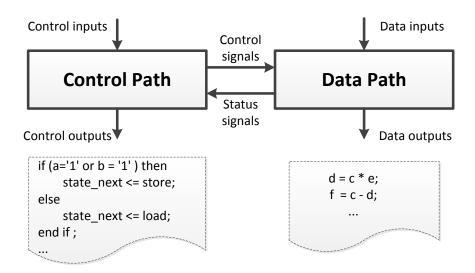

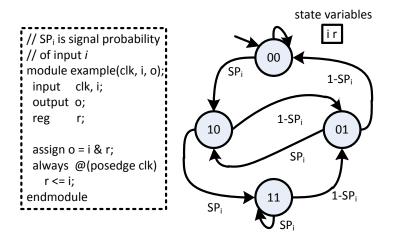

|   |      | 4.2.1 RTL Control and Data Paths                               | 49 |

|   |      | 4.2.2 Fault Model and Register Vulnerability                   | 49 |

|   |      | 4.2.3 Formal Methods for Soft Error Analysis                   | 50 |

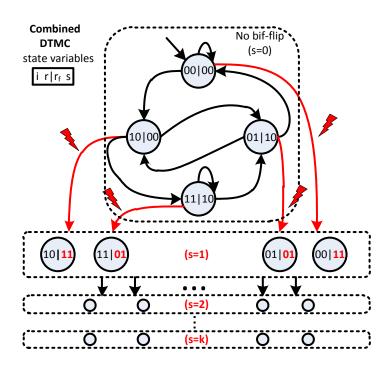

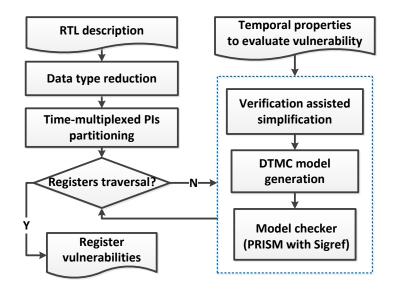

|   | 4.3  | Register Vulnerability Evaluation in RTL Control Paths         | 52 |

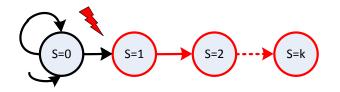

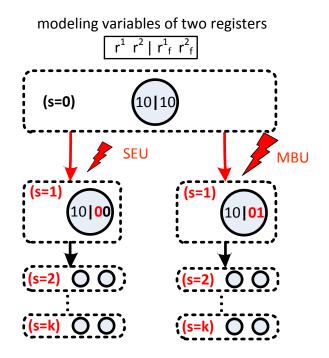

|   |      | 4.3.1 Probabilistic Model Construction                         | 52 |

|   |      | 4.3.2 Property Specification                                   | 54 |

|   |      | 4.3.3 Model Checking                                           | 55 |

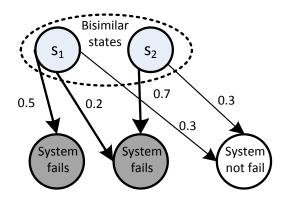

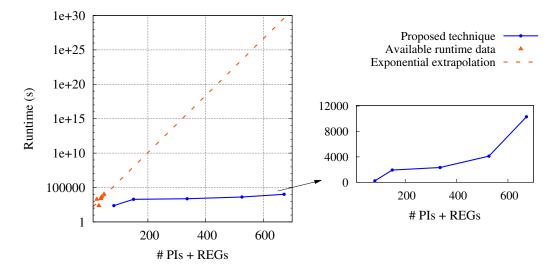

|   |      | 4.3.4 Scalability Improvement of the RTL Model Checking        | 56 |

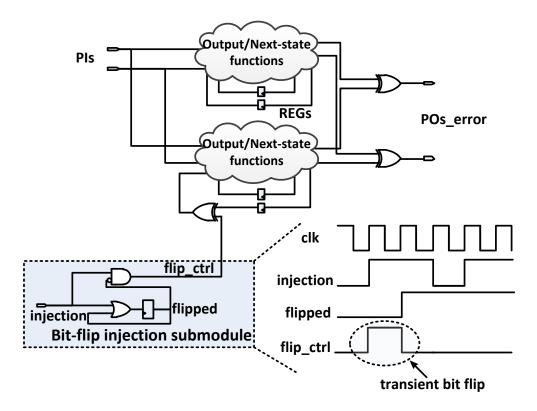

|   | 4.4  | Word-level Error Analysis in RTL Data Paths                    | 61 |

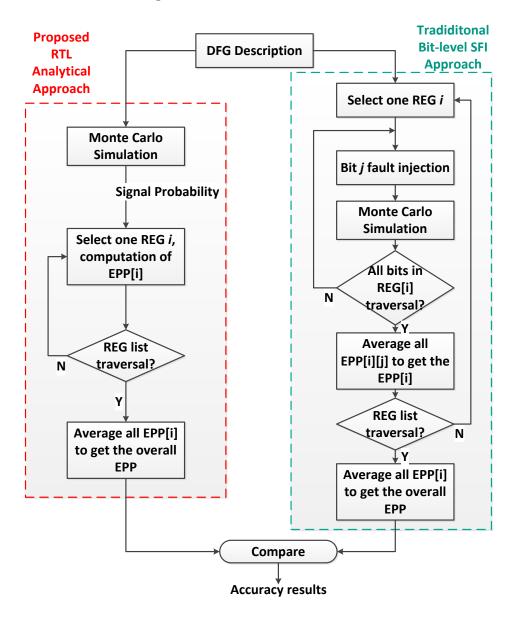

|   |      | 4.4.1 Basic Idea                                               | 61 |

|   |      | 4.4.2 Bit-level vs Register-level                              | 61 |

|   |      | 4.4.3 Register-level EPP Rules                                 | 63 |

|   |      | 4.4.4 Overall EPP Estimation                                   | 66 |

|   | 4.5  | Vulnerability Analysis at Behavioral Level                     | 67 |

|   |      | 4.5.1 Random Error Occurrence Modeling                         | 67 |

|   |      | 4.5.2 Error Propagation Modeling                               | 67 |

|   |      | 4.5.3 Vulnerability Evaluation                                 | 69 |

|   | 4.6  | Experimental Results                                           | 69 |

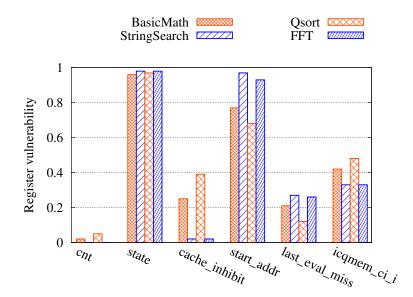

|   |      | 4.6.1 Control Path Evaluation Results                          | 69 |

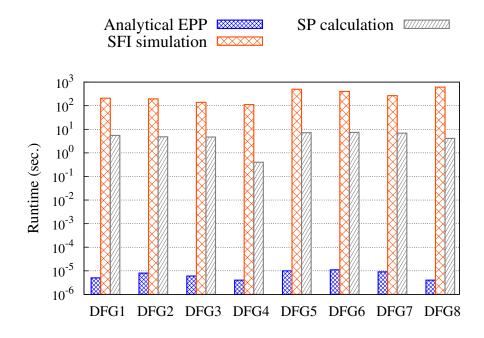

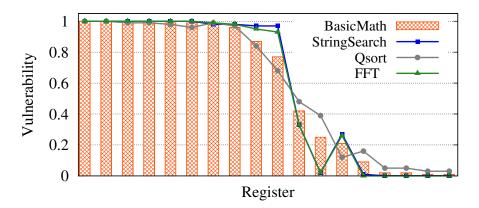

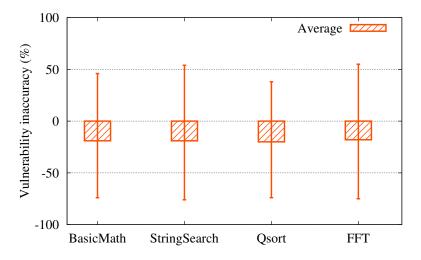

|   |      | 4.6.2 Data Path Evaluation Results                             | 72 |

|   |      | 4.6.3 Case Study of OpenRISC IC FSM                            | 76 |

|   |      | 4.6.4 Comparison with Related Work                             | 77 |

|   | 4.7  | Conclusion and Summary                                         | 79 |

|   |      |                                                                |    |

| 5 | Reli | ability-aware Resource Allocation and Binding                  | 81 |

|   | 5.1  | Introduction                                                   | 81 |

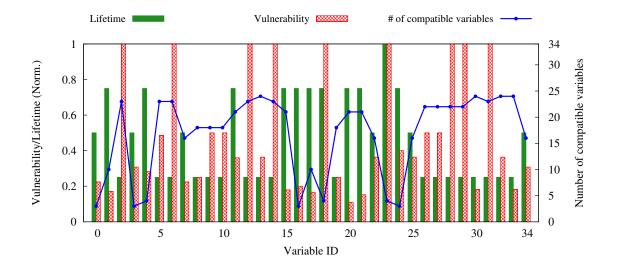

|   | 5.2  | Motivation                                                     | 83 |

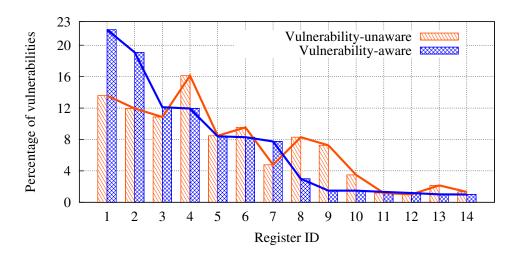

|   |      | 5.2.1 Non-uniform Soft Error Vulnerabilities                   | 83 |

|   |      | 5.2.2 Non-unique Binding Solutions                             | 84 |

|   | 5.3  | Reliability-aware Register Binding                             | 84 |

|   |      | 5.3.1 Definitions and Notations                                | 85 |

|   |      | 5.3.2 Register Binding Optimization                            | 86 |

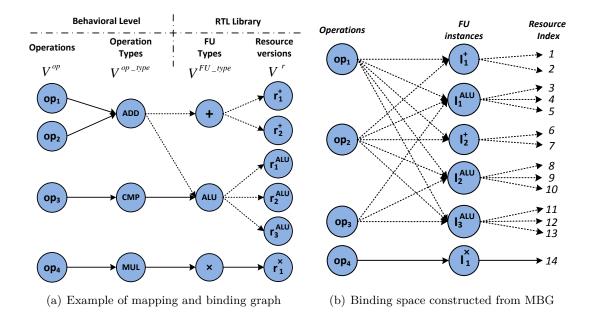

|   | 5.4  | Functional Unit Allocation and Binding                         | 87 |

|   |      | 5.4.1 FU Allocation and Binding Space Determination            | 88 |

|   |      | 5.4.2 Constraints and Objective                                | 90 |

|   |      | 5.4.3 Reliability-aware FU Binding Optimization                | 91 |

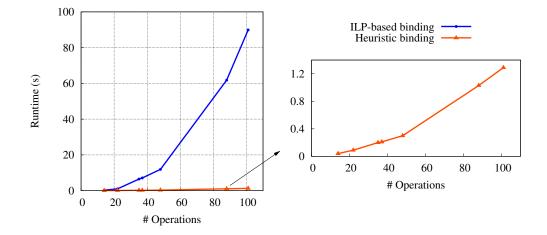

|   | 5.5  | Vulnerability Compaction and Heuristic Resource Binding        | 91 |

|   | 5.6  | Experimental Results                                           | 92 |

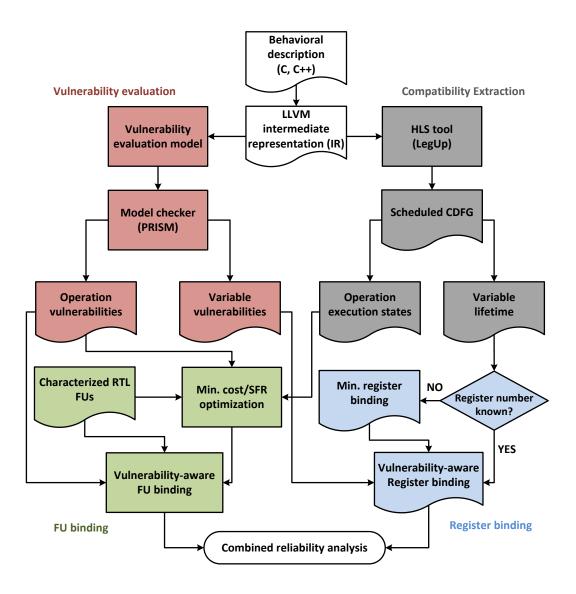

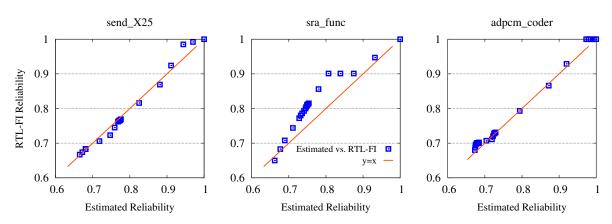

|   |      | 5.6.1 Work Flow                                                | 94 |

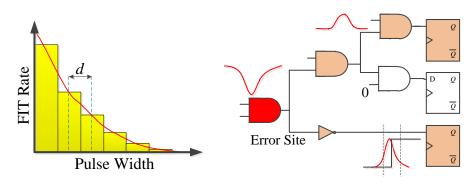

|   |      | 5.6.2 Characterization of the RTL Resources                    | 94 |

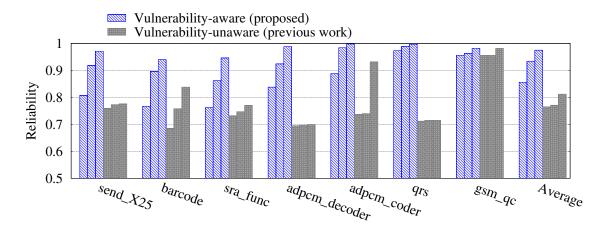

|   |      | 5.6.3 Register Binding Results Analysis                        | 96 |

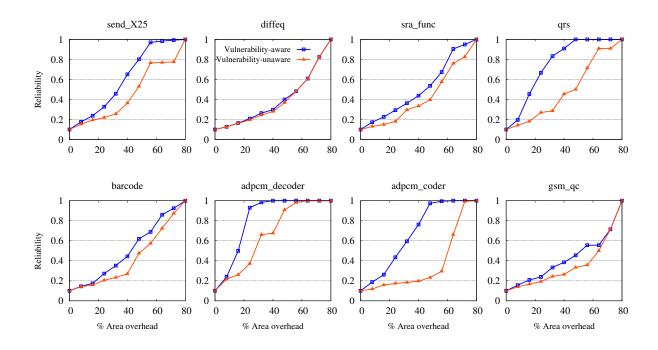

|   |      | 5.6.4 FU Binding Results Analysis                              | 99 |

|     |              | 5.6.5                        | Combined analysis of register and FU binding      | 101 |

|-----|--------------|------------------------------|---------------------------------------------------|-----|

|     | 5.7          | Conclu                       | sion and Summary                                  | 102 |

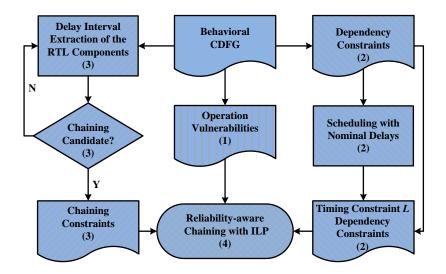

| 6   | Relia        | ability-a                    | ware Operation Chaining                           | 105 |

|     | 6.1          | Introduction                 |                                                   |     |

|     | 6.2          | Preliminaries and Motivation |                                                   |     |

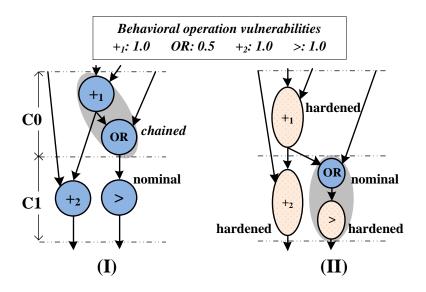

|     |              | 6.2.1                        | Behavioral Design and Reliability Models          | 106 |

|     |              | 6.2.2                        | Reliability-aware Chaining in CFI Designs         | 107 |

|     | 6.3          | Reliabi                      | ility-aware Scheduling and Binding                | 108 |

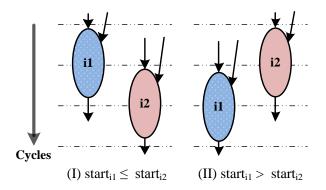

|     |              | 6.3.1                        | Definitions and Notations                         | 108 |

|     |              | 6.3.2                        | Basic Scheduling Constraints                      | 110 |

|     |              | 6.3.3                        | Operation Chaining Constraints                    | 111 |

|     |              | 6.3.4                        | Binding Constraints and Multiplexer Consideration | 113 |

|     |              | 6.3.5                        | Objective                                         | 114 |

|     |              | 6.3.6                        | Heuristic Algorithm                               | 114 |

|     | 6.4          | 5                            |                                                   | 115 |

|     |              | 6.4.1                        | Experimental Setup                                | 115 |

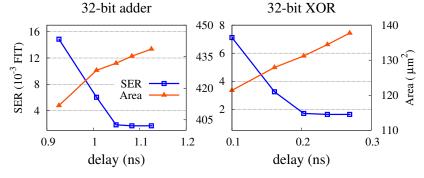

|     |              | 6.4.2                        | RTL Component Library Characterization            | 116 |

|     |              | 6.4.3                        | Results Analysis                                  | 117 |

|     |              | 6.4.4                        | Comparison with Related Work                      | 118 |

|     | 6.5          | Conclu                       | sion and Summary                                  | 119 |

| 7   | Con          | cluding                      | Remarks and Outlook                               | 121 |

| Bil | Bibliography |                              |                                                   |     |

## Glossary

## A | B | C | D | E | F | H | I | L | M | N | P | R | S | T | V

Α

ACE Architecturally Correct Execution.ADPCM Adaptive Differential Pulse Code Modulation.ALU Arithmetic Logic Unit.AVF Architectural Vulnerability Factor.

## В

BB Basic Block.BISER Built-in Soft Error Resilience.

## С

CC Correlation Coefficient.

CCM Correlation Coefficient Method.

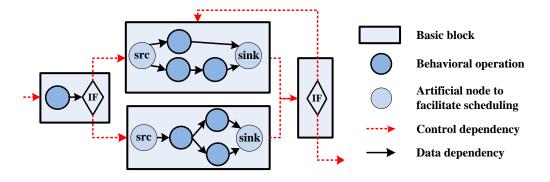

CDFG Control and Data Flow Graph.

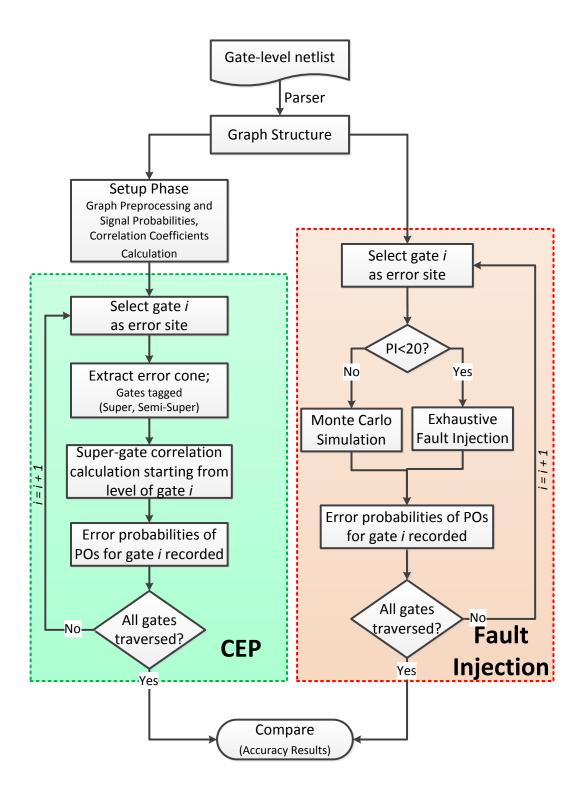

CEP Correlated Error Propagation.

CFI Control Flow Intensive.

CMOS Complementary Metal-Oxide-Semiconductor.

## D

DFG Data Flow Graph.DFI Data Flow Intensive.DFS Depth First Search.DICE Dual Interlock Storage Cells.DTR Data Type Reduction.

## Ε

ECC Error Correction Code.EPF Error Propagation Function.EPP Error Propagation Probability.

## F

FI Fault Injection.FIT Failure in Time.FPE Failures per Execution.FSM Finite State Machine.FU Functional Unit.

#### Н

**HLS** High Level Synthesis.

I

#### Glossary

IC Instruction Cache.ILP Integer Linear Programming.

## L

**LLVM** Low Level Virtual Machine. **LP** Linear Programming.

#### М

MBG Mapping and Binding Graph.

MBU Multi Bit Upset.

MC Monte-Carlo simulation.

MCU Multi Cell Upset.

MDP Markov Decision Process.

MPSoC Multi-Processor System on Chip.

MTTF Mean Time To Failure.

MUX Multiplexer.

#### Ν

${\sf NP}~$  Nondeterministic Polynomial.

#### Ρ

PCC Pearson product-moment Correlation Coefficient.

PI Primary Input.

PMC Probabilistic Model Checking.

PO Primary Output.

PRISM A probabilistic model checker.

#### R

**RAM** Random Access Memory.**RTL** Register-Transfer Level.

## S

SAT Boolean Satisfiability.

SBU Single Bit Upset.

SDG Signal Dependency Graph.

SEE Single Event Effects.

SEL Single Event Latchup.

SER Soft Error Rate.

SET Single Event Transient.

SEU Single Event Upset.

SFI Statistical Fault Injection.

SFR System Failure Rate.

SOI Silicon-On-Insulator.

SP Signal Probability.

$\ensuremath{\mathsf{SPICE}}$  Simulation Program with Integrated Circuit Emphasis.

## т

**TCAD** Technology Computer-Aided Design.

$\ensuremath{\mathsf{TMR}}$  Triple Modular Redundancy.

**TPP** Time-multiplexed PIs Partitioning.

## v

$\ensuremath{\mathsf{VAS}}$  Verification Assisted Simplification.

$\boldsymbol{\mathsf{VCD}}\xspace$  Value Change Dump.

$\label{eq:VLSI} Very\mbox{-}Large\mbox{-}Scale\mbox{ Integration}.$

# List of Figures

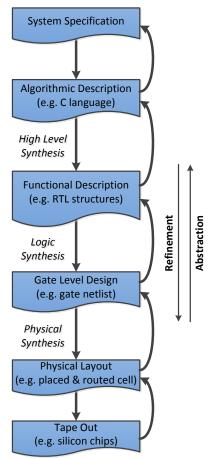

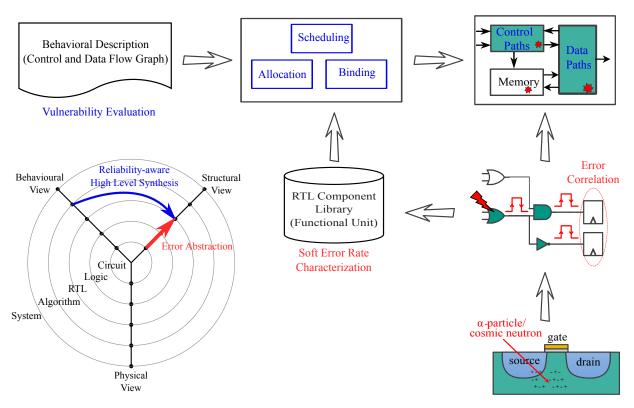

| $1.1 \\ 1.2$ | A typical digital system design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\frac{3}{4}$ |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

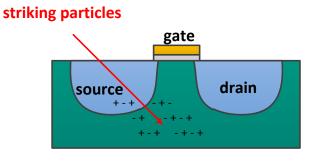

| 2.1          | Particle striking and the induced ionization in a transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8             |

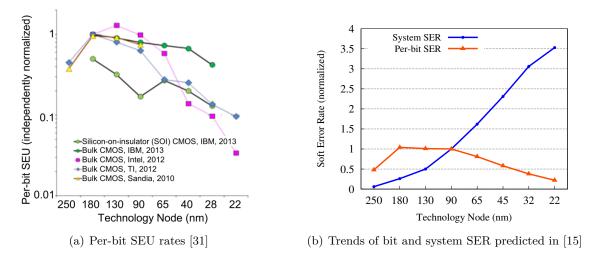

| 2.2          | Soft error trends for SRAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10            |

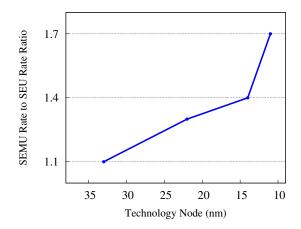

| 2.2<br>2.3   | Single-event multiple upsets (SEMU) rate to SEU rate ratio for the SRAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10            |

| 2.0          | with Silicon-on-Insulator CMOS process [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11            |

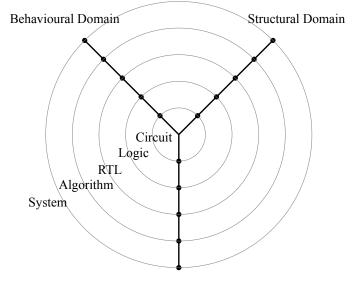

| 2.4          | Gajski-Kuhn chart (Y-chart)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12            |

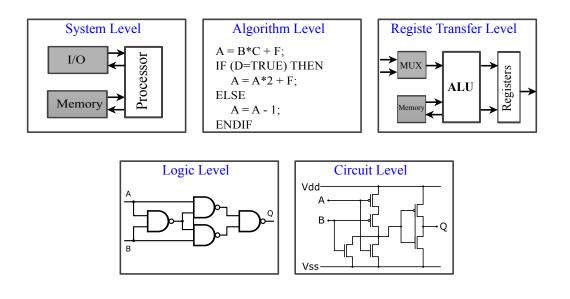

| 2.5          | Illustration of the design at different abstraction levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13            |

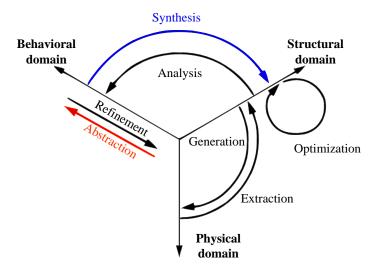

| 2.6          | Y-chart and design activities [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14            |

| 2.7          | Three masking effects in the combinational logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15            |

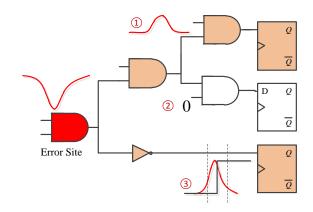

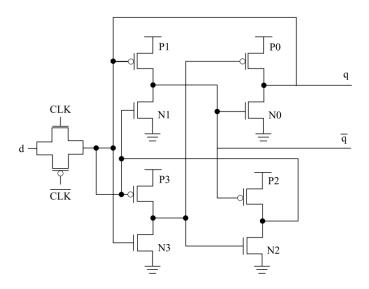

| 2.8          | Schematic of a DICE latch [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17            |

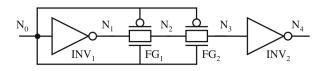

| 2.9          | Transient filter schematic [4] with the Filter Gates (FG) driven by the input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17            |

| 0.10         | node $N_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17            |

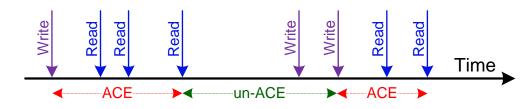

| 2.10         | ACE and un-ACE intervals in the generic ACE analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18            |

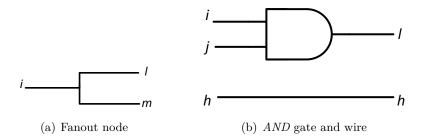

| 3.1          | Typical structures for correlation calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25            |

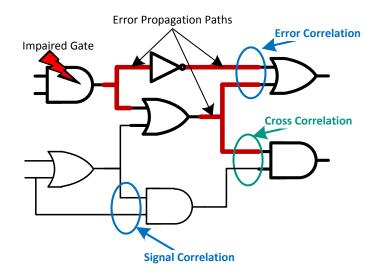

| 3.2          | Different types of correlation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26            |

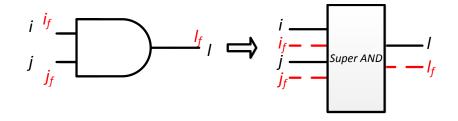

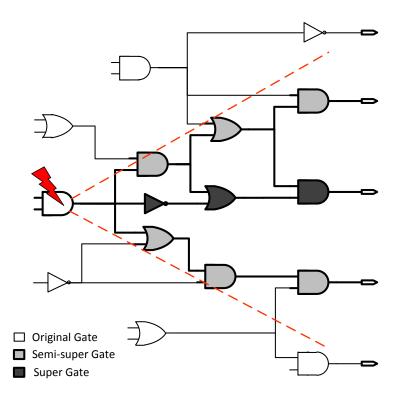

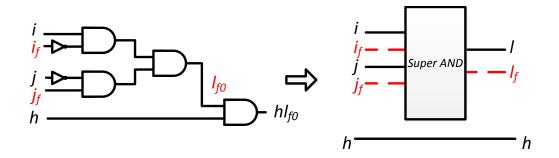

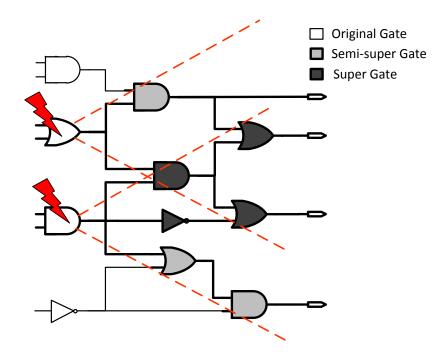

| 3.3          | Super gate representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27            |

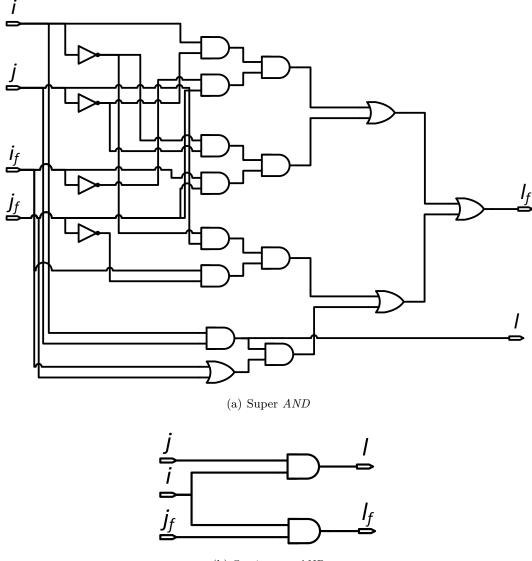

| 3.4          | Super and semi-super AND gate-level implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28            |

| 3.5          | Error propagation paths and error cone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29            |

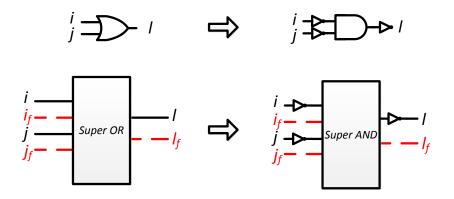

| 3.6          | Super-AND and wire correlation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30            |

| 3.7          | Super-AND equivalent of Super-OR gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31            |

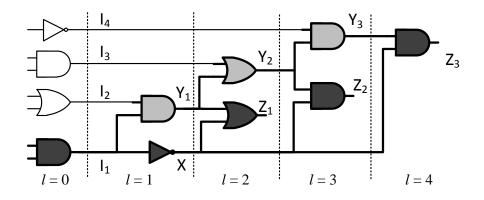

| 3.8          | Correlation reduction with signal/error propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32            |

| 3.9          | Propagation paths with multiple error cones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35            |

| 3.10         | I show of the second seco | 37            |

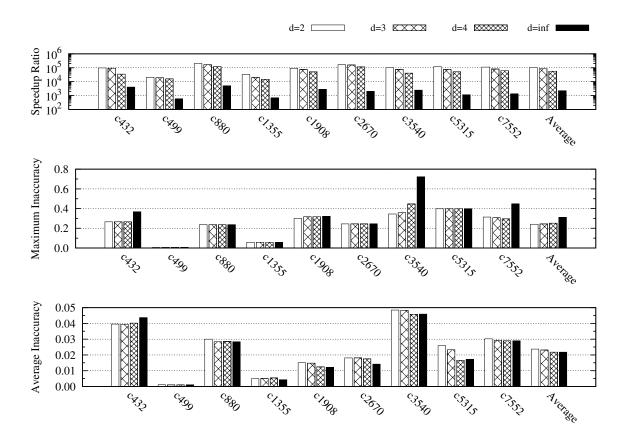

| 3.11         | Speedup, maximum and average inaccuracy for considering variant correlation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

|              | depths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38            |

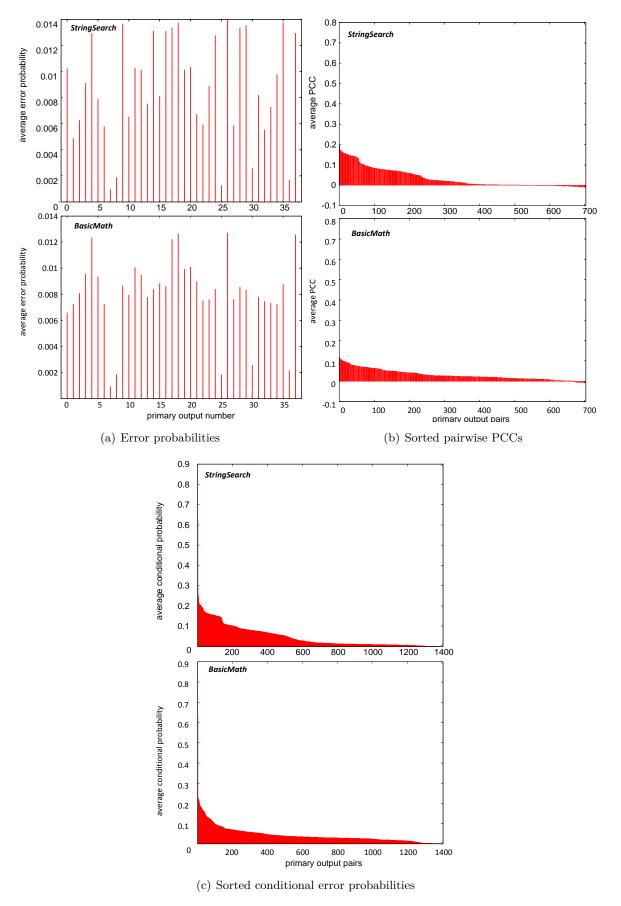

| 3.12         | Primary input statistics of OpenRISC ALU running applications <i>StringSearch</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|              | and BasicMath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41            |

| 3.13         | Error statistics for primary outputs of OpenRISC ALU running applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10            |

|              | StringSearch and BasicMath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42            |

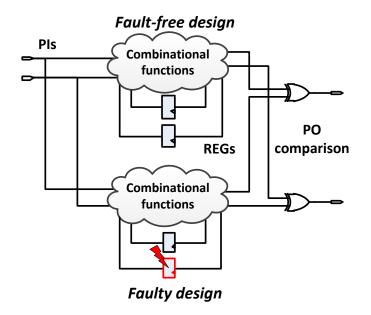

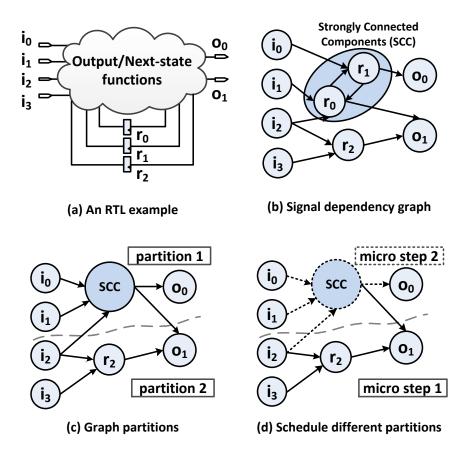

| 4.1          | RTL control and data paths with code examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50            |