## DRAM Aware Last-Level-Cache Policies for Multi-core Systems

zur Erlangung des akademischen Grades eines

### Doktors der Ingenieurwissenschaften

der Fakultät für Informatik der Karlsruher Institut für Technologie (KIT)

genehmigte

### Dissertation

von

### **Fazal Hameed**

Tag der mündlichen Prüfung: 6. Februar 2015

- Referent: Prof. Dr.-Ing. Jörg Henkel, Karlsruher Institut für Technologie (KIT), Fakultät für Informatik, Lehrstuhl für Eingebettete Systeme (CES)

- Korreferent: Prof. Dr. rer.nat. Wolfgang Karl, Karlsruher Institut für Technologie (KIT), Fakultät für Informatik, Lehrstuhl für Rechnerarchitektur und Parallelverarbeitung (CAPP)

### DOI: 10.5445/IR/1000049345

This document is licensed under the Creative Commons Attribution – Share Alike 3.0 DE License (CC BY-SA 3.0 DE): http://creativecommons.org/licenses/by-sa/3.0/de/

Fazal Hameed Luisenstr. 22, 76137 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

# Dedication

To the memory of my beloved late mother, Parveen Subhan. I miss you very much. May your soul rest in eternal peace

## Acknowledgements

This thesis is dedicated to my loving beloved mother, Parveen Subhan, who passed away during the course of my PhD studies. My mother was an everlasting source of inspiration, love, and affection. She prepared me to face the challenges of life with patience and dignity.

I express my sincere gratitude to Professor Dr.-Ing. Jörg Henkel for his guidance in mentoring me during the course of my PhD studies. He taught me the true essence of academic research and motivated me to explore new research ideas and directions. He provided the proper balance of guidance and freedom required to make a smooth progress in research. It has been a more pleasant learning experience to work under his guidance.

I would like to pay my deepest gratitude to Professor Dr-Ing. Wolfgang Karl for his acceptance to become my co-examiner.

I am grateful to my co-supervisor, Dr.-Ing Lars Bauer, whose valuable suggestions and indepth critique feedback during proof reading helped me to complete this work. He has been very friendly and kind to me and his thoughtful reviews significantly improved the quality of my several conference submissions. In addition to the technical support, I explicitly acknowledge his efforts to arrange HiWi and DFG funding to support this work. I would also like to thank my former co-supervisor Dr.-Ing. Mohammad Abdullah Al Faruque who provided me valuable feedback and suggestions while submitting my first paper in Design Automation and Test in Europe (DATE) conference.

I want to thank my colleagues in the Chair of Embedded systems (CES) for their company to provide a congenial and learning work environment for my studies. I would like to thank my office-mates Manyi Wang, Heba Khdr, and Florian Kriebel for their patience and tolerance with me and my jokes. I would like to thank Waheed Ahmed, Nabeel Iqbal and Usman Karim for joining me at the lunch breaks to have some fun. I will never forget the family gathering and sport activities (especially cricket) we have done together on weekends. I would like to thank Martin Buchty, Sammer Srouji, Hussam Amrouch, Artjom Grudnitsky, Martin Haaß, Chih-Ming Hsieh, Sebastian Kobbe, Mohammadi Abbas, Volker Wenzel, and Farzad Samie for their wonderful company during my stay at CES.

I am also grateful to Institute of Space Technology (IST) and German Research Foundation (DFG) for providing the financial support to complete this work.

Finally, I am specially thankful to my father Fazal Subhan and wife Rozina Khan for their encouragement, patience, and prayers during my PhD. studies. I especially thank my wife for her continued moral support and sacrifices when I felt dejected and depressed.

"Ideally one would desire an indefinitely large memory capacity such that any particular [...] word would be immediately available [...] It does not seem possible physically [...]. We are therefore forced to recognize the possibility of constructing a hierarchy of memories, each of which has greater capacity than the preceding but which is less quickly accessible."

A.W. Burks, H.H. Goldstine, and J. von Neumann - 1946

## **List of Publications**

#### **Conferences (double-blind peer reviewed)**

- [C.1] F. Hameed, L. Bauer, and J. Henkel, "Reducing Latency in an SRAM/DRAM Cache Hierarchy via a Novel Tag-Cache Architecture", In *IEEE/ACM Design Automation Conference (DAC'14)*, June, 2014.

- [C.2] F. Hameed, L. Bauer, and J. Henkel, "Reducing Inter-Core Cache Contention with an Adaptive Bank Mapping Policy in DRAM Cache", In *IEEE International Conference on Hard-ware/Software Codesign and System Synthesis (CODES+ISSS'13)*, October 2013.

#### Nominated for the best paper.

- [C.3] F. Hameed, L. Bauer, and J. Henkel, "Simultaneously Optimizing DRAM Cache Hit Latency and Miss Rate via Novel Set Mapping Policies", In *International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES'13)*, October 2013.

- [C.4] F. Hameed, L. Bauer, and J. Henkel, "Adaptive Cache Management for a Combined SRAM and DRAM Cache Hierarchy for Multi-Cores", In *Proceedings of the 16<sup>th</sup> conference on Design, Automation and Test in Europe (DATE'13)*, pages 77–82, March 2013.

- [C.5] F. Hameed, L. Bauer, and J. Henkel, "Dynamic Cache Management in Multi-Core Architectures through Run-time Adaptation", In *Proceedings of the 15<sup>th</sup> conference on Design, Automation and Test in Europe (DATE'12)*, pages 485–490, March 2012.

- [C.6] F. Hameed, M.A. Al Faruque, and J. Henkel, "Dynamic Thermal Management in 3D Multi-core Architecture Through Run-Time Adaptation", In *Proceedings of the 14<sup>th</sup> conference on Design*, *Automation and Test in Europe (DATE'11)*, pages 299–304, March 2011.

#### **PhD Forum**

[P.1] F. Hameed, L. Bauer, and J. Henkel, "DRAM Aware Last Level Cache Policies for Multi-Core Systems", In 17<sup>th</sup> conference on Design, Automation and Test in Europe (DATE), March 2014.

## **The Big Picture**

The Chair for Embedded Systems (CES) at the Karlsruhe Institute of Technology (KIT) provided me the required research platform and infrastructure to complete my thesis. The people at CES are primarily involved in research in the field of Design and Architectures for Embedded Systems. A current focus of research are multi-core systems, dependability, and low power design. I worked in the multi-core research group with a focus on cache and processor architectures leveraging the application access patterns to achieve performance and reliability goals.

The CES is involved in various projects of the DFG Transregional Collobarative Research Center (TCRC) 89 "Invasive Computing" [44, 122]. This collaboration between various departments at KIT (including the CES), Technische Universität München (TUM), and University of Erlangen (FAU), aimed to investigate a novel paradigm for the design and resource aware programming of future parallel computing systems. This scientific team includes experts in algorithms for parallel algorithm design, hardware architects for multi-core system development as well as language, compiler, application and operating system designers. The key idea of invasive computing is to develop resource aware programming support so that programs are given the capability to dynamically spread its computations over a dynamic area in the multi-core systems similar to a phase of invasion. This requires revolutionary changes in architecture, programming languages, compilers, operating systems, and design of multi-core systems to effectively enable resource aware programming for various processor and memory configurations. I primarily contributed to the "Invasive Computing" research project by introducing novel architectural concepts in the multi-core cache hierarchy [C.1][C.2][C.3][C.4][C.5]. The proposed architectural techniques aimed to develop efficient run-time hardware techniques to exploit the full potential of the multi-core cache hierarchy.

The CES also makes significant contributions to the DFG SPP 1500 "Dependable Embedded Systems" projects. The key idea of SPP 1500 research project is to address the increasing dependability and reliability issues in future nano-scale technologies [41] due to device aging, high chip power densities, and process variation. The SPP aimed to develop reliability aware mechanisms at both the hardware level (i.e., architecture and micro-architecture), and software level (i.e. compilers, operating system, and application). The SPP 1500 comprises various individual sub-projects, working synergistically to develop reliability modeling and aging mitigation techniques based on the future technology trends [42]. The major challenges addressed by SPP 1500 include dark silicon and thermal challenges [43, 110]. One of the key contributions of the CES towards SPP 1500 is the "VirTherm-3D" research project is to address dependability problems in 3D stacked many-core architectures resulting from extreme temperatures. I also contributed to the VirTherm-3D project by proposing an efficient processor architecture and designed different components of processing cores (arithmetic units, register file, instruction scheduler, cache, reorder buffer, etc.) for performance, power and thermal improvement [C.6].

## Abstract

In addition to fast and small L1 and L2 caches, that are typically dedicated to a particular core in multi-core systems, the larger so-called Last-Level-Cache (LLC) is shared among all cores and used to bridge the latency gap between high speed cores and slower off-chip main memory. Traditionally, the LLC in multi-core systems consists of on-chip SRAM memory which comes at a large area overhead that limits the LLC size. As multi-core systems employ more and more cores on a single chip, the limited LLC size leads to an increasing number of off-chip memory accesses. This increases the average latency per access which reduces the overall performance. Therefore, recent research in academia and industry (e.g. IBM POWER7) has employed high capacity on-chip DRAM as LLC between L1/L2 SRAM cache and main memory. The primary reason for employing on-chip DRAM cache is that it provides greater capacity benefits for a given area compared to SRAM cache (~8×), which reduces off-chip accesses.

When the DRAM cache is shared among multiple cores, the cores might interfere with each other in the DRAM cache controller causing inter-core interference that increases DRAM cache hit latency. The problem is exacerbated, when one core evicts useful data belonging to another core causing inter-core cache eviction that increases DRAM cache miss rate. This thesis primarily focuses on reducing DRAM cache miss rate and DRAM cache hit latency via novel application-aware and DRAM-aware cache policies while addressing the above mentioned challenges. This thesis makes the following novel contributions:

- Different applications have different cache access behavior that make them better suited to

use different DRAM insertion rates (DRAM insertion rate is defined as the percentage of data

insertions into DRAM cache). To choose a suitable insertion rate at runtime, this thesis proposes an adaptive DRAM insertion policy that mitigates inter-core cache eviction by adapting

the DRAM insertion rate in response to the dynamic requirements of the individual applications with different cache access behaviors. The proposed policy selects a suitable insertion

rate from multiple insertion rates depending on which insertion rate provides reduced off-chip

memory accesses.

- 2. To further mitigate the miss rate, this work proposes a DRAM set balancing policy after analyzing that DRAM accesses are not evenly distributed across the sets of the DRAM cache, which leads to increased conflict misses via unbalanced set utilization. The proposed set balancing policy reduces conflict misses via reduced inter-core cache eviction that lead to a reduced miss rate, hereby improving the overall system performance.

- 3. DRAM row-buffer conflicts occurs, when multiple simultaneous requests are mapped to different rows of the same DRAM bank, causing high DRAM cache hit latency compared to a scenario when these requests are mapped to the same row. To reduce DRAM cache hit latency, this thesis proposes a novel DRAM row buffer mapping policy that reduces row buffer conflicts by exploiting data access locality in the row buffer.

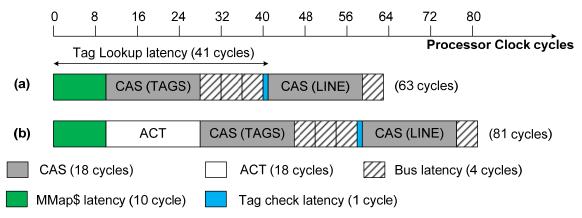

- 4. To further reduce the DRAM cache hit latency, this thesis proposes a small and low latency SRAM structure namely DRAM Tag-Cache (*DTC*) that holds the tags of rows that were recently accessed in the DRAM cache. The proposed *DTC* has a high hit rate, because it exploits data access locality provided by the proposed DRAM row buffer mapping policy mentioned above. It provides fast tag lookup because for a *DTC* hit, it reads the tags from the low

latency *DTC* in two cycles. In contrast, state-of-the-art DRAM cache always reads the tags from DRAM cache that incurs high tag lookup latencies of up to 41 cycles.

In summary, high DRAM cache hit latencies, increased inter-core interference, increased inter-core cache eviction, and the large application footprint of complex applications necessitates efficient policies in order to satisfy the diverse requirements to improve the overall throughput. This thesis addresses how to design DRAM caches to reduce DRAM cache hit latency, DRAM cache miss rate and hardware cost, while taking into account both application and DRAM characteristics by presenting novel DRAM and application aware policies. The proposed policies are evaluated for various applications from SPEC2006 using a cycle accurate multi-core simulator based on SimpleScalar that is modified to incorporate DRAM in the cache hierarchy. The combination of the proposed DRAM-aware and application-aware complementary policies improve the average performance of latency-sensitive applications by 47.1% and 35% for an 8-core system compared to [102] and [77] respectively while requiring 51% less hardware overhead.

## Zusammenfassung

Neben schnellen und kleinen L1- und L2-Caches, die in Mehrkernsystemen typischerweise einem bestimmten Kern fest zugeordnet sind, wird der größere sogenannte Last-Level-Cache (LLC) von allen Kernen gemeinsam genutzt und wird verwendet, um die unterschiedlichen Latenzen von Kernen mit hoher Geschwindigkeit und dem langsameren externen Hauptspeicher zu überbrücken. Traditionellerweise besteht der LLC in Mehrkernsystemen aus einem on-chip SRAM-Speicher, der einen hohen Flächenverbrauch mit sich bringt, welcher die Größe des LLC begrenzt. Da Mehrkernsysteme immer mehr Kerne auf einem einzelnen Chip integrieren, führt die begrenzte LLC-Größe zu einer steigenden Anzahl von off-chip Speicherzugriffen. Dies erhöht die durchschnittliche Latenz pro Zugriff, was die Gesamtleistungsfähigkeit reduziert. Deshalb verwenden jüngste Forschungen in Akademie und Industrie (z.B. IBM POWER7) onchip DRAM mit hoher Kapazität als LLC zwischen L1/L2 SRAM Cache und dem Hauptspeicher. Der primäre Grund für die Nutzung eines on-chip DRAM Caches ist, dass dieser im Vergleich zu SRAM Cache höhere Kapazitätsvorteile für eine festgelegte Fläche erreicht (~8×), wodurch die off-chip Zugriffe reduziert werden.

Wenn der DRAM Cache von mehreren Kernen gemeinsam genutzt wird, könnten die Kerne sich im DRAM Cachecontroller gegenseitig beeinflussen und Inter-Kern-Interferenzen verursachen, welche die Cache-Hitlatenz erhöhen. Das Problem verschlimmert sich, wenn ein Kern nützliche Daten verdrängt die einem anderen Kern gehören und damit eine Inter-Kern-Cacheverdrängung verursacht, welche die DRAM Cache Missrate erhöht. In dieser Arbeit liegt der Schwerpunkt auf der Verringerung der DRAM Cache Missrate und der DRAM Cache neue applikationsund DRAM-bewusste Hitlatenz durch Cacherichtlinien unter Berücksichtigung der oben genannten Herausforderungen. Diese Arbeit leistet die folgenden neuen Beiträge:

- Verschiedene Applikationen haben unterschiedliches Cachezugriffsverhalten, wodurch sich verschiedene DRAM Einfügungsraten besser eignen (die DRAM Einfügungsrate ist definiert als der Anteil der vom Hauptspeicher zu einem Kern gebrachten Daten, die auch in den DRAM Cache eingefügt wird). Um zur Laufzeit eine geeignete Einfügungsrate zu wählen, schlägt diese Arbeit eine adaptive DRAM Einfügungsrate als Antwort auf die dynamischen Anforderungen der einzelnen Applikationen mit unterschiedlichem Cachezugriffsverhalten reduziert. Die vorgeschlagene Richtlinie wählt aus mehreren Einfügungsraten eine geeignete aus – abhängig davon welche Rate eine Verringerung der off-chip Speicherzugriffe liefert.

- 2. Nach der Analyse, dass DRAM Zugriffe nicht gleichmäßig über die Sätze (Sets) des DRAM Caches verteilt sind, was zu einem Anstieg der durch Konflikte verursachten Cache Misses durch unbalancierte Satznutzung führt, schlägt diese Arbeit eine DRAM Satzbalancierungsrichtlinie vor, um die Missrate weiter zu verringern. Sie reduziert die durch Konflikte verursachten Cache Misses durch Verringerung der Inter-Kern-Cacheverdrängung, was zu einer geringeren Missrate führt, und verbessert damit die Gesamtleistung des Systems.

- 3. DRAM Zeilenpufferkonflikte treten auf, wenn mehrere gleichzeitige Anfragen auf verschiedene Zeilen derselben DRAM Bank abgebildet werden, was eine hohe DRAM Cache Hitlatenz zur Folge hat (verglichen mit dem Fall, dass diese Anfragen auf dieselbe Zeile

abgebildet worden wären). Um die DRAM Cache Hitlatenz zu verringern schlägt diese Arbeit eine neuartige Richtlinie zur DRAM Zeilenpufferabbildung vor, welche die Zeilenpufferkonflikte durch Ausnutzen von Datenzugriffslokalität im Zeilenpuffer verringert.

4. Um die DRAM Hitlatenz weiter zu verbessern schlägt diese Arbeit eine kleine SRAM Struktur mit geringer Latenz namens DRAM Tag-Cache (DTC) vor, welche die Tags der Zeilen enthält, auf die kürzlich im DRAM Cache zugegriffen wurde. Der DTC hat eine hohe Hitrate, da er die Datenzugriffslokalität nutzt, welche von der oben genannten vorgeschlagenen Richtlinie zur DRAM Zeilenpufferabbildung bereitgestellt wird. Er ermöglicht ein schnelles Nachschlagen des Tags, da für einen DTC Hit der Tag innerhalb von zwei Zyklen aus dem DTC gelesen werden kann. Im Gegensatz dazu werden bei derzeitigen DRAM Caches die Tags immer aus dem DRAM Cache gelesen, was eine hohe Tag-Nachschlagelatenz von bis zu 41 Zyklen mit sich bringt.

Zusammenfassend lässt sich feststellen, dass eine hohe DRAM Cache Hitlatenz, gestiegene Inter-Kern-Interferenz, gestiegene Inter-Kern-Cacheverdrängung und der große Bedarf von komplexen Applikationen effiziente Richtlinien notwendig machen, um die verschiedenen Anforderungen zur Verbesserung des Gesamtdurchsatzes zu erfüllen. Diese Arbeit behandelt das Design von DRAM Caches zur Reduzierung der DRAM Cache Hitlatenz, DRAM Cache Missrate und Hardwarekosten, wobei sowohl die Eigenschaften der Applikationen als auch die des DRAM durch neuartige DRAM- und applikationsbewusste Richtlinien berücksichtigt werden. Die vorgeschlagenen Richtlinien wurden für verschiedene Applikationen aus der SPEC2006 Benchmarksuite mit Hilfe eines zyklenakkuraten Mehrkernsimulators bewertet, der auf SimpleScalar basiert und modifiziert wurde, um DRAM in die Cachehierarchie zu integrieren. Die Kombination aus den vorgeschlagenen und sich ergänzenden DRAM- und applikationsbewussten Richtlinien verbessert die durchschnittliche Leistung von latenzsensitiven Applikationen um 47,1% und 35% für ein 8-Kern System verglichen mit [98] und [73], wobei ein um 51% geringerer Hardwareaufwand notwendig ist.

# Contents

| Dedica  | tion     |                                                  | i     |

|---------|----------|--------------------------------------------------|-------|

| Ackno   | wledge   | ments                                            | i     |

| List of | Public   | ations                                           | V     |

| The Bi  | g Pictu  | re                                               | vii   |

|         | -        |                                                  |       |

|         |          |                                                  |       |

|         |          | ssung                                            |       |

| Conte   | ents     |                                                  | xiii  |

| List of | Figure   | S                                                | xvii  |

| List of | Tables   |                                                  | xxi   |

| Abbre   | viation  | S                                                | xxiii |

| Chant   | er 1 Int | roduction                                        |       |

| 1.1     |          | On-chip DRAM cache?                              |       |

|         | •        | Benefits of On-Chip DRAM cache                   |       |

| 1.2     |          | enges in DRAM Cache Hierarchy                    |       |

|         | 1.2.1    | Inefficient resource allocation                  | 5     |

|         | 1.2.2    | Limited row buffer hit rate                      | 5     |

|         | 1.2.3    | High tag lookup latency                          | 5     |

|         | 1.2.4    | High Hardware cost                               | 5     |

| 1.3     | Thesi    | s Contribution                                   | 5     |

| 1.4     | Thesi    | s Outline                                        | 6     |

| Chapte  | er 2 Ba  | ckground and Related Work                        | 9     |

| 2.1     | Cache    | e Basics and Terminology                         | 9     |

|         | 2.1.1    | Least Recently Used (LRU) Replacement Policy     | 12    |

|         | 2.1.2    | Multi-level Cache Hierarchies                    | 13    |

| 2.2     | DRA      | M Cache                                          | 14    |

|         | 2.2.1    | Physical Realization                             | 14    |

|         | 2.2.2    | DRAM Organization                                | 15    |

|         | 2.2.3    | Tag-Store Mechanism                              | 16    |

| 2.3     | Impor    | rtant Application and DRAM Cache Characteristics | 17    |

|        | 2.3.1 Inter-core Cache Contention                     |    |

|--------|-------------------------------------------------------|----|

|        | 2.3.2 Inter-core DRAM Interference in the DRAM cache  |    |

|        | 2.3.3 Impact of Associativity                         |    |

|        | 2.3.4 Impact of Row Buffer Mapping                    | 19 |

|        | 2.3.5 Impact of cache line size                       | 19 |

| 2.4    | State-of-the-art DRAM Cache                           |    |

|        | 2.4.1 LH-Cache [73, 74]                               |    |

|        | 2.4.2 MMap\$ Organization                             |    |

|        | 2.4.3 Alloy-Cache [98]                                |    |

|        | 2.4.4 Further Related Work in block-based DRAM Caches |    |

|        | 2.4.5 Page-based DRAM Caches                          |    |

|        | 2.4.6 Distinction with the state-of-the-art           |    |

| Chapte | r 3 Overview of Proposed Policies                     |    |

| 3.1    | Adaptive DRAM Insertion Policy                        |    |

| 3.2    | Set Balancing Policy                                  |    |

| 3.3    | DRAM Row Buffer Mapping Policy                        |    |

| 3.4    | Tag Cache Design                                      |    |

| 3.5    | Super-block MMap\$ (SB-MMap\$)                        |    |

| 3.6    | Summary                                               |    |

| Chapte | r 4 Experimental Setup                                |    |

| 4.1    | Simulation Infrastructure                             |    |

| 4.2    | Simulation Parameters                                 |    |

| 4.3    | Benchmarks and classification                         | 40 |

| 4.4    | Simulation Methodology                                | 40 |

| 4.5    | Performance Metric                                    |    |

| Chapte | r 5 Policies for Miss Rate Reduction                  |    |

| 5.1    | Motivation                                            |    |

| 5.2    | Adaptive DRAM Insertion Policy (ADIP)                 | 45 |

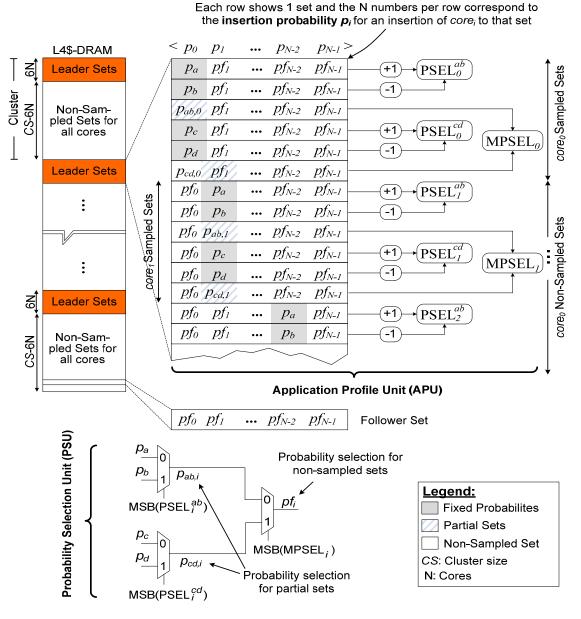

|        | 5.2.1 Application Profiling Unit (APU)                | 46 |

|        | 5.2.2 Probability Selection Unit (PSU)                | 47 |

|        | 5.2.3 Probability Realization                         | 48 |

| 5.3    | Set Balancing Policy (SB-Policy)                      |    |

|        | 5.3.1 Row Assignment                                  | 50 |

| 5.4    | Implementation                                        | 51 |

| 5.5    | Overhead                                              | 52 |

| 5.6    | Experimental Results                                  |    |

|       | 5.6.1    | ADIP and SB-policy on top of LH-Cache [74]              | 52 |

|-------|----------|---------------------------------------------------------|----|

|       | 5.6.2    | Impact on DRAM cache bandwidth and capacity utilization |    |

|       | 5.6.3    | Impact on miss rate                                     |    |

|       | 5.6.4    | -                                                       |    |

|       | 5.6.5    | ADIP and SB-policy on top of Alloy-Cache [98]           |    |

|       | 5.6.6    | Impact of Set Balancing Policy (SB-policy)              |    |

| 5.7   | ' Sumn   | nary                                                    |    |

| Chapt | er 6 Pol | icies for Latency Reduction                             | 59 |

| 6.1   |          | ems of the State-of-the-art                             |    |

| 6.2   | Propo    | sed SRAM/DRAM Cache Organization                        | 61 |

| 6.3   | -        | M Row Buffer Mapping Policies                           |    |

|       | 6.3.1    |                                                         |    |

|       |          | (RBM-A7)                                                | 63 |

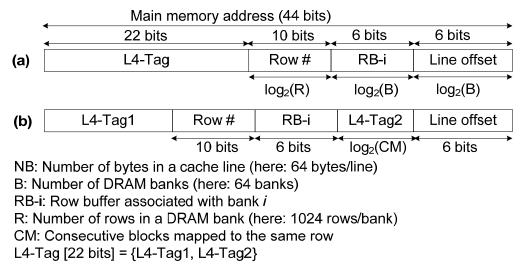

|       | 6.3.2    | Configurable Row Buffer Mapping Policy (CRBM)           | 64 |

|       | 6.3.3    |                                                         |    |

|       | 6.3.4    | Comparisons of different row buffer mapping policies    | 71 |

|       | 6.3.5    | Impact of parameter CM                                  |    |

| 6.4   | Super    | -block MMap\$ (SB-MMap\$)                               | 72 |

|       | 6.4.1    | Impact of super-block size on storage reduction         | 74 |

| 6.5   | Innov    | ative Tag-Cache Organization for larger caches          | 74 |

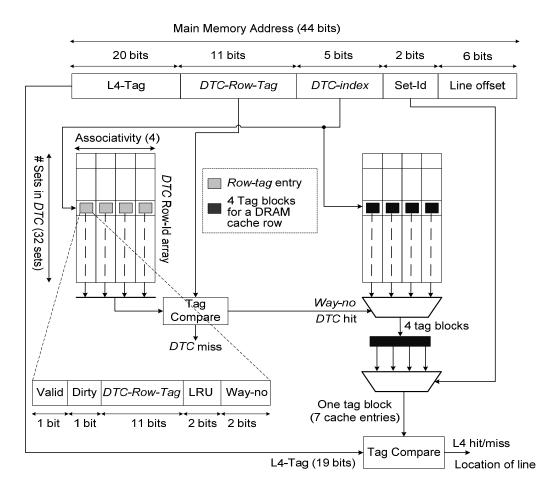

|       | 6.5.1    | DRAM Tag-Cache (DTC) Organization                       | 74 |

|       | 6.5.2    | DTC Implementation with SB-MMap\$                       | 76 |

|       | 6.5.3    | Writing tag-blocks for a <i>DTC</i> hit                 | 77 |

|       | 6.5.4    | DTC organization for RBM-A7 policy                      | 79 |

|       | 6.5.5    | SRAM Tag-Cache (STC) Organization                       | 81 |

| 6.6   | Storag   | ge Overhead                                             | 82 |

| 6.7   | ' Evalu  | ation and Analysis                                      | 82 |

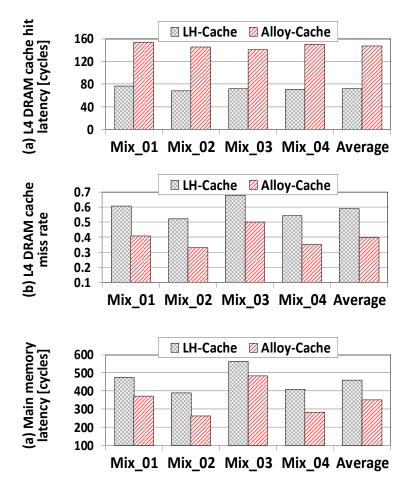

|       | 6.7.1    | Impact on L4 DRAM miss rate                             | 84 |

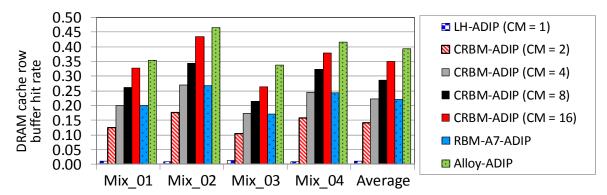

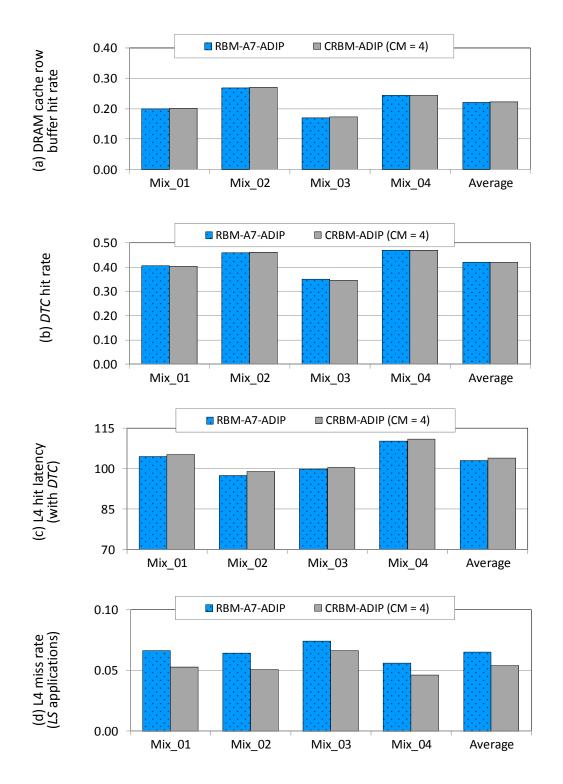

|       | 6.7.2    | Impact on the L4 DRAM row buffer hit rate               | 85 |

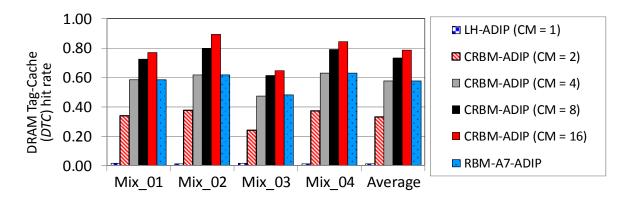

|       | 6.7.3    | Impact on the DTC hit rate                              | 86 |

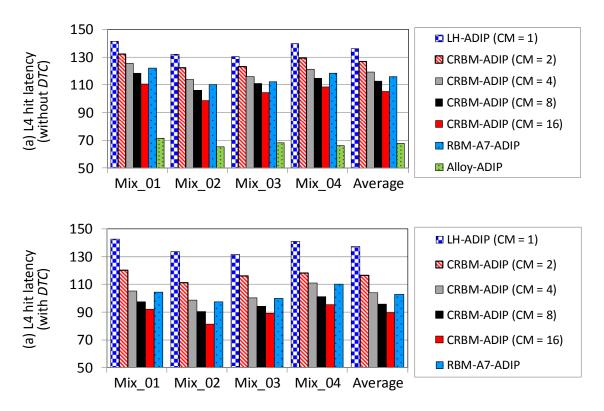

|       | 6.7.4    | Impact on the L4 DRAM hit latency                       | 86 |

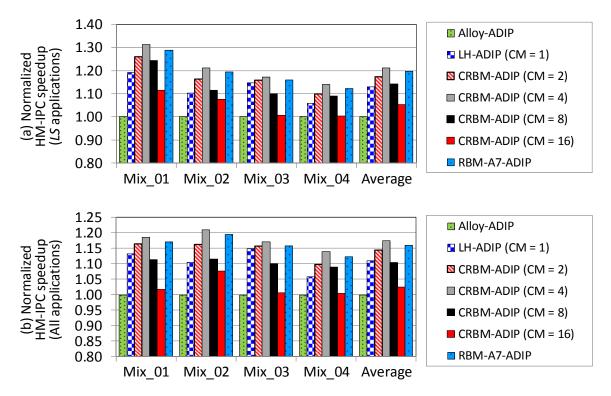

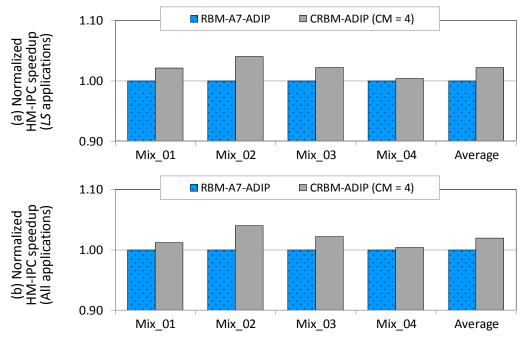

|       | 6.7.5    | Performance improvement without DTC                     | 87 |

|       | 6.7.6    | Performance improvement with DTC                        | 88 |

|       | 6.7.7    | Comparison of proposed policies                         | 89 |

| 6.8   | 8 Evalu  | ating CRBM policy                                       | 91 |

|       | 6.8.1    | Impact of row buffer mapping policy                     | 91 |

|       | 6.8.2    | Impact of Tag-Cache on performance                      | 91 |

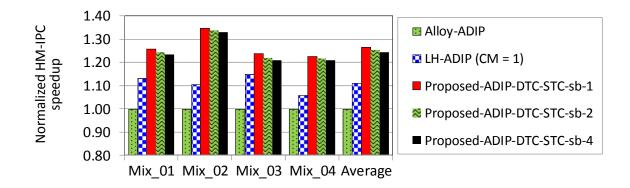

|         | 6.8.3 Impact of the super-block size on performance          | . 92 |

|---------|--------------------------------------------------------------|------|

| 6.9     | Summary                                                      | . 94 |

| Chapte  | r 7 Putting It All together: DRAM Last-Level-Cache Policies  | . 95 |

| 7.1     | Evaluation                                                   | . 96 |

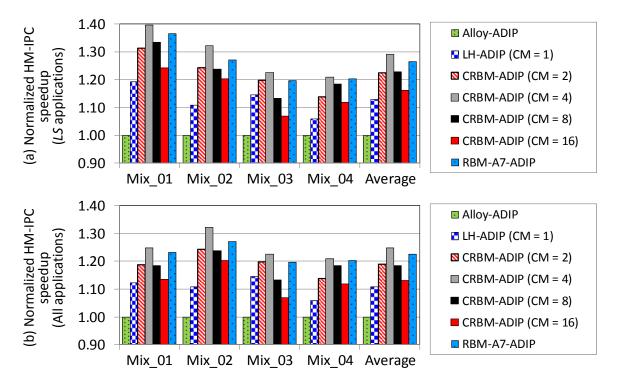

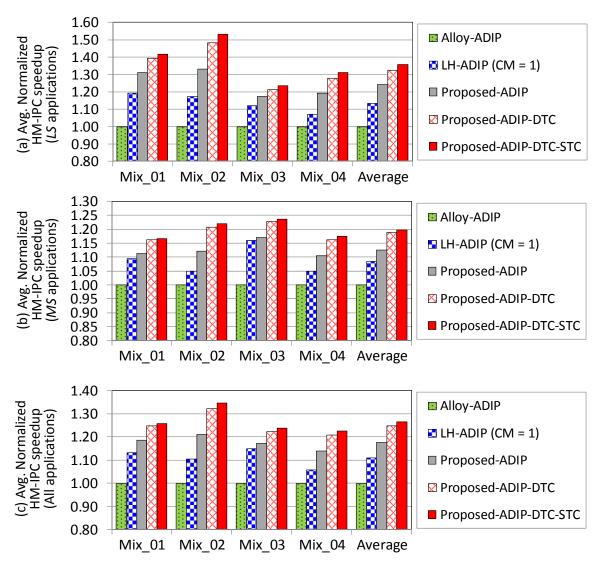

|         | 7.1.1 Performance benefits                                   | . 97 |

|         | 7.1.2 DRAM Aware Last-Level-Cache Policies are complementary | . 98 |

| 7.2     | Result analysis                                              | . 98 |

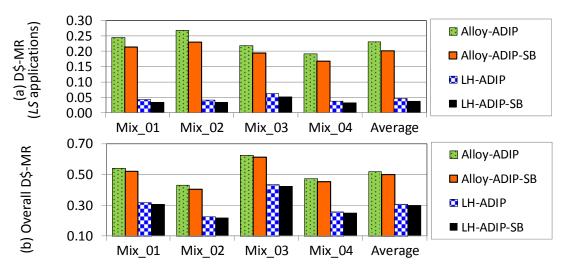

|         | 7.2.1 Miss rate reduction                                    | . 98 |

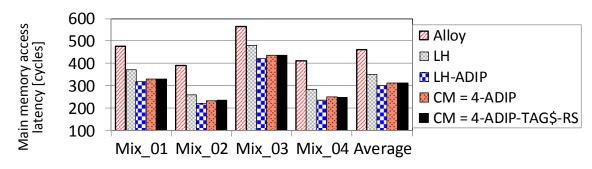

|         | 7.2.2 Off-chip memory latency reduction                      | . 99 |

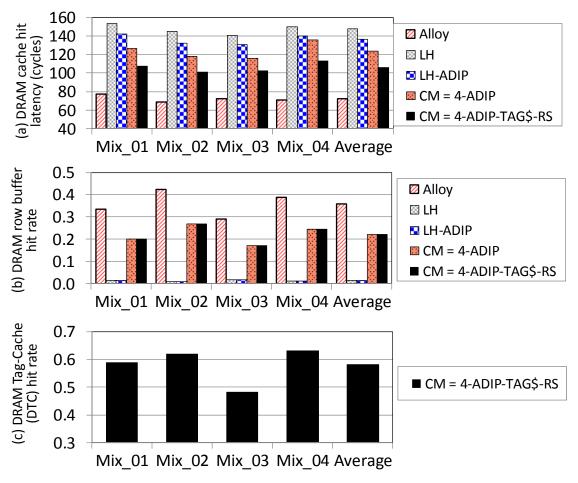

|         | 7.2.3 L4 DRAM hit latency reduction                          | . 99 |

| 7.3     | Summary                                                      | 101  |

| Chapte  | r 8 Conclusion and Outlook                                   | 103  |

| 8.1     | Thesis Summary                                               | 103  |

| 8.2     | Future Work                                                  | 105  |

| Bibliog | raphy                                                        | 107  |

# **List of Figures**

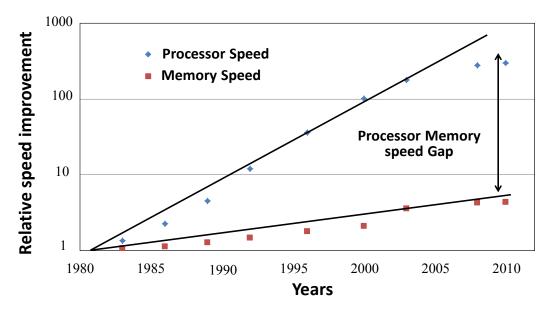

| Figure 1.1:  | Processor memory speed gap over the past 30 years [12]                                                                                            | 1  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

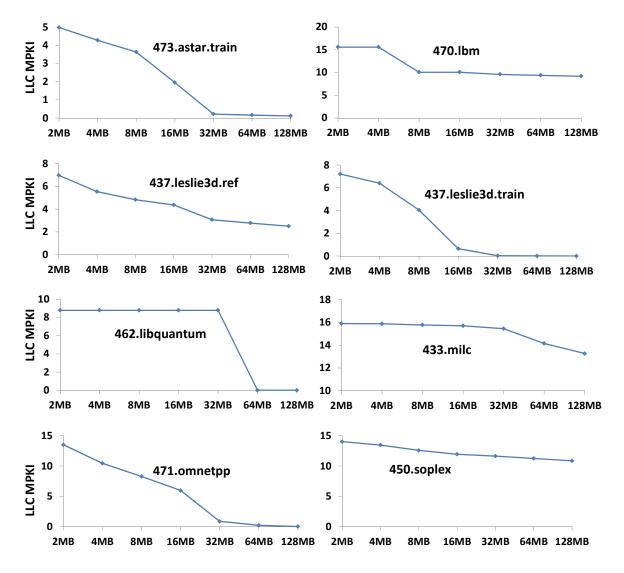

| Figure 1.2:  | LLC misses per thousand instructions (LLC MPKI) for different<br>SPEC2006 [5] applications                                                        | 3  |

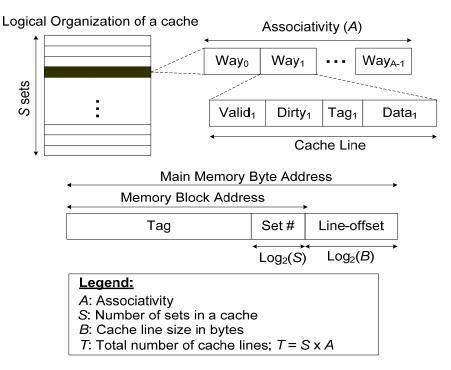

| Figure 2.1:  | A logical cache organization                                                                                                                      | 9  |

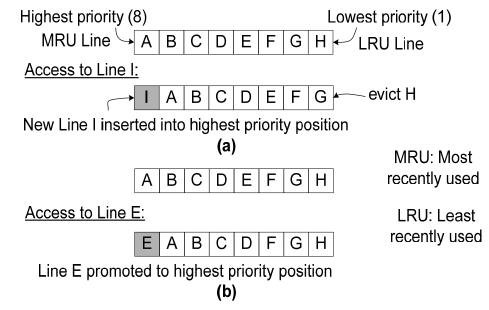

| Figure 2.2:  | Example illustrating LRU replacement policy for an 8-way associative cache (i.e. $A = 8$ ) (a) Insertion and eviction Policy (b) Promotion Policy | 12 |

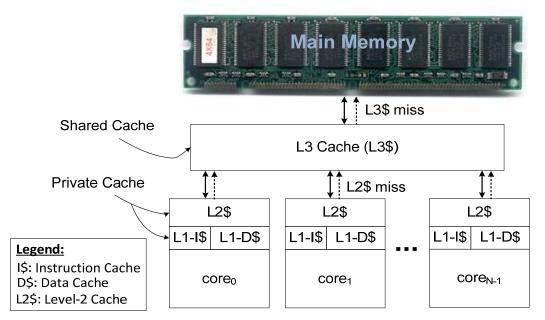

| Figure 2.3:  | A typical three-level multi-core cache hierarchy                                                                                                  | 13 |

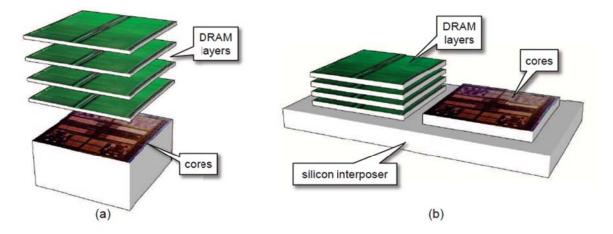

| Figure 2.4:  | Die-stacked DRAM with multi-core chip [73, 74] implemented as (a) a vertical stack (b) silicon interposer                                         | 14 |

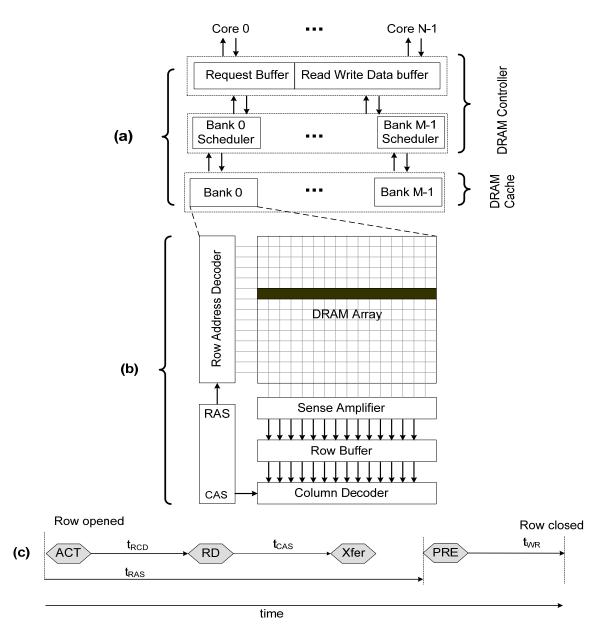

| Figure 2.5:  | (a) DRAM organization (b) DRAM bank organization (c) Timing diagram<br>for a DRAM bank access                                                     | 16 |

| Figure 2.6:  | Example showing inter-core cache contention between thrashing and non-<br>thrashing applications                                                  | 18 |

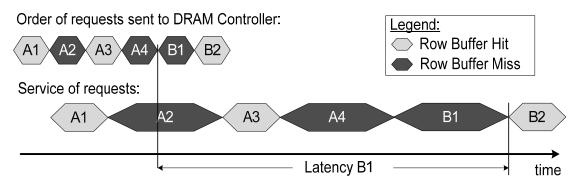

| Figure 2.7:  | Example showing inter-core interference at the DRAM bank                                                                                          | 18 |

| Figure 2.8:  | LH-Cache Cache Organization with Tags-In-DRAM for 2KB row size [73, 74]                                                                           | 21 |

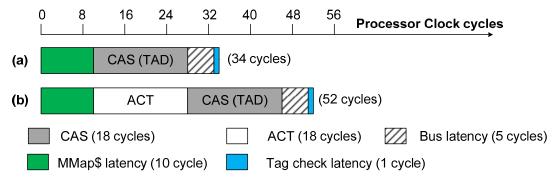

| Figure 2.9:  | LH-Cache (a) row buffer hit latency (b) row buffer miss latency for 2KB row size with $T = 3$ and $A = 29$                                        | 21 |

| Figure 2.10: | LH-Cache row buffer mapping policy                                                                                                                | 22 |

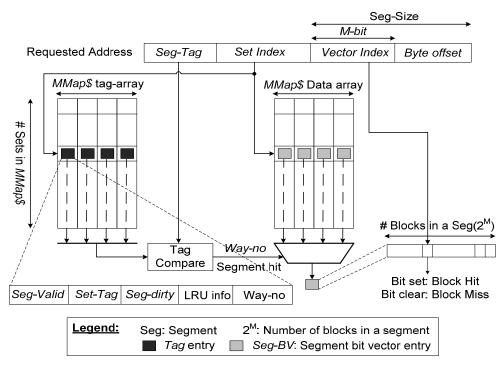

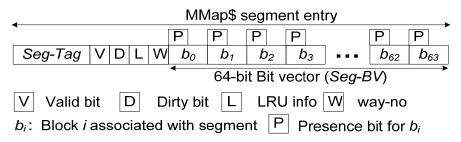

| Figure 2.11: | MMap\$ for DRAM cache hit/miss detection [73, 74]                                                                                                 | 23 |

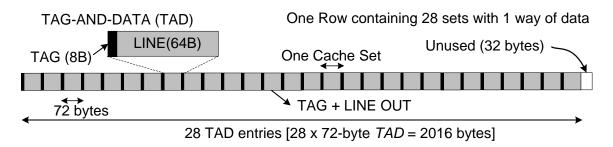

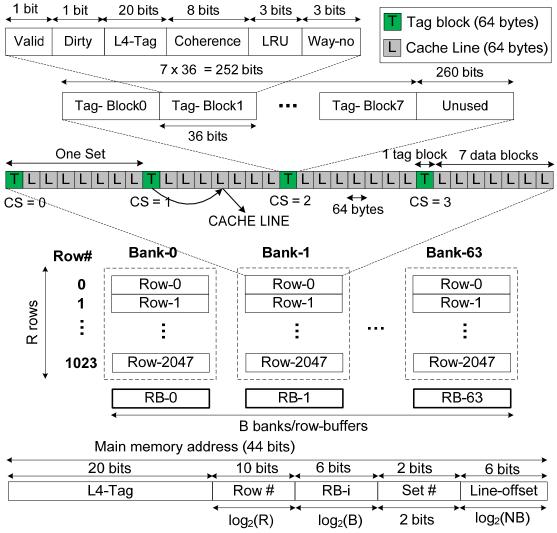

| Figure 2.12: | DRAM cache row organization used by Alloy-Cache for 2KB row size                                                                                  | 24 |

| Figure 2.13: | Alloy-Cache (a) row buffer hit latency (b) row buffer miss latency                                                                                | 24 |

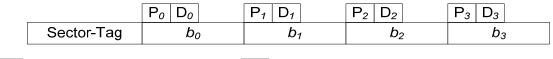

| Figure 2.14: | Sector organization with 4 blocks per sector                                                                                                      | 25 |

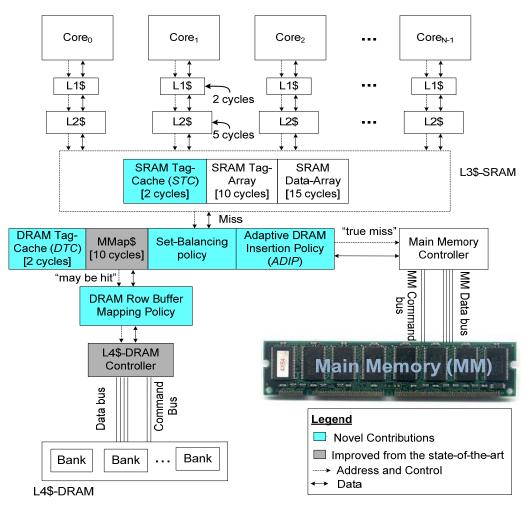

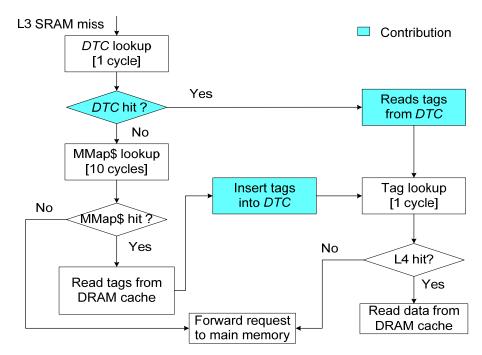

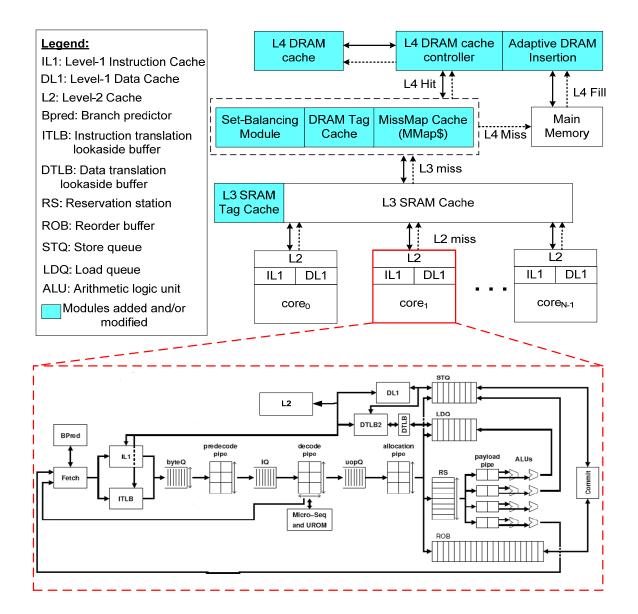

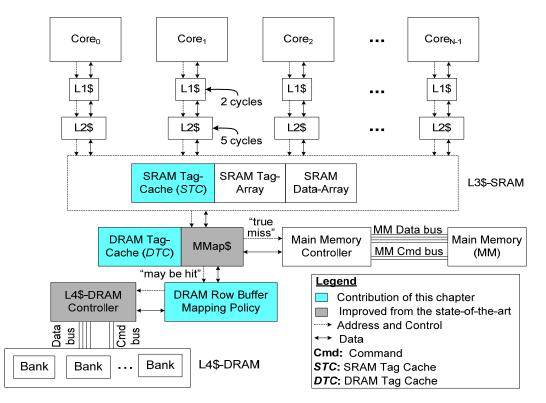

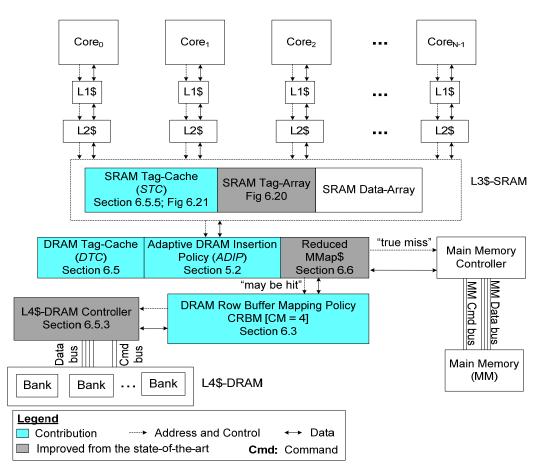

| Figure 3.1:  | Proposed SRAM/DRAM cache hierarchy for an N-core system                                                                                           | 29 |

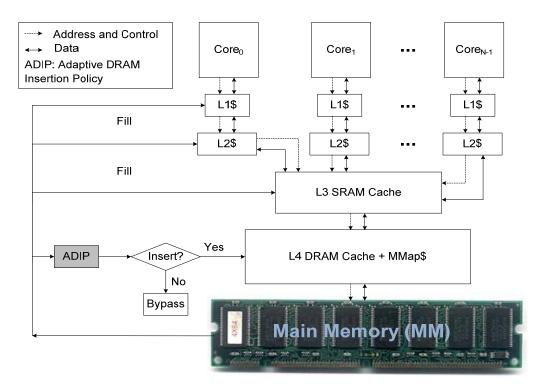

| Figure 3.2:  | High level view of the proposed Adaptive DRAM Insertion Policy                                                                                    | 30 |

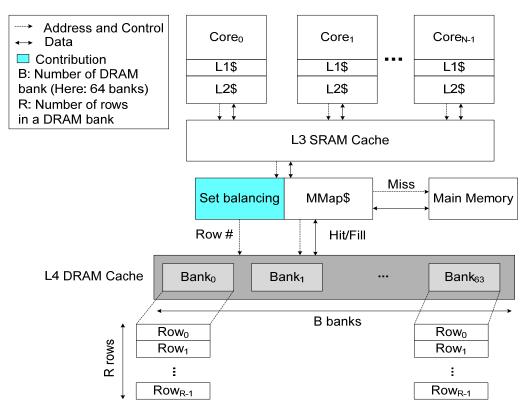

| Figure 3.3:  | High level view of the proposed Set balancing policy                                                                                              | 31 |

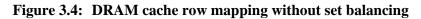

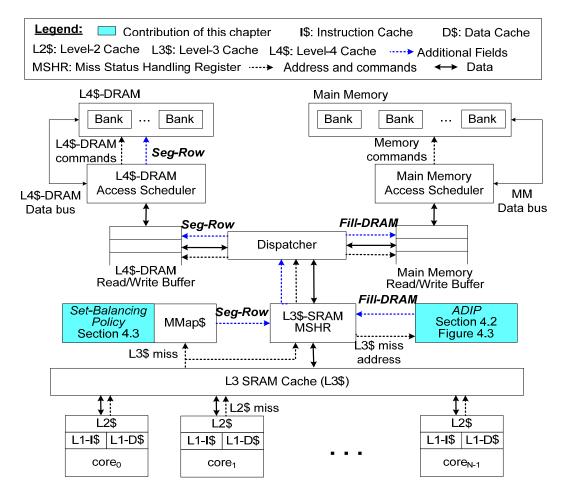

| Figure 3.4:  | DRAM cache row mapping without set balancing                                                                                                      | 32 |

| Figure 3.5:  | Steps involved in L4 DRAM tag lookup after an L3 SRAM miss                                                                                        | 33 |

| Figure 4.1:  | Overview of the simulator based on Zesto simulator [75]                                                                                           | 37 |

| Figure 5.1:  | Proposed DRAM cache hierarchy for an N-core system                                                                                                | 43 |

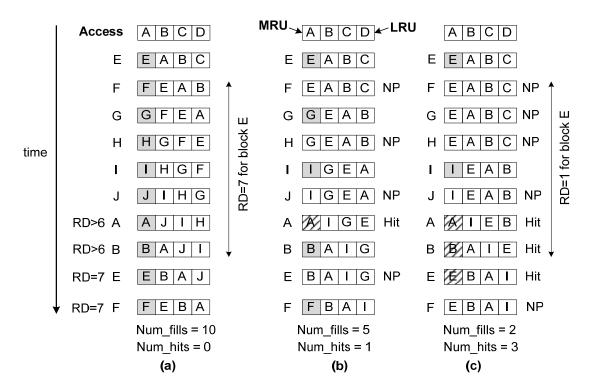

| Figure 5.2:  | Example illustrating DRAM insertion probability of (a) 1, (b) $\frac{1}{2}$ , and (c) $\frac{1}{4}$                                               | 45 |

| Figure 5.3:  | Adaptive DRAM Insertion Policy for an N-core system                                                                                               | 47 |

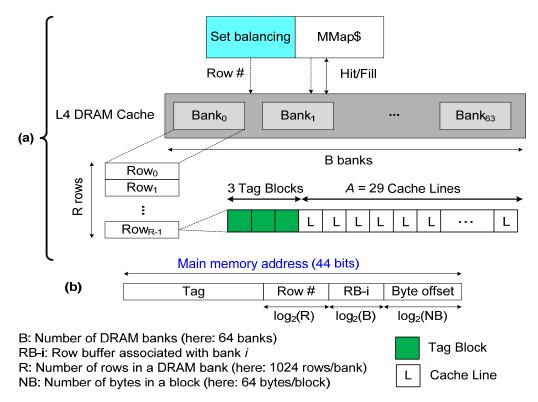

| Figure 5.4:                                                                                                                                                                         | : DRAM cache row mapping for LH-Cache [73] (a) with <i>SB-Policy</i> (b) without <i>SB-Policy</i>                                                                                                                                      |    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

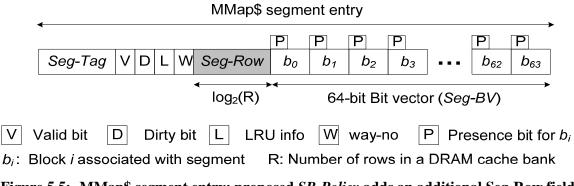

| Figure 5.5:                                                                                                                                                                         | : MMap\$ segment entry; proposed <i>SB-Policy</i> adds an additional Seg-Row field to MMap\$ entry for set balancing                                                                                                                   |    |  |

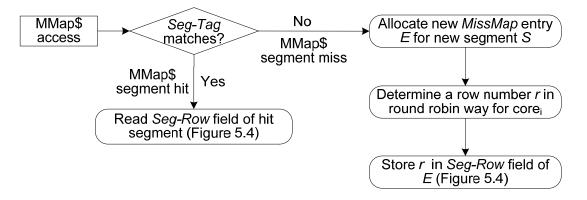

| Figure 5.6:                                                                                                                                                                         | Row assignment for SB-policy                                                                                                                                                                                                           | 50 |  |

| Figure 5.7:                                                                                                                                                                         | Steps involved in cache lookup operation                                                                                                                                                                                               | 51 |  |

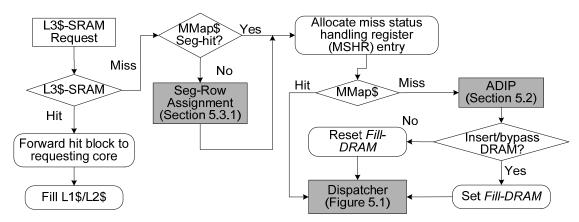

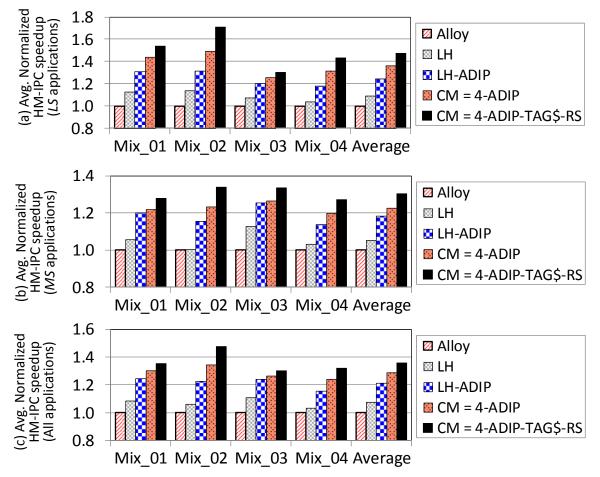

| Figure 5.8:Normalized HM-IPC speedup compared to LRU [73] for (a) Latency<br>Sensitive (LS) applications (b) Memory Sensitive (MS) applications (c)<br>Both LS and MS applications. |                                                                                                                                                                                                                                        |    |  |

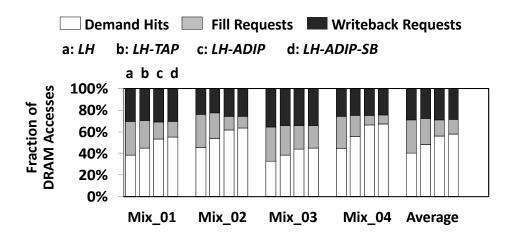

| Figure 5.9:                                                                                                                                                                         | Distribution of DRAM cache accesses for different policies                                                                                                                                                                             | 54 |  |

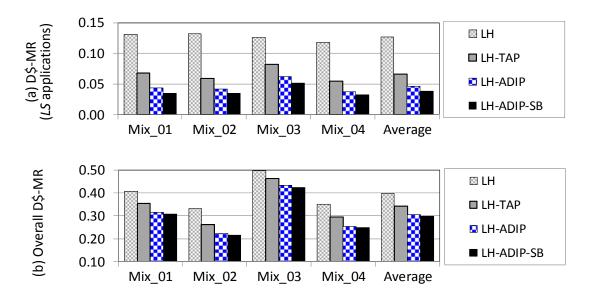

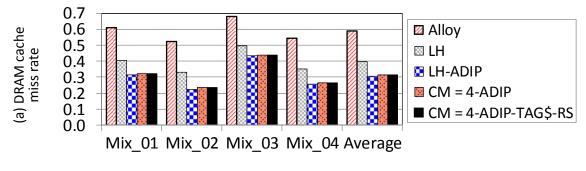

| Figure 5.10:                                                                                                                                                                        | (a) DRAM cache miss rate (D\$-MR) for Latency Sensitive ( <i>LS</i> ) applications (b) Overall DRAM cache miss rate                                                                                                                    | 55 |  |

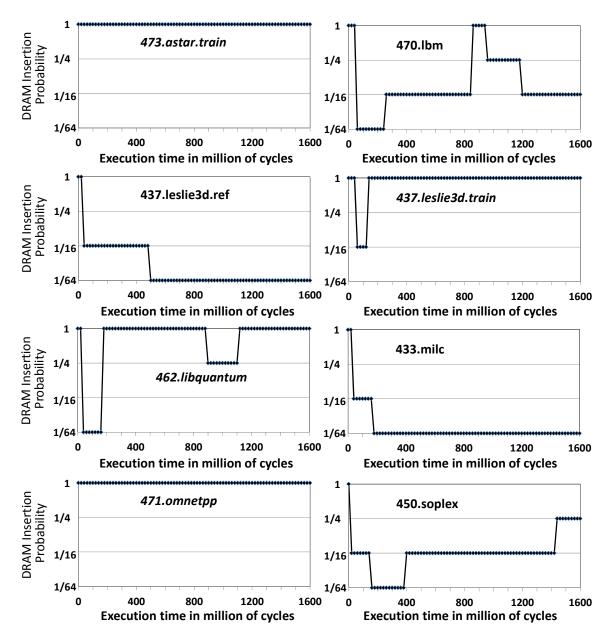

| Figure 5.11:                                                                                                                                                                        | Run-time DRAM insertion probability for non-sampled sets of all applications in Mix_01                                                                                                                                                 | 56 |  |

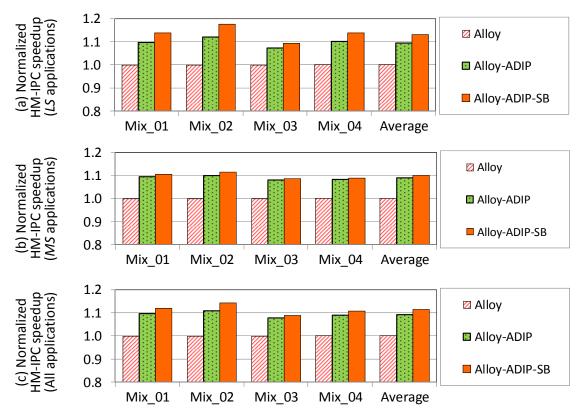

| Figure 5.12:                                                                                                                                                                        | Normalized HM-IPC speedup compared to <i>Alloy</i> [98] for (a) <i>Latency</i><br><i>Sensitive</i> ( <i>LS</i> ) applications (b) <i>Memory Sensitive</i> ( <i>MS</i> ) applications (c)<br>Both <i>LS</i> and <i>MS</i> applications. | 57 |  |

| Figure 5.13:                                                                                                                                                                        | (a) DRAM cache miss rate (D\$-MR) for Latency Sensitive ( <i>LS</i> ) applications (b) Overall DRAM cache miss rate                                                                                                                    | 58 |  |

| Figure 6.1:                                                                                                                                                                         | SRAM/DRAM cache hierarchy highlighting the novel contributions                                                                                                                                                                         | 59 |  |

| Figure 6.2:                                                                                                                                                                         | (a) L4 DRAM hit latency (b) L4 DRAM miss rate (c) main memory latency                                                                                                                                                                  | 60 |  |

| Figure 6.3:                                                                                                                                                                         | Row Buffer Mapping with Associativity of 7 (RBM-A7)                                                                                                                                                                                    | 62 |  |

| Figure 6.4:                                                                                                                                                                         | Memory block mapping for the proposed RBM-A7 policy                                                                                                                                                                                    | 63 |  |

| Figure 6.5:                                                                                                                                                                         | Row buffer mapping policy used by (a) LH-Cache [73] (b) CRBM policy [Proposed]                                                                                                                                                         | 64 |  |

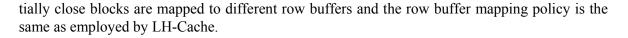

| Figure 6.6:                                                                                                                                                                         | Block mapping for configurable row buffer mapping policy with different values of CM                                                                                                                                                   | 65 |  |

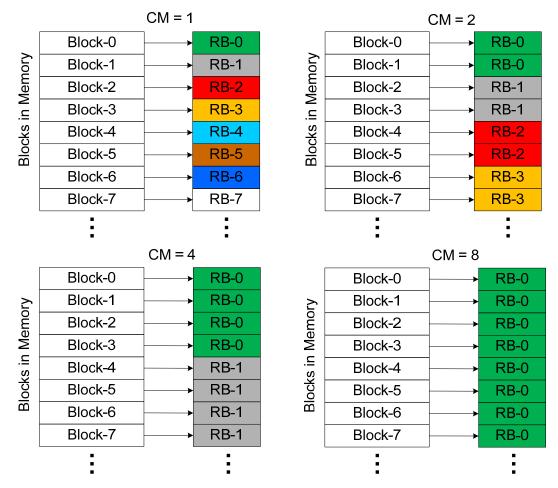

| Figure 6.7:                                                                                                                                                                         | DRAM cache row buffer hit rate for different values of CM                                                                                                                                                                              | 66 |  |

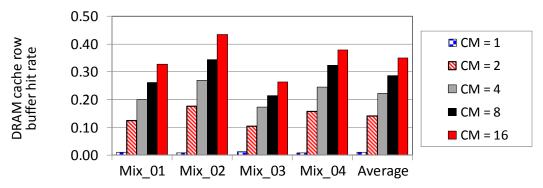

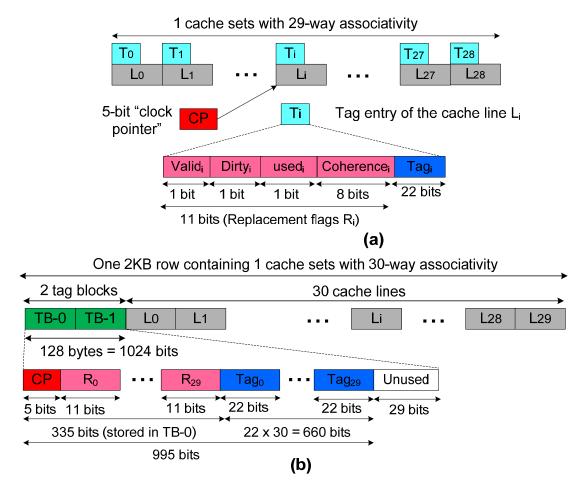

| Figure 6.8: (a) Overview of LRU policy with 29-way associative cache (b) how the tag entry fields are organized in LH-Cache [73, 74]                                                |                                                                                                                                                                                                                                        | 66 |  |

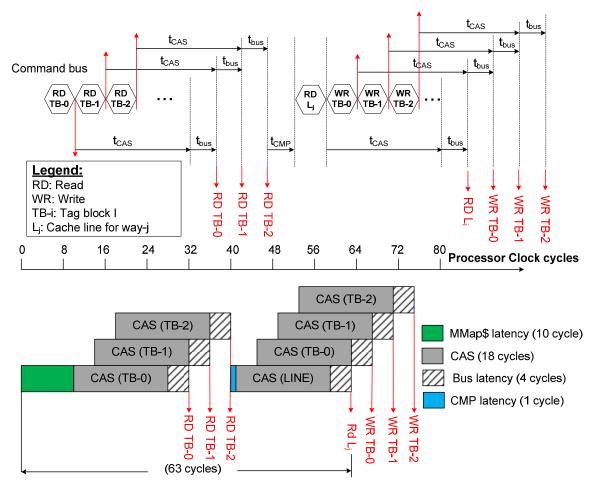

| Figure 6.9: Timing and sequence of commands for L4 DRAM hit that his in the row buffer for LH-Cache                                                                                 |                                                                                                                                                                                                                                        | 67 |  |

| Figure 6.10: (a) Overview of "pseudo LRU" policy (b) how the tag entry fields are organized in configurable row buffer mapping policy                                               |                                                                                                                                                                                                                                        | 68 |  |

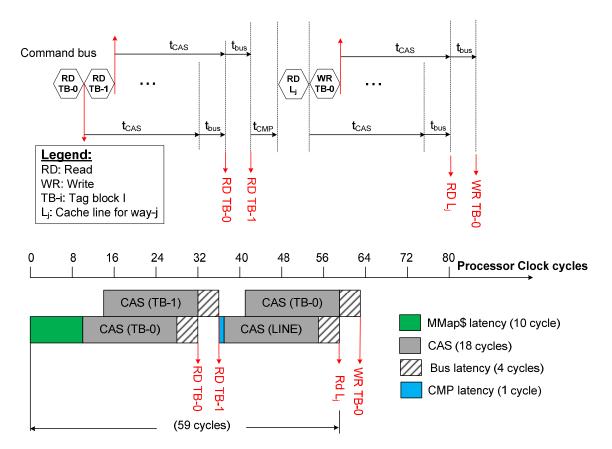

| Figure 6.11: Timing and sequence of commands for L4 DRAM read hit that his in the row buffer for configurable row buffer mapping policy                                             |                                                                                                                                                                                                                                        | 69 |  |

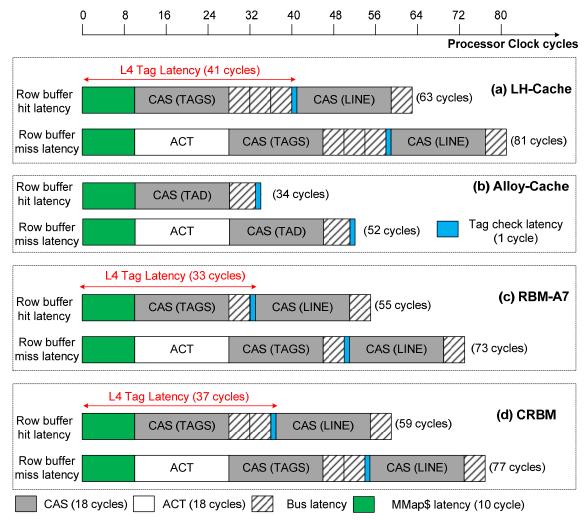

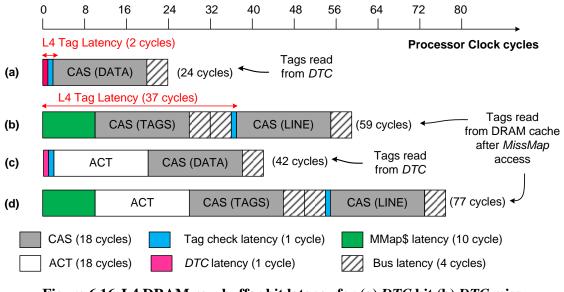

| Figure 6.12:                                                                                                                                                                        | L4 DRAM cache Latency breakdown for a 2KB row size (a) LH-Cache<br>[73, 74] (b) Alloy-Cache [98] (c) RBM-A7 [proposed] (d) CRBM                                                                                                        | 70 |  |

|                                                                                                                                                                                     | [proposed]                                                                                                                                                                                                                             | /0 |  |

| Figure 6.13:                                                                                                                                                           | MMap\$ entry covering a 4KB memory segment for LH-Cache [73, 74]72                                                                                                                                                                                                                                                                    |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

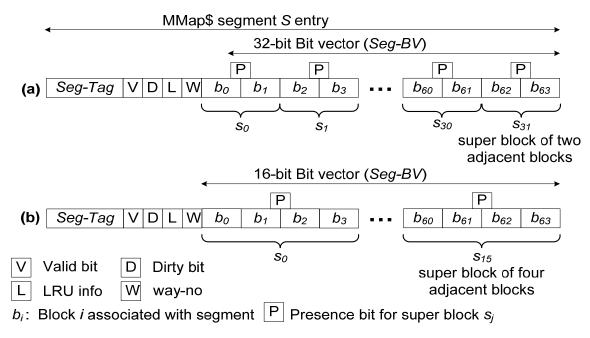

| Figure 6.14:                                                                                                                                                           | Proposed SB-MMap\$ entry representing a 4KB memory segment for a                                                                                                                                                                                                                                                                      |    |  |

|                                                                                                                                                                        | super-block containing (a) two adjacent blocks (b) four adjacent blocks                                                                                                                                                                                                                                                               | 73 |  |

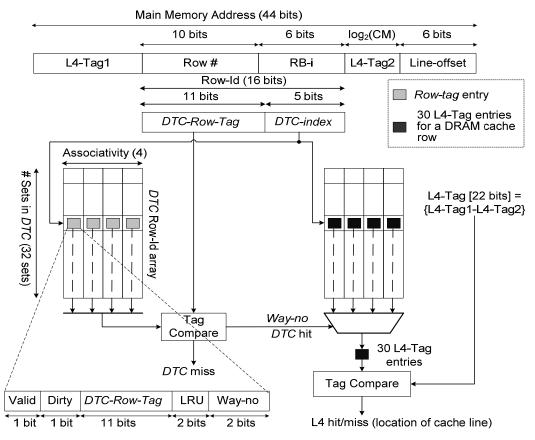

| Figure 6.15:                                                                                                                                                           | DRAM Tag Cache (DTC) Organization for configurable row buffer                                                                                                                                                                                                                                                                         |    |  |

|                                                                                                                                                                        | mapping policy                                                                                                                                                                                                                                                                                                                        | 75 |  |

| Figure 6.16:                                                                                                                                                           | L4 DRAM row buffer hit latency for (a) DTC hit (b) DTC miss                                                                                                                                                                                                                                                                           | 76 |  |

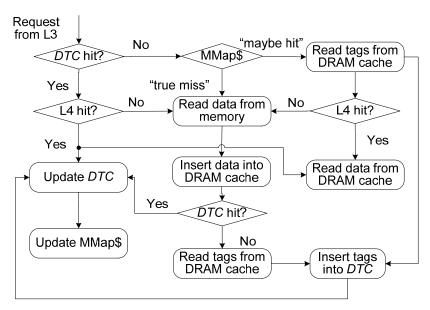

| Figure 6.17:                                                                                                                                                           | DTC and MMap\$ lookup following an L3 SRAM miss                                                                                                                                                                                                                                                                                       | 77 |  |

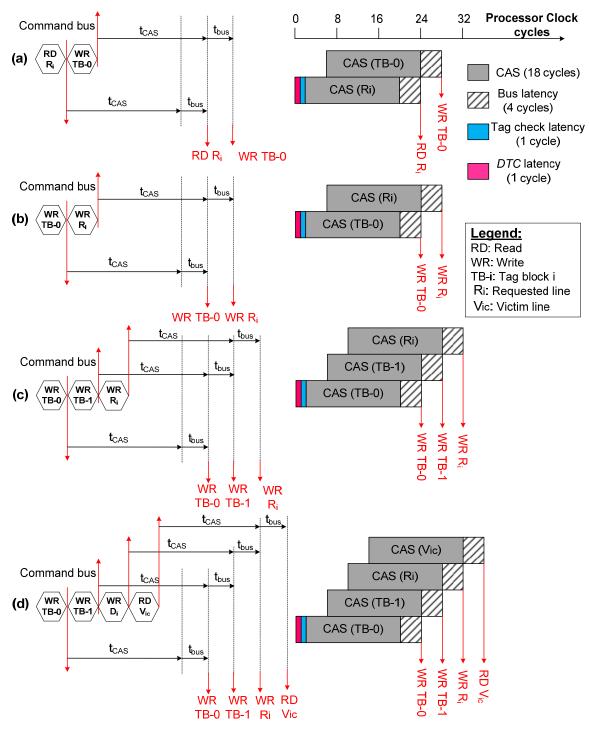

| Figure 6.18:                                                                                                                                                           | Timing and sequence of commands to update the tags in the DRAM cache<br>after a <i>DTC</i> hit in the configurable row buffer mapping policy for an L4<br>DRAM row buffer hit (a) read request (b) write/write back request (c) fill<br>request with clean victim block eviction (d) fill request with dirty victim<br>block eviction | 78 |  |

| Figure 6.19:                                                                                                                                                           | DRAM Tag Cache (DTC) Organization for the RBM-A7 policy                                                                                                                                                                                                                                                                               | 79 |  |

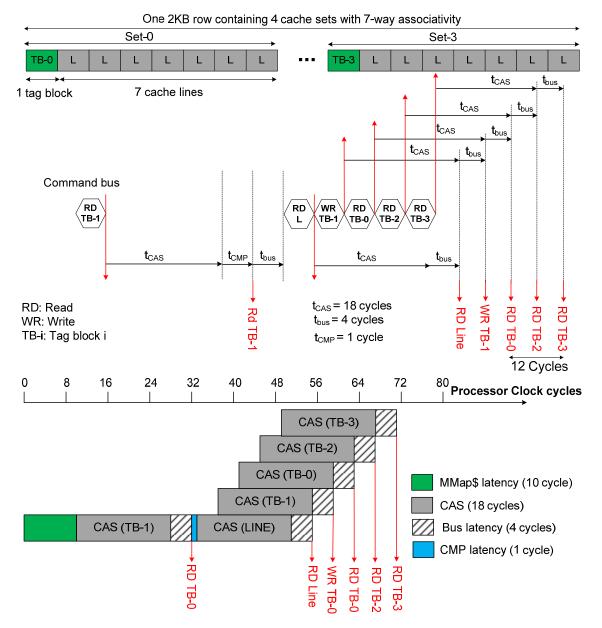

| Figure 6.20:                                                                                                                                                           | Timing and sequence of commands to fill the <i>DTC</i> after a <i>DTC</i> miss for a data block that belongs to Set-1 in the RBM-A7 policy                                                                                                                                                                                            | 80 |  |

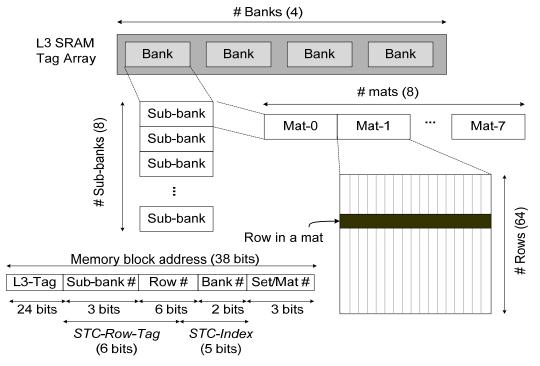

| Figure 6.21:                                                                                                                                                           | Layout of a large L3 SRAM tag array [118]                                                                                                                                                                                                                                                                                             | 81 |  |

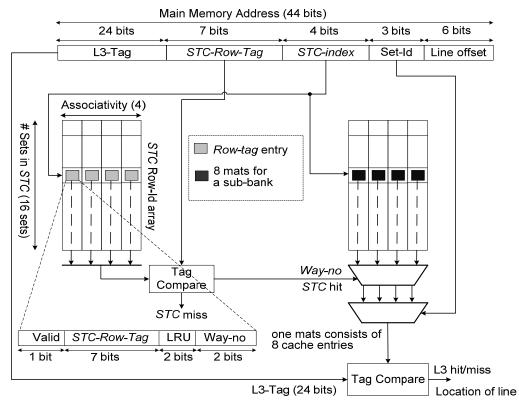

| Figure 6.22:                                                                                                                                                           | SRAM Tag-Cache (STC) organization                                                                                                                                                                                                                                                                                                     | 82 |  |

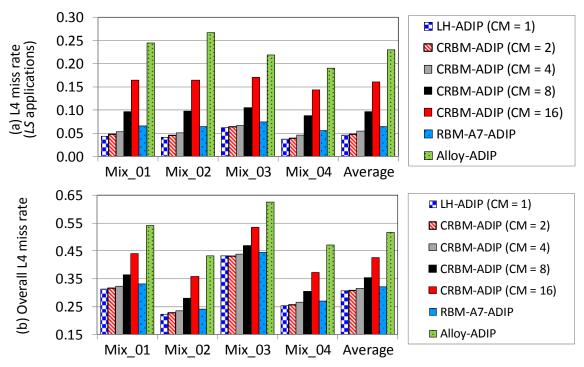

| Figure 6.23:                                                                                                                                                           | Figure 6.23: L4 DRAM miss rate (a) for Latency Sensitive applications (b) Overall miss rate; for different row buffer mapping policies                                                                                                                                                                                                |    |  |

| Figure 6.24:                                                                                                                                                           | DRAM cache row buffer hit rates for different row buffer mapping                                                                                                                                                                                                                                                                      |    |  |

|                                                                                                                                                                        | policies                                                                                                                                                                                                                                                                                                                              |    |  |

| Figure 6.25:                                                                                                                                                           | DRAM Tag-Cache hit rates for different row buffer mapping policies                                                                                                                                                                                                                                                                    | 86 |  |

| Figure 6.26:                                                                                                                                                           | L4 DRAM cache hit latency (a) without <i>DTC</i> (b) with <i>DTC</i> ; for different row buffer mapping policies                                                                                                                                                                                                                      | 87 |  |

| Figure 6.27:                                                                                                                                                           | Normalized HM-IPC speedup compared to Alloy-ADIP for different row buffer mapping policies without DRAM Tag-Cache ( <i>DTC</i> ) for (a) latency sensitive applications (b) all applications                                                                                                                                          | 88 |  |

| Figure 6.28:                                                                                                                                                           | Normalized HM-IPC speedup compared to Alloy-ADIP for different row buffer mapping policies with DRAM Tag-Cache ( <i>DTC</i> ) (a) latency sensitive applications (b) all applications                                                                                                                                                 |    |  |

| Figure 6.29: Average (a) DRAM cache row buffer hit rate (b) <i>DTC</i> hit rate (c) L4 hit latency with <i>DTC</i> (d) L4 miss rate for latency sensitive applications |                                                                                                                                                                                                                                                                                                                                       |    |  |

| Figure 6.30:                                                                                                                                                           | Normalized HM-IPC speedup compared to the <i>RBM-A7-ADIP</i> policy with DRAM Tag-Cache ( <i>DTC</i> ) (a) latency sensitive applications (b) all applications.                                                                                                                                                                       | 91 |  |

| Figure 6.31:                                                                                                                                                           | Normalized HM-IPC speedup compared to Alloy-ADIP for (a) Latency<br>Sensitive ( <i>LS</i> ) applications (b) Memory Sensitive ( <i>MS</i> ) applications (c)<br>Both <i>LS</i> and <i>MS</i> applications                                                                                                                             | 92 |  |

| Figure 6.32:                                                                                                                                                           | Normalized HM-IPC speedup for different super-block (sb) sizes                                                                                                                                                                                                                                                                        |    |  |

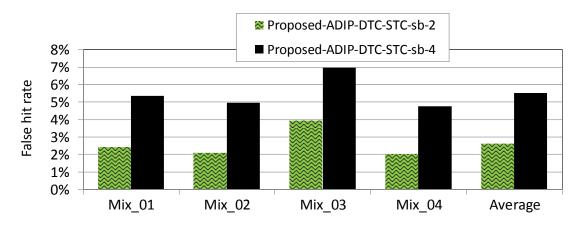

| Figure 6.33:                                                                                                                                                           | Percentage of false hits for super-blocks (sb) of size 2 and 4                                                                                                                                                                                                                                                                        | 93 |  |

| Figure 7.1: | Proposed SRAM/DRAM cache hierarchy showing integration of selected policies                                                                                                                    | 95  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

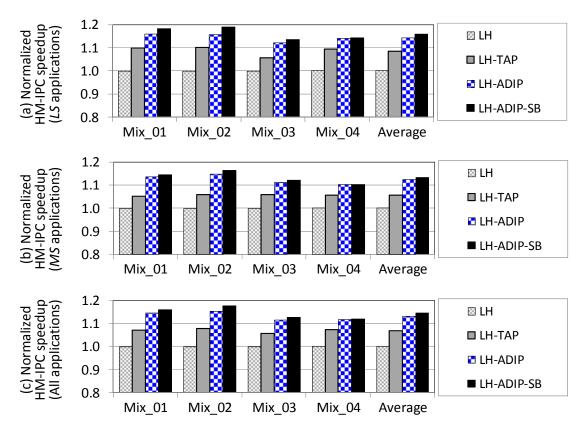

| Figure 7.2: | Normalized HM-IPC speedup compared to Alloy for (a) Latency Sensitive ( <i>LS</i> ) applications (b) Memory Sensitive ( <i>MS</i> ) applications (c) Both <i>LS</i> and <i>MS</i> applications | 97  |

| Figure 7.3: | L4 DRAM cache miss rate                                                                                                                                                                        | 99  |

| Figure 7.4: | Off-chip main memory access latency                                                                                                                                                            | 99  |

| Figure 7.5: | (a) L4 DRAM hit latency (b) DRAM row buffer hit rate (c) DRAM Tag-<br>Cache hit rate                                                                                                           | 100 |

# **List of Tables**

| Table 1.1: | On-Chip SRAM LLC sizes over the past years for Intel Processor Chips  | 2  |

|------------|-----------------------------------------------------------------------|----|

| Table 2.1: | Comparisons between different DRAM cache designs for a 2KB row size   | 27 |

| Table 2.2: | Advantages of the proposed Policies                                   | 27 |

| Table 3.1: | Overview of the proposed Policies                                     | 35 |

| Table 4.1: | Core and cache parameters                                             | 39 |

| Table 4.2: | Main memory parameters                                                | 40 |

| Table 4.3: | Application mixes                                                     | 41 |

| Table 6.1: | Impact of row buffer mapping policy on associativity and latency      | 71 |

| Table 6.2: | Storage overhead of DRAM Tag-Cache (DTC) and SRAM Tag-Cache           |    |

|            | (STC)                                                                 | 83 |

| Table 7.1: | Overview of different configurations with their incorporated policies | 96 |

# Abbreviations

| Α                | Associativity                                  |  |  |  |

|------------------|------------------------------------------------|--|--|--|

| ADIP             | Adaptive DRAM Insertion Policy                 |  |  |  |

| CRBM             | Configurable Row Buffer Mapping Policy         |  |  |  |

| D\$              | Shared DRAM cache                              |  |  |  |

| DRAM             | Dynamic Random Access Memory                   |  |  |  |

| DTC              | DRAM Tag-Cache                                 |  |  |  |

| FR-FCFS          | First Ready First Come First Serve             |  |  |  |

| HL               | Hit Latency                                    |  |  |  |

| HMIPC            | Harmonic Mean Instruction Per Cycle            |  |  |  |

| KB               | Kilo Byte (also KByte): 1024 Byte              |  |  |  |

| ILP              | Instruction Level Parallelism                  |  |  |  |

| IPC              | Instruction Per Cycle                          |  |  |  |

| LLC              | Last Level Cache                               |  |  |  |

| LRU              | Least Recently Used Policy                     |  |  |  |

| MB               | Mega Byte (also MByte): 1024 →KB               |  |  |  |

| ML               | Miss Latency                                   |  |  |  |

| MR               | Miss Rate                                      |  |  |  |

| MUX              | Multiplexer                                    |  |  |  |

| OS               | Operating System                               |  |  |  |

| RAM              | Random Access Memory                           |  |  |  |

| RBM-A7           | Row Buffer Mapping with Associativity of seven |  |  |  |

| RD               | Reuse Distance                                 |  |  |  |

| ROB              | Reorder Buffer                                 |  |  |  |

| S\$              | Shared SRAM cache                              |  |  |  |

| SB-Policy        | Set Balancing Policy                           |  |  |  |

| SiP              | System In Package                              |  |  |  |

| SRAM             | Static Random Access Memory                    |  |  |  |

| STC              | SRAM Tag-Cache                                 |  |  |  |

| t <sub>CAS</sub> | Column Access Strobe delay                     |  |  |  |

| t <sub>RAS</sub> | Row Access Strobe delay                        |  |  |  |

$t_{RCD} \qquad \qquad \text{Row to Column Command delay}$

t<sub>RP</sub> Row Precharge delay

t<sub>WR</sub> Write Recovery time

TSV Through Silicon Via

## **Chapter 1** Introduction

Moore's law [85] predicts that the number of transistors for a given chip area double every 18 months. The exponential growth in transistor density driven by Moore's law and advanced microarchitecture techniques such as pipelining [119] and out-of-order execution [125] has led to the significant increase in processor performance [12, 82] over the past several years. However, compared to processor performance, the memory performance [140] has increased at a slower pace as illustrated in Figure 1.1. This slower improvement in memory performance has led to the significant speed gap between processor and memory referred to as "Memory Bandwidth" problem [12, 60, 108, 131, 136, 144].

Figure 1.1: Processor memory speed gap over the past 30 years [12]

To alleviate the "Memory Bandwidth" problem, caches [29, 30] have been used to bridge the latency gap between high speed cores and slower main memory. The cache is a smaller and faster on-chip memory that stores copies of recently accessed data from frequently used memory locations to take advantage of the spatial and temporal locality of the applications. At first, processors used a single level of cache as used by Intel Pentium P5 processor in 1993. However, the widening gap between processor and memory speed has led to the evolution of multi-level cache hierarchies [12, 59, 96]. For instance, the recent Intel Xeon E5-2690 processor chip [3], introduced in 2012 employs three levels of cache hierarchy. In these hierarchies, fast and small L1 and L2 caches are dedicated to each core and provide low hit latency. The larger Last-Level-Cache (LLC) is shared among all cores and provides low miss rate.

### 1.1 Why On-chip DRAM cache?

A recent trend in industry towards mitigating the "Memory Bandwidth" problem is to use a large on-chip SRAM Last-Level-Cache (LLC) by dedicating a larger die area for the LLC. Table 1.1

illustrates this observation showing SRAM LLC capacity over the past several years for Intel processor chips [1]. For example, Intel P5 processor introduced in 1993 was equipped with a small 16KB SRAM cache, the recent Intel Xeon E5-2690 processor, introduced in 2012, has employed a larger 20MB SRAM LLC. Larger high-speed SRAM cache improves the performance by sending fewer requests to the low-speed off-chip memory because it can contain the working set size (i.e. the amount of memory required to execute the program) of many applications. However, for a given cache capacity, SRAM cache significantly increases the system cost compared to DRAM cache in terms of larger die area because it provides lower density compared to DRAM cache [18, 54, 55].

| Year | Intel Processor Name   | # Cores | <b>On-Chip Caches</b> | LLC size (Cache Level) |

|------|------------------------|---------|-----------------------|------------------------|

| 1993 | Pentium P5             | 1       | L1                    | 16KB (L1)              |

| 1995 | Pentium Pro 6          | 1       | L1, L2                | 256KB (L2)             |

| 1997 | Pentium II Klamath     | 1       | L1, L2                | 512KB (L2)             |

| 2001 | Pentium III-S Tualatin | 1       | L1, L2                | 512KB (L2)             |

| 2004 | Pentium IV Prescott    | 1       | L1,L2                 | 2MB (L3)               |

| 2006 | Core 2 Duo Conroe      | 2       | L1, L2                | 4MB (L2)               |

| 2008 | Xeon 7130M             | 2       | L1,L2                 | 8MB (L2)               |

| 2010 | Xeon 7130M             | 6       | L1, L2, L3            | 12MB (L3)              |

| 2012 | Xeon E5-2690           | 8       | L1, L2, L3            | 20MB (L3)              |

Table 1.1:

On-Chip SRAM LLC sizes over the past years for Intel Processor Chips [1]

Despite continual increase in SRAM LLC size over the past years, the demand for cache space has always exceeded due to large working set sizes of complex applications [32]. Figure 1.2 illustrates this observation by showing LLC misses per thousand instructions for different LLC sizes and different SPEC2006 [5, 46] applications. It shows that the working set sizes of some applications (e.g. 462.libquantum, 471.omnetpp, and 473.astar.train) exceeds the available SRAM LLC size, even for the Intel Xeon E5-2690 processor chip with 20MB LLC. On the other hand, the applications with small working set sizes (e.g. 437.leslie3d.train) obtain significant benefits from a 20MB LLC, because the majority of cache requests will be satisfied in the LLC for these applications.

Single-core processors [2, 7, 9, 25, 63, 111] have shown significant performance increase during the last decades which is mainly driven by transistor speed as well as by exploiting instruction level parallelism (ILP) [12, 82, 91]. However, the diminishing transistor-speed scaling and energy limits of single-core processors have led to the evolution of multi-core systems [2, 7, 9, 14, 25, 26, 27, 31, 33, 63, 111] because it is less complex to design a chip with many small cores compared to a chip with a single larger core. For this reason, computing industry has announced multi-core processor chips that consist of several computing cores fabricated on a single chip in contrast to traditional single-core processor chips.

Figure 1.2: LLC misses per thousand instructions (LLC MPKI) for different SPEC2006 [5] applications

Multi-core systems provide improved performance compared to a single-core system through better resource utilization by replicating multiple cores on the chip. However, these multi-core systems place a high pressure on the SRAM LLC due to their limited cache capacity because it has to be shared among multiple applications. Recent trends likes Intel Tera-scale [127] and Tilera TILE64 [9] multi-core processor chips show that the number of cores will likely continue to increase in the future. As future multi-core systems are expected to have a large number of cores (see Table 1.1), the aggregate working set size (i.e. the amount of memory required to execute all applications) on a multi-core system will increase as well. As a result, increased number of insertions in the limited size SRAM LLC from multiple cores will cause *inter-core cache eviction* [15, 16, 35, 51, 64, 65, 73, 75, 86, 98, 99, 138] where one core could evict useful data used by another core. Increased inter-core cache eviction for traditional on-chip SRAM LLC [77, 78, 102] increases the number of off-chip memory accesses, which may degrade the performance due to limited off-chip memory bandwidth [12, 60, 108, 131, 136, 144].

The total die area dedicated for the LLC is an important design parameter for multi-core chip vendors. Increasing the amount of cache capacity for the SRAM LLC can greatly improve the performance by increasing the cache hit rate and reducing the number of high-latency off-chip accesses. However, it increases the system cost in terms of larger die area due to high cost-per-bit of the SRAM cache [123]. DRAM cache offers a lower cost-per-bit because it provides 8 to 16 times [54, 55] higher density compared to traditional SRAM caches. For a given cache capacity, DRAM cache significantly reduces the system cost in terms of smaller die area. As a result, it provides significantly higher cache capacity that leads to reduced off-chip accesses and reduced inter-core cache eviction compared to an area equivalent SRAM cache. For instance, the IBM POWER7 processor [7, 129] utilizes a 32MB on-chip DRAM as LLC between L1/L2 SRAM cache and main memory.

#### 1.1.1 Benefits of On-Chip DRAM cache

Integrating on-chip DRAM cache in the cache hierarchy provides significant performance benefits due to the following reasons:

- 1. It provides eight times more bandwidth benefits compared to an off-chip memory [54, 55], because it provides wider bus widths through the use of shorter on-chip interconnects [34, 77, 78] compared to conventional off-chip memory interfaces.

- 2. It operates at a higher clock speed through the use of low latency on-chip interconnects [52, 61, 62, 70] compared to off-chip memory.

- 3. It provides more independent channels compared to off-chip memory [66] because off-chip memory cannot provide more channels due to limited pin bandwidth [60].

- 4. It provides 8 to 16 times capacity benefits compared to an area equivalent SRAM cache [11, 54, 55, 75] due to its small cell size per bit. Thus, it reduces contention for the off-chip main memory due to its high capacity [77, 78, 102], hereby reducing off-chip memory accesses.

- 5. It offers up to four times higher bandwidth compared to an SRAM cache [53] due to its capability to service multiple outstanding requests in parallel due to the large number of DRAM banks.

### 1.2 Challenges in DRAM Cache Hierarchy

On-chip DRAM cache is a promising alternative to SRAM cache, but its high access latency prohibits its adoption as SRAM cache replacement. Neither SRAM nor DRAM cache alone can provide both highest capacity and fastest access for multi-core system, respectively. Therefore, stateof-the-art SRAM/DRAM cache hierarchies [77, 78] exploit the latency benefits of fast SRAM cache and the capacity benefits of slower DRAM cache.

The advantages of on-chip DRAM cache come at the cost of higher latency compared to SRAM cache (but lower latency compared to off-chip memory). If designed efficiently, DRAM cache could satisfy the high capacity needs of complex applications [32] while reducing the number of high latency off-chip memory accesses. Before summarizing the thesis contributions in Section 1.3, the following subsections explain the key challenges and drawbacks that are faced by state-of-the-art and that are addressed in this thesis:

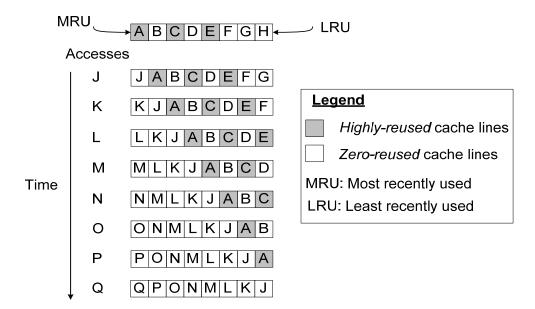

### 1.2.1 Inefficient resource allocation

When the DRAM cache is shared among multiple cores, the cores might interfere with each other in the DRAM cache controller causing inter-core interference that increases DRAM cache hit latency. State-of-the-art DRAM cache suffers from increased inter-core interference because it always allocates DRAM resources for both *highly-reuse* data (i.e. data that is reused in the near future) and *zero-reuse* data (i.e. data that is not reused before it gets evicted). Furthermore, they lead to inefficient DRAM cache bandwidth utilization and increased miss rate due to unnecessary resource allocation for *zero-reuse* data.

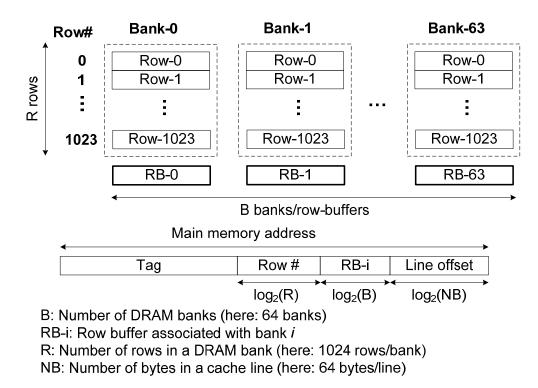

### 1.2.2 Limited row buffer hit rate

The DRAM sub-system is composed of DRAM banks which consist of rows and columns of memory cells called the DRAM array [68, 69, 88, 89, 141]. Each DRAM bank provides a row buffer (typically 2 to 8 KB) that consists of SRAM cells (detailed background of a DRAM bank is provided in Section 2.2.2) that operate faster than the DRAM array. Data in a DRAM bank can only be accessed after it is fetched to the row buffer. Any subsequent access to the same row (so-called row buffer hit) will bypass the DRAM array access and the data is directly read from the row buffer. Such row buffer locality reduces the access latency compared to when actually accessing the DRAM array. State-of-the-art DRAM cache architectures [77, 78] do not exploit the full potential of row buffer locality and their disadvantageous row buffer hit rate leads to high DRAM cache access latencies due to reduced spatial locality because they map consecutive memory blocks to different row buffers.

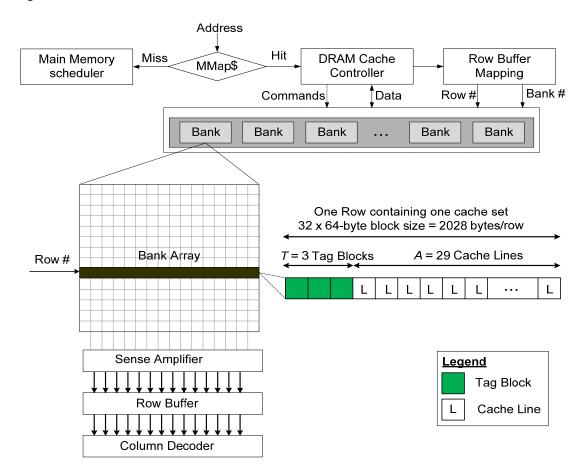

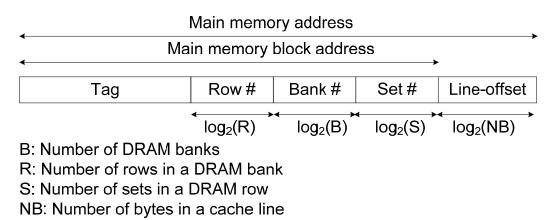

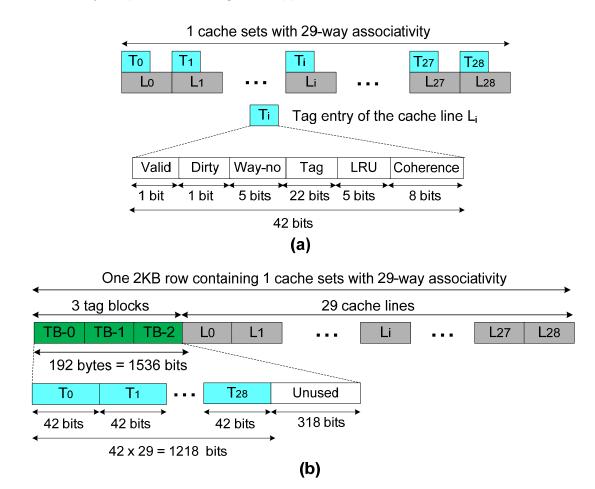

### 1.2.3 High tag lookup latency

In state-of-the-art DRAM cache [77, 78], each DRAM row (2048 bytes) consists of one cache set which is divided into 29 64-byte data blocks ( $29 \times 64 = 1856$  bytes) and 3 tag blocks ( $3 \times 64 = 192$  bytes). The tag lookup latency is a severe bottleneck due to the following reasons. First, it requires reading the tags (192 bytes) and data (64 bytes) for every DRAM cache access. The extraneous DRAM bandwidth required for reading this large tag information results in higher tag lookup latency. Second, the structure and access methods for DRAM subsystem (detailed back-ground of DRAM subsystem is provided in Section 2.2) incurs high tag lookup latency compared to SRAM cache tag lookup.

### 1.2.4 High Hardware cost

Recent state-of-the-art DRAM cache architectures [77, 78] invest noticeable hardware overhead for auxiliary structures to circumvent some of the above-mentioned drawbacks. For instance, they require 2MB SRAM storage for managing 128MB DRAM cache, which reduces the area advantages of DRAM cache.

## 1.3 Thesis Contribution

The major challenges in the design of an SRAM/DRAM cache hierarchy is to reduce the on-chip latency and off-chip memory accesses that majorly depends upon efficient utilization of DRAM

cache bandwidth and capacity, tag-store mechanism (i.e. where to store the tags of the DRAM cache and how to access them), efficient utilization of off-chip memory bandwidth, and DRAM cache row buffer hit rate. This thesis investigates state-of-the-art SRAM/DRAM cache hierarchies for multi-core systems and presents novel application-aware and DRAM-aware policies for efficiently managing SRAM/DRAM cache hierarchies, while addressing the above mentioned challenges.

#### In particular, this thesis makes the following novel contributions:

- 1. This thesis proposes an application-aware **adaptive DRAM insertion policy** (an insertion policy decides whether an incoming data when brought from off-chip memory should be inserted into cache or not). It adaptively selects from multiple insertion policies at runtime on a per-core basis depending on the monitored miss rate behavior of concurrently running applications. It provides efficient utilization of DRAM cache bandwidth that leads to improved performance via reduced inter-core interference in the DRAM cache controller.

- 2. This thesis proposes a **DRAM set balancing policy** after analyzing that DRAM accesses are not evenly distributed across the sets of the DRAM cache, which leads to increased conflict misses via unbalanced set utilization. The proposed policy improves the DRAM capacity utilization via reduced conflict misses, which leads to a reduced miss rate.

- **3.** To reduce the DRAM cache hit latency, this thesis proposes several DRAM **row buffer mapping policies** that improve the row buffer hit rate by exploiting data access locality in the row buffer.

- 4. To reduce the tag lookup latency, this thesis proposes a small and low latency SRAM structure namely **DRAM Tag-Cache** that allows most DRAM accesses to be serviced at significantly reduced access latency compared to when tags are accessed from the DRAM cache.

Altogether, this thesis develops a combined SRAM/DRAM cache organization that integrates all of the proposed policies in a single unified framework. This includes modifying existing DRAM cache controller policies to incorporate the proposed row buffer mapping policies and DRAM Tag-Cache structures. This thesis also reduces the storage overhead required for DRAM cache management with minimal impact on the overall instruction throughput for our novel row buffer mapping policies.

### 1.4 Thesis Outline

The thesis is organized as follows: Chapter 2 presents the background for caches (especially the DRAM cache) and the recent related work on SRAM and DRAM caches.

Chapter 3 provides a short overview of the proposed application and DRAM aware policies employed in this thesis. The detailed explanation and investigation of the proposed policies will later be presented in Chapter 5 and Chapter 6.