# The Customizable Virtual FPGA: Generation, System Integration and Configuration of Application-Specific Heterogeneous FPGA Architectures

## Răzvan Peter Figuli

## The Customizable Virtual FPGA: Generation, System Integration and Configuration of Application-Specific Heterogeneous FPGA Architectures

Zur Erlangung des akademischen Grades eines

### DOKTOR-INGENIEURS (Dr.-Ing.)

von der Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Institut für Technologie (KIT) genehmigte

#### DISSERTATION

von

### Dipl.-Ing. Razvan Peter Figuli

geboren in Hermannstadt (Rumänien)

Tag der mündlichen Prüfung: 21.09.2017

Hauptreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker Korreferent: Prof. Dr.-Ing. Klaus Hofmann

### Abstract

During the past three decades the evolution of Field Programmable Gate Arrays (FPGAs) has been strongly influenced by Moore's Law, process technology (scaling) and commercial markets. State-of-the-art FPGAs are moving closer and closer to general purpose on the one hand, but on the other hand, now that FPGAs have superseded more and more traditional Application-Specific Integrated Circuit (ASIC) domains, the efficiency expectations are growing. With the end of Dennard scaling, efficiency improvements can no longer rely on technology scaling alone. These facets along with trends towards reconfigurable System-on-Chips (SoCs) and new low-power applications such as cyber physical systems and internet of things require a better fit of target FPGAs, which can be facilitated through customization. Collaterally, trends towards mainstream deployment of FPGAs in day-to-day consumer products and services, the latter especially with the recent developments to employ FPGAs in data centres and cloud services, necessitate instant portability of applications across current and future FPGA devices. In this context, hardware virtualization can be a seamless vehicle for platform independence and portability. Candidly, purposes of customization and of virtualization are in a field of conflict as customization is intended for efficiency improvement yet virtualization adds additional area overhead. However, virtualization not only benefits from customization but also adds more flexibility to it as the architecture can be altered anytime. This peculiarity can be exercised for adaptive systems.

Both, customization and virtualization of FPGA architectures are predominantly unaddressed by the industry. Despite a few existing academic works they can be considered unexplored and are emerging areas of research.

The main goal of the work presented in this thesis is to expedite the generation of custom FPGA architectures that are tailored towards an efficient befitting of the application. In contrast to the usual approach with commercial off-the-shelf FPGAs, where the FPGA architecture is considered as a given constraint and the application is mapped onto the available resources, this work follows a new paradigm in which the application or application class is considered as given and the target architecture is tailored to efficiently accommodate the application. This results in customized application-specific FPGAs. The three pillars of this thesis are the aspects of *virtualization, customization* and the *framework*.

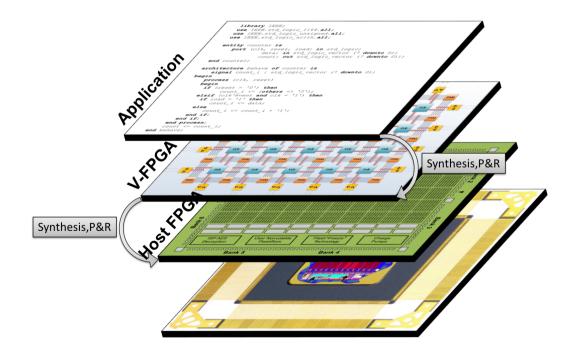

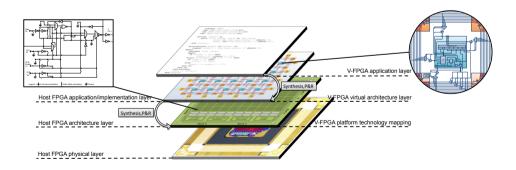

The central element is an extensively parameterizable virtual FPGA architecture, called *V*-*FPGA*, with the primary scope to be mapped onto any commercial off-the-shelf FPGA, while applications are executed on the virtual layer. This ensures portability and migration even on bitstream level as the specification of the virtual layer can persist, while the hosting physical platform can be exchanged. Furthermore, this technique is utilized to enable dynamic and partial reconfiguration on platforms that don't support it natively. Apart from virtualization, the *V*-*FPGA* architecture is further intended to serve as an embedded FPGA integrated into an ASIC, delivering efficient yet flexible system-on-chip

solutions. Therefore, target technology mapping methodologies for both, virtualization and physical implementation are addressed and an example for physical implementation in a 45 *nm* standard-cell approach is carried out.

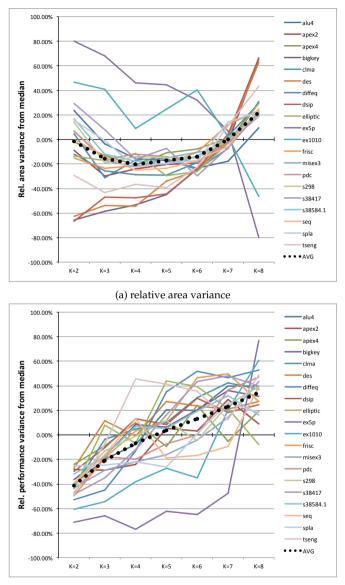

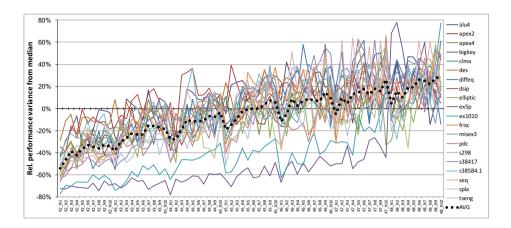

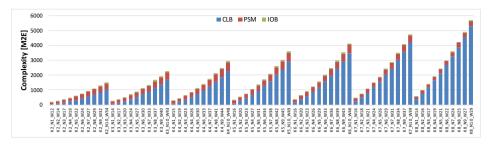

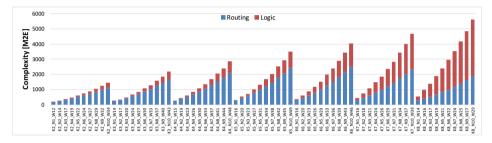

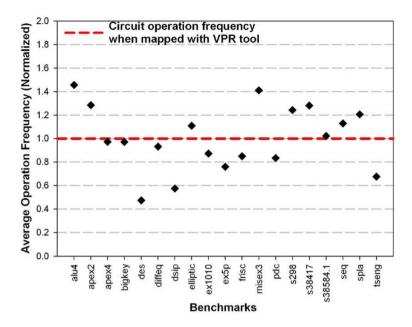

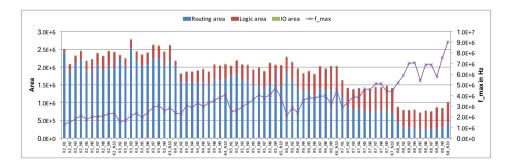

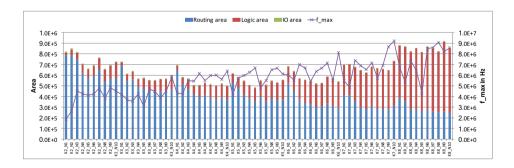

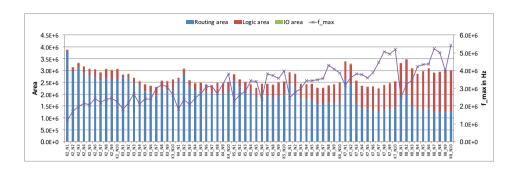

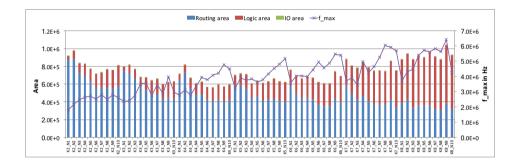

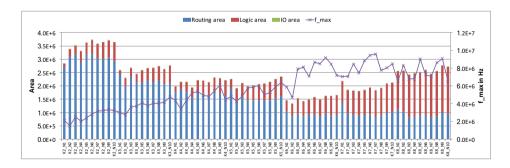

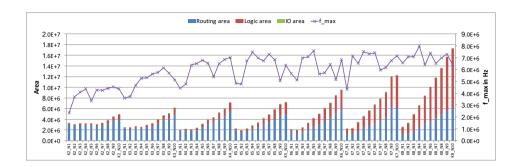

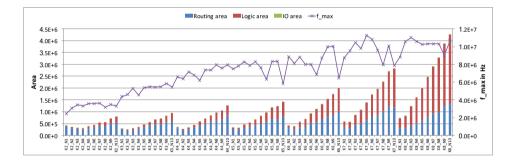

The highly flexible *V-FPGA* architecture can be tuned by more than 20 parameters, including Lookup Table (LUT) size, clustering, 3D stacking, routing structure and many more. The effects of the parameters on area and performance of the architecture are studied and an extensive analysis of over 1400 benchmark runs reveals a high parameter sensitivity with variances up to  $\pm 95.9\%$  in area and  $\pm 78.1\%$  in performance, which proves the high significance of customization when it is up to efficiency. To systematically tune the parameters towards the application's needs, a parametric design space exploration methodology based on suitable area and delay models is proposed.

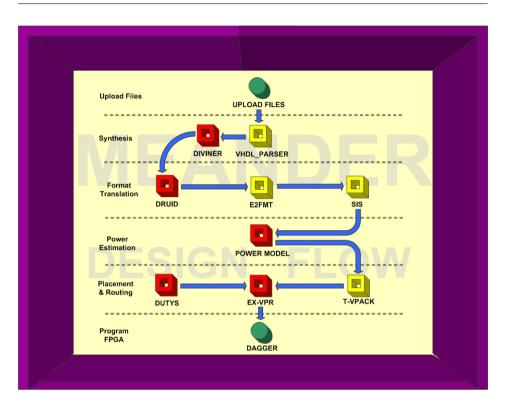

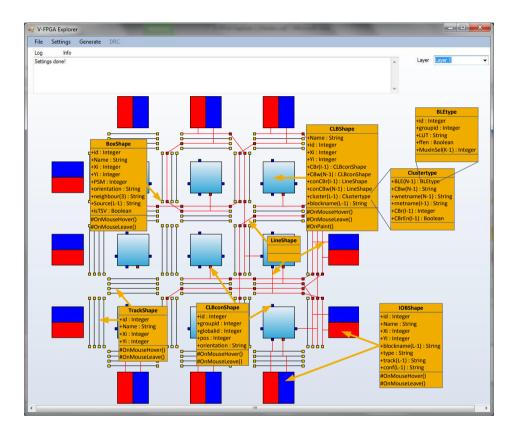

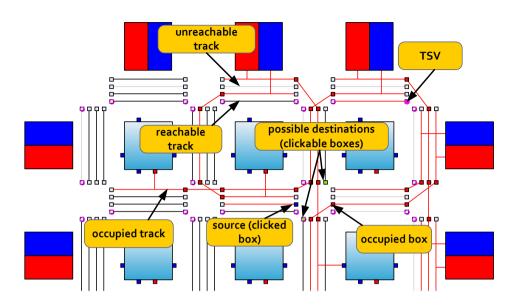

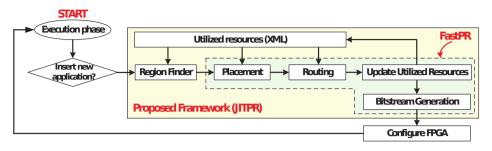

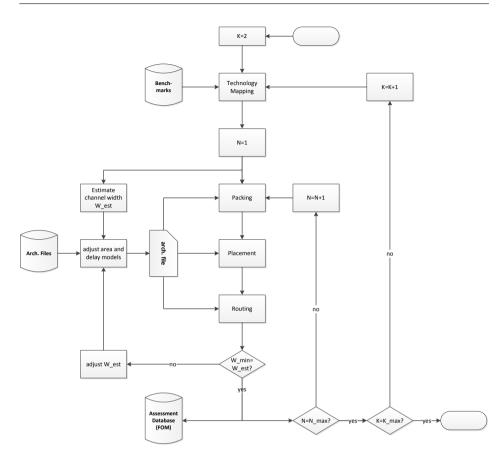

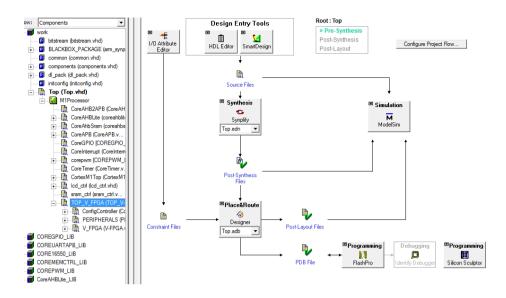

A challenge of custom architectures is their design effort and the need for custom tools. Therefore, this work comprises a framework for architecture generation, design space exploration, application mapping and evaluation. Above all, the *V-FPGA* is designed in a fully synthesizable generic Very High Speed Integrated Circuit Hardware Description Language (VHDL) code, being highly flexible yet eliminating the need for external code generators. System designers can benefit from different types of generic SoC architecture templates to reduce design time. All necessary design steps for application development and mapping onto *V-FPGA* are supported by a tool-flow for electronic design automation, that exploits a collection of existing commercial and academic tools, customized by suitable models and complemented by a new tool called *V-FPGA Explorer*. This new tool not only acts as back-end tool for application mapping onto the *V-FPGA* but is also a graphical configuration and layout editor, a bitstream generator, an architecture file generator for the place & route tools, a script generator and a testbench generator. A specialty is the support of just-in-time compilation with fast algorithms for in-system application mapping.

Finally, this thesis resolves with the closure of *V*-*FPGA* being so far employed in use-case applications in the fields of industrial process automation, medical imaging, adaptive systems and education.

### Zusammenfassung

In den vergangenen drei Jahrzehnten wurde die Entwicklung von Field Programmable Gate Arrays (FPGAs) stark von Moore's Gesetz, Prozesstechnologie (Skalierung) und kommerziellen Märkten beeinflusst. State-of-the-Art FPGAs bewegen sich einerseits dem Allzweck näher, aber andererseits, da FPGAs immer mehr traditionelle Domänen der Anwendungsspezifischen integrierten Schaltungen (ASICs) ersetzt haben, steigen die Effizienzerwartungen. Mit dem Ende der Dennard-Skalierung können Effizienzsteigerungen nicht mehr auf Technologie-Skalierung allein zurückgreifen. Diese Facetten und Trends in Richtung rekonfigurierbarer System-on-Chips (SoCs) und neuen Low-Power-Anwendungen wie Cyber Physical Systems und Internet of Things erfordern eine bessere Anpassung der Ziel-FPGAs. Neben den Trends für den Mainstream-Einsatz von FPGAs in Produkten des täglichen Bedarfs und Services wird es vor allem bei den jüngsten Entwicklungen, FPGAs in Rechenzentren und Cloud-Services einzusetzen, notwendig sein, eine sofortige Portabilität von Applikationen über aktuelle und zukünftige FPGA-Geräte hinweg zu gewährleisten. In diesem Zusammenhang kann die Hardware-Virtualisierung ein nahtloses Mittel für Plattformunabhängigkeit und Portabilität sein. Ehrlich gesagt stehen die Zwecke der Anpassung und der Virtualisierung eigentlich in einem Konfliktfeld, da die Anpassung für die Effizienzsteigerung vorgesehen ist, während jedoch die Virtualisierung zusätzlichen Flächenaufwand hinzufügt. Die Virtualisierung profitiert aber nicht nur von der Anpassung, sondern fügt auch mehr Flexibilität hinzu, da die Architektur jederzeit verändert werden kann. Diese Besonderheit kann für adaptive Systeme ausgenutzt werden.

Sowohl die Anpassung als auch die Virtualisierung von FPGA-Architekturen wurden in der Industrie bisher kaum adressiert. Trotz einiger existierenden akademischen Werke können diese Techniken noch als unerforscht betrachtet werden und sind aufstrebende Forschungsgebiete.

Das Hauptziel dieser Arbeit ist die Generierung von FPGA-Architekturen, die auf eine effiziente Anpassung an die Applikation zugeschnitten sind. Im Gegensatz zum üblichen Ansatz mit kommerziellen FPGAs, bei denen die FPGA-Architektur als gegeben betrachtet wird und die Applikation auf die vorhandenen Ressourcen abgebildet wird, folgt diese Arbeit einem neuen Paradigma, in dem die Applikation oder Applikationsklasse fest steht und die Zielarchitektur auf die effiziente Anpassung an die Applikation zugeschnitten ist. Dies resultiert in angepassten anwendungsspezifischen FPGAs.

Die drei Säulen dieser Arbeit sind die Aspekte der Virtualisierung, der Anpassung und des Frameworks. Das zentrale Element ist eine weitgehend parametrierbare virtuelle FPGA-Architektur, die V-FPGA genannt wird, wobei sie als primäres Ziel auf jeden kommerziellen FPGA abgebildet werden kann, während Anwendungen auf der virtuellen Schicht ausgeführt werden. Dies sorgt für Portabilität und Migration auch auf Bitstream-Ebene, da die Spezifikation der virtuellen Schicht bestehen bleibt, während die physische

Plattform ausgetauscht werden kann. Darüber hinaus wird diese Technik genutzt, um eine dynamische und partielle Rekonfiguration auf Plattformen zu ermöglichen, die sie nicht nativ unterstützen. Neben der Virtualisierung soll die V-FPGA-Architektur auch als eingebettetes FPGA in ein ASIC integriert werden, das effiziente und dennoch flexible System-on-Chip-Lösungen bietet. Daher werden Zieltechnologie-Abbildungs-Methoden sowohl für Virtualisierung als auch für die physikalische Umsetzung adressiert und ein Beispiel für die physikalische Umsetzung in einem 45 *nm* Standardzellen Ansatz aufgezeigt.

Die hochflexible V-FPGA-Architektur kann mit mehr als 20 Parametern angepasst werden, darunter LUT-Grösse, Clustering, 3D-Stacking, Routing-Struktur und vieles mehr. Die Auswirkungen der Parameter auf Fläche und Leistung der Architektur werden untersucht und eine umfangreiche Analyse von über 1400 Benchmarkläufen zeigt eine hohe Parameterempfindlichkeit bei Abweichungen bis zu  $\pm 95,9\%$  in der Fläche und  $\pm 78,1\%$  in der Leistung, was die hohe Bedeutung von Anpassung für Effizienz aufzeigt. Um die Parameter systematisch an die Bedürfnisse der Applikation anzupassen, wird eine parametrische Entwurfsraum-Explorationsmethode auf der Basis geeigneter Flächen- und Zeitmodellen vorgeschlagen.

Eine Herausforderung von angepassten Architekturen ist der Entwurfsaufwand und die Notwendigkeit für angepasste Werkzeuge. Daher umfasst diese Arbeit ein Framework für die Architekturgenerierung, die Entwurfsraumexploration, die Anwendungsabbildung und die Evaluation. Vor allem ist der V-FPGA in einem vollständig synthetisierbaren generischen Very High Speed Integrated Circuit Hardware Description Language (VHDL) Code konzipiert, der sehr flexibel ist und die Notwendigkeit für externe Codegeneratoren eliminiert. Systementwickler können von verschiedenen Arten von generischen SoC-Architekturvorlagen profitieren, um die Entwicklungszeit zu reduzieren. Alle notwendigen Konstruktionsschritte für die Applikationsentwicklung und -abbildung auf den V-FPGA werden durch einen Tool-Flow für Entwurfsautomatisierung unterstützt, der eine Sammlung von vorhandenen kommerziellen und akademischen Werkzeugen ausnutzt, die durch geeignete Modelle angepasst und durch ein neues Werkzeug namens V-FPGA-Explorer ergänzt werden. Dieses neue Tool fungiert nicht nur als Back-End-Tool für die Anwendungsabbildung auf dem V-FPGA sondern ist auch ein grafischer Konfigurations- und Layout-Editor, ein Bitstream-Generator, ein Architekturdatei-Generator für die Place & Route Tools, ein Script-Generator und ein Testbenchgenerator. Eine Besonderheit ist die Unterstützung der Just-in-Time-Kompilierung mit schnellen Algorithmen für die In-System Anwendungsabbildung.

Die Arbeit schliesst mit einigen Anwendungsfällen aus den Bereichen industrielle Prozessautomatisierung, medizinische Bildgebung, adaptive Systeme und Lehre ab, in denen der *V-FPGA* eingesetzt wird.

### Preface

The presented work has been conceived during my time as research associate / PhD student at the Institute for Information Processing Technologies (ITIV) at the Karlsruhe Institute of Technology (KIT) from February 2011 to January 2017. Initially, my main motivation to pursue a PhD was to take the challenge and exceed my own boundaries. Indeed, during my time at the KIT I have grown a lot in my capabilities and gained invaluable experiences, not only in my actual research but also in teaching, project planning, writing project proposals, project management, scientific reviews, publishing, networking, collaborations and international affairs. Furthermore I was able to travel to new places for conferences, workshops and collaborative projects and to meet new people. Above all, the greatest achievement in my life happened during my time at KIT when I met my now wife Shalina and married her. So I can truly say that the time at KIT had a significant impact on my life and I have plenty of reasons to be grateful.

First and above all I am thanking God Almighty for all His goodness, grace and mercy upon my life, without Whom I couldn't have reached this position in my life. He has been my source of strength to Whom I always looked to. He carried and lifted me all throughout my good days and desperate days. Time and again He showed His sovereignty and faithfulness to me and proved that He has the final say over everything.

I want to express my sincere gratitude towards my supervisor Prof. Dr-Ing. Dr. h. c. Jürgen Becker for enabling me to pursue a PhD at his Institute, for supporting me in all possible ways and for his guidance even during my tough times. Especially I appreciate his trust on me from the very beginning and that he granted me the freedom to explore the research fields that I like and to develop therein.

I am thanking Prof. Dr.-Ing. Klaus Hofmann for being the second referee, for all his support and for the very interesting talks that we had during the preparation of the PARFAIT project proposal. I really enjoyed the fruitful time we had spent as a team together with Tillmann Krauss.

Special thanks go to Prof. Dr.-Ing. Michael Hübner who not only injected the idea of virtual FPGAs in me but also persistently urged me to pursue a PhD. Even though I refused initially as it was not part of my plans, his perseverance was like a call and made me to rethink it seriously and to chose this path. Sometimes we need destiny helpers in our lives and he was definitely my destiny helper in this regard.

I want to thank Prof. Dimitrios Soudris, Prof. Kostas Siozios and Dr. Charalampos (Harry) Sidiropoulos from the National Technical University of Athens (NTUA) for the great and very fruitful collaboration that we had. The CAD tools from NTUA and the V-FPGA architecture from KIT suddenly fitted perfectly together and built a symbiosis that enabled "crazy" research ideas and resulted in numerous joint publications in reputed conferences and journals and a "best paper" award. Furthermore I would like to thank all the students who contributed to the implementation of the *V-FPGA* either as part of their thesis or through HiWi jobs. Thomas Bruckschlögl contributed with the dynamic defragmentation strategy and the implementation of the Snapshot functionality. Michael Mechler was involved in the implementation of the clustering and the 3D extension. Marc Bo Hartmann helped with the tile based structure. Weiqiao Ding was involved in conducting experiments for design space exploration, in integrating the clustering with the tile based structure and in the implementation of the fractional input MUX.

I'm so much grateful for all the love, care, support and sacrifices of my parents Georg and Ileana Figuli. They have been my constant source of comfort and encouragement at all times even when the sun didn't shine through. My special thanks goes to my brother's family Daniel, Roxana and Sofia Figuli for their continual advice, support and help all throughout my PhD career. My niece Sofia always brought joy and warmth to my heart that made me to press on.

I have not enough words to express my thanks to my wife Shalina. She was a great source of encouragement and took me out even when I was drawn in desperation. She stood with me side by side through all the tough times and through sleepless nights. She believed in me when I did not. She supported me in all possible ways a wife can do. In all situations she showed me her love and I love her so much. My warm thanks extend to also my parents-in-law George and Vasantha Ford for upholding me with their love and prayers. I'm also grateful to my sister-in-law's family Suvitha and Alfred for being there for me though they are far away.

Last but not least I'm indebted to all my friends and relatives who made my journey more beautiful, enjoyable and lively. It won't be complete if I don't thank all those who persevered with me through their prayers.

Karlsruhe, July 2017 Peter Figuli

### Contents

| 1. | Intro        | oduction                                              | 1        |  |  |  |  |  |  |  |  |

|----|--------------|-------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

|    | 1.1.         | Trends in Reconfigurable Architectures                | 1        |  |  |  |  |  |  |  |  |

|    | 1.2.         | Need for Specialization and Customization             | 4        |  |  |  |  |  |  |  |  |

|    | 1.3.         | Virtualization from different viewpoints              | 5        |  |  |  |  |  |  |  |  |

|    | 1.4.         | Challenges and Proposed Solutions                     | 7        |  |  |  |  |  |  |  |  |

|    | 1.5.         | Contribution                                          | 8        |  |  |  |  |  |  |  |  |

|    | 1.6.         | Outline                                               | 9        |  |  |  |  |  |  |  |  |

| _  | _            |                                                       | 11       |  |  |  |  |  |  |  |  |

| 2. |              | undamentals                                           |          |  |  |  |  |  |  |  |  |

|    |              | Efficiency in Context of This Work                    | 11       |  |  |  |  |  |  |  |  |

|    | 2.2.         | $\partial$                                            | 12       |  |  |  |  |  |  |  |  |

|    |              | 2.2.1. Fine Grain Reconfigurable Architectures        | 12       |  |  |  |  |  |  |  |  |

|    |              | 2.2.2. Heterogeneous Reconfigurable Architectures     | 16       |  |  |  |  |  |  |  |  |

|    |              | 2.2.3. Programming Technologies                       | 18       |  |  |  |  |  |  |  |  |

|    |              | Partial and Dynamic Reconfiguration                   | 20       |  |  |  |  |  |  |  |  |

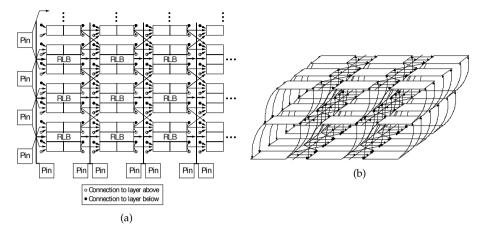

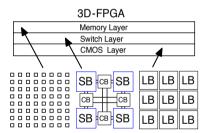

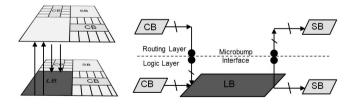

|    | 2.4.         | 3D Integration                                        | 21       |  |  |  |  |  |  |  |  |

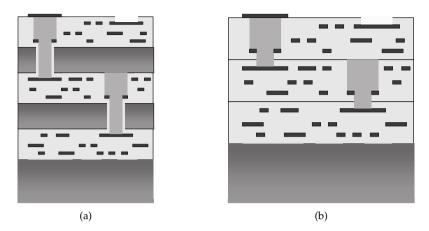

|    |              | 2.4.1. Wire bonded                                    | 22       |  |  |  |  |  |  |  |  |

|    |              | 2.4.2. Microbump                                      | 22       |  |  |  |  |  |  |  |  |

|    |              | 2.4.3. Through Via                                    | 23       |  |  |  |  |  |  |  |  |

|    |              | 2.4.4. Contactless                                    | 24       |  |  |  |  |  |  |  |  |

|    | 2.5.         | Design Steps for Application Mapping onto FPGAs       | 25       |  |  |  |  |  |  |  |  |

| 2  | Pola         | ted Work and State of the Art                         | 27       |  |  |  |  |  |  |  |  |

| э. | 3.1.         |                                                       |          |  |  |  |  |  |  |  |  |

|    | 3.2.         |                                                       | 28       |  |  |  |  |  |  |  |  |

|    |              |                                                       |          |  |  |  |  |  |  |  |  |

|    |              | Generic CAD Tools for FPGAs                           | 33<br>37 |  |  |  |  |  |  |  |  |

|    | 3.4.<br>3.5. | 3D FPGA Architectures                                 | 37<br>39 |  |  |  |  |  |  |  |  |

|    | 5.5.         | SD FFGA Architectures                                 | 39       |  |  |  |  |  |  |  |  |

| 4. | V-FI         | PGA: Virtual Field Programmable Gate Array            | 43       |  |  |  |  |  |  |  |  |

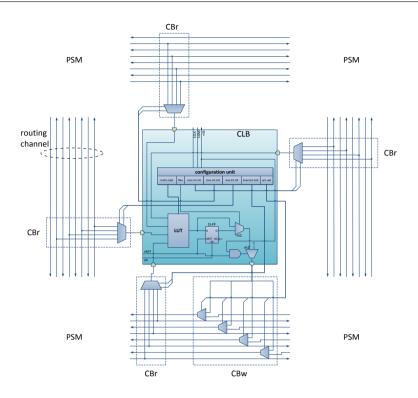

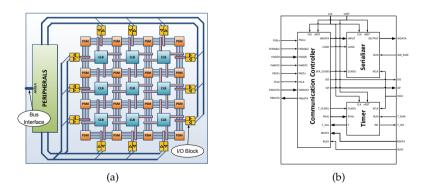

|    | 4.1.         | 2D Generic Architecture                               | 46       |  |  |  |  |  |  |  |  |

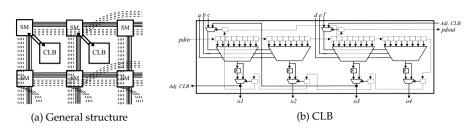

|    |              | 4.1.1. Configurable Logic Blocks                      | 46       |  |  |  |  |  |  |  |  |

|    |              | 4.1.2. I/O Blocks                                     | 53       |  |  |  |  |  |  |  |  |

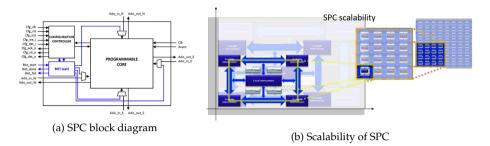

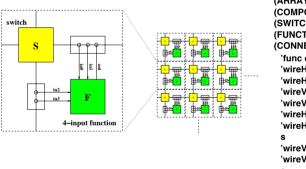

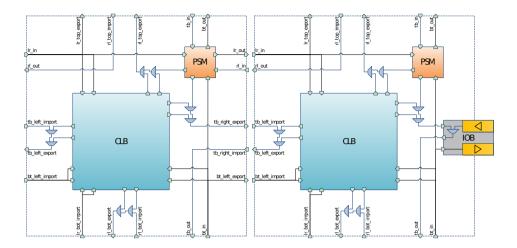

|    |              | 4.1.3. Programmable Switch Matrix                     | 54       |  |  |  |  |  |  |  |  |

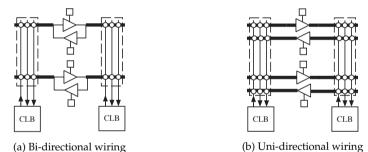

|    |              | 4.1.4. Bi-directional Tracks                          | 58       |  |  |  |  |  |  |  |  |

|    |              | 4.1.5. Clustering                                     | 61       |  |  |  |  |  |  |  |  |

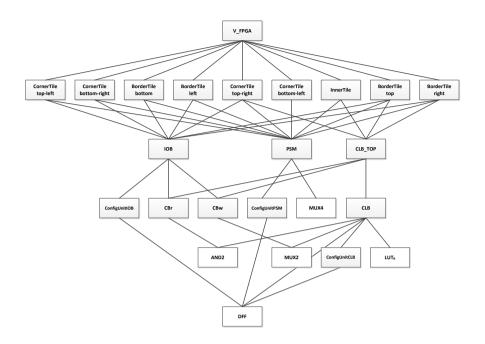

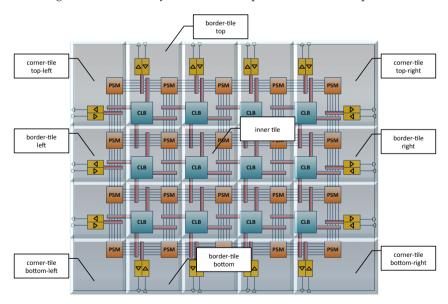

|    |              | 4.1.6. Tile Based Structure                           | 68       |  |  |  |  |  |  |  |  |

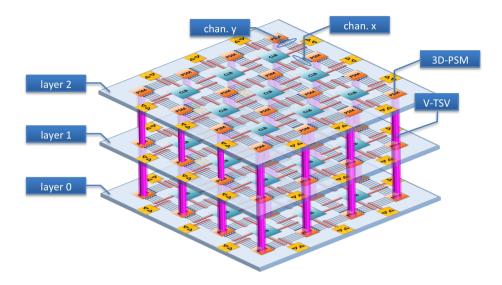

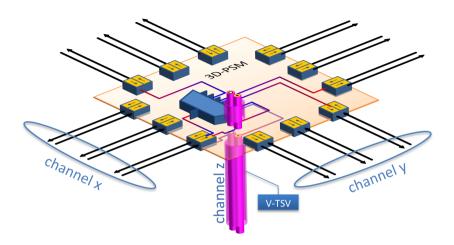

|    | 4.2.         | 3D Extension                                          | 70       |  |  |  |  |  |  |  |  |

|    |              | 4.2.1. The customizable 3D <i>V-FPGA</i> Architecture | 71       |  |  |  |  |  |  |  |  |

|    | 4.3. | Configuration Mechanisms                                                    | 73  |

|----|------|-----------------------------------------------------------------------------|-----|

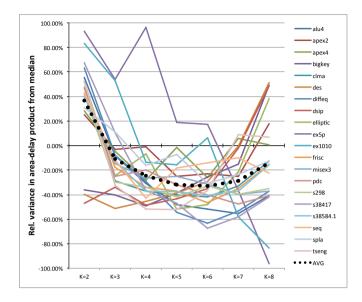

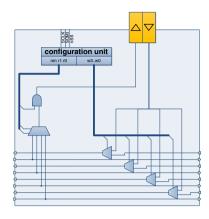

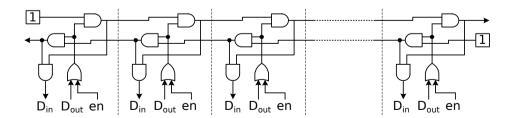

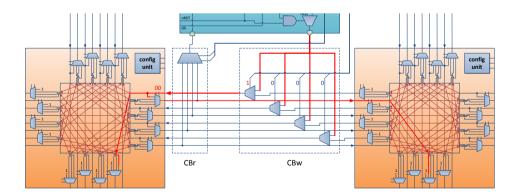

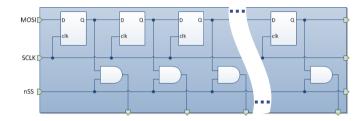

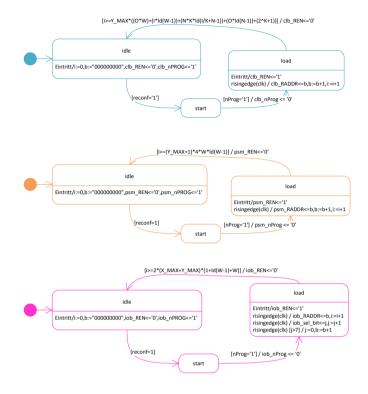

|    |      | 4.3.1. Configuration Units                                                  | 73  |

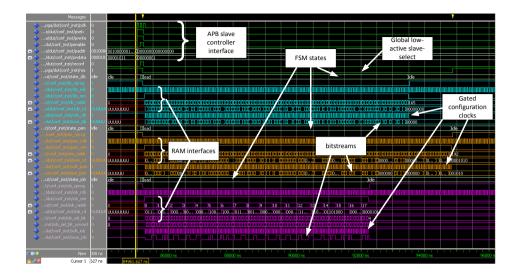

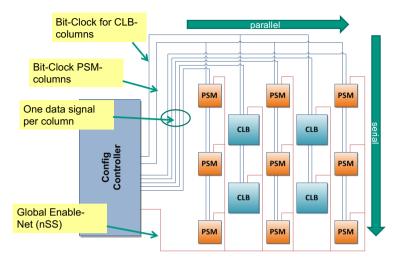

|    |      | 4.3.2. Configuration Controller                                             | 74  |

|    |      | 4.3.3. Area vs. Speed Trade-offs in Configuration Infrastructure Topologies | 77  |

|    |      | 4.3.4. Coarse-Grain Partial Reconfiguration                                 | 78  |

|    |      | 4.3.5. Fine-Grain Partial Reconfiguration                                   | 80  |

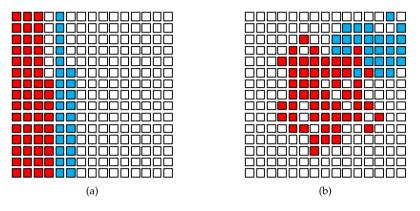

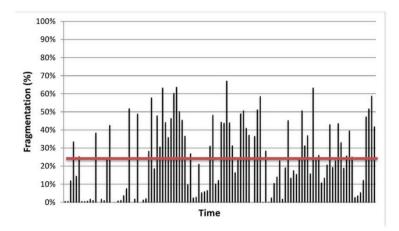

|    |      | 4.3.6. Runtime Task Migration and Defragmentation                           | 82  |

|    | 4.4. |                                                                             | 89  |

|    |      | 4.4.1. ViSA: VLIW Inspired Slot Architecture                                | 89  |

|    |      | 4.4.2. ViSA-VIS: ViSA and <i>V-FPGA</i> Integrated System                   | 93  |

|    | 4.5. | о ,                                                                         | 95  |

|    |      |                                                                             |     |

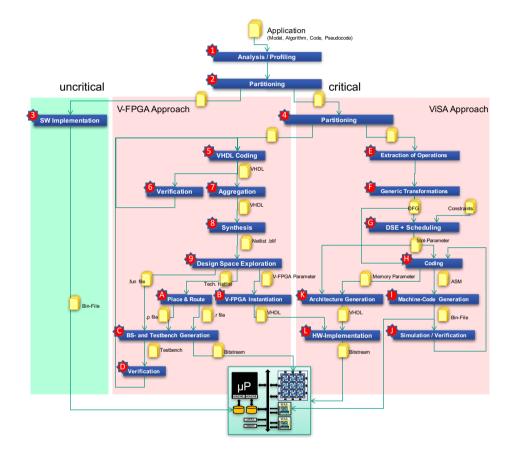

| 5. |      | lication Mapping and Toolflow                                               | 97  |

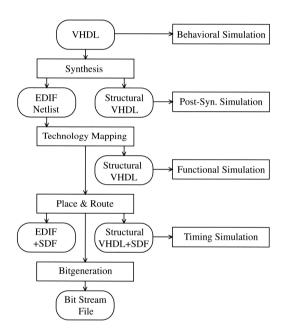

|    |      | Design Entry and Synthesis with Altera Quartus II and QUIP                  |     |

|    | 5.2. | $O_{2}$ 11 $O'_{2}$                                                         |     |

|    | 5.3. |                                                                             |     |

|    | 5.4. |                                                                             |     |

|    |      | 5.4.1. Graphical Editor                                                     |     |

|    |      | 5.4.2. Import from External P&R Tools                                       | 113 |

|    |      | 5.4.3. Bitstream Generation                                                 | 122 |

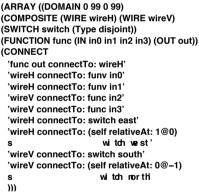

|    |      | 5.4.4. Architecture File Generator                                          | 125 |

|    |      | 5.4.5. Automated Testbench Generation with <i>V-FPGA Explorer</i>           | 127 |

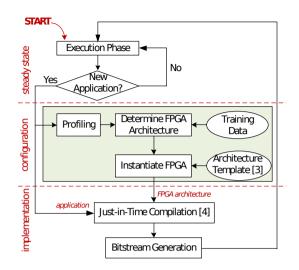

|    | 5.5. | Just-in-Time Compilation                                                    | 128 |

|    |      | 5.5.1. Target Architecture                                                  |     |

|    |      | 5.5.2. JIT Compilation Flow                                                 | 130 |

|    |      | 5.5.3. Run-time Enhancements                                                |     |

|    |      | 5.5.4. Experimental Results                                                 |     |

|    | 5.6. | Area and Delay Models for Optimized Application Mapping and DSE             |     |

|    |      | Conclusion                                                                  |     |

| _  | ~    |                                                                             |     |

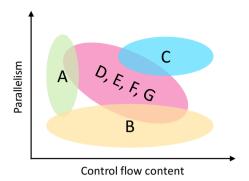

| 6. |      | cepts and Methodologies for Customizing Reconfigurable Architectures        |     |

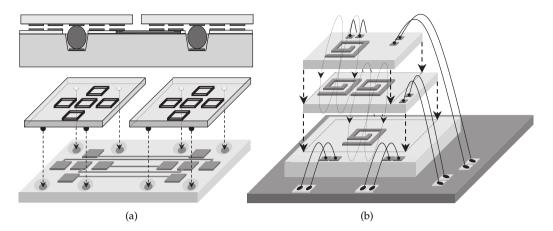

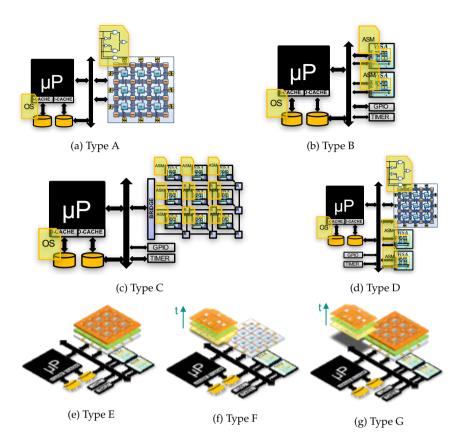

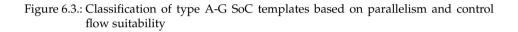

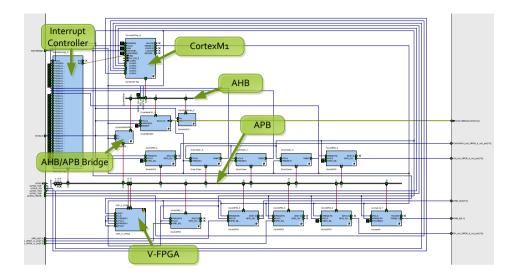

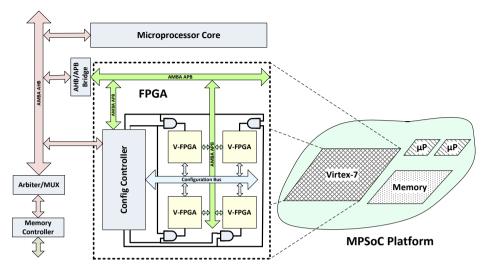

|    |      | Generic SoC Architecture Templates                                          | 137 |

|    | 6.2. |                                                                             | 141 |

|    |      | 6.2.1. V-FPGA Customization                                                 |     |

|    |      | 6.2.2. <i>ViSA</i> Customization                                            |     |

|    | 6.3. |                                                                             |     |

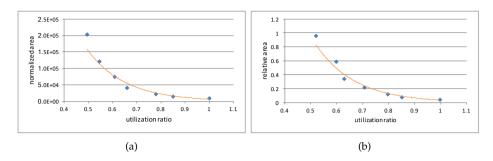

|    |      | 6.3.1. Average Utilization Ratios                                           |     |

|    |      | 6.3.2. Generic Equivalents                                                  |     |

|    | 6.4. | Design Space Exploration Methodology                                        |     |

|    | 6.5. | Conclusion                                                                  | 157 |

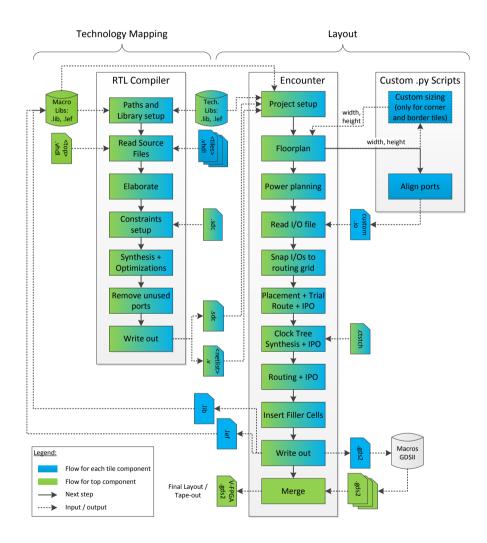

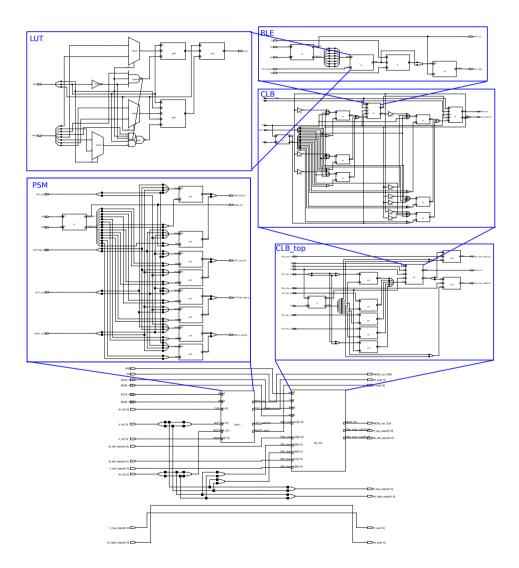

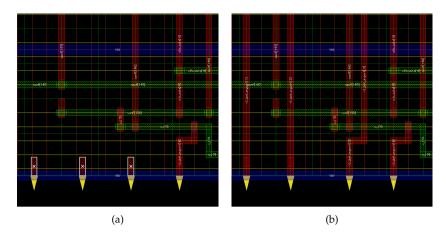

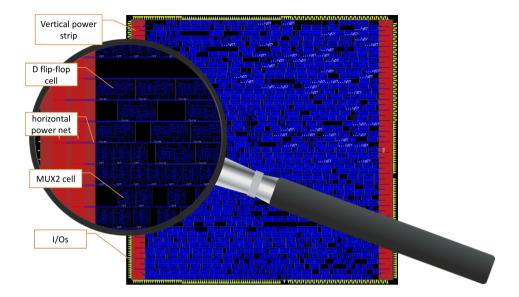

| 7  | Tara | get Technology Mapping and Characterization Flow                            | 159 |

| •• |      |                                                                             |     |

|    |      | From Virtual to Physical                                                    |     |

|    | 1.2. | 7.2.1. Standard-cell Mapping                                                |     |

|    |      | 7.2.1. Standard-cen Mapping         7.2.2. Hierarchical Layout              |     |

|    |      | 7.2.2. Inclatencal LayOut                                                   | 101 |

| 7.3. Characterization Fow                                                                                                                                                                                                                                                                                                               |                                                                                |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>8. Use Cases</li> <li>8.1. Industrial Process Automation</li></ul>                                                                                                                                                                                                                                                             | PGA181<br>. 186<br>. 188<br>. 193<br>. 193<br>. 196<br>. 200<br>. 200<br>. 201 |  |  |  |  |  |

| 9. Conclusion and Future Work                                                                                                                                                                                                                                                                                                           | 205                                                                            |  |  |  |  |  |

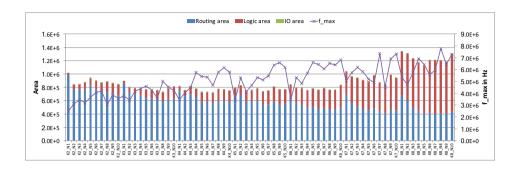

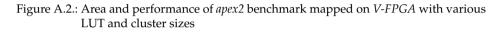

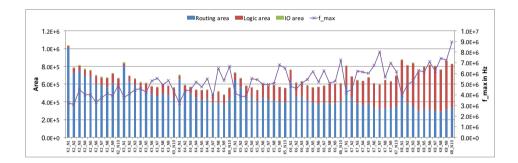

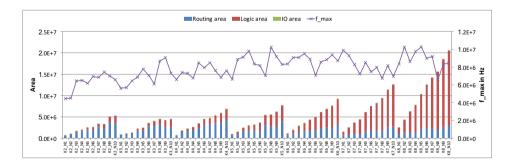

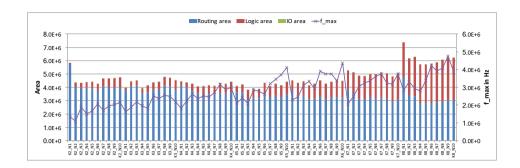

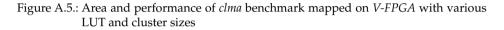

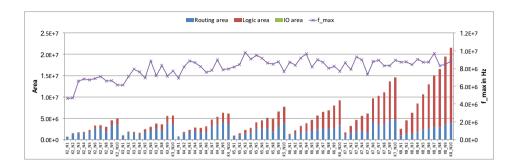

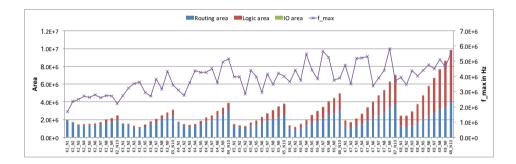

| <ul> <li>A. Appendix</li> <li>A.1. Evaluation of MCNC Benchmarks Mapped on <i>V-FPGA</i> with Various LUT and Cluster Sizes</li> <li>A.2. Architecture File Template</li> <li>A.3. Frame File Template for Testbench Generation in <i>V-FPGA Explorer</i></li> <li>A.4. Python Script for Aligning Block I/Os of Tile Macros</li> </ul> |                                                                                |  |  |  |  |  |

| Indexes<br>Figures                                                                                                                                                                                                                                                                                                                      | <b>229</b><br>229<br>234                                                       |  |  |  |  |  |

| Acronyms Abbreviations                                                                                                                                                                                                                                                                                                                  |                                                                                |  |  |  |  |  |

| Bibliography                                                                                                                                                                                                                                                                                                                            | 241                                                                            |  |  |  |  |  |

| Supervised Student Research                                                                                                                                                                                                                                                                                                             | 251                                                                            |  |  |  |  |  |

| Own Publications                                                                                                                                                                                                                                                                                                                        | 253                                                                            |  |  |  |  |  |

### 1. Introduction

Field Programmable Gate Arrays (FPGAs) as the prime example of reconfigurable architectures are no longer just prototyping and research devices, but are meanwhile experiencing mass-deployment in products and applications. In their infancy they were almost abandoned due to their area inefficiency compared to ASICs, yet now their density is high enough to accommodate very complex circuits and the flexibility that they offer is so sweet and compelling that they have superseded ASICs in many domains despite the ASIC gap. Even though FPGAs are a platform for implementing application specific digital circuits, they are actually general purpose off-the-shelf devices. As things get more ambitious one might realize that *"one size fits all"* probably fits none really well.

This thesis goes one step further and advocates a new paradigm of application or domain specific FPGAs. As such, the main focus is the customization of FPGA architectures towards the needs and peculiarities of the applications that they are going to implement. After a reflection of the trends in reconfigurable architectures (Section 1.1), the *raison d'être* for this new paradigm is deduced in Section 1.2.

A second emphasis in this thesis is laid on virtual FPGAs, which add a new dimension of flexibility and are motivated in Section 1.3. Thereby, to be upfront with it, virtualization is not a must for a custom FPGA and customization is not a must for a virtual FPGA. However, the area hungry virtualization benefits from customization. In return, virtualization is a vehicle for prototyping, exploring and exchanging custom architectures and can ensure seamless and instant portability across diverse custom FPGAs or commercial off-the-shelf FPGAs.

### 1.1. Trends in Reconfigurable Architectures

To understand the trends and to anticipate the future it is always wise to reflect first the past. Reconfigurable architectures in context of Field Programmable Gate Arrays (FP-GAs) have to date a history of three decades and their evolution has been mainly driven by Moore's Law [76], CAD tools, economic aspects, commercial exploitation, application fields and the entering into new markets. In [102] Trimberger divides the evolution of FPGAs into three epochs: the age of invention, the age of expansion, and the age of accumulation, which are summarized from Trimberger's paper and further references in the following.

**Age of invention (AD 1984-1991):** The first commercial FPGA, the Xilinx XC2064, was invented in 1984 by Bill Carter [78]. It featured 64 logic blocks with each one 3-input LUT and one register, and 58 I/O blocks. The FPGA was designed without CAD tools in a modified CMOS logic style with around 85000 transistors by repetitive use of a modular

CLB and a modular I/O block. The XC2064 dies were manufactured in a 2.5  $\mu$ m process technology with two metal layers on a Seiko fab and the die size measured around 300 mil x 300 mil. Consequently the first FPGA with only 64 logic cells suffered greatly area inefficiency and the large die was prone to low yield and high costs per chip. Furthermore, the programming bitstream needed to be stored on an external memory chip (initially PROM) and loaded during startup. This means that functionality per dollar and space was rather low and it was not competitive to the alternatives. This focussed the attention towards increasing area efficiency as a high priority in further developments and process technology.

Actel was able to make a big step in area efficiency by introducing the anti-fuse technology for programming the FPGA, eliminating the need for configuration memory cells and external PROM. However, this came at the expenses of one-time programmability.

Even though it turned out early that a granularity of 4 inputs per LUT provides a good trade-off between area and delay, in practical applications they suffered from low utilization ratios (e.g. due to unused inputs and configurations), wasting area. Consequently this set off a wave towards very fine-grained logic cell architectures with two-input function generators ([5], [40], [77]) or even at the granularity of individual transistors with programmable interconnections through anti-fuse [66].

In contrast to PALs, interconnection architectures in FPGAs followed 2D topologies with short interconnect segments between adjacent blocks and pass transistor switches, yielding a more efficient wiring. However, the pass transistor networks led to increased signal delay due to their accumulated series resistance and large capacitance. Furthermore, since interconnect networks consumed area which is not accountable for logic, they were integrated very stingily by the FPGA architects, leading to routing congestions and challenges in utilization of the FPGA resources.

Age of expansion (AD 1992-1999): The age of expansion began with an aggressive addition of interconnects to FPGAs due to the launch of chemical-mechanical polishing (CMP), which made the birth of stacked metal layers possible thereby trailing certain significant effects in the era of expansion. Area was no longer the precious commodity as it could be traded off for performance, features and ease-of-use. On one hand the immense growth in capacity with decrease in costs propelled large FPGA applications whereby manual automation was no longer in discussion, paving way for automated synthesis, placement and routing as part and parcel of the design process. On the other hand, upgradation in process scaling as well as the cheaper metal usage made automated placement more precise. It also promoted performance to a great extent by its longer segmented interconnects making physically distant logics logically closer and eliminating exact alignment of logic cells, which are done for the sake of higher performance. Opposing to the payoff is the wastage of unused parts of the metal wire even though it is in the acceptable range. This era put an end to logic-waste-based fine-grained architectures, brought efficient architectures which are based on starving interconnects to an end and doomed timemultiplexed devices. The only thriving companies were Altera, AT&T and Xilinx. The surge in Moore's law pressurized the FPGA vendors to take possession of the leadingedge process technology to keep up the balance between doubling capacity and halving costs, throwing companies with technologies such as EPROM, Flash and antifuse into chaos due to their technology dependent architectures. Though in the mid-1990s LUT- based architectures were "synthesis unfriendly", they survived and started to dominate once its simplicity in mapping, efficient layout in silicon as memories and interconnect saving capabilities have been explored and exploited persuading companies like Xilinx, Altera and AT&T/Lucent to adopt LUT architectures along with distributed-memory-cell architectures. The latter due to its architectural freedom and its proficiency in giving the FPGA vendors a nearly universal access to process technology. During the age of expansion, the FPGA's capacity growth started to address majority of ASIC applications and fought its way through EDA and ASIC technologies.

Age of accumulation (AD 2000-2007): The birth of new millennium brought FPGAs a huge market in the data communications industry. Their high-throughput, real-time computation and generality earned them a wide range of applications including control and automotive systems. Though hiking capacity growth escalated market growth, increased product cost started to weigh down the customers. This conflicting challenge was tackled by producing lower-capacity, lower-performance "low-cost" FPGAs for low-end markets and apprising the high-end markets with libraries of soft logic (IP) for important functions like microprocessors (Xilinx MicroBlaze and Altera Nios), memory controllers and various communication protocol stacks. For example, Ethernet MAC was implemented as soft core in Virtex-II before it was available as transistors in Virtex-4. FPGAs were not only expected to increase the logic size but were anticipated by the users to adhere to their system standards by keeping the cost and power efficiency under check, thereby compelled the inclusion of logic blocks such as large memories, microprocessors, multipliers, flexible I/O and source-synchronous transceivers. Built from custom-designed transistors made them often more efficient than ASIC implementations. The resultant "Platform FPGA" was a collection of programmable logic, soft core IPs and logic blocks. Especially the launch of logic generators like System Generator from Xilinx and DSP Builder from Altera assisted the users to build their own functionality from the available dedicated functions and soft logic. Embedded (System) Design Kits made possible to have Linux OS running on FPGA processor. Finally, the age of accumulation came to an end with Moore's law being under a subject of discussion as performance came to a slowdown in trade-off with power even though improvements in cost and capacity continued to stepup.

**Today** one of the major technological trends in reconfigrable computing is the formation of programmable SoC hybrids combining programmable logic, microprocessors, on-chip networks and interfaces in a single device. The integration of two or more circuit classes (e.g. FPGA, processor, dedicated HW logic, etc.), that classically have been treated and interconnected as separate chips, has tremendous benefits in terms of efficiency. For instance, on chip interconnects require less area, are more performant and allow a much higher complexity than off-chip interconnects, meanwhile reducing the pin count and the silicon- and power-hungry IO buffers. Recently, major FPGA vendors have realized this potential and are showing serious efforts towards heterogeneous SoC platforms [110] [73] [52].

With respect to new workloads, we can see a hype of extending the classical application fields of FPGAs by machine learning, artificial intelligence, search engine indexing, encryption and data compression [47]. We are currently witnessing a new major breakthrough of FPGAs by employing them in data centers and cloud farms to accelerate workloads. Prominent projects are, e.g. Intel Xeon+FPGA Integrated Platform [45] or Microsoft's Catapult project [83]. Recently, Amazon started employing FPGAs in cloud farms, where integrated FPGA instances can be rented to accelerate applications in the cloud [9].

With the rising complexity and the demand for faster time to market high-level synthesis and growing IP libraries are the most obvious trends in EDA for FPGAs. This is especially essential for entering into markets that are dominated by CPU or GPU devices and where large pools of developers are trained for and used to utilize higher level programming languages and models. But also in terms of CPU-FPGA hybrid solutions the process of outsourcing of CPU workloads to FPGAs, preferably during runtime, benefits from abstraction layers that hide the underlying hardware. One of the most recent trends is the support of OpenCL in this direction and Altera (now part of Intel) and Xilinx put lots of efforts in it.

### 1.2. Need for Specialization and Customization

While devices like the Xilinx ZYNQ or Altera Cyclone V SoC are getting closer to general purpose computing, there is also an increasing need for specialized devices for high volume, low cost and low power applications, e.g. in the fields of mobile devices, Cyber-Physical System (CPS), Internet of Things (IoT), sensor networks, wearables and others. The tight power budgets of such devices are hard to meet by general purpose FPGAs. Wireless devices need to operate for a long time from battery, some need even to be selfsustained through energy harvesting. Even wired devices can have tight power limitations. For instance, intelligent sensor nodes that use the same one wire for power supply and for Highway Addressable Remote Transducer (HART) communication have a current limit of <4mA for their internal electronics in order to not disturb the 4-20 mA current-modulated communication which is on the same wire. Apart from power also form-factor, size and price play an important role, which are hard to meet with current general purpose Commercial off-the-Shelf (COTS) FPGAs. If FPGAs are to supersede ASICs in these domains, then they need more specialization.

With respect to high performance computing, the recent embracement of FPGAs by large scale contemporary and upcoming markets (Datacenter, Cloud, Ai, Security) presumably sets the volumes high enough to afford specialized FPGAs for certain application classes. According to [47] it is unlikely that FPGAs employed in data centers will take the role of general purpose computing. Instead, they are seen as a companion to CPUs accelerating certain workloads. Meanwhile, power matters more and more also in data centers, which according to [45] is a strong motivation to replace GPUs by FPGAs. With power, performance, hyper workload classes and the high volumes in mind, certainly specialization could pay out in these highly competitive markets, where chip giants are currently reshuffling the cards by stacking up with strategic acquisitions and fusion of technologies.

From a high level viewpoint, another more general need for specialization is coming from the limitations that the semiconductor industry is running against. In former decades Moore's law (originally formulated in 1965 in [76] and revised ten years later) predicted

the doubling of transistors per area every two years, which used to be a quite reliable selffulfilling prophecy. Also the formulations of Dennard [29], which in essence conclude that power requirements are proportional to actual area, which in conjunction with Moore's law means that performance-per-watt would increase when transistor density increases, were valid in former decades. This way, the industry was able to deliver generation by generation more value to their customers and an increased efficiency by roughly 40% per generation through scaling alone [19].

Today, while Moore's law is threatened but probably still continues for some time, Dennard Scaling is already invalid. It came to an end roughly one decade ago because at feature sizes below 65 nm the exponential growth of leakage current is not neglect-able anymore and also threshold voltage is difficult to reduce further. This impedes the downscaling of operating voltage and increases the power and heat density with shrinking feature sizes. The consequence is that scaling alone doesn't automatically lead to efficiency improvements anymore. Yet the market is used to get more and more value with every new generation, which is also the reason why they have been investing again and again in the latest technology. This puts now pressures on increasing the efficiency of integrated circuits through other means.

One option to achieve this is through specialization on architecture level, in order to obtain a better fit of the architecture to the application and consequently a higher efficiency. Naturally, specialization demands a high price in terms of effort, especially if things need to be developed from scratch. This can be considerably mitigated through generic architecture models (and corresponding tools) that can be customized to fit the application.

### 1.3. Virtualization from different viewpoints

**Portability.** FPGAs are gaining more and more popularity and their large scale deployment surely will make them more and more affordable as the NRE costs will be shared by more units. If this movement continues at this rate, FPGAs will become mainstream in the near future and indispensable in our day-to-day systems and applications such as entertainment, communication, assistance, automation, cyber-physical systems, Internet of Things (IoT) devices, cloud services, monitoring, controlling, and many more. There will be the situation that FPGA based devices and applications change more often than how it is today, thereby making it necessary to loosen the bond between application and the execution platform [34].

Virtualization is a key for instant portability and migration of applications even on bitstream level without redesigning or recompiling. Thereby, an optimized reconfigurable architecture as a virtual layer can be mapped onto an existing COTS FPGA, while the application itself will be executed on the virtual layer, thus being independent of the underlying physical platform. The eminent advantage is that the specification of the virtual architecture can persist, while the hosting physical platform can be exchanged by another one. Not only can this be used for task migration scenarios during runtime but is also a strong aspect for the industry to have a "second source" in order to overcome disruptive situations like the discontinuation of the employed COTS FPGA platform. In such cases, the same bitstream can be executed on another hosting COTS FPGA from another vendor through virtualization. **Partial and Dynamic Reconfiguration.** The configuration mechanisms of a virtual FPGA can be decoupled from the configuration mechanisms of the underlying physical platform. This can be exploited to enable partial and dynamic reconfiguration on platforms that don't support it natively. This is a very powerful aspect of FPGA virtualization as it actually extends the capabilities and functionality of a COTS FPGA through the virtual layer. Dynamic partial reconfiguration in particular is a desirable feature as it allows to reuse parts of the chip area for temporal exclusive functions on demand [18] [103] [50] [35]. It virtually increases chip area compared to static solutions that need to accommodate all functions at the same time even though they are not needed simultaneously. Many COTS FPGAs, especially low power devices such as Actel's ProASIC3, Igloo, etc., don't offer dynamic reconfiguration. In [50] and [35] this limitation is canceled through virtualization.

**Adaptivity.** The added level of flexibility through virtualization enables to adapt the custom FPGA architecture to the workloads. Being mapped onto a programmable platform, the architecture can be altered any time and in case the underlying platform supports dynamic partial reconfiguration, this can happen during run time operation. The adaptivity can be exploited to tune the architectural parameters of a custom FPGA for an optimized befitting with respect to the application, leveraging the Reconfigurable Computing paradigm to new dimensions in space and time and following a new paradigm in which the application comes first and the architecture follows as opposed to the old off-the-shelf approaches.

**Prototyping and Emulation.** Virtualization serves also as a vehicle for prototyping custom physical FPGA architectures, be it stand-alone or embedded in systems, and associated runtime environments. The custom FPGA and other system(-on-chip) components along with monitoring and debug logic can be mapped on a COTS FPGA or a multi-FPGA platform to test the design. Since virtualization exploits the same degree of parallelization as the intended ASIC realization, this makes the testing and benchmarking of such complex systems much faster than through simulation on a PC, which is mainly sequential. Following the observations of [56] on the ASIC gap, we can presume this type of virtualization/prototyping to be only around  $3.4 \times$  to  $4.6 \times$  slower than a targeted standard-cell implementation of the custom FPGA architecture. One could take advantage on this to initially release an early fully-functional "*light*" variant of a new product with a COTS FPGA virtualizing the new reconfigurable system-on-chip architecture. Later, the product line can be updated once the new higher-performance chip is fabricated. This strategy not only reduces time-to-market of new products but can also help making the digital portion of the intended chip mature at the first manufacturing attempt, because already the experiences and customer feedbacks from the virtualized version can be used to improve the design early enough before chip manufacturing. Furthermore, the risk of the product is lower as the initial virtualized version can be altered through reconfiguration in case of faults. This helps to cope with infancy in the initial product phase.

**Accessibility.** Another benefit of virtualization is accessibility. Novel FPGA architectures can be accessed and made tangible through virtualization without the need of expensive

chip implementation. This way, researchers and students can conduct functional experiments on custom FPGA architectures that are accommodated by regular COTS FPGAs, which are usually present in any university. Same applies to educational workshops and training sessions. Furthermore, tools and application developers can start developing and debugging for custom FPGAs in parallel to the chip development and prior to production, as they have access to the new FPGA architecture through virtualization. This not only affects the applications to be mapped onto the new FPGA, but also the interplay with other system components, such as microprocessor, memory, network interfaces, etc..

### 1.4. Challenges and Proposed Solutions

Customization and virtualization come with a number of principle challenges that are systematically addressed by the work of this thesis:

1. The **design efforts** to create custom FPGA architectures and programmable SoCs are very high if everything needs to be developed from scratch. This might impede the acceptance of application specific custom FPGAs.

-> Proposed solution: The design efforts are minimized by generic architecture templates, that can be customized through parameters. This way system architects don't need to develop the FPGA architecture, but just change the parameters to obtain an optimized suitable architecture for the application. The more parameters the generic architecture offers, the better is the achievable fit.

2. Architectural **design choices** can get rather complex due to interdependency of parameters and trade-offs. Especially the introduced freedom can be also a pain if the number of parameters is overwhelming.

-> Proposed solution: The process of choosing the right design parameters is assisted by model based parametric design space exploration.

- Custom FPGA architectures require custom EDA tools for application mapping and design space exploration.

Proposed solution: Flexible toolflow that seamlessly adapts to the customized architectures through parameterizable architecture models.

- 4. Static analysis is not sufficient for **evaluating** dynamic systems with applications or benchmarks mapped onto the custom FPGA. Event or time driven simulation is able to do so but is too slow to observe a relevant time frame in acceptable tool runtime. Furthermore, the interplay with other system components that are not modelled is not possible in simulation.

Proposed solution: Prototyping through virtualization on a COTS FPGA exploits the same degree of parallelism as the target, thus is much faster than simulation. Existing external components can be interconnected and don't need to be modelled.

5. Virtual FPGAs have the drawback of a high area overhead and also performance is degraded compared to physical FPGAs due to the additional layer.

-> Proposed solution 1: As sure as there is an ASIC gap for physical FPGAs, similarly the overhead for the virtual layer can not be eliminated. There is a price that has to be paid for the added flexibility and the benefits. However, this can be mitigated through customization.

A better fit leads to a better utilization leads to less logic elements needed to accommodate the application. Since virtualization happens on top of a reconfigurable platform, it comes for free and can be updated on a per-application basis.

-> Proposed solution 2: If there are temporal exclusive functions/applications that the virtual FPGA has to execute, the partial and dynamic reconfiguration feature of the custom virtual FPGA reduces the area requirements because not all functions need to be present at the same time. Thus they can be loaded on demand while others are discarded. In case the number of temporal exclusive functions is greater than the overhead factor, this technique compensates the area overhead.

6. Due to dependency on underlying platform and coarse scaling quantization, virtual architectures don't follow the same area and performance patterns as their physical counterparts. Consequently **existing models** adopted from physical FPGAs are inaccurate for virtual FPGAs.

-> Proposed solution: Introduction of new area and delay models based on minimum sized basic elements, taking into account the underlying platform.

### 1.5. Contribution

Despite a few related works ([58], [65], [20]), the field of Virtual FPGAs is considered unexplored. Neither reconfigurable computing nor the idea of virtualization are new topics. However, to the best of my knowledge, the framework presented in this document incorporates the first concrete 3D Virtual FPGA that is able to execute applications.

Furthermore, the framework satisfies the different views on virtualization presented above.

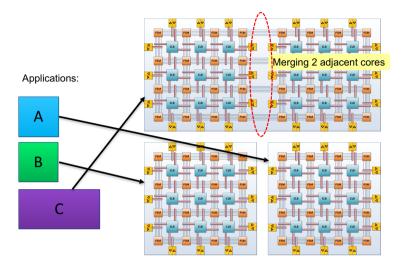

Architecture wise there are a number of new innovations contributed, such as *Loopback-Propagation* for emulating bi-directional wires, *CoreFusion* to merge adjacent *V-FPGA* cores, slice-level dynamic and partial reconfiguration mechanisms, *Snapshot* mechanisms for fast dynamic migration of applications from one region to another during runtime, inclusion of *ViSA* cores as programmable heterogeneous blocks for efficient implementation of complex arithmetic functions or control flow.

In contrast to related works that have a rather fix architecture, the *V*-*FPGA* architecture presented in this thesis can be customized by more then 20 parameters.

For guiding the selection and adjustment of parameters towards objectives, a customization methodology is proposed, whereby starting with an analysis of the application, suitable architectural parameter values are determined through design space exploration.

The *V-FPGA* has a rather complete tool support for EDA of applications, architecture level DSE and customization. Existing solutions were focused on the exploration of hypothetical architectures at abstract level. Within this work a new tool called *V-FPGA Explorer* was developed that closes the gap between abstract layout and actual reconfiguration by importing the abstract layout information and mapping it onto the programmable resources and configuration mechanisms. Apart from bitstream generation it features graphical configuration editing, testbench generation, architecture file generation and tool control script generation.

In this work new area and delay models along with transferrable metrics suitable for virtual FPGAs are introduced. Prior works relied on borrowed models from physical FPGAs for DSE and area/timing driven application mapping. However, those transistor-level models were not suitable for virtual FPGAs as they have different base units. This gap is now closed with the new models presented in this thesis.

A detailed analysis of the effects of architectural parameters on area and performance is contributed in this thesis. Similar analysis were carried out for physical FPGAs by prior art related works, however this was missing for virtual FPGAs.

In addition, the transition from virtual to physical is considered and can be emulated in an early design stage. A physical design methodology with hierarchical layout is introduced for the *V*-*FPGA* in case a mapping onto standard-cell ASIC is targeted.

A unique type of educational support is provided by the TEAChER framework which is based on and utilizes the Virtual FPGA.

### 1.6. Outline

The rest of the thesis is organized as follows:

In chapter 2, apart from a definition of efficiency, the most important fundamental basics about reconfigurable architectures, partial and dynamic reconfiguration, 3D integration, electronic design automation steps for FPGAs are covered. This chapter is intended to provide a common understanding about the terms and topics throughout the thesis. Readers that are already confidently familiar with these topics can skip this chapter.

Chapter 3 surveys related works in context of architectural efforts for efficiency increase, custom embedded or embedded FPGAs, virtual FPGAs, generic CAD tools and 3D FPGA architectures and discusses briefly how the *V-FPGA* differentiates or complements these works.

Chapter 4 describes in detail the *V*-*FPGA* architecture which is the center piece of the framework. Thereby it includes also analysis of design parameters to justify customization of such parameters.

In chapter 5 the complete toolflow for mapping applications onto the *V*-*FPGA* considering that it is a custom architecture is described. Apart from existing customizable tools also the new *V*-*FPGA Explorer* tool is described which closes the gap between abstract layout and actual configuration.

Chapter 6 is devoted to the customization process itself by presenting generic SoC architecture templates and concepts and methodologies to determine the right parameters for a good fit of the application and architecture. Furthermore it includes new area related metrics targeted at the peculiarities of virtualization.

Chapter 7 covers the mapping of the *V*-*FPGA* onto various underlying platforms, including virtualization and physical implementation in a standard-cell approach. Closely related to the target technology mapping is the characterization which is needed for area and delay models. Therefore a characterization flow is also described in this chapter.

### 1. Introduction

Chapter 8 presents various use cases with the *V-FPGA* employed. Finally, in chapter 9 the conclusion of this work is summarized.

### 2. Fundamentals

### 2.1. Efficiency in Context of This Work

One of the most important optimization goals (but not the only) of this work is efficiency improvement. In [31] a to the point definition of the term "efficiency" as quoted in the following is given:

Efficiency is the (often measurable) ability to avoid wasting materials, energy, efforts, money, and time in doing something or in producing a desired result. In a more general sense, it is the ability to do things well, successfully, and without waste. In more mathematical or scientific terms, it is a measure of the extent to which input is well used for an intended task or function (output). It often specifically comprises the capability of a specific application of effort to produce a specific outcome with a minimum amount or quantity of waste, expense, or unnecessary effort.

Efficiency can have different aspects. The following ones are relevant for this work:

**Energy efficiency** and the widely accepted synonym *performance per watt* (note that energy is power integrated over time) refers here to the ability to perform computations with low energy or power consumption. This is especially important for mobile and battery powered devices, however it has gained extreme importance also in high performance computing since Moore's Law began to run into the power wall leading to extreme power (and heat) densities in microprocessors nearly comparable to those of nuclear reactors [81].

**Area efficiency** refers to function density per area or performance per area. Often it is expressed in logic density or gate equivalents per die area, however this is not always a meaningful measure, since function density not only depends on the circuit complexity but also on the architecture type. An example of higher area efficiency with less logic density is presented in [36].

**Cost efficiency** as function of possible performance per chip cost (or per system cost) is related to area efficiency, but also depends on the technology node, integration, production volume and manufacturing process.

**Mapping efficiency** is used here to express how well an application can be mapped on the resources of an underlying platform in terms of resource utilization. The goal is to

#### 2. Fundamentals

utilize the allocated resources as much as possible. An example of an inefficient mapping is the realization of a 2-input NAND gate by a 6-input LUT: 67% of the LUT inputs and 95% of the LUT area remain unutilized and are wasted. Increasing the mapping efficiency can have also a positive effect on the area efficiency because the same application fits in a smaller area.

Throughout the rest of the thesis, if not otherwise specified, the term efficiency refers implicitly to one or more of the above mentioned aspects depending on the context that it is used in.

### 2.2. Reconfigurable Architectures

Reconfigurable architectures in context of this work are circuit architectures for semiconductor devices that can be configured by the user after the manufacturing process has been completed. The primary target is the realization of application specific integrated circuits, whereby in contrast to classical ASICs the flexibility and ability to alter the circuits is given and is the main differentiation. For this purpose reconfigurable architectures generally consist of arrays of flexible and programmable logic cells, programmable I/O cells as well as programmable interconnects. The purpose of each logic cell is to realize a logic function that has a limited amount of variables, i.e. a logic cell is a function generator. The programmable interconnects are there to combine logic cells in a way that the composite realizes a function of higher complexity out of several functions of little complexity. Furthermore, they route signals from the logic cells to the I/O cells for off-chip communication.

Reconfigurable architectures can be classified in at least two groups, fine grain and coarse grain, depending on the size and complexity of the programmable components. Compton and Hauck [26] distinguish the granularity by the bit size of the logic cells, i.e. a 3-input LUT would be fine-grained and a 6-input LUT coarse grained. Shannon [89] however distinguishes by bit level data manipulation and interconnect (fine-grained) vs. word-level data manipulation and interconnect (coarse-grained). Throughout this thesis the classification by Shannon is followed because the classification by Compton and Hauck suffers a blurred discrimination and would fail as soon as we talk about adaptive LUTs with variable size.

### 2.2.1. Fine Grain Reconfigurable Architectures

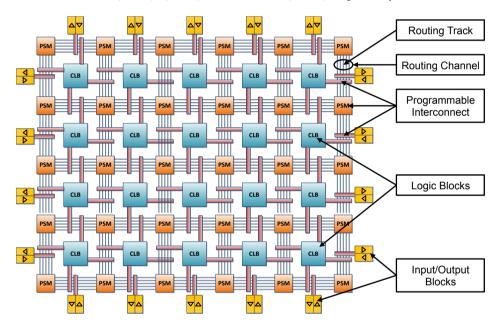

Field Programmable Gate Arrays fall in the category of fine grained reconfigurable architectures. The essence of FPGAs are programmable logic cells and programmable interconnect networks in a regular structure to realize digital circuits through individual programming of these resources. Apart from this, modern derivates contain also optimized macro-blocks of common functions, such as Block Random Access Memorys (BRAMs), Digital Signal Processing (DSP), I/O serializer/de-serializer. Fundamentally, the most important differentiators between existing FPGAs are the types of logic cells, the routing topologies for the interconnects and the programming technologies, which are explained in the following subsections.

#### 2.2.1.1. General Topologies

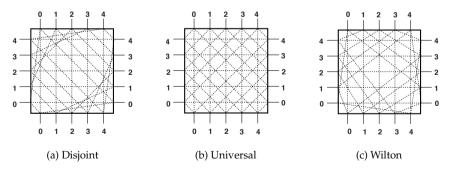

The established fundamental topologies are island-style, row-based and sea-of-gates.

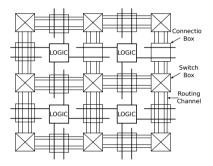

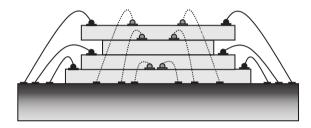

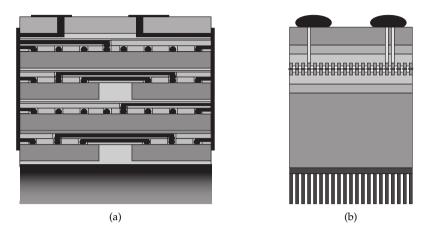

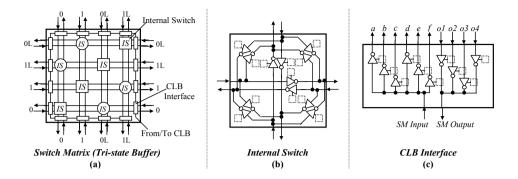

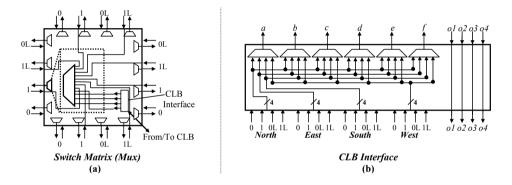

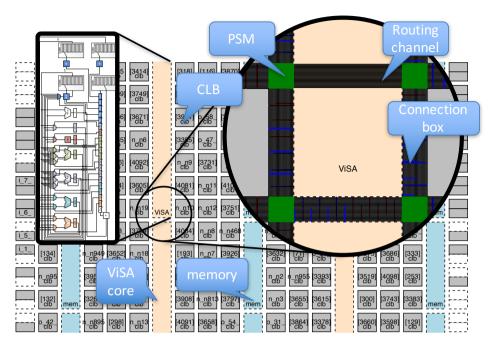

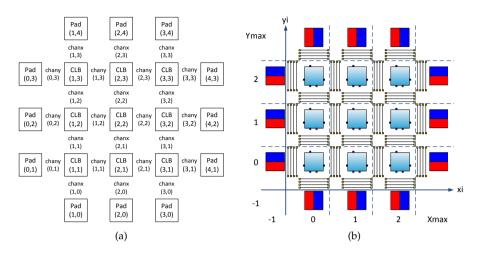

**Island-style** FPGAs are characterized by the fact that all logic cells are surrounded by routing channels (see Figure 2.1). Typically, in such architectures the inputs and outputs of the logic cells are distributed on all four sides and are connected to the tracks of routing channels via connection boxes. At the intersection points of the vertical and horizontal routing channels there are switching matrices that can interconnect tracks from different routing channels. This is the dominating topology of commercial FPGAs.

Figure 2.1.: Island-style FPGA topology [10]

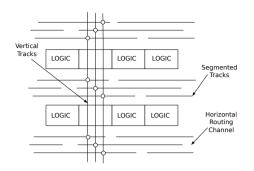

**Row-based**. In row-based FPGAs, the logic cells are arranged in a row-shaped manner (see Figure 2.2). Between these rows are horizontal routing channels. The tracks are segmented in the routing channels and can also have different lengths. Furthermore, there are vertical tracks that pass through some logic cells and cross the horizontal routing channels. In this way, tracks from different rows can be connected to each other. Row-based architectures are used, for example, in Actel ACT3 FPGAs [72].

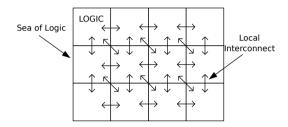

**Sea-of-gates.** In "sea-of-gates" based architectures (see Figure 2.3) there are no routing channels between the logic cells. Here, the routing is established by local connections between adjacent logic cells. The SX family of Actel for example, uses such a topology.

#### 2.2.1.2. Logic Cells

The most common type of logic cells uses LUTs as function generators. This approach relies on precomputing a boolean function with a fixed number of variables under all possible combinations of values during the design time and storing the results in a table. If K is the number of variables, then the LUT needs to contain  $2^{K}$  single bit storage elements for the results. The inputs of a LUT correspond to the function variables and drive the

Figure 2.2.: Row-based FPGA topology [10]

Figure 2.3.: Sea-of-gates FPGA topology [10]

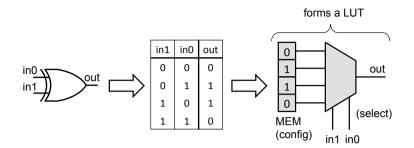

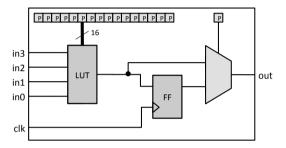

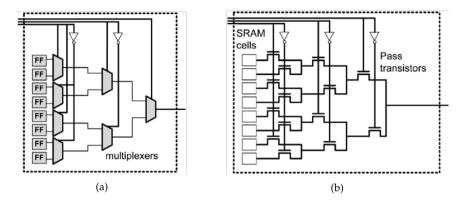

select signals of a MUX, thus each value combination addresses one of the stored results to drive the output as depicted in Figure 2.4. With a *K*-input LUT there are  $2^{2^{K}}$  possible functions realizable. Furthermore, logic cells usually contain also a flip-flop at the output of a LUT in order to realize sequential processes, while it can be bypassed if only combinational logic is to be implemented. Figure 2.5 shows the structure of a basic LUT based logic cell. Comercial versions of LUT-based logic cells can differ greatly from manufacturer to manufacturer. For instance, not only the number of inputs of a LUT can vary, but also a plurality of LUTs (and possibly flip-flops) can be clustered in different ways and, if necessary, locally interconnected, along with providing extra signals, both internally and externally, for realizing e.g. carry chains.

Figure 2.4.: Principle of lookup table (LUT) as programmable logic

Figure 2.5.: Logic cell containing a LUT, a flip-flop and a bypass MUX, programmable through SRAM cells P

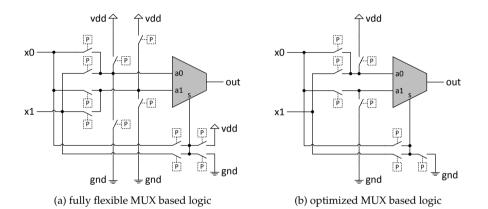

An alternative to LUT is multiplexer-based logic. The principle of MUX based logic is that a 2:1 MUX can generate the boolean functions listed in Table 2.1 if each input as well as the select signal can be tied by programmable switches to any of the function variables (x0, x1) or to *gnd* or to *vdd* according to Figure 2.6a. Having two MUX inputs (a0, a1) and one select signal *s*, there are  $4^3 = 64$  possible combinations. However, some of the combinations lead to the same results and are redundant. Removing the redundant combinations, there remain the 11 possible functions from Table 2.1. The same redundancy leaves also room for minimizing the number of required switches, e.g. as shown in Figure 2.6b. For comparison, it is to mention that a 2-input LUT can realize 16 possible functions, i.e. MUX based logic misses 5 functions. However, with the functions presented in table 2.1 any other boolean function can be realized through combination of several MUX based logic cells.

| S   | a1         | a0  | function                |  |  |  |  |  |  |

|-----|------------|-----|-------------------------|--|--|--|--|--|--|

| x0  | gnd        | x0  | 0                       |  |  |  |  |  |  |

| x1  | gnd        | x0  | (NOT x1) AND x0         |  |  |  |  |  |  |

| x1  | gnd        | vdd | NOT x1                  |  |  |  |  |  |  |

| x0  | gnd        | x1  | (NOT x0) AND x1         |  |  |  |  |  |  |

| x0  | gnd        | vdd | NOT x0                  |  |  |  |  |  |  |

| x1  | gnd        | x1  | x0 AND x1               |  |  |  |  |  |  |

| x0  | x0         | x0  | x0                      |  |  |  |  |  |  |

| x1  | x0         | vdd | (NOT x1) OR (x1 AND x0) |  |  |  |  |  |  |

| gnd | gnd        | x1  | x1                      |  |  |  |  |  |  |

| x0  | <b>x</b> 0 | x1  | x1 OR x0                |  |  |  |  |  |  |

| x0  | x0         | vdd | 1                       |  |  |  |  |  |  |

Table 2.1.: Functions realizable with a 2:1 MUX

Figure 2.6.: Multiplexer based logic: (a) fully flexible (b) optimized. Both alternatives can implement the same function set (see Table 2.1)

#### 2.2.2. Heterogeneous Reconfigurable Architectures

The need for heterogeneity arises from the fact that functions implemented on *specific-purpose logic* causes significant reduction in area when they are left unused in the target application, even though when utilized leads to higher performance. Thereby, the urge to have a heterogeneous mixture of *general-purpose* and *specific-purpose* logic blocks peaked in the last decade. To perceive the importance of heterogeneity, it is important to understand the terms "hard-core" or "hard circuit structure" and "soft core" or "soft logic fabric". Both of them are an array of combinational logic elements and each Logic Element (LE) consists of a logic function implemented as a gate of LUTs. The difference between hard-core and soft-core is being the fact that the latter one connects the LEs through programmable routing fabric, while in the former case the routing is made fixed in the fabric and cannot be reconfigured.

| SOFT SOFT | Memory Memory<br>Block Block | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

|-----------|------------------------------|------|---------------|---------------|

| SOFT SOFT |                              | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT SOFT |                              | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT SOFT |                              | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT SOFT | Memory<br>Block              | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT SOFT |                              | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

Figure 2.7.: An example of tile-based heterogeneity [57]

According to [57] there are two kinds of heterogeneity: *soft fabric heterogeneity* and *tilebased heterogeneity*. The name *soft fabric heterogeneity* by itself suggests that the FPGAs are constructed from an array of identical tiles, each containing the basic soft logic block and soft fabric heterogeneous elements. When distinct tiles, each having dedicated hard circuit structures, are included along with the soft logic blocks in the same substrate as illustrated in Figure 2.7, they fall into the latter category.

### 2.2.2.1. Soft Fabric Heterogeneous Elements

By definition, flip-flops are dedicated logic blocks and hence are hard circuit structures. Researches were carried out to emulate flip-flops as soft logic blocks, yet the significant impact on area efficiency has led to the inclusion of "hard" flip-flops within logic elements in most commercial FPGAs <sup>1</sup>. These are typically edge-triggered and include a variety of set, reset, load, enable and clocking capabilities, which depending upon the FPGA family can have fixed or programmable signal selection. Other explicit soft fabric elements are addition/subtraction/carry logic (carry lookahead and carry-skip) to make adder and subtraction units smaller and faster. Small memory units can also be built from LUTs which in turn can be connected together to form larger memories. [57]

### 2.2.2.2. Hard Structure Heterogeneous Elements

Block RAMS are one of the first hard-core heterogeneous tiles with the flexibility to have different aspect ratio configurations, which can be suited for different applications with varying memory requirements. With the addition of a small amount of soft logic, they can be combined to form larger memory blocks. These block RAMS can support dual functionality of reading and writing simultaneously and can be configured to have First-in First-out (FIFO) functionality. The unused memory blocks can be utilized efficiently by converting them into large LUTs. Multiplier is another such heterogeneous computation-oriented tile. When unused, they offer little benefit, which can be dealt with by creating

<sup>&</sup>lt;sup>1</sup>One exception is Actel's *VersaTile* technology used in the ProASIC3 and Igloo devices [2], where a core cell can be configured either as a 3-input logic function or as a flip-flop or latch

sub-families within the FPGA family using the same basic architecture but with different ratio of hard and soft logic. In order to improve performance, microproccessors have been often made hard-core in spite of the challenges that arise in the interface layer between the processor, memory system and soft fabric. Though having them as soft-core means lower performance and larger area, they are customizable, which is very beneficial for applications with varying resource requirements. [57]

### 2.2.3. Programming Technologies

In FPGAs there have been mainly three relevant programming technologies established, that are commercially and successfully employed until today: SRAM, flash and anti-fuse.

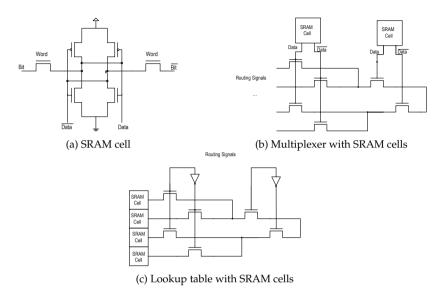

**SRAM.** The static memory cells like the one shown in Figure 2.8a form the basis of SRAM programming technology. They are used to either interconnect signals by setting the select lines to multiplexers or to store data in LUTs as illustrated in Figure 2.8b and Figure 2.8c. Their re-programmability and their competence to make use of CMOS process technology made their mark in FPGAs and are employed by vendors like Xilinx and Altera. On the other hand, this approach is marked down because of the following demerits:

- 1. The SRAM cell along with the programmable element requires at least 6 to 7 transistors.

- 2. Its necessity for external storage devices during power down degrades the cost effectiveness of the FPGAs.

- 3. The on-resistances of pass transistors, which are used to implement multiplexers lead to capacitive load.

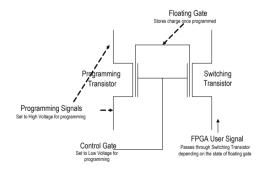

**Flash.** Figure 2.9 depicts the functionality of a flash memory cell. The programming transistor programs the floating gate (as it "floats" above the transistor) and the switching transistor acts as the programmable switch. Though the flash-based programming technology doesn't need to wait for the loading of configuration data, omits the usage of external devices for storing data and exhibits non-volatility and more area efficient than SRAM cells, it aids in area overhead because of the inclusion of high and low voltage buffers in programming circuitry, adds design complexity in switching transistor to keep up the source-drain voltage from being injected into the floating gate, suffers from high resistance and capacitance of transistor-based switches and finally the charge buildup in the oxide prevents them to be reprogrammed infinite number of times. The emerging trend of using flash cells in combination with SRAM cells provides non-volatility with infinite reconfigurability with the price being paid in area overhead.

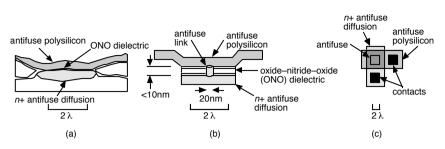

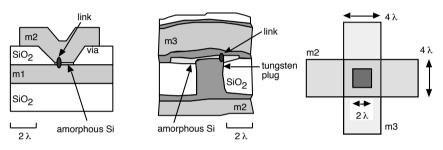

**Anti-fuse**, an alternative non-volatile programming technology, can be implemented using either dielectric (Figure 2.10) or metal-to-metal (Figure 2.11) based approach. The former approach is largely replaced by the latter one, which sandwiches an insulating

Figure 2.8.: SRAM programming technology [57]

Figure 2.9.: Flash programming technology [57]

Figure 2.10.: Dielectric anti-fuse technology [11]

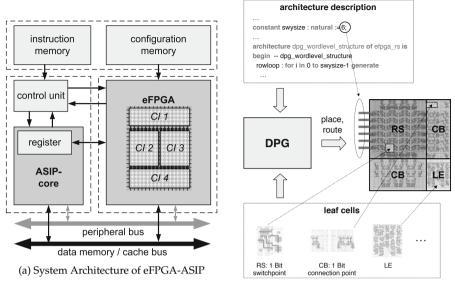

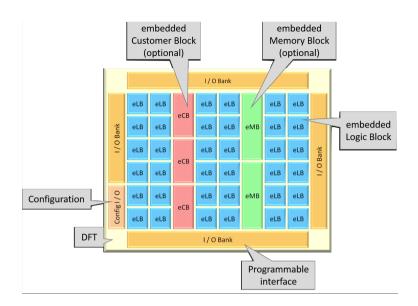

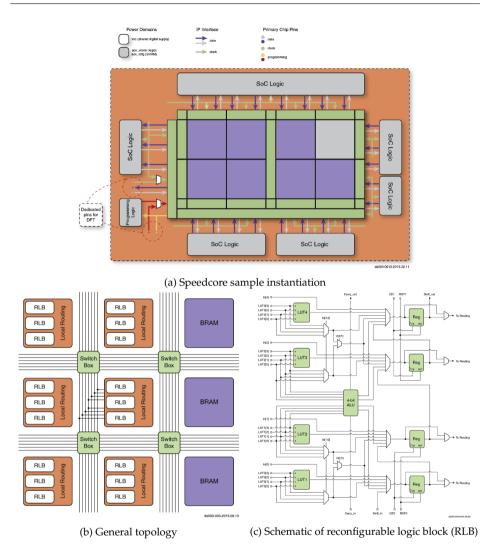

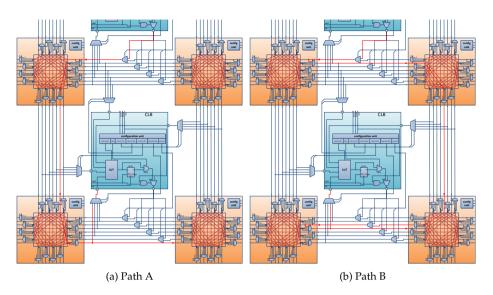

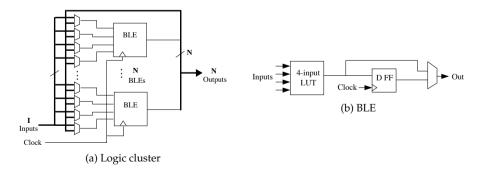

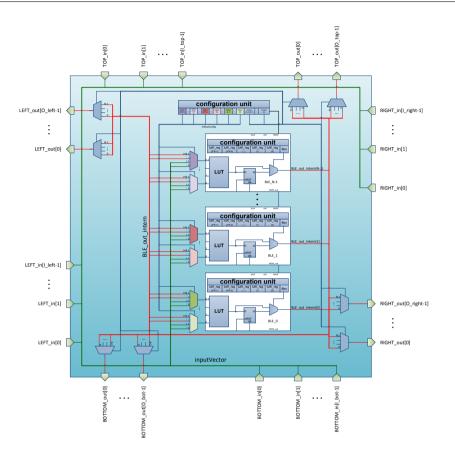

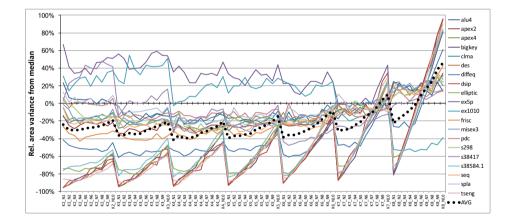

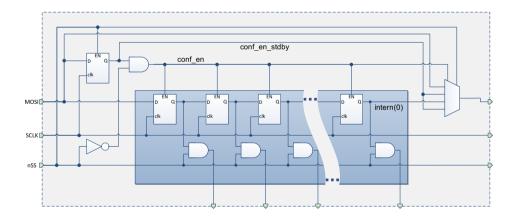

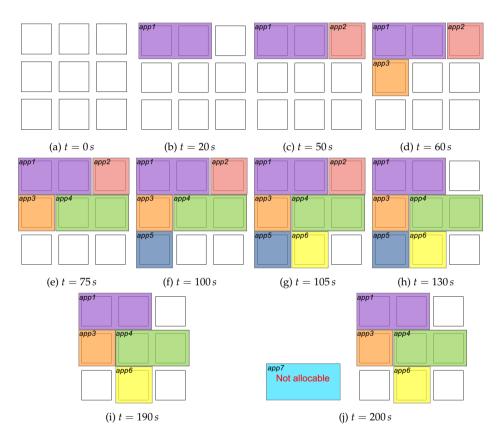

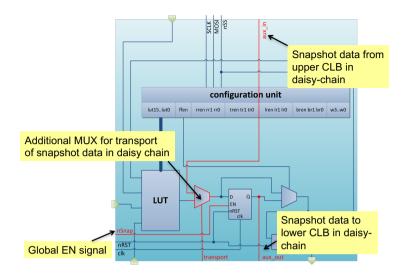

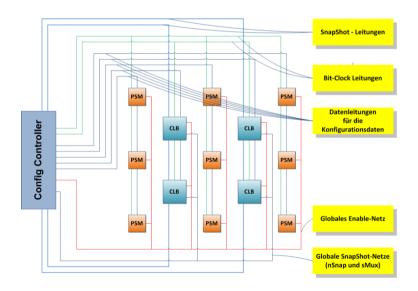

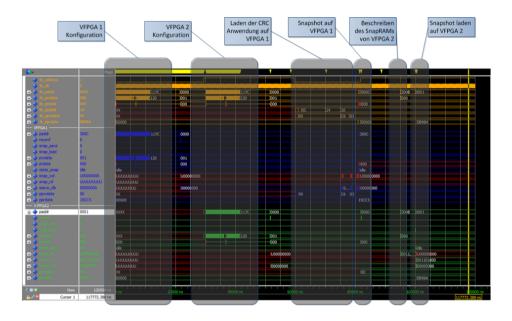

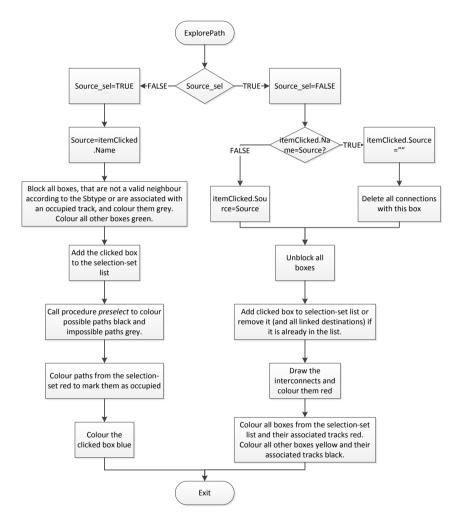

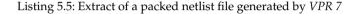

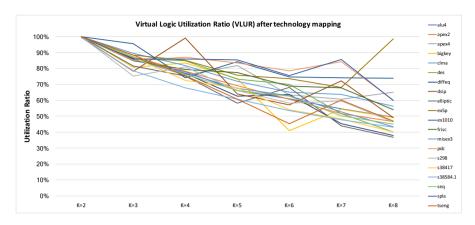

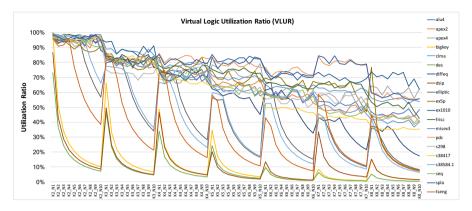

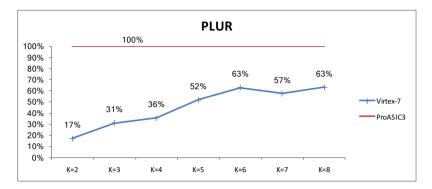

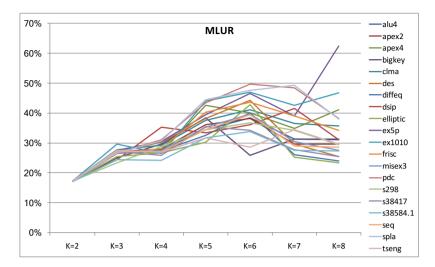

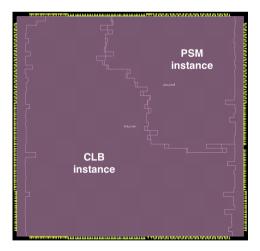

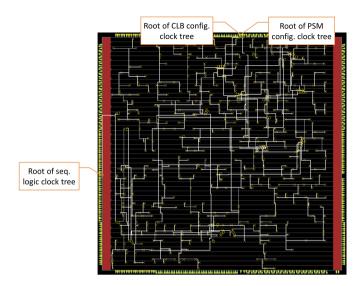

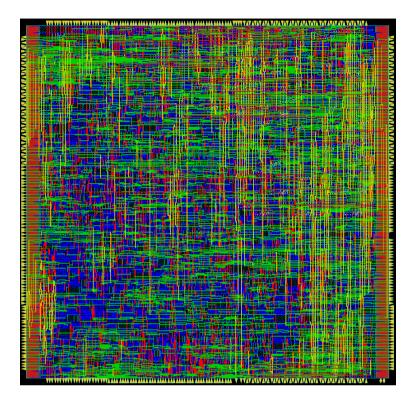

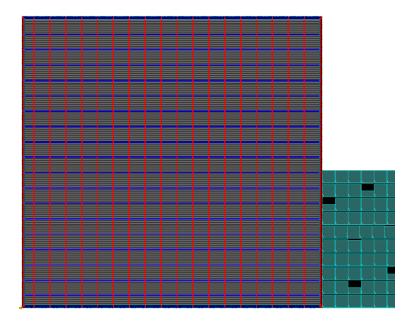

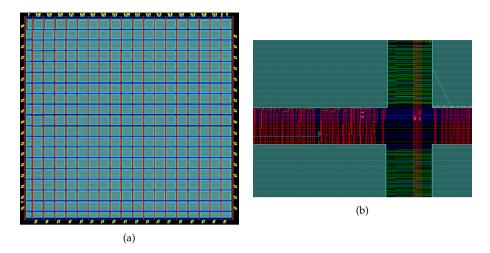

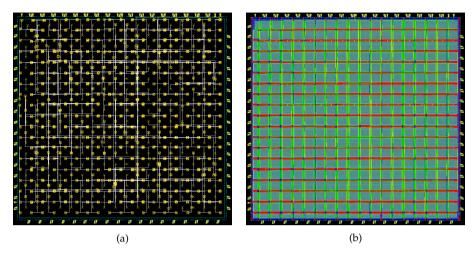

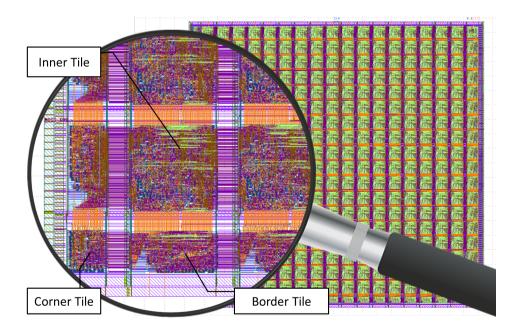

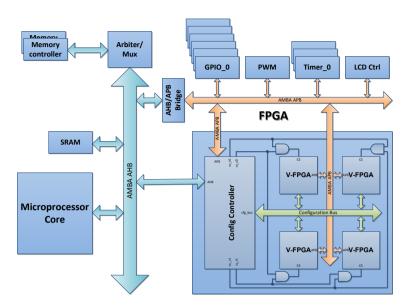

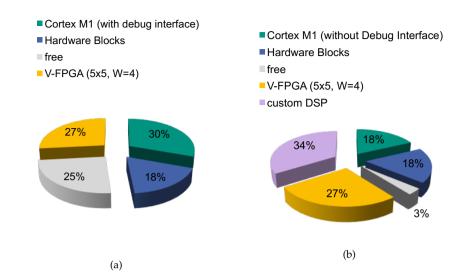

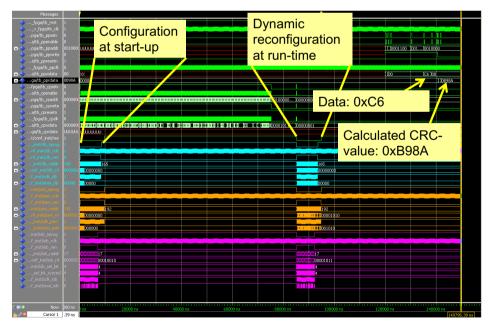

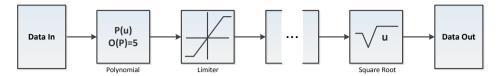

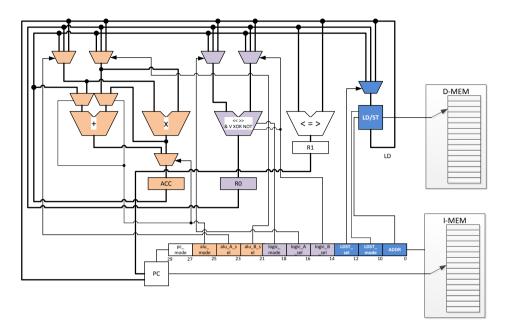

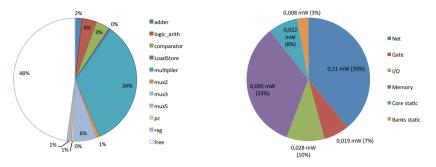

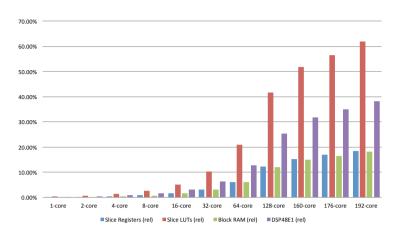

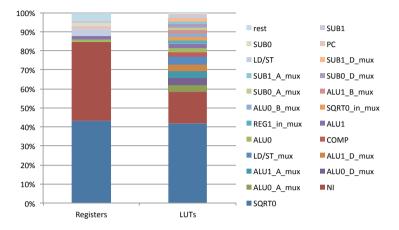

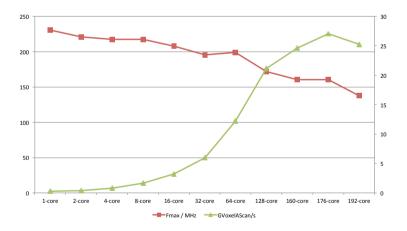

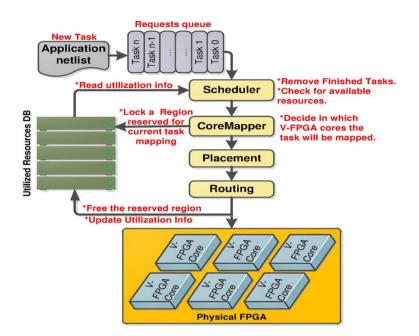

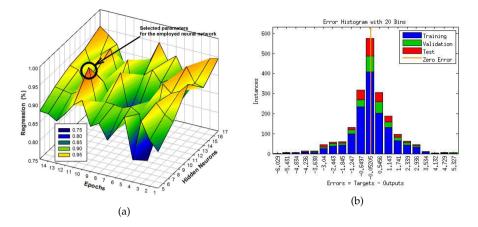

Figure 2.11.: Metal-to-metal anti-fuse technology [11]