論文目録 報告番号 工第 68 号 氏名 Andrew Colin Flavell

学位論文題目

High-Speed Message Routing Mechanisms for Massively Parallel Computers

### 論文の目次

第1章: Introduction

第2章: Scalable Multicomputer Systems

第3章: Tokkyu:A High-Performance, Randomizing, Adaptive Message

Router with Packet Expressway

第4章: Restricted Length Hardware Multicasting in Multicomputer Networks

第5章: Conclusions

#### 参考論文

### 主論文

- Flavell, A. C. and Takahashi, Y., "Tokkyū: A High-Performance, Randomizing, Adaptive Message Router with Packet Expressway", IEICE Trans. on Information and Systems, vol. E78-D, no. 10, pp. 1248-1260, October 1995.

- 2. Flavell, A. C. and Takahashi, Y., "Restricted Length Hardware Multicasting in Multicomputer Networks", *Transactions of the IPSJ*, vol. 36, no. 5, pp. 1228-1238, May 1995.

### 副論文

- Flavell, A. C. and Takahashi, Y., "The Tokkyū Router: A Randomizing Router for k-ary n-cubes", Proc. of the International Symposium on Parallel and Distributed Supercomputing, pp. 127-134, September 1995.

- Flavell, A. C. and Takahashi, Y., "Continuum: A Hybrid Time/Space Communications Paradigm for k-ary n-cubes", Proc. of the International Conference on Parallel Processing 1994, vol. I, pp. I38-I41, August 1994.

- Flavell, A. C. and Takahashi, Y., "Mandala: An Interconnection Network for a Scalable Massively Parallel Computer", in *Proceedings of the 33rd IPSJ Programming Symposium*, pp. 79-90, January 1992.

- 4. Flavell, A. C. et. al., "Mandala: An Interconnection Network for a Scalable Massively Parallel Computer", *Technical Report of the IPSJ*, vol. 91, no. 100, pp. 91.101-91.109, November 1991.

論 文 内 容 要 旨

報告番号 工工 第 68号 氏名 Andrew Colin Flavell 工修 High-Speed Message Routing Mechanisms for Massively Parallel Computers

内容要旨

現在超並列処理システム(MPP)は、伝統的なベクトルプロセッサや SIMD マシンの 牙城であった多くの分野に進出している。これらのシステムは、入手が容易な高性能 CPUの急激な進歩をうまく利用し、これらを数百~数千個接続して均質なマルチプロセッサのシステムとして構成したものである。しかし、これらのシステムの性能は、現実の問題を解くときは必ずしも良くなく、常に公称の最高性能にははるかに及ばないのが現状である。これらのシステムではプロセッサ間の通信はすべて相互結合網によって行われるので、実現可能な最高性能を決める決定的な要素は相互結合網と、それに使われる通信機構である。

本論文ではMPPの相互結合網に使われる、効率的な通信機構を実現する2つの方法を提案する。第1は「特急ルータ」の提案であり、これを相互結合網に用いた場合の適合性を検証する。特急ルータは多重の単方向レジスタ挿入バスを利用して、時間空間混合分割型ネットワークを実現するためのものである。異なる基数や次元数について、特急ルータのスイッチ回路とバッファ回路の性能を予測するための正確なモデルを開発した。この結果、特急ルータは効率的な通信を行うためのすべての条件を満足していることが確かめられた。さらに重要な点は、特急ルータはネットワークに故障のある場合や、通信が錯綜する場合にも、低遅延時間、高スループットを損なわない経路制御が行えることである。シミュレーションによって評価した特急ルータのの性能は、これまでに発表された固定経路選択方式のルータより優れており、また他の適応経路制御方式のルータに比べても、同程度あるいはそれを越えていることが確かめられた。

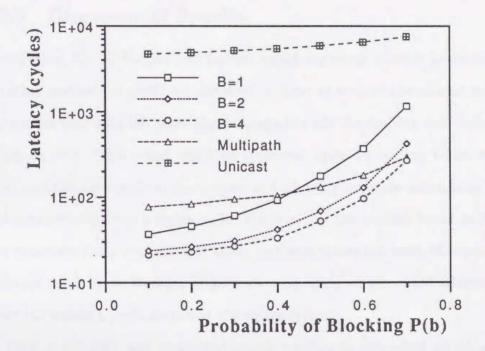

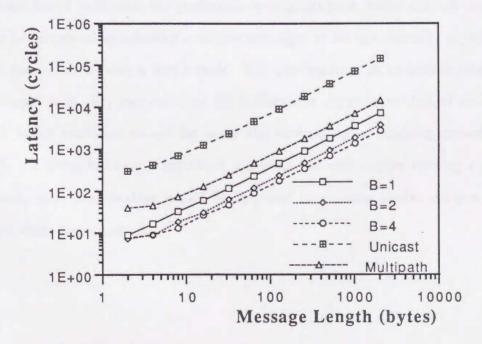

第2は経路長制限方式のマルチキャスト通信の提案である。マルチキャスト通信は多くの並列処理問題において速度向上に寄与する通信方式である。そこでワームホール通信方式において問題となるマルチキャスト通信におけるデッドロックの問題について研究した。そしてこの問題を解決する方法として経路長制限方式のマルチキャスト通信を提案し、この方式による通信性能をシミュレーションによって評価し、ユニキャスト方式やマルチパス方式によるマルチキャスト通信の性能と比較した。その結果、提案する経路長制限方式のマルチキャスト通信は、バリヤ同期のためのクラスタへのマルチキャスト通信や、最近傍ノードへのマルチキャストや全ノードへの放送の場合に、特に優れた解決法となることを明らかにした。

### 論文審査の結果の要旨

| 報告番号 | 甲乙工 | 工工修 | 第                 | 6 8 | 号  | 氏 | 名                    | Andrew Colin Flavell |

|------|-----|-----|-------------------|-----|----|---|----------------------|----------------------|

|      | 主   | 査   |                   | 高橋  | 義造 |   |                      |                      |

| 審查委員 | 剧   | 查   |                   | 島田  | 良作 |   |                      |                      |

|      | 剧   | 査   |                   | 赤松  | 則男 |   |                      |                      |

|      |     |     | -Speed<br>ively P |     |    |   | ng Mechanisms for rs |                      |

#### 審査結果の要旨

超並列計算機は、数百~数千個のプロセッサ要素を接続して並列に動作させ、超高速処理を 行わせようとするものである。ここではプロセッサ間の通信はすべて相互結合網によって行わ れるので、このシステムの総合性能を決める決定的な要素は相互結合網の通信機構と通信制御 方式になるが、まだ十分に満足できるものが得られていないのが現状である。

本論文では相互結合網の通信機構と通信制御方式について研究し、新方式のルータ機構と、独特の制御を行うマルチキャスト通信方式を提案している。新しいルータ機構を「特急ルータ」と呼んでいるが、多重の単方向レジスタ挿入バスを用いて 時分割・空間分割混合型ネットワークを実現し、ネットワークに故障のある場合や著しく通信量が多い場合にも、低遅延時間、高スループットを損なわない経路制御が行えることを特長としている。実際シミュレーションによって詳細な性能評価を行った結果、従来の固定経路選択方式のルータより優れ、他の適応経路制御方式のルータに比べても、遜色のない性能を持つことがことが確かめられている。

次に新しい通信方式としてパケット長制限方式マルチキャスト通信を提案している.マルチキャスト通信は多くの並列処理問題において必要とされる機能であるが、これをできるだけ高速に行う必要がある.しかしワームホール通信の場合にはマルチキャスト通信はデッドロックを起こす可能性があるという問題がある.この問題を研究した結果、パケット長を自動的に制限してマルチキャスト通信を行えば、性能を損なうことなくデッドロックを回避できることを証明した.また、シミュレーションによってこの方式の通信性能を評価した結果、バリヤ同期のためのクラスタへのマルチキャスト通信や、最近傍ノードへのマルチキャストや全ノードへの放送の場合に、特に優れた効果を発揮することを確かめられた.

以上本研究は高性能の超並列計算機を構成するための重要な要素である相互結合網について、 その通信機構と通信制御方式についての新しい提案を行い、その効果を実証したものであり、 本論文は博士(工学)の学位授与に値するものと判定する. High-Speed Message Routing Mechanisms for Massively Parallel Computers

March 1996

Andrew G. Playell

# High-Speed Message Routing Mechanisms for Massively Parallel Computers

March 1996

Andrew Colin Flavell

# High-Speed Message Routing Mechanisms for Massively Parallel Computers

A dissertation submitted to the Department of Information Science and Intelligent Systems and the Graduate School of the University of Tokushima in partial fulfillment of the requirements for the degree of Doctor of Engineering

by

Andrew Colin Flavell

March 1996

Approved as to the style and content by

Professor Veshiga Talsaha

Professor Yoshizo Takahashi

Dept. of Information Science and Intelligent Systems

Dissertation Supervisor

島田良祚

Professor Ryosaku Shimada

Dept. of Information Science and Intelligent Systems

nous ARagnals

Professor Norio Akamatsu

Dept. of Information Science and Intelligent Systems

## Acknowledgments

I wish to express my sincere gratitude to Professor Yoshizo Takahashi, for enabling me to study for a doctoral degree in Japan. His guidance has served me well and has helped to keep me focused on the task at hand. I also wish to thank Professors Ryosaku Shimada and Norio Akamatsu, for their contributions as the members of my defense committee. Thanks must also go to the Japanese Ministry of Education, Science and Culture, for granting me the scholarship which has made studying in Japan a reality.

To Masahiko Sano and Tomio Inoue, many thanks for helping to make my university life, and adjustment to life in Japan, simpler and more enjoyable. Thanks to Dr. Tim Gleeson for his useful and constructive criticism of my written work, especially the comments relating to this dissertation.

Finally, special thanks must go to my wife, Figen Ulgen. Her belief in my ability has been, and continues to be, an inspiration. I couldn't wish for anything more...

Figen, bu senin için...

### Abstract

Massively parallel processing systems (MPPs) are currently making inroads into many areas that are traditionally a stronghold for vector or SIMD processors. These systems leverage the rapid advances being made in readily available high performance CPUs by connecting hundreds or thousands of them together to form homogeneous multiprocessor systems. Unfortunately, the performance of these systems when solving real-world problems has been somewhat disappointing and always falls far short of the theoretical peak performance quoted by system vendors. As all of the communications between processors in these systems rely on the interconnection network, a critical component in determining the maximum achievable performance is the interconnection network and the communications structures supported by it.

This dissertation introduces two solutions to providing effective communications structures for MPP systems. The Tokkyū router is presented and its suitability for use in MPP interconnection networks is demonstrated. The Tokkyū router utilizes multiple, unidirectional, register-insertion buses to provide a hybrid time/space division network. Accurate models are developed to predict the switch and buffer performance of Tokkyū routers for varying radix and dimension. The Tokkyū router meets all of the requirements necessary to be considered effective. Importantly, the support for routing in the presence of faults or network congestion does not compromise the low latency and high throughput of the router. The simulated performance of the Tokkyū router exceeds that of published results for oblivious

routers and is equal to or exceeds those reported for other adaptive routers.

The multicast deadlock problem is investigated, as multicast has been identified as an area which can provide significant speedup to a number of parallel applications. Restricted-length multicast is introduced as a solution to multicast deadlock in wormhole routed networks and the implementation of this multicast scheme is examined. Restricted-length multicast is then compared to unicast and multi-path based multicasts by simulation. The results of the simulations indicate that restricted-length multicast provides a good solution to multicast problems such as multicasting to clusters of nodes found in barrier synchronization, multicasting to nearest neighbors and broadcasting to all of the nodes in the network.

### List of Publications

### Papers Accepted for Journal Publication

- Flavell, A. C. and Takahashi, Y., "Tokkyū: A High-Performance, Randomizing, Adaptive Message Router with Packet Expressway", IEICE Trans. on Information and Systems, vol. E78-D, no. 10, pp. 1248-1260, October 1995.

- Flavell, A. C. and Takahashi, Y., "Restricted Length Hardware Multicasting in Multicomputer Networks", *Transactions of the IPSJ*, vol. 36, no. 5, pp. 1228-1238, May 1995.

### Papers Accepted to International Conferences

- Flavell, A. C. and Takahashi, Y., "The Tokkyū Router: A Randomizing Router for k-ary n-cubes", *Proc. of the International Symposium on Parallel and Distributed Supercomputing*, pp. 127-134, September 1995.

- Flavell, A. C. and Takahashi, Y., "Continuum: A Hybrid Time/Space Communications Paradigm for k-ary n-cubes", Proc. of the International Conference on Parallel Processing 1994, vol. I, pp. I38-I41, August 1994.

### Other Related Papers

- Flavell, A. C. and Takahashi, Y., "Mandala: An Interconnection Network for a Scalable Massively Parallel Computer", in *Proceedings of the 33rd IPSJ Programming Symposium*, pp. 79-90, January 1992.

- Flavell, A. C. et. al., "Mandala: An Interconnection Network for a Scalable Massively Parallel Computer", *Technical Report of the IPSJ*, vol. 91, no. 100, pp. 91.101-91.109, November 1991.

# Contents

| A  | bstra                          | ct                                                  | iii |  |  |  |  |  |  |  |  |

|----|--------------------------------|-----------------------------------------------------|-----|--|--|--|--|--|--|--|--|

| Li | st of                          | Publications                                        | v   |  |  |  |  |  |  |  |  |

| 1  | Intr                           | roduction                                           | 1   |  |  |  |  |  |  |  |  |

| 2  | Scalable Multicomputer Systems |                                                     |     |  |  |  |  |  |  |  |  |

|    | 2.1                            | Node Structure                                      | 5   |  |  |  |  |  |  |  |  |

|    | 2.2                            | Interconnection Network Topologies                  | 6   |  |  |  |  |  |  |  |  |

|    | 2.3                            | Message Switching                                   | 14  |  |  |  |  |  |  |  |  |

|    | 2.4                            | Message Routing                                     | 17  |  |  |  |  |  |  |  |  |

|    |                                | 2.4.1 Deterministic Routing                         | 18  |  |  |  |  |  |  |  |  |

|    |                                | 2.4.2 Adaptive Routing                              | 22  |  |  |  |  |  |  |  |  |

|    | 2.5                            | Deadlock                                            | 26  |  |  |  |  |  |  |  |  |

|    | 2.6                            | Multicast Messages                                  | 28  |  |  |  |  |  |  |  |  |

|    |                                | 2.6.1 Multicast Deadlock                            | 31  |  |  |  |  |  |  |  |  |

| 3  | Tok                            | kyū: A High-Performance, Randomizing, Adaptive Mes- |     |  |  |  |  |  |  |  |  |

|    | sag                            | e Router with Packet Expressway                     | 35  |  |  |  |  |  |  |  |  |

|    | 3.1                            | The Register-insertion Bus                          | 36  |  |  |  |  |  |  |  |  |

|    |                                | 3.1.1 Register-insertion Bus Operation              | 36  |  |  |  |  |  |  |  |  |

|    | 3.2                            | Architecture of the Tokkyū Router                   | 40  |  |  |  |  |  |  |  |  |

|    |                                | 3.2.1 Router Operation                              | 41  |  |  |  |  |  |  |  |  |

|    | 3.3                            | Switch and Buffer Design                            | 49  |  |  |  |  |  |  |  |  |

|    |                                | 3.3.1 Switch Evaluation                             | 49  |  |  |  |  |  |  |  |  |

|    |                                | 3.3.2 Buffer Evaluation                             | 56  |  |  |  |  |  |  |  |  |

| C | ONT | ENTS             | vi                                                | i |

|---|-----|------------------|---------------------------------------------------|---|

|   |     |                  |                                                   |   |

|   | 3.4 | Perfor           | mance                                             | 9 |

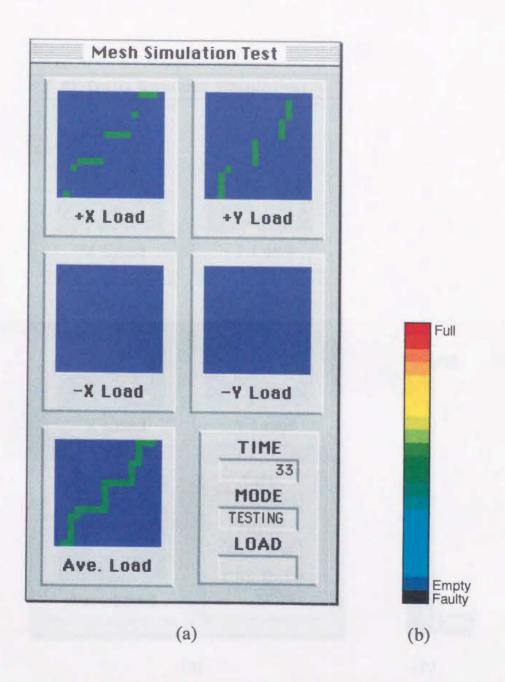

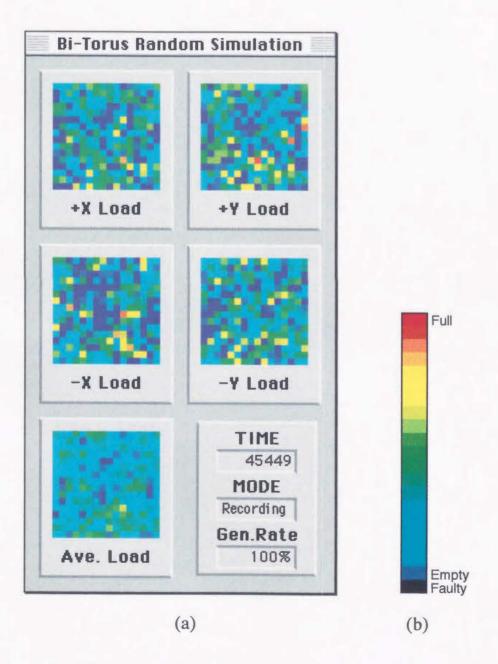

|   |     | 3.4.1            | Simulation of Uniform Random Traffic 6            | 5 |

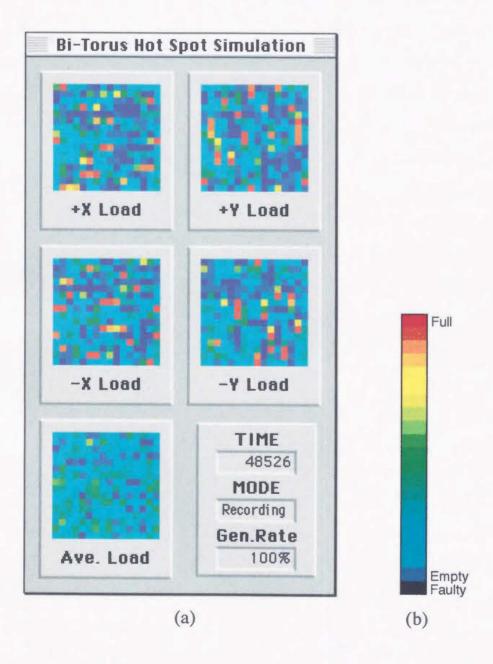

|   |     | 3.4.2            | Simulation of Hot-spot Traffic                    | 0 |

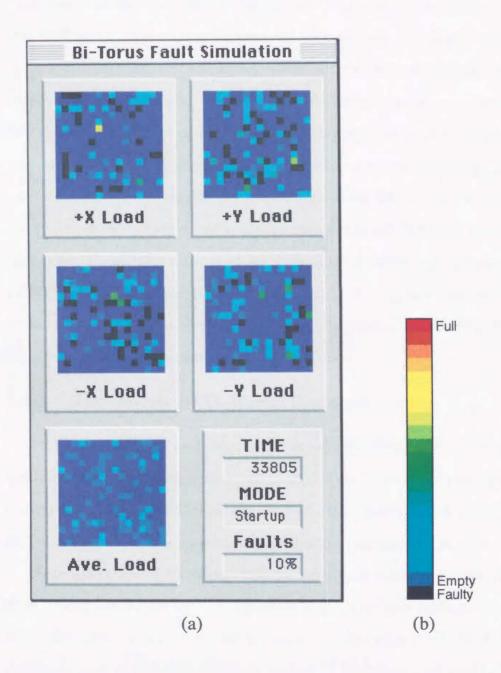

|   |     | 3.4.3            | Simulation of Traffic in the Presence of Faults 7 | 1 |

|   |     | 3.4.4            | Discussion of Results                             | 4 |

| 4 |     | tricted<br>works | d-length Hardware Multicasting in Multicomputer   | 6 |

|   | 4.1 | Prelin           | ninaries 7                                        | 6 |

|   |     | 4.1.1            | Definition of Multicast Deadlock Problem 7        | 6 |

|   | 4.2 | Restri           | cted-Length Multicasting 8                        | 1 |

|   |     | 4.2.1            | Gate-array Implementation 8                       | 3 |

|   | 4.3 | Simul            | ation                                             | 6 |

|   |     | 4.3.1            | Multicast Latency                                 | 6 |

|   |     | 4.3.2            | Simulation Results                                | 7 |

|   |     | 4.3.3            | Discussion of Results                             | 0 |

| 5 | Cor | nclusio          | ns 9                                              | 1 |

# List of Figures

| 1.1  | Generic multiprocessor architecture                              | 2  |

|------|------------------------------------------------------------------|----|

| 2.1  | Generic node architecture                                        | 6  |

| 2.2  | (a) Simple ring network and (b) corresponding spanning sub-      |    |

|      | graph                                                            | 7  |

| 2.3  | (a) Strongly connected digraph and (b) corresponding directed    |    |

|      | tree, which is also a rooted tree                                | 8  |

| 2.4  | Contemporary static network topologies:(a) 2D torus (b) 2D       |    |

|      | mesh (c) 3D mesh (d) 4D Hypercube (e) Fat-Tree (f) Mandala       |    |

|      | interconnection network.                                         | 10 |

| 2.5  | Communications channels for a 2-dimensional router               | 11 |

| 2.6  | Latency of various switching techniques                          | 14 |

| 2.7  | Division of information units                                    | 16 |

| 2.8  | Three virtual channels sharing a unidirectional physical channel | 17 |

| 2.9  | e-cube routing on a hypercube                                    | 20 |

| 2.10 | Dimension order routing on a 2D mesh                             | 21 |

| 2.11 | (a) Dimension order routing (b) Adaptive routing                 | 22 |

| 2.12 | Physical communication channels divided into routing planes .    | 23 |

| 2.13 | Two-dimensional chaos router                                     | 25 |

| 2.14 | (a) Network and (b) its channel dependency graph without         |    |

|      | virtual channels. (c) Network and (b) its' channel dependency    |    |

|      | graph with extra virtual channels                                | 27 |

| 2.15 | (a) Multicast by unicast (b) Tree based multicast (c) Path       |    |

|      | based multicast                                                  | 30 |

| 2.16 | Multicast deadlock in binary tree                                | 31 |

| 2.17 | Multipath multicast                                              | 33 |

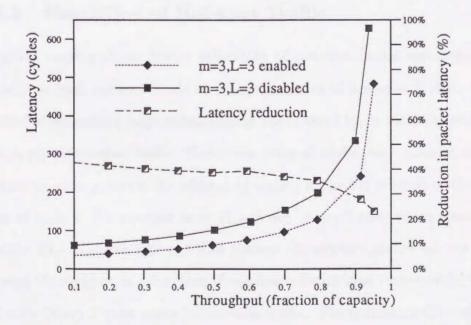

| 3.18 | Latency and reduction in latency versus applied load under     |    |

|------|----------------------------------------------------------------|----|

|      | uniform random traffic with packet expressway enabled and      |    |

|      | disabled                                                       | 69 |

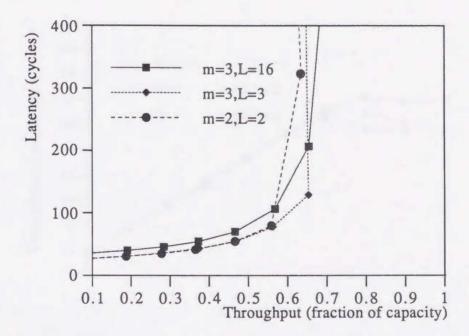

| 3.19 | Latency versus offered traffic for a 256 node 16-ary 2-cube    |    |

|      | under bit reversal traffic                                     | 70 |

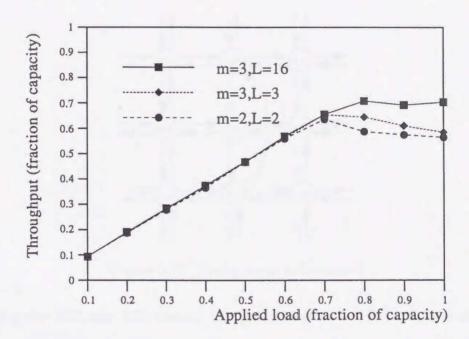

| 3.20 | Throughput versus offered traffic for a 256 node 16-ary 2-cube |    |

|      | under bit reversal traffic                                     | 71 |

| 3.21 | Faulty node is bypassed                                        | 72 |

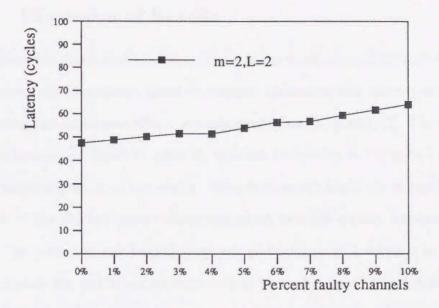

| 3.22 | Average latency versus percent faulty channels at 50% applied  |    |

|      | load (m=2, L=2). Mean latency averaged over ten random         |    |

|      | fault sets                                                     | 73 |

| 3.23 | Throughput versus percent faulty channels at 50% applied       |    |

|      | load (m=2, L=2). Mean throughput averaged over ten ran-        |    |

|      | dom fault sets                                                 | 73 |

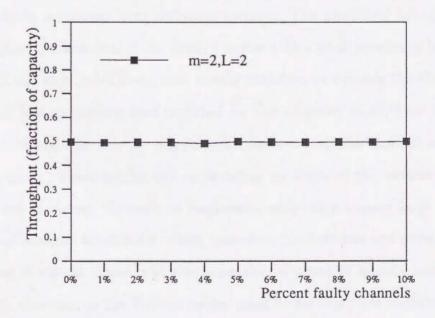

| 4.1  | (a) Multicast by node (2,1) and (b) the resulting concurrent   |    |

|      | resource trees                                                 | 81 |

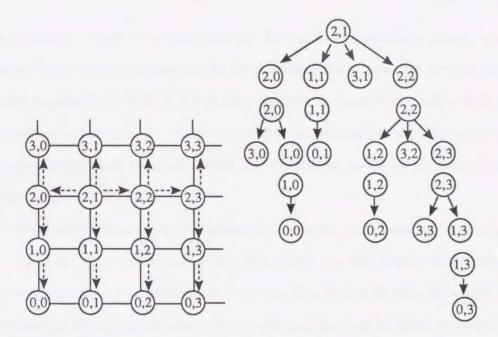

| 4.2  | Organization of a single MEGA router input                     | 83 |

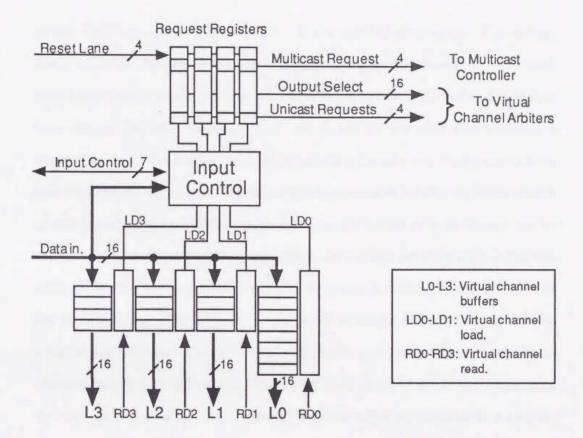

| 4.3  | Send latency for $L_m = 16$ bytes                              | 89 |

| 4.4  | Send latency for $Pr(b) = 0.5 \dots \dots \dots$               | 89 |

# List of Tables

| 2.1 | Routing steps from $s = 0000$ to $d = 1101 \dots \dots$                 | 20 |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | 2-tuples defining total distance to travel and $\Psi_{d_g}$ for packets |    |

|     | in an 8-ary 2-cube                                                      | 52 |

| 3.2 | Probability of $j$ dimensions remaining to be traversed                 | 54 |

| 4.1 | Resource usage for various buffer structures                            | 85 |

# Chapter 1

# Introduction

The peak performance levels of Massively Parallel Processing (MPP) systems have recently begun to rival those which are obtained using traditional vector and SIMD supercomputers. Many therefore believe that MPP systems, constructed by the interconnection of thousands of homogeneous computational nodes, are a promising technology for the construction of computers with teraflops performance. However, the efficiency of multicomputer based MPP systems when solving real world problems tends to be disappointing, especially when compared to vector supercomputers [11, 20].

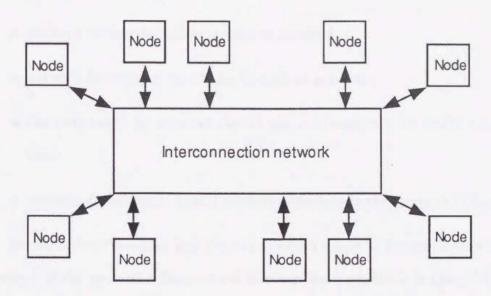

Although there are many ways in which the nodes of an MPP system can be connected, by far the most popular is the static or direct network. Each node in a direct network has a point-to-point, or direct, connection to its' 'neighboring' nodes and these connections form the interconnection network as is illustrated in Fig. 1.1. Direct networks are popular as they are said to scale well, i.e. as the number of nodes in the system is increased, the total processing power, communication bandwidth and memory bandwidth of the system also increases.

Inter-process communication, data-sharing and synchronization in an MPP

Figure 1.1: Generic multiprocessor architecture

system are all achieved by the passing of messages via the interconnection network (IN), and therefore a critical component in determining the maximum achievable performance of MPP systems is the IN and the communications structures supported by it. A considerable amount of research has therefore been conducted in both the design and evaluation of interconnection networks [1, 2, 46, 5, 42, 47, 22, 23, 24, 25, 26, 27, 28, 29], and this continues to be an active avenue of research.

The interconnection networks of massively parallel systems must provide effective, dynamic and arbitrary connectivity between all of the processors in the system. In order to be considered effective it is desirable that the interconnection network satisfies the following requirements:

- the packet routing algorithm must be free from deadlock

- the network must be free from livelock, i.e. packets must not be infinitely delayed in the network

- · network latency should be as low as possible

- · network throughput should be as high as possible

- the path taken by a packet should adapt dynamically to traffic conditions

- network performance should degrade gracefully in the presence of faults

Freedom from deadlock and livelock are both essential for the correct operation of the network. Guaranteed freedom from deadlock is essential to ensure that there is no potential for the network being brought to a complete halt because of dependencies in the allocation of network resources, and freedom from livelock is essential to ensure that packets do not endlessly cycle in the network, never reaching their destinations. Low latency and high throughput are necessary to allow a good balance of the computation/communication ratio of the system. Adaptive packet routing and graceful degradation of network performance in the presence of faults are both desirable features, provided they do not compromise the latency and throughput of the network[44]. Adaptive routing allows better utilization of communication resources, especially at high network loads or in the presence of hot-spot traffic [31, 9, 32, 35, 41, 15], and networks which are fault tolerant are becoming increasingly important as the size and complexity of massively parallel systems grows. In addition to these requirements, multicast communication, in which a source node transmits a single message to a number of destination nodes in the system, has been identified as being crucial to achieving acceptable performance in a number of application areas [37, 51].

# Organization of this Dissertation

This dissertation focuses on simple and effective solutions to meeting the requirements for an IN to be considered effective and is divided into two distinct areas. An introduction to scalable multicomputer systems is given in Chapter 2 and this is followed in Chapter 3 with an examination of adaptive routing in multicomputer networks and the introduction and investigation of the  $Tokky\bar{u}$  interconnection network. In Chapter 4 an examination of multicast deadlock in wormhole routed networks is given and the concept of restricted-length multicasting is introduced and investigated. Finally, a summary and conclusions are given in Chapter 5.

# Chapter 2

# Scalable Multicomputer Systems

### 2.1 Node Structure

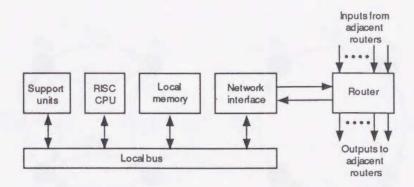

Each node in most current MPP systems contains an off-the-shelf RISC processor, local memory, a number of support units, an interface to a communications network and a message router, as illustrated in Fig. 2.1. Off-the-shelf processors are often chosen for MPP system construction as they are inexpensive and can help to reduce the design time of the system. For example, the Connection Machine CM-5 uses 32-MHz SPARC processors, the NEC Cenju-3 uses 75-MHz NEC VR4400SC processors and the Intel Paragon XP/S uses 50-MHz i860 processors. Support units may include vector processing units, a graphics controller and HIPPI, SCSI, ethernet or some other I/O interface. The role of the network interface unit is to perform message assembly/disassembly and provide flow control for messages entering and leaving the network, while the router provides routing and flow control for messages within the communication network. By removing the functions of message assembly/disassembly, routing and flow control from the CPU, com-

Figure 2.1: Generic node architecture

munication and computation can occur concurrently, significantly increasing the performance of the system.

## 2.2 Interconnection Network Topologies

The topology of a network defines how the nodes are connected and can usually be represented using graph notation. Therefore, a brief introduction to the relevant graph theory notation is presented before the discussion of static interconnection networks.

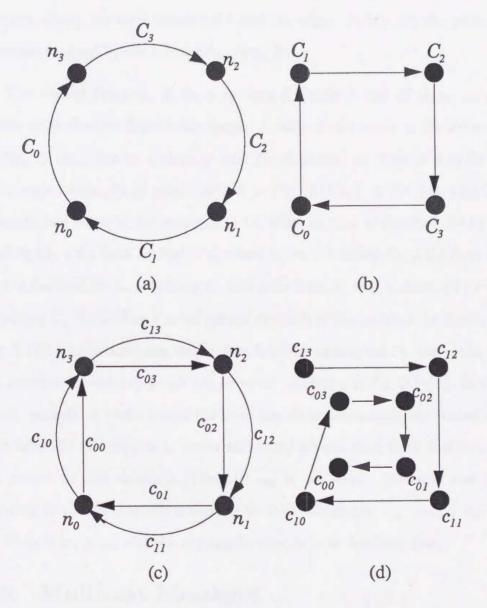

**Definition 1** A static interconnection network may be represented by the strongly connected directed graph, digraph, I = G(N,C), where the vertex set N(I) and the arc set C(I) represent the nodes and channels of the network respectively. The degree of a vertex n, in I, denoted d(n), is the number of edges incident with n. The graph H = G(N,C) is a subgraph of I if  $N(H) \subseteq N(I)$  and  $C(H) \subseteq C(I)$ , and H is a spanning subgraph of I if N(H) = N(I).

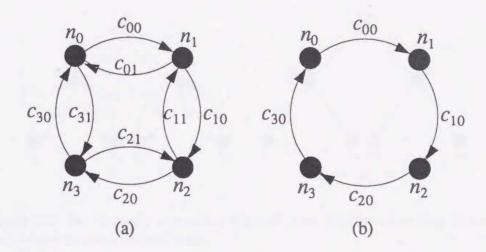

Figure 2.2: (a) Simple ring network and (b) corresponding spanning subgraph

Figures 2.2(a) and (b) illustrate Definition 1. Figure 2.2(a) presents a simple ring network, which is a strongly connected digraph and Figure 2.2(b) represents a spanning subgraph of (a), as it contains the same set of nodes.

**Definition 2** A tree is a connected graph which contains no cycles, and it follows that a subgraph which is a tree is called a subtree, and a spanning subgraph which is a tree is called a spanning tree. A directed tree is a digraph which becomes a tree when the directions of the edges are ignored and a rooted tree is a directed tree with one vertex of in degree 0, and all other vertices of in degree 1.

Figures 2.3(a) and (b) illustrate Definition 2. Figure 2.3(a) presents a strongly connected digraph and Figure 2.2(b) represents the corresponding directed tree. This tree is a binary tree and therefore it is also a rooted tree.

Some of the more important static evaluative measures of an interconnection network are its degree, diameter, average distance [2], channel bisection

Figure 2.3: (a) Strongly connected digraph and (b) corresponding directed tree, which is also a rooted tree.

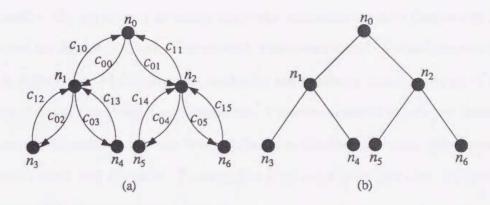

width [12], maximum message density, and its ability to be scaled. The degree is defined as the number of channels incident on a node, the diameter as the maximum of the shortest distances between any two nodes in a system, and the average distance as the average number of channels that a message must traverse when traveling from a source node to a destination node. As the degree of a node and the average distance for a given network are often interrelated, the normalized average distance, given by average distance  $\times$  degree, may provide a more useful measure for static evaluation. The channel bisection width, B, is defined as the minimum number of channels that, when cut, separate the network into two equal parts, and the maximum message density is the maximum of the total number of communications paths passing through each node in the system. Scalability is defined as the relative ease with which the number of processing elements in a system can be increased. A system which requires major hardware changes and/or rewiring to increase the number of processors is therefore not considered scalable when compared to a system in which an additional processor can be plugged in. Feng [21] classified the topologies of static networks according to the dimensions required for layout, i.e. one-dimensional, two-dimensional, three-dimensional, and hypercube. Multicomputer networks are typically constructed from arrays of nodes in at least two-dimensions. Two-dimensional topologies include the ring, 2D mesh, torus and tree, while three-dimensional topologies include the 3D mesh and 3D torus. Presented in Figure 2.4 are a number of contemporary static network topologies.

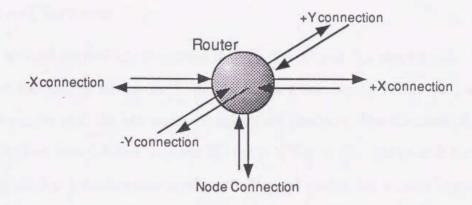

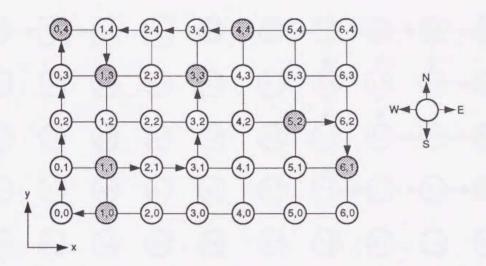

The networks under consideration here are bi-directional, as these networks allow locality of communication to be employed in the programming model of the parallel machine. Therefore, each arc in Fig 2.4 is divided into two communications channels, one in each direction. A router in a 2-dimensional network will have communications channels in the +x, -x, +y and -y directions, along with a connection to the local processor, as shown in Fig. 2.5.

#### Torus

The torus of Fig. 2.4(a) is a member of the general k-ary n-cube family. For the example torus of Fig. reffig:static, k=4 and n=2.

**Definition 3** A k-ary n-cube is an n-dimensional cube of radix k, and a node within a k-ary n-cube can be identified by the n-digit radix k address,  $(a_0, a_1, ..., a_{n-1})$ . Each node in a k-ary n-cube is connected to every other node whose address differs in exactly one digit by  $\pm 1$  modulo k.

The number of nodes in the network, N, is related to n and k by:

$$N = k^n$$

,  $(k = \sqrt[n]{N}, n = \log_k N)$

Figure 2.4: Contemporary static network topologies:(a) 2D torus (b) 2D mesh (c) 3D mesh (d) 4D Hypercube (e) Fat-Tree (f) Mandala interconnection network.

Figure 2.5: Communications channels for a 2-dimensional router

Although there are many possible topologies for the direct networks employed in MPP systems, by far the most popular in the current generation of MPP systems are k-ary n-cubes and those networks which are isomorphic to them<sup>1</sup>. Parallel systems based on 2 and 3-dimensional k-ary n-cubes have been intensely investigated in the past, due to their ease of construction within the confines of 3-dimensional space and the natural mapping of a number of algorithms to them. Usually, low dimensional k-ary n-cubes are referred to as tori, while higher dimensional binary n-cubes are called hypercubes. The diameter of a torus is  $2\lfloor n/2 \rfloor$ . Although the wrap-around links of the torus reduce the diameter of the system, they can complicate message routing in the system and may make it difficult to connect peripherals to the network. However, several parallel machines have been constructed using tori. The 2D torus is used in the iWarp[6] and the K2 parallel processor[3], and more recently, the 3D torus has been used in the construction of the Cray Research T3D[43].

<sup>&</sup>lt;sup>1</sup>One notable exception to this is the CM-5, which is based on a fat-tree IN[36]

#### 2D and 3D Mesh

2D and 3D meshes are presented in Figs. 2.4(b) and (c) respectively. The mesh topology is an aperiodic variant of the k-ary n-cube family, and looks like a torus with the end around connections removed. The 2D mesh of Fig. 2.4(b) has (n=2,k=4) and the 3D mesh of Fig. 2.4(b) has (n=3,k=3). In general a k-dimensional mesh with  $N=n^k$  nodes has a node degree of 2k and a network diameter of k(n-1). Several simple routing algorithms have been presented for the mesh, including fault tolerant algorithms, and the unused connections around the edge of the mesh provide an abundance of connections for peripheral devices. A number of commercial parallel computers have been constructed based on the 2D mesh, including the CM-2 and the Intel Paragon [53], and a 3D mesh has been utilized in the J-machine [16] and the Wavetracer Inc. Data Transport Computer [53].

### Binary Hypercube

The 4-dimensional binary hypercube of Fig. 2.4(d) is a member of the k-ary n-cube family, with k fixed at two. The hypercube, as it is often referred to, has a network diameter of n, which is one of the lowest known average communications distances of any IN. Many numerical algorithms are suited to this topology, and it is simple to embed other topologies in the hypercube. The main disadvantage of the hypercube is that the number of nodes in the system is increased by increasing the dimension of the network. Thus a large number of connections are required for each node if a large system is to be built. In spite of this, the hypercube topology has been used for a number of commercial and research machines including the Cosmic Cube, CM-2 and

nCube corporations nCube2.

#### Fat-Tree

The fat-tree takes a somewhat different approach to implementing a static IN. A typical binary tree has a bisection width of only 1, which results in severe message-traffic congestion at the root node of the tree. The number of communications channels, and therefore the communications bandwidth in a fat-tree, increases as you move up the tree hierarchy, thus alleviating the communications bottleneck experienced by a standard binary tree interconnection network. One disadvantage of this scheme is that it requires several different types of routing nodes and the number of communications channels in the hierarchy can become very large. However, the network is quite practical as the Connection Machine Corporation CM-5 is constructed using a 4-ary fat-tree [36]. The 4-ary fat-tree of Fig. 2.4(e) has clusters of four processors located at the leaves of a tree, each of which is connected to two router chips.

#### Mandala

The Mandala network, presented in Fig. 2.4(f), is a hierarchical network proposed by Takahashi and Flavell [22, 23, 24]. It can be described by the size of its clusters, C and number of levels, L. For example the network in Fig. 2.4(f) is a (4,2) Mandala network. The number of nodes in this system is given by N = CL. Each of the nodes in a network of cluster size C, has C-1 communications channels forming a complete connection at level 1, with 1 channel per node reserved for connection to higher levels. The degree

Figure 2.6: Latency of various switching techniques

of each node is given by C and the average distance is given by  $\sqrt[C]{N}$ .

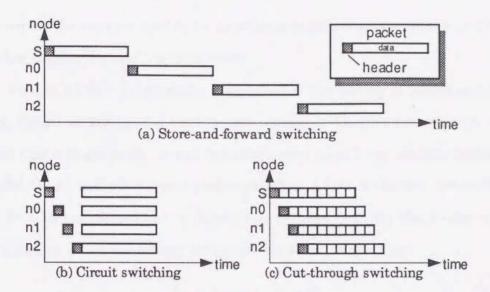

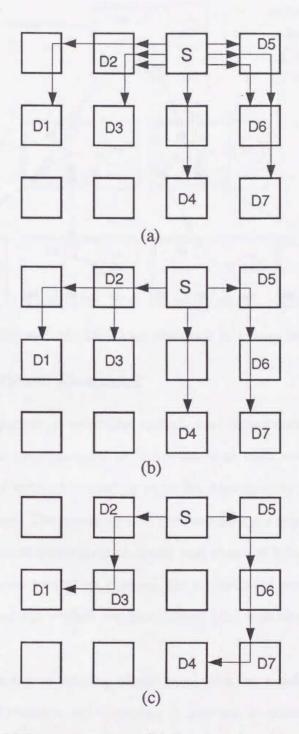

# 2.3 Message Switching

The message switching technique, i.e. the method by which data is passed from the input of a router to the output, can have a significant effect on the latency of the network. There are a number of possible switching techniques and these include circuit switching, packet switching, virtual cut-through routing and wormhole routing. Circuit switching was originally used in telephone networks and involves the formation of a physical channel between the source and destination nodes. In packet switching, or store-and-forward networks, complete packets are buffered at each node between the source and destination and the header of a packet may not leave a node until the tail has been received.

Both virtual cut-through [34] and wormhole routing [12] use cut-through

to reduce the network latency by allowing a packet to be forwarded as soon as the routing decision has been made.

Figures 2.6 (a) - (c) present a comparison of the latency of packet switching, circuit switching and cut-through routing techniques respectively. In each case a single packet is sent from the source node S via the intermediate nodes n0, n1 and n2. Given a packet length of L bits, a channel bandwidth of W bits per second and a distance of D hops between the source and destination nodes the latency for circuit switching is given by

$$T_{cs} = T_{setup} + \frac{L}{W} + D \tag{2.1}$$

the latency for cut-through routing is given by

$$T_{ct} = \frac{L}{W} + D \tag{2.2}$$

and the latency for store-and-forward switching is given by

$$T_{sf} = \frac{L}{W}(D+1) \tag{2.3}$$

If L >> D then  $T_{ct}$  becomes L/W and thus the distance has negligible effect on latency. Clearly the latency of store-and-forward routing is considerably higher than that of both circuit and cut-through routing. Also, in the absence of contention, the network latency of cut-through based switching is similar to that of circuit switching. However, if there is a large amount of contention in the network, the time taken to establish a complete circuit between the source and destination nodes can add a considerable amount to the delay of a circuit switched message.

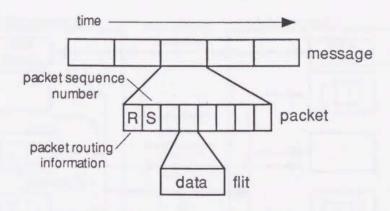

When channels become blocked, networks using wormhole routing buffer only small units of data called flow control digits or *flits* which are illus-

Figure 2.7: Division of information units

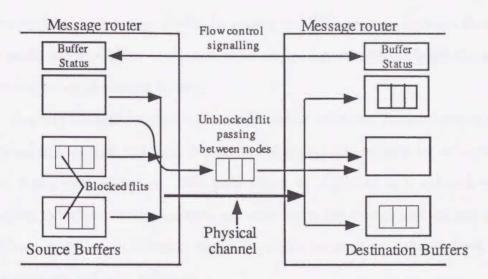

trated in Fig. 2.7, whereas networks employing virtual cut-through routing buffer entire packets and therefore requires considerably more buffer resource than wormhole routing. Wormhole routing and virtual cut-through routing provide low latency message delivery and often make use of virtual channels, which can significantly improve the throughput of an interconnection network [13]. Moreover, deadlock free routing algorithms for many multicomputer topologies which utilize these switching mechanisms have been proposed [17, 30]. Virtual channels provide excellent channel utilization and allow multiple disjoint logical networks to coexist on a single physical network, which is very useful for adaptive routing. Figure 2.8 presents a physical channel which is being shared by three virtual channels. Even though two of the destination buffers are full, the physical channel can still be utilized as the third destination buffer is free. Thus, the data in the free channel can pass the data in the blocked channels.

Figure 2.8: Three virtual channels sharing a unidirectional physical channel

# 2.4 Message Routing

The routing of a message in a direct IN involves the selection of an appropriate path from the source node to the destination node. Routing can be classified in several ways. In source routing, as the name implies, the source nodes determines the entire path of a packet prior to injecting it into the network. While this method may reduce the complexity of the message router hardware, it requires that each packet carry the information in its' header, increasing the packet size. Also, the path of the packet is fixed and cannot be changed once it has left the source node. Most current state-of-the-art direct INs employ distributed routing. In this case a routing decision is made at each intermediate router which lies on the path between the source and the destination nodes. The decision process determines whether the packet should be delivered to the local processor or forwarded to a neighboring router. If the message is to be forwarded, the routing algorithm decides which of the adja-

cent routers the message should be passed to. This routing decision should be as simple as possible to allow it to be easily implemented in hardware and provide minimal routing latency.

Routing can also be classified as *oblivious* or *adaptive*. In oblivious or *deterministic* routing, the path of a packet is completely defined by its' source and destination addresses. The path taken by a packet in a network employing dynamic routing depends not only upon the source and destination address, but also on dynamic network conditions such as network load, or the presence of faulty channels.

### 2.4.1 Deterministic Routing

Most current state-of-the-art interconnection networks employ deterministic routing. Although deterministic routers are not fault tolerant and have poor performance in networks experiencing high traffic loads or hot-spots, they are extremely simple and therefore fast. This makes them suitable in the practical implementation of interconnection network hardware [44]. Many multicomputer systems, such as the Cosmic Cube, NCUBE, J-machine, iWarp and Intel Paragon, therefore utilize deterministic routers. The most widely used routing algorithms for these machines are the e-cube routing algorithm [49], which is used for routing on hypercubes, and dimension order routing, which is used on n-dimensional meshes.

### e-cube Routing

In an *n*-cube with  $N=2^n$  nodes, each node's address is binary coded as  $a=(a_0,a_1,...,a_{n-1})$ . Given a source address  $s=(s_0,s_1,...,s_{n-1})$  and a des-

tination address  $d = (d_0, d_1, ..., d_{n-1})$  the routing function should determine a route from s to d with a minimum number of steps. Denoting the n dimensions as i = 1, 2, ..., n, where the ith dimension corresponds to the (i-1)st bit in the node address and letting  $v = v_{n-1} ... v_1 v_0$  be any node along the packet route, the route is determined as follows:

- 1. Compute the direction bit  $r_i = s_{i-1} \oplus d_{i-1}$  for all n dimensions (i = 1, 2, ..., n)

- 2. Start with dimension i = 1 and v = s

- 3. If  $r_i = 1$ , route from the current node v to the next node  $v \oplus 2^{i-1}$ , else skip this step.

- 4. Move to dimension i+1 (i.e.,  $i \leftarrow i+1$ ). If  $i \leq n$ , go to step 3, else quit.

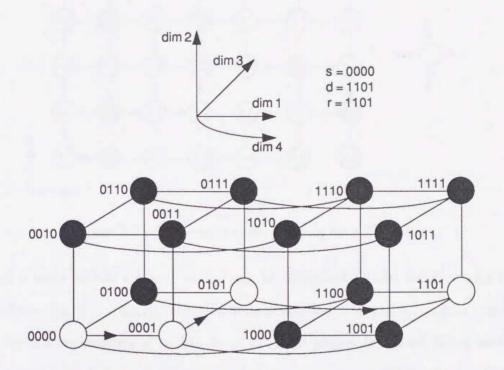

An example of e-cube routing on a 16 node hypercube is presented in Fig. 2.9. In the example n=4, s=0000 and d=1101. Thus  $r=r_4r_3r_2r_1=1101$ . The routing steps are summarized in Table 2.1. As can be seen in the example, the packet is routed from dimension 1 to dimension 4. If the *i*th bit of s and d are the same, no routing is needed along dimension i. Thus in the example, no routing is required for dimension 2. If the ith bit of s and d differ then the packet is routed from the current node along dimension i. this process is repeated until the destination is reached.

### Dimension order Routing

Dimension order routing is somewhat similar to e-cube routing. As was discussed previously, a k-ary n-cube is an n-dimensional cube of radix k,

Figure 2.9: e-cube routing on a hypercube

Table 2.1: Routing steps from s = 0000 to d = 1101

| Step  | $r_i$ | Operation           | Next node |

|-------|-------|---------------------|-----------|

| i = 1 | 1     | $0000 \oplus 2^{0}$ | 0001      |

| i = 2 | 0     | skip                | n/a       |

| i = 3 | 1     | $0001 \oplus 2^2$   | 0101      |

| i=4   | 1     | $0101 \oplus 2^3$   | 1101      |

Figure 2.10: Dimension order routing on a 2D mesh

and a node within a k-ary n-cube can be identified by the n-digit radix k address,  $(a_0, a_1, ..., a_{n-1})$ . Given a source address  $s = (s_0, s_1, ..., s_{n-1})$  and a destination address  $d = (d_0, d_1, ..., d_{n-1})$ , a packet is routed along each dimension i = 1, 2, ..., n, where the ith dimension corresponds to the (i-1)st digit in the node address, until  $s_{i-1}$  is equal to  $d_{i-1}$ .

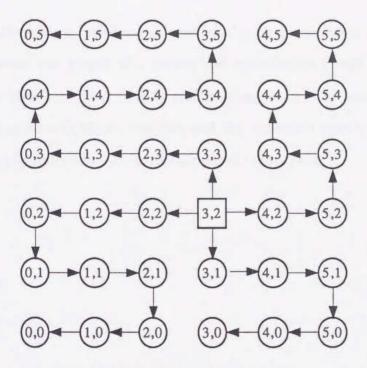

This is illustrated in Fig. 2.10, which shows routing between four (source, destination) pairs on a two-dimensional mesh. A packet from any source node  $s = (x_1y_1)$  to any destination node  $d = (x_2y_2)$  will first route along the X-axis until it reaches column  $y_2$ , where d is located. It will then route along the Y-axis until d is reached. A west-north route is taken from node (1,0) to (0,4). An east-north route is traversed from node (1,1) to (3,3). A west-south route is needed from node (4,4) to node (1,3) and an east-south route is required from node (5,2) to node (6,1).

Dimension order routing alone is sufficient to ensure that deadlock does not occur in mesh connected networks, as it prevents a circular wait for

Figure 2.11: (a) Dimension order routing (b) Adaptive routing

channel resources. However, the same dimension ordering scheme will not prevent a deadlock from occurring in a torus network. This is discussed in further detail in Section 2.5

### 2.4.2 Adaptive Routing

Although deterministic routers are simple to implement and therefore fast, they suffer from poor performance in the presence of hot-spot traffic and are not fault tolerant. Figure 2.11(a) presents a simple example in which dimension order routing may result in poor use of channel resources. Node (0,4) is sending a packet to (4,4), while at the same time node (1,4) has a packet to send to (4,1), node (2,4) as a packet to send to node (4,2) and node (3,4) has a packet to send to node (4,3). As dimension order routing in a two-dimensional mesh requires that the message be sent along the X-axis first, nodes (1,4), (2,4) and (3,4) are unable to sent their packets, even though

Figure 2.12: Physical communication channels divided into routing planes

a plethora of available channels exist. In Fig. 2.11(b) the routing rules have been relaxed to allow adaptive routing so that the packets from nodes (1,4), (2,4) and (3,4) can be transmitted concurrently with the packet from node (0,4). This allows better channel utilization and lower packet latency.

A number of different approaches have been proposed for the construction of adaptive and fault tolerant routers. Many of these proposals have advocated the use of virtual channels to supply multiple virtual paths between a given (source, destination) pair and thus provide varying degrees of adaptivity and fault tolerance. These include *Planar-Adaptive Routing* [9], Virtual Networks [32], Adaptive Routing with Virtual Channels [15] and The Turn Model for Adaptive Routing [30].

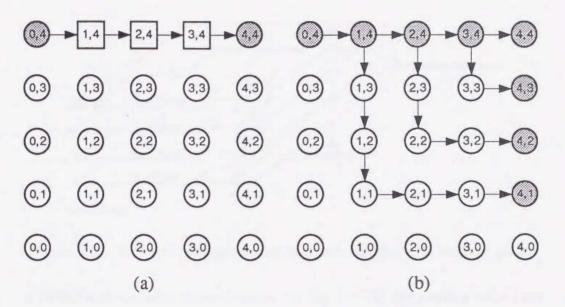

A general technique for providing adaptive routing is to partition the physical network into a number of disjoint subsets, where each subset constitutes a corresponding subnetwork. Packets are routed through different subnetworks depending upon the location of the source and destination nodes.

Figure 2.12 illustrates an application of this method to a 2D mesh. The

network is partitioned into four subnetworks or planes, the +X+Y plane, the -X+Y plane the +X-Y plane and the -X-Y plane. If, for example, the destination node is to the left and above the source node, that is, if  $d_x < s_x$ and  $d_y > s_y$ , then the packet will be routed along the -X+Y plane. If in this example  $d_x$  was equal to  $s_x$ , then the packet can be routed in either of the +X+Y or the -X+Y planes. This adaptive routing algorithm is said to be minimal and fully adaptive, that is, a packet can be delivered through any of the shortest paths between the source and destination. In addition to this, for the 2D mesh it can be proven to be deadlock free. However, providing minimal fully adaptive and deadlock free routing algorithms using this method for the general class of k-ary n-cubes may require additional channels. Linden and Harden [38] have demonstrated that a k-ary n-cube will require  $2^{n-1}$  subnetworks or routing planes and thus the number of channels required increases rapidly with n. The use of virtual channels is also expensive in terms of latency and cycle time[8] and requires that flow control information be sent in the reverse direction to signal the availability of buffering on the receiving node. This flow control information either requires extra wires, or will consume communications bandwidth from the reverse communications channel.

Ngai and Seitz also proposed a non-minimal adaptive mesh router which allows complete freedom of path selection between any (source, destination) pair, by using misrouting to prevent deadlock[41]. However, this approach requires the use of time stamps and prioritization to prevent livelock, requiring that extra state information be stored for each packet and results in a complex router design.

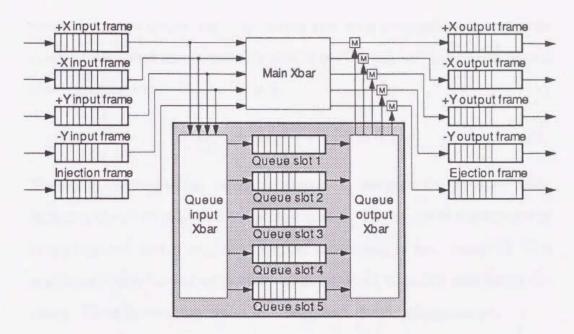

Figure 2.13: Two-dimensional chaos router

Another non-minimal adaptive router which utilizes misrouting to avoid deadlock is the Chaos router proposed by Konstantinidou and Snyder [35]. A block diagram of a two-dimensional router is presented in Figure 2.13. The Chaos router utilizes randomization to provide probablistic freedom from livelock and therefore does not require any extra state information to make routing decisions. The central queue of Fig. 2.13 is used to store packets which arrive at an input frame and are unable to be routed to an output frame before the entire packet is received. Once the central queue becomes full and a message is specified to be sent to the queue, one of the packets in the queue will be randomly selected and sent to the first available output frame.

Konstantinidou and Snyder have shown that no packet in a router is ever mis-routed with certainty or in other words, every message has a non-zero 2.5 Deadlock 26

chance to avoid misrouting [35]. Using this as a starting point they also demonstrated that the probability that a packet will not have been routed after i routing steps, where  $i \to \infty$  is:

$$\lim_{i \to \infty} Q(i) = (1 - \epsilon^{\log N})^i = 0 \tag{2.4}$$

Therefore, the longer that a message remains in the network, the more probable that it will be delivered to its' destination. The major disadvantages of this router are that it requires a central misrouting queue, queues at both inputs and outputs, and extra state information to make the misrouting decision. These factors may result in a large and slow implementation.

### 2.5 Deadlock

Deadlock occurs in an IN of a parallel computer when no packet can advance towards its destination because the queues or channels of the message system are full and no packet can release the queue space that it currently holds. This phenomenum has been studied extensively for wormhole routed networks and a general solution for deadlock avoidance in any wormhole routed network, based on the concept of virtual channels, has been proposed [18]. Deadlock in wormhole routed networks is normally described in terms of a network's routing function and channel dependency graph.

**Definition 4** A routing function,  $\Re: C \times N \to C$ , maps the current channel,  $C_c$ , and the destination node,  $N_d$ , to the next channel,  $C_n$ , on the route from the source node to the destination node. A channel is not allowed to route to itself,  $C_c \neq C_n$ .

2.5 Deadlock

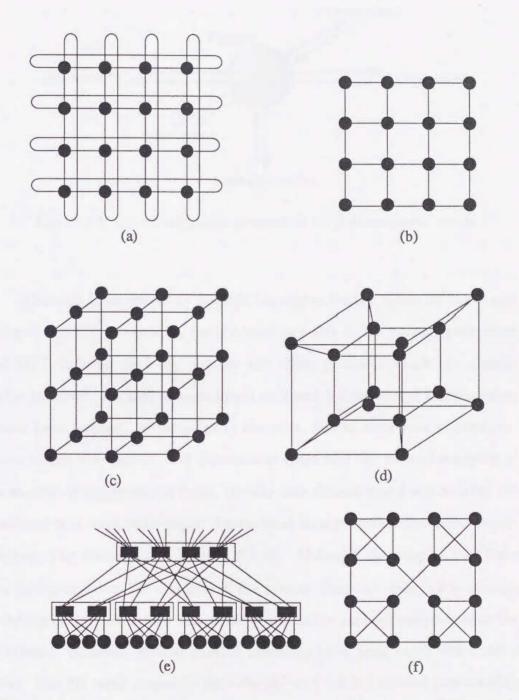

Figure 2.14: (a) Network and (b) its channel dependency graph without virtual channels. (c) Network and (b) its' channel dependency graph with extra virtual channels.

**Definition 5** A channel dependency graph, D, for an interconnection network, I, and routing function,  $\Re$ , is the directed graph, D = G(C, M). The vertices, D(C), are the channels of I and the edges, D(M), are the pairs of channels mapped by the routing function,  $\Re$ .

The routing function,  $\Re$ , for a network is deadlock free iff there are no cycles in its channel dependency graph. Deadlock can occur in the network of Fig. 2.14(a), due to a circular wait for channels, as there is a cycle in its' channel dependency graph, shown in Fig. 2.14(b). A circular wait for channels can occur if, for example, a flit from  $n_0$  that is destined for  $n_2$  is holding  $C_0$ , a flit from  $n_3$  that is destined for  $n_1$  is holding  $C_3$ , a flit from  $n_2$  that is destined for  $n_0$  is holding  $C_2$  and a flit from  $n_1$  that is destined for  $n_3$  is holding  $C_1$ . By adding a set of virtual channels to the network, as shown in Fig. 2.14(c), and modifying the routing function appropriately, the cycles in the channel dependency graph are removed, as shown in Fig. 2.14(d). In the figure, packets at nodes numbered less than their destination are routed on high channels and packets at nodes numbered greater than their destination are routed on low channels. Channel  $c_{00}$  is not used. There is now an ordering of virtual channels according to their subscripts:  $c_{13} > c_{12} > c_{11} > c_{10} > c_{03} > c_{02} > c_{01}$  and the routing function is now deadlock free.

### 2.6 Multicast Messages

Point to point, or unicast communication, in which a source node sends a message to a single destination node, is the basic structure supported by present multicomputers. Broadcast and multicast communications are the

transmission of a message from a source node to all other nodes in the system, and from a source node to a subset of the nodes in a system respectively. Broadcast communication can be viewed as a special case of a multicast communication, in which the same message is delivered to all of the nodes in the system [40].

Two parameters commonly used to measure the efficiency of multicast schemes are channel traffic and communication latency. Channel traffic is defined as the number of channels used to deliver the message under consideration and latency is defined as the longest packet transmission time involved. These two parameters are somewhat interrelated as is illustrated in Fig. 2.15. The unicast based multicast generates traffic = 14 and has has distance = 3, the tree based multicast has traffic = 9 and distance = 3 and the path based multicast has traffic = 7 and distance = 4.

Multicast communications can be implemented using multiple unicasts, software multicast trees, or by hardware multicast facilities. Multiple unicasts, while simple to implement, generate large amounts of unnecessary traffic which can cause blocking and contention in the network [37]. Software multicast trees, in which a worker node will forward the multicast message to its neighbors upon reception of the message, exhibit considerable speedup when compared to multiple unicasts [51], but are still inferior to hardware based multicast schemes. Although hardware based multicast schemes offer the best potential performance for the implementation of multicasting, it has been shown that these schemes may result in deadlock in those networks which employ wormhole routing [37].

Figure 2.15: (a) Multicast by unicast (b) Tree based multicast (c) Path based multicast

Figure 2.16: Multicast deadlock in binary tree

#### 2.6.1 Multicast Deadlock

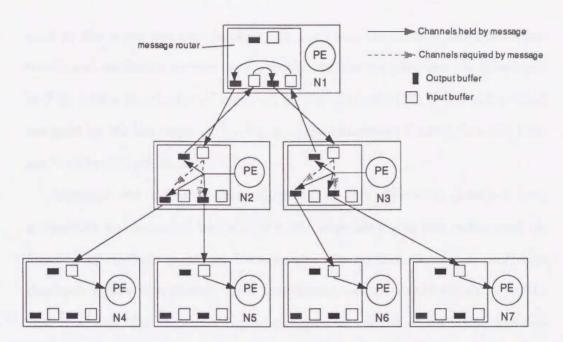

One of the properties of wormhole routed, tree based multicast schemes is that, due to the small amount of buffer space at each node, a potentially large number of network resources must be concurrently held by a single multicast message. The resources that the messages are competing for in the network are the communication channels and message buffers of each node. Each physical communication channel has a dedicated message buffer and typically the message buffers are partitioned into separate virtual channel buffers [13].

While a number of routing algorithms, such as e-cube routing in hypercubes and dimension order routing in meshes, guarantee deadlock free routing of unicast messages, multicast trees based on these algorithms are prone to deadlock. In fact, networks which are inherently free of deadlock, such as the *n-ary tree* and *fat tree* [36], may also deadlock if more than one tree based multicast occurs concurrently. In the simple example presented in Fig. 2.16 a deadlock has occurred as the channels (N3,N6),(N3,N7) that are held by N3 are required by N2, and the channels (N2,N4),(N2,N5) that are held by N2 are required by N3.

Although the unicast routing algorithm of this network is deadlock free, a deadlock has occurred because of cyclic dependency in the concurrent allocation of multiple resources between the two multicasts. Thus, multicast deadlock differs significantly from traditional unicast deadlock, as in multicast deadlock, the resources contributing to the deadlock situation are distributed over a number of nodes. Traditional methods of deadlock avoidance, such as releasing all of the deadlocked resources once deadlock is detected or requesting all of the required resources prior to initiating an operation which might result in deadlock, are not suitable for prevention of multicast deadlock. Releasing the distributed deadlocked resources results in considerable waste of communications bandwidth and may be difficult to implement due to the large number of distributed resources which may need to be released, while requesting all of the necessary channels prior to initiating a multicast would significantly increase the multicast latency. New methods of deadlock avoidance for multicast must therefore be found.

Multicast deadlock avoidance has typically been achieved by limiting the growth of the multicast tree and Lin, McKinley, and Ni have extensively studied the use of multi-path multicasting algorithms utilizing Hamiltonian paths to ensure that deadlock does not occur [40, 37, 51]. In addition to deadlock avoidance, multi-path multicast allows arbitrary multicast destinations

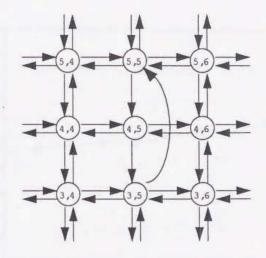

Figure 2.17: Multipath multicast

and they have demonstrated that this technique has the added advantage of reducing the amount of traffic in the network. Figure 2.17 illustrates a multi-path broadcast in an  $6 \times 6$  mesh network. As can be seen in Fig. 2.17, a multi-path message is broadcast by sending four copies of the message on individual multicast paths. Similarly, Byrd et al. have investigated the restricted branch multicast approach to multicasting [7]. This approach requires that a multicast message can only be split into two paths at any given node, and that one of these paths must be connected to the local processing element.

Multi-path and restricted branch multicasting have a number of disadvantages. For example both restricted branch and multi-path multicasting require that the packet header store multiple destination addresses, as all of the destinations for a broadcast or multicast must be stored in the header, which increases the length of a packet and complicates router design. In addition to this, restricted branch multicasting requires an extra port resource to guarantee deadlock freedom, and the algorithm used in multi-path multicasting to determine the multicast paths is complex.

## Chapter 3

# Tokkyū: A High-Performance, Randomizing, Adaptive Message Router with Packet Expressway

The Tokkyū router is a new high-performance message router for k-ary n-cube multicomputer systems[26, 29, 28]. The k-ary rings that make up the interconnection network are constructed using uni-directional register-insertion buses. Tokkyū utilizes misrouting to prevent deadlock and randomization to prevent livelock in a fully adaptive routing environment. Any packet arriving at an input to a Tokkyū router that can not be profitably routed is immediately misrouted. This is significantly different than both the Ngai/Seitz router and the Chaos router which defer the misrouting of a packet that is waiting for an output until it is to be overwritten by a newly arriving packet. The misrouting rate is minimized by utilizing a small number of queues, placed at the outputs of the communication ports. As blocking or buffering flow control is not used, all of the available communications bandwidth can be utilized for sending messages between processors in the system. Finally,

uncongested network performance is improved by the inclusion of the *packet* expressway, which provides a low latency bypass path for packets which need not pass through the core of the router.

### 3.1 The Register-insertion Bus

High performance ring buses have become a favorable alternative in the implementation of local area networks [45]. However, LAN/WAN structures are not directly applicable to INs due to differences in the node structure and communications patterns [15]. The use of the unidirectional register-insertion bus in the construction of INs does, however, have a number of advantages. These advantages include:

- A packet may propagate through a large number of bus interfaces without being buffered.

- Processors are free to inject packets at any time, subject to available space in the transmit queue. Thus there is no global arbitration, as each processor can decide whether to inject a packet according to information local to its bus interface.

- Active repeaters can be used at the output of each message router, instead of the pulldown structure required for a bi-directional bus, thus making the network more scalable.

### 3.1.1 Register-insertion Bus Operation

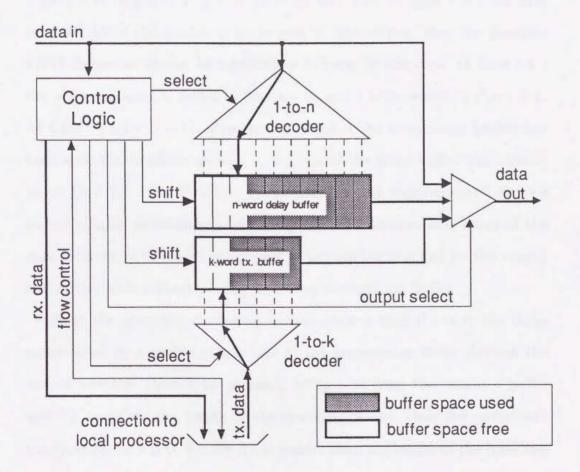

With reference to Fig 3.1 the operation of a register-insertion bus is as follows; Assume that the input and output data is synchronized at the same transmission rate, so that for each word received, another can be transmitted. The transmit (tx.) buffer is used to temporarily store a packet from the local processor while it is waiting for injection onto the bus. These packets are of variable length and so only a portion of the tx. buffer may be used for a particular packet, however, the packet length must not exceed the length of the tx. buffer. The function of the delay buffer can explained by first considering the area currently being used. The used, or active portion of the delay buffer, operates as a FIFO queue that delays the incoming packets. Assuming that the entire delay buffer has a capacity of n words and that iwords are currently used,  $1 \le i \le n$ , then n-i words remain for the unused or inactive portion. Thus locations  $w_0, w_1, \ldots, w_{i-1}$  of the delay buffer are active and locations  $w_i, w_{i+1}, \ldots, w_{n-1}$  are inactive. If, in each time step t, a new word can be received, and a new word is to arrive at time t+1, then the active portion of the delay buffer represents a FIFO queue containing the words which arrived at times  $t, t+1, \ldots, t+(i-1)$ . At time t+1 the word stored in  $w_0$  is removed from the queue and sent to the output. Simultaneously, the incoming word is added to the queue such that locations  $w_0, w_1, \ldots, w_{i-1}$  now contain data which arrived at times  $t+1, t+2, \ldots, t+i$ , and the queue length remains unchanged.

It is desirable that in each time step, if  $i \geq 1$ , the queue size be reduced. A reduction can take place iff the data received at the input is not part of any packet destined for the output. In this case, the previous discussion should be modified so that the incoming word is not stored in location  $w_{i-1}$  and also so that i is reduced to i' = i - 1. Furthermore, if i = 0, then any incoming word need not be stored at all and can pass directly to the output.

Figure 3.1: Register-insertion bus interface

In this case the incoming word is not stored in location  $w_{i-1}$  and i is constant at i = 0.

The inactive portion of the buffer is essential for the injection of packets into the network from the tx. buffer. Assuming that the tx. buffer contains a packet of length l,  $1 \leq l < (n-i)$ , and that at time t+i the first word of the of this packet is to be sent to the output, then the previous FIFO discussion should be modified as follows; In this case, at time t+i the incoming word is stored in location  $w_i$  and i is increased to i'=i+1. At time t+((i+l)-1), after the last word of the transmitted packet has been sent, the locations  $w_0, w_1, \ldots, w_{(i+1)-1}$  of the delay buffer now contain words  $t, t+1, \ldots, t+((i+l)-1)$ . In addition, the requirements for queue reduction must be modified such that queue reduction can only occur iff the data received at the input is not part of any packet destined for the output and no packet is currently being sent from the local tx. buffer.

From the preceding discussion we can observe that if i = 0, the delay experienced by a packet is only due to the propagation delay through the output selector. Also if no packet is being sent from the transmit buffer and i is less than the length of the incoming packet, then the packet will cut-through the FIFO. Finally if i is greater than the length of the incoming packet, or a packet is being transmitted and l is greater than the length of the incoming packet, then the incoming packet will be completely buffered in the FIFO, in a store-and-forward manner.

The concept of the register-insertion bus can easily be extended to the k-ary n-cube as is shown in Fig. 3.2, which illustrates the structure of a single port of an n-dimensional register-insertion bus router. The delay buffer of

Figure 3.2: N-dimensional register-insertion bus port.

Fig 3.1 is replaced by a group of output buffers. These buffers store packets that are changing dimensions, in addition to those which must be delayed while the local processor injects new packets into the network. Also, the control is now distributed between the input and output control sections to improve performance.

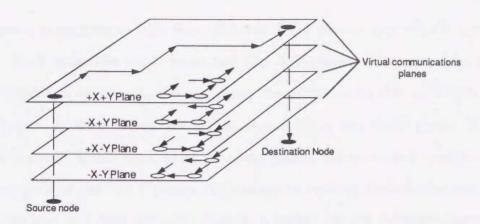

### 3.2 Architecture of the Tokkyū Router

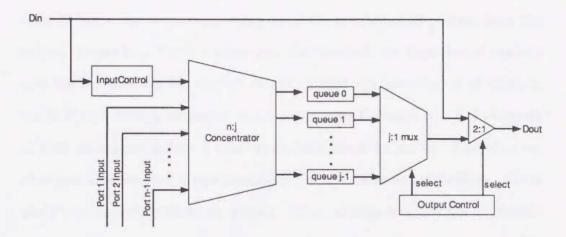

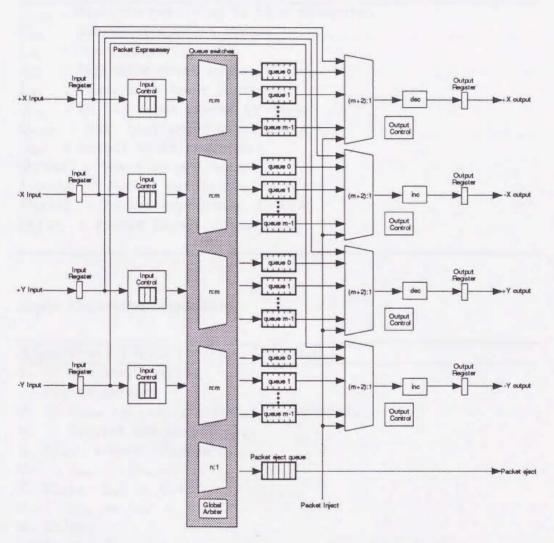

The architecture of a two-dimensional Tokky $\bar{\mathbf{u}}$  router is presented in Fig. 3.3. The input queues of a typical oblivious router have been replaced by m queues per output and n:m switches connect the inputs to the queues, where n=4 for a two-dimensional router. A small input frame is also provided in each input controller to temporarily store several words of an incoming packet while a routing decision is made. Each of the output queues is capable of holding multiple, variable length packets and all of the queues support cutthrough routing. As the router may buffer complete packets when output contention occurs, it requires the use of comparatively short packets, i.e. less

than 32 bytes. An output controller schedules the output of packets from the output queues in a FIFO manner and also controls the injection of packets into the network via the output switch. Under the assumption of uniform traffic distribution, each packet in a k-ary n-cube traverses  $\sigma = k/4$  channels in each dimension before a routing decision must be made. Therefore we have provided the  $packet\ expressway$  which, in the absence of blocking, allows packets to pass directly to an output. Thus, a single unidirectional channel in any dimension can be viewed as a high speed register-insertion ring[26]. The header of each packet is updated prior to entering the output register, when passing through the inc or dec modules, to reflect the progress of the packet through the network.

As misrouting is used to prevent deadlock and randomization is used to prevent livelock, correct operation of the router can be guaranteed provided no packet, or part of a packet, is lost due to buffer overflow. The aggregate data rate into any router must therefore never exceed the aggregate data rate out of the router. A simple way for the data rates within the network to remain tightly matched is through the use of a globally distributed clock. Then, by restricting packet injection to only occur when sufficient space exists to completely store any packet which may arrive while injection is taking place, buffer overflow is guaranteed not to occur.

### 3.2.1 Router Operation

The operation of the router can be understood by examining the control algorithms of its major components. These components are the input and the output controllers of each port, the queue controller associated with each

Figure 3.3: Architecture of a two-dimensional Tokky $\bar{\mathbf{u}}$  router

output queue and the arbiter which controls access to the output queues via the queue switches. Throughout this section the following notation is adopted for convenience:

```

D_{rem}: Distance remaining in this dimension P_{len}: Length of current packet I_{len}: Input count register J_{len}: Injection count register L_{len}: Queue load count register Q_{len}: No. of words stored in queue Q_{max}: Max. contiguous queue space O_{len}: Output count register Output: Queue output selected Passive: Packet expressway selected Bypass: Packet expressway in use Inject: Packet injection selected

```

#### Input Controller Algorithm

```

Algorithm 3.1 Input Controller Algorithm

1. If no packet, wait;

2. Decode header;

3. If D_{rem} = 0 or Passive not asserted,

4. Request new output(s);

5. Else, assert Bypass;

6. I_{len} = P_{len} - 1;

7. While I_{len} > 0 do

8. I_{len} = I_{len} - 1;

9. Enddo;

10.Reset Bypass;

11.Goto 1;

```

With reference to Algorithm 3.1 the input controller operation is as follows; The received data is sampled by the input controller on each clock cycle to test for a valid packet header. Upon the detection of the first word of a packet, the header is decoded to generate the output request(s). A packet which is j-dimensions from its destination will generate j valid output requests. If the packet has finished traversing the current dimension ( $D_{rem}=0$ ) or the output switch is not in the Passive state, then the output request(s) will be passed to the global arbiter. Bypass is asserted if  $D_{rem} \geq 1$  and the output switch is Passive, to signal that the packet is passing to the output via the packet expressway. The packet length is loaded into the input count register and on each subsequent clock cycle  $I_{len}$  is decremented as each new word of the packet is received. Once  $I_{len}$  has decremented to zero, indicating that the entire packet has been received, Bypass is reset and the input controller begins to sample the input for a valid header once again.

#### Output Controller Algorithm

With reference to Algorithm 3.2 the output controller operation is as follows; Operation of the output controller begins with setting the output switch to the Passive state, allowing any packet on the packet expressway to pass directly to the output register. Once an output request is detected and no packet is currently bypassing the output, the request is processed and the output switch is set accordingly. If an injection request is being made and there exists sufficient space for any incident packet to be temporarily stored while the new packet is being injected  $(Q_{max} \geq J_{len})$ , then the switch is set to the injection input. This ensures that there always exists sufficient space to buffer an arriving packet within the node while a new packet is injected so that no information, i.e. no part of a packet, is lost. The packet length

#### Algorithm 3.2 Output Controller Algorithm

```

1. Assert Passive;

2. If no output requests, wait;

3. If Bypass is asserted, wait;

4. Reset Passive;

5. While output requests do

6. If injection request,

If Q_{max} \geq J_{len},

7.

Assert Inject;

8.

If Inject not asserted and output request,

9.

10.

Assert Output;

Get first output request;

11.

12.

O_{len} = P_{len};

While O_{len} > 0 do

13.

14.

Output word;

15.

O_{len} = O_{len} - 1;

16.

If Output asserted, Q_{len} = Q_{len} - 1;

17.

Else, J_{len} = J_{len} - 1;

Enddo;

18.

29. Enddo;

20.Goto 1;

```

is loaded into the output count register and a new word of the packet being output is placed in the output register during each clock cycle.  $O_{len}$  and either of  $Q_{len}$  or  $J_{len}$  are decremented until the entire packet has been sent.

### Global Arbiter Algorithm

#### Algorithm 3.3 Global arbiter algorithm

- 1. If no requests, wait;

- 2. While requests do

- Get first request;

- If requested output(s) free,

- 5. Assign available queue;

- 6. Else, Assign random queue;

- 7. Enddo;

- 8. Goto 1;

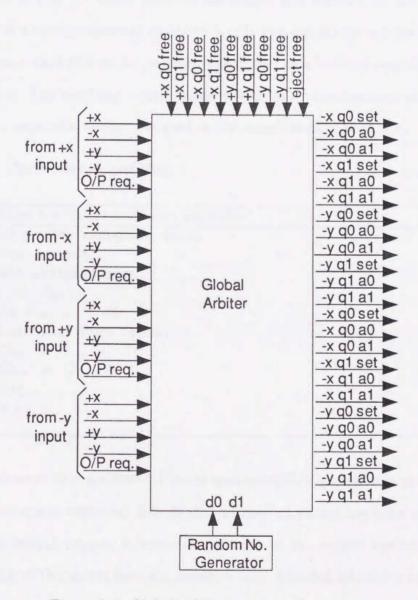

With reference to Algorithm 3.3 the output controller operation is as follows; The global arbiter processes each output request sequentially, beginning with the request at the head of the request queue. The arbiter examines the output request and the current state of the queue switches and the output queues in an attempt to profitably route the requesting packet. If it is not possible to profitably route the packet, it will be randomly misrouted to any available output queue. Although it may appear that this approach of immediately misrouting blocked packets will result in excessive misrouting of packets, the discussion in Sect. 3.3 and the simulation results of Sect. 3.4 demonstrate that the careful selection of the switch and output queue sizes prevents this from occurring.

The arbiter algorithm presented here processes each input sequentially. At first glance it might be appear that it would be beneficial to process all

Figure 3.4: Global arbiter inputs and outputs

of the inputs simultaneously using a large combinatorial logic circuit, as this may result in shorter average time to make routing decisions. However, with reference to Fig. 3.4 which presents the inputs and outputs for the arbiter section of a two-dimensional router with only two queues per output port, it can be seen that this would require the solution to a boolean equation with 31 inputs. The resulting circuit would therefore be cumbersome and slow, and so a sequential design was used in the simulations of Sect. 3.4.

#### Queue Controller Algorithm

```

Algorithm 3.4 Queue controller algorithm

```

- If no packet assigned, wait;

Request output;

- Select assigned port;

- 4.  $L_{len} = P_{len}$ ;

- 5. While  $L_{len} > 0$  do

- Load word from input;

- 7.  $L_{len} = L_{len} 1;$

- 8.  $Q_{len} = Q_{len} + 1;$

- 9. Enddo;

- 10.Goto 1;

With reference to Algorithm 3.4 the output controller operation is as follows; When the queue controller detects that a received packet has been assigned to it, an output request is immediately made to the output controller and the length of the packet from the assigned port is loaded into the queue load count register  $(L_{len})$ . A new word of the packet is loaded into the queue in each clock cycle,  $(L_{len})$  is decremented and the count of the number of words currently stored in the queue  $(Q_{len})$  is incremented, until the entire packet has been received  $(L_{len} = 0)$ .

### 3.3 Switch and Buffer Design

The misrouting of packets provides a simple solution to the problem of dead-lock. However, any packets which are misrouted will remain in the network, requiring channel and buffer resources. This may exacerbate any existing congestion and result in further misrouting. It is therefore desirable that the output switch and buffer sizes be selected so that under normal operation there is a minimal amount of misrouting occurring. Karol et al [33] and Yeh et al [52] have studied in detail the design and performance of systems employing output queues. However, their analyses have focused on those systems in which an arriving packet can only select one possible output from those available, and where the number of inputs, n, approaches infinity. We extend their work here by examining the switch and buffer requirements for those cases in which an arriving packet may select from a number of outputs, and we focus on small values of n, typically 4 or 6. To simplify the following discussion we assume that all packets are of fixed size.

#### 3.3.1 Switch Evaluation

Assume that fixed size packets arrive at the n inputs to the k-ary n-cube router. In each time slot, packet arrival is governed by independent and identical Bernoulli processes and packets arrive independently at each input with probability  $\rho$ . Under the assumption of uniform random traffic in a k-ary n-cube, on average, each packet must traverse  $\sigma = k/4$  channels in each dimension and the average distance of a packet,  $d_{ave}$ , is  $(n \times \sigma)$ . Of the arriving packets,  $1/d_{ave}$  are destined for the local processor and therefore the

probability that an arriving packet is destined for one of the queue switches associated with an output, which we define as  $\alpha$ , is equal to  $\rho - (\rho/d_{ave})$ . The probability of i packets arriving at the router inputs, all destined for a single output queue switch,  $a_i^*$ , has the binomial probabilities

$$a_i^* = \binom{n}{i} \left(\frac{\alpha}{n}\right)^i \left(1 - \frac{\alpha}{n}\right)^{n-i}$$

$$i = 0, 1, 2, ..., n$$

(3.1)

If the probability of misrouting is very low then most arriving packets will be profitably routed, i.e. routed towards their destinations. Arriving packets are therefore equally likely to be destined for only n-1 of the available outputs, as the  $n^{th}$  output will send the packets in the opposite direction to which they have just travelled, and thus Eq. 3.1 becomes

$$a_{i} = {n-1 \choose i} \left(\frac{\alpha}{n-1}\right)^{i} \left(1 - \frac{\alpha}{n-1}\right)^{n-1-i}$$

$$i = 0, 1, 2, ..., n-1$$

$$(3.2)$$

Packets arriving at the n router inputs to the k-ary n-cube must compete for access to the m queues associated with each output, via the queue switches. If i packets arrive at the inputs at the same time, all destined for the same output, and i < m, then all requests can be satisfied by the switch. If i > m, then i - m requests will be rejected and these packets will have to be misrouted. It follows then that the probability of an output request being unsuccessful, for the case where a packet can be successfully routed via only

one output, is given by the sum of the probabilities of i > m

$$\Pr(M_{j=1}) = \frac{1}{\alpha} \sum_{i=m+1}^{n-1} \left[ (i-m) \binom{n-1}{i} \right]$$

$$\cdot \left( \frac{\alpha}{n-1} \right)^i \left( 1 - \frac{\alpha}{n-1} \right)^{n-1-i}$$

(3.3)

Extending Eq. 3.3 to the case where a packet can be profitably routed via more than one output: If i packets arrive at the router inputs at the same time, each of which can be profitably routed via j outputs, and  $i \leq jm$ , then all of the requests can be satisfied by the switches. If i > jm, then i - jm requests will be rejected and these packets will have to be misrouted. The probability that i > jm is

$$\Pr(i > jm) = \frac{1}{\alpha} \sum_{i=jm+1}^{n-1} \left[ (i - jm) \binom{n-1}{i} \right] \cdot \left( \frac{\alpha}{n-1} \right)^{i} \left( 1 - \frac{\alpha}{n-1} \right)^{n-1-i}$$

$$(3.4)$$

In order to evaluate the effect of allowing packets to request more than one output, we need to determine  $\beta_j$ , the fraction of arriving packets with j dimensions still to traverse, where  $0 \leq j \leq n$ . To calculate  $\beta_j$ , we need to determine the distance distribution for newly generated packets. This is given by the number of ways in which the n-tuple describing the total distance to travel in each dimension,  $(c_0, c_1, c_2, ..., c_{n-1})$ , can be arranged so that the sum  $c_0 + c_1 + c_2 + ... + c_{n-1}$  is equal to the distance to travel,  $d_g$ , where  $0 \leq c_l \leq k/2$  for all l = 0, 1, 2, ..., n - 1. The number of solutions for the equation  $c_0 + c_1 + c_2 + ... + c_{n-1} = d_g$ , which we define as  $\Psi_{d_g}$ , is given by the coefficient of  $x^{d_g}$  in the generating function,  $f(x) = (1 + x + x^2 + ... + x^{k/2})^n$ ,

Table 3.1: 2-tuples defining total distance to travel and  $\Psi_{d_g}$  for packets in an 8-ary 2-cube

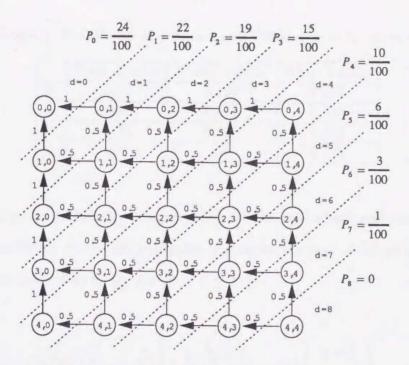

| $d_g$ | j = 1      | j = 2                | $\Psi_{d_g}$ |