Dissertation 学位請求論文

3. 345

# Simulation-based Device Characterization and its Application to Device Parameter Optimization

計算機シミュレーションによる 集積デバイスの特性抽出および デバイスパラメータ最適設計

Supervisor: Professor Kunihiro Asada 指導教官: 浅田邦博 教授

> Rimon Ikeno 池野 理門

Department of Electronic Engineering, Faculty of Engineering, University of Tokyo 東京大学 工学部 電子工学科

> December 20th, 1996 平成8年12月20日提出

# Contents

| 1 | Introduction |                                                               |   |

|---|--------------|---------------------------------------------------------------|---|

|   | 1.1          | Roles of Computer Simulations in Semiconductor Device Design  | 1 |

|   | 1.2          | A Brief History of Analytical and Numerical Modeling of Semi- |   |

|   |              | conductor Devices                                             | 3 |

|   | 1.3          | Outline of This Thesis                                        | 7 |

| 2 | Eva          | luation of Power Consumption of CMOS Circuits with            |   |

|   | Phy          | sics-based Models 13                                          | 3 |

|   | 2.1          | Introduction                                                  | 3 |

|   | 2.2          | Formulation of Power Consumption in CMOS Circuits 14          | 4 |

|   |              | 2.2.1 Power consumption in CMOS circuits                      | 4 |

|   |              | 2.2.2 Dynamic power consumption                               | 5 |

|   |              | 2.2.3 Static power consumption                                | 6 |

|   |              | 2.2.4 Total power and energy consumption                      | 6 |

|   | 2.3          | Circuit Element Modeling                                      | 7 |

|   |              | 2.3.1 Requirement of physics-based accurate models 1          | 7 |

|   |              | 2.3.2 Drain current modeling of MOSFET                        | 8 |

|   |              | 2.3.3 Load capacitance model                                  | 1 |

|   | 2.4          | Calculation Results                                           | 2 |

|     |      | 2.4.1    | Basic characteristics of a CMOS inverter circuit         | 22 |

|-----|------|----------|----------------------------------------------------------|----|

|     |      | 2.4.2    | Evaluation of consumed energy per switching              | 23 |

|     | 2.5  | Conclu   | ısion                                                    | 25 |

| 3   | Dev  | rice Pa  | rameter Optimization for Low Power VLSIs using           |    |

|     | Circ | cuit Si  | mulation                                                 | 27 |

|     | 3.1  | Introd   | uction                                                   | 27 |

|     | 3.2  | Circui   | t Optimization Criteria                                  | 28 |

|     |      | 3.2.1    | Switching energy optimization                            | 28 |

|     |      | 3.2.2    | Power consumption and circuit speed optimization $$ . $$ | 28 |

|     | 3.3  | Restri   | ctions for Device Parameter Ranges                       | 30 |

|     |      | 3.3.1    | Limitations from bulk punch-through phenomena            | 30 |

|     |      | 3.3.2    | Limitations from drain-induced barrier lowering $\dots$  | 31 |

|     |      | 3.3.3    | Limitations from avalanche break down                    | 31 |

|     | 3.4  | Device   | e Parameter Optimization                                 | 33 |

|     |      | 3.4.1    | Switching energy optimization                            | 33 |

|     |      | 3.4.2    | Delay time minimization under restricted chip power $$ . | 38 |

|     | 3.5  | Conclu   | usion                                                    | 41 |

| 4   | Dox  | riao Do  | rameter Estimation of SOI MOSFETs using One-             |    |

| ıt: |      |          | nal Numerical Simulation for Subthreshold Char-          |    |

|     |      | eristics |                                                          |    |

|     |      |          |                                                          | 44 |

|     | 4.1  |          | luction                                                  | 44 |

|     | 4.2  |          | Dimensional Numerical Simulation of SOI MOSFETs          | 46 |

|     |      | 4.2.1    | Basic equations for One-dimensional Poisson equation     |    |

|     |      |          | based device simulation                                  | 46 |

|     |      | 122      | Drain gurrant modeling                                   | 10 |

|   | 4.3 | Evalua | ation of One-Dimensional Device Simulator and Device     |    |

|---|-----|--------|----------------------------------------------------------|----|

|   |     | Param  | eter Estimation                                          | 50 |

|   |     | 4.3.1  | Accuracy of one-dimensional device simulator             | 50 |

|   |     | 4.3.2  | Threshold voltage characteristics with substrate bias    |    |

|   |     |        | condition                                                | 52 |

|   |     | 4.3.3  | Device parameter estimation                              | 53 |

|   | 4.4 | Prope  | rty of parameter fitting results                         | 54 |

|   | 4.5 | Concl  | isions                                                   | 56 |

| 5 | Nur | nerica | l Methods for Robust and Efficient Two- and              |    |

|   | Thr | ee-Dir | nensional Device Simulation of SOI MOSFET                | 59 |

|   | 5.1 | Introd | uction                                                   | 59 |

|   | 5.2 | Robus  | t simulation for the hysteresis phenomena of SOI MOS-    |    |

|   |     | FET's  | by Quasi-Transient Method                                | 60 |

|   |     | 5.2.1  | Qusi-Transient device simulation                         | 60 |

|   |     | 5.2.2  | Efficiency of QT device simulation                       | 62 |

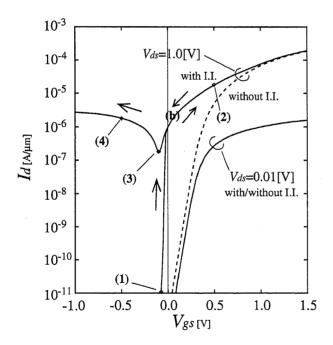

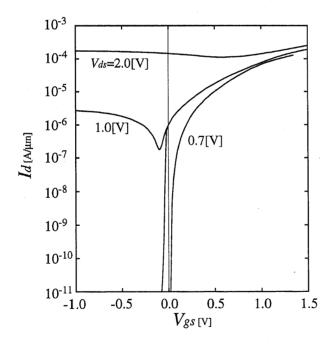

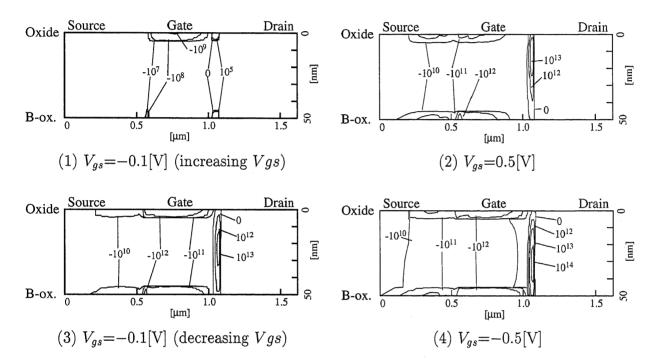

|   |     | 5.2.3  | Device Simulation of Single-Transistor Latch Phenomena   | 64 |

|   | 5.3 | Device | e Structure Dependent Convergence Ability of Matrix      |    |

|   |     | Soluti | ons                                                      | 67 |

|   |     | 5.3.1  | Problems in iterative linear solutions in device simula- |    |

|   |     |        | tion of SOI MOSFETs                                      | 67 |

|   |     | 5.3.2  | Convergence efficiency iterative linear solutions with   |    |

|   |     |        | SOI layer thickness                                      | 68 |

|   |     | 5.3.3  | Data dependent scaling scheme                            | 73 |

|   | 5.4 | Concl  | usions                                                   | 76 |

| 6 | On  | ie-Dim | ensional Analysis of Subthreshold Characteristics        |    |

|   | of S     | OI-MC         | OSFET Considering Quantum Mechanical Effects                                 | 79   |

|---|----------|---------------|------------------------------------------------------------------------------|------|

|   | 6.1      | Introd        | uction                                                                       | 79   |

|   | 6.2      | Quant         | um Mechanical Formulations                                                   | 80   |

|   |          | 6.2.1         | ${\bf Two\text{-}dimensional\ electron\ calculation\ with\ self-consistent}$ |      |

|   |          |               | Schrödinger and Poisson equations                                            | 80   |

|   |          | 6.2.2         | Quantum mechanical mobility modeling in two-dimension                        | ally |

|   |          |               | quantized electron layer                                                     | 84   |

|   |          | 6.2.3         | Drain current modeling in quantum mechanical analysis                        | 90   |

|   | 6.3      | Mobili        | ty Evaluation of Quantum Mechanical Model                                    | 91   |

|   |          | 6.3.1         | Back-bias dependent mobility characteristics                                 | 91   |

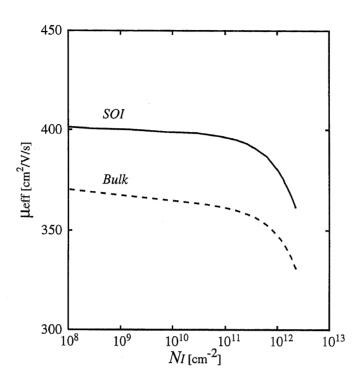

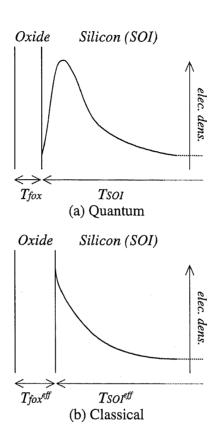

|   |          | 6.3.2         | Mobility calculation for SOI and bulk MOSFET                                 | 92   |

|   | 6.4      | Device        | Parameter Estimation by Quantum Mechanical Models                            | 94   |

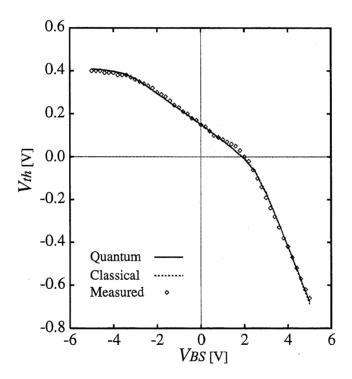

|   |          | 6.4.1         | Parameter fitting results                                                    | 94   |

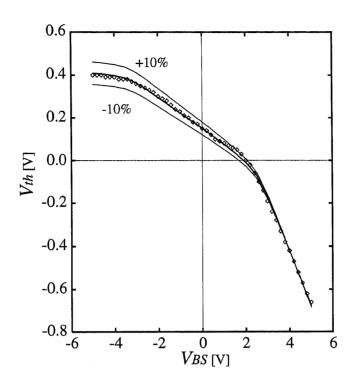

|   |          | 6.4.2         | Effects of parameter fluctuation                                             | 96   |

|   |          | 6.4.3         | Device-dimensional scaling and quantum mechanical                            |      |

|   |          |               | effects                                                                      | 100  |

|   | 6.5      | Conclu        | sion                                                                         | 102  |

| 7 | <b>C</b> | _1            |                                                                              | 100  |

| 7 | Cor      | onclusion 100 |                                                                              | 106  |

# List of Figures

| 1.1 | Computer-Aided Design techniques in VLSI development                     | 2  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Simulation and fabrication stages on VLSI development                    | 3  |

| 1.3 | Early history of analytical and numerical semiconductor mod-             |    |

|     | eling                                                                    | 4  |

| 2.1 | Inverter characterization by circuit simulation                          | 15 |

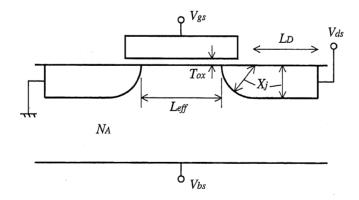

| 2.2 | Schematic of MOSFET                                                      | 17 |

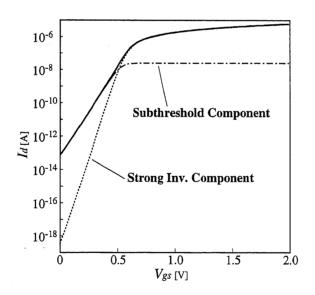

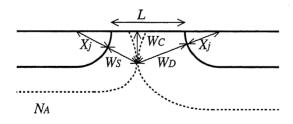

| 2.3 | Charge sharing model                                                     | 19 |

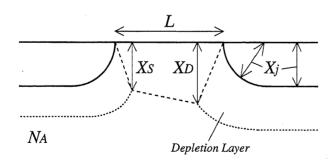

| 2.4 | $I_{d}$ - $V_{gs}$ characteristics of nMOSFET                            | 20 |

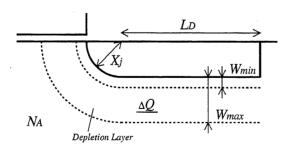

| 2.5 | Junction capacitance modeling                                            | 21 |

| 2.6 | Basic characteristics of CMOS inverter circuit                           | 22 |

| 2.7 | Total switching energy of inverter circuit, $\mathcal{N}_A$ as parameter | 24 |

| 2.8 | Total switching energy of inverter circuit, $T_{ox}$ as parameter        | 24 |

| 3.1 | Circuit speed limitation with power restriction                          | 29 |

| 3.2 | Bulk punch-through                                                       | 30 |

| 3.3 | Surface avalanche breakdown concerning effective field                   | 32 |

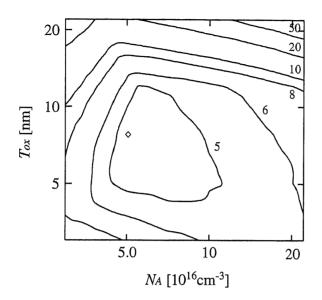

| 3.4 | Minimum value of total switching energy $[fJ]$                           | 33 |

| 3.5 | Optimum device parameters for the minimum energy con-                    |    |

|     | sumption                                                                 | 34 |

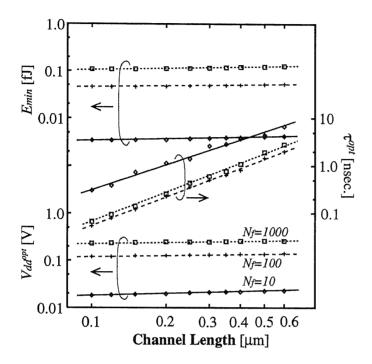

| 3.6 | Dependence of $E_{min}$ , $V_{dd}^{opt}$ and $\tau^{opt}$ on $L_{eff}$   | 35 |

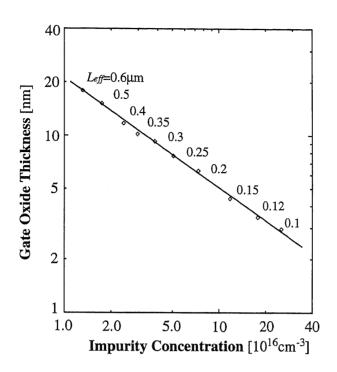

| 3.7  | Channel length dependent optimum device parameters                       | 36 |

|------|--------------------------------------------------------------------------|----|

| 3.8  | Fan-out dependent $E_{min}$ , $V_{dd}^{opt}$ and $\tau^{opt}$            | 36 |

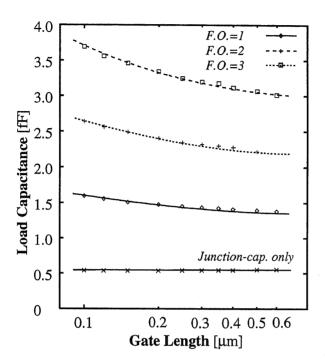

| 3.9  | Optimum load and junction capacitance for the minimum energy             | 37 |

| 3.10 | The minimum delay time under restricted chip power                       | 39 |

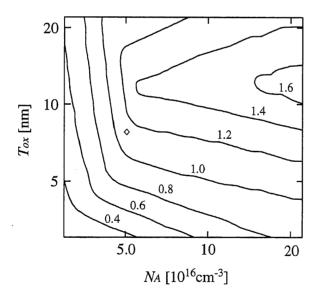

| 3.11 | The optimum supply voltage for the minimum delay time                    | 39 |

| 3.12 | Optimum device parameters for minimum delay time                         | 40 |

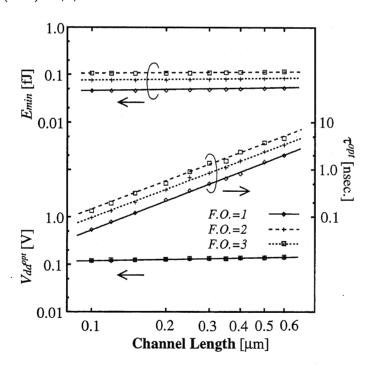

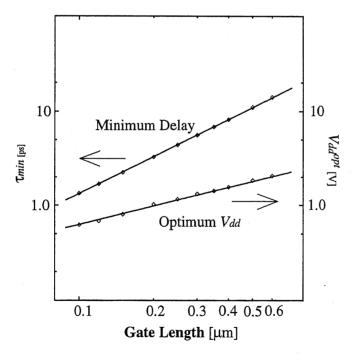

| 3.13 | Dependence of $	au_{min}$ and $V_{dd}^{opt}$ on $L_{eff}$                | 40 |

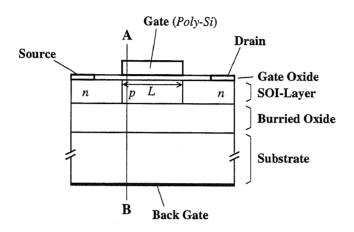

| 4.1  | Schematic cross section of SOI MOSFET                                    | 47 |

| 4.2  | 1-D device simulation of SOI MOSFET                                      | 47 |

| 4.3  | Channel length dependent $I_d$ - $V_{gs}$ characteristics of n-type SOI  |    |

|      | MOSFET by 1- and 2-D device simulation                                   | 51 |

| 4.4  | Substrate bias dependent $I_d$ - $V_{gs}$ characteristics of n-type SOI  |    |

|      | MOSFET by 1- and 2-D device simulation                                   | 51 |

| 4.5  | $V_{th}$ - $V_{bs}$ characteristics of n-type SOI MOSFET by designed     |    |

|      | parameters                                                               | 52 |

| 4.6  | $V_{th}	ext{-}V_{bs}$ characteristics of n-type SOI MOSFET by fitted pa- |    |

|      | rameters                                                                 | 53 |

| 4.7  | Cross sections of mean-square error contours                             | 55 |

| 5.1  | Flow-chart of Quasi-Transient method                                     | 61 |

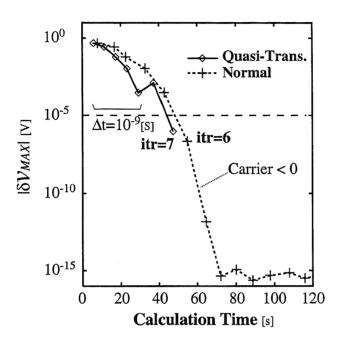

| 5.2  | Comparison of convergence efficiency                                     | 63 |

| 5.3  | $I_d	ext{-}V_{gs}$ characteristics of n-type SOI MOSFET $\dots \dots$    | 64 |

| 5.4  | $I_d	ext{-}V_{gs}$ characteristics of n-type SOI MOSFET $\dots$          | 65 |

| 5.5  | Generation and recombination rate in SOI layer                           | 66 |

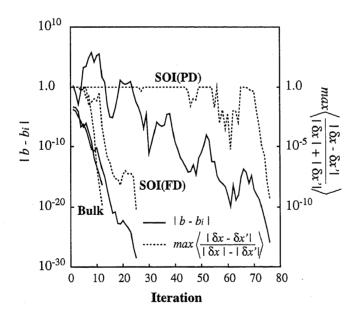

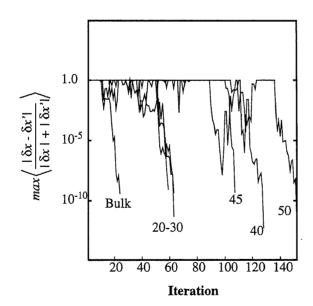

| 5.6  | Convergence efficiency of linear solutions for bulk/FD/PD $$             | 67 |

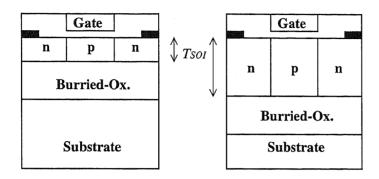

| 5.7  | Simulated structures of SOI MOSFETs                                      | 69 |

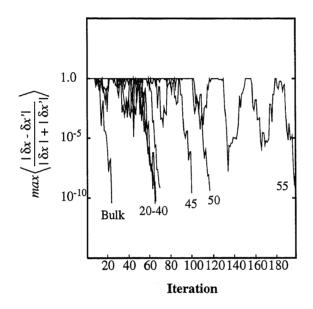

| 5.8  | Convergence efficiency of linear solutions $(V_{qs}=0.0\text{V})$        | 70 |

| 5.9  | Convergence efficiency of linear solutions ( $V_{gs}$ =0.1V)                    | 71  |

|------|---------------------------------------------------------------------------------|-----|

| 5.10 | Convergence efficiency of linear solutions ( $V_{gs}$ = $-0.1$ V)               | 71  |

| 5.11 | Eigenvalue analysis for ILU-preconditioned matrixes                             | 72  |

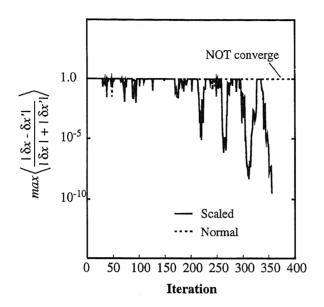

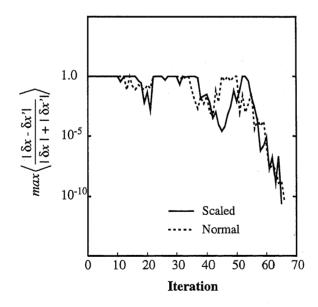

| 5.12 | Normalized carrier scaling method                                               | 73  |

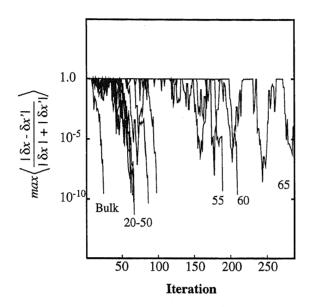

| 5.13 | Convergence efficiency of linear solutions ( $T_{SOI}$ =60nm)                   | 75  |

| 5.14 | Convergence efficiency of linear solutions ( $T_{SOI}$ =25nm)                   | 75  |

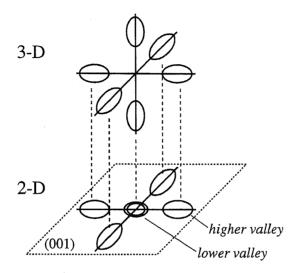

| 6.1  | Schematic valley structure for 3-D and 2-D electron valleys                     | 81  |

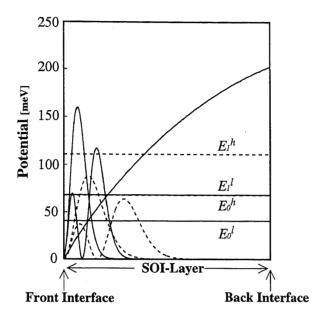

| 6.2  | $2\text{-}\mathrm{D}$ subband diagrams and electron wave functions in SOI layer | 83  |

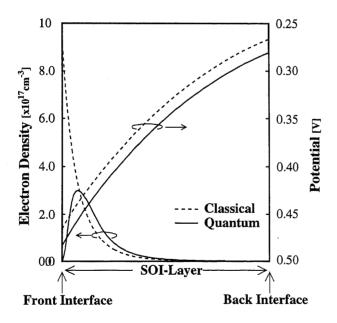

| 6.3  | Simulated potential and electron distribution in SOI layer                      | 83  |

| 6.4  | Inter valley scattering processes                                               | 86  |

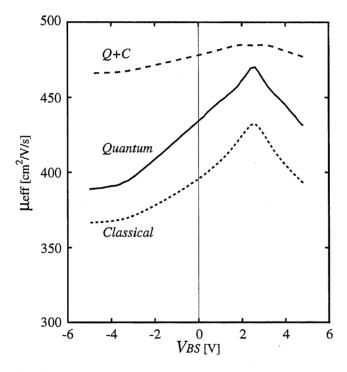

| 6.5  | $\mu_{eff}$ - $V_{BS}$ characteristics of SOI MOSFET                            | 91  |

| 6.6  | $\mu_{eff}$ - $N_I$ characteristics of SOI and bulk MOSFET                      | 93  |

| 6.7  | Electron distribution in channel<br>(SOI) layer                                 | 93  |

| 6.8  | $V_{th}$ - $V_{bs}$ characteristics of n-type SOI MOSFET by QM models           | 94  |

| 6.9  | Difference of estimated device parameters by the electron dis-                  |     |

|      | tribution aspects                                                               | 96  |

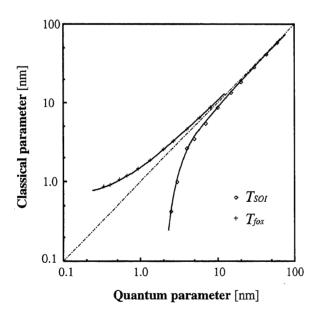

| 6.10 | Fluctuation of $V_{th}$ - $V_{bs}$ characteristics by $T_{fox}$ modulation      | 98  |

| 6.11 | Fluctuation of $V_{th}$ - $V_{bs}$ characteristics by $T_{SOI}$ modulation      | 98  |

| 6.12 | Fluctuation of $V_{th}$ - $V_{bs}$ characteristics by $T_{box}$ modulation      | 99  |

| 6.13 | Fluctuation of $V_{th}$ - $V_{bs}$ characteristics by $N_A$ modulation          | 99  |

| 6.14 | Scaled parameters given to the quantum simulation and clas-                     |     |

|      | sically estimated parameters                                                    | 100 |

| 71   | Complete view of this work                                                      | 108 |

# List of Tables

| 4.1 | Designed and estimated device parameters of SOI MOSFET .        | 54 |

|-----|-----------------------------------------------------------------|----|

| 5.1 | Device parameters used in evaluating QT method                  | 63 |

| 5.2 | Device structure data for evaluating the convergence efficiency | 69 |

| 6.1 | Physical parameters used in Schrödinger equation                | 82 |

| 6.2 | Physical parameters used in intra- and inter-valley phonon      |    |

|     | scattering models                                               | 88 |

| 6.3 | Physical parameters used in surface roughness scattering model  | 89 |

| 6.4 | Estimated device parameters of SOI MOSFET                       | 95 |

## Chapter 1

#### Introduction

#### 1.1 Roles of Computer Simulations in Semiconductor Device Design

In recent years, a VLSI(Very Large Scale Integrated circuit) contains a huge number, even over millions, of circuit elements and the integration scale is continuously growing as well as the integrated devices are continuously shrinking. Now, computer-aided design(CAD) techniques are important and indispensable skills all over the research, development and fabrication stages of such integrated circuits.

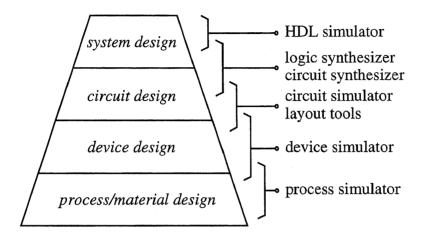

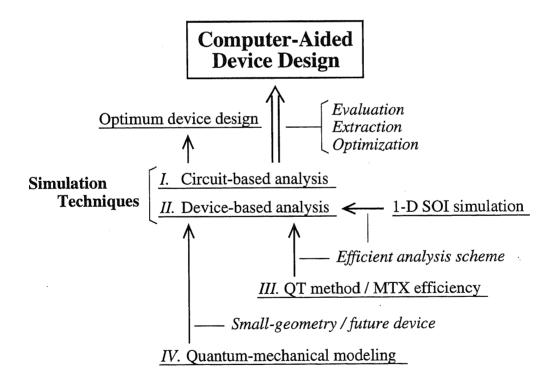

CAD tools used in VLSI development contains many kinds of simulation, synthesis and design tools(fig.1.1). In the lower level, there are process simulator, device simulator and parameter extractor, which mainly concern the fabrication stages of VLSIs. In the higher level, there are high-level synthesizer, circuit synthesizer, logic simulator, circuit simulator and layout tools, which concern the VLSI design stages.

This dissertation concentrates on the circuit and the device simulation techniques, which evaluate performance of circuits and semiconductor de-

Figure 1.1: Computer-Aided Design techniques in VLSI development vices.

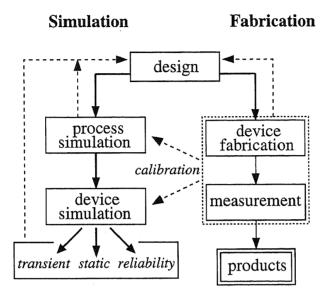

Relations between the simulation and the fabrication stages of VLSI development are illustrated in fig.1.2 on the device simulation case, for example.

In the development flow, the device simulation works as a prediction tool for device characteristics such as static I-V characteristics, transient responses and reliabilities, etc.. Those device characteristics are fed back and examined to improve the device design for desired performance. Simulation tools also concern the real fabrication processes or the real device characteristics, in the calibration processes for the simulation models.

As well as device simulation, circuit simulation predicts the performance of manually or automatically designed circuits and also the characteristics are fed back to the design stage.

From the iterations of the design and the simulation stages, optimized circuit and device designs are obtained and real products of devices and VLSIs are to be fabricated. This is the computer-aided fabrication flow.

Figure 1.2: Simulation and fabrication stages on VLSI development

In this dissertation, optimization schemes in VLSI design are discussed especially in terms of semiconductor device design by optimization of device parameters. The key techniques in device and circuit evaluation with the computer simulations is the device modeling. In the following section, a history of semiconductor device modelings in both analytical and numerical ways are summarized briefly. Then, the goal of this work is presented with the outline of this dissertation in the last section of this chapter.

# 1.2 A Brief History of Analytical and Numerical Modeling of Semiconductor Devices

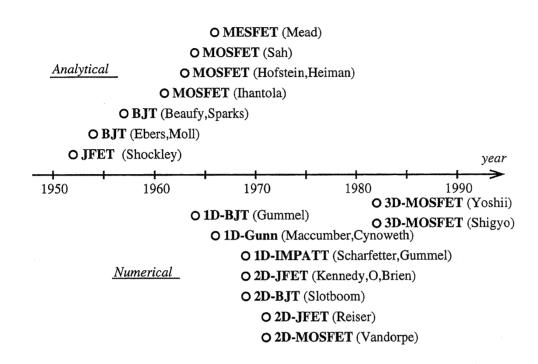

The history of analytical 'compact' modeling of semiconductor devices has begun at the same time as the concept of junction field-effect transis-

Figure 1.3: Early history of analytical and numerical semiconductor modeling tor(JFET) was proposed by Shockley in 1952[1.1].

An analytical model for bipolar junction transistor(BJT) was presented by Ebers and Moll in 1954[1.2]. In 1957, the charge control model of BJT was presented by Beaufy and Sparks[1.3].

Metal-semiconductor field-effect transistor(MESFET) was firstly proposed by Mead in 1966[1.4]. The operation principle of a MESFET was similar to that of a JFET.

Another idea for field-effect controlled semiconductor devices is metal-oxide-semiconductor field-effect transistor(MOSFET), which has very old history down to 1930s. Device characteristics of MOSFETs were studied by Ihantora and Moll[1.5][1.6], Sah[1.7], and Hofstein and Heiman[1.8] in the

early 1960s. Since MOSFETs are suitable for integration in VLSIs, the minimum feature length has been shrunk continuously. Then, the short-channel effects such as the threshold shift or other scaling problems have become the important matters of modelings[1.9] and a lot of works have been proposed for the sake of establishing accurate models for device and circuit analysis.

Circuit simulators have also been investigated and developed to analyze circuit performance with the compact models. The most famous circuit simulation tool is SPICE (Simulation Program with Integrated Circuit Emphasis) which had been developed in University of California, Berkeley in 1973[1.10]. SPICE was evolved into SPICE2 in 1975[1.11], and currently SPICE3 and the improved versions of it are widely used among circuit engineers all over the world.

Numerical methods for semiconductor device modeling have their own history for about 30 years, which are described with fundamental device physics but requires a large amount of computer resources.

The numerical semiconductor device simulation based on the partial differential formulation of the drift-diffusion model was firstly presented in 1964 by Gummel with one-dimensional static analysis of BJT[1.12]. Mac-Cumber and Chynoweth analyzed the Gunn oscillation of GaAs device by one-dimensional transient simulation in 1966 [1.13]. In 1969, Scharfetter and Gummel proposed, in analysis of Read IMPATT diode, a discretization scheme for the continuity equations with physically based expressions, which has been widely made use of in numerical simulation programs [1.14].

A two-dimensional numerical simulation of JFET was presented in 1969 by Kennedy and O'Brien with Poisson equation and one continuity equation [1.15]. BJT was simulated two-dimensionally in 1969 by Slotboom [1.17] with Poisson and both continuity equations. The transient

behavior of JFET was investigated by Reiser in 1971 with two-dimensional simulation [1.16] Also in 1971, two-dimensional simulation of MOSFETwas demonstrated by Vandorpe [1.18].

A lot of investigations have been attempted especially on two-dimensional numerical analysis of MOS devices, because the two-dimensional model has been believed to have enough ability to reproduce the characteristics of those devices.

Activities on three-dimensional numerical simulation have appeared in 1980s with requirement for analyzing three-dimensional effects in small geometry devices, such as the narrow channel effects, for example ref.[1.19] and [1.20]. The dramatic evolution of the computational power was one of the driving force for those activities.

Nowadays, a lot of commercial products for semiconductor device simulation based on three basic equations have been developed and are widely used in design, development and research stages of semiconductor devices.

On the opposite side of the partial differential method of the drift-diffusion model stands the Monte-Carlo method. The Monte-Carlo method has been known as a general mathematical method for solutions of various natural-and social-scientific problems based on random numbers and samplings since the early this century [1.21].

In 1966, Kurosawa has applied the Monte-Carlo method to simulation of the transport of electrons under high electric field[1.22]. Through 1970s and 1980s, many investigations of semiconductor devices with the Monte-Carlo methods have been carried out, for example ref.[1.24],[1.24],[1.23] and [1.26]. However, it was not a popular approach to model semiconductor devices with the Monte-Carlo method because the Monte-Carlo method based simulations require a large amount of computational time.

In the late 1980s, as computers had had a great improvement and as the limits of the drift-diffusion modeling of small geometry semiconductor devices had become frequently mentioned, the Monte-Carlo scheme became an important and an indispensable technique for semiconductor device simulations.

#### 1.3 Outline of This Thesis

The aim of this dissertation is to present the design methodology of small geometry integrated semiconductor devices, especially CMOS devices, for high speed, low power and low energy operation. Analytical and numerical characterization methods are discussed in terms of the optimum design and the estimation of device parameters. As well as the simulation-based characterization methods, simulation methods themselves are investigated for efficient analyses.

In this dissertation, following works are presented and summarized.

In the first part, design methodology of MOSFETs for low power and low energy optima is discussed based on circuit simulation with compact models. In chapter 2, an evaluation method of power and energy consumption of CMOS circuits is presented using circuit simulation of a inverter circuit with physically based analytical models. In chapter 3, device design parameters are optimized to minimize energy consumption during a switching or to minimize the gate delay under restricted chip power.

In chapter 4, a one-dimensional numerical simulation of SOI MOSFETs for modeling the subthreshold characteristics is presented. Using the simulator, real device structural parameters of SOI MOSFETs are estimated by the curve fitting.

In chapter 5, stable and efficient schemes for two- and three-dimensional simulation of SOI MOSFETs are discussed. In the first half, a Quasi-Transient device simulation formulation is presented for stable and efficient SOI simulation. The Single-Transistor Latch(STL) phenomena are successfully reproduced by the method. In the latter half, matrix calculation problems of iterative linear solutions in SOI simulation are investigated and efficiency of a data-dependent scaling criterion is reported.

In chapter 6, quantum-mechanical considerations for thin-film SOI devices are introduced to the one-dimensional simulator presented in chapter 4, with electron mobility models by the relaxation time approximation. The parameter fitting is also demonstrated and necessity of the quantum-mechanical considerations in the analysis of thin-film devices is discussed.

Finally, in chapter 7, the studies on computational analyses for VLSI device design are summarized and discussed for the conclusion of this dissertation.

## **Bibliography**

- [1.1] W.Schockley, "A Unipolar 'Filed-Effect' Transistor," *Proc. IRE*, pp.1365–1377, 1952.

- [1.2] J.J.Ebers and J.L.Moll, "Large-Signal Behavior of Junction Transistors," *Proc. Inst. Radio Engers.*, vol.42, no.12, pp.1761-, Dec. 1954.

- [1.3] R.Beaufy and J.J.Sparks, "The Junction Transistor as a Charge-Controlled Device," *ATE J.*, vol.13, no.4, pp.310–, Apr. 1957.

- [1.4] C.A.Mead, "Schottky Barrier Gate Filed-Effect Transistor," *Proc. IEEE*, no.54, pp.307, 1966.

- [1.5] H.K.J.Ihantola, "Design Theory of a Surface Field-Effect Transistor," Stanford Electron. Lab. Tech. Rep. No. 1661-1, 1961.

- [1.6] H.K.J.Ihantola and J.L.Moll, "Design Theory of a Surface Field-Effect Transistor," *Solid-State Electronics*, vol.7, pp.423–, 1964.

- [1.7] C.T.Sah, "Characteristics of the Metal-Oxide-Semiconductor Field Effect Transistors," *IEEE Trans. Electron Devices*, vol.51, pp.324–, 1964.

- [1.8] S.R.Hofstein and F.P.Heiman, "The Silicon Insulated-Gate Field-Effect Transistor," *Proc. IEEE*, vol.51, pp.1190-, 1963.

- [1.9] S.M.Sze, Physics of Semiconductor Devices 2nd Edition, John Wiley & Sons, Inc., New York, 1984.

- [1.10] L.W.Nagel and D.O.Pederson, "Simulation with Integrated Circuit Emphasis (SPICE)," 16th Midwest Symposium on Circuit Theory, Ontario, Apr. 1973.

- [1.11] L.W.Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," Electronics Research Laboratory Report, no.ERL-M520, University of California, Berkeley, 9 May, 1975.

- [1.12] H.K.Gummel, "A Self-Consistent Iterative Scheme for One-Dimensional Steady State Transistor Calculations," *IEEE Trans. Electron Devices*, vol.20, no.10, pp.455–465, Oct. 1964.

- [1.13] D.E.MacCumber and A.G.Chynoweth, "Theory of Negative-Conductance Amplification and of Gunn Instabilities in 'Two-Valley' Semiconductors," *IEEE Trans. Electron Devices*, vol.13, no.1, pp.4–21, Jan. 1966.

- [1.14] D.L.Scharfetter and H.K.Gummel, "Large-Signal Analysis of a Silicon Read Diode Oscillator," *IEEE Trans. Electron Devices*, vol.16, no.1, Jan. 1969.

- [1.15] D.P.Kennedy and R.R.O'Brien, "Two-Dimensional Mathematical Analysis of a Planar Type Junction Field-Effect Transistor," IBM J. Res. Dev., vo.13, pp.662-674, 1969.

- [1.16] M.Reiser, "Difference Methods for the Solution of the Time-Dependent Semiconductor Flow-Equations," *Electron. Lett.*, vol.7, pp.353–355, 1971.

- [1.17] J.W.Slotboom, "Iterative Scheme for 1- and 2-Dimensional D.C.-Transistor Simulation," *Electron. Lett.*, vol.5, pp.677–678, 1969.

- [1.18] D.Vandorpe and N.H.Xuong, "Mathematical 2-Dimensional Model of Semiconductor Deivces," *Electron. Lett.*, vol.7, pp.47–50, 1971.

- [1.19] A.Yoshii, H.Kitazawa, M.Tomizawa, S.Horiguchi and T.Sudo, "A three-dimensional analysis of semiconductor devices," *IEEE Trans. Electron Devices*, vol.29, no.2, pp.184–189, Feb. 1982.

- [1.20] N.Shigyo, M.Konaka and R.M.L.Dang, "Three-dimensional Simulation of Inverse Narrow-Channel Effect," *Electron. Lett.*, vol.18, no.6, pp.274–275, June 1982.

- [1.21] C.Jacoboni and P.Lugli, The Monte Carlo Method for Semiconductor Device Simulation, Springer-Verlag, Wien New York, 1989.

- [1.22] K.Kurosawa, "Monte Carlo Calculation of Hot Electron Problems," J. Phys. Soc. of Japan, vol.21, pp.424-426, 1966.

- [1.23] P.J.Price, "Monte Carlo Calculation of Hot Electron Transport in Solids," Semiconductor and Semimetals, vol.14, pp.249–334, 1979.

- [1.24] R. A. Warriner, "Computer Simulation of Negative-Resistance Oscillators using Monte Carlo Methods of Gallium Arsenide," *Solid-State Electron Devices*, vol.1, no.4, pp.97–104, Apr. 1977.

- [1.25] R.A.Warriner, "Computer Simulation of Gallium Arsenide Field-Effect Transistors using Monte Carlo Methods," Solid-State Electron Devices, vol.1, no.4, pp.105–110, Apr. 1977.

[1.26] C.Jacoboni and L.Reggiani, "The Monte Carlo Method for the Solution of Charge Transport in Semiconductors with Application to Convalent Material," Rev. of Mod. Phys., vol.55, pp.645–705, 1983.

## Chapter 2

# Evaluation of Power Consumption of CMOS Circuits with Physics-based Models

#### 2.1 Introduction

In recent years, more and more MOSFETs and other circuit elements are integrated in a VLSI. A large number of circuit elements with high density integration cause large power consumption with thermal problems. They are especially noticeable in portable equipments with battery operations, such as PCS(Personal Communication System) terminals or note-book type PCs(Personal Computers), which have rapidly grown in number in this couple of years.

Many researches have been reported aiming to reduce power consumption of VLSIs, proposing new circuit designing methodology, evolving device and process technologies or optimizing signal/supply voltages.

In this chapter, we take a inverter circuit for an example and give a

generalized formulation of power consumption from simulated characteristics of the circuit with physically based device models.

From the simulation results, the supply voltage optima can be found from the view points of the switching energy minimization or the speed maximization under restricted power. These methods are applicable for device/process design of CMOS VLSIs considering the circuit characteristics.

# 2.2 Formulation of Power Consumption in CMOS Circuits

#### 2.2.1 Power consumption in CMOS circuits

The power consumed in a CMOS circuit is composed of two parts, the dynamic power due to the load capacitance's charging/discharging and the static power due to the leak current of stand-by devices.

It is often mentioned that especially in a CMOS logic circuit the dominant part of the consumed power is the dynamic power, because the leak current of MOSFETs is extremely small when threshold voltages of MOSFETs are sufficiently low comparing with the supply voltage of the circuit.

However, in the recent trend of low supply voltage application for power saving, it is impossible to keep enough margin between the threshold voltage and the supply voltage. The decrease of the supply voltage also causes decrease of the active current, which results increase of the gate delay of a CMOS circuit.

As the result, the contribution of the static power to the whole power consumption is relatively increased in low-voltage circuits and it isn't always effective to reduce the supply voltage for saving the circuit power.

#### 2.2.2 Dynamic power consumption

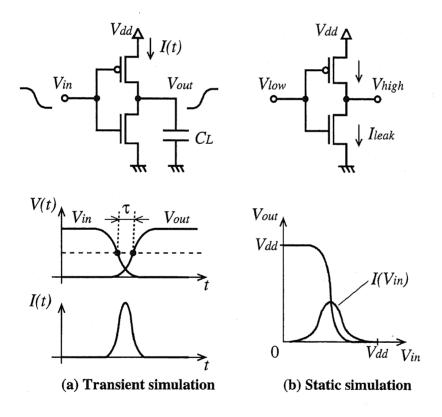

To evaluate the dynamic power consumption, a transient simulation of switching of a CMOS inverter circuit is carried out(fig.2.1(a)). From the simulation, the supplyed current of the inverter are obtained as a function of time, I(t), along with the gate delay time,  $\tau$ .

The dynamic power,  $P_{dyn}$ , is formulated as eq.(2.1), which is the product of effective frequency of the circuit switching,  $\tilde{f}$ , and switching energy,  $E_{sw}$ .

$$P_{dyn} = \tilde{f} \cdot E_{sw} \tag{2.1}$$

For the effective frequency, we assume that the mean time between switch-

Figure 2.1: Inverter characterization by circuit simulation

ings is determined with the delay time,  $\tau$ . Then, supposing  $N_f$  is a constant which represents the gate activity,  $\tilde{f}$  is formulated as eq.(2.2).

$$\tilde{f} = (N_f \cdot \tau)^{-1} \tag{2.2}$$

The switching energy is derived from the supplyed voltage,  $V_{dd}$ , and the supplyed current during a switching, I(t), as eq.(2.3).

$$E_{sw} = \int_0^T I(t) \cdot V_{dd} dt \tag{2.3}$$

Here, T denotes the period when the switching completes.

#### 2.2.3 Static power consumption

To evaluate the static power consumption, a DC static circuit simulation is carried out and  $V_{out}$ - $V_{in}$  characteristics are obtained. Among the characteristics, the input voltage,  $V_{in}$ , whose output voltage,  $V_{out}$ , is equal to  $V_{dd}$ - $V_{in}$  is looked for. Then the leak current,  $I_{leak}$ , is given as the supplyed current at this input voltage.

The static power,  $P_{stat}$ , is formulated in proportional to the supply voltage and the leak current as eq.(2.4).

$$P_{stat} = I_{leak} \cdot V_{dd} \tag{2.4}$$

#### 2.2.4 Total power and energy consumption

The total power consumption of a CMOS inverter circuit,  $P_{total}$  is formulated as the sum of eq.(2.1) and eq.(2.4).

$$P_{total} = P_{dyn} + P_{stat}$$

$$= \tilde{f} \cdot E_{sw} + I_{leak} \cdot V_{dd}$$

(2.5)

As the same way, the total energy per switching is formulated as follows.

$$E_{total} = \frac{P_{total}}{\tilde{f}}$$

$$= E_{sw} + (N_f \cdot \tau)I_{leak} \cdot V_{dd}$$

(2.6)

#### 2.3 Circuit Element Modeling

#### 2.3.1 Requirement of physics-based accurate models

For the accurate device modeling down to sub-threshold gate voltage, we adopt Dunlop's model[2.1] for the MOSFET model in this study, which keeps the continuity of derivatives of the drain current in any region of gate/drain terminal voltage. The fact that the model is described simply with device structural parameters and has few fitting parameters is also favorable for our analysis.

The MOSFET model has a single-drain structure and a uniform channel doping profile as shown in fig.2.2.

The load capacitance,  $C_L$ , is also modeled with the device structural parameters with simple assumptions of the gate and drain shape.

Figure 2.2: Schematic of MOSFET

#### 2.3.2 Drain current modeling of MOSFET

#### Subthreshold current

The subthreshold drain current is modeled as eq.(2.7) with following equations.

$$I_{d}^{\text{Sub}} = \frac{q\mu_{0}W_{eff}}{L_{eff}} \cdot \frac{n_{i}L_{Bi}}{\sqrt{2}\beta} \cdot \frac{e^{\beta(b'-1)\phi_{F}} - 1}{\sqrt{\beta(\phi_{F} - V_{bs}) - 1}}$$

$$\times e^{-\beta\phi_{F}/2} \cdot (1 - e^{-\beta V_{ds}}) \qquad (2.7)$$

$$b' = b - (1/\beta\phi_{F}) \cdot \ln(e^{\beta(b-2)\phi_{F}} + 1)$$

$$b \cdot \phi_{F} = (V_{gs} - V_{FB}) + (F \cdot \gamma)^{2}$$

$$-F\gamma\sqrt{(V_{gs} - V_{FB}) - V_{bs} + \frac{(F\gamma)^{2}}{4}} \qquad (2.9)$$

Here, the parameters presented in above equations are given as follows.

$$eta^{-1} = rac{kT}{q}$$

thermal voltage  $L_{Bi} = \sqrt{rac{arepsilon_{si}}{eta q n_i}}$  (intrinsic Debey-length)  $\phi_F = rac{kT}{q} \ln rac{N_A}{n_i}$  (Fermi potential)  $\gamma = rac{\sqrt{2qarepsilon_{si}N_A}}{C_{ox}}$  (body effect coefficient[2.3])  $C_{ox} = rac{arepsilon_{ox}}{T_{ox}}$  (gate-oxide capacitance per unit area)

The flat-band voltage,  $V_{FB}$ , is formulated as follows, assuming the n-type polysilicon gates for nMOSFETs.

$$V_{FB} = -0.56 + \frac{kT}{q} \ln \frac{n_i}{N_A} \tag{2.10}$$

The short-channel effect, F[2.4], will be described later.

#### Linear region

The drain current in the linear region is modeled as follows;

$$I_d^{\text{lin}} = \mu C_{ox} \frac{W_{eff}}{L_{eff}} \{ (V_{gs} - V_{on}) V_{ds} - \frac{aV_{ds}^2}{2} \}$$

(2.11)

Here, body-effect coefficiency, a, is assumed 1.0.  $V_{on}$  is defined as eq.(2.12) and is equivalent to  $V_{th}$  when  $b'=2(b \geq 2: \text{strong inversion})$ .

$$V_{on} = b'\phi_F + V_{FB} + \gamma F \sqrt{b'\phi_F - V_{bs}}$$

$$(2.12)$$

This formulation is applicable when  $V_{ds} \leq V_{gs} - V_{on} (\equiv V_p)$ .

#### Saturation region

The drain current in the saturation region  $(V_{ds} \geq V_p)$  is modeled as follows.

$$I_d^{\text{sat}} = \mu C_{ox} \frac{W_{eff}}{L_{eff}} \{ (V_{gs} - V_{on}) V_p - \frac{aV_p^2}{2} \}$$

(2.13)

#### Short-channel effects

To model the short channel effects, we consider the charge sharing model [2.4] in the channel depletion layer(fig,2.3). Then, the short-channel coefficient,

Figure 2.3: Charge sharing model

F, is formulated with following equations.

$$F = 1 - \frac{1}{2} \{ F(X_S) + F(X_D) \}$$

(2.14)

$$F(X_S) = \frac{X_j}{L} \left\{ 1 + \frac{2}{X_j} \left[ \frac{2\varepsilon_{si}(2\phi_F - V_{bs})}{qN_A} \right]^{\frac{1}{2}} \right\}^{\frac{1}{2}} - 1 \right\}$$

(2.15)

$$F(X_D) = \frac{X_j}{L} \left\{ 1 + \frac{2}{X_j} \left[ \frac{2\varepsilon_{si}(2\phi_F - V_{bs} + V_{ds})}{qN_A} \right]^{\frac{1}{2}} \right\}^{\frac{1}{2}} - 1 \right\}$$

(2.16)

#### Total current expression

The total drain current,  $I_d$ , is expressed as the sum of the subthreshold current and the 'on'-current for the linear or the saturation region. An example of  $I_d$ - $V_{gs}$  characteristics of an n-type MOSFET is shown in fig.2.4.

Figure 2.4:  $I_d$ - $V_{gs}$  characteristics of nMOSFET  $(L_{eff}{=}W_{eff}{=}1.0\mu\text{m},\ N_A{=}1.6\times10^{16}\text{cm}^{-3},\ T_{ox}{=}50\text{nm},\ V_{ds}{=}0.1\text{V},\ V_{bs}{=}0.0\text{V})$

#### 2.3.3 Load capacitance model

To model the load capacitance, we take into account the intrinsic gate capacitance and drain junction capacitance. The gate fringe capacitance and the metal wire capacitance are neglected simply because these are deeply dependent on the process technologies.

The intrinsic gate capacitance is formulated as eq.(2.17), assuming  $F_o$  is the effective fan-out number.

$$C_{inv} = C_{ox} \cdot W_{eff} \cdot L_{eff} \times 2 \times F_o \tag{2.17}$$

For the junction capacitance, we estimate difference of the maximum and the minimum thickness of depletion layer from the supplyed voltage and the spatial charge in the intermediate region,  $\Delta Q$ , with eq.(2.18)(fig.2.5).

$$\Delta Q = qN_A W_D [L_D (W_{max} - W_{min}) + \frac{\pi}{4} \{ (W_{max} + X_j)^2 - (W_{min} + X_j)^2 \}^{\frac{1}{2}} ]$$

(2.18)

$$W_{min} = \left[\frac{2\varepsilon_{si}(2\phi_F - V_{bs})}{qN_A}\right]^{\frac{1}{2}} \tag{2.19}$$

$$W_{max} = \left[\frac{2\varepsilon_{si}(2\phi_F - V_{bs} + V_{dd})}{qN_A}\right]^{\frac{1}{2}}$$

(2.20)

Figure 2.5: Junction capacitance modeling

In eq.(2.18), the first term of right hand is for the plate capacitance below the drain diffusion and the second term is for the rounded capacitance at the edge of the drain-channel junction.

Then the junction capacitance is formulated as follows.

$$C_{junc} = \frac{\Delta Q}{V_{dd}} \tag{2.21}$$

#### 2.4 Calculation Results

#### 2.4.1 Basic characteristics of a CMOS inverter circuit

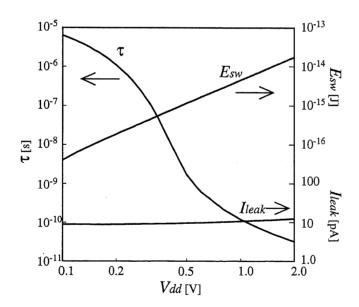

Examples of simulated basic characteristics of a inverter circuit, the switching energy,  $E_{sw}$ , the delay time,  $\tau$ , and the static leak current,  $I_{leak}$ , are shown

Figure 2.6: Basic characteristics of CMOS inverter circuit ( $L_{eff}=0.7\mu\mathrm{m},W_{eff}=1.0\mu\mathrm{m},\,N_A=4.0\times10^{16}\mathrm{cm}^{-3},\,T_{ox}=16\mathrm{nm})$

in fig.2.6, for the functions of the supply voltage,  $V_{dd}$ . In this analysis, the junction depth,  $X_j$ , is fixed to  $0.1[\mu m]$ .

The threshold voltage of the device is estimated to 0.28[V]. The switching energy,  $E_{sw}$ , increases in proportional to the square of the supply voltage,  $V_{dd}$ . The leak current,  $I_{leak}$ , shows slight increase with  $V_{dd}$  increase. The delay time,  $\tau$ , increases dramatically with  $V_{dd}$  decrease. When  $V_{dd} < 0.5[V]$ ,  $\tau$  is inversely proportional to the logarithm of  $V_{dd}$ , while the logarithm of  $\tau$  is inversely proportional to the logarithm of  $V_{dd}$  when  $V_{dd} > 0.5[V]$ .

#### 2.4.2 Evaluation of consumed energy per switching

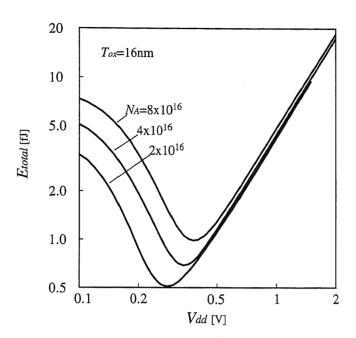

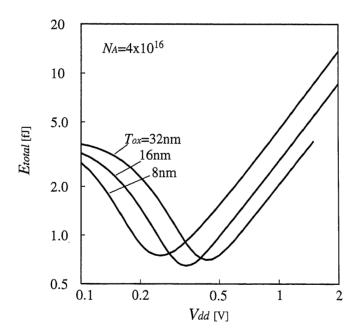

Figure 2.7 shows the characteristics of the total energy consumption per switching,  $E_{total}$ , for three cases of the channel dopant density,  $N_A$ .  $E_{total}$  decreases as  $V_{dd}$  decreases for higher supply voltage than 0.5[V], and turns to increase for lower supply voltage due to the fact that the leak current becomes dominant compared to the switching energy. The minimum switching energy is realized at a supply voltage ranging from 0.2[V] to 0.5[V] depending on  $N_A$ . In this analysis, the constant for the effective frequency,  $N_f$ , is set to 1000.

Figure 2.8 shows the characteristics of  $E_{total}$  for three cases of the gate oxide thickness,  $T_{ox}$ . As same as the  $N_A$  cases, the minimum switching energy is also realized at a supply voltage for each device.

Figure 2.7: Total switching energy of inverter circuit,  $N_A$  as parameter  $(L_{eff}=0.7\mu{\rm m},W_{eff}=1.0\mu{\rm m})$

Figure 2.8: Total switching energy of inverter circuit,  $T_{ox}$  as parameter  $(L_{eff}=0.7\mu{\rm m},W_{eff}=1.0\mu{\rm m})$

#### 2.5 Conclusion

In this chapter, following works were presented.

- 1. Evaluation methods for the energy consumption per switching and the power consumption of CMOS circuits were presented using circuit simulation with physically based analytical models.

- 2. As shown in sample results of a CMOS inverter circuit, existence of the optimum supply voltage for the energy consumption minima was proved.

- 3. From the results of devices with different design parameters, it was proved that the minimum switching energy and the optimum supply voltage are determined depending on device parameters

# **Bibliography**

- [2.1] L.Dunlop, "An Efficient MOSFET Current Model for Analog Circuit Simulation — Subthreshold to Strong Inversion," *IEEE J. Solid-State Circuits*, vol. 25, no.2, pp.616–619, Apr. 1990.

- [2.2] H.C.Chow, W.S.Feng and J.B.Kuo, "An Improved Analytical Short-Channel MOSFET Model Valid in All Regions of Operation for Analog/Digital Circuit Simulation," *IEEE Trans. Electron Devices*, vol.11, no.12, pp.1522–1528, Dec. 1992.

- [2.3] V.Altschul and Y.S.Diamand, "Modeling of the MOSFET Inversion Charge and Drain Current in Moderate Inversion," *IEEE Trans. Electron Devices*, vol.37, no.8, pp.1909–1915, Aug. 1990.

- [2.4] T.Yamaguchi and S.Morimoto, "Analytical Model and Characterization of Small Geometry MOSFET's," *IEEE Trans. Electron Devices*, vol.30, no.6, pp.559–566, June, 1983.

- [2.5] B.J.Sheu, D.L.Sharfetter, P.K.Ko and M.C.Jeng, "BSIM: Berkley Short-Channel IGFET Model for MOS Transistors," *IEEE J. Solid-State Circuits*, vol.22, no.4, pp.558–565, Aug. 1987.

## Chapter 3

# Device Parameter Optimization for Low Power VLSIs using Circuit Simulation

#### 3.1 Introduction

As described in chapter 2, circuit performance deeply depends on the device parameters and the supply voltage of the circuit. Namely, optimizing the device parameters and the supply voltage is one way to realize well designed circuits.

In this chapter, we demonstrate an optimization scheme of MOSFETs with the energy and power consumption evaluation method using CMOS inverter simulation presented in chapter 2.

The device parameters are optimized in terms of the absolute minimum switching energy or the minimal delay time under a constraint of the maximum circuit power. Those criteria are useful in design of portable equipments which require less speed but longer operation time.

The parameters to be optimized are the channel dopant density,  $N_A$ ,

and the gate oxide thickness,  $T_{ox}$ , along with the optimization of the supply voltage,  $V_{dd}$ .

### 3.2 Circuit Optimization Criteria

#### 3.2.1 Switching energy optimization

The evaluation factor firstly introduced is the total energy per switching,  $E_{total}$ , described as eq.(2.6).

This criterion will be useful for absolute reduction of the operating power where battery lifetime is of the first importance.

With recent VLSI technologies, the requirement for high-speed operation of VLSIs is not as the matter as the requirement for long term operation, especially in portable machineries. Further more, low-speed circuits can be accelerated by the parallel operations. Then, it can be concluded that the most concerning factor for the low power operation of VLSIs is the total energy consumption per switching of each circuit element.

# 3.2.2 Power consumption and circuit speed optimization

The other evaluation factor is the power consumption which is formulated as eq.(2.5).

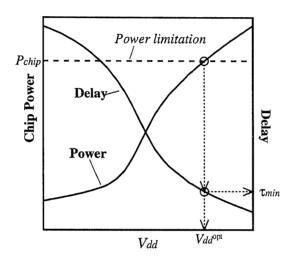

This evaluation is important in such case that chip power is a key factor to determine the package cost.

When the maximally acceptable power consumption per chip,  $P_{chip}$ , is given from thermal problems or battery limits, there is a maximally supplyable voltage,  $V_{dd}^{opt}$  and in most case it gives the minimum delay time of the circuit,  $\tau_{min}$  (fig.3.1).

This restriction for the power consumption of a inverter circuit,  $P_{total}$ , is described as:

$$P_{total} \leq \frac{P_{chip}}{N_{inv}} \tag{3.1}$$

Here,  $N_{inv}$  is the effective number of CMOS logic gates in a chip, assuming all gates are inverters.

Figure 3.1: Circuit speed limitation with power restriction

### 3.3 Restrictions for Device Parameter Ranges

Device parameters have the maximum and the minimum limitations of values determined by several physical factors[3.1].

In this study, we take into consideration the limitations from the bulk punch-through phenomena and the drain-induced barrier lowering and the avalanche breakdown at the drain junction. The device parameters and the supply voltage are ranged in the accepted region.

# 3.3.1 Limitations from bulk punch-through phenomena

In short-channel MOSFETs, the depleted region of the drain junction and the source junction are grown by the drain and the substrate bias and often touch each other in the substrate and current flows through the depleted region, even if the channel does not induced at the oxide interface. This is the bulk punch-through phenomena.

The device parameter limitations from the bulk punch-through is formulated as follows with a model shown in fig.3.2[3.2].

$$L > \left[ (X_j + W_S)^2 - W_C^2 \right]^{\frac{1}{2}} + \left[ (X_j + W_D)^2 - W_C^2 \right]^{\frac{1}{2}} - 2X_j$$

(3.2)

Figure 3.2: Bulk punch-through

Here,  $W_C$  is the depth where the punch-through occurs and it is obtained from the solutions of eq.(3.3).  $W_S$  and  $W_D$  are equivalent to  $W_{min}$  and  $W_{max}$ (eq.2.19 and 2.20) in chapter 2, respectively.

$$\begin{cases}

W_C = \left[\frac{2\varepsilon_{si}(2\phi_S - V_{BS})}{qN_A}\right]^{\frac{1}{2}} \\

V_{GS} = V_{FB} + \phi_S + \frac{qN_AW_C}{C_{ox}}

\end{cases}$$

(3.3)

#### Limitations from drain-induced barrier lower-3.3.2 ing

In short-channel MOSFETs, electric field by the drain potential reduces the channel potential and this causes various subthreshold characteristics degenerations. The parameter limitations from this drain-induced barrier lowering(DIBL) effect is modeled as follows in ref.[3.3].

$$L > 0.41 \left[ X_j T_{ox} (W_S + W_D)^2 \right]^{\frac{1}{3}}$$

(3.4)

#### 3.3.3Limitations from avalanche break down

The avalanche break down at the drain junction has two critical regions, the first one is the junction corner and the second is the oxide surface.

The first limitation for the supply voltage from the corner break down is expressed as follows[3.4].

$$V_{BD} = 60 \left(\frac{E_g}{1.1}\right)^{3/2} \left(\frac{N_A}{tens16}\right)^{-3/4} \gamma_{sp}$$

$$\gamma_{sp} = \zeta^2 + 2.14 \zeta^{6/7} - (\zeta^3 + 3\zeta^{13/7})^{2/3}$$

(3.5)

$$\gamma_{sp} = \zeta^2 + 2.14\zeta^{6/7} - (\zeta^3 + 3\zeta^{13/7})^{2/3} \tag{3.6}$$

$$\zeta = \frac{X_j}{W_d} \tag{3.7}$$

Here,  $E_g$  is the bandgap energy of bulk silicon and  $\gamma_{sp}$  represents the the spherical curvature effect at the drain junction corner.

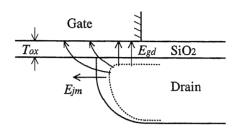

Figure 3.3: Surface avalanche breakdown concerning effective field

The second limitation by the surface break down is expressed as:

$$E_{dx} \leq E_{AV,crit} \tag{3.8}$$

where  $E_{dx}$  is the surface field parallel to the Si-SiO<sub>2</sub> interface at zero gate bias and  $E_{AV,crit}$  (=1.4[MV/cm]) is the critical field for the surface avalanche breakdown[3.5].  $E_{dx}$  is formulated as follows with  $E_{gd}$  and  $E_{jm}$ , which represent the vertical field at the drain-gate overlap region and the maximum lateral field at the drain-substrate junction, respectively[3.6](fig. 3.3).

$$E_{dx} = \frac{2}{\pi} E_{gd} + E_{jm} \tag{3.9}$$

$$E_{gd} = \left[ \left( \frac{qN_D T_{ox}}{\varepsilon_{ox}} \right)^2 + \frac{2qN_D (V_{BD} - V_{FB})}{\varepsilon_{si}} \right]^{1/2} = \frac{qN_D T_{ox}}{\varepsilon_{ox}}$$

(3.10)

$$E_{jm} = \left[\frac{2qN_D(V_{BD} - V_{FB})}{\varepsilon_{si}}\right]^{1/2} \tag{3.11}$$

### 3.4 Device Parameter Optimization

#### 3.4.1 Switching energy optimization

By the first optimization criterion(sec.3.2.1), the devices parameters and the supply voltage are optimized for the minimum total energy per switching,  $E_{total}$ .

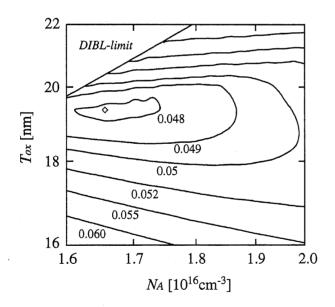

In Fig.3.4, the minimum value of the total switching energy  $E_{total}$  is plotted with contours on the parameter space of  $(N_A, T_{ox})$ . Though the parameter space is limited by DIBL effect[3.1], the absolute minimum energy of a device with  $L_{eff}$ =0.25[ $\mu$ m] and  $W_{eff}$ =1.0[ $\mu$ m] is about 0.048[fJ] at  $N_A = 1.65 \times 10^{16}$ [cm<sup>-3</sup>],  $T_{ox} = 19.4$ [nm] and the delay time of 0.33[ns] for

Figure 3.4: Minimum value of total switching energy [fJ]  $(L_{eff}=0.25\mu m,\ W_{eff}=1.0\mu m)$

the supply voltage of  $V_{dd}$ =0.13[V]. In this analysis,  $N_f$ =100 is assumed.

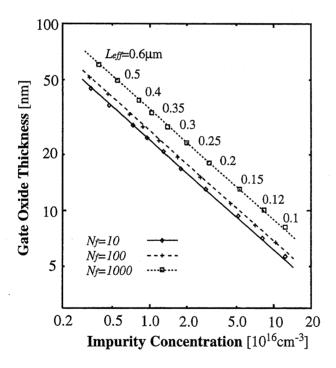

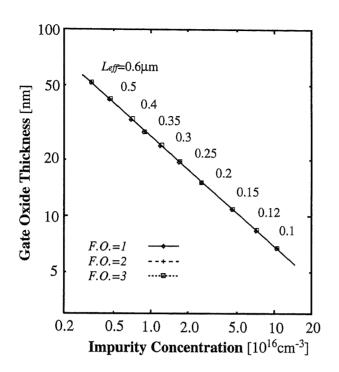

Figure 3.5 shows the channel length,  $L_{eff}$ , dependent optimum device parameters for the minimum energy consumption. As the channel length is scaled down, the optimum gate oxide thickness decreases and the channel dopant density increases. The oxide thickness and the dopant density show the linear relationship in the logarithmic plot.

Figure 3.6 shows the minimum energy,  $E_{min}$ , the optimum supply voltage,  $V_{dd}^{opt}$ , and the delay time,  $\tau^{opt}$ , for various channel length. As the channel length is scaled down,  $\tau^{opt}$  decreases with a linear relation in the log-scale, but  $E_{min}$  and  $V_{dd}^{opt}$  show slight relationships with the channel length. This is because the optimum device with long channel has relatively thick gate

Figure 3.5: Channel length dependent optimum device parameters  $(N_A, T_{ox})$  for the minimum energy consumption

Figure 3.6: Dependence of the minimum energy,  $E_{min}$ , the optimum supply voltage,  $V_{dd}^{opt}$ , and the optimum gate delay,  $\tau^{opt}$  on the channel length

oxide and has small gate capacitance per area, then, the total capacitance is almost at the same order in each device.

The energy minimizing optimum device parameters are shown in fig.3.7 for the fan-out(F.O.)=1,2 and 3. The optimum parameters are almost independent of the fan-out number.

Figure 3.8 shows the fan-out dependence of the minimum energy,  $E_{min}$ , the optimum supply voltage,  $V_{dd}^{opt}$ , and the delay time,  $\tau^{opt}$ .  $V_{dd}^{opt}$  characteristics are also independent of the fan-out number. Thus, all of the device design parameters are optimized uniquely independent of the fan-out. The increase of  $\tau^{opt}$  and  $E_{min}$  are simply explained by the increase of the load capacitance which are caused by increase of the gate capacitance.

Figure 3.7: Channel length dependent optimum device parameters  $(N_A, T_{ox})$  for fan-out(F.O)=1,2, and 3

Figure 3.8: Fan-out dependent minimum energy,  $E_{min}$ , optimum supply voltage,  $V_{dd}^{opt}$ , and optimum gate delay,  $\tau^{opt}$

Figure 3.9: Channel length dependent optimum load capacitance,  $C_L$ , and junction capacitance,  $C_J$ , for the minimum energy (F.O.=1,2,3)

The optimized load capacitance,  $C_L$ , are shown in fig.3.9 for F.O.=1,2 and 3, along with the junction capacitance component,  $C_j$ , which is also included in the load capacitance. The optimum junction capacitance is independent of both the channel length and the fan-out number. The optimum load capacitance increases as the channel length decreases, because even the gate area decreases as the channel length shrinks, the optimum gate oxide thickness,  $T_{ox}$ , also decreases and the gate capacitance which is determined by the gate area and the oxide thickness increases consequently.

# 3.4.2 Delay time minimization under restricted chip power

By the second optimization criterion(sec. 3.2.2), the device parameters and the supply voltage are optimized for the minimum delay time under a restricted chip power.

In fig.3.10, the minimum delay time,  $\tau_{min}$ , is plotted with contours on the parameter space of  $(N_A, T_{ox})$ . The optimum supply voltage is shown in fig.3.11 for the parameters. The absolute minimum delay of a device with  $L_{eff}=0.25\mu\mathrm{m}$  and  $W_{eff}=1.0[\mu\mathrm{m}]$  is about 4.4[ps] at  $N_A=5.0\times10^{16}[\mathrm{cm}^{-3}]$  and  $T_{ox}=7.8[\mathrm{nm}]$  for the supply voltage of  $V_{dd}=1.1[\mathrm{V}]$ . In this analysis,  $N_f=100$ ,  $P_{chip}=10.0[\mathrm{W}]$  and  $N_{inv}=10^6$  are assumed.

In fig.3.12, the channel length,  $L_{eff}$ , dependent optimum device parameters for the minimum delay time are shown. The conditions for the analysis are as same as those described above. Similar to the energy optimum results, as  $L_{eff}$  is scaled down, the optimum gate oxide thickness decreases and the channel dopant density increases. The oxide thickness and the dopant density also show the linear relationship in the logarithmic plot.

Figure 3.13 shows the characteristics of the minimum delay time,  $\tau_{min}$ , and the optimum supply voltage,  $V_{dd}^{opt}$ , on the channel length.  $\tau^{min}$  and  $V_{dd}^{opt}$  decrease as the channel length is scaled down.

Figure 3.10: The minimum delay time ([ps]) under restricted chip power ( $L_{eff}$ =0.25 $\mu$ m,  $W_{eff}$ =1.0 $\mu$ m,  $P_{chip}$ =10.0 $\mu$ W)

Figure 3.11: The optimum supply voltage for the minimum delay time under restricted chip power ( $L_{eff}$ =0.25 $\mu$ m,  $W_{eff}$ =1.0 $\mu$ m,  $P_{chip}$ =10.0 $\mu$ W)

Figure 3.12: Channel length dependent optimum device parameters  $(N_A, T_{ox})$  for the minimum delay time under restricted chip power

Figure 3.13: Dependence of minimum delay time,  $\tau_{min}$ , and optimum supply voltage,  $V_{dd}^{opt}$ , under restricted chip power on the channel length

#### 3.5 Conclusion

Following works were presented in this chapter.

- 1. Two optimization criteria for VLSI device parameters were presented based on the energy and power evaluation method with circuit simulation presented in chapter 2.

- 2. Device parameter optimization for the minimum switching energy was demonstrated with scaling of the channel length.

- The minimum energy per switching was not scaled while the delay time was scaled down as the channel length decreases, in case the device width is not scaled down.

- The optimized device parameters and the supply voltage are independent of the fan-out number of the logic gates.

- The optimized load capacitance increases as the channel length shrinks.

- It can be concluded that the essential merits of the channel length scaling of MOSFET are for the speed and the area advantages, not for the energy and the power advantages.

- 3. Device parameter optimization for the minimum delay under a given maximum power par chip was demonstrated.

- The trends of the optimum device parameters and the supply voltage with the scaling of the channel length were shown.

- The optimum supply voltage is scaled down as the channel length shrinks for the optimized minimum delay.

## **Bibliography**

- [3.1] W.H.Lee, T.Osakama, K.Asada and T.Sugano, "Design Methodology and Size Limitations of Submicron MOSFET's for DRAM Application," *IEEE Trans. Electron Devices*, vol.35, no.11, pp.1876–1884, Nov. 1988.

- [3.2] C.Y.Wu, Z.Hsiao and H.H.Chen, "A Simple Punchthrough Voltage Model for Short-channel MOSFET's with Single Channel Implantation in VLSI," *IEEE Trans. Electron Devices*, vol.32, no.2, pp.178– 179, Feb. 1985.

- [3.3] R.R.Troutman, "VLSI Limitations from Drain-Induced-Barrier-Lowering," IEEE J. Solid-State Circuits, vol.14, no.2, pp.383-391, Apr. 1979.

- [3.4] S.M.Sze, *Physics of Semiconductor Devices* 2nd Edition, John Wiley & Sons, Inc., New York, 1984.

- [3.5] C.Bulucea, A.Rusu and C.Postolache, "Surface breakdown in silicon planer junctions — A computer-aided experimental determination of critical field," Solid-State Electronics, vol.17, pp.881–888, 1974.

[3.6] H.Hara, Y.Okamoto and H,Ohnuma, "Avalanche breakdown voltage of MOS transistors," Trans. IEICE, vol.54-C, no.2, pp.178–179, Feb. 1971.

## Chapter 4

## Device Parameter Estimation of SOI MOSFETs using One-Dimensional Numerical Simulation for Subthreshold Characteristics

#### 4.1 Introduction

Semiconductor devices with SOI(Silicon-On-Insulator) structures were firstly introduced about 30 years ago. On their primitive stage, SOI devices were taken notice of for their capabilities for three-dimensional integrated circuits, their applicabilities for high voltage devices, and their performance of radiation hadness[4.1]. SOI devices were made on relatively thick silicon layers on their first stage.

SOI MOSFETs at that time have been developed in respect to the improved short-channel effects comparing with bulk MOSFETs, by suppressing the bulk-punch through and by reducing the parasitic capacitance and the junction leak. In contrast, SOI devices with thick silicon layers suffered from the particular problems such as the kink-effects with the floating body features of SOI devices.

Fully-depleted SOI MOSFETs, firstly proposed by Malhi[4.2], have very thin silicon layers(thin-film SOI layers) of  $10\sim100[\mathrm{nm}]$  and are almost free from the kink effects. They also show the small parasitic capacitance, which enable fast and low-power circuit operations. But, as for other SOI features, they still have a lot of problems to be solved.

On the other hand, in thin-film SOI devices, the substrate bias has a great influence on the subthreshold characteristics of MOSFETs such as the threshold voltage,  $V_{th}$ , and the subthreshold swing, S. Those characteristics are also affected by the structural device parameters of the SOI multi-layer structure [4.3][4.4][4.5].

In this chapter, we present a one-dimensional Poisson equation based device simulation method for the subthreshold characteristics of SOI MOS-FETs. Since only one-dimensional numerical calculations are needed in this simulator, extremely fast and efficient analyses can be realized.

Using the simulator, estimation of the device parameters of real SOI multi-layer structure is demonstrated by fitting the simulated characteristics with measured data. For the subthreshold characteristics to be fitted, substrate bias,  $V_{bs}$ , dependent threshold voltage,  $V_{th}$ , characteristics are measured on real devices and are also evaluated with the one-dimensional simulator.

# 4.2 One-Dimensional Numerical Simulation of SOI MOSFETs

# 4.2.1 Basic equations for One-dimensional Poisson equation based device simulation

In this section, a one-dimensional (1-D) device simulation method for SOI MOSFET is formulated basing on only the Poisson equation. While conventional two- or three-dimensional device simulators are composed of three basic equations of the Poisson equation and the continuity equations for electrons and holes, our one-dimensional subthreshold simulation needs only Poisson equation in one-dimensional form (eq.4.1) to be solved. The continuity equations of carriers are absent from the numerical model, by assuming the thermal-equilibrium conditions for electrons and holes (eq.4.2).

$$\frac{d}{dx} \left\{ \varepsilon \frac{d}{dx} \psi(x) \right\} = -q \{ N_A - n(x) + p(x) \}$$

(4.1)

$$\begin{cases}

n(x) = n_i \exp\left[\frac{q}{kT}\psi(x)\right] &: \text{in SOI layer} \\

n(x) = n_i \exp\left[\frac{q}{kT}\{\psi(x) - V_{bs}\}\right] &: \text{in substrate} \\

p(x) = n_i^2/n(x)

\end{cases}$$

(4.2)

Here,  $N_A$  is the ionized impurity density in the SOI layer or in the substrate, and  $n_i$  is the intrinsic carrier density in bulk silicon.

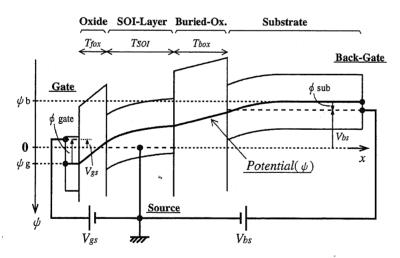

The SOI multi-layer structure is modeled as fig.4.2, as the vertical cross section of an SOI MOSFET (A—B in fig.4.1). The finite differential method[4.6] is applied to solving the Poisson equation to obtain potential distribution,  $\psi(x)$ . The carrier density, n(x) and p(x), are calculated by eq.(4.2). The Poisson equation and the carrier equations are solved alterna-

Figure 4.1: Schematic cross section of SOI MOSFET

Figure 4.2: 1-D device simulation of SOI MOSFET with front/back bias conditions (cross-section A—B in fig.4.1)

tively until revisions of the potential distribution are sufficiently small, and then, the self-consistent solution is obtained.

Boundary conditions for the simulation are given as bias voltages for the gate(front-gate),  $V_{gs}$ , and for the substrate(back-gate),  $V_{bs}$ , as follows.

$$\begin{cases}

\psi_{g} = V_{gs} - \phi_{gate} \\

\psi_{b} = V_{bs} - \phi_{sub}

\end{cases}$$

(4.3)

Here,  $\phi_{\text{gate}}$  is the work-function difference of silicon and n-type-doped polysilicon.  $\phi_{\text{sub}}$  is shift of the Fermi level in the substrate by the ionized impurity, which is formulated as:

$$\phi_{\text{sub}} = \frac{kT}{q} \log \left( \frac{N_{sub}}{N_i} \right) \tag{4.4}$$

assuming  $N_{sub}$  is the ionized impurity density in the substrate.

#### 4.2.2 Drain current modeling

From the potential and the carrier distributions in the SOI layer, the drain current,  $I_d$ , is calculated as eq.(4.5), which is composed of only the diffusion current term. The drift current term is not taken into account because the major conduction mechanism is the carrier diffusion in the subthreshold region of MOSFET operations[3.4].

$$I_d = \frac{qW}{L} \int_0^{T_{SOI}} D(x) \{ n_s(x) - n_d(x) \} dx \tag{4.5}$$

Here, D(x) is the electron diffusibility and  $n_s(x)$  and  $n_d(x)$  are electron densities at depth of x from the front surface of SOI layer near source and drain, respectively.

In this analysis,  $n_s(x)$  is calculated from the one-dimensional analysis based on the Poisson equation described above. On the other hand,  $n_s(x)$  is assumed to be 0, because the carrier density near the drain is sufficiently

small comparing with that near the source, when the diffusion current is dominant.

The electron diffusibility, D, is proportional to the electron mobility,  $\mu$ , by the Einstein's relationship as:

$$D(x) = \frac{kT}{q} \cdot \mu(x) \tag{4.6}$$

Consequently, the drain current is summarized as following form, where  $n_s(x)$  is replaced with n(x).

$$I_d = \frac{qW}{L} \cdot \frac{kT}{q} \int_0^{T_{SOI}} \mu(x) n(x) dx \tag{4.7}$$

We took into account the scattering effects by the lattice temperature, the ionized impurity [4.7] and the surface roughness [4.8] for the mobility model in this analysis.

Finally, we introduce the effective mobility for describing the relationship between the total carrier number and the drain current. The effective mobility,  $\mu_{eff}$ , is defined as:

$$\mu_{eff} = \frac{1}{N_I} \int_o^{SOI} \mu(x) n(x) dx \tag{4.8}$$

where

$$N_I = \int_0^{SOI} n(x)dx \tag{4.9}$$

Here,  $N_I$  represents the sheet density of the electrons in the SOI layer.

Then, the drain current can be simply described as eq.(4.10) with the effective mobility and the sheet density of electrons.

$$I_d = \frac{qW}{L} \cdot \frac{kT}{q} \cdot \mu_{eff} \cdot N_I \tag{4.10}$$

### 4.3 Evaluation of One-Dimensional Device Simulator and Device Parameter Estimation

#### 4.3.1 Accuracy of one-dimensional device simulator

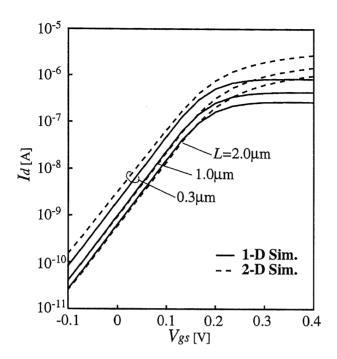

One-dimensional simulation results of  $I_d$ - $V_{gs}$  characteristics of n-type SOI MOSFETs with several channel length are shown in fig.4.3, along with the results by two-dimensional device simulation with the same model parameters.

For rather long-channel devices (1.0 and  $2.0[\mu m]$ ), the one-dimensional results show good agreement with the two-dimensional results in the subthreshold region. They show different results on the  $0.3[\mu m]$  device because of the short-channel effects. In high gate voltage region where the drift current term is the major conduction mechanism, the one- and two-dimensional results show much differences, because of the absence of the drift term from the one-dimensional model.

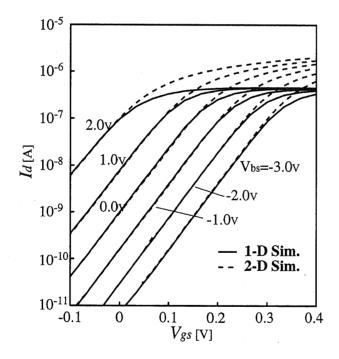

Figure 4.4 shows substrate bias dependence of the subthreshold characteristics by the one- and the two-dimensional simulation for a device of  $L=1.0[\mu\mathrm{m}]$ . They also show good agreement in the subthreshold region.

Calculation time of each curve is about 1 hour for two-dimensional simulations and less than 1 second for one-dimensional simulations.

Figure 4.3: Channel length dependent  $I_d$ - $V_{gs}$  characteristics of n-type SOI MOSFET; solid-line: 1-D, dashed-line: 2-D (W=1.0 $\mu$ m,  $N_A$ =1.5×10<sup>17</sup>cm<sup>-3</sup>)

Figure 4.4: Substrate bias dependent  $I_d$ - $V_{gs}$  characteristics of n-type SOI MOSFET; solid-line: 1-D, dashed-line: 2-D (W=1.0 $\mu$ m,  $N_A$ =1.5×10<sup>17</sup>cm<sup>-3</sup>)

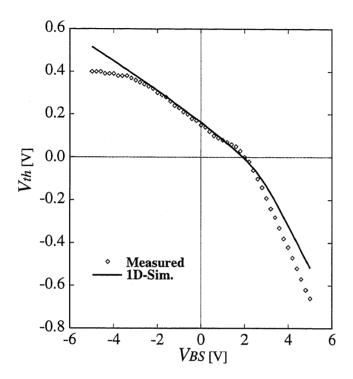

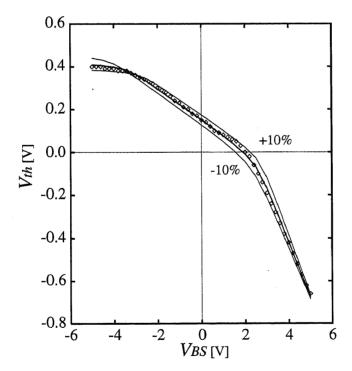

Figure 4.5:  $V_{th}$ - $V_{bs}$  characteristics of n-type SOI MOSFET; points: measured, line: 1-D simulation with 'designed' parameters ( $L=W=100 \mu m$ )

# 4.3.2 Threshold voltage characteristics with substrate bias condition

$V_{th}$ - $V_{bs}$  characteristics were measured for n-type SOI MOSFETs fabricated by SIMOX technology[4.9]. Here, the threshold voltage is defined as the gate voltage where  $I_d$ =10[nA] for the device of L=W=100[ $\mu$ m]

Figure 4.5 shows the measured  $V_{th}$ - $V_{bs}$  characteristics with the simulated characteristics by the one-dimensional subthreshold simulator. In this simulation, the device parameters were given as described in 'designed' column of table 6.4. In these results, the measured and the simulated characteristics show much differences over the whole substrate bias region.

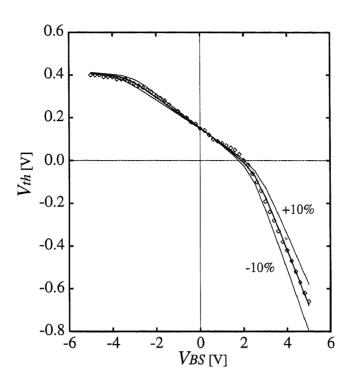

#### 4.3.3 Device parameter estimation

The simulated  $V_{th}$ - $V_{bs}$  characteristics curve was fitted with the measured data by tuning device parameters in the SOI multi-layer structure. The parameters fitted here were the channel dopant density,  $N_A$ , the thickness of gate oxide,  $T_{fox}$ , the thickness of SOI layer,  $T_{SOI}$ , and the thickness of buried oxide,  $T_{box}$ .

The curve fitting was carried out by the steepest descent method in the four-dimensional parameter space evaluating a mean-square error function;

$$\Delta = \sum_{i} \{ V_{th}^{\text{mes}}(V_{bs}^{i}) - V_{th}^{\text{sim}}(V_{bs}^{i}) \}^{2}$$

(4.11)

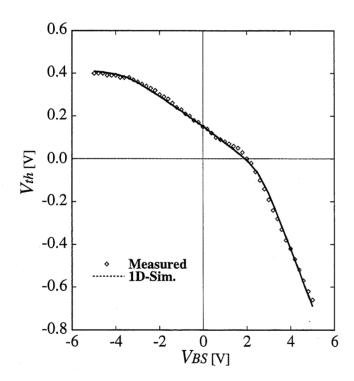

Figure 4.6:  $V_{th}$ - $V_{bs}$  characteristics of n-type SOI MOSFET; points: measured, line: 1-D simulation with 'fitted' parameters ( $L=W=100 \mu m$ )

Table 4.1: Designed and estimated device parameters of SOI MOSFET

|           |                          | designed | fitted |

|-----------|--------------------------|----------|--------|

| $N_A$     | $[10^{17} { m cm}^{-3}]$ |          | 2.36   |

| $T_{fox}$ | [nm]                     | 7        | 6.43   |

| $T_{SOI}$ | [nm]                     | 30       | 41.3   |

| $T_{box}$ | [nm]                     | 80       | 70.7   |

Here, i denotes data index,  $V_{th}^{\text{mes}}$  and  $V_{th}^{\text{sim}}$  are the measured and the simulated threshold voltage at substrate bias,  $V_{bs}^{i}$ , respectively.

Figure 4.6 shows the fitted  $V_{th}$ - $V_{bs}$  curve with the measured data. In table 4.1, designed and fitted device parameters are described.

### 4.4 Property of parameter fitting results

Here, we examine the property of the parameter fitting results with the steepest descent method.

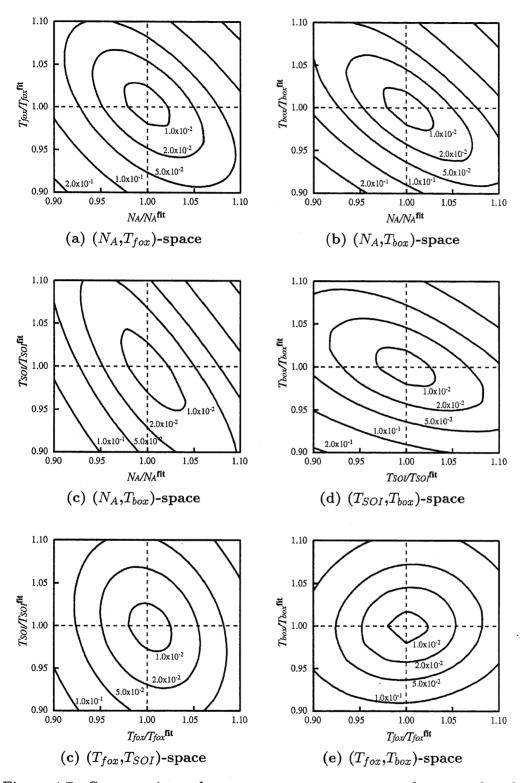

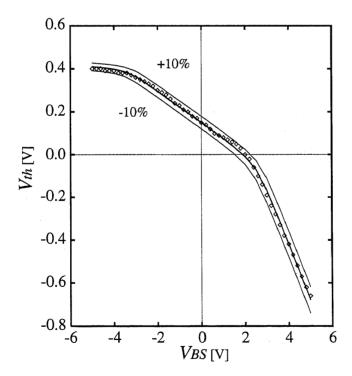

In fig.4.7, the mean-square errors are plotted with contours by twodimensional cross sections of the four dimensional parameter space around the fitted parameter set. They show hyper-ellipsoid like distributions in the four-dimensional space.

To evaluate the efficiency and the property of the fitting results, the Laplacian matrix of mean-square errors around the optimum point is calculated numerically. In this analysis, the square roots of eigenvalues of the matrix represent length of axes of the hyper-ellipsoid. Then, the ratio of the longest axes and the shortest axes represents the sufficiency and the robustness of the steepest descent method.

From the matrix analysis, we had the ratio of 2.9 and it can be concluded that the fitting was carried out successfully.

Figure 4.7: Cross sections of mean-square error contours of measured and simulated  $V_{th}$ - $V_{bs}$  characteristics 55

#### 4.5 Conclusions

Following works were presented in this chapter.

- 1. A one-dimensional numerical simulation method for the subthreshold characteristics of SOI MOSFETs was presented basing on the Poisson equation assuming the thermal-equilibrium conditions.

- 2. One-dimensionally simulated drain current characteristics show good agreement with conventional two-dimensional results in the subthreshold region for long channel devices.

- 3. Efficiency of the one-dimensional simulation was proved by comparing calculation time with the two-dimensional simulation.

- 4. Device parameters of the SOI multi-layer structure were estimated using the one-dimensional simulation by fitting  $V_{th}$ - $V_{bs}$  characteristics with the measured data.

- 5. Property of the curve fitting results by the steepest descent method was proved by eigenvalue analysis of the error function in the parameter space.

## **Bibliography**

- [4.1] S.Cristoloveanu and S.S.Li, *Electrical Characterization of Silicon-On-Insulator Materials and Devices*, Kluwer Academic Publishers, Massachusetts, 1995.

- [4.2] S.D.S.Malhi, H.W.Lam, R.F.Pinizzoto, A.H.Hamdi and F.D.MacDaniel, "Novel SOI CMOS Design Using Ultra Thin Near Intrinsic Substrate," *IEDM Tech. Dig.*, pp.107–110, Dec. 1982.

- [4.3] D.J.Wouters, J.P.Colinge and H.E.Maes, "Subthreshold Slope in Thin-Film SOI MOSFET's," *IEEE Trans. Electron Devices*, vol.17, no.9, pp.2022–2033, Nov. 1990.

- [4.4] K.Tokunaga and J.C.Sturm, "Substrate Bias Dependence of Subthreshold Slopes in Fully Depleted Silicon-on-Insulator MOSFET's," IEEE Trans. Electron Devices, vol.38, no.8, pp.1803–1807, Aug. 1991.

- [4.5] J.P.Colinge, "Subthreshold Slope of Thin-Film SOI MOSFET's," *IEEE Electron Device Letters*, vol.7, no.4, pp.244, Apr. 1986.

- [4.6] H. K. Gummel, "A Self-Consistent Iterative Scheme for One-Dimensional Steady State Transistor Calculations", *IEEE Trans. Electron Devices*, vol 11, no. 10, pp.455–465, Oct. 1964.

- [4.7] N.Arora, J.R.Hauser, D.J.Roulston, "Electron and Hole Mobilities in Silicon as Function of Concentration and Temperature," *IEEE Trans. Electron Devices*, vol.29, no.2, pp.292-295, Feb. 1982.

- [4.8] S.Selberherr, Analysis and Simulation of Semiconductor Devices, Springer-Verlag, Wien, 1984.

- [4.9] K.Izumi, M.Doken and H.Ariyoshi, "C.M.O.S. devices fabricated on buried  $SiO_2$  layers formed by oxygen implantation into silicon," *Electron. Lett.*, vol.14, no.18, pp.593–594, Aug. 1978.

## Chapter 5

## Numerical Methods for Robust and Efficient Two- and Three-Dimensional Device Simulation of SOI MOSFET

#### 5.1 Introduction

Device simulation of SOI MOSFETs has several difficulties originating from their floating body features.

One of the problems is numerical unstability of solutions of carrier densities in the channel region due to the floating body effects, which is unlike conventional MOSFETs. Another problem is physical possibility of multiple solutions even at the same bias condition, which results in the hysteresis characteristics such as Single-Transistor Latch(STL) phenomena[5.8]. For the last of them, we have found that in SOI device simulation the iterative linear solutions show less efficiency than conventional bulk-MOS devices.

In this chapter, robust and efficient device simulation methods for SOI MOSFETs are studied from the numerical points of view.

To improve robustness of SOI simulation, we have developed a Quasi-Transient(QT) method for static(DC) mode analyses, and showed that fast and stable DC analyses are realized in device simulation of SOI MOSFETs. The QT method is suitable for analizing the floating body and the parasitic bipolar effects of thin-film SOI devices, and the STL phenomena of SOI MOSFETs are successfully simulated with the QT method.

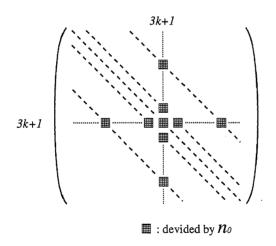

In the latter half of this chapter, convergence efficiency of the iterative linear solution, especially ILU-CGS method, are investigated, along with evaluation of the formed matrices of the semiconductor equations in device simulation of SOI MOSFET. Eigenvalue analysis of the Jacobi matrices are carried out to clarify the differences of matrix characteristics for both SOI and bulk MOSFETs. And then, a data-dependent scaling scheme for efficient solutions of iterative linear solutions are presented and evaluated.

### 5.2 Robust simulation for the hysteresis phenomena of SOI MOSFET's by Quasi-Transient Method

#### 5.2.1 Qusi-Transient device simulation

In conventional semiconductor device simulators three basic semiconductor equations, the Poisson equation(eq.5.1) and the continuity equations for carriers(eq.5.2 and 5.3) are applied.

$$\operatorname{div}(\varepsilon \cdot \operatorname{grad}\psi) = -q(N_D - N_A + p - n) \tag{5.1}$$

$$\frac{\partial n}{\partial t} + \operatorname{div}(\mu_n \cdot n \cdot \operatorname{grad}\psi - D_n \cdot \operatorname{grad}n) = GR$$

(5.2)

$$\frac{\partial p}{\partial t} - \operatorname{div}(\mu_p \cdot p \cdot \operatorname{grad}\psi + D_p \cdot \operatorname{grad}p) = \operatorname{GR}$$

(5.3)

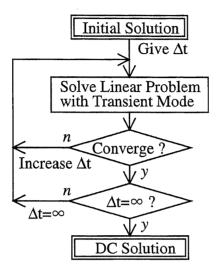

Figure 5.1: Flow-chart of Quasi-Transient method

Here,  $\psi$  is the electron potential and  $\varepsilon$  is the permittivity and  $N_A$  and  $N_D$  are the density of ionized acceptors and donors. n and p are electron and hole density.  $\mu_n$  and  $\mu_p$  are the carrier mobilities and  $D_n$  and  $D_p$  are the carrier diffusivity of electrons and holes, respectively. GR is the carrier generation and recombination rate.

To improve robustness and efficiency of the Newton's iterative calculation in SOI MOSFET device simulation for DC analysis with a numerical approach, we take a notice of the time-concerning 'transient' terms in the continuity equations, which are used only in transient analyses in the conventional formulation in device simulation.

Figure 5.1 shows a generalized flow-chart of the Quasi-Transient device simulation. In the QT simulation, the solution of the former bias condition is used as the initial guess for new bias condition, as is in the conventional method. The Newton's iterative calculation is carried out with the formulation for transient analyses. At this point, the initial guess is also assumed to be the former bias condition of quai-time step,  $\Delta t$ , before. Then,  $\Delta t$  is gradually increased as the iterative loops are processed, and finally, the DC formulae with the condition of  $\Delta t \to \infty$  are calculated, so that we can obtain the same solution as a DC simulation gives.

The advantages of this QT simulation are as follows.