# Progress in the Smart Pixel Technologies

H. Scott Hinton, Senior Member, IEEE

(Invited Paper)

Abstract—The purpose of this paper is to review the recent progress in the developing smart pixel technologies. This paper will begin by reviewing some of the rapidly evolving smart pixel terminology. It will then describe several of the smart pixel technologies that have recently emerged. Finally, it will outline the performance of these technologies in both device complexity and aggregate capacity.

#### I. INTRODUCTION

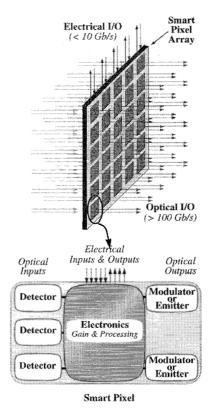

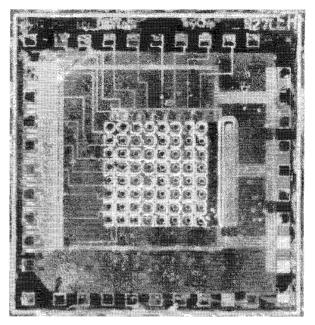

smart pixel is an optoelectronic structure composed of electronic processing circuitry (CMOS, BiCMOS, bipolar, etc.) enhanced with optical inputs and/or outputs [1]. The optical signals entering and/or leaving the smart pixels are typically arranged into two-dimensional (2-D) arrays that can be supported by the free-space optical interconnection of different smart pixel arrays (SPA's). In the simplest case, a SPA is formed by creating a 2-D array of similar smart pixels (uniformly distributed) as shown in Fig. 1.

The input optical signals to these smart pixels are detected by optoelectronic devices such as p-i-n or metal-semiconductor-metal (MSM) photodetectors. These detected signals are then amplified to the required (digital) electrical levels by analog electrical amplifiers [2].

Once the signals have been amplified to the appropriate electrical level they can be processed by the specific electrical circuitry of the smart pixel. The functionality of the smart pixels can range from one or two transistors providing some type of nonlinear gain to a smart pixel composed of several thousand transistors processing an ATM packet header. For this uniformly distributed type of SPA, the electronics in each smart pixel are localized to the area of the smart pixel preventing long, across-chip lines that can lead to reduced electrical performance because of skew, crosstalk, and the special drivers required to drive the longer electrical interconnects

Finally, after the input signals, both optical and electrical, have been processed, they can be directed to the optoelectronic outputs. These can be either sources, such as LED's or VCSEL's, or modulators such as MQW p-i-n diodes.

#### II. SMART PIXEL DEFINITIONS

As the smart pixel technology continues to evolve, there needs to be a basic understanding and acceptance of key performance metrics including connection density, complexity, and aggregate capacity.

Manuscript received June 19, 1996; revised July 15, 1996.

The author is with the Department of Electrical and Computer Engineering, University of Colorado, Boulder, CO 80309–0425 USA.

Publisher Item Identifier S 1077-260X(96)07977-4.

Fig. 1. Smart pixel array.

#### A. Connection Density

Since optical interconnection is the prime advantage of SPA's [3], the number of optical inputs and outputs of a SPA becomes an important parameter. The connection density refers to the number of optical connections per cm² (input + output) supported by a SPA and its associated optical interconnect. As an example, if there are 1000 smart pixels in a 1-cm² SPA and each smart pixel requires two signal inputs and two signal outputs, then the connection density that would need to be supported by the interconnect optics would be 4000 connections/cm². If the signals are differential, then the connection density would need to be 8000 connections/cm².

#### B. Complexity

The second major advantage of SPA's is the intelligence provided through the electronic processing circuitry. It is this intelligence that allows the smart pixels to perform complex operations on the data entering/exiting the SPA. It is this

1077-260X/96\$05.00 © 1996 IEEE

intelligence that separates SPA's from photonic integrated circuits (PIC's) where PIC's refer to monolithically integrated optical and optoelectronic devices (lasers, detectors, optical waveguides, gratings, couplers, etc.) but do not include electronic structures. The complexity of the SPA's will be defined as the average number of transistors per optical I/O. It will be calculated by dividing the total number of transistors in the SPA by the total number of optical I/O.

#### C. Aggregate Capacity

To exploit the connectivity advantage of free-space optics, each SPA should have an aggregate optical throughput or capacity that is much larger than the electrical aggregate capacity. The aggregate optical capacity refers to the sum of all the optical inputs and/or outputs multiplied by their associated bit rates. On the other hand, the aggregate electrical capacity refers to the sum of all the electrical inputs and outputs multiplied by their associated bit rates. As an example, if there are 1000 optical inputs and 1000 optical outputs, each operating at 100 Mb/s, then the aggregate optical capacity is 200 Gb/s.

#### III. SMART PIXEL PARTITIONING

The physical architecture or partitioning of the optical I/Os in SPA's is constrained by the type of optical interconnect employed in the system. There are three basic partitioning approaches, including: 1) uniformly distributed smart pixels, 2) concentrated I/Os, and 3) clustered smart pixels. Each is described below.

## A. Uniformly Distributed

For the case of uniformly distributed smart pixels (Fig. 1), there are two major interconnection methodologies. The first is to use a large, complex, and bulky multi-element imaging system that will support a large field of view to cover the entire SPA and at the same time have a low enough f/# to collect the light emitted from the SPA sources and also image the received input information onto the SPA photodetectors. Despite the tremendous amount of progress in developing these systems, they tend to be both bulky and expensive. Examples of this approach include both AT&T System<sub>4</sub> architecture, which imaged  $32 \times 32$  optical channels between six uniformly distributed SPA chips [4], and System<sub>6</sub>, which provides the interconnection of  $\sim 10\,000$  optical channels on/off a single uniformly distributed SPA [42].

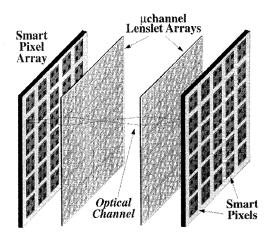

A second approach is to provide each optical input and/or output with its own  $\mu$ channel through the use of lenslet arrays [5] as illustrated in Fig. 2. These lenslet arrays have the potential of being mass produced and inexpensive. In this particular configuration, the separation between the optical I/O is equal to the size of the lenslet arrays. Thus, the total number of optical connections that can be supported by the  $\mu$ channel approach is relatively small. Despite this limitation, this type of optical interconnect could be effective for complex SPA's that require a large area per smart pixel (a large number of transistors per optical I/O).

Fig. 2. Microchannel interconnected SPA's.

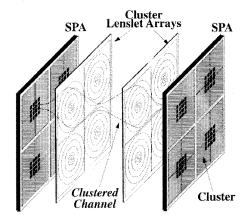

Fig. 3. SPA clustered interconnects.

## B. Centralized I/O

To reduce the field of view required by the interconnection optics, the SPA's can be partitioned such that the optical I/O for all the smart pixels is concentrated together in the center of the SPA. The advantage of this partitioning is that the optical I/O can be tightly packed, thus reducing the field of view of the interconnection optics, which reduces the complexity and cost of the optics. The disadvantage is that the centralization of the optical I/O creates an electrical interconnection bottleneck in routing the electrical signals from the surrounding SPA electronics to the tightly packed optoelectronic I/O devices. This electrical connectivity issue is the same problem faced by large spatial light modulators.

# C. Clustering

Clustering is a combination of both of the previous partitioning methods [6]. In this approach, the optical I/O for a small group of the smart pixels is clustered together as shown in Fig. 3. The size of the cluster is linked to the size of the lenslet that will support each cluster. In this case, the lenslet will support multiple channels instead of the single channel per lenslet supported in the  $\mu$ channel approach. This approach can provide a significant connection density when

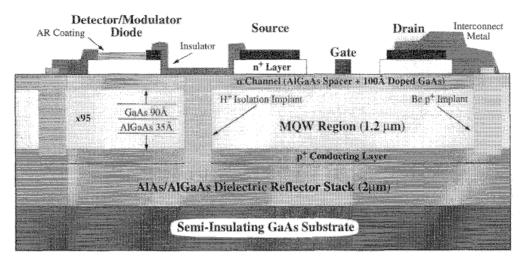

Fig. 4. Cross section of the AT&T FET-SEED technology.

the distance between the SPA's is small [6]. It also builds on the inexpensive lenslet technologies and avoids the use of expensive bulk lenses.

This approach has been recently used in McGill's Phase II Hybrid CMOS-SEED system demonstrator [7].

# IV. SMART PIXEL TECHNOLOGIES

There are several rapidly evolving SPA technologies approaching the point where they can be used in full-scale optoelectronic systems. These SPA technologies can be categorized as either modulator-based or source-based smart pixels. The modulator-based SPA's were the first to be developed and have been included in several demonstration systems. The source-based SPA's are rapidly evolving as the characteristics of VCSEL's are improving. Both of these categories of SPA's will be discussed in the section below.

#### A. Modulator-Based Smart Pixels

The first SPA technologies to be developed were based on the monolithic integration of photodetectors, electronics, and modulators into a single functional device. There are two major advantages of modulator-based SPAs: 1) they are simple devices and should be reliable, manufacturable, and uniform, and 2) the input light (power supply) can be centrally controlled, thus simplifying system synchronization. The major disadvantage is that the required interconnect optics are significantly more difficult. The three major SPA technologies discussed in this section are the FET-SEED Hybrid CMOS-SEED and liquid-crystal-on-silicon technologies.

1) FET-SEED Smart Pixels: The FET-SEED technology was the first smart pixel technology to monolithically integrate: 1) multiple-quantum-well (MQW) reflection modulators [8] based on a GaAs-Al $_x$ Ga $_{1-x}$ As stack, 2) p-i-n photodetectors using the same MQW stack as the modulators, 3) doped-channel MIS-like field effect transistors (DMT), and 4) optional integrated resistors [9]. The cross section of the FET-SEED technology is shown in Fig. 4.

A single molecular-beam epitaxial (MBE) growth sequence is used to provide the DMT channel, the quantum well absorbing region for both the modulators and photodetectors, the doped n- and p-type contact layers, and the dielectric mirrors required by the reflection modulators. Reflection modulators were used to provide both a structure suitable for batch fabrication and to enable heat sinking on the back side of the chip. Heat sinking is necessary in order to insure a stable excitonic absorption wavelength. These basic circuit elements were then stitched together using the buffered FET logic (BFL) to form larger and more complicated functional circuits. As an example of the general functionality of this technology, below is a list of the circuits that were designed at the AT&T/ARPA FET-SEED workshop [10].

- · Time-integrating correlator

- · Transceiver arrays

- Crossbar switch array

- Address decoders

- · Smart spatial light modulator arrays

- · Shift registers

- · Wavelet transformer self-routing switching nodes

- · Serial-to-parallel converters

- Exchange/bypass switching nodes

- Pulse-arithmetic neural network

- · Test circuits

Fig. 5 is a photograph of one of the smart pixels in the  $4 \times 4$  FET-SEED SPA used in the AT&T System<sub>5</sub> photonic switching system demonstrator [11]. Each smart pixel included 24 FET's, 17 diodes, four MQW photodetectors, and four MQW modulators and was able to operate at 400 Mb/s.

The FET-SEED technology has also been employed in demonstration systems at McGill University (16-channel optical backplane) [12], Optivision (16-channel optical interconnect) [13], and the University of Southern California (network application circuits) [14].

2) Hybrid CMOS-SEED Smart Pixels: The Hybrid CMOS-SEED technologies were pursued based on the philosophy that individual optical logic gates will not be able to compete with the existing or future silicon electronics technology platforms

Fig. 5. AT&T System<sub>5</sub> smart pixel.

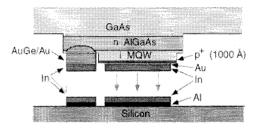

with respect to power consumption, device size, and system complexity. It has also become obvious that silicon electronics is going to continue to increase in both performance and complexity while its cost will continue to decrease. Rather than compete with this rapidly growing technology, the objective of the smart pixel technology is to complement it. Since the added value of optics in the digital electronic domain is interconnection, providing optical inputs and outputs for the existing electronic integrated circuit platforms became the technologies' driving force. The first approach at integrating modulators/photodetectors onto silicon circuits was to put InGaAs modulators on silicon CMOS chips [15]. This use of  $GaAs-Al_xGa_{1-x}As$  modulators/photodetectors on silicon CMOS was then pursued by AT&T [16]. In this process, MQW modulators/photodetectors are grown on GaAs chips such that the n and p contacts are coplanar (see Fig. 6). A Ti-Au pad is then deposited at the location of the optical windows of the MQW modulators/photodetectors to act as a 40% reflector. A lead-tin alloy is then deposited on the electrical contacts of the modulators/photodetectors to be used for the flip-chip bonding between the two substrates. The silicon CMOS chips have been obtained from the MOSIS foundry (both 1.2- $\mu$ m and 0.8- $\mu$ m line rules have been used). The aluminum bonding pads on the CMOS chip are then coated with a thin Ti-Pt-Au to provide a solder-wetable surface for the solder bump bonding later in the process. The two chips are then flip-chip solder-bonded together. Prior to removing the GaAs substrate, a silica-filled epoxy is wicked between the chips to protect both the GaAs and silicon chips. The GaAs substrate is then etched off, leaving only the small MQW modulators/photodetectors in the desired locations on the chip. An antireflection coating is then applied across the chip. A close-up of a CMOS-SEED SPA is shown in Fig. 7. It should be pointed out that this technique is not limited exclusively to silicon CMOS but could be used with other silicon circuit families such as ECL, bipolar, BiCMOS, etc.

As an example of the general functionality of this technology, below is a list of the circuits that were designed at the

Fig. 6. Hybrid CMOS-SEED process.

# AT&T/ARPA Hybrid-SEED Workshop [17].

- · Half-tone imaging

- · Shared memory processor interconnect

- · Multi-access interconnect architecture

- Digital cellular

- · Imaging processor

- Optical A/D converter

- Optical permutation network

- · Programmable logic smart pixel devices

- Crossbar switch

- · Sorting switching nodes

- ATM switching nodes

- ATM-based optical backplane

- Focal plane processor

- Field programmable smart pixel arrays

- High-performance bus interface

- · Linear fringe detector

- FFT nodes

- · Wavelength meter

- Position-tolerant array sensor

- Cellular neural network

- Detector arrays

- Multidimensional interchanger

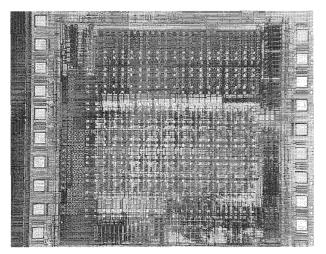

An example of a complete CMOS-SEED SPA is shown in Fig. 8. It is a  $4 \times 9$  SPA for a buffered *HyperPlane* ATM backplane-based switching fabric. It includes  $\sim 60$  transistors per smart pixel with a total of  $\sim 20\,600$  transistors in a 4-mm<sup>2</sup> area. It also includes 144 optical inputs and outputs and can store up to three concurrent ATM cells [18]. This technology has operated at bit rates greater than 1 Gb/s [19].

3) Liquid Crystal on Silicon: Finally, the liquid-crystal-onsilicon (LCOS) smart pixel technology provides optical out-

Fig. 7. Close-up of a CMOS-SEED smart pixel

Fig. 8. Buffered HyperPlaneSPA.

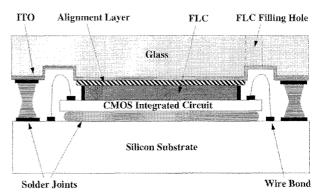

puts for any standardized electronic platform through the use of integrated arrays of liquid-crystal modulators [20]. The majority of this effort has focused on the integration of the high-birefringence and low-voltage operation of ferroelectric liquid-crystal (FLC) modulators on preprocessed silicon CMOS circuits. The cross section of an experimental LCOS device is shown in Fig. 9 [21]. The construction of this device begins with a silicon substrate that provides both the mechanical support for the assembly as well as the general electrical interconnect for the electrical signals entering and leaving the SPA. The silicon CMOS integrated circuit is first solder bonded to the silicon substrate and then the electrical connections between the CMOS chip and the substrate are made using standard wire-bonding techniques. The next step is to mount the SPA cover glass, which is composed of: 1) optically flat glass, 2) ITO coating, 3) FLC alignment layer, 4) mechanical polyimide spacers, 5) solder pads, and 6) a foursided trench with a hole drilled through the front surface. This is accomplished with a solder reflow process that allows the solder joints to self-align and provide the necessary force to

Fig. 9. Liquid-crystal-on-silicon.

maintain the desired spacing for the FLC. An FLC paste is the place in the hole where it will become a liquid when the structure is heated in a vacuum chamber. The liquid FLC will then fill the gap between the cover glass and the silicon CMOS integrated circuit by capillary action.

Although this technology is limited to modulator response times in the microseconds regime, it has found many applications that require massive optical interconnection. Examples include spatial light modulators, displays, and optical neural networks [20].

#### B. Source-Based Smart Pixels

An alternate to the modulator-based SPA's described above is a smart pixel technology based on the use of optical sources for the SPA outputs instead of modulators. The simplest, and most near-term, approach is to bring together, in a hybrid package, an electronic processing platform such as CMOS, an array of optical detectors, an electronic processing platform such as CMOS, and/or an array of optical sources such as VCSEL's. A second approach is to place the optoelectronic components on the electronic platform via thin-film integration techniques. A third approach is to flip-chip bond the detector and VCSEL arrays directly onto the electronic platform. Finally, the fourth approach is to monolithically integrate the detectors, electronics, and sources all onto a single substrate. Each of these approaches is described below.

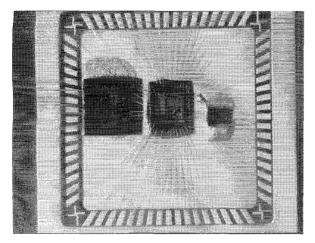

1) Hybrid MSM/VCSEL Smart Pixels: The VCSEL/MSM hybrid technology is based on the hybrid integration of VCSEL's, MSM photodetectors, and a standard electronic integrated circuit platform such as ECL, bipolar, CMOS, BiCMOS, etc. into a common electronic package [22]. An example of this approach is shown in Fig. 10 where a  $4\times4$  VCSEL array, a  $0.8-\mu$ m CMOS chip fabricated through the MOSIS process, and a  $4\times4$  array of MSM detectors were packaged together in the same PGA package [23]. Due to manufacturing costs, this is a short-term solution and will eventually be replaced by one of the other source-based approaches.

2) ELO-Based Smart Pixels: Using a technique referred to as epitaxial lift off (ELO) [24], high-quality, single-crystal thin-film materials and devices can be separated from a lattice-matched growth substrate using selective etching and then aligned and bonded to a host substrate such as preprocessed

Fig. 10. Hybrid MSM/CMOS/VCSEL smart pixel array.

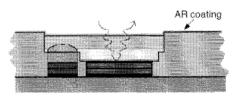

silicon CMOS substrates. The devices to be bonded to the host substrate are removed from the growth substrate through stop-etch layers. These epitaxial thin-film devices are then handled manually using a thick (100  $\mu$ m) wax handling layer. Using this handling layer, the devices are then attached to a transparent transfer diaphragm constructed of either polyimide or mylar and supported by a ring of silicon on the outer edge. The diaphragm is then inverted with the thin-film devices facing the host substrate. The optoelectronic devices are then visually aligned and bonded to the host substrate using a pressure probe [25]. The performance of these devices has been shown to be comparable to that of devices that have not been separated from the growth substrate [26].

This technology has been able to demonstrate the placement of 64 AlGaAs detectors on a single silicon substrate [27] (see Fig. 11), thin-film LED-based transmitters that operate at 155 Mb/s [28] and receivers that operate at 250 Mb/s [29]. It has also become driving SPA technology in a through-wafer systems effort [30], [31]. This technology is not limited to source-based outputs but could also be applied to modulator-based SPA's.

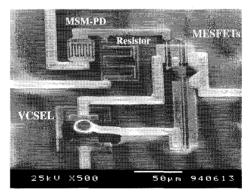

- 3) Monolithic MSM/MESFET/VCSEL Smart Pixels: The GaAs MSM/MESFET/VCSEL smart pixel is based on the monolithic integration of VCSEL's, MSM detectors, and MESFET transistors. This smart pixel technology, pioneered by NTT, uses optical sources instead of modulators as the output device in each smart pixel [32]. Smart pixels based on this technology have demonstrated 3-dB bandwidths of 220 MHz. Fig. 12 is a picture of a simple monolithically integrated MSM/MESFET/VCSEL smart pixel.

- 4) Flip-Chip Bonded VCSEL/MSM Smart Pixels: A natural extension of the Hybrid-SEED technology is to flip-chip bond VCSEL's to an electronic platform instead of modulators.

#### V. SPA PERFORMANCE

Over the past five years, there has been tremendous progress in the development of the smart pixel technology. This section will review the progress in device aggregate capacity, SPA complexity, and the performance of the SPA demonstrators.

Fig. 11. ELO ALGaAs-based p-i-n detectors on silicon neural network circuitry.

Fig. 12. NTT monolithic GaAs MSM/MESFET/VCSEL smart pixel [32].

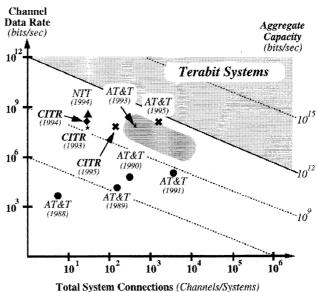

# A. SPA Aggregate Capacity

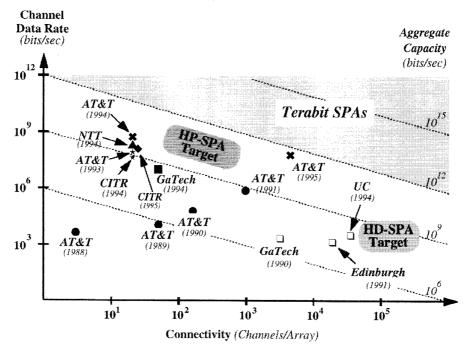

Fig. 13 illustrates the progress in aggregate capacity of single SPA's as a function of connectivity (pin-outs per chip) and per channel data rate (bits per second). The upper right corner of the figure (shaded) is the desired high-performance region supporting greater than a terabit aggregate capacity. The performance of several of the SPA device demonstrators representing the different SPA technologies have been mapped onto the figure. In this figure, the S-SEED devices represent the progress associated with simple optical logic gates. Despite the progress in developing optical logic gates, it became obvious that more speed and intelligence was needed. The first generation of these high-performance SPA's (HP-SPA) were primarily 4 × 4 arrays with bit rates ranging from 10-500 Mb/s. The next generation will be targeting 8 × 8 SPA's (or larger) as the device demonstrators for the 1996-1997 timeframe.

Another class of SPA's, the high-density SPA's (HD-SPA), targeting the high-connection density applications such as

Fig. 13. The smart pixel array connectivity versus the individual optical channel bit rate with the following demonstrated SPAs: 1) AT&T (1988) [33], 2) AT&T (1989) [34], 3) AT&T (1990) [35], 4) AT&T (1991) [36], 5) GaTech (1994) [37], 6) CITR (1994) [38], 7) CITR (1995) [39], 8) AT&T (1993) [40], 8) NTT (1994) [41], 9)AT&T (1994) [16], 10) AT&T (1995) [42], 11) GaTech (1990) 12) Edinburgh (1991) [43], and 13) UC (1994) [44]. The smart pixel technologies represented include: ×—Hybrid CMOS-SEED, ▲—Monolithic MSM/MESFET/VCSEL, ♦—Hybrid MSM/VCSEL, ★—FET-SEED, ■—S-SEED, ■ and □-FLC-LCOS

smart spatial light modulators has also made significant progress. This progress is illustrated in the lower right corner of the figure. The target devices for this type of smart pixel include large arrays greater than  $512 \times 512$  with modulator switching speeds in the 100- $\mu s$  range.

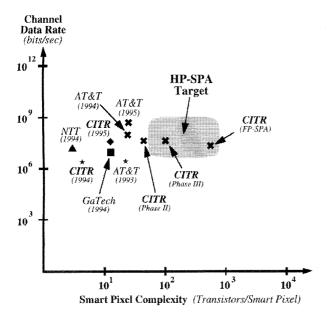

# B. SPA Complexity

Fig. 14 shows the trends in SPA intelligence. Since SPA's are based on the electronic integrated circuit technologies, they will be directly linked to the evolution of the semi-conductor industry. The Semiconductor Industry Association's semiconductor roadmap, partially listed in Table I, illustrates the projected evolution of both the semiconductor electronic and the smart pixel technologies to the year 2010 [46].

Based on these SIA projections, it is conceivable that by the year 1998,  $32 \times 32$  SPA's will be using 0.25- $\mu$ m CMOS with each smart pixel containing up to 4000 transistors and operating in excess of 450 Mb/s per channel. This would provide greater than 450 Gb/s aggregate capacity per SPA! Further extrapolation leads to the year 2007 when  $32 \times 32$  SPA's will be using 0.1- $\mu$ m CMOS with each smart pixel containing up to  $12\,000$  transistors and operating in excess of 1 Gb/s per channel. This would realize the technology design objective of 1 Tb/s aggregate capacity per SPA.

#### C. SPA Demonstrator Performance

There have been several SPA-based systems that have been successfully constructed and demonstrated within the past few years. These demonstrators include photonic switching

TABLE I SIA SEMICONDUCTOR ROADMAP

| First DRAM Shipment Minimum Feature Size | <b>1995</b><br>0.35 μm | 1998<br>0.25 μm | 2001<br>0.18 µm | 2004<br>0.13 μm | 2007<br>0.1 μm                        | 2010<br>0.07μm |

|------------------------------------------|------------------------|-----------------|-----------------|-----------------|---------------------------------------|----------------|

| Memory                                   | 0.55 μπ                | 0.25 µm         | 0.10 µm         | 0.13 μπ         | 0.1 µm                                | 0.07 μm        |

| Bits/Chip (DRAM/Flash)                   | 64M                    | 256M            | 1G              | 4G              | 16G                                   | 64G            |

| Logic (High Volume µP)                   |                        | 1               |                 |                 |                                       |                |

| Transistors/cm <sup>2</sup> (packed)     | 4M                     | 7M              | 13M             | 25M             | 50M                                   | 90M            |

| Logic (Low Volume ASIC)                  |                        |                 |                 |                 |                                       |                |

| Transistors/cm2 (auto layout)            | 2M                     | 4M              | 7M              | I2M             | 25M                                   | 40M            |

| Number of Chip I/O                       |                        |                 |                 | -               |                                       |                |

| High Performance                         | 900                    | 1350            | 2000            | 2600            | 3600                                  | 4800           |

| Chip Frequency (MHz)                     |                        |                 |                 |                 | · · · · · · · · · · · · · · · · · · · |                |

| On-chip (cost performance)               | 150                    | 200             | 300             | 400             | 500                                   | 625            |

| On-chip (high performance)               | 300                    | 450             | 600             | 800             | 1000                                  | 1100           |

| Chip-to-board                            | 150                    | 200             | 250             | 300             | 375                                   | 475            |

| Chip Size (cm²)                          |                        |                 |                 |                 |                                       |                |

| DRAM                                     | 1.9                    | 2.8             | 4.2             | 6.4             | 9.6                                   | 14.0           |

| Microprocessor                           | 2.5                    | 3.0             | 3.6             | 4.3             | 5.2                                   | 6.2            |

| ASIC                                     | 4.5                    | 6.6             | 7.5             | 9.0             | 11.0                                  | 14.0           |

| Power Suppy Voltage (V)                  |                        |                 |                 |                 | -                                     |                |

| Desktop                                  | 3.3                    | 2.5             | 1.8             | 1.5             | 1.2                                   | 0.9            |

| Battery                                  | 2.5                    | 1.8-2.5         | 0.9-1.8         | 0.9             | 0.9                                   | 0.9            |

| Maximum Power                            |                        |                 |                 |                 |                                       |                |

| HP with heatsink (W)                     | 80                     | 100             | 120             | 140             | 160                                   | 180            |

| Logic w/o heatsink (W/cm <sup>2</sup> )  | 5                      | 7               | 10              | 10              | 10                                    | 10             |

| Battery (W)                              | 2.5                    | 2.5             | 3.0             | 3.5             | 4.0                                   | 4.5            |

systems, optical computing systems, and free-space optical backplanes. The performance of these systems is shown in Fig. 15. The total systems connections is the sum of the individual SPA connectivities. As an example, the 1993 AT&T System included five  $4 \times 4$  FET-SEED SPA's. Each SPA had 32 optical inputs (32 optical channels comprised of 64 differential optical signals) and 32 optical outputs (64 differential optical signals) for a total of 640 system optical connections (this does not include the optical power supply inputs, 64 per SPA, required for this type of modulator-based

Fig. 14. The smart pixel array complexity versus the individual optical channel bit rate for the following SPAs: 1) NTT (1994) [41], 2) CITR (1994) [39], 3) CITR (1995) [39], 4) GaTech (1994) [37], 5) AT&T (1993) [40], 6)AT&T (1994) [16], 7) AT&T (1995) [42], 8) CITR (*Phase III*) [39], and 10) CITR (*FP-SPA*) [45]. The smart pixel technologies represented include: ×—Hybrid CMOS-SEED, ▲—Monolithic MSM/MESFET/VCSEL, ♦—Hybrid MSM/VCSEL, ★—FET-SEED, and ■—ELO.

system). This figure also shows the performance targets for SPA-based systems to be demonstrated in the 1996–1997 timeframe.

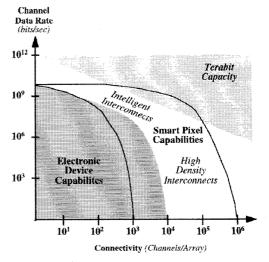

#### VI. APPLICATIONS

There are two main classes of applications that match the capabilities of the smart pixel technologies: high-performance intelligent interconnects and high-density interconnects. High-performance intelligent interconnects refer to applications that require a modest number (10–10 000) of high-performance interconnects (>100 Mb/s) supported by a significant amount of intelligence (>50 transistors per optical I/O). This application class includes optical backplanes, switching networks, and high-performance computers. The second class of applications, high-density interconnects, focuses more on connectivity (1000–100 000) than performance (<100 Mb/s) and/or intelligence (<50 transistors per optical I/O). Specific applications include: advanced displays, optical storage, analog optical processing, optical neural networks, etc. Fig. 16 illustrates the potential application space of the smart pixel technology.

Perhaps the most critical aspect in the evolution of applications based on the SPA technology will be the development of a low-cost, high-reliability packaging technology. The optomechanical tolerances required to optically interconnect successive SPA's will require modular, manufacturable optical hardware modules (OHM) that can transfer optical information from the transmitting SPA to the photodetectors of the receiving SPA. In addition, for the case of modulator-based systems, the OHM will also have the responsibility to deliver optical power to the modulators. In order to integrate SPA's

Fig. 15. SPA system connectivity versus the individual optical channel bit rate with the following demonstrated SPAs: 1) AT&T (1988) [33], 2) AT&T (1989) [34], 3) AT&T (1990) [35], 4) AT&T (1991) [36], 5) CITR (1993) [38], 6) CITR (1994) [39], 7) CITR (1995) [39], 8) AT&T (1993) [40], 9) NTT (1994) [41], and 10) AT&T (1995) [42]. The smart pixel technologies represented include: ×—Hybrid CMOS-SEED, ▲—Monolithic MSM/MESFET/VCSEL, ♦—Hybrid MSM/VCSEL, ★—FET—SEED, and ●—S-SEFD.

Fig. 16. Smart pixel application space.

into the existing digital electronic infrastructure, it is necessary that a compact and durable optical system be designed and developed that is compatible with current computer packaging. This implies the following OHM requirements.

- 1) Support a smart pixel density of 1000 smart pixels/cm<sup>2</sup>

- 2) Fit in a standard electrical rack:  $\sim 1''$  spacing between SPA's and a 1-in<sup>3</sup> optomechanical volume per SPA pair.

- 3) Support a SPA size of 1 cm  $\times$  1 cm.

- 4) For modulator-based systems, keep the loss between the optical power supply and the detector less than 10 dB, and for the source-based systems, keep the loss between the VCSEL's and the detector less than 3 dB.

- 5) Use only elements which are potentially cost-effective in mass production.

- 6) Minimize the number of critical alignments.

- Maintain optomechanical stability over a 100° temperature range.

- Modular OHM's that can operate in a "plug and play" environment.

The push to decrease optical system size has dramatically changed the methods for system packaging. Previous free-space digital optics systems typically used nearly all 32 ft<sup>2</sup> of an optical table [4]. The large system size was due to the large size of the off-the-shelf optical components and their mounting mechanisms. With the shrinking of optical components and the availability of high-power laser diodes, new optical system packaging methods are evolving which are compatible with the physical conventions of current electronic systems. The current optomechanical approaches include: slotted baseplates [4], barrels [39], glued optics [41], and, finally, active alignment [47].

#### VII. CONCLUSION

This paper has described the major SPA technologies that are currently evolving toward manufacturable device platforms. The reviewed SPA technologies included both the modulator-based FET-SEED, Hybrid CMOS-SEED, and LCOS smart pixels and the source-based Hybrid VCSEL/MSM, ELO, flip-chip-bonded VCSEL/MSM, and monolithic MSM/MESFET/VCSEL smart pixels.

# REFERENCES

- H. S. Hinton, "Architectural considerations for photonic switching networks," *IEEE J. Select. Areas Commun.*, vol. 6, pp. 1209–1226, Aug. 1988.

- [2] T. K. Woodward, A. L. Lentine, and L. M. F. Chirovsky, "Experimental sensitivity studies of diode-clamped FET-SEED smart pixel optical receivers," *IEEE J. Quantum Electron.*, vol. 30, pp. 2319–2324, Oct. 1994

- [3] D. A. B. Miller, "Optics for low-energy communication inside digital processors: Quantum detectors, sources, and modulators as efficient impedance converters," *Opt. Lett.*, vol. 14, no. 2, pp. 146–148, Jan. 15, 1989.

- [4] H. S. Hinton et al., "Free-space digital optical systems," Proc. IEEE, vol. 82, pp. 1632–1649, Nov. 1994.

- [5] F. B. McCormick, F. A. P. Tooley, T. J. Cloonan, J. M. Sasian, H. S. Hinton, K. O. Mersereau, and A. Y. Feldblum, "Optical interconnection using microlens arrays," *Opt. Quantum Electron.*, vol. 24, no. 4, pp. S465–S477, Apr. 1992.

- [6] D. R. Rolston, B. Robertson, H. S. Hinton, and D. V. Plant, "Analysis of a microchannel interconnect based on the clustering of smart-pixeldevice windows," *Appl. Opt.*, vol. 35, no. 8, pp. 1220–1233, Mar. 10, 1996.

- [7] D. V. Plant, B. Robertson, H. S. Hinton, M. H. Ayliffe, G. C. Boisset, D. J. Goodwill, D. N. Kabal, R. Iyer, Y. S. Liu, D. R. Rolston, W. M. Robertson, and M. R. Taghizadeh, "A multistage CMOS-SEED optical backplane demonstration system," in 1996 Top. Meet. Optical Computing, Sendai, Japan, Apr. 21–25, pp. 14–15.

- [8] A. L. Lentine and D. A. B. Miller, "Evolution of the SEED technology: Bistable logic gates to optoelectronic smart pixels," *IEEE J. Quantum Electron.*, vol. 29, pp. 655–669, Feb. 1993.

- [9] L. A. D'Asaro, L. M. F. Chirovsky, E. J. Laskowski, S. S. Pei, T. K. Woodward, A. L. Lentine, R. E. Leibenguth, M. W. Focht, J. M. Freund, G. G. Guth, and L. E. Smith, "Batch fabrication and operation of GaAs-Al<sub>x</sub>Ga 1<sub>-x</sub>As field-effect transistor-self-electrooptic effect device (FET-SEED) smart pixel arrays," *IEEE J. Quantum Electron*, vol. 29, pp. 670-677, Feb. 1993.

[10] AT&T/ARPA FET-SEED Workshop Technical Notes, July 1995, un-

- [10] AT&T/ARPA FET-SEED Workshop Technical Notes, July 1995, unpublished.

- [11] F. B. McCormick, T. J. Cloonan, A. L. Lentine, J. M. Sasian, R. L. Morrison, M. G. Beckman, S. L. Walker, M. J. Wojcik, S. J. Hinterlong, R. J. Crisci, R. A. Novotny, and H. S. Hinton, "A 5-stage free-space optical switching network with field-effect transistor self-electro-optic-effect smart pixel arrays," *Appl. Opt.*, vol. 33, no. 8, pp. 1601–1618, Mar. 10, 1994.

- Mar. 10, 1994.

[12] D. V. Plant, A. Z. Shang, M. R. Otazo, D. R. Rolston, B. Robertson, and H. S. Hinton, "Design, modeling, and characterization of FET-SEED smart pixel transceiver for optical backplanes," *IEEE J. Quantum Electron.*, vol. 32, no. 8, Aug. 1996.

- [13] M. W. Derstine, K. K. Chau, and S. Wakelin, "A FET-SEED-based transmitter/receiver array," in *IEEE LEOS Summer Top. Meet. Smart Pixels*, Lake Tahoe, NV, July 11–13, 1994, pp. 34–35.

- Pixels, Lake Tahoe, NV, July 11–13, 1994, pp. 34–35.

[14] C. B. Kuznia, A. A. Sawchuk, and L. Cheng, "FET-SEED smart pixel chip for network applications," in Proc. IEEE/LEOS Summer Top. Meet. Smart Pixels, IEEE Lasers and Electro-Optics Society, Piscataway, NJ, July 11–13, 1994, pp. 28–29.

- [15] M. J. Goodwin, A. J. Moseley, M. Q. Kearley, R. C. Morris, C. J. G. Kirkby, J. Thompson, R. C. Goodfellow, and I. Bennion, "Opto-electronic component arrays for optical interconnection of circuits and subsystems," *IEEE J. Lightwave Technol.*, vol. 9, no. 12, pp. 1639–1645, Dec. 1991.

- [16] K. W. Goossen, J. A. Walker, L. A. D'Asaro, S. P. Hui, and B. Tseng, "GaAs MQW modulators integrated with silicon CMOS," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 360–362, 1995.

- [17] AT&T/ARPA Workshop on Hybrid-SEED Smart Pixels, George Mason University, 1995.

- [18] K. E. Devenport and H. S. Hinton, "A buffered ATM hyperplane smart pixel array," presented at the 1996 Topical Meeting on Smart Pixels, Keystone, CO, Aug. 7–9.

- [19] T. K. Woodward, A. V. Krishnamoorthy, A. L. Lentine, K. W. Goossen, J. A. Walker, J. E. Cunningham, W. Y. Jan, L. A. D'Asaro, L. M. F. Chirovsky, S. P. Hui, B. Tseng, D. Kossives, D. Dahringer, and R. E. Leibenguth, "1-Gb/s two-beam transimpedance smart-pixel optical receivers made from hybrid GaAs MQW modulators bonded to 0.8 μm silicon CMOS," *IEEE Photon. Technol. Lett.*, vol. 8, p. 422, 1996

- [20] K. M. Johnson, D. J. McKnight, and I. Underwood, "Smart spatial light modulators using liquid crystals on silicon," *IEEE J. Quantum Electron.*, vol. 25, pp. 699–714, Feb. 1993.

[21] T. H. Ju, W. Lin, Y. C. Lee, D. J. McKnight, and K. M. Johnson, "Pack-

- [21] T. H. Ju, W. Lin, Y. C. Lee, D. J. McKnight, and K. M. Johnson, "Packaging of a 128 × 128 liquid-crystal-on-silicon spatial light modulator using self-pulling soldering," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 1010–1012, Sept. 1995.

- [22] D. V. Plant, B. Robertson, H. S. Hinton, M. H. Ayliffe, G. C. Boisset, W. Hsiao, D. Kabal, N. K. Kim, Y. S. Liu, R. M. Otazo, A. Z. Shang, J. Simmons, and W. M. Robertson, "A 4 × 4 VCSEL/MSM optical backplane demonstrator," presented at the 1995 LEOS Annual Meeting, post-deadline paper PD5.

- [23] K. Devenport, D. Kabal, D. V. Plant, and H. S. Hinton, unpublished.

- [24] E. Yablonovitch, T. J. Gmitter, J. P. Harbison, and R. Bhat, "Extreme selectivity in the liftoff of epitaxial GaAs films," *Appl. Phys.*, vol. 51, no. 26, pp. 2222–2224, 1987.

- [25] C. Camperi-Ginestet, M. Hargis, N. M. Jokerst, and M. Allem, "Alignable epitaxial liftoff of GaAs materials with selective deposition using polyimide diaphragms," *IEEE Photon. Technol. Lett.*, vol. 3, pp. 1123–1126, Dec. 1991.

- [26] K. H. Calhoun, C. Camperi-Ginestet, and N. M. Jokerst, "Vertical optical communication through stacked silicon wafers using hybrid monolithic thin film InGaAsP emitters and detectors," *IEEE Photon. Technol. Lett.*, vol. 5, pp. 254–257, Feb. 1993.

- [27] S. M. Fike, B. Buchanan, N. M. Jokerst, M. A. Broode, T. G. Morris, and S. P. DeWeerth, "8 × 8 array of thin-film photodetectors vertically electrically interconnected to silicon circuitry," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 1168–1170, Oct. 1995.

- Lett., vol. 7, pp. 1168–1170, Oct. 1995.

O. Vendier, S. T. Wilkinson, S. Bond, M. Lee, Z. Hou, A. Lopez-Lagunas, P. May, M. A. Brooke, N. M. Jokerst, and S. Wills, "A 155 Mb/s digital transmitter using GaAs thin film LED's bonded to silicon driver circuits," presented at the 1996 Topical Meeting on Smart Pixels, Keystone, CO, Aug. 7–9.

- [29] M. Lee, O. Vendier, M. A. Brooke, and N. M. Jokerst, "A 250 Mbps CMOS optical receiver with an integrated InGaAs thin-film inverted MSM detector," presented at the 1996 Topical Meeting on Smart Pixels, Keystone, CO, Aug. 7–9.

- [30] N. M. Jokerst, C. Camperi-Ginestet, B. Buchanan, S. Wilkinson, and M. A. Brooke, "Communication through stacked silicon circuitry using integrated thin film InP-based emitters and detectors," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 1028–1030, Sept. 1995.

- [31] D. S. Wills, W. S. Lacy, C. Camperi-Ginestet, B. Buchanan, H. H. Cat, S. Wilkinson, M. Lee, N. M. Jokerst, and M. A. Brooke, "A three-dimensional high-throughput architecture using through-wafer optical interconnect," *J. Lightwave Technol.*, vol. 13, pp. 1085–1092, June 1995.

- [32] S. Matsuo, T. Nakahara, Y. Kohama, Y. Ohiso, S. Fukushima, and T. Kurokawa, "Monolithically integrated photonic switching device using an MSM PD, MESFET's, and a VCSEL," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 1165–1167, Oct. 1995.

- [33] E. Kerbis, T. J. Cloonan, and F. B. McCormick, "An all-optical realization of a 2 × 1 free-space switching node," *IEEE Photon. Technol. Lett.*, vol. 2, pp. 600–602, Aug. 1990.

- Lett., vol. 2, pp. 600–602, Aug. 1990.

[34] T. J. Cloonan, M. J. Herron, F. A. P. Tooley, G. W. Richards, F. B. McCormick, E. Kerbis, J. L. Brubaker, and A. L. Lentine, "An alloptical implementation of a 3D crossover switching network," *Photonic Switching II*, K. Tada and H. S. Hinton, Eds. New York: Springer-Verlag, 1990, pp. 196–199.

- [35] F. B. McCormick, F. A. P. Tooley, T. J. Cloonan, J. L. Brubaker, A. L. Lentine, R. L. Morrison, S. J. Hinterlong, M. J. Herron, S. L. Walker, and J. M. Sasian, "Experimental investigation of a free-space optical switching network by using symmetric self-electro-optic-effect devices," *Appl. Opt.*, vol. 31, no. 26, pp. 5431–5446, Sept. 10, 1992.

- [36] F. B. McCormick, T. J. Cloonan, F. A. P. Tooley, A. L. Lentine, J. M. Sasian, J. L. Brubaker, R. L. Morrison, S. L. Walker, R. J. Crisci, R. A. Novotny, S. J. Hinterlong, H. S. Hinton, and E. Kerbis, "A six-stage digital free-space optical switching network using S-SEED's," Appl. Opt., vol. 32, no. 26, pp. 5153–5171, Sept. 10, 1993.

- [37] C. Camperi-Ginestet et al., Optical Computing, 1995 OSA Tech. Dig. Ser. Washington, DC: Opt. Soc. Amer., 1995, vol. 10, pp. 145–147.

- [38] D. V. Plant, B. Robertson, G. C. Boisset, N. K. Kim, Y. S. Liu, R. M. Otazo, D. R. Rolston, A. Z. Shang, H. S. Hinton, and W. M. Robertson, "16-channel FET-SEED based optical backplane interconnection," in *Tech. Dig. 1994 OSA Top. Meet. Optical Computing*, 1995, pp. 272–275.

- [39] D. V. Plant, B. Robertson, H. S. Hinton, M. H. Ayliffe, G. C. Boisset, W. Hsiao, D. Kabal, N. K. Kim, Y. S. Liu, R. M. Otazo, A. Z. Shang, J. Simmons, and W. M. Robertson, "A 4 × 4 VCSEL/MSM optical backplane demonstrator," presented at the IEEE LEOS Annual Meeting, San Francisco, CA, post-deadline paper PD5.

- [40] F. B. McCormick, T. J. Cloonan, A. L. Lentine, J. M. Sasian, R. L. Morrison, M. G. Beckman, S. L. Walker, M. J. Wojcik, S. J. Hinterlong, R. J. Crisci, R. A. Novotny, and H. S. Hinton, "A 5-stage free-space optical switching network with field-effect transistor self-electro-optic-effect smart pixel arrays," Appl. Opt., vol. 33, no. 8, pp. 1601–1618, Mar. 10, 1994.

- [41] S. Matsuo, T. Makahara, Y. Kohama, Y. Ohiso, S. Fukushima, and T. Kurokawa, "Monolithically integrated photonic switching device using

- an MSM PD, MESFET's, and a VCSEL," IEEE Photon. Technol. Lett., vol. 7, pp. 1165–1167, Oct. 1995.

- [42] A. L. Lentine, R. A. Novotny, D. J. Reiley, R. L. Morrison, J. M. Sasian, M. G. Beckman, D. B. Buchholz, S. J. Hinterlong, T. J. Cloonan, G. W. Richards, and F. B. McCormick, "Demonstration of an experimental single chip optoelectronic switching system," presented at the IEEE LEOS Annual Meeting, San Francisco, CA, Nov. 1995, post-deadline paper.

- [43] I. Underwood, D. G. Vass, R. M. Silitto, G. Bradford, N. E. Fancey, A. O. AlChalabi, M. J. Birch, W. A. Crossland, A. P. Sparks, and S. G. Letham, "A high performance spatial light modulator," *Proc. SPIE*, vol. 1562, pp. 107–115, 1991.

- [44] D. J. McKnight, K. M. Johnson, and R. A. Serati, "256 × 256 liquid-crystal-on-silicon spatial light modulator," *Appl. Opt.*, vol. 33, pp. 2775–2784, 1994.

- [45] T. H. Szymanski, S. Sherif, and H. S. Hinton, presented at the 1995 Annual Meeting for Canadian Institute for Telecommunications.

- [46] National Technology Roadmap for Semiconductors, Semiconductor Industry Association, 1994, p. B2.

[47] G. C. Boisset, B. Robertson, and H. S. Hinton, "Design and con-

- [47] G. C. Boisset, B. Robertson, and H. S. Hinton, "Design and construction of an active alignment demonstrator for a free-space optical interconnect," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 676–678, June 1995

H. Scott Hinton (S'81-M'82-SM'92) was born in Salt Lake City, UT, in 1951. He received the B.S.E.E. degree from Brigham Young University, Provo, UT, in 1981 and the M.S.E.E. degree from Purdue University, Lafayette, IN, in 1982.

In 1981, he joined AT&T Bell Laboratories, Naperville, IL, as a Member of the Technical Staff. He was promoted to Supervisor of the Photonic Switching Technologies group in 1985 and then Head of the Photonic Switching Department in 1989, where his department was responsible for

the development of systems applications of the S-SEED and FET-SEED technology. From 1992 to 1994, he was the BNR-NT/NSERC Chair in Photonic Systems at McGill University, Montreal, PQ, Canada. In 1994, he accepted the position as the Hudson Moore, Jr., Professor of Electrical and Computer Engineering at the University of Colorado at Boulder. His current research is focused on developing systems applications of smart pixels and free-space optical interconnection.

Mr. Hinton is a member of the Optical Society of America. He was an IEEE LEOS Distinguished Lecturer for 1993–1994.