Utah State University DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

5-2010

# A Finite Domain Constraint Approach for Placement and Routing of Coarse-Grained Reconfigurable Architectures

Rohit Saraswat Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Computer Engineering Commons, and the Electrical and Electronics Commons

# **Recommended Citation**

Saraswat, Rohit, "A Finite Domain Constraint Approach for Placement and Routing of Coarse-Grained Reconfigurable Architectures" (2010). *All Graduate Theses and Dissertations*. 689. https://digitalcommons.usu.edu/etd/689

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

# A FINITE DOMAIN CONSTRAINT APPROACH FOR PLACEMENT AND ROUTING OF COARSE-GRAINED RECONFIGURABLE ARCHITECTURES

by

Rohit Saraswat

A dissertation submitted in partial fulfillment of the requirements for the degree

of

## DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

Approved:

Dr. Brandon Eames Major Professor Dr. Aravind Dasu Committee Member

Dr. Koushik Chakraborty Committee Member Dr. Sanghamitra Roy Committee Member

Dr. Scott Budge Committee Member Dr. Steve Allan Committee Member

Dr. Byron R. Burnham Dean of Graduate Studies

UTAH STATE UNIVERSITY Logan, Utah

2010

Copyright © Rohit Saraswat 2010

All Rights Reserved

# Abstract

A Finite Domain Constraint Approach for Placement and Routing of Coarse-Grained Reconfigurable Architectures

by

Rohit Saraswat, Doctor of Philosophy

Utah State University, 2010

Major Professor: Dr. Brandon Eames Department: Electrical and Computer Engineering

Scheduling, placement, and routing are important steps in Very Large Scale Integration (VLSI) design. Researchers have developed numerous techniques to solve placement and routing problems. As the complexity of Application Specific Integrated Circuits (ASICs) increased over the past decades, so did the demand for improved place and route techniques. The primary objective of these place and route approaches has typically been wirelength minimization due to its impact on signal delay and design performance. With the advent of Field Programmable Gate Arrays (FPGAs), the same place and route techniques were applied to FPGA-based design. However, traditional place and route techniques may not work for Coarse-Grained Reconfigurable Architectures (CGRAs), which are reconfigurable devices offering wider path widths than FPGAs and more flexibility than ASICs, due to the differences in architecture and routing network. Further, the routing network of several types of CGRAs, including the Field Programmable Object Array (FPOA), has deterministic timing as compared to the routing fabric of most ASICs and FPGAs reported in the literature. This necessitates a fresh look at alternative approaches to place and route designs. This dissertation presents a finite domain constraint-based, delay-aware placement and routing methodology targeting an FPOA. The proposed methodology takes advantage of the deterministic routing network of CGRAs to perform a delay aware placement.

(190 pages)

To the two most important ladies in my life, my mother Sushil and my wife Netra.

# Acknowledgments

I will be eternally grateful to several people who directly or indirectly contributed to the success of this dissertation. First and foremost, I would like to thank my family for their support and encouragement. I am grateful to my parents who themselves set the standards so high that not pursuing a Ph.D. was never an option. Special thanks to my mom, who in spite of being on the other side of the planet, has always been close enough to support me through my struggles as a graduate student. I thank my wife, Netra, for her unconditional love, constant support, patience, and enthusiasm which kept my morale high and motivated me to keep going through to the end, even when I spent more time with my computer than with her. Honestly, it would take another dissertation to express my appreciation, love, and devotion to her. I also thank my sister, Jyoti, and my wife's parents for their support.

I express my gratitute and thanks to my advisor, Dr. Brandon Eames, for his vision, guidance, and patience through the last four years of graduate school. I thank him for making me aware of the pitfalls along the research path, but more so for letting me shoot myself in the foot for a first-hand experience. He is one the best teachers and researchers that I have come across in my student life. Working with him made me feel more like a fellow researcher than a student. He is truly a friend, philosopher, and guide (the last two not because he has a Ph.D. but because he is my advisor), from whom I have learned a lot in the classroom and beyond.

The other members of my committee have also been instrumental in enriching my graduate experience. I am grateful to Dr. Aravind Dasu who helped me achieve my goals through his encouragement and constructive criticisms. I am also thankful to Dr. Koushik Chakraborty and Dr. Sanghamitra Roy for providing valuable inputs that helped me think beyond my world of deterministic timing and for being as much friends as committee members. I also thank Dr. Steve Allan and Dr. Scott Budge for their influence on my graduate career.

I am also thankful to my friends and colleagues, especially Arvind, Shantanu, Prasad, Atul, and Sravanthi, who made my stay in Logan enjoyable. I would also like to acknowledge Mathstar and the ECE Department, which partially provided financial support for this research.

Rohit Saraswat

# Contents

|     |                                 | Pa                                                                                                                                                                          | age                                                                                                                           |

|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Ab  | stra                            | $\operatorname{\mathbf{ct}}$                                                                                                                                                | iii                                                                                                                           |

| Ac  | knov                            | wledgments                                                                                                                                                                  | vi                                                                                                                            |

| Lis | t of                            | Tables                                                                                                                                                                      | xi                                                                                                                            |

| Lis | t of                            | Figures                                                                                                                                                                     | xii                                                                                                                           |

| Lis | t of                            | Algorithms                                                                                                                                                                  | xvi                                                                                                                           |

|     |                                 | /ms                                                                                                                                                                         | vii                                                                                                                           |

| 1   | •                               | oduction         Motivation of this Research         Research Contributions         Overview of This Document                                                               | $f 1 \\ 3 \\ 6 \\ 7 \fi$                                                                                                      |

|     | Rela<br>2.1<br>2.2<br>2.3       | ated Work2D Mesh Coarse-Grained Reconfigurable ArchitecturesSearch TechniquesPlacement and Routing Techniques2.3.1P&R for ASICs2.3.2P&R for FPGAs2.3.3P&R for CGRAs         | <ol> <li>9</li> <li>15</li> <li>18</li> <li>19</li> <li>23</li> <li>28</li> </ol>                                             |

|     | <b>Bac</b><br>3.1<br>3.2        | kgroundFPOA Architecture3.1.1 ALU Object3.1.2 MAC Object3.1.3 RF Object3.1.4 Interconnect FrameworkFinite Domain Constraints3.2.1 Propagation3.2.2 Distribution3.2.3 Search | <ul> <li><b>31</b></li> <li>31</li> <li>32</li> <li>32</li> <li>33</li> <li>36</li> <li>37</li> <li>38</li> <li>41</li> </ul> |

| •   | <b>Res</b><br>4.1<br>4.2<br>4.3 | ource Allocation and Scheduling         Data Flow Graph         Resources in an FPOA         Resource Allocation and Scheduling         4.3.1         Resource Allocation   | <b>42</b><br>42<br>43<br>44<br>45                                                                                             |

|          |                | 4.3.2 Scheduling                                                                                                                           |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.4            | Resource Allocation and Scheduling Algorithms                                                                                              |

|          | 4.5            | Schedule Relaxation                                                                                                                        |

|          | 4.6            | A Finite Domain Model for Allocation and Scheduling                                                                                        |

|          | 1.0            | 4.6.1 A Finite Domain Model for Allocation                                                                                                 |

|          |                | 4.6.2 A Finite Domain Model for Scheduling                                                                                                 |

|          |                | 4.6.3 Distribution Strategy for Allocation and Scheduling                                                                                  |

|          |                | 4.0.5 Distribution Strategy for Anocasion and Scheduling                                                                                   |

| <b>5</b> | $\mathbf{Del}$ | ay Aware Placement                                                                                                                         |

|          | 5.1            | A Formal Model for Objects in an FPOA                                                                                                      |

|          | 5.2            | Placement Problem                                                                                                                          |

|          |                | 5.2.1 Nearest Neighbor Communication                                                                                                       |

|          |                | 5.2.2 Party Line Communication                                                                                                             |

|          | 5.3            | Placement Algorithm                                                                                                                        |

|          | 5.4            | Solving Placement Problem Using FD Constraints                                                                                             |

|          |                | 5.4.1 FD Variables and Constraints                                                                                                         |

|          |                | 5.4.2 Improving Propagation                                                                                                                |

|          |                | 5.4.3 Distribution Strategy 90                                                                                                             |

|          | 5.5            | Placement Summary                                                                                                                          |

|          |                |                                                                                                                                            |

| 6        |                | 1 ting                                                                                                                                     |

|          | 6.1            | Mathematical Model of Routing Resources                                                                                                    |

|          | 6.2            | Routing Problem                                                                                                                            |

|          |                | 6.2.1 Register and Multiplexer Location                                                                                                    |

|          |                | 6.2.2 Party Line Groups                                                                                                                    |

|          |                | 6.2.3 Register and Multiplexer Orientation                                                                                                 |

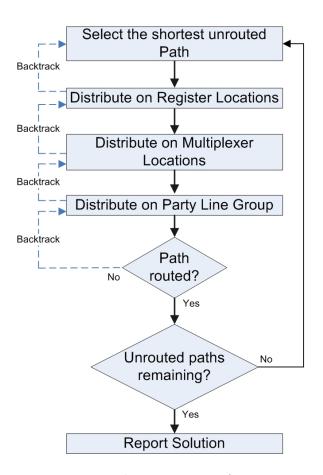

|          | 6.3            | Routing Algorithm                                                                                                                          |

|          | 6.4            | Solving Routing Problem Using FD Constraints                                                                                               |

|          |                | 6.4.1 FD Variables and Constraints                                                                                                         |

|          |                | 6.4.2 Improving Search Convergence                                                                                                         |

|          |                | 6.4.3 Distribution Strategy 112                                                                                                            |

|          | 6.5            | Summary 114                                                                                                                                |

| 7        | Dag            | ulta 116                                                                                                                                   |

| 7        |                | Sults         116           Overview of Benchmarks         116                                                                             |

|          | 7.1            |                                                                                                                                            |

|          | 7.2            | Performance Evaluation of Proposed Tools                                                                                                   |

|          |                | 7.2.1 Scheduling 118                                                                                                                       |

|          |                | 7.2.2 Placement                                                                                                                            |

|          |                | 7.2.3 Routing                                                                                                                              |

|          | 7.3            | Tool Performance for Varying Problem Size    134                                                                                           |

|          | 7.4            | Tool Performance Beyond Arrix Architecture    137                                                                                          |

| 8        | Cor            | clusions and Future Work                                                                                                                   |

| п        | ofore          | 140                                                                                                                                        |

| n        | erere          | $\mathrm{nces} \ldots 146$ |

ix

| Appendices                                                     | <br>155 |

|----------------------------------------------------------------|---------|

| Appendix A MaxEightALU Constraint Implementation in C++        | 156     |

| A.1 MaxEightALU Header File                                    | 156     |

| A.2 MaxEightALU Source Code                                    | 159     |

| Appendix B NAND Gate Count and Execution Latency of Benchmarks | 164     |

| Appendix C Layout of Benchmarks                                | 165     |

| Vita                                                           | <br>170 |

# List of Tables

| Table |                                                                                              | Page  |

|-------|----------------------------------------------------------------------------------------------|-------|

| 2.1   | Summary of coarse-grained reconfigurable architectures. A * indicates pro-<br>prietary tools | 16    |

| 2.2   | Design tools for CGRAs                                                                       | 17    |

| 2.3   | Placement and routing methods for ASICs                                                      | 24    |

| 2.4   | Placement and routing methods for FPGAs                                                      | 28    |

| 2.5   | Placement and routing methods for CGRAs.                                                     | 30    |

| 4.1   | Latency of FPOA objects.                                                                     | 45    |

| 7.1   | Benchmarks used for evaluating scheduling, placement, and routing tools                      | 117   |

| 7.2   | Effect of bounding box on placement tool performance                                         | 126   |

| 7.3   | Effect of divide and conquer on placement tool performance                                   | 127   |

| 7.4   | Performance of simulated annealing-based placement.                                          | 129   |

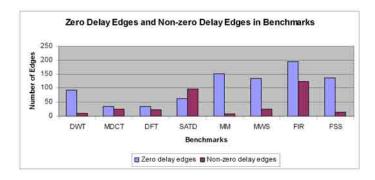

| 7.5   | Party line resource utilization for routing non-zero delay edges                             | 131   |

| B.1   | Number of objects, NAND gate count, and execution latency of benchmarks                      | . 164 |

| C.1   | Number of different types of operations in a benchmark                                       | 165   |

# List of Figures

| Figure |                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Flexibility vs. performance for different types of architectures                                                 | 2    |

| 1.2    | ASIC/FPGA placement and routing objective.                                                                       | 3    |

| 1.3    | FPOA placement and routing objective.                                                                            | 4    |

| 1.4    | Proposed FPOA tool flow                                                                                          | 7    |

| 3.1    | FPOA arrix architecture.                                                                                         | 32   |

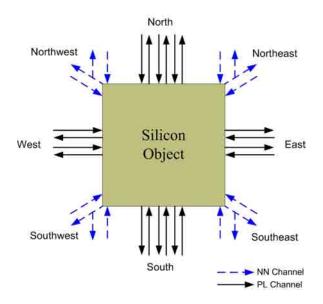

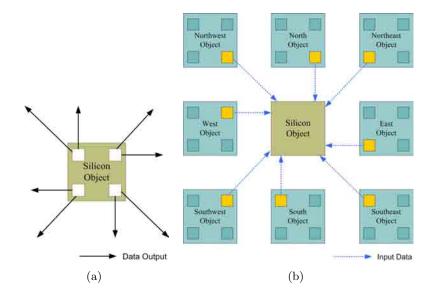

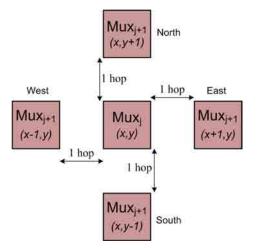

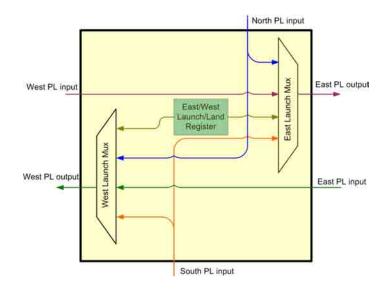

| 3.2    | Communication channels.                                                                                          | 33   |

| 3.3    | Nearest neighbor registers (a) Local NN registers for data output, and (b) Adjacent NN registers for data input. | 34   |

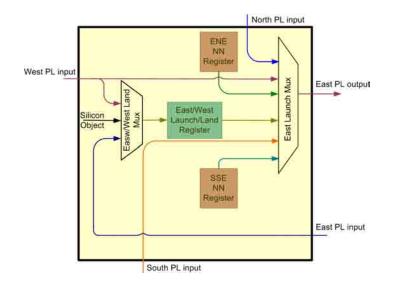

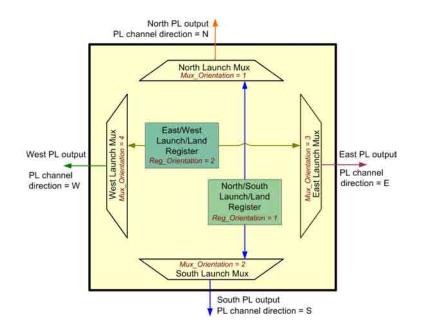

| 3.4    | Party line launch and land register                                                                              | 35   |

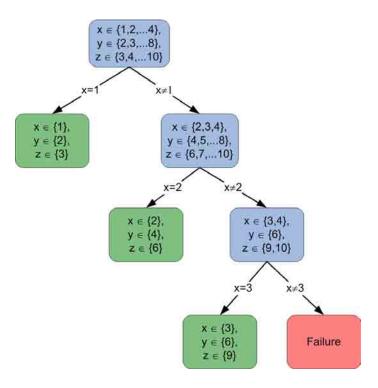

| 3.5    | Distribution steps for $x + y = z$                                                                               | 39   |

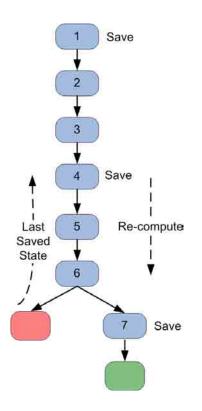

| 3.6    | Recomputation with step size $S_{RC} = 3$                                                                        | 40   |

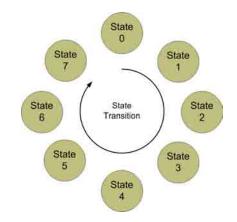

| 4.1    | Instruction state machine of an ALU.                                                                             | 44   |

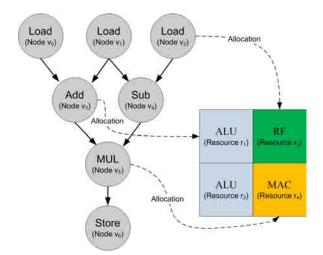

| 4.2    | Allocating resources to nodes of a DFG                                                                           | 46   |

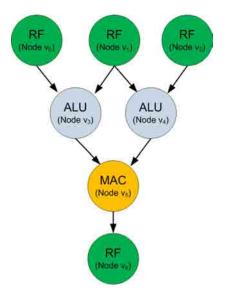

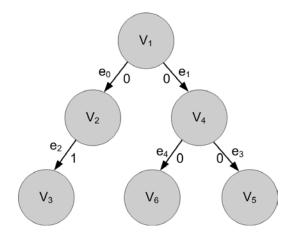

| 4.3    | An allocated DFG                                                                                                 | 48   |

| 4.4    | Two nodes connected by edge $e_k$ . Node $v_s$ precedes node $v_d$                                               | 48   |

| 4.5    | ALU merging resulting in an unplaceable schedule                                                                 | 56   |

| 4.6    | Oz implementation for initializing allocation problem.                                                           | 57   |

| 4.7    | Oz implementation for imposing distinct constraints on MAC and RF                                                | 59   |

| 4.8    | Oz implementation for imposing distinct constraint on ALU.                                                       | 60   |

| 4.9    | Oz implementation for initializing scheduling algorithm.                                                         | 62   |

| 4.10   | Oz implementation for imposing precedence constraints on ALU type nodes.                                         | 63   |

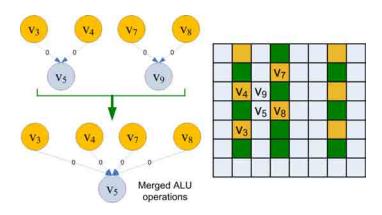

| 4.11 | Oz implementation to prohibit two MACs from being NN                                                                                                        | 63  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.12 | Oz implementation for limiting two RFs from being NN                                                                                                        | 64  |

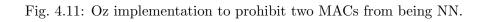

| 4.13 | Distribution strategy for scheduling                                                                                                                        | 66  |

| 5.1  | Assigning Cartesian coordinates to silicon objects.                                                                                                         | 68  |

| 5.2  | Silicon object locations and corresponding $SO_{id}$                                                                                                        | 70  |

| 5.3  | Nearest neighbor input and output                                                                                                                           | 73  |

| 5.4  | Party line communication - four hops in one clock cycle                                                                                                     | 74  |

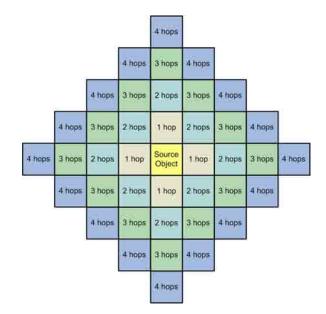

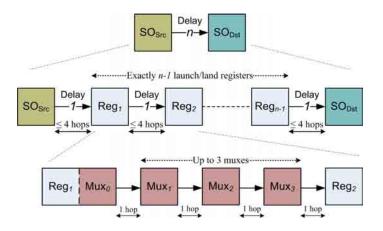

| 5.5  | Route with $n$ clock cycle delay                                                                                                                            | 75  |

| 5.6  | Creating and initializing finite domain variables for placement problem. $\ . \ .$                                                                          | 80  |

| 5.7  | Narrowing domains by removing invalid unique identifier values                                                                                              | 82  |

| 5.8  | Imposing distinct constraint on $v_{-id}$ FD variables                                                                                                      | 82  |

| 5.9  | Proximity constraints                                                                                                                                       | 84  |

| 5.10 | Additional proximity constraints                                                                                                                            | 87  |

| 5.11 | Oz implementation for introducing additional proximity constraints                                                                                          | 87  |

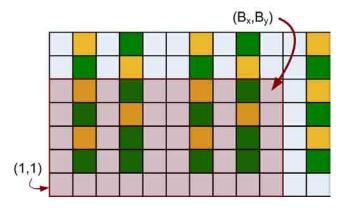

| 5.12 | Limiting search area using a bounding box                                                                                                                   | 88  |

| 5.13 | Using a bounding box to reduce search space                                                                                                                 | 89  |

| 5.14 | Distribution strategy for placement.                                                                                                                        | 91  |

| 6.1  | Register and multiplexer orientations.                                                                                                                      | 94  |

| 6.2  | Routing a path with delay $n$                                                                                                                               | 97  |

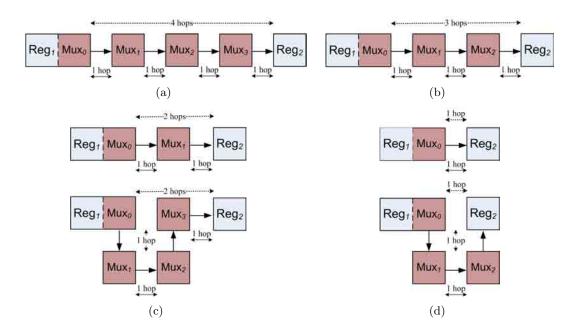

| 6.3  | Routing paths for (a) four hops, (b) three hops, (c) two hops, and (d) one hop long path segments. Possible alternative paths are also shown in (c) and (d) | 98  |

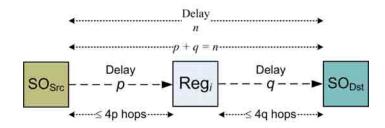

| 6.4  | A launch and land register $i$ along a path with delay $n$                                                                                                  | 99  |

| 6.5  | Possible locations of adjacent multiplexers in a connected multiplexer pair.                                                                                | 102 |

| 6.6  | Launch register and $Mux_0$ orientation.                                                                                                                    | 103 |

xiii

| 6.7  | Initializing finite domain variables for all launch and land registers in a single path                         | 108  |

|------|-----------------------------------------------------------------------------------------------------------------|------|

| 6.8  | Proximity constraints for consecutive launch and land registers in a path.                                      | 109  |

|      |                                                                                                                 |      |

| 6.9  | Initializing finite domain variables for all multiplexers in a path segment.                                    | 110  |

| 6.10 | Distribution strategy for routing                                                                               | 113  |

| 7.1  | Zero delay edges vs. non-zero delay edges                                                                       | 118  |

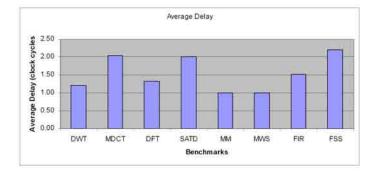

| 7.2  | Average delay (does not include zero delay edges)                                                               | 119  |

| 7.3  | Node reduction due to ALU operation merging                                                                     | 120  |

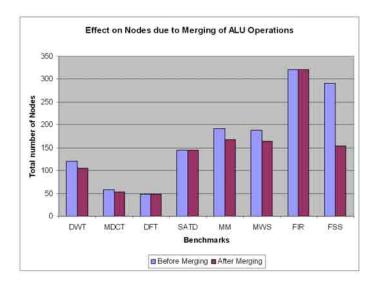

| 7.4  | Edge reduction due to ALU operation merging                                                                     | 120  |

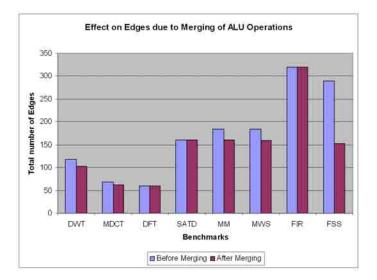

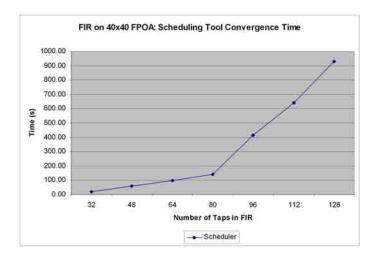

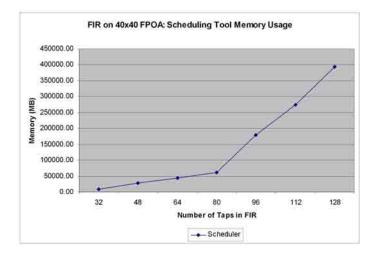

| 7.5  | Scheduling tool convergence time                                                                                | 121  |

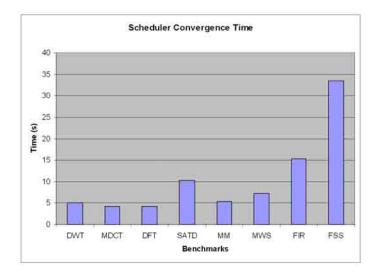

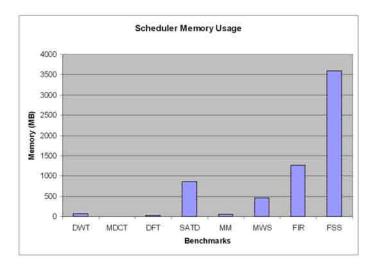

| 7.6  | Scheduling tool memory usage                                                                                    | 121  |

| 7.7  | Scheduling tool distribution and backtracks                                                                     | 122  |

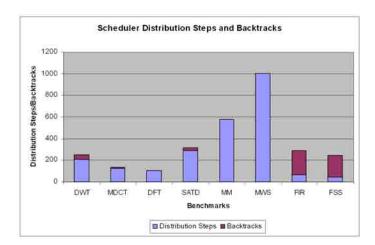

| 7.8  | Placement tool convergence time                                                                                 | 124  |

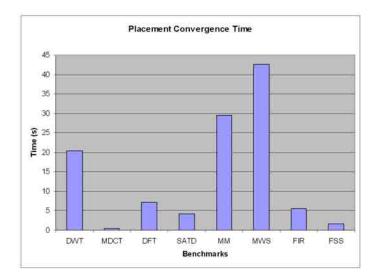

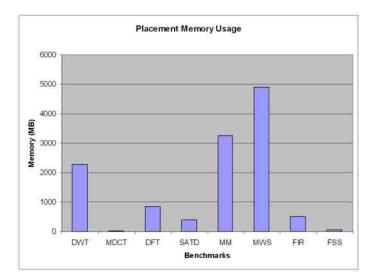

| 7.9  | Placement tool memory usage                                                                                     | 124  |

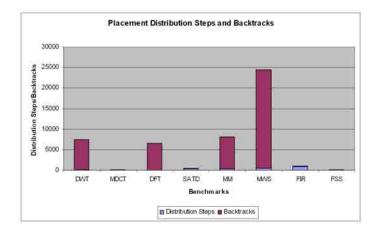

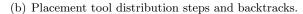

| 7.10 | Placement tool distribution and backtracks                                                                      | 125  |

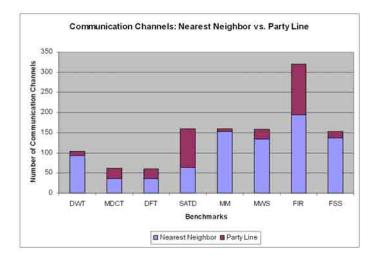

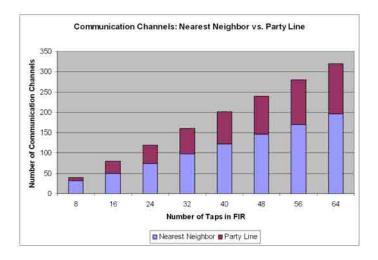

| 7.11 | Zero delay (NN) and non-zero delay (PL) communication channels                                                  | 130  |

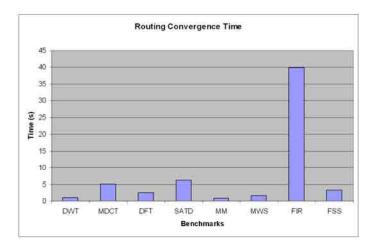

| 7.12 | Routing tool convergence time                                                                                   | 131  |

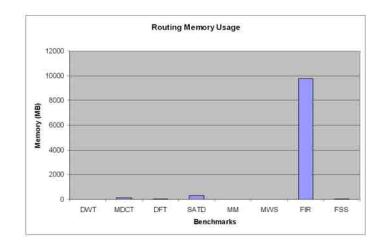

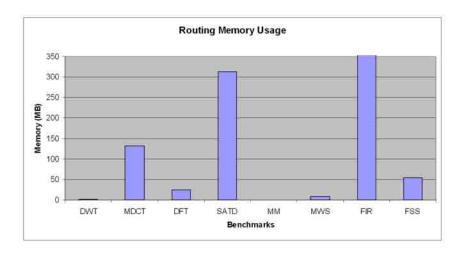

| 7.13 | Routing tool memory usage for all eight benchmarks                                                              | 132  |

| 7.14 | A rescaled view of routing memory usage for all eight benchmarks                                                | 132  |

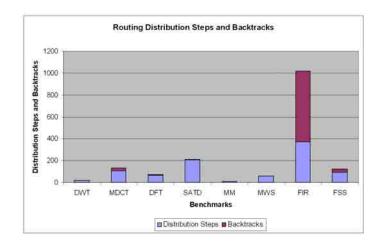

| 7.15 | Routing tool distribution and backtracks.                                                                       | 133  |

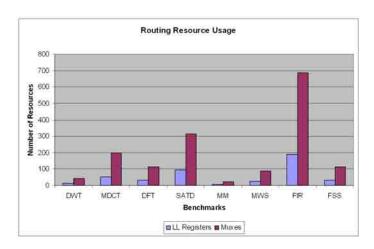

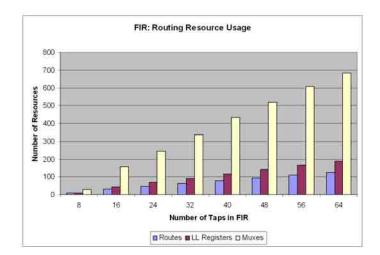

| 7.16 | Routing resource usage: Launch and land registers and multiplexers                                              | 133  |

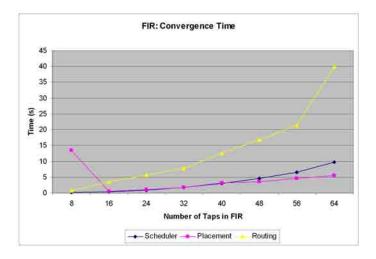

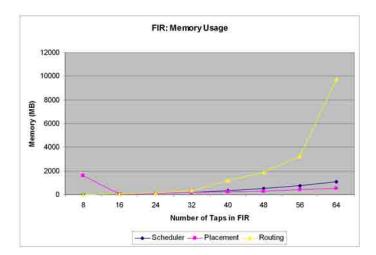

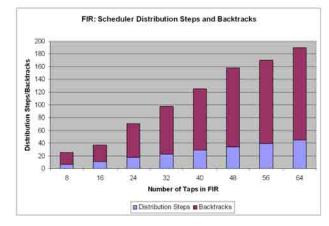

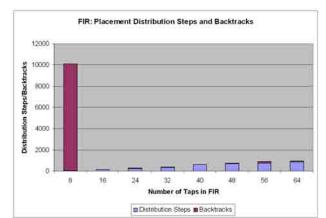

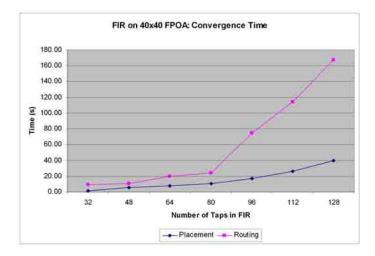

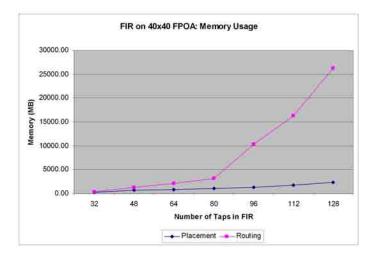

| 7.17 | Search convergence time for FIR configurations                                                                  | 134  |

| 7.18 | Memory usage during scheduling, placement, and routing of FIR configurations                                    | .135 |

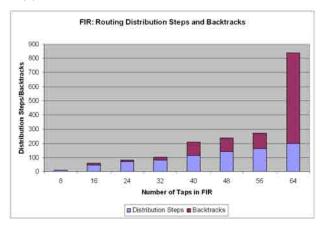

| 7.19 | Distribution steps and backtracks for FIR configurations during (a) scheduling, (b) placement, and (c) routing. | 136  |

| 7.20 | Zero delay and non-zero delay communication channels for FIR configurations                                     | .137 |

| 7.21 | Registers and multiplexers used for routing FIR configurations                                      | 138 |

|------|-----------------------------------------------------------------------------------------------------|-----|

| 7.22 | Scheduling tool search convergence time for FIR configurations on a $40 \times 40$ FPOA             | 138 |

| 7.23 | Scheduling tool memory usage for FIR configurations on a $40\times40$ FPOA                          | 139 |

| 7.24 | Placement and Routing tool search convergence time for FIR configurations on a $40 \times 40$ FPOA. | 139 |

| 7.25 | Placement and Routing tool memory usage for FIR configurations on a $40 \times 40$ FPOA             | 140 |

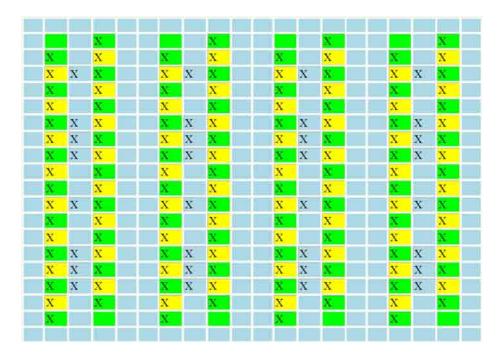

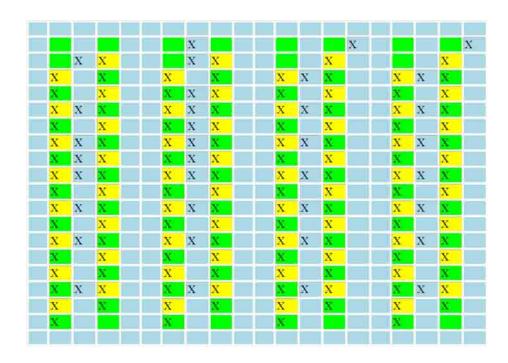

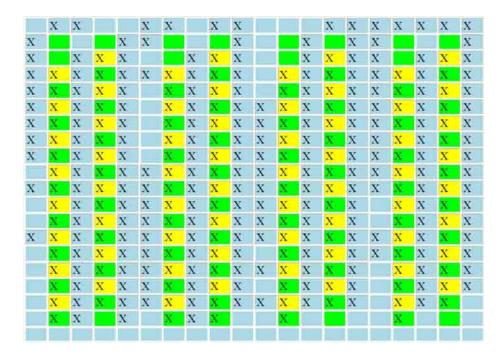

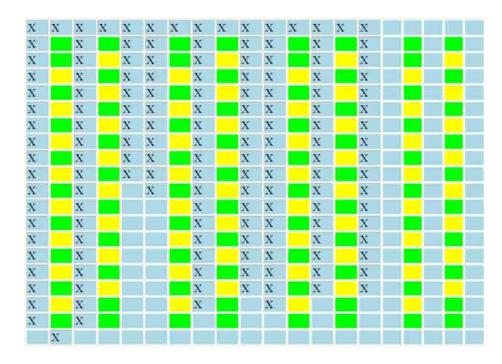

| C.1  | Legend for benchmark layouts.                                                                       | 165 |

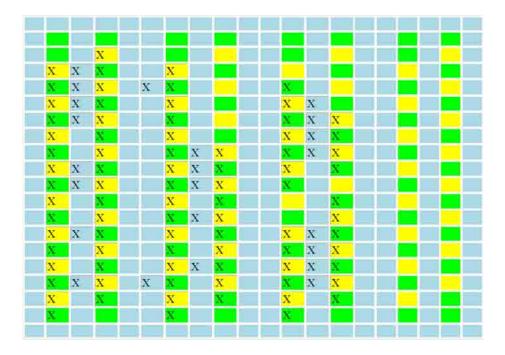

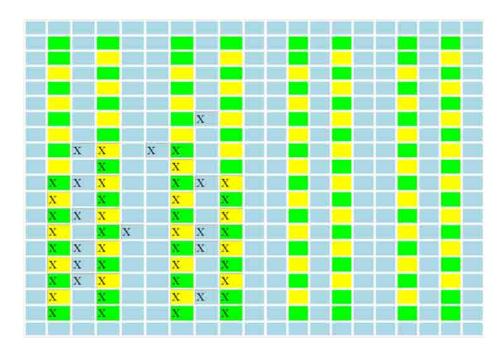

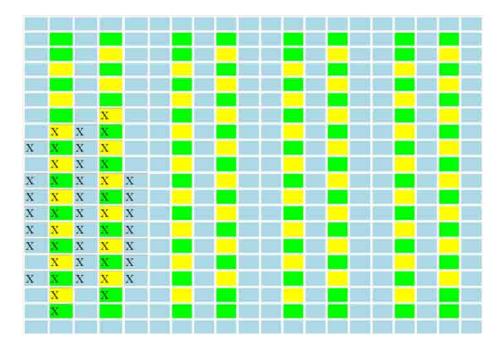

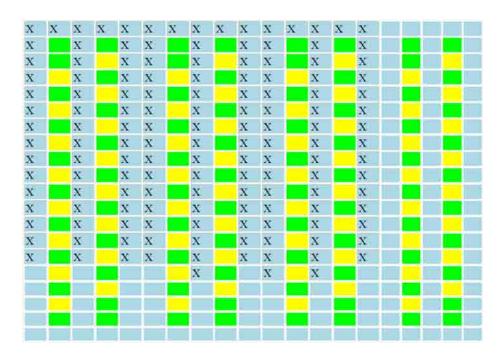

| C.2  | Layout of DWT benchmark.                                                                            | 166 |

| C.3  | Layout of MDCT benchmark.                                                                           | 166 |

| C.4  | Layout of DFT benchmark.                                                                            | 167 |

| C.5  | Layout of SATD benchmark.                                                                           | 167 |

| C.6  | Layout of MM benchmark.                                                                             | 168 |

| C.7  | Layout of MWS benchmark                                                                             | 168 |

| C.8  | Layout of FIR benchmark                                                                             | 169 |

| C.9  | Layout of FSS benchmark                                                                             | 169 |

xv

# List of Algorithms

| Algorit | hm                                     | Page |

|---------|----------------------------------------|------|

| 4.1     | Allocation algorithm                   | 50   |

| 4.2     | Scheduling algorithm                   | 52   |

| 4.3     | Disallow two MACs as nearest neighbors | 53   |

| 5.1     | Placement algorithm                    | 77   |

| 6.1     | Routing algorithm                      | 105  |

# Acronyms

ACM Association for Computing Machinery ADRES Architecture for Dynamically Reconfigurable Embedded Systems ALAP As Late As Possible ALB Arithmetic Logic Block ALU Arithmetic Logic Unit ASAP As Soon As Possible ASIC Application Specific Integrated Circuit BLB **Basic Logic Blocks** BPU **Basic Functional Unit** CFB Configurable Functional Block CGHRA Coarse Grained and Hybrid Reconfigurable Architecture CGRA Coarse-Grained Reconfigurable Architectures CLB Configurable Logic Block CLP Constraint Logic Programming CPE **Configurable Processing Element** DFG Data Flow Graph DFT **Discrete Fourier Transform** DMA **Direct Memory Access** DP **Data** Ports DP-FPGA Data Path Field Programmable Gate Array DPU Data Processing Unit DSP **Digital Signal Processing** DWT **Discrete Wavelet Transform** ECA **Elemental Computing Array**  $\mathbf{FB}$ Frame Buffer

| FD    | Finite Domain                                     |

|-------|---------------------------------------------------|

| FIFO  | First In First Out                                |

| FIR   | Finite Impulse Response                           |

| FPCA  | Field Programmable Computing Array                |

| FPGA  | Field Programmable Gate Array                     |

| FPOA  | Field Programmable Object Array                   |

| FPR   | Field Programmable Gate Array Place and Route     |

| FSS   | Five Step Search                                  |

| GA    | Genetic Algorithm                                 |

| GNU   | GNU is Not Unix                                   |

| GSL   | GNU Scientific Library                            |

| HPWL  | Half Perimeter Wire Length                        |

| IEEE  | Institute of Electrical and Electronics Engineers |

| IFU   | Interconnect Functional Unit                      |

| ILP   | Instruction Level Parallelism                     |

| LL    | Launch/Land                                       |

| MAC   | Multiply Accumulate                               |

| MB    | Mega Bytes                                        |

| MDCT  | Modified Discrete Cosine Transform                |

| MI    | Memory Interface                                  |

| MILP  | Mixed Integer Linear Programming                  |

| MM    | Matrix Multiplication                             |

| MP3   | Moving Picture Experts Group Layer-3 Audio        |

| MTAP  | Multi Threaded Array Processor                    |

| MSMSM | Multi-Source Multi-Sink Maze                      |

| MWS   | MP3 Window Subband                                |

| NN    | Nearest Neighbor                                  |

| NoC   | Network-on-Chip                                   |

| P&R                 | Place and Route                                       |

|---------------------|-------------------------------------------------------|

| PE                  | Processing Element                                    |

| PL                  | Party Line                                            |

| POWV                | Possible Optimal Wire length Vector                   |

| RAM                 | Random Access Memory                                  |

| RAP                 | Reconfigurable Arithmetic Processing                  |

| RAW                 | Reconfigurable Architecture Workstation               |

| RBI                 | Routing Based Interleaving                            |

| RC                  | Reconfigurable Cells                                  |

| REMARC              | Reconfigurable Multimedia Array Coprocessor           |

| $\operatorname{RF}$ | Register File                                         |

| RPU                 | Reconfigurable Processing Unit                        |

| RSA                 | Rectilinear Steiner Arborescence                      |

| $\mathbf{SA}$       | Schedule Analyzer                                     |

| SAP                 | Simulated Annealing-Based Placement                   |

| SATD                | Sum of Absolute Transformed Difference                |

| SDP                 | Spreading Data Path                                   |

| SIMD                | Single Instruction Multiple Data                      |

| TDFG                | Timed Data Flow Graph                                 |

| TIERS               | Topology Independent Pipelined Routing and Scheduling |

| VLIW                | Very Large Instruction Word                           |

| VLSI                | Very Large Scale Integration                          |

| VPR                 | Versatile Place and Route                             |

| WDM                 | Wiring Distribution Maps                              |

# Chapter 1

# Introduction

Over the last few decades, computing needs have outgrown what general-purpose microprocessor devices can offer. Higher transistor density, smaller feature size, and increased clock frequencies have made microprocessors far more advanced than their predecessors. In spite of these improvements in computing technology, modern applications are becoming increasingly complex, necessitating the growth of high performance computing architectures. In order to target specific computing needs, the concept of Application Specific Integrated Circuits (ASICs) was introduced. ASICs are integrated circuits intended for specialized applications and they typically consolidate multiple functions into a single, high-speed device. However, despite their advantages, ASICs are limited to a specific target application and have limited flexibility and usability in other applications.

Field Programmable Gate Arrays (FPGAs) are at the opposite end of the Very Large Scale Integration (VLSI) spectrum, offering bit-level configurability. FPGAs are devices that consist of Configurable Logic Blocks (CLBs) and switch blocks. CLBs can be programmed to implement logic functions and multiple CLBs can be connected through configurable switch blocks and routing channels. The functionality of a FPGA can be modified at a later stage by reconfiguring the device. Bit-level granularity and reconfigurability makes FPGAs flexible for design prototyping and for applications that require in-field functional modifications. However, the flexibility of FPGAs comes at the price of large routing area overhead.

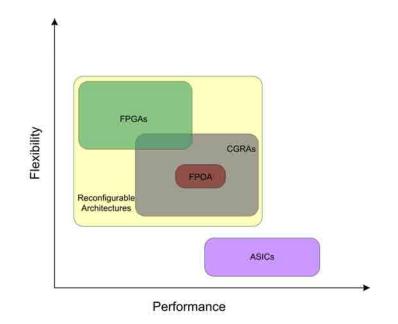

Coarse-Grained Reconfigurable Architectures (CGRAs) are reconfigurable devices which offer wider pathwidths than FPGAs and more flexibility than ASICs. In the VLSI spectrum, CGRAs are placed between ASICs and FPGAs due to their wider data paths, efficient coarse-grained Configurable Functional Blocks (CFBs), and fewer routing resources. Due to these features, CGRAs offer ASIC-like computing power along with FPGA-like configurability. Figure 1.1 offers a relative comparison of flexibility and performance of various computational architectures.

In spite of these differences, a design must be placed and routed on the chip prior to use. Placement is the process of determining exact locations of circuit elements inside a chip's area. Once placement is complete, the circuit components must be connected. The procedure of establishing interconnections among the placed circuit components is called routing. Placement and routing are therefore common steps in the design flow of ASICs, FPGAs, and CGRAs.

The quality of placement and routing has a significant impact on the performance of a design. A poor placement can render a design unroutable or may lead to violations of performance requirements during routing. Even with a good placement, inefficient routing can impair the performance of an implemented design. Place and Route (P&R) techniques have received much attention in the past few decades and several methods have been proposed, a sampling of which is discussed in Chapter 2. Though some of these techniques can be applied to CGRAs, the objectives of placement and routing are different for CGRAs as

Fig. 1.1: Flexibility vs. performance for different types of architectures.

compared to the other two architectures.

#### 1.1 Motivation of this Research

The performance of a design on an ASIC or FPGA is dependent on the path delay, which in turn is dependent on the wirelength of the critical path. Placement tools for ASIC/FPGA try to place the design such that the routing wirelength is minimized. This phase is important because a bad placement may prohibit the router from finding short paths, or in the worst case, may yield an unroutable design. Hence, significant emphasis is given on finding a good placement. However, the placement tool must be able to obtain some routability estimate to generate a good placement. Wirelength estimation is often used as the metric for guiding the placement process since it directly impacts the delay and is used in a variety of tools [1–3]. The same is not the case with CGRAs, such as the Field Programmable Object Array (FPOA). The interconnect network of an FPOA has deterministic timing with a predefined relation between wire segments and delay. Unlike ASICs and FPGAs, in CGRAs such as the FPOA, it is not the wirelength that decides the delay, but it is the delay that determines the wirelength. Hence, wirelength minimization is not the correct approach to solve the FPOA P&R problem.

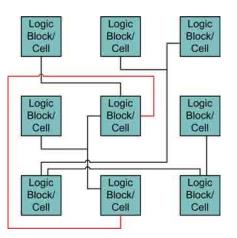

Figures 1.2 and 1.3 illustrate the difference between the routing objectives of ASIC/ FPGA and FPOA. In fig. 1.2, each logic block must be placed such that the length of a route

Fig. 1.2: ASIC/FPGA placement and routing objective.

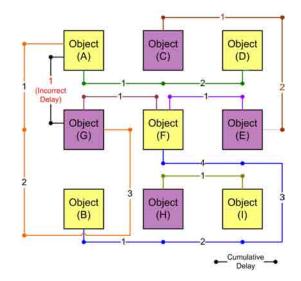

Fig. 1.3: FPOA placement and routing objective.

connecting any two logic blocks can be minimized, and routing complements placement by favoring the shortest candidate paths. In contrast, delay satisfaction takes precedence over wirelength minimization in FPOA P&R. Figure 1.3 shows a post P&R design on an FPOA with possible routes between various objects. Routes between object pairs (G, F), (F, E), and (H, I) have a unit delay which is satisfied by the shortest connections between the respective object pairs. However, if the input specification mandates a delay of three units between object pair (A, G), then the shortest connection offers an incorrect delay of one unit and results in an invalid route. Instead, a correct solution must use a longer route with a delay of three units between A and G.

Further, the source in both cases is different. A Steiner tree [4], or a routing graph, is the starting point for most P&R tools. Steiner trees offer the advantage of minimum total wirelength, which is a desirable goal in standard P&R. Moreover, in FPOA-based P&R, the timing of the input graph has already been established and is provided in the form of a scheduled Data Flow Graphs (DFG). Each node in a scheduled DFG is associated with a processing element or resource, and every edge is annotated with the required communication delay along that edge. Unlike ASIC/FPGA, where interconnect wirelength is minimized and the critical edge decides how fast the design operates, the length of an interconnect in an FPOA is constrained to fall within an interval  $[min\_length, max\_length]$ , determined by the delay requirement imposed by the schedule. The problem is no longer to find the shortest path, but to find a path with length  $\ell$ , such that  $min\_length \leq \ell \leq max\_length$ . Any value of wirlength that falls within these bounds is acceptable, since all such paths will support the required delay.

The P&R problem is further complicated by the heterogeneity of an FPOA. Unlike FPGAs, where all CLBs are identical, the processing elements in an FPOA perform different logical functions. The placement must not only conform to the routing delay, but must also assign the operations to the correct processing element. The placement problem can be interpreted as a one-on-one assignment of a finite set of operations in a DFG to a finite set of processing elements, where the assigned processing element is capable of performing the operation assigned to it. Similarly, the routing problem translates into a search for a set of n switch blocks, where n is the path delay, such that the n switch blocks establish a route between source and sink processing elements. The distance between any two switch blocks is further restricted by the maximum distance necessary for executing the design at a predetermined clock rate.

Furthermore, the type of decisions required for placing and routing a design on an FPOA is different than for FPGAs. For example, a Xilinx Virtex II Pro XC2VP100 FPGA chip has 11280 CLBS (= 44096 slices = 88192 LUTs and 88192 FFs) and approximately 11067 switch boxes [5]. Even if the problem is simplified to a one-on-one assignment of operations to CLBs, there are 11280! ways in which the design can be placed. Considering a channel width W = 4 bits, 398412 transistors must be configured during the routing phase. But, for an FPOA, a placement tool deals with 400 coarse-grained objects, and a total of 4000 multiplexers, 2000 launch/land registers, and 1600 nearest neighbor registers must be configured to route a design. The FPOA's heterogeneity further reduces the number of assignment permutations during place and route phase. However, the place and route decisions for FPOAs are driven by design-dictated communication delay. Thus, even though the cardinality of the FPOA resource set is typically lower than an FPGA resource set, the

resource allocation in CGRAs must adhere to the design's timing schedule, requiring a time-aware approach that is not offered by traditional P&R. The temporal nature of FPOA P&R warrants a method that explicitly deals with time.

The apparent differences between P&R for FPOA vs. ASIC/FPGA necessitates a fresh perspective towards FPOA placement and routing. New objective functions are needed to drive the search for finding appropriate solutions. This research explores and identifies such search objectives, and proposes a finite domain constraint satisfaction-based placement and routing approach for FPOAs. While the FPOA placement and routing problems are conceptually different than operation scheduling, they both can be formulated as problems, similar to scheduling.

Finite domain constraints have been applied to solve scheduling problems but their application to solving a P&R problem remains an unexplored area. Following is the theme of the work presented in this dissertation:

It is possible to develop a finite domain constraint satisfaction methodology to schedule, place, and route a design on an FPOA that minimizes schedule length, communication delay, area, and routing resources.

#### **1.2** Research Contributions

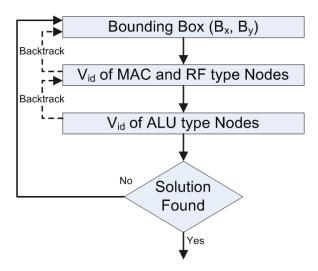

The FPOA belongs to the category of 2-dimensional (2D) mesh CGRAs and its intricate details are described later in Chapters 2 and 3. This dissertation discusses the development of a P&R tool for the FPOA. The proposed FPOA tool flow is shown in fig. 1.4. During the initial phase, a design specification in the form of a DFG is translated into a Timed Data Flow Graph (TDFG) through a resource allocation and operation scheduling procedure. A high-level architecture specification of an FPOA is used as the target platform for placing the design represented by this TDFG. Next, the design is placed and routed using finite domain constraint-based placement and routing algorithms. It is possible that a placed design is not routable, in which case the placement step is repeated. If new placements are also not routable, reallocation and rescheduling of the input DFG generates a new RCG for place and route.

Fig. 1.4: Proposed FPOA tool flow.

The contributions of this research include:

- A simultaneous resource allocation and operation scheduling of a DFG using finite domain constraint satisfaction;

- Development of a constraint satisfaction methodology for placement of design on an FPOA;

- Development of a routing algorithm for FPOA using finite domain constraints;

- Evaluation of placement and routing methodology using scientific applications, multimedia, and signal processing benchmarks.

# 1.3 Overview of This Document

This dissertation discusses the development of multiple design tools to facilitate the implementation of a design on an FPOA. Chapter 2 outlines various coarse-grained recon-

figurable mesh architectures reported in surveyed literature along with a brief overview of search techniques. It also includes a list of various placement and routing techniques developed for ASICs, FPGAs, and CGRA design flows. Chapter 3 reviews the fundamental concepts used in this research, such as FPOA architecture, finite domain constraint satisfaction, and the Oz/Mozart tool. The methodology for allocating resources and scheduling a DFG to generate an RCG is described in Chapter 4. Chapter 5 delves into the description of a finite domain constraint solution for FPOA placement, elaborating on a mathematical model from which the placement solution is derived. The constraint satisfaction-based routing methodology is discussed in Chapter 6. Chapter 7 presents an overview of the test cases used for evaluating and demonstrating this research effort. The same chapter also presents the results for all the test cases after allocation, scheduling, placement, and routing phases. Chapter 8 concludes the dissertation and discusses future directions of research as related to this topic.

# Chapter 2

# **Related Work**

Place and route steps are vital for VLSI design. Existing literature reports a plethora of placement and routing techniques that have been developed for different architectures. In the case of ASIC design, the P&R step decides the final architecture, but the scenario is different for FPGAs and CGRAS where the architecture is fixed. In both of these cases, a search technique forms the core of the P&R algorithm. This chapter surveys several meshbased CGRAs, search techniques, and provides an overview of the various techniques that have been reported for P&R of applications targeting ASICs, FPGAs, and CGRAs.

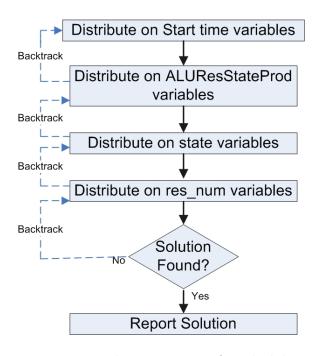

#### 2.1 2D Mesh Coarse-Grained Reconfigurable Architectures

2D mesh architectures are characterized by a Manhattan arrangement of Processing Elements (PEs) that communicate using horizontal and vertical connections. Typically, two types of interconnect mechanisms are used: nearest-neighbor links and long-distance links. The nearest-neighbor links allow a PE to communicate with eight adjacent PEs corresponding to the eight directions. To connect distant PEs, interconnect segments of various lengths are used with varying interconnect data paths ranging from 1 bit to larger widths depending on the architecture. Various mesh-style coarse-grained architectures are discussed below.

#### Data Path-FPGA

Cherepacha and Lewis introduced an architecture similar to an FPGA but with coarsegrained features [6]. This new architecture, called Data Path FPGA (DP-FPGA), combines the flexibility of fine-grained programmability with the advantages of data path regularity, and is intended for use in data path intensive designs, such as digital signal processing, communications, circuit emulation, and special-purpose processor applications. A design is implemented on a DP-FPGA using Chortle [7] and Hill's algorithm [8].

# Kress Array

Introduced by Hartenstein and Kress [9], the reconfigurable Data Path Architecture (rDPA), currently known as the KressArray architecture, is a 2D grid of identical reconfigurable Data Path Units (DPUs), that are connected using a mesh of interconnects. Each DPU is composed of an ALU to perform standard arithmetical and logical operations, and a microprogrammable control unit for more complex operations such as division.

## **D-Fabrix**

The D-Fabrix architecture is an array of 4-bit ALUs, multiplexers, registers, and memory, which are connected through a mesh network configurable by using routing switches [10]. The hierarchical architecture consists of tiles that are composed of two demi-tiles, each containing an ALU, three registers, two multiplexers, and one switchbox. One of the salient features of D-Fabrix is that data is kept local to the processing elements to minimize data transfers, thus reducing power consumption.

## Colt

Unlike FPGAs, Colt architecture [11,12] is designed to operate on 16-bit words. Primarily targeted towards signal processing applications, Colt supports run-time reconfiguration and uses wormhole routing for communication between functional units. The architecture consists of 16-bit Interconnect Functional Units (IFUs), Data Ports (DP), crossbars, and a multiplier.

# MATRIX

MATRIX is an 8-bit architecture and is comprised of identical Basic Functional Units (BFUs) which are connected using a hierarchical interconnect network [13]. MATRIX has a three-level hierarchical interconnect network - the lowest level with zero clock cycle communication delay, the second level with length of four bypass interconnect, and the top-most level with global lines for long connections.

## Garp

Garp [14] is a hybrid architecture that combines the merits of a conventional microprocessor with a reconfigurable computation unit. The main processor in Garp is built around the MIPS-II instruction-set with additional instructions to configure and execute the reconfigurable array.

# FIPSOC

A FIPSOC chip [15,16] consists of an 8051 microcontroller core, an FPGA, configurable analog circuit block, on-chip memory, configuration memory, and I/O subsystem. User applications execute on the microcontroller, which interfaces with the FPGA and the analog circuit block to enhance its computing power.

## RAW

Reconfigurable Architecture Workstation (RAW) shifts away from trends commonly applied in superscalar processor design [17–19]. The RAW architecture simplifies the hardware by moving many of the tasks to development software. The architecture consists of identical processing elements called tiles, connected as a homogeneous array. Data travels a short distance, from one tile to another, instead of using long communication network, resulting in higher clock-speed and increased scalability of the design.

# REMARC

Reconfigurable Multimedia Array Coprocessor (REMARC) [20] consists of 64 processing elements called nanoprocessors arranged in an 88 matrix. The nanoprocessors communicate with their immediate neighbors using dedicated nearest neighbor connectivity and with those in the same row or column using 32-bit horizontal or vertical buses. REMARC is tightly coupled to a MIPS RISC processor, whose ISA has been extended to configure and execute instructions on REMARC.

# **IRAM Architecture**

The Intelligent RAM or IRAM architecture takes advantage of the low-latency and high bandwidth available on the memory chip [21,22]. The architecture consists of memory chips that act as regular DRAM but includes an array of processors and a floating point unit, making them different from conventional RAM architectures. By having sufficiently large memory, enough data can be loaded onto the memory to perform in-situ computation, decreasing the off-chip data traffic.

## **CHESS** Array

Hewlett Packard laboratories proposed a reconfigurable arithmetic array, called CHESS, consisting of 4-bit ALUs, switchboxes, interconnection buses, and embedded block RAMs [23]. The routing structure consists of 16 segmented 4-bit buses in each row and column of the reconfigurable array. The routing occupies 50% of the array area, which is considerably less than most FPGAs.

## MorphoSys

The Morphoing System (MorphoSys) is a reconfigurable processor array which includes an array of 16-bit reconfigurable cells (RCs) that is controlled by a 32-bit TinyRISC processor [24–27]. The RC array consists of 64 identical RCs or processing elements that are arranged symmetrically in an  $8 \times 8$  matrix. This matrix is further split into four  $4 \times 4$  quadrants. A hierarchical three-level interconnection network allows the RCs to access data from other RCs. The architecture also incorporates a context memory to save the configuration data, a Frame Buffer (FB), and a direct memory access (DMA) controller.

## **DReAM** Array

Dynamically reconfigurable architecture for mobile systems (DReAM) is comprised of a

2D mesh of 16-bit processing elements called the reconfigurable processing unit (RPU) [28]. The RPU is responsible for all application specific data-flow and control-flow operations. It consists of two 8-bit reconfigurable arithmetic processing (RAP) units, one Spreading Data Path (SDP), one RPU-controller, two dual port RAMs, and a communication protocol controller. RPUs communicate with adjacent RPUs through a 16-bit fast local interconnect and use 16-bit global buses for long distance communication.

#### MONARCH

MOrphable Networked micro-ARChitecture (MONARCH) is a heterogeneous parallel processor which combines six 32-bit 5-stage pipeline RISC processors with a Field Programmable Compute Array (FPCA) [29, 30]. A high-bandwidth dynamic switched interconnect aids in data transfer among neighboring FPCA elements. The FPCA design is optimized for streaming data and signal processing application, and can be configured to implement a 256-bit wide SIMD engine.

# ADRES

Mei et al. [31, 32] have proposed an architecture called Architecture for Dynamically Reconfigurable Embedded System (ADRES). The ADRES architecture has two components: a VLIW processor and a coarse-grained reconfigurable matrix, which are coupled as a processor and a co-processor. The VLIW processor exploits Instruction Level Parallelism (ILP) while the reconfigurable matrix improves the performance by exploiting the parallelism.

#### Field Programmable Object Array

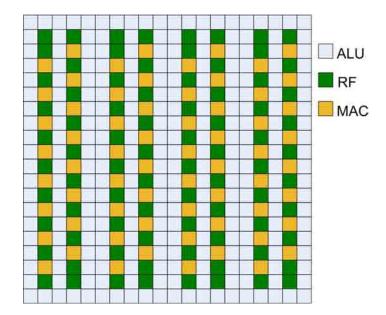

Mathstars Field Programmable Object Array (FPOA<sup>TM</sup>) is a coarse-grained heterogeneous reconfigurable computing platform consisting of coarse-grained silicon objects which communicate though a configurable communication network. The Arrix family [33] is the current generation of FPOA and consists of 400+ silicon objects. Chapter 3 describes FPOA architecture in detail.

# ClearSpeed CSX Family

ClearSpeeds CSX family of processors is built on top of a multi-threaded array processor (MTAP) core to support parallel data processing [34, 35]. The architecture of an MTAP processor has a highly parallel execution unit instead of single ALU, register file, and I/O device configuration. The execution unit contains a mono execution unit for processing scalar data while the poly execution unit contains a large number of poly execution (PE) cores. Each PE core has an ALU, a floating point unit, a multiple-accumulate unit, a register file, memory, status and enable registers, I/O channels, and paths for inter-PE communication.

#### **Coarse-Grained Hybrid Reconfigurable Architecture**

Verma and Akoglu have proposed a Coarse-Grained and Hybrid Reconfigurable Architecture (CGHRA) [36] targeted for applications like variable block size motion estimation used in H.264 video compression standard [37,38]. The architecture contains 16 configurable processing elements (CPEs), four processing elements of type-2 (PE2s), two processing elements of type-3 (PE3s), and a memory interface (MI). A network-on-chip (NoC) provides the communication backbone to these PEs.

## **Element CXI Elemental Computing Array**

Element CXI is an Elemental Computing Array (ECA), consisting of non-homogeneous, pipelined computational engines called elements [39]. Each element has four 16-bit inputs, two 16-bit outputs, a controller called Judge, and an associated context. Due to its hierarchical interconnect and run-time task binding, Element CXI does not fall under the target architecture domain of this dissertation.

# TILE<sup>TM</sup> Multicore Processor Architecture

Tilera® Corporation has developed a family of tile-based multicore processor architectures which include TILE64, TILEPro36, TILEPro64, and most recently the TI-LEGx [40–42]. These processors feature a multicore architecture ranging from 36 identical tiles in TILEPro36 to 100 tiles in TILE-Gx. All the tiles communicate through Tileras  $iMesh^{TM}$ on-chip network [43]. A multicore development environment facilitates tile processor programming using a C/C++ compiler.

#### SmartCell

SmartCell is a coarse-grained reconfigurable architecture targeting stream-based applications [44]. The architecture consists of processing elements operating on 16-bit inputs to generate 36-bit outputs, and includes input registers, an arithmetic and logic unit, instruction memories, instruction controllers, and multiplexers. The prototype contains 16 cells which are tiled in a 2D mesh structure and communicate through a three-level layered interconnect network.

# Summary of 2D Mesh CGRAs

Table 2.1 summarizes the architectures described earlier in this section. Architecture and granularity columns illustrate the name and the granularity of an architecture. Granularity is defined as the data path width of an architecture and multiple entries under granularity indicate a multi-granular architecture. The third column displays the nature of the routing network: static and/or dynamic, channel-width specifies the number of parallel wires in the interconnect and can differ from an architectures granularity, and processing element denotes the type of fundamental processing unit(s) used in the architectures. A Y in column six indicates if any design tools for an architecture have been reported, while an N denotes its absence. An asterisk (\*) indicates that the tool is a proprietary too. Finally, the last column displays the year in which an architecture was reported, and Table 2.2 lists any design tools reported for architectures mentioned in Table 2.1.

#### 2.2 Search Techniques

Several search techniques have been reported in the literature which include integer linear programming, evolutionary algorithms, simulated annealing, and constraint satisfaction.

Table 2.1: Summary of coarse-grained reconfigurable architectures. A \* indicates proprietary tools.

| Architecture | Granul- | Routing | Channel          | Processing     | Design | Year |

|--------------|---------|---------|------------------|----------------|--------|------|

|              | arity   | Network | $\mathbf{Width}$ | Element        | Tools  |      |

| DP-FPGA      | 4-bit   | Static  | 4-bit            | LUT            | Y      | 1994 |

| Kress Array  | 32-bit  | Static  | 32-bit           | rDPU/ALU       | Y      | 1995 |

|              |         | Dynamic |                  |                |        |      |

| D-Fabrix     | 4-bit   | Static  | 4-bit            | ALU            | Y*     | 1995 |

|              |         | Dynamic |                  |                |        |      |

| Colt         | 16-bit  | Dynamic | 16-bit           | IFU/ALU        | N      | 1996 |

| MATRIX       | 8-bit   | Static  | 8-bit            | BFU/ALU        | N      | 1996 |

|              |         | Dynamic |                  | Control Logic  |        |      |

| Garp         | 2-bit   | Static  | 2-bit            | LUT Clusters   | Y      | 1997 |

|              |         | Dynamic |                  |                |        |      |

| FIPSOC       | 4-bit   | Static  | 4-bit            | Microprocessor | Y      | 1997 |

|              | 8-bit   |         |                  | Digital Cells  |        |      |

|              | 9-bit   |         |                  | Analog Cells   |        |      |

| RAW          | 32-bit  | Static  | 32-bit           | RISC processor | Y      | 1997 |

| REMARC       | 16-bit  | Static  | 16-bit           | Nanoprocessors | Y      | 1998 |

|              |         |         | 32-bit           |                |        |      |

| IRAM         | 8-bit   | Static  | N/A              | ALU            | N      | 1998 |

|              |         |         |                  | RISC processor |        |      |

| CHESS        | 4-bit   | Static  | 4-bit            | ALU            | Ν      | 1999 |

| MorphoSYs    | 16-bit  | Static  | 16-bit           | Multiplier-ALU | Y      | 1999 |

| DReAM        | 8-bit   | Static  | 16-bit           | RPU            | N      | 2000 |

| MONARCH      | 32-bit  | Dynamic | 32-bit           | RISC processor | Y*     | 2002 |

|              |         |         |                  | Multiplier-ALU |        |      |

| ADRES        | 32-bit  | Static  | 32-bit           | ALU            | Y      | 2003 |

| FPOA         | 16-bit  | Static  | 21-bit           | ALU, MAC       | Y*     | 2003 |

|              |         | Dynamic |                  |                |        |      |

| ClearSpeed   | 64-bit  | Static  | 64-bit           | ALU            | Y*     | 2006 |

| CGHRA        | 8-bit   | Dynamic | 32-bit           | Subtractors    | N      | 2008 |

|              |         |         |                  | Adders         |        |      |

| SmartCell    | 16-bit  | Static  | 16-bit           | ALU            | Y      | 2009 |

|              |         | Dynamic | 36-bit           |                |        |      |

Dantzig developed a technique called the Simplex method [45,46] to solve linear programs. The concept of linear programming has been extended to Mixed Integer Linear Programming (MILP) [47], which formulates an optimization problem as the minimization or maximization of a cost function, subject to a set of constraints. MILP suffers from limited scalability and has limited expressiveness.

| Architecture | Design Tools Reported in Literature                             |

|--------------|-----------------------------------------------------------------|

| DP-FPGA      | Uses Chortle and Hill's algorithm                               |

| Kress Array  | Data path synthesis system based on Simulated Annealing         |

| D-Fabrix     | Proprietary tools                                               |

| Garp         | Garp Configurator, C compiler-based design flow, Garp simulator |

| FIPSOC       | Proprietary tools                                               |

| RAW          | RAW compiler                                                    |

| REMARC       | REMARC configuration Environment                                |

| MorphoSYs    | Morphosim VHDL simulator                                        |

| MONARCH      | Proprietary tools                                               |

| ADRES        | VHDL synthesis and simulation                                   |

| FPOA         | Proprietary tools                                               |

| ClearSpeed   | Proprietary tools                                               |

| SmartCell    | Smart_C prototype compiler                                      |

Table 2.2: Design tools for CGRAs

Evolutionary algorithms and simulated annealing are combinatorial search techniques and have been used in embedded system design, electronic system level design tools, and ASIC/FPGA placement and routing. Evolutionary algorithms or genetic algorithms model the search space as a population of potential solutions or chromosomes. New generations are created by combining parent chromosomes or by randomly changing the genes within the chromosome. A fitness function evaluates the quality of the population after creating a new generation and discards inferior offsprings. The population grows and improves with each iteration of the process and terminates after a pre-defined number of generations have been created. An evolutionary search problem can be divided into two sub-components: the problem definition and the search algorithm. PISA [48] is an interface specification that allows a problem definition and an evolutionary multi-objective search algorithm to be implemented as separate communicating processes. The PISA framework establishes a formal model that dictates the control flow and data exchange between these two processes. All the communication takes place through text-files, which further allows the two processes to be located on different machines running different operating systems. However, both the processes are required to be PISA compliant. Even though the goal of PISA is multiobjective optimization, PISA is not a search tool but instead, it is an interface specification that enables the user to combine a search problem with an evolutionary search technique to address an optimization problem.

Simulated annealing [49], on the other hand, is a concept that has been borrowed from metallurgy. The problem is modeled as a random and possibly invalid solution state. Random perturbations produce new states, where the frequency and the degree of perturbation is controlled by a parameter called temperature such that the number of random changes decrease as the temperature cools. A new state is accepted if it is better than the existing state, as evaluated using a cost function. The algorithm terminates once the temperature falls below a threshold. For both the above search techniques, the random changes avoid being stuck in local minima. However, neither guarantees a good solution nor ensures full coverage of search space.

Constraint Logic Programming (CLP) is a combination of constraint satisfaction and logic programming [50]. A CLP problem involves a constraint domain, variables, and set of constraints defined over the variables. The constraint domain defines the domain of computation and the set of permissible operations on the values represented by the domain. A typical program for CLP specifies a domain, a set of constraints, and a goal. The constraint solver attempts to prove the goal while satisfying the constraints by assigning values to the variables, where the values lie within the constraint domain. The simplest form of a constraint consisting of a single operation and corresponding number of arguments is called a basic constraint. Complex constraints can be expressed as a conjunction of multiple basic constraints.

Finite Domain (FD) constraints are a field of CLP such that the constraint domain is restricted to a finite set of values. The constraint domain is restricted to non-negative integers and permits integral as well as Boolean operations. FD constraints facilitate the representation of, and solution for, discrete search problems [51]. FD constraint programming has been applied to high-level synthesis [52], static scheduling of real-time systems [53], and design space exploration [54].

# 2.3 Placement and Routing Techniques

Several placement and routing techniques have been proposed in the literature. These

techniques have been implemented using various search algorithms [55] and target different architectures. Even for the same architecture, the objectives of two P&R methods can be different. The following sections provide an overview of the place and route methodologies used in design flow of ASICs, FPGAs, and CGRAs.

# 2.3.1 P&R for ASICs

P&R is an essential step in the design of an integrated circuit and consists of two phases: Placement and Routing. During placement, the VLSI cells are laid out on the chip layout, such that the cells do not overlap and can be connected through wires as per the design netlist. Once the design is placed, routing phase establishes the actual interconnects among cells. Routing is dependent on placement and a bad placement can result in a nonroutable design. The quality of placement is measured in terms of the cost of placement, which can be the total wirelength, number of cuts, congestion, timing, etc. This cost is calculated using cost functions. The goal of placement is to place the cells while minimizing one or more cost functions.

Minimizing wirelength reduces the congestion and signal delay, while also decreasing the chip area required for routing the wires. Almost all placement tools use some form of wirelength minimization criterion. For minimizing the wirelength during placement, the tool must ideally know the exact routing of wires. Since the placement phase precedes routing, actual routing information is not available. Instead, techniques are used for estimating wirelength for guiding the placement. Typically, a cost function is defined based on some design criteria: such as minimal total-wirelength, penalty for wires longer than a given threshold, etc.

In a 2D mesh network, the shortest interconnect among various nodes is a Steiner tree [55] connection. Measurement and minimization of the rectilinear Steiner tree wirelength is a good objective for placement, but unfortunately it is computationally expensive. During placement, the cost function needs to be evaluated often, because an expensive function results in a slow and unacceptable placement procedure. Since an exact wirelength is not required during placement, alternative techniques for estimating the wirelength may be used. Instead of Steiner tree, other wiring schemes such as minimal spanning tree, chain connections [55], and multi-source multi-sink [56] connections are used. Bounding box or Half Perimeter Wire Length (HPWL) estimation is a popular method for wirelength approximation [57]. For lower degree nets, HPWL gives the exact minimal rectilinear Steiner wirelength.

FLUTE [58] is another approach that uses lookup tables for estimating wirelength for networks with small number of pins. The lookup table consists of possible optimal wirelength vectors (POWVs), where a POWV represents a potential optimal route for a net along Hanan's grid [4]. Possible routing topologies are generated by removing redundant or non-optimal routes from the set to obtain a POWV for each net. For larger degree nets, a divide and conquer approach is used and the nets are subdivided into several nets of smaller degrees.

Dragon2000 [59] is a 2-phase hierarchical iterative placement tool developed for large circuits. In the first/global phase, the area is divided into four bins and the cells are distributed to each bin, followed by subsequent subdivisions. Cell overlap is permitted during this phase with the goal of minimizing both wirelength and min-cut. A greedy algorithm is used for legalizing the placement and reducing wirelength during the second/detailed placement.

Roy and Markov propose that Steiner Tree Wire Length (StWL) correlates better with the routed wirelength than the commonly used half perimeter wirelength [60]. However, building Steiner trees and estimating StWL for each net is computationally expensive and becomes a bottleneck when used in an iterative placement approach. Fast Steiner evaluators such as FastSteiner [61] and FLUTE exist but may still not have reasonable runtimes for large problems. The authors have developed a placement algorithm called ROOSTER [60] based on net weighted StWL estimation. In order to evaluate StWL in a reasonable time, the authors propose the use of an efficient data structure which reduces the execution time for Steiner evaluators.

Min-cut is a partitioning-based placement method where a design is subdivided into

smaller partitions, with the goal that the number of interconnects between partitions is minimized. It is a top-down approach that initially emphasizes global placement. Breuer [62] proposed the first min-cut placement algorithm for physical implementation of electrical circuits: Quadrature placement procedure and Slice/bi-section placement procedure. In the former algorithm, the cut lines alternate between vertical and horizontal. In the latter case, the area is iteratively divided into horizontal slices and elements are assigned to the bottom row at each iteration. Finally, the cells are assigned to the columns using vertical bisection. Lauther [63] suggested cell rotation, squeezing, and reflection to reduce whitespace and improve min-cut placement.

NTUplace [64] is a hierarchical, partitioning-based placement algorithm which uses weighted-nets, ratio partitioning, and look-ahead bi-partitioning to place mixed size cells. The partitioning problem is formulated as a hypergraph partitioning problem with weights assigned to the edges in the hypergraph. The chip area is divided into regions, with blocks assigned to a region, such that the HPWL of the nets is minimized. To determine appropriate cut-size for the regions, higher weights are assigned to larger cells and the resulting weight determines the cut-size.

Capo [65] is an academic min-cut hypergraph partitioning-based placement tool which performs recursive bi-section placement. Capo generates wirelengths comparable to commercial placers and the placed design is usually routable. Kahng and Reda [66] have proposed an iterative placement feedback technique for improving terminal propagation during placement. The idea is to perform a placement step, undo it, and feed the results back into the current step to drive the terminal propagation. The authors have implemented their technique in Capo and have reported HPWL reductions on standard benchmarks.