# Formal verification of dynamically reconfigurable systems

| 著者                | Yanase Ryo, Sakai Tatsunori, Sakai Makoto,  |

|-------------------|---------------------------------------------|

|                   | Yamane Satoshi                              |

| journal or        | 2015 IEEE 4th Global Conference on Consumer |

| publication title | Electronics                                 |

| volume            | GCCE 2015                                   |

| number            | 7398597                                     |

| page range        | 71-75                                       |

| year              | 2016-02-03                                  |

| URL               | http://hdl.handle.net/2297/45586            |

doi: 10.1109/GCCE.2015.7398597

## Formal Verification of Dynamically Reconfigurable Systems

Ryo Yanase \*, Tatsunori Sakai \*, Makoto Sakai \* and Satoshi Yamane <sup>†</sup> \* Graduate School of Natural Science and Technology Kanazawa University, Kakuma-machi 920–1192 Email: ryanase@csl.ec.t.kanazawa-u.ac.jp <sup>†</sup> Institute of Science and Engineering Kanazawa University, Kakuma-machi 920–1192 Email: syamane@is.t.kanazawa-u.ac.jp

Abstract—A dynamically reconfigurable system can perform complicated operations with dynamically changing the configuration. For ensuring the safety of the system, a model checking is one of the efficient formal approach. In our work, we define the specification language of a dynamically reconfigurable system and propose the model checking algorithm of verifying safety properties.

#### I. INTRODUCTION

If a system changes its configuration during the operation, we call it *dynamically reconfigurable system*. The feature of a dynamically reconfigurable system is appeared in many realtime systems (e.g., embedded systems, networks, etc.). Since the operation of a such system is generally complex, it is difficult to guarantee that the system is safe. Model checking is a formal method for verification, and it is one of the effective approach. In our work, we define the specification language *dynamic linear hybrid automaton (DLHA)* of dynamically reconfigurable systems and propose an approach to the model checking of safety properties.

### II. RELATED WORKS

Linear hybrid automaton provides continuous and discrete operations but cannot describe the dynamic change of the configuration[1]. Therefore, the system is modeled as a static system[2]. Dynamic Input/Output automaton describes asynchronous concurrent systems with FIfO channels and also provides the dynamic change as creation and destruction of automata[3]. However, this language doesn't provide continuous transition and cannot describe a real-time system. Hierarchical linear hybrid automaton is based on concepts of object-orientation[4]. For this language, given a large scale system, the specification and the verification method tend to be complex. H. Nakano and others have developed a dynamically configurable processor LSI that the circuit configuration is changed by a single clock[5]. In our work, we assume that a dynamically reconfigurable system can change its configuration by a single clock.

#### III. SPECIFICATION LANGUAGE

We propose a specification language *Dynamic Linear Hybrid Automaton* (DLHA). A DLHA is a hybrid automaton extended by creation/destruction of automata and queue operations.

#### A. Dynamic Linear Hybrid Automaton

A *dynamic linear hybrid automaton*(DLHA) is a linear hybrid automaton extended with special actions that are labels representing the types of transitions.

1) Syntax of a DLHA: A DLHA is a tuple consisting of the following components:

- A finite set L of locations

- A finite set V of variables

- A function *Inv* that assigns a constraint to each location: A constraint  $\phi$  on V is defined by

$$\phi ::= true \mid x \sim e \mid x - y \sim e \mid \phi_1 \land \phi_2$$

where  $x, y \in V$ ,  $e \in \mathbb{Q}$ ,  $\phi_1$  and  $\phi_2$  are constraints on V, and  $\sim \in \{=, <, >, \le, \ge\}$ .  $\Phi(V)$  denotes a set of all constraints on V. For a location  $l \in L$ , a constraint Inv(l) is called *invariant* of l.

• A function *Flow* that assigns a *flow condition* to each location: Let  $V = \{x_1, \ldots, x_n\}$  be a finite set of (real-valued) variables. A *flow condition* f on V is defined by

$$f ::= \dot{x}_1 = d_1 \wedge \ldots \wedge \dot{x}_n = d_1$$

where  $d_1, \ldots, d_n \in \mathbb{Q}$ . We can also write a set of all flow conditions in F(V).

- A finite set Act of actions: An action is either one among *input action*, *output action* and *internal action*. An input action that has the form m? represents receiving the message m. An output action that has the form m! represents sending (broad-casting) the message m. An internal action  $a_{\tau}$  represents an asynchronous transition between two locations. In particular, the special actions are below:

- *Creation actions:*  $Crt_A_i$ ! and  $Crt_A_i$ ? denote the creation of  $A_i$ .

- *Destruction actions:*  $Dst_A_i$ ! and  $Dst_A_i$ ? denote the destruction of  $A_i$ .

- Enqueue actions:  $q_i!m$  denotes enqueueing the message m into the queue  $q_i$ .

- Dequeue actions:  $q_i$ ?m denotes dequeueing the message m from the queue  $q_i$ .

A finite set T ⊆ L × Φ(V) × Act × 2<sup>UPD(V)</sup> × L of transitions: A constraint of transition g ∈ Φ(V) is called guard condition. UPD(V) is a set of update expressions. An update

UPD(V) is a set of *update expressions*. An update expression  $\lambda$  is defined by

$$\lambda ::= x := c \mid x := x + c$$

where  $x \in V$  and  $c \in \mathbb{Q}$ .

- An initial transition  $t_0 \in L \times (Act_{in} \cup Act_{\tau}) \times 2^{UPD(V)}$

- A finite set  $T_{end} \subseteq L \times \Phi(V) \times Act_{out}$  of destruction transitions

2) Semantics of a DLHA: A state  $\sigma$  of a DLHA is defined as  $(l, \nu)$  or  $\bot$ , where l is a location,  $\nu$  is an *evaluation* of variables and  $\bot$  is an undefined state (that is, the DLHA is not created). An evaluation is an assignment of variables to real numbers.

The operational semantics of a DLHA is defined by the following rules:

- Time transition:

- For any  $d \in \mathbb{R}_{\geq 0}$ ,  $\bot \Rightarrow_d \bot$ .

- For  $d \in \mathbb{R}_{\geq 0}$  and a state  $(l, \nu)$ ,

$$(l, \nu) \Rightarrow_d (l, \nu + d)$$

if  $\nu + d \in Inv(l)$

where  $\nu + d$  is a shorthand for a function defined by  $\nu(x) + Flow(x) \cdot d$ .

- Discrete transition:

- For a transition  $(l, \phi, a, \lambda, l') \in T$ ,

$$(l,\nu) \Rightarrow_a (l',\nu[\lambda]) \text{ if } \nu \in \phi, \nu[\lambda] \in Inv.$$

• For a destruction-transition  $(l, \phi, a) \in T_{end}$ ,

$$(l,\nu) \Rightarrow_a \perp$$

if  $\nu \in \phi$ .

• For the initial transition  $t_0 = (l_0, a_0, \lambda_0)$ ,

$$\perp \Rightarrow_{a_0} (l_0, \vec{0}[\lambda])$$

where  $\vec{0}$  is an evaluation that assigns 0 to each variables.

#### B. Dynamically Reconfigurable System

A dynamically reconfigurable system consists of a set of DLHAs and a set of queues. Formally, a system S is defined by a tuple (A, Q), where A is a finite set of DLHAs and Q is a finite set of queues (unbounded FIfO buffers). A state of the system is a pair  $\langle \vec{\sigma}, \vec{w}_Q \rangle = \langle (\sigma_1, \dots, \sigma_{|A|}), (w_1, \dots, w_{|Q|}) \rangle$  of a vector of DLHA-states and a vector of queue-contents.

1) *Time Transition:* For an arbitrary  $\delta \in \mathbb{R}_{\geq 0}$ , the time transition is defined by the following rule:

$$\langle \vec{\sigma}, \vec{w_Q} \rangle \rightarrow_{\delta} (\vec{\sigma}', \vec{w_Q}) \iff \forall i. [\sigma_i \Rightarrow_{\delta} \sigma_i].$$

2) Discrete Transition: Let  $\vec{\sigma}, \vec{\sigma}', \vec{w}_Q$  and  $\vec{w}'_Q$  be

$$\begin{split} \vec{\sigma} &= (\sigma_1, \dots, \sigma_{|A|}), \\ \vec{\sigma}' &= (\sigma'_1, \dots, \sigma'_{|A|}), \\ \vec{w}_{\mathcal{Q}} &= (w_1, \dots, w_{|\mathcal{Q}|}) \\ \text{and } \vec{w}'_{\mathcal{Q}} &= (w'_1, \dots, w'_{|\mathcal{Q}|}). \end{split}$$

• For any output action  $a!, \langle \vec{\sigma}, \vec{w}_Q \rangle \rightarrow_a \langle \vec{\sigma}', \vec{w}_Q \rangle$

if

$$\exists i. [\sigma_i \Rightarrow_{a!} \sigma'_i \land \forall j \neq i. [\sigma_j \Rightarrow_{a?} \sigma_j \lor (\neg \exists \sigma. [\sigma_j \Rightarrow_{a?} \sigma'_j] \land \sigma_j = \sigma'_i)]].$$

An output action is broadcasted to all DLHAs, and a DLHA receiving the action moves by the synchronization if the state holds the guard condition.

- For an internal action  $a_{\tau}$ ,

- $\circ \quad \text{In case of } a_{\tau} = q_k! w, \ \langle \vec{\sigma}, \vec{w}_{\mathcal{Q}} \rangle \quad \rightarrow_{q_k! w} \\ \langle \vec{\sigma}', \vec{w}_{\mathcal{Q}}' \rangle$

if

$$\exists i. [\sigma_i \Rightarrow_{q_k!w} \sigma'_i \land \forall j \neq i. [\sigma_j = \sigma'_j]$$

$\land w'_k = w_k w \land \forall l \neq k. [w_k = w'_k]].$

$$\circ \quad \text{In case of } a_{\tau} = q_k ? w, \ \langle \vec{\sigma}, \vec{w}_{\mathcal{Q}} \rangle \rightarrow_{q_k ? w} \\ \langle \vec{\sigma}', \vec{w}'_{\mathcal{Q}} \rangle \\ \text{if } \exists i. [\sigma_i \Rightarrow_{q_k ? w} \sigma'_i \land \forall j \neq i. [\sigma_j = \sigma'_j] \\ \land w_k = w w'_k \land \forall l \neq k. [w_l = w'_l]]. \\ \circ \quad \text{Otherwise, } \langle \vec{\sigma}, \vec{w}_{\mathcal{Q}} \rangle \rightarrow_{a_{\tau}} \langle \vec{\sigma}', \vec{w}_{\mathcal{Q}} \rangle$$

if

$$\exists i. [\sigma_i \Rightarrow_{a_\tau} \sigma'_i \land \forall j \neq i. [\sigma_j = \sigma'_j]].$$

A *run(or path)*  $\rho$  of the system S is the following finite(or infinite) sequence of states.

$$\rho: s_0 \to_{a_0}^{\delta_0} s_1 \to_{a_1}^{\delta_1} \cdots \to_{a_{i-1}}^{\delta_{i-1}} s_i \to_{a_i}^{\delta_i} \cdots$$

where  $\rightarrow_{a_i}^{\delta_i}$  between  $s_i$  and  $s_{i+1}$  is defined as follows:

$$s_i \rightarrow_{a_i}^{\delta_i} s_{i+1} \iff \exists s'_i \cdot [s_i \rightarrow_{\delta_i} s'_i \land s'_i \rightarrow_{a_i} s_{i+1}].$$

The initial state  $s_0$  of a dynamically reconfigurable system is  $\langle (\sigma_{01} \dots, \sigma_{0|A|}), (w_{01}, \dots, w_{0|Q|}) \rangle$  where each  $\sigma_{0i}$  is the initial state of DLHA  $\mathcal{A}_i$  and each  $w_{0j}$  is empty, that is  $\forall j.w_{0j} = \varepsilon$

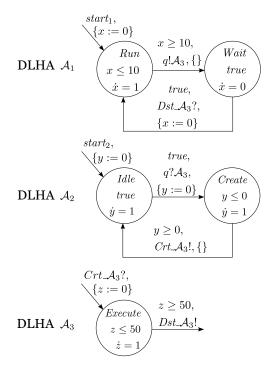

An example of a dynamically reconfigurable system is shown in Fig.1. This system consists of three DLHAs and one queue.

A DLHA  $A_1$  has two locations, *Run* and *Wait*, that are expressed as circles. In the location *Run*, an invariant is  $x \leq 10$  and a flow condition is  $\dot{x} = 1$ .

A run of this system is as below:

$$\rho: \langle ((Run, x = 0), (Idle, y = 0), \bot), (\varepsilon) \rangle$$

(1)

$$\rightarrow_{q!\mathcal{A}_3}^{10} \left\langle ((Wait, x = 10), (Idle, y = 0), \bot), (\mathcal{A}_3) \right\rangle$$

(2)

$$\rightarrow_{q^2\mathcal{A}_3}^0 \left\langle ((Wait, x = 10), (Create, y = 0), \bot), (\varepsilon) \right\rangle$$

(3)

$$\rightarrow_{creat}^0 \left\langle ((Wait, x = 10), (Idle, y = 0), \bot) \right\rangle$$

$$Crt_{\mathcal{A}_3} \langle ((wall, x = 10), (lale, y = 0), (\varepsilon) \rangle$$

$$(Execute, z = 0)), (\varepsilon) \rangle$$

(4)

$$\rightarrow_{Dst\_A_3}^{50} \langle ((Run, x = 0), (Idle, y = 0), \bot), (\varepsilon) \rangle$$

$$\rightarrow \cdots$$

(5)

Here,  $\varepsilon$  denotes the empty string.

In this tiny system, each DLHA has the following features:

- Environment:  $A_1$  periodically sends a message to request creation of  $A_3$ .

- Dispatcher:  $A_2$  receives the message from  $A_1$  and creates  $A_3$  with actions  $Crt_A_3!$  and  $Crt_A_3?$ .

- Task:  $A_3$  is created by  $A_2$  synchronously with actions  $Crt_A_3!$ .

In the initial state,  $A_1$  and  $A_2$  is already created because they have initial transitions with internal actions, and the content of the queue is empty (1). Next,  $A_1$  sends a creation request of  $A_3$ to  $A_2$  via the queue (2). Receiving the request asynchronously,  $A_2$  prepares to create  $A_3$ , that is,  $A_2$  moves from *Idle* to *Create* and the content of the queue becomes empty (3).  $A_3$  is created and its state moves from  $\bot$  to (*Execute*, z = 0) (4). When  $A_3$ finishes executing the process, it is destroyed with the action  $Dst_A_3$ ! (5).

Fig. 1. An example of a dynamically reconfigurable system

#### IV. REACHABILITY ANALYSIS

#### A. Reachability Problem

Given a dynamically reconfigurable system S = (A, Q)and a location  $l_t$ , we say "S reaches  $l_t$ " if there exists a path from the initial state to a state containing  $l_t$ . The reachability problem is the problem of determining whether S reaches  $l_t$ .

#### B. Convex Polyhedra

In our proposed method, we introduce *convex polyhedra* for the reachability analysis according to [6]. For a set V =

$\{x_1, \ldots, x_n\}$  of variables, a convex polyhedron  $\zeta$  on V has the following syntax:

$$\zeta ::= true \mid false \mid \sum_{i=1}^{n} a_i x_i \sim a_{n+1} \mid \zeta_1 \land \zeta_2$$

where  $\sim \in \{=, <, >, \leq, \geq\}$  and  $\zeta_1, \zeta_2$  are convex polyhedra.

Let  $\llbracket \zeta \rrbracket$  be a set of vertices such that are contained in the region described by  $\zeta$ , that is,  $\llbracket \zeta \rrbracket = \exists V [\zeta] \subseteq \mathbb{R}^n$ .

Then, the equivalence of convex polyhedra is defined as follows:

$$\zeta_1 = \zeta_2 \iff \llbracket \zeta_1 \rrbracket = \llbracket \zeta_2 \rrbracket$$

### C. Algorithm

For the reachability analysis, a state of system is defined as  $(L, \zeta, \vec{w}_Q)$ , where L is a set of locations,  $\zeta$  is a convex polyhedron, and  $\vec{w}_Q$  is a vector of queue-contents. The overview of the reachability analysis is shown in Fig. 2. The analysis is performed by breadth-first order with QDDs[7] as the following procedures:

- 1) Compute an initial state  $s_0$  of the system S (line 1 line 3).

- 2) Initialize a traversed set Visit and a untraversed set Wait of states by  $\emptyset$  and  $\{s_0\}$  (line 4).

- 3) While Wait is not empty, the following processing is repeated (line 8).

- a) Take a state  $(L, \zeta, \vec{w_Q})$  from Wait and remove the state from Wait (line 9 line 10).

- b) If the set L of locations contains the target location, return "yes" and terminate (line 11 line 13).

- c) If the state is not traversed yet  $((L, \zeta, \vec{w_Q}) \notin Visit)$ :

- i) Add the state into Visit (line 15).

- ii) Compute a set  $S_{post}$  of successors by the subroutine Succ (line 17).

- iii) Add all components of  $S_{post}$  into Wait (line 18).

The subroutine Succ that computes successors of a state is shown in Fig.3. Given a state  $(L, \zeta, \vec{w}_Q)$  and a system, successors are computed by the following procedure:

- 1) For each transition  $(l, \phi, a, \lambda, l')$  (or destructiontransition  $(l, \phi, a_l!)$ ) outgoing from a location  $l \in L$ , a set  $S_{post}$  of post states is computed as below:

- 2) If a is an enqueue action  $q_k!w$ : Add a message w to the content of queue  $q_k$  and add the new state to  $S_{post}$  (line 11 line 15).

- 3) If a is a dequeue action  $q_k$ ?w: Remove a message w from the content of queue  $q_k$  and add the new state to  $S_{post}$  (line 16 line 19).

- 4) If a is other internal action: Add the new state to  $S_{post}$  (line 22).

- 5) If a is an output action  $a_l$ !:  $S_{post}$  is computed by subroutine Syncs as the following steps (line 29).

- a) Compute a set  $T_{sync}$  of transitions synchronizing with t.

- b) Compute a set L' of locations of the new state with t and  $T_{sync}$ .

**Input:** a system S and a target location  $l_t$ Output: "yes" or "no"

- 1: /\* Compute the initial state \*/

- 2:  $L_0 \leftarrow \{l_{0i} \mid t_{0i} = (l_{0i}, a_{0i}, \lambda_{0i}), a_{0i} \neq Crt_A_i?\}$

- 3:  $\lambda_0 \leftarrow \bigcup \{\lambda_{0i} \mid t_{0i} = (l_{0i}, a_{0i}, \lambda_{0i}), a_{0i} \neq Crt\_\mathcal{A}_i?\}$

- 4:  $s_0 \leftarrow (L_0, \vec{0}[\lambda_0], (\varepsilon, \dots, \varepsilon))$

- /\* Initialize a set Visit of visited states and a queue Wait of states to search \*/ 5:

- 6: Visit  $\leftarrow \emptyset$ , Wait  $\leftarrow \{s_0\}$

- /\* Traverse in a breadth-first order \*/ 7:

- while Wait  $\neq \emptyset$  do 8:

- 9:

- $\begin{array}{l} (L,\zeta,\vec{w}_{\mathcal{Q}}) \leftarrow s \in \text{Wait} \\ \text{Wait} \leftarrow \text{Wait} \setminus \{(L,\zeta,\vec{w}_{\mathcal{Q}})\} \end{array}$ 10:

- 11: if  $l_t \in L$  then return "yes"

- if  $(L, \zeta, \vec{w}_{\mathcal{Q}}) \notin \text{Visit then}$ 12:

- Visit  $\leftarrow$  Visit  $\cup \{(L, \zeta, \vec{w}_{\mathcal{Q}})\}$ 13:

- /\* Compute a set of post-states \*/ 14:

- 15:  $S_{post} \leftarrow \text{Succ}((L, \zeta, \vec{w}_Q), \mathcal{S})$

- Wait  $\leftarrow$  Wait  $\cup$   $S_{post}$ 16:

```

return "no"

```

6)

Fig. 2. Algorithm of Reachability Analysis

- Compute a convex polyhedron  $\zeta'$  of the new c) state with t and  $T_{sync}$ . Add the new state  $(L', \zeta', w_Q)$  to  $S_{post}$ .

- d)

- If a is an input action:  $S_{post} = \emptyset$ .

#### V. IMPLEMENTATION AND PRACTICAL EXPERIMENTS

We have developed a prototype model checker of dynamically reconfigurable systems. The model checker is implemented in Java and comprised of about 1,600 lines of code using external libraries LAS[8], PPL[9], and QDD[7], [10].

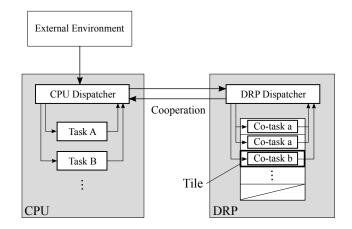

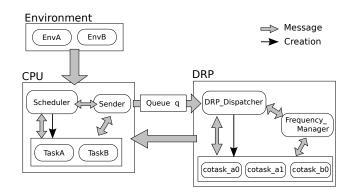

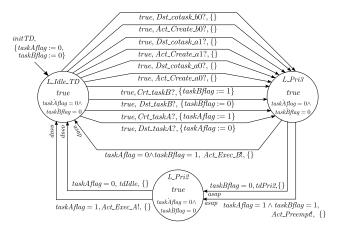

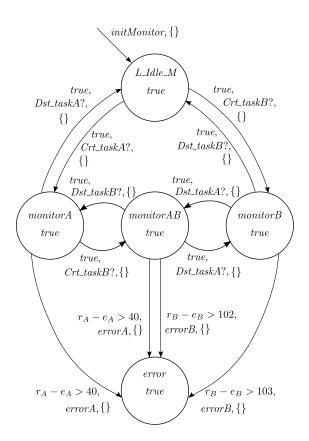

Moreover, for practical experiments, we have specified a cooperating system consisting CPU and DRP(Dynamically Reconfigurable Processor), and verified several safety properties for the system. The configuration of the embedded system is shown in Fig.4, and components of the system is shown in Fig.5. This system consists of 11 DLHAs and 1 queue. We show the DLHA of Scheduler in Fig.6 for example. The external environment consists of EnvA and EnvB that create periodically TaskA and TaskB. That is, EnvA creates TaskA with Crt taskA! every 70 milliseconds and EnvB creates TaskB with Crt\_taskB! every 200 milliseconds. Scheduler performs scheduling in accordance with the priority and actions for creation and destruction of DLHAs. For example, when TaskA is created by EnvA with Crt taskA! and TaskB is already running, Scheduler receives Crt taskA? and sends Act Preempt!. Then, TaskA moves to location RunA and TaskB moves to the location WaitB with the action.

TaskA and TaskB send a message to Sender if they need a co-task. Sender enqueues the message to create a cotask to the queue q when it receives a message from tasks. When TaskA moves to location RunA from location WaitA with Act\_Create\_a0!, Sender receives Act\_Create\_a0? and enqueues *cotask\_a0* to *q* with *q*!*cotask\_a0*.

DRP\_Dispatcher dequeues a message and creates cotask\_a0, cotask\_a1 and cotask\_b0 if there are enough free tiles. Frequency\_Manager is a module which manages the operating frequency of DRP. When a DLHA of co-task is created, Frequency\_Manager moves to the location fixing the frequency to minimum value.

For example, we have verified the schedulability of tasks. This property provides that each task must be finished processing within its deadline. To verify the property, a monitor automaton is defined as Fig.7. Monitor automaton checks whether the system satisfies the property, and it moves to a special location called *error location* when the property is not satisfied. In this case, the schedulability is verified in 180 seconds with 169 [MB] on a machine with Intel (R) Core (TM) i7-3770 (3.40 [GHz]) CPU and 16 [GB] RAM.

Fig. 4. Overview of the CPU-DRP embedded system

#### VI. CONCLUSION

In this paper, we have presented the specification language of dynamically reconfigurable systems and the reachability analysis algorithm for the verification. The next step would be to focus on more effective methods (e.g., Counterexample Guided Abstraction Refinement, Satisfiability Modulo Theories, etc.) for the verification.

**Input:** a state  $(L, \zeta, \vec{w}_Q)$  and the system S

**Output:** the set  $S_{post}$  of post-states 1:  $T_N \leftarrow \bigcup_{i=1}^{|A|} \{(l, \phi_g, a, \lambda, l') \in T_i \mid l \in L\}$  /\* Set of outgoing transitions \*/ 2:  $T_D \leftarrow \bigcup_{i=1}^{|A|} \{(l, \phi_g, a) \in T_{endi} \mid l \in L\}$  /\* Set of outgoing destruction transitions \*/ 3:  $S_{post} \leftarrow \emptyset, T_{post} \leftarrow T_N \cup T_D$ 4:  $\zeta_{\delta} \leftarrow \text{Tsucc}(L, \zeta) \land \bigwedge_{l_p \in L} Inv_s(l_p)$  /\* Convex polyhedron for the time transition \*/ 5: for all  $t \in T_{post}$  do if  $t = (l, \phi_g, a, \lambda, l')$  then 6: if a is an internal action then 7:  $L' \leftarrow (L \setminus \{l\}) \cup \{l'\}$  /\* Locations of the post-state \*/  $\zeta' \leftarrow (\zeta_{\delta} \land \phi_g)[\lambda] \land \zeta'_i \land \bigwedge_{l'_p \in L'} Inv_s(l'_p)$  /\* The convex polyhedron of the post-states \*/ 8: 9: if  $\zeta' \neq false$  then 10: if a is a enqueue action  $q_k!w$  then 11:  $\begin{array}{l} (w_1, \ldots, w_{|\mathcal{Q}|}) \leftarrow \vec{w_Q} \\ (w_1, \ldots, w_{|\mathcal{Q}|}) \leftarrow \vec{w_Q} \\ w'_k \leftarrow w_k w \ /* \ \text{Enqueue the message into } q_k \ */ \\ \vec{w'_Q} \leftarrow (w_1, \ldots, w_{k-1}, w'_k, w_{k+1}, \ldots, w_{|\mathcal{Q}|}) \\ S_{post} \leftarrow S_{post} \cup \{(L', \zeta', \vec{w'_Q})\} \\ \end{array}$ else if a is a dequeue action  $q_k ?w$  then 12: 13: 14. 15: 16: if  $w_k = ww'_k$  then  $\vec{w}'_{\mathcal{Q}} \leftarrow (w_1, \dots, w_{k-1}, w'_k, w_{k+1}, \dots, w_{|\mathcal{Q}|})$  /\* Dequeue the message from  $q_k$  \*/  $S_{post} \leftarrow S_{post} \cup \{(L', \zeta', \vec{w}'_{\mathcal{Q}})\}$ 17: 18: 19: else 20:  $S_{post} \leftarrow S_{post} \cup \{(L', \zeta', \vec{w}_Q)\}$  /\* For other internal action \*/ 21: else if a is an output action  $a_l!$  then 22:  $S_{post} \leftarrow S_{post} \cup Syncs((L, \zeta, \vec{w}_{Q}), t, S)$  /\* Compute the set of states by the synchronous transitions \*/ 23: 24: else  $S_{post} \leftarrow S_{post} \cup \text{Syncs}((L, \zeta, \vec{w}_{Q}), t, S)$  /\* Compute the set of states by the destruction transition \*/ 25:

return  $S_{post}$ Fig. 3. Subroutine Succ

Fig. 5. Components of the system

#### REFERENCES

- [1] R. Alur, C. Courcoubetis, T. A. Henzinger, and P. H. Ho, "Hybrid automata: An algorithmic approach to the specification and verification of hybrid systems," *Lecture Notes in Computer Science*, vol. 736, pp. 209–229, 1993.

- [2] S. Minami, S. Takinai, S. Sekoguchi, Y. Nakai, and S. Yamane, "Modeling, specification and model checking of dynamically reconfigurable processors," in *Computer Software 28(1)*. Japan Society for Software Science and Technology, 2011, pp. 190–216.

- [3] P. C. Attie and N. A. Lynch, "Dynamic input/output automata, a formal model for dynamic systems," in *Proceedings of the twentieth annual* ACM symposium on Principles of distributed computing, ser. PODC '01, 2001, pp. 314–316.

- [4] H. Yamada, Y. Nakai, and S. Yamane, "Proposal of specification language and verification experiment for dynamically reconfigurable

Fig. 6. DLHA of Scheduler

system," Journal of Information Processing Society of Japan, Programming, vol. 6, no. 3, pp. 1–19, 2013.

- [5] H. Nakano, T. Shindo, T. Kazami, and M. Motomura, "Development of dynamically reconfigurable processor LSI," *NEC Technical Journal*, vol. 56, no. 2, pp. 99–102, 2003.

- [6] R. Alur, C. Courcoubetis, N. Halbwachs, T. A. Henzinger, P.-H. Ho, X. Nicollin, A. Olivero, J. Sifakis, and S. Yovine, "The algorithmic analysis of hybrid systems," *THEORETICAL COMPUTER SCIENCE*, vol. 138, pp. 3–34, 1995.

- [7] B. Boigelot and P. Godefroid, "Symbolic verification of communication protocols with infinite statespaces using qdds," *Form. Methods Syst. Des.*, vol. 14, no. 3, pp. 237–255, 1999.

Fig. 7. Monitor automaton for schedulability

- [8] Y. Ono and S. Yamane, "Computation of quantifier elimination of linear inequilities of first order predicate logic," *IEICE Technical Report. COMP, Computation*, vol. 111, no. 20, pp. 55–59, 2011.

- [9] R. Bagnara, P. M. Hill, and E. Zaffanella, "The parma polyhedra library: Toward a complete set of numerical abstractions for the analysis and verification of hardware and software systems," *Sci. Comput. Program.*, vol. 72, no. 1-2, pp. 3–21, 2008.

- [10] B. Boigelot, P. Godefroid, B. Willems, and P. Wolper, "The power of qdds (extended abstract)," in SAS, 1997, pp. 172–186.