Simultaneous enlargement of SRAM read/write noise margin by controlling virtual ground lines

| 著者                | Makino Hiroshi, Kusumoto Takahito, Nakata<br>Shunji, Mutoh Shinichiro, Miyama Masayuki,<br>Yoshimura Tsutomu, Iwade Shuhei, Matsuda<br>Yoshio |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| journal or        | Proceedings of the 8th IEEE International                                                                                                     |

| publication title | NEWCAS Conference                                                                                                                             |

| volume            | NEWCAS2010                                                                                                                                    |

| number            | 5603927                                                                                                                                       |

| page range        | 73-76                                                                                                                                         |

| year              | 2010-01-01                                                                                                                                    |

| URL               | http://hdl.handle.net/2297/25791                                                                                                              |

doi: 10.1109/NEWCAS.2010.5603927

# Simultaneous Enlargement of SRAM Read/Write Noise Margin by Controlling Virtual Ground Lines

Hiroshi Makino<sup>1</sup>, Takahito Kusumoto<sup>2</sup>, Shunji Nakata<sup>3</sup>, Shin'ichiro Mutoh<sup>3</sup>, Masayuki Miyama<sup>2</sup>, Tsutomu Yoshimura<sup>4</sup>, Shuhei Iwade<sup>1</sup> and Yoshio Matsuda<sup>2</sup>

<sup>1</sup>Faculty of Information Science and Technology/<sup>4</sup>Faculty of Engineering, Osaka Institute of Technology, Hirakata, Japan <sup>2</sup>Graduate School of Natural Science, Kanazawa University, Kanazawa, Japan

<sup>3</sup> NTT Microsystem Integration Laboratories, Nippon Telegraph and Telephone Corporation, Atsugi, Japan

*Abstract*—The SRAM operating margin in 65nm technology is analyzed. The peak characteristic in the read margin versus the supply voltage was found to be caused by the channel length modulation effect. Controlling the memory cell virtual ground line proved to be effective in enlarging the operating margin simultaneously in the read and the write operations. A simple optimum circuit which does not require any dynamic voltage control is proposed, realizing an improvement in the operating margin comparable to conventional circuits requiring dynamic voltage control.

# I. INTRODUCTION

Advanced LSIs, such as System-on-a-Chips (SoCs) and microprocessors, continuously require more and more SRAM storage capacity to improve their performance. Recently, the progress of process technology has enabled over one hundred million bits of SRAM to be included in a chip [1]. Shrinking the physical dimensions of the SRAM, however, is becoming difficult because fluctuations of the device characteristics increase remarkably with the reduction of transistor area [2], [3]. Such fluctuation degrades memory cell stability both in the read and the write operations, so that any increase in bit capacity is limited.

To stabilize the SRAM memory cell, we have to consider both the read and the write operations, because their stabilizing conditions usually work in opposition. Several circuit techniques have been proposed to stabilize the SRAM memory cell. Controlling the word line voltage in the read operation increases the static noise margin (SNM) [4], [5], and the read noise margin. Weakening the power supply of the memory cell in the write operation increases the write noise margin (WNM) [4]-[7]. Although these circuit techniques are effective, they require complicated voltage control circuits which reduce the design simplicity and process portability.

In general, the SNM is supposed to increase as the supply voltage becomes higher. There are, however, some cases under certain circuit conditions in which the SNM does not improve, even if the supply voltage increases [4], [8]. This indicates the possibility of further optimization of the memory cell voltage to improve stability.

In this paper, we make a detailed analysis of the read and the write operations of the SRAM memory cell. Especially in the read operation, we clarify the reason, using a simple model, why the SNM does not increase steadily as the supply voltage increases. Then, we propose the optimum circuit and voltage condition to realize maximum memory cell stability.

#### II. ANALYSIS OF THE READ OPERATION

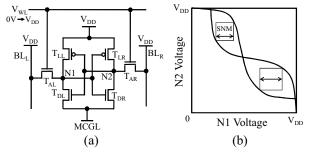

# A. Definition of the read noise margin

Fig.1(a) shows a memory cell circuit in the read operation. The memory cell ground line (MCGL) is set to GND level, bit lines ( $BL_L$  and  $BL_R$ ) are fixed to the power supply voltage ( $V_{DD}$ ) and the word line voltage ( $V_{WL}$ ) changes from 0V to  $V_{DD}$ . Then, the data stored in N1 and N2 are read out to the  $BL_L$  and  $BL_R$ , respectively. The static noise margin (SNM) is used to estimate the stability of the memory cell in the read operation [9]. Fig.1(b) shows a butterfly curve which consists of a pair of transfer curves of the storage nodes, N1 and N2, when the  $V_{WL}$  is fixed to  $V_{DD}$ . The SNM, as shown in Fig.1(b), is defined as one side length of the maximum inscribed square. If the sizes of the two maximum inscribed squares are different, the SNM is defined as the smaller one.

Fig.1. (a) SRAM read operation and (b) definition of SNM

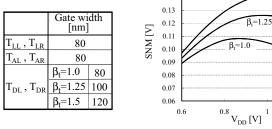

#### B. Voltage dependence of SNM

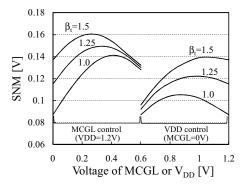

We simulated the voltage dependences of the SNM in various cases using the 65nm SPICE parameter [10]. Transistor sizes are summarized in Table 1. Gate lengths of all transistors are 65nm. As shown in the table,  $\beta_t$  is the gate width ratio of the driver transistor to the access transistor. In the simulation, the V<sub>DD</sub> is simultaneously applied to the word line and the bit lines. Fig.2 shows the dependence of the SNM on the V<sub>DD</sub>. As the V<sub>DD</sub> increases, the SNM initially increases, and then decreases in all three cases of  $\beta_t$ =1.0, 1.25, and 1.5. That is, the SNM peaks at a certain V<sub>DD</sub>. This tendency becomes more obvious in smaller  $\beta_t$ . The peak position shifts to the higher voltage side as the  $\beta_t$  increases.

Although the saturating characteristic of the SNM versus  $V_{DD}$  has been suggested in previous works [4], [8], studies have given neither a detailed analysis nor a description of the peak characteristic. Ref. [8] indicates that the saturation is caused by the channel length modulation effect.

Table 1. Transistor sizes

0.15

0.14

Fig.2. Dependence of SNM on  $V_{DD}$

1.2

$\beta_t = 1.5$

From the following analysis, we found that the peak characteristic is also caused by the same channel length modulation effect. As our aim is not to reproduce the simulation results precisely, but to clarify the origin of the peak, we started from the following simple equations of transistor I-V characteristics.

$$I_{p,linear} = \beta_p (V_{gs} - V_{thp} - \frac{V_{ds}}{2}) V_{ds} (1 + \lambda_p V_{ds})$$

(1)

$$I_{p,sat} = \frac{\beta_p}{2} (V_{gs} - V_{thp})^2 (1 + \lambda_p V_{ds})$$

(2)

$$I_{n,linear} = \beta_n (V_{gs} - V_{lhn} - \frac{V_{ds}}{2}) V_{ds} (1 + \lambda_n V_{ds})$$

(3)

$$I_{n,sat} = \frac{\beta_n}{2} (V_{gs} - V_{thn})^2 (1 + \lambda_n V_{ds})$$

<sup>(4)</sup>

The suffixes p and n represent the pMOS and the nMOS transistors, respectively.  $I_{n,linear}$  and  $I_{p,linear}$  are the transistor currents in the linear region and  $I_{n,sat}$  and  $I_{p,sat}$  in the saturation region.  $\beta_p$  and  $\beta_n$  are transconductances,  $V_{thp}$  and  $V_{thn}$  are the threshold voltages, and  $\lambda_p$  and  $\lambda_n$  are the channel length modulation parameters.  $V_{ds}$  and  $V_{gs}$  denote the drain and the gate voltages to the source voltage, respectively.

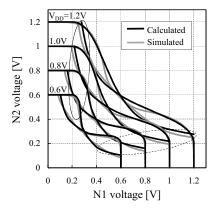

We determined the parameters,  $\beta_p$ ,  $\beta_n$ ,  $\lambda_p$ ,  $\lambda_n$ ,  $V_{thp}$  and  $V_{thn}$ in (1)-(4), by fitting the memory cell butterfly curves to the SPICE simulation results in  $\beta_t$ =1.0. The determined values of the parameters are  $-V_{thp}=V_{thn}=0.2V$ ,  $-\lambda_p=\lambda_n=1$ ,  $\beta_p=4.5\times10^{-5}$ ,  $\beta_n=1.3\times10^{-4}$  for the driver transistors and  $\beta_n=7.8\times10^{-5}$  for the access transistors

Fig.3. Butterfly curves at various  $V_{DD}$

Fig.3 shows the butterfly curves at the supply voltages of 0.6V, 0.8V, 1.0V and 1.2V. The black lines are the numerically calculated results from equations (1)-(4) after the fitting. The gray lines are the results of the SPICE simulation.

In spite of our rough approximation, the calculated lines closely correspond to the simulated results and possess the characteristics of real butterfly curves. Both curves obviously show the decrease of SNM in high  $V_{DD}$ .

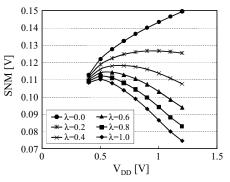

To investigate the influence of the channel length modulation effect on the SNM, we measured the SNMs of the calculated butterfly curves by changing  $\lambda_p$  and  $\lambda_n$ . Fig.4 shows the dependence of the SNM on the  $V_{DD}$  for various  $\lambda_s$ , where  $\lambda = -\lambda_p = \lambda_n$  and  $\beta_t = 1.0$ . Although the SNM increases at a steady rate as the  $V_{DD}$  increases for  $\lambda = 0$ , peak characteristics appear for  $\lambda = 0.2$ -1.0. The  $V_{DD}$  peak decreases as the  $\lambda$ increases. This phenomenon is caused by the decrease of the SNM at high  $V_{DD}$ . This decrease becomes more noticeable as the  $\lambda$  increases. In Ref. [8], the peak does not appear clearly because the SNM is observed within a small range of  $\lambda$ .

Fig.4. Dependence of SNM on  $V_{DD}$  for various  $\lambda s$

The reason for the SNM decrease at high  $V_{\text{DD}}$  is explained as follows.

- (i) The current of the driver transistor in the saturation region increases by the channel length modulation effect as the  $V_{DD}$  increases. This causes the rapid decrease of the butterfly curve (see the solid ellipse in Fig. 3). As a result, the SNM is reduced.

- (ii) As the current of the access transistor in the saturation region increases, the low level of the butterfly curve goes up as the  $V_{DD}$  increases (see the dotted ellipse in Fig. 3). This also reduces the SNM.

Generally, the SNM increases as the  $V_{DD}$  increases. On the other hand, when the channel length modulation effect increases, the SNM is reduced. Thus, the opposite effects induce the peak on the curve of SNM versus  $V_{DD}$ .

It should be noted that the higher peak of the SNM is obtained by raising the memory cell ground line, the MCGL in Fig.1, instead of lowering the V<sub>DD</sub>. The SPICE simulation in Fig.5 shows the dependence of the SNM both on the MCGL voltage and the  $V_{DD}$ . The  $V_{DD}$  is set to 1.2V in controlling the MCGL and the MCGL is set to 0V in controlling the  $V_{\text{DD}}$ . In this simulation, the bodies (p-well) of the nMOS transistors are tied to the GND level. Raising the MCGL voltage is more effective in improving the SNM than decreasing the  $V_{DD}$ . As a result, the peak SNM in raising MCGL voltage is more than 15% larger than that in decreasing  $V_{DD}$  for all cases of  $\beta_t$ =1.0, 1.25 and 1.5. This is because raising the MCGL voltage causes an increase in the threshold voltage of the nMOS transistors in the memory cell by a reverse body bias effect. Increasing the threshold voltages of the nMOS transistors, especially those in the access transistors, improves the SNM.

Fig.5. Dependence of SNM on MCGL and  $V_{DD}$

## C. Consideration of Vth fluctuation

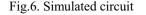

In the deep-submicron process, random fluctuations of the device characteristics are noticeable [2], [3]. Therefore, we have to take such fluctuations into account when discussing the improvement of read stability. We investigated the dependence of read stability on transistor threshold voltages because their fluctuations strongly affect read stability. Fig.6 shows a simulated circuit which demonstrates the worst case for a read operation. The  $\Delta V_{thn}(>0)$  and the  $\Delta V_{thp}(<0)$ represent the random fluctuations of the threshold voltages of the nMOS and pMOS transistors ( $V_{thn}$  and  $V_{thp}$ ), respectively. From the Stolk's equation [3] and the SPICE parameters [10], we estimated that the standard deviations of the  $V_{thn}$  and  $V_{thp}$  $(\sigma V_{thn} \text{ and } \sigma V_{thp})$  are 35.1mV and 34.3mV. As an example of the worst case, the  $\Delta V_{thn}$  and the  $\Delta V_{thp}$  are set to  $3*\sigma V_{thn}$  and  $3*\sigma V_{thp}$ . The simulation is carried out by examining whether the read operation is possible or not for various  $V_{thn}$  and  $V_{thp}$ . Here, we changed the VTH0s of nMOS and pMOS SPICE parameters [10] to vary the  $V_{thn}$  and the  $V_{thp}$ .

Fig.7 shows the simulation results. Five curves express the boundaries of the "PASS" region and the "FAIL" region for the MCGL of 0.0V, 0.1V, 0.2V, 0.3V and 0.4V at  $\beta_t$ =1.0. In the "PASS" region, the read operation is successful and in the "FAIL" region, the read operation fails. The "PASS" region gets larger as the MCGL increases to 0.3V. For example, although the read operation fails for an MCGL of less than 0.2V when V<sub>thn</sub>=0.5V and V<sub>thp</sub>=0.4V, it is successful for an MCGL voltage above 0.2V. For an MCGL higher than 0.4V, however, the "PASS" region shrinks. These behaviors closely match the results (Fig.5) in the earlier section. Therefore, the read margin can be improved by increasing MCGL voltage, even if there are random fluctuations in the threshold voltages.

#### 0.7 FAIL 0.6 MCGL $V_{thp}[V]$ - 0.0V **—** 0.1V 0.5 ▲ 0.2V 0.3V $\rightarrow 0.4V$ 04 PASS BL. 0.3 0.4 0.6 0.7 0.3 0.5 MCGL V<sub>thn</sub> [V]

Fig.7. Boundary curves between "PASS" and "FAIL"

# III. IMPROVEMENT OF THE WRITE MARGIN

#### A. Definition of the write noise margin

Fig.8(a) shows a memory cell circuit in the write operation. The memory cell power line (MCPL) and the MCGL are usually connected to the  $V_{DD}$  and GND, respectively. Initially, the storage nodes (N1 and N2) are "1" and "0", respectively, and the word line voltage ( $V_{WL}$ ) is 0V. Then, the left and right bit lines (BL<sub>L</sub> and BL<sub>R</sub>) are set to GND and  $V_{DD}$ , respectively, and the  $V_{WL}$  rises from 0V to  $V_{DD}$ . Fig.8(b) shows the voltages of the storage nodes in the write operation. When the N1 and N2 voltages turn over together at a certain value of  $V_{WL}$  ( $V_W$ ), the write operation is complete. We adopt the definition of write noise margin (WNM) as the voltage difference between  $V_W$  and  $V_{DD}$  [11]. A larger WNM corresponds to an easier write operation.

Fig.8. (a) SRAM write operation and (b) Definition of WNM

#### B. Voltage dependence of the WNM

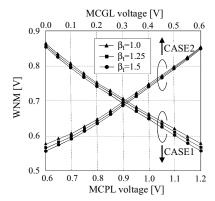

The WNM can be increased by lowering the memory cell supply voltage [4]-[7]. There are two possible means to lower the memory cell supply voltage. One is decreasing the MCPL (CASE1) and the other is increasing the MCGL (CASE2).

We simulated the voltage dependences of the WNM in CASE1 and CASE2. Fig.9 shows the simulation results. The WNM improves similarly in both Case1 and Case2, with voltage changes in the MCPL and MCGL. Also, the dependence of the WNM on the  $\beta_t$  is small. This is because the source-to-drain currents of the load transistor and the access transistor,  $T_{LL}$  and  $T_{AL}$  in Fig.1(a), mainly determine the WNM. Those currents are almost the same in both cases for any  $\beta_t$ , because the gate-to-source voltages are almost the same. Therefore, the stability of the SRAM memory cell in the write operation improves by increasing the MCGL as much as by decreasing the MCPL.

Fig.9. Dependence of WNM on  $V_{DD}$  and MCGL voltages

### IV. OPTIMIZATION

# A. Optimized circuit

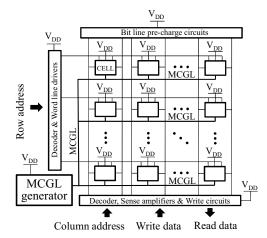

The above analysis proves that controlling the MCGL is more effective in enlarging the operating margins simultaneously in the read and the write operations than in controlling the  $V_{DD}$  or the MCPL. Fig.10 shows the concept of the optimized SRAM circuit. The power supply of the memory cell is connected to the V<sub>DD</sub> together with all the other circuits. Only the virtual ground line of the memory cell array, the MCGL, is separated from the ground lines of the other circuits and controlled by the "MCGL generator" circuit. The "MCGL generator" generates the optimum MCGL voltage to maximize memory cell stability. Unlike the case of MCGL=0V, under optimum MCGL, the stabilities of the memory cell both in the read and the write operations simultaneously improve. This circuit is guite simple when compared with conventional circuits [4]-[7] because there is no need to dynamically control the power line. The optimized MCGL voltage is constant and does not change during the read and write operations.

Fig.10. Concept of the optimized SRAM circuit

(b) Optimum MCGL vs.  $\beta_t$

# B. Optimization of MCGL voltage

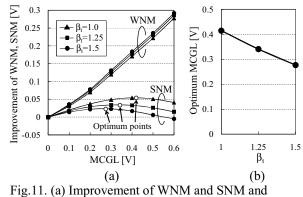

Optimum MCGL voltage can be determined from the above analysis. Fig.11(a) shows the dependence of WNM and SNM improvements on the MCGL voltage. These improvements are measured by subtracting the values of the WNM and SNM at MCGL=0V from those at each MCGL

voltage. Improvement of the WNM increases steadily for the MCGL and is much higher than that of the SNM. Therefore, to create the optimum condition, we should select the maximum point of the SNM. Fig.11(b) plots the optimum MCGL voltage versus the  $\beta_t$  taken from Fig.10(a). For a  $\beta_t$  from 1.0 to 1.5, which is used in ordinary memory cell design, the optimum MCGL voltage varies from 0.41V to 0.28V. The improvement of the SNM at the optimum MCGL varies from 22mV to 53mV, which is comparable to that of the conventional read assist circuit [4]. We can maximize memory cell stability by using the optimum MCGL voltage.

#### V. CONCLUSION

From the analysis of the SRAM memory cell, both in the read and the write operations using 65nm SPICE, controlling the MCGL proved to be effective in simultaneously enlarging the SNM and the WNM. The channel length modulation effect created the peak characteristic in the SNM versus  $V_{DD}$ , which then enabled the SNM increase by raising the MCGL. We proposed the optimum SRAM circuit and MCGL voltage. The improvement of the SNM at the optimum MCGL voltage is comparable to that of the conventional read assist circuit. Because the channel length modulation effect will become greater and greater in the future, we are convinced that the proposed scheme will become more and more effective.

#### REFERENCES

- B. Stackhouse, B. Cherkauer, M. Gowan, P. Gronowski and C. Lyles "A 65nm 2-Billion-Transistor Quad-Core Itanium Processor," ISSCC, 2008, pp. 92-93, 2008.

- [2] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching Properties of MOS Transistors," IEEE J. Solid-State Circuits, vol. 24, no. 5, pp. 1433–1440, Oct., 1989.

- [3] P. A. Stolk, F. P. Widdershoven and D. B. M. Klaassen, "Modeling Statistical Dopant Fluctuations in MOS Transistors", IEEE Trans. on Electron Devices, Vol. 45, No. 9, 1960-1971, 1998.

- [4] S. Ohbayashi, M. Yabuuchi, K. Nii, Y. Tsukamoto, S. Imaoka, Y. Oda, et al., "A 65 nm SoC Embedded 6T-SRAM Designed for Manufacturability with Read and Write Operation Stabilizing Circuits," IEEE Journal of Solid-State Circuits, vol. 42, no. 4, pp.820-829, April. 2007.

- [5] K. Nii, M. Yabuuchi, Y. Tsukamoto, S. Ohbayashi, S. Imaoka, H. Makino, et al., "A 45-nm Bulk CMOS Embedded SRAM with Improved Immunity against Process And Temperature Variations," IEEE Journal of Solid-State Circuits, vol. 43, no. 1, pp.180-191, Jan. 2008.

- [6] M. Yamaoka, N. Maeda, Y. Shinozaki, Y. Shimazaki, K. Nii, S.Shimada, et al., "90-nm Process-variation Adaptive Embedded SRAM Modules with Power-line-floating Write Technique," IEEE J. Solid-State Circuits, vol. 41, no. 3, pp. 705–711, Mar. 2006.

- [7] K. Zhang, U. Bhattacharya, C. Zhanping, F. Hamzaoglu, D. Murray, N. Vallepalli, et al., "A 3-GHz 70-Mb SRAM in 65-nm CMOS Technology with Integrated Column-based Dynamic Power Supply," IEEE J. Solid-State Circuits, vol. 41, no. 1, pp. 146–151, Jan. 2006.

- [8] H. Shinohara, K. Nii and H. Onodera, "Analytical Model of Static Noise Margin in CMOS SRAM for Variation Consideration," IEICE Trans. Electron., vol. E91-C, no. 9, pp. 1488-1500, Sept. 2008

- [9] E. Seevinck, F. J. List and J. Lohstroh, "Static-Noise Margin Analysis of MOS SRAM Cells," IEEE Journal of Solid-State Circuits, vol. sc-22, no. 5, pp. 748-754, Oct. 1987.

- [10] "65nm BSIM4 model card for bulk CMOS: V1.0," Predictive Technology Model, http://www.eas.asu.edu/~ptm/

- [11] N. Gierczynski, B. Borot, N. Planes and H. Brut, "A New Combined Methodology for Write-margin Extraction of Advanced SRAM," IEEE Int. Conf. on Microelectronic Test Structures, pp. 97-100, 2007