# Fabrication of GaAs MISFET with nm-thin oxidized layer formed by UV and ozone process

| 著者                | liyama Koichi, Kita Yukihiro, Ohta Yosuke,   |

|-------------------|----------------------------------------------|

|                   | Nasuno Masaaki, Takamiya Saburo, Higashimine |

|                   | Koichi, Ohtsuka Nobuo                        |

| journal or        | IEEE Transactions on Electron Devices        |

| publication title |                                              |

| volume            | 49                                           |

| number            | 11                                           |

| page range        | 1856-1862                                    |

| year              | 2002-11-01                                   |

| URL               | http://hdl.handle.net/2297/1786              |

# Fabrication of GaAs MISFET With nm-Thin Oxidized Layer Formed by UV and Ozone Process

Koichi Iiyama, *Member, IEEE*, Yukihiro Kita, Yosuke Ohta, Masaaki Nasuno, Saburo Takamiya, Koichi Higashimine, and Nobuo Ohtsuka

Abstract—A gate insulating layer with single nm-order thickness for suppressing gate leakage current is one of the key factors in extending downsizing limits, based upon the scaling rule, of field-effect-type transistors. We describe the fabrication and characterization of GaAs MISFETs with a nm-thin oxidized laver as the gate insulating layer, which is formed by an ultraviolet (UV) and ozone process. The UV and ozone process forms oxidized GaAs layers near the surface, which effectively suppress the reverse leakage current by several orders of magnitude. The fabricated GaAs MISFET can operate not only in the depletion mode, but also in the accumulation mode up to 3 V of the gate voltage for 8-nm-thick oxidized layer due to the current blocking effect of the oxidized layer. A current cutoff frequency of 6 GHz and a maximum oscillation frequency of 8 GHz are obtained for a GaAs MISFET with a 1- $\mu$ m-long gate length and 8-nm-thick oxidized layer.

Index Terms—Compound semiconductors, GaAs, MISFET, self-align, ultraviolet (UV) and ozone process.

### I. INTRODUCTION

**▼** OMPOUND semiconductor field effect transistors (FETs) and high-electron mobility transistors (HEMTs) are widely used in mobile telephones and high-speed optoelectronic circuits, such as optical receivers, and are very promising electronic devices in high-speed optical communication systems over 40 Gb/s, satellite communication systems, intelligent transport systems (ITS) etc. In the compound semiconductor FETs and HEMTs, Schottky junction has been used as the gate structure for a long time, and a cutoff frequency of  $f_T = 396$  GHz was obtained in 2001 [1]. However, the progress in the cutoff frequency is very slow (from  $f_T = 342 \text{ GHz}$  [2] in 1992 to 396 GHz in 2001) because of short-channel effects (SCEs). In the Schottky gate structure, the gate leakage current increases due to tunneling effect according to an increase of the donor density which accompanies with downsizing the device to achieve high-speed operation.

The alternative gate structure is the metal-insulator-semiconductor (MIS) to reduce the gate leakage current and to overcome the SCE [3], [4]. The advantages of the MIS gate structure are as follows:

Manuscript received March 26, 2002; revised August 12, 2002. The review of this paper was arranged by Editor M. Anwar.

K. Iiyama, Y. Kita, Y. Ohta, M. Nasuno, and S. Takamiya are with the Department of Electrical and Electronic Engineering, Faculty of Engineering, Kanazawa University, Kanazawa 920-8667, Japan (e-mail: iiyama@ee.t.kanazawa-u.ac.jp).

K. Higashimine and N. Ohtsuka are with the School of Materials Science, Japan Advanced Institute of Science and Technology (JAIST), Ishikawa 923-1292. Japan

Digital Object Identifier 10.1109/TED.2002.804720

- high-speed operation due to downsizing the device more and more;

- 2) possibility of single power supply due to enhancement mode operation;

- 3) possibility of complementary device structure;

- 4) improvement of thermal property and breakdown voltage. However, no MIS-gate FET/HEMT has been practically used because a high-quality thin-film insulating layer cannot be achieved on the surface of the compound semiconductor due to high density of interface states. A number of MIS gate structures have been tried for realizing MISFET to date. The insulated gate InGaAs/InAlAs PHEMT utilizing a silicon interface control layer was reported [4]. The *in-situ* Ga<sub>2</sub>O<sub>3</sub>/Gd<sub>2</sub>O<sub>3</sub> film growth on GaAs by molecular beam epitaxy (MBE) was reported for GaAs MISFET [5]. The GaAs MISFET with SiO<sub>2</sub> as the insulating layer [6] and the GaAs MOSFET with oxidized GaAs as the insulating layer [7] were also reported. These reports show some good results for high-performance GaAs MISFETs. However, the thickness of the insulating layers in such GaAs MISFETs are relatively thick (20 nm-40 nm). To achieve ultra-high-speed transistor which can operate in a terahertz frequency range, a nm-thin insulating layer is

We have been studying the MIS gate structure with a nm-thin GaAs-oxide layer prepared by ultraviolet (UV) and ozone treatment [8]. The gate leakage current can be suppressed by five orders of magnitude with an 8-nm-thin GaAs-oxidized layer. In this paper, we present GaAs MISFETs with nm-thin GaAs-oxide layers formed by a UV and ozone process including microscopic structural details and RF performance in addition to our previous work [9], focusing on the gate current suppression effect.

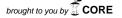

### II. UV AND OZONE PROCESS

The oxidation of the GaAs surface was carried out by UV and ozone process (SAMCO: UV and Ozone Cleaner, UV-1). After removing the native oxide layer on the surface of n-GaAs/semi-insulating-GaAs wafers by buffered hydrofluoric acid, the wafers were directly oxidized by the UV and ozone process for  $15\sim480$  min at the wafer stage temeperature of 300 °C. Then, the oxidized layer was partially removed photolithographically by buffered hydrofluoric acid etching, and the thickness was measured by using an atomic force microscope (AFM). The measured thickness of the oxidized layer against the UV and ozone time is shown in Fig. 1. The oxidation at 100 °C for 240 min was also carried out, which resulted in the oxide thickness of  $6\sim9$  nm, suggesting very

Fig. 1. Measured thickness of the oxidized layer against the UV and ozone time.

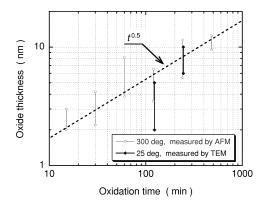

Fig. 2. Measured composition of the oxidized layer by the XPS.

weak dependence on the temperature. The uncertain range for each data indicates positional dependence of the measured data, reflecting the nonuniformity of the thickness of the oxidized layer. The thickness is nearly proportional to square root of the oxidation time. The thickness of the oxidized layer processed at 25 °C is also shown in Fig. 1, which was measured by the cross-sectional high-resolution transmission electron microscope (TEM), as described in Section III. No significant dependency of the thickness of the oxidized layer on the oxidation temperature is observed.

X-ray photoelectron spectroscopy (XPS) analysis was carried out to investigate the composition of the oxidized layer. Fig. 2 shows the measured composition of a 480-min oxidized surface against the Ar etching time that reflects the depth. Fig. 2 suggests the outdiffusion and the decomposition of As near the surface and the incorporation of oxygen. Due to insufficient depth resolution ( $\approx 10$  nm) of the XPS, Fig. 2 does not show accurate distributions. However, it clearly suggests that the oxide layer is mainly composed of Ga-oxide (mainly Ga<sub>2</sub>O<sub>3</sub>), although As-oxide (As<sub>2</sub>O<sub>3</sub>, As<sub>2</sub>O<sub>5</sub>) may still remain to some extent.

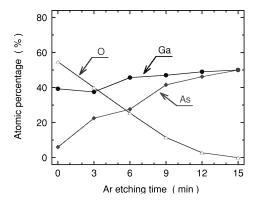

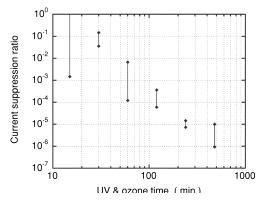

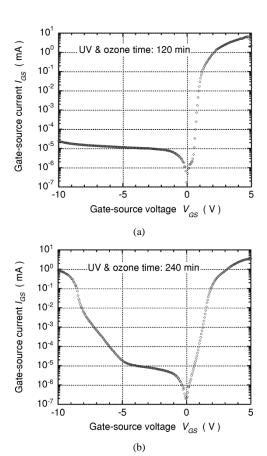

Next, we measured the *I–V* characteristics for both the Schottky diodes and the MIS diodes. Fig. 3 shows the measured results for the Schottky (open circles) and the MIS diodes (closed circles). It can clearly be seen that the nm-thin insulating layers effectively suppress the reverse leakage currents while keeping the shapes of the curves. Fig. 4 shows the current suppression ratio of the MIS diode to the current of the

Fig. 3. Measured I-V characteristics for both the Schottky and the MIS diodes, (a) UV and ozone time: 120 min. (b) UV and ozone time: 240 min.

Fig. 4. Current suppression ratio of the MIS diode to the current of the Schottky diode.

Schottky diode. The current can be suppressed by five orders of magnitude when the oxidation was carried out for 240 min.

### III. DEVICE STRUCTURE AND FABRICATION

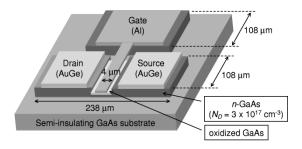

The structure of the fabricated GaAs MISFET is shown in Fig. 5. The substrate used in our experiments was n-GaAs (donor concentration:  $3.1 \times 10^{17}$  cm<sup>-3</sup>, thickness:  $0.42~\mu$ m)/semi-insulating-GaAs epitaxial wafer. The native oxide layer on the surface of the substrate was first removed by buffered hydrofluoric acid etching and the epitaxial layer was thinned to  $0.29~\mu$ m by etching in order to reduce the mesa-step-height, then rinsed by deionized water. The drain and

Fig. 5. Structure of the fabricated GaAs MISFET.

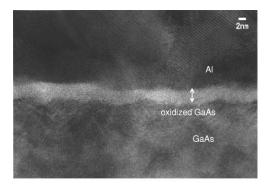

Fig. 6. Cross-sectional high-resolution TEM image of the thin oxide layer existing between the GaAs and the Al gate electrode. The magnification is 3 750 000.

the source electrodes were formed by evaporating AuGe and then sintered at 367 °C for 1 min. After mesa-etching the epitaxial layer by the etchant ( $H_3PO_4:H_2O:H_2O_2=4:90:1$ ) for isolating the gate, a photoresist was coated and patterned for the recess etching, the oxidation of the GaAs, and the formation of the gate electrode with a self-align process. The recess etching was carried out by using the same etchant, and a typical resultant recess thickness was 0.16  $\mu$ m. Then, the sample was oxidized by the UV and ozone process at room temperature. Only the recess region was selectively oxidized by the presence of the photoresist mask pattern. Then, Al was deposited for the gate electrode, and finally the photoresist mask pattern was removed. The gate length and the gate width were 4  $\mu$ m and 100  $\mu$ m, respectively.

Fig. 6 shows the cross-sectional high-resolution TEM image of the thin oxidized layer existing between the GaAs and the Al gate electrode. The oxidation was carried out at 25 °C for 120 min. The image was taken in the (110) direction of the GaAs. The oxide layer appears as an amorphous image, while the GaAs and the Al exhibit lattice fringes. Periodic fringes are seen in some small regions in the oxide layer, which may be attributed to overlapping of the oxide layer with either the GaAs or the Al crystals in the imaging direction due to the wavy interfaces. Moire fringes are seen in the Al crystalline regions, which are caused by overlapping of different crystalline grains. Both the flatness of the interface between the GaAs and the oxidized layer and the thickness of the oxidized layer are far from atomic flat. The thickness of the oxide layer is position-dependent and can be read to be  $2 \sim 5$  nm, which is plotted in Fig. 1. Similar TEM observation was also carried out for a 240-min oxidized sample, and the oxide thickness of  $6 \sim 10$  nm was obtained.

Fig. 7. I-V characteristics between the gate and the source for the GaAs MISFET with the UV and ozone times of 120 min and 240 min. (a) UV and ozone time: 120 min. (b) UV and ozone time: 240 min.

## IV. DC CHARACTERISTICS

Fig. 7 shows the current-voltage (I-V) characteristics between the gate and the source for the GaAs MISFETs with the UV and ozone time of 120 min and 240 min. The device with the oxidation time of 240 min has smaller forward current due to current blocking effect by the oxidized GaAs layer. For the backward bias voltage larger than -5 V, the device with the oxidation time of 240 min has larger backward current. This may be due to the Fowler-Nordheim (FN) tunneling. In the MISFETs, the nm-order insulating layer and the depletion layer with several tens  $\sim 100$  nm thickness share the bias voltage. When the insulating layer is very thin and the tunneling prevents accumulation of holes at the interface between the GaAs and the oxidized GaAs, most of the bias voltage is applied to the depletion layer like a Schottky junction. When the insulating layer becomes thick enough to prevent the tunneling, an additional bias voltage is mostly applied to the oxidized layer and causes the FN tunneling. In the case of SiO<sub>2</sub>/Si systems as a reference, the critical SiO<sub>2</sub> thickness is about 4 nm [10]. The thickness of the oxidized GaAs layers estimated by the TEM (see Fig. 1) are approximately 3 nm and 8 nm for the oxidation time of 120 min and 240 min, respectively. The thicker oxidized layer may accumulate holes at the insulator-semiconductor (IS) interface, and then the additional bias voltage is applied only to the oxidized layer, which causes the FN tunneling.

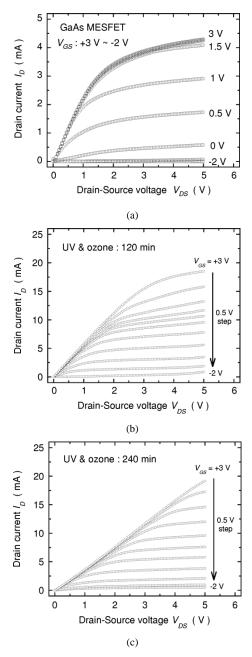

Fig. 8 shows the measured drain current-drain voltage  $(I_D-V_D)$  characteristics for the GaAs MISFETs along with

Fig. 8. Drain current-drain voltage  $(I_D-V_D)$  characteristics for the GaAs MEFET and GaAs MISFET with the UV and ozone times of 120 min and 240 min. The thickness of the oxide layers estimated by the TEM image are 3 nm and 8 nm, respectively. (a) GaAs MEFET. (b) UV and ozone time: 120 min. (c) UV and ozone time: 240 min.

that for the MESFET by using a semiconductor parameter analyzer (Hewlett Packard: HP 4156A). The UV and ozone process was 120 min and 240 min at room temperature. The thickness of the oxidized layer was estimated to be 3 nm and 8 nm, respectively, from the TEM image. The gate voltage was changed from -2 V to +3 V with 0.5 V step. In the GaAs MESFET [see Fig. 8(a)], the drain current is saturated when the gate voltage reaches +1.5 V. However, in the GaAs MISFETs, the drain current increases until the gate voltage reaches +3 V. Thus, the MISFETs can operate even under accumulation mode (beyond the flat-band condition) in spite of such ultrathin insulating layers. This result coincides well with the gate voltage which gives mA-order forward gate current

(see Fig. 7), and means that the injected electrons from the source is directed to the drain without leaking to the gate due to current blocking by the oxidized nm-thin GaAs layer. A high ohmic contact resistance also increases the saturation gate voltage. However, Fig. 7 clearly shows that the forward voltage at a certain current increases with the oxide thickness even below the series-resistance-limited current region, verifying the current blocking effect of the insulating layer. The difference of the drain current between the MESFET and the MISFETs is mainly due to the difference of the recess thickness from wafer to wafer. We also find out that the transconductance decreases when the gate voltage is around the flat-band voltage  $(+0.5 \text{ V} \sim +1.5 \text{ V})$  for the device with the UV and ozone time of 120 min. Most of the samples with 120 min oxidation and some of the samples with 240 min oxidation show such recessed transcoductances around the flat-band voltage.

We also measured the  $I_D$ – $V_D$  characteristics by using an analog semiconductor curve tracer (Iwatsu: TT-507). The  $I_D$ – $V_D$  characteristics have hysteresis loop, and a large hysteresis loop was observed when the gate voltage is around the flat-band voltage. This implies the existence of movable ion or trap/release mechanism of charges in the oxidized layer and/or the interface between the GaAs and the oxidized layer.

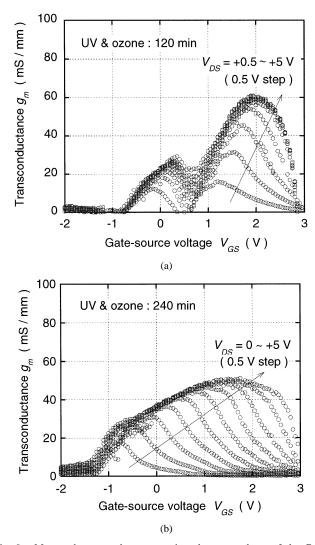

Fig. 9 shows the measured transconductance against the gate voltage. The transconductance drops around the flat-band voltage for the device with the UV and ozone time of 120 min. This may be caused by a combination of trap/release and spatial distributions of electrons, as described in Section VI. The maximum transconductance is  $50 \sim 60$  mS/mm. Such a low transconductance is due to the long gate length and the nonoptimized recess etching.

Long-term reliability test of the MISFETs is not performed due to the remaining hysteresis problem. However, power cosumption ( $I_D \times V_{DS}$ ) at the device failure for the device with the oxdation time of 240 min, tested by the curve tracer, is nearly equal to that of a commercial low-noise GaAs MESFET with a nearly equal gate width.

### V. RF CHARACTERISTICS

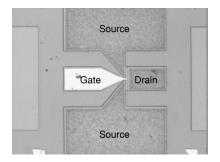

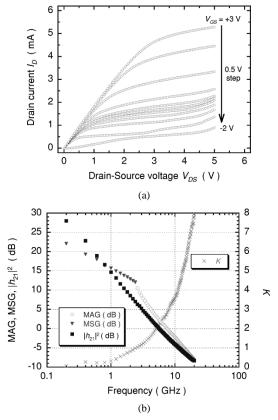

We fabricated similar MISFET with a coplaner electrode structure and the AuGe/Ni source and drain electrodes, as shown in Fig. 10 for on-wafer measurement of S parameters of the device. The UV and ozone time was 240 min, and the gate length and the gate width are 1  $\mu$ m and 80  $\mu$ m (40  $\mu$ m×2) fingers), respectively. Fig. 11(a) shows the measured  $I_D$ – $V_D$ characteristic of the device (1 finger). Due to the small gate width and excess recess etching, the drain current is smaller than that shown in Fig. 7. However, the availability of the forward gate bias operation beyond the flat-band voltage and the recessed transconductance around the flat-band condition are reproduced. Fig. 11(b) shows the stability factor K, the maximum available power gain (MAG), the maximum stable power gain (MSG), and the  $|h_{21}|^2$  evaluated from the measured S parameters. The drain and the gate voltages are  $V_{DS} = +4 \text{ V}$ and  $V_{GS} = +1$  V, respectively. The current cutoff frequency  $f_T$  and the maximum oscillation frequency  $f_{

m osc}$  are estimated to be  $f_T=6~\mathrm{GHz}$  and  $f_\mathrm{osc}=8~\mathrm{GHz}$ , respectively. We also

Fig. 9. Measured transconductance against the gate voltage of the GaAs MISFET with the UV and ozone times of 120 min and 240 min. (a) UV and ozone time: 120 min. (b) UV and ozone time: 240 min.

measured the device at  $V_{DS}=+4~{\rm V}$  and  $V_{GS}=+2~{\rm V}$ , but no substantial change in the RF performance was observed. This implies that the recessed transcondunctance of the dc  $I_D$ - $V_D$  curve does not directly affect the RF performance. The main reasons for the relatively low  $f_T$  and  $f_{\rm max}$  are relatively high ohmic contact, estimated to be  $R_{DS}=600~\Omega$  from Fig. 11(a), and an unoptimized recess thickness.

### VI. DISCUSSIONS

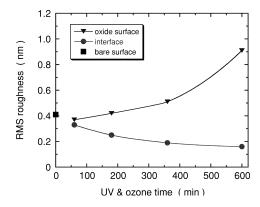

The nonuniform oxide thickness could be one of the problems which causes different performances between the devices even in a wafer, especially in the thinner oxide devices. Fig. 12 shows oxidation time-dependence of the roughness of the oxide surfaces and the oxide/GaAs interfaces. The surface roughness increases with increasing oxidation time, but the interface roughness decreases with increasing oxidation time. This trend is similar to that reported for thermally oxidized SiO<sub>2</sub>/Si systems [11], and suggests that the interface inherently tends to approach a perfect (100) plane by long-time oxidation. Hence, the nonuniformity of the oxide thickness can be minimized by using (100) wafer with minimized surface roughness, which is obtainable by

Fig. 10. Photograph of the fabricated GaAs MISFET with a coplaner electrode structure.

Fig. 11. Measured  $I_D$ – $V_D$  characteristic and the RF characteristics of the GaAs MISFET. The UV and ozone time is 240 min, and the gate length and the gate width are 1  $\mu$ m and 80  $\mu$ m, respectively.  $V_{DS}=+4$  V and  $V_{GS}=+1$  V. (a)  $I_D$ – $V_D$  characteristic. (b) RF characteristics.

removing an oxide layer after long-time oxidation, using a combination of heteroepitaxial growth, material-selective etching, etc.

Most of the samples with the oxidation time of 120 min and some of the samples with the oxidation time of 240 min show a drop in the transconductances around the flat-band voltage. The main reason we attribute it to trap/release of electrons is as follows. We measured the leakage currents of Ni/n-GaAs Schottky junctions which were formed after UV and ozone oxidation and removal of the oxidated layers. They showed much larger leakage currents than the Schottky junction formed on an original GaAs surface [8]. This suggests that the oxidation process creates deep levels in the GaAs wafers near the IS interfaces. The leakage current increased with the oxidation time up to 120 min, and then decreased by longer oxidation time. Our

Fig. 12. Measured RMS roughness of the oxide layer and the interface against the oxidation time.

recent work [12], [13] on the C-V characteristics of Ni/GaAs-oxide/n-GaAs, Ni/GaAs-oxinitride/n-GaAs, etc, suggests that the deep levels are positively charged under the reverse bias condition, and then trap electrons when the bias approaches the flat-band voltage. Moreover, nitridation of the oxide film solves insufficient increase of high-frequency capacitance at a forward bias, which Passlack *et al.* theoretically derived as a sign of unpinning [14]. Frequency dependence of C-V curves of the Ni/GaAs-oxide/n-GaAs system, in a frequency range of  $10 \text{ kHz} \sim 1 \text{ MHz}$ , is small [12].

### VII. CONCLUSION

We describe the fabrication and the characterization of GaAs MISFETs with nm-thin oxidized layers as the gate insulating layer. The oxidation was carried out by the UV and ozone process. The thickness of the oxidized layer was proportional to the square root of the oxidation time and was about 8 nm for 240 min oxidation time. From the I-V characteristics of the MIS diodes, the current suppression ratio of the MIS diode to the Schottky diode is  $10^{-5}$  for 240 min oxidation time. The GaAs MISFETs with nm-thin oxidized layer formed by the UV and ozone process were fabricated. They could operate not only in the depletion mode but also in the accumulation mode up to 2 V and 3 V of the gate voltages for 3-nm-thick and 8-nm-thick oxidized layers, respectively, due to the current blocking effect of the oxidized layer. However, the  $I_D$ - $V_D$  characteristics have hysteresis loop, and a large hysteresis was observed when the gate voltage is around the flat-band voltage. This result suggests the existence of interface states. The RF response of the GaAs MISFETs was measured, showing the current cutoff frequency of 6 GHz and the maximum oscillation frequency of 8 GHz with 1- $\mu$ m-long gate length and 8-nm-thick oxidized layer. The quality improvement of the oxide layer is now being studied [12] and the results will be presented elsewhere along with some dielectric properties of the oxide layer.

# ACKNOWLEDGMENT

The authors are grateful to Dr. T. Inokuma at Kanazawa University for his contribution to the XPS analysis, and to S. Hashimoto and M. Wada in our laboratory for their technical support.

### REFERENCES

- [1] Y. Yamashita, A. Endoh, K. Shinohara, M. Higashiwaki, K. Hikosaka, T. Mimura, S. Hiyamizu, and T. Matsui, "Ultrashort 25-nm-gate lattice-matched InAlAs/InGaAs HEMTs within the range of 400 GHz cutoff frequency," *IEEE Electron Device Lett.*, vol. 22, pp. 367–169, Aug. 2001.

- [2] L. D. Nguyen, A. S. Brown, M. A. Thompson, and L. M. Jelloian, "50-nm self-aligned-gate pseudomorphic AlInAs/GaInAs high-electron mobility transistors," *IEEE Trans. Electron Devices*, vol. 39, pp. 2007–20014, Sept. 1992.

- [3] T. Sugimura, T. Tsuzuku, Y. Kasai, K. Iiyama, and S. Takamiya, "I-V characteristics of Schottky/metal-insulator-semiconductor diodes with tunnel thin barriers," Jpn. J. Appl. Phys., pt. I, vol. 39, no. 7B, pp. 4521–4522, 2000.

- [4] Y. G. Xie, S. Kasai, H. Takahashi, C. Jiang, and H. Hasegawa, "Low leakage, high breakdown voltage and high transconductance insulated gate PHEMTs utilizing silicon interface control layer," in *Proc. TWHM*, Kyoto, Japan, 2000, pp. 24–25.

- [5] F. Ren, M. Hong, W. S. Hobson, J. M. Kuo, J. R. Lothian, J. P. Mannaerts, J. Kwo, S. N. G. Chu, Y. K. Chen, and A. Y. Cho, "Demonstration of enhancement-mode p- and n-channel GaAs MOSFETs with Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) as gate oxide," *Solid State Electron.*, vol. 41, p. 1751, 1997

- [6] M. P. Houng, Y. H. Wang, C. J. Huang, S. P. Huang, and J.-H. Horng, "Quality optimization of liquid phase deposition SiO<sub>2</sub> films on gallium arsenide," *Solid State Electron.*, vol. 44, pp. 1917–1923, 2000.

- [7] J.-Y. Wu, H.-H. Wang, Y.-H. Wang, and M.-P. Houng, "Fabrication of depletion-mode GaAs MOSFET with a selective oxidation process by using metal as the mask," *IEEE Electron Device Lett.*, vol. 22, pp. 2–4, Jan. 2001.

- [8] T. Sugimura, T. Tsuzuku, T. Katsui, Y. Kasai, T. Inokuma, S. Hashimoto, K. Iiyama, and S. Takamiya, "A preliminary study of MIS diodes with nm-thin GaAs-oxide layers," *Solid State Electron.*, vol. 43, no. 8, pp. 1571–1576, 1999.

- [9] Y. Kita, Y. Ohta, N. C. Paul, K. Iiyama, and S. Takamiya, "Depletion and accumulation mode operation of GaAs MISFET with nm-thin gate insulating layers formed by UV and ozone process," in *Proc. 28th ISCS*, vol. 56, Tokyo, Japan, 2001, p. 56.

- [10] M. Hiroshima, T. Yasaka, S. Miyazaki, and M. Hirose, "Electron tunneling through ultrashin gate oxide formed on hydrogen-terminated Si (100) surfaces," *Jpn. J. Appl. Phys.*, vol. 33, no. 1B, pp. 395–398, 1994.

- [11] M. Fujimura, H. Nohira, and T. Hattori, "Surface morphology of ultrathin thermal oxide film formed on Si (100) surface," in *Proc. 4th Work*shop Formation Characterizaion Reliability of Ultrathin Silicon Oxide Films, 1999, JSAP Catalog No: AP992 204, pp. 275–279.

- [12] N. C. Paul, Y. Ohta, D. Tezuka, M. Nasuno, Y. Yamamura, T. Inokuma, K. Iiyama, and S. Takamiya, "Quality improvement of oxidized-GaAs/ n-GaAs structure by nitrogen plasma treatment," in *Proc. 14th Indium Phosphide and Related Materials Conf.*, Stockholm, Sweden, 2002, pp. 217–220.

- [13] N. C. Paul, D. Tezuka, T. Inokuma, K. Iiyama, and S. Takamiya, "Effect of oxidation and/or nitridation of (100) n -GaAs surface," in Abstract Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD), Sapporo, Japan, 2002, pp. 253–256.

- [14] M. Passlack, M. Hong, E. F. Schubert, G. J. Zydzik, J. P. Mannaerts, W. S. Hobson, and T. D. Harris, "Advancing metal-oxide-semiconductor theory: Steady-state nonequilibrium conditions," *J. Appl. Phys.*, vol. 81, no. 11, pp. 7647–7661, 1997.

Koichi Iiyama (M'95) was born in Fukui, Japan, on March 19, 1963. He received the B.E., M.E., and D.E. degrees in electronics from Kanazawa University, Kanazawa, Japan, in 1985, 1987, and 1993, respectively.

From 1987 to 1988, he was with Yokogawa Hewlett-Packard Ltd. Since 1988, he has been with the Faculty of Engineering, Kanazawa University, and now is an Associate Professor in the Department of Electrical and Electronic Engineering. From 2001 to 2002, he was a Guest Scientist in Heinrich-Hertz-Institut für Nachrichtentechnik Berlin GmbH, Berlin, Germany. He is now working in research on optical fiber science, high-speed photoreceivers, and high-speed compound semiconductor devices.

Dr. Iiyama is a member of the IEICE and the Japan Society of Applied Physics.

**Yukihiro Kita** received the B.E. and M.E. degrees in electrical and computer engineering from Kanazaa University, Kanazawa Japan, in 2000 and 2002, respectively. While at Kanazawa University, he researched the development of MISFETs/MIS-HEMTs.

He is currently with Oki Electric Industry Co., Ltd., Tokyo, Japan.

Yosuke Ohta received the B.E. and the M.E. degrees in electrical and computer engineering from Kanazaa University, Kanazawa, Japan, in 2000 and 2002, respectively. While at Kanazawa University, he researched the development of MISFETs/MIS-HEMTs.

He is currently with Hitachi Ltd., Tokyo, Japan.

Masaaki Nasuno was born in Toyama, Japan, on December 5, 1979. He received the B.E. degree in electrical and computer engineering from Kanazawa University, Kanazawa, Japan, in 2002. He is now pursuing the M.E. degree in electronics in Kanazawa University. His current research interest is development of MISFETs/MIS-HEMTs.

**Saburo Takamiya** was born in Tokyo, Japan, on March 1, 1943. He received the B.E. degree in physics in 1965 and the D.E. degree in electronics in 1977, both from the Tokyo Institute of Technology.

He joined Mitsubishi Electric Corporation in 1965. From 1965 to 1967, he was a Visiting Research Scientist at the Semiconductor Research Institute, Sendai, Japan. Beginning in 1965, he was in charge of developing optoelectric and microwave semiconductor devices such as laser diode, photodetectors, microwave diodes, and microwave transistors. From 1993 to 1997, he managed the Advanced Materials Technology Department of the Mitsubishi Electric Corporation. Since 1997, he has been a Professor in the Department of Electrical and Electronic Engineering, Faculty of Engineering, Kanazawa University. He is currently investigating microwave semiconductor and optical devices.

Dr. Takamiya received the Yonezawa Memorial Young Engineer Award in 1975 and the Paper Award in 1976, both from the IEICE. He is a Member of the IEICE and the Japan Society of Applied Physics.

**Koichi Higashimine**, photograph and biography not available at the time of publication.

Nobuo Ohtsuka, photograph and biography not available at the time of publication.