# EFFICIENT RUNTIME SYSTEMS FOR SPECULATIVE PARALLELIZATION

A dissertation submitted towards the degree Doctor of Engineering (Dr.-Ing.) of the Faculty of Mathematics and Computer Science of Saarland University

by Clemens Hammacher

Saarbrücken February 2017

| Day of Colloquium<br>Dean of the Faculty | 27.07.2017<br>UnivProf. Dr. Frank-Olaf Schreyer |

|------------------------------------------|-------------------------------------------------|

| Chair of the Committee                   | Prof. Dr. Jan Reineke                           |

| Reporters:                               |                                                 |

| First Reviewer                           | Prof. Dr. Andreas Zeller                        |

| Second Reviewer                          | Prof. Dr. Sebastian Hack                        |

| Third Reviewer                           | Dr. Björn Franke                                |

| Academic Assistant                       | Dr. María Gómez Lacruz                          |

#### SAARLAND UNIVERSITY

# Zusammenfassung

Chair of Software Engineering and Compiler Design Lab Department of Computer Science

Dissertation

#### Efficient Runtime Systems for Speculative Parallelization

by Clemens Hammacher

Manuelle Parallelisierung ist zeitaufwändig und fehleranfällig. Automatische Parallelisierung andererseits findet häufig nur einen Bruchteil der verfügbaren Parallelität. Mithilfe von Spekulation kann jedoch auch für komplexere Programme ein Großteil der Parallelität ausgenutzt werden. Spekulativ parallelisierte Programme benötigen zur Ausführung immer ein Laufzeitsystem, um die spekulativen Annahmen abzusichern und für den Fall des Nichtzutreffens die korrekte Ausführungssemantik sicherzustellen. Solche Laufzeitsysteme sollen die Ausführungszeit des parallelen Programms so wenig wie möglich beeinflussen. In dieser Arbeit untersuchen wir, inwiefern aktuelle Systeme, die Speicherzugriffe explizit und in Software beobachten, diese Anforderung erfüllen, und stellen Änderungen vor, die die Laufzeit massiv verbessern. Außerdem entwerfen wir zwei neue Systeme, die mithilfe von virtueller Speicherverwaltung das Programm indirekt beobachten und dadurch eine deutlich geringere Auswirkung auf die Laufzeit haben. Eines der vorgestellten Systeme ist mittels eines Moduls direkt in den Linux-Betriebssystemkern integriert und bietet

so die bestmögliche Effizienz. Darüber hinaus bietet es weitreichendere Sicherheitsgarantien als alle bisherigen Techniken, indem sogar Systemaufrufe zum Beispiel zur Datei Ein- und Ausgabe in der spekulativen Isolation mit eingeschlossen sind. Wir zeigen an einer Reihe von Benchmarks die Überlegenheit unserer Spekulationssyteme über den derzeitigen Stand der Technik. Sämtliche unserer Erweiterungen und Neuentwicklungen stehen als *open source* zur freien Verfügung.

Diese Arbeit ist in englischer Sprache verfasst.

#### SAARLAND UNIVERSITY

### Abstract

Chair of Software Engineering and Compiler Design Lab Department of Computer Science

Dissertation

#### Efficient Runtime Systems for Speculative Parallelization

by Clemens Hammacher

Manual parallelization is time consuming and error-prone. Automatic parallelization on the other hand is often unable to extract substantial parallelism. Using speculation, however, most of the parallelism can be exploited even of complex programs. Speculatively parallelized programs always need a runtime system during execution in order to ensure the validity of the speculative assumptions, and to ensure the correct semantics even in the case of misspeculation. These runtime systems should influence the execution time of the parallel program as little as possible. In this thesis, we investigate to which extend state-of-the-art systems which track memory accesses explicitly in software fulfill this requirement. We describe and implement changes which improve their performance substantially. We also design two new systems utilizing virtual memory abstraction to track memory changed implicitly, thus causing less overhead during execution. One of the new systems is integrated into the Linux kernel as a kernel *module*, providing the best possible performance. Furthermore it provides stronger soundness guarantees than any state-of-the-art

system by also capturing system calls, hence including for example file I/O into speculative isolation. In a number of benchmarks we show the performance improvements of our virtual memory based systems over the state of the art. All our extensions and newly developed speculation systems are made available as *open source*. To Anna, with love.

## A cknowledgements

This thesis would not have been possible without substantial support from many people.

First and foremost, I want to thank my advisors Andreas and Sebastian, who both saw my potential before I saw it myself, and put a lot of trust in me right from the beginning. Thank you, Andreas, for arranging funding for my research and for providing such a great working environment. I enjoyed the confidence you put in all your PhD students, which gave me ample freedom to pursue my research. Thank you, Sebastian, for all the time you invested already as a Junior Professor to get down to the bottom of technical challenges. I always admired your steady urge to be directly involved in the work of your students, even after your responsibilities and your group grew greatly after you assumed your full professorship.

I am also thankful for all the discussions with my collegues, be it at the retreats in Dagstuhl or Otzenhausen, or individually at the university. Especially in tough times of setbacks and failure, the support from people who knew the struggle and overcame it was invaluable. Special thanks go to Kevin, my good friend and collegue from my first semester onwards. We shared an office for more than five years and went through numerous ups and downs together. Thank you for always looking forward and keeping our team in motion!

I am deeply grateful for all the support I received from my parents throughout my life, putting me in the position to successfully complete this dissertation. Thank you for all the effort it took you to get me to where I am today. And last but not least I want to thank Anna for her love, her patience and her endless support throughout the last years. I would not have gotten to know you without my postgraduate studies for my doctorate, and this thesis would not exist without you.

# Contents

| Z | usan          | nmenfassung                                     | iii          |

|---|---------------|-------------------------------------------------|--------------|

| Α | bstr          | act                                             | $\mathbf{v}$ |

| Α | .cknc         | owledgements                                    | ix           |

| 1 | Int           | roduction                                       | 1            |

|   | 1.1           | Thesis Organization                             | 5            |

|   | 1.2           | Terminology                                     | 6            |

|   | 1.3           | Publications                                    | 12           |

| 2 | Sta           | ate of the Art                                  | 15           |

|   | 2.1           | Automatic Parallelization                       | 15           |

|   | 2.2           | Runtime Systems for Speculative Parallelization | 23           |

|   |               | 2.2.1 Software Transactional Memory             | 24           |

|   |               | 2.2.2 Hardware Transactional Memory             | 32           |

|   |               | 2.2.3 Thread Level Speculation                  | 34           |

|   |               | 2.2.4 Virtual-Memory Based Memory Tracking      | 37           |

|   |               | 2.2.5 The Importance of Granularity             | 40           |

|   | 2.3           | Conclusion and Open Issues                      | 41           |

| 3 | $\mathbf{Th}$ | e Sambamba Framework                            | 43           |

|   | 3.1           | General Design                                  | 44           |

|   | 3.2           | Phases During Compilation                       | 46           |

|   | 3.3           | Phases During Execution                         | 49           |

| 4 | $\mathbf{Pre}$                                      | eparing | g STM for Speculative Parallelization 53                                                                                |

|---|-----------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|

|   | 4.1                                                 | Chang   | ges in STM Design                                                                                                       |

|   |                                                     | 4.1.1   | Commit Ordering                                                                                                         |

|   |                                                     | 4.1.2   | Hash Tables for Transactional Logs 55                                                                                   |

|   |                                                     | 4.1.3   | Adaptive Initial Sizes of Hash Table 58                                                                                 |

|   |                                                     | 4.1.4   | Hopscotch Hashing 60                                                                                                    |

|   | 4.2                                                 | Instru  | mentation $\ldots \ldots 62$ |

|   | 4.3                                                 | Evalua  | ation $\ldots \ldots 67$            |

|   |                                                     | 4.3.1   | State-of-the-Art Performance 67                                                                                         |

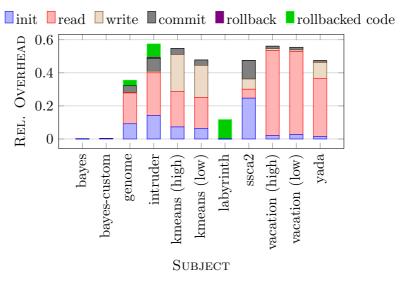

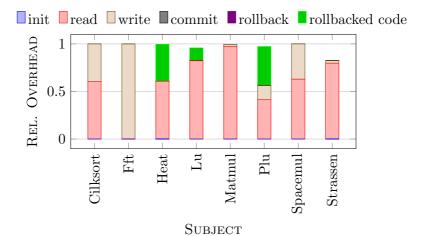

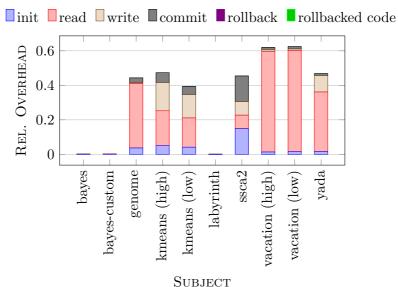

|   |                                                     |         | 4.3.1.1 Overhead Breakdown 69                                                                                           |

|   |                                                     | 4.3.2   | Improved Implementation                                                                                                 |

|   |                                                     | 4.3.3   | Case study: Runtime Improvement in a Real-                                                                              |

|   |                                                     |         | World Application                                                                                                       |

|   | 4.4                                                 | Conclu  | usion                                                                                                                   |

| 5 | 5 Virtual-Memory Based Speculation in User Space 87 |         |                                                                                                                         |

|   | 5.1                                                 |         |                                                                                                                         |

|   | 5.2                                                 | Design  | n of U-TLS 91                                                                                                           |

|   |                                                     | 5.2.1   | Data Structures                                                                                                         |

|   |                                                     | 5.2.2   | Forking Speculative Tasks                                                                                               |

|   |                                                     | 5.2.3   | Execution of a Speculative Task 95                                                                                      |

|   |                                                     | 5.2.4   | Validating and Committing Speculative State . 96                                                                        |

|   |                                                     | 5.2.5   | Optimizations                                                                                                           |

|   |                                                     | 5.2.6   | Restrictions of U-TLS                                                                                                   |

|   | 5.3                                                 | Evalua  | ation                                                                                                                   |

|   |                                                     | 5.3.1   | TLS Overhead                                                                                                            |

|   |                                                     |         | 5.3.1.1 Spawning Tasks 100                                                                                              |

|   |                                                     |         | 5.3.1.2 Execution Overhead $\ldots \ldots \ldots \ldots 103$                                                            |

|   |                                                     |         | 5.3.1.3 Validation and Commit 109                                                                                       |

|   |                                                     | 5.3.2   | Usage in Automatic Parallelization                                                                                      |

|   | 5.4                                                 | Conclu  | -                                                                                                                       |

| 6 | Vii                                                 | rtual-N | Iemory Based Speculation in Kernel Space117                                                                             |

| - | 6.1                                                 |         | n of K-TLS                                                                                                              |

|   |                                                     | 6.1.1   | Data Structures                                                                                                         |

|      | 6.1.2    | User-Space Interface                                                                                          |

|------|----------|---------------------------------------------------------------------------------------------------------------|

|      | 6.1.3    | Kernel-Space Interface                                                                                        |

|      | 6.1.4    | Execution of Speculative Tasks                                                                                |

|      | 6.1.5    | Validation and Commit                                                                                         |

|      | 6.1.6    | Handling of System Calls                                                                                      |

|      | 6.1.7    | Optimizations                                                                                                 |

| 6.2  | Impro    | oving Granularity via Instrumentation 127                                                                     |

|      | 6.2.1    | Overall Design                                                                                                |

|      | 6.2.2    | Accessing the Shadow Memory                                                                                   |

|      | 6.2.3    | Code Instrumentation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 131$                                   |

|      |          | 6.2.3.1 Load and Store Operations 133                                                                         |

|      |          | 6.2.3.2 Updating Larger Memory Blocks 136                                                                     |

|      | 6.2.4    | Changes to the Kernel Module                                                                                  |

|      |          | $6.2.4.1  \text{Task Setup}  \dots  \dots  \dots  \dots  \dots  139$                                          |

|      |          | $6.2.4.2  \text{Validation}  \dots  \dots  \dots  \dots  \dots  140$                                          |

|      |          | $6.2.4.3  \text{Commit} \dots 141$                |

| 6.3  | Evalu    | ation $\ldots \ldots 142$ |

|      | 6.3.1    | TLS Overhead $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 143$                             |

|      |          | 6.3.1.1 Spawning Tasks                                                                                        |

|      |          | $6.3.1.2  \text{Execution Overhead}  \dots  \dots  \dots  145$                                                |

|      |          | 6.3.1.3 Validation and Commit 148                                                                             |

|      | 6.3.2    | Usage in Automatic Parallelization 149                                                                        |

|      | 6.3.3    | Effect of Additional Instrumentation 153                                                                      |

| 6.4  | Concl    | usion $\ldots \ldots 161$ |

| 7 Co | onclusio | ons and Future Work 163                                                                                       |

| 7.1  |          | S                                                                                                             |

| 7.2  |          | S                                                                                                             |

| 7.3  |          | amba                                                                                                          |

|      |          |                                                                                                               |

### Bibliography

# LIST OF FIGURES

| Figure 1.1 Development of different processor features over                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| the last 40 years. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                             | 2  |

| Figure 3.1 Overview of the compilation phase of Sam-                                                                                                                               | _  |

| bamba                                                                                                                                                                              | 5  |

|                                                                                                                                                                                    | 7  |

| Figure 3.3 The phases executed at runtime of a program                                                                                                                             |    |

| compiled with Sambamba 5                                                                                                                                                           | 0  |

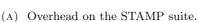

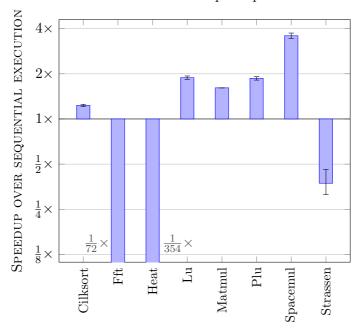

| Figure 4.1 Breakdown of TinySTM overhead on different<br>programs from STAMP and the <i>Cilk</i> example pro-                                                                      |    |

| 5 <i>,</i> 5                                                                                                                                                                       | '1 |

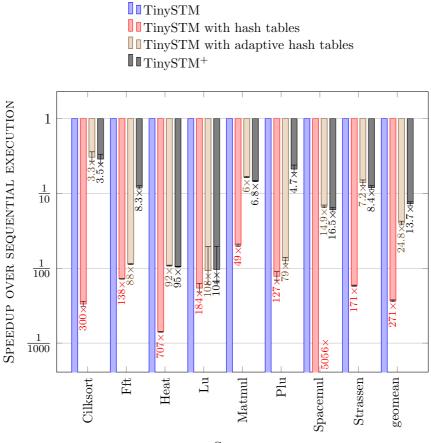

| Figure 4.2 Runtime comparison of different data struc-<br>tures for read and write sets in STM, evaluated on<br>automatically parallelized <i>Cilk</i> programs, executed in       |    |

|                                                                                                                                                                                    | 8  |

| Figure 4.3 Breakdown of TinySTM <sup>+</sup> overhead on different<br>programs from STAMP and the $Cilk$ example pro-                                                              |    |

| 0                                                                                                                                                                                  | 0  |

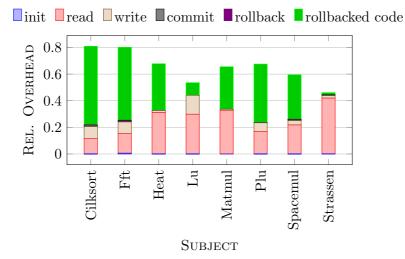

| Figure 4.4 Runtime for speculative indexing of C files of<br>varying size and with a varying number of conflicts, ex-<br>ecuted either sequentially, or speculatively parallelized |    |

| 0 0                                                                                                                                                                                | 2  |

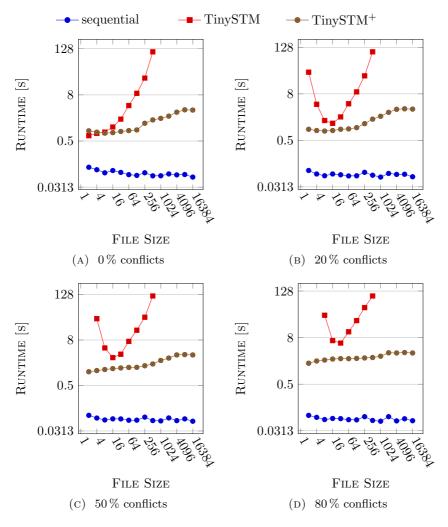

| Figure 4.5Overhead breakdown for the <i>cindex</i> program<br>executed in TinySTM $^+$ .8                                                                                          | 4  |

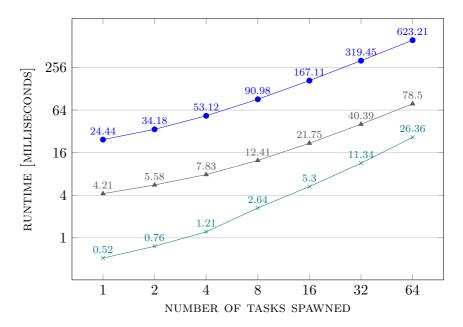

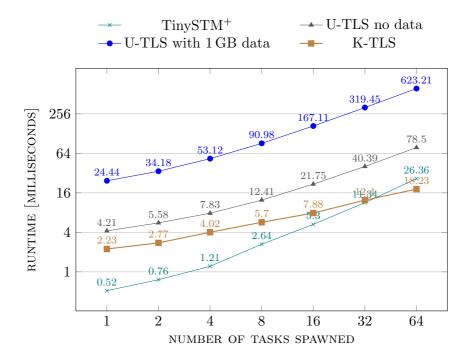

| Figure 5.1 Overhead of spawning a task list of varying size<br>in U-TLS against TinySTM <sup>+</sup>                                                                               | )1 |

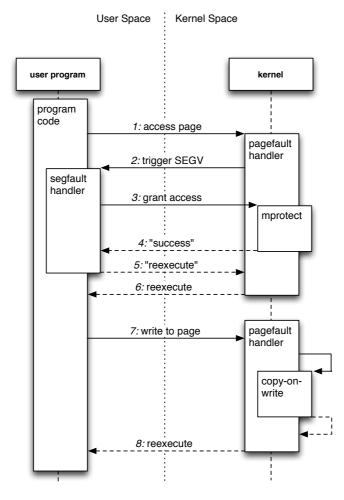

| Figure 5.2 Handling of page faults during execution in                                                                                                                             |    |

| U-TLS                                                                                                                                                                              | 4  |

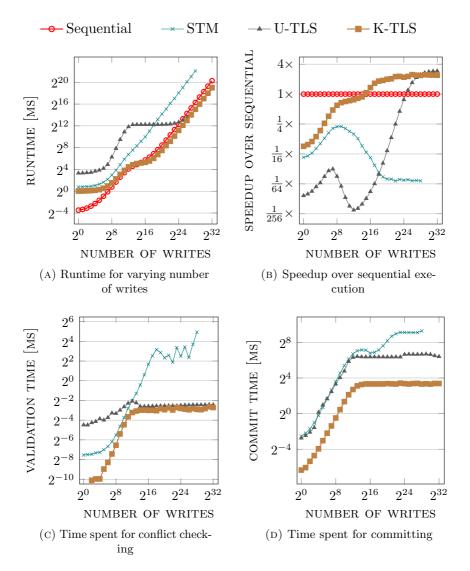

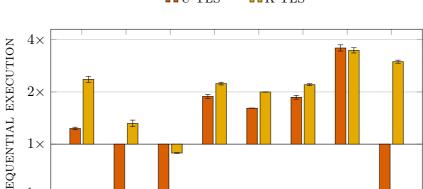

| Figure 5.3 Performance of TinySTM <sup>+</sup> and U-TLS in an      |     |

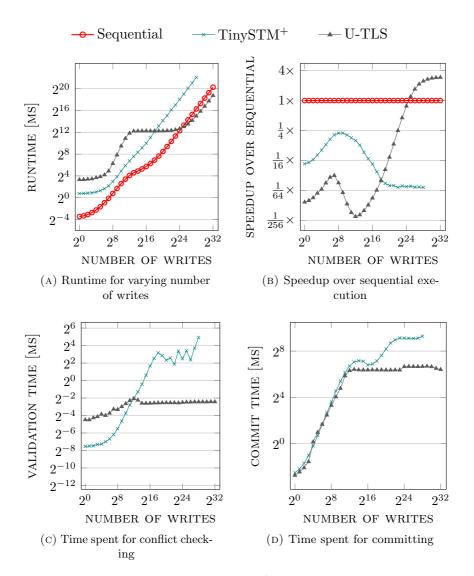

|---------------------------------------------------------------------|-----|

| artificial benchmark, in which each task randomly                   |     |

| updates memory cells within a $16\mathrm{MB}$ memory block.         | 106 |

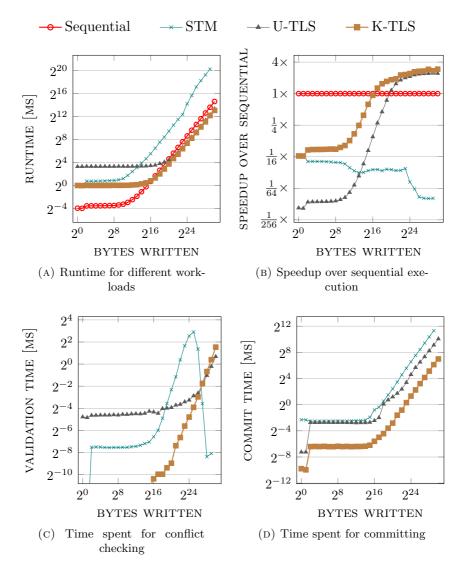

| Figure 5.4 Second benchmark comparing U-TLS perfor-                 |     |

| mance against $TinySTM^+$ . This time each task writes              |     |

| a linear block of memory with varying size. $\ldots$ .              | 108 |

| Figure 5.5 Speedup of U-TLS achieved by automatic par-              |     |

| all<br>elization of eight programs from the $Cilk$ suite            | 114 |

| Figure 6.1 Overhead comparison for spawning a task list             |     |

| of varying size in K-TLS versus U-TLS and multi-                    |     |

| threaded systems.                                                   | 144 |

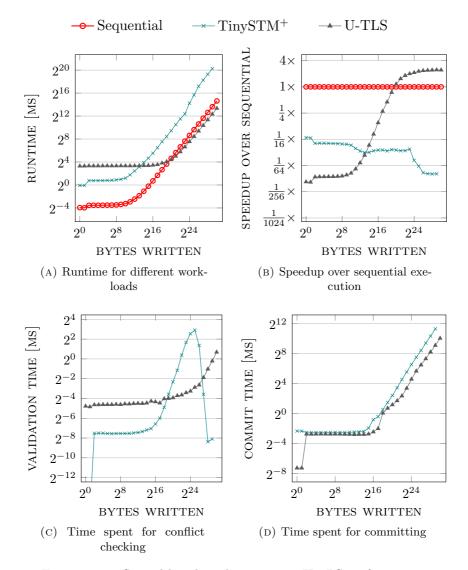

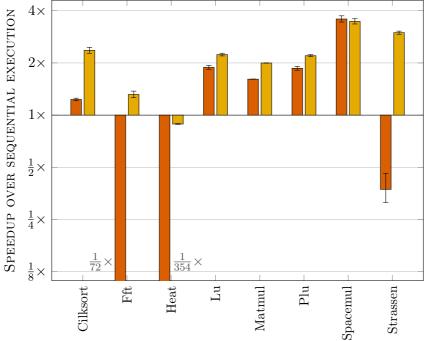

| Figure 6.2 Performance of the different runtime systems in          |     |

| an artificial benchmark, in which each task randomly                |     |

| updates memory cells within a $16\mathrm{MB}$ memory block          |     |

| (cf. Figure 5.3). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 146 |

| Figure 6.3 Performance comparison of K-TLS, U-TLS and               |     |

| $\mathrm{TinySTM^{+}}$ in a benchmark in which each task writes     |     |

| linearly to a memory block of varying size (cf. Fig-                |     |

| ure 5.4). $\dots$                                                   | 147 |

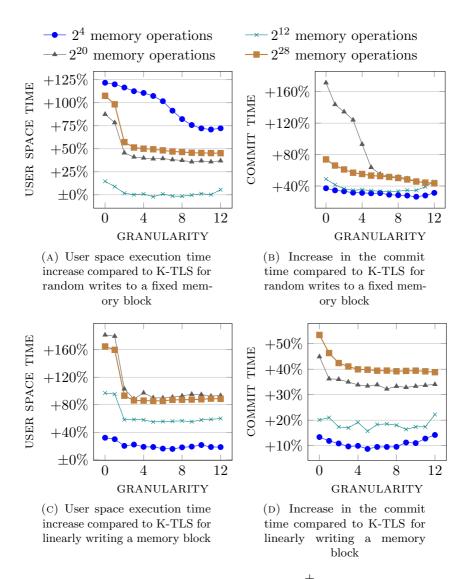

| Figure 6.4 Comparison of the speedup achieved by auto-              |     |

| matic parallelization of eight programs from the $Cilk$             |     |

| suite.                                                              | 152 |

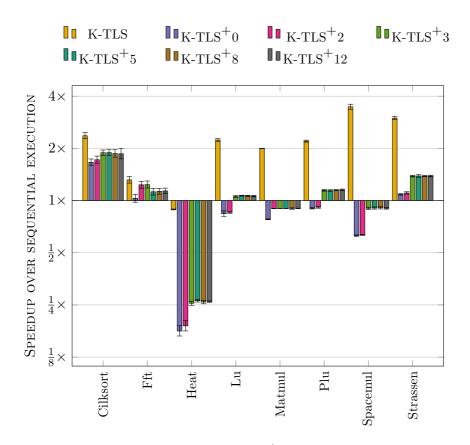

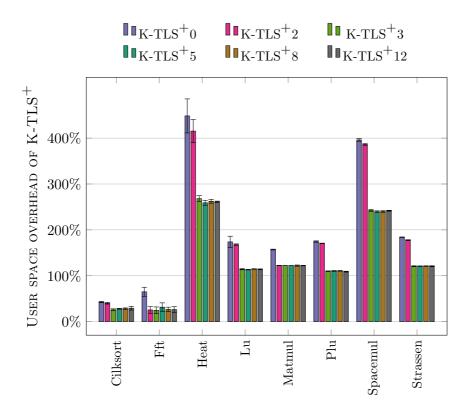

| Figure 6.5 Overhead introduced by K-TLS <sup>+</sup> for tracking   |     |

| memory accesses during execution and using it during                |     |

| $\operatorname{commit.}$                                            | 154 |

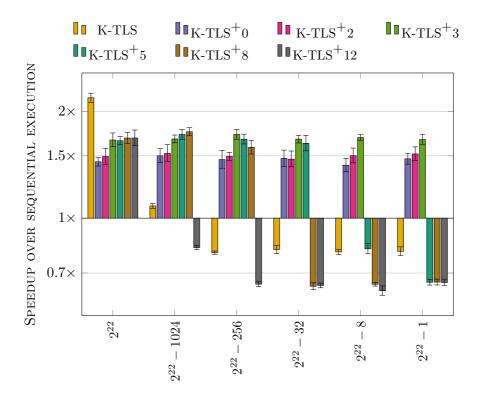

| Figure 6.6 The speedup of K-TLS <sup>+</sup> with different gran-   |     |

| ularities over sequential execution on Cilk programs                |     |

| without memory conflicts.                                           | 158 |

| Figure 6.7 Overhead caused by tracking memory updates               |     |

| in user space at different granularities, relative to exe-          |     |

| cution in K-TLS.                                                    | 159 |

| Figure 6.8 Performance of <i>Cilksort</i> for different sizes, exe- |     |

| cuted in K-TLS or K-TLS <sup>+</sup> with different granularities.  | 160 |

# LIST OF TABLES

| Table 4.1 C  | C interface of TinySTM, used for automated                                                                                                                            |    |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| instrum      | entation of speculatively parallelized regions $\boldsymbol{\theta}$                                                                                                  | 63 |

| Table 4.2 C  | haracteristics of the STAMP benchmark suite                                                                                                                           |    |

| program      | ns usually used to evaluate STM performance. 7                                                                                                                        | 74 |

| Table 4.3 Cl | haracteristics of the <i>Cilk</i> example programs, au-                                                                                                               |    |

| tomatica     | ally parallelized and instrumented using STM                                                                                                                          |    |

| to guard     | d against misspeculation                                                                                                                                              | 75 |

|              |                                                                                                                                                                       |    |

| Table 5.1 T  | LS interface to be called from generated code.                                                                                                                        | 39 |

| Table 6.1 C  | haracteristics of eight programs from the <i>Cilk</i>                                                                                                                 |    |

|              | a suite, automatically parallelized using the                                                                                                                         |    |

|              | <i>iba</i> framework                                                                                                                                                  | 50 |

| Table 6.2 P  | Performance of eight programs from the <i>Cilk</i>                                                                                                                    |    |

| program      | n suite, automatically parallelized using the                                                                                                                         |    |

| Sambam       | ba framework                                                                                                                                                          | 51 |

| Table 6.3 St | tatic number of <i>meta data unit</i> updates for the                                                                                                                 |    |

| benchm       | ark programs from the $Cilk$ suite 15                                                                                                                                 | 56 |

|              |                                                                                                                                                                       |    |

|              | haracteristics of the different speculative run-                                                                                                                      |    |

| time sys     | stems examined in this thesis. $\ldots \ldots \ldots$ | j4 |

# LIST OF ALGORITHMS

| 5.1 | Pseudo-code implementation of U-TLS (first part; con-                   |

|-----|-------------------------------------------------------------------------|

|     | tinued in Algorithm 5.2) $\ldots \ldots \ldots \ldots \ldots \ldots 92$ |

| 5.2 | Pseudo-code implementation of U-TLS (second part;                       |

|     | continuation of Algorithm 5.1) $\ldots \ldots \ldots \ldots 33$         |

| 6.1 | Pseudo-code implementation of K-TLS                                     |

| 6.2 | Computations done for a single-bit shadow memory                        |

|     | update. See Algorithm $6.3$ for the actual LLVM in-                     |

|     | structions emitted to implement this computation.<br>$134$              |

| 6.3 | Instrumentation of one store instruction in LLVM. $$ 135                |

| 6.4 | Pseudo-code implementation of a multi-MDU update.                       |

|     | See Algorithm $6.5$ for the actual LLVM instructions                    |

|     | emitted to implement it                                                 |

| 6.5 | LLVM instructions emitted to implement a multi-MDU                      |

|     | update                                                                  |

## CHAPTER 1

## INTRODUCTION

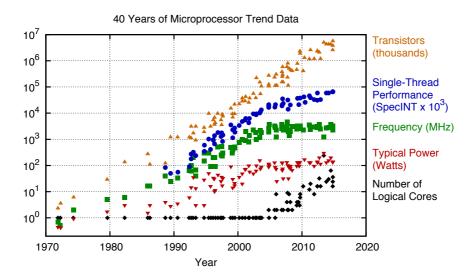

The increase in the density of integrated circuits continues till today. Since the beginning of the millennium, however, processor manufacturers struggle to translate this to increased clock speeds, and thus increased single-thread performance. The limiting factor is mostly *power consumption*: It increases exponentially with a linear increase of frequency. Figure 1.1 shows that around the year 2000, power consumption reached the critical level of 100 watts. Dissipating the produced heat becomes increasingly difficult if this level is exceeded, making such processor designs uneconomical. However, Figure 1.1 also shows that the number of transistors continues to grow exponentially. This is because the size of the semiconductors—constituting the transistors—can still be reduced, allowing Moore's law to hold true at least for the next couple of years<sup>1</sup>. These additional transistors are used by processor vendors to place *multiple processor cores* on a single die. From 2005 onwards we see an exponential growth of the

<sup>&</sup>lt;sup>1</sup>The current manufacturing process uses 14 nm structures, with 10 nm technology being developed. At about 5 nm, the structures cannot be reduced any further on silicon based dies due to increasing quantum tunneling effects.

FIGURE 1.1: The number of transistors is growing exponentially over the full time range, while frequency and power consumption stopped increasing shortly after the year 2000. Instead, the number of cores starts rising exponentially from that time on.

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten. New plot and data collected for 2010–2015 by K. Rupp [93].

number of logical cores in a processor. This development, however, shifts the burden to translate advances on the processor's side into increased software performance to the software developers.

In order to benefit from the computational power of multiple cores, software needs to be *parallelized*. The traditional approach is manual parallelization. It requires expert programmers that fully comprehend the dependencies within the software that should be parallelized, and are able to introduce the right set of synchronization mechanisms to still guarantee correctness of the program while exposing the maximum amount of parallelism. As manual parallelization is a tedious and error-prone task, and the resulting program is fragile with respect to later changes of the code, it is only done for specific and important software. Nowadays the majority of software still executes single-threaded.

The alternative to manual parallelization is automatic parallelization. It does not require the skill set and investment of time of manual parallelization. Instead, the traditionally developed sequential program is analyzed and automatically transformed into a parallel program. Over the last decades, many approaches have been presented which are able to handle different classes of programs. All these parallelization schemes, however, necessitate precise information about dependences in the code. Such dependence analysis is successful for computation kernels with regular memory access patterns, as they often occur in scientific or mathematical computations. If programs get bigger, the picture changes. Dynamic data structures built around pointers often pose hard to solve problems for static analyses. In those cases, dependence analyses typically overapproximate and detect a potential dependence. As modern programs use many of such dynamic data structures, traditional automatic parallelization approaches fail to find a substantial amount of parallelism there.

Speculation is a technique that allows to parallelize such programs anyway. By making optimistic assumptions—e.g. assuming that a potential dependence will not manifest at runtime—parallel code can be generated. The execution of speculatively parallelized code is not guaranteed to succeed at runtime, however. If one of the optimistic assumptions does not hold, the program might produce wrong output or might even crash. Hence, a runtime system is needed to guard the execution against such *misspeculations*, and bring it back to a safe and correct execution state. This thesis investigates and improves the state of the art in software-only runtime systems for speculative parallelization, and argues that such systems are often insufficient for automatic speculative parallelization. We then present novel approaches that use facilities of the operating system and the underlying hardware, and show that using these systems, automatic speculative parallelization often provides great speedups. Our main contributions are as follows:

- We apply *implicit memory tracking* in the form of *software transactional memory (STM)* to the problem of automatic speculative parallelization. We identify the main sources of overhead and propose and implement different solutions. We show that these changes reduce the overhead by orders of magnitude.

- We describe a *virtual-memory based* runtime system for speculative execution along the lines of previously published approaches. We evaluate its performance on several real-world programs and demonstrate an enormous performance benefit compared to STM.

- We further improve both performance as well as the isolation guarantees of the virtual-memory based system by implementing the main functionality directly in the Linux kernel. This is the first work describing such an implementation. In the evaluation, we demonstrate a further significant performance gain.

- We describe a novel approach to address the problem of *coarse* granularity of virtual-memory based systems. By instrumenting the program and keeping minimal metadata about the memory operation of the program, the granularity can be chosen

arbitrarily down to individual bytes. We show that this can be done with moderate overhead.

• We make all systems developed in this thesis available as open source.

### 1.1 Thesis Organization

The thesis is organized as follows:

- After introduction and clarification of general terms in Chapter 1, we review the state of the art in automatic parallelization in general, speculative parallelization, as well as runtime systems for speculative execution in Chapter 2.

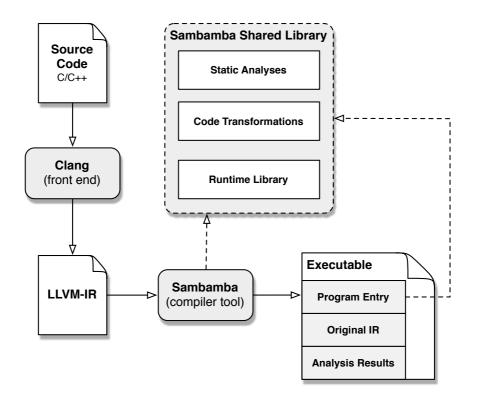

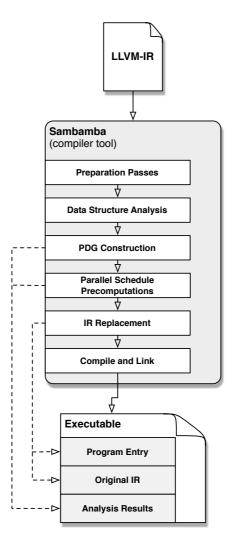

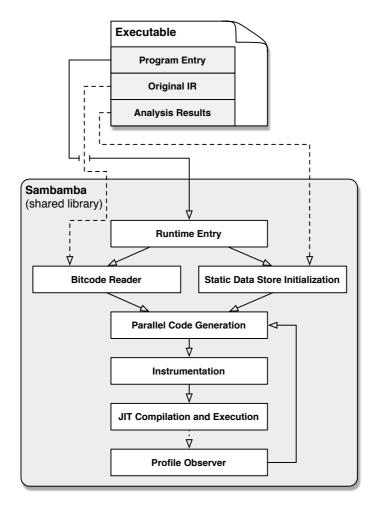

- In Chapter 3, we introduce the Sambamba framework we developed to integrate the different approaches developed in this thesis and automatic parallelization approaches by my colleague Kevin Streit.

- Chapter 4 applies the state of the art software transactional memory system TinySTM to the problem of speculative parallelization, and shows how to improve the performance substantially.

- In Chapter 5 we introduce our U-TLS system, which implements a virtual-memory based runtime system for speculative parallelization in user space.

- Chapter 6 shows how to transfer the same concepts to the kernel space, and evaluates the performance gain of this system called

K-TLS. In Section 6.2, we supplement K-TLS with instrumentation for variable granularities and evaluate the performance impact of this addition. We call this system K-TLS<sup>+</sup>.

• Finally, Section 7 concludes this thesis and lists ideas for future work.

### 1.2 Terminology

As different authors in the literature use different names for the same concepts, and sometimes mean different concepts by a specific term, we clarify the vocabulary used in this thesis in the following compilation of general terms related to speculative parallelization.

- **Parallelization.** Parallelizing a piece of software means preparing it for parallel execution. There is a variety of approaches for parallelization. It can either be done statically (at or before compile-time), or dynamically (at run-time). In either case it can optionally be speculative. All these cases are further detailed below.

- Static Parallelization. Parallelization is called static if it happens before actually executing the program. It can either be performed manually by a developer (potentially assisted by language extensions, libraries or compiler hints), or by a compiler which automatically determines appropriate code transformations and performs them at some stage during compilation. Also in static parallelization, there might exist different parallel variants of the same code, or also a sequential variant. If

just the decision which of these variants to execute is made at run-time, we still consider this static parallelization.

Static parallelization may also utilize *profiling information* generated at previous runs of the program.

**Dynamic Parallelization.** In dynamic parallelization, the decisions where to parallelize as well as the generation of the parallel code happen at run-time. This means that a just in time (JIT) compiler needs to be available to dynamically recompile parallelized functions. Typically, profiling information or other dynamic data is used to guide the dynamic parallelization decisions.

All dynamic parallelization approaches that we are aware of are *automatic* approaches.

- Automatic Parallelization. As the name suggests, automatic parallelization is performed without involving interaction of a developer. Instead, static or dynamic *parallelization analyses*, typically consisting of points-to, alias or shape analyses, are used to find parallelizable locations in the program.

- **Speculative Parallelization.** The parallelization of a specific code region is called *speculative*, if the soundness of its execution (with regards to the sequential semantics) cannot be inferred before actually starting the execution. This execution is then also called *speculative*. The sequential semantics might be violated with respect to the memory effects, i.e. the modifications to the virtual memory performed by the code, termination effects (non-termination or abortion), or other side effects like system calls executed, for example due to I/O effects.

In order to still provide soundness guarantees when executing speculatively parallelized code, runtime checks have to be installed to determine *misspeculations*.

- Thread Level Speculation (TLS). Speculative execution is any execution that is performed without knowing whether the result can or will be used afterwards. Modern processors for example include *instruction level parallelism (ILP)*: They fetch and execute instructions in parallel or out-of-order in order to increase the throughput. By *speculatively* executing instructions even memory instructions— without knowing yet whether they should really be executed, the amount if ILP can be drastically increased. This is mainly driven by *branch prediction*. Similarly, TLS is used to extract parallelism at the *thread level* as opposed to the instruction level by executing code either without knowing whether it would be executed in sequential execution, or by ignoring data dependences and thus potentially producing wrong results. Both of these techniques are described in the following.

- **Control Flow Speculation.** This form of speculation assumes that certain branches will not be executed, hence it ignores all effects of these blocks. The decision where to speculate can be based on statistical execution frequencies, value profiles, or benefit driven (e.g. speculate that blocks containing calls to the **abort** function will not execute).

Detecting misspeculations of control flow speculation is cheap and does not require collecting any further data. Whenever the corresponding branch is taken, a misspeculation has happened. Memory Speculation. This is the kind of speculation we mostly focus on. Memory speculation means to ignore possible memory effects of parallelized code or to assume non-aliasing of parallel memory accesses without being able to prove this beforehand. The goal is to reduce the number of data dependencies between speculative tasks.

Memory speculation always requires a sophisticated runtime system which tracks the memory regions accessed within parallel tasks, checks for overlaps and performs appropriate actions to recover from misspeculation.

Memory Conflict. A memory conflict (also called memory violation) is reported by the runtime system if it determines that the memory state produced by speculatively parallelized code might not be correct, thus it is a special case of *misspeculation*. In most cases, these checks are not precise, hence memory conflict must be *overapproximated*, leading to *false conflicts* being reported.

A memory conflict generally occurs if a speculative task has read a value from memory which was subsequently overwritten by another task *which commits first* (a minor relaxation of the Bernstein condition [5]). The detection of such conflicts can happen *eagerly* during transactional read or write operations, *lazily* (or *delayed*) during transactional commit, or concurrently by another processing unit.

False Sharing / False Conflict. In memory speculation systems (see above), most often memory is not tracked at the granularity of individual bytes, but in larger chunks. For TLS systems, this often is even the granularity of memory pages (4 kB on

most architectures). Hence disjoint *objects* in memory *share* the same metadata which tracks accesses to this memory, if they are located within the same *memory block* (defined by the granularity). Since accesses to those disjoint memory regions cannot be distinguished by the runtime system, memory conflicts have to be reported *pessimistically* whenever speculative tasks compete for the same block. If a finer granularity had resolved this *memory conflict*, we would call it *false conflict*, because another tracking scheme would not have reported it.

Runtime System. A runtime system is a software library which is available to the program under execution during its run-time, but does not belong to the program itself. It is often triggered by the executing program via *callbacks* (function calls into the runtime system) placed in the executed code, but it can also run concurrently to the executed program and interact with it proactively.

Examples of runtime systems are *just in time* compilers, *software transactional memory* or other speculation guarding systems.

- Sequential Execution. Sequential (sometimes also called *serial*) execution is the execution of code on *one single thread*, hence it is the opposite of parallel execution. In some cases, also *parallelized code* will be executed sequentially, for example if speculative parallelization was detected to fail at run-time.

- **Speculative Task.** A *speculative task* is the dynamic instantiation of one piece of speculative work. In the context of parallelization, speculative tasks are often optimistically executed in parallel

to each other, while a runtime system or the code itself checks for misspeculations. Each task will in the end either *commit* its changes, i.e. merge it into the non-speculative state, or *roll back* and re-execute either speculatively or non-speculatively.

- Strong Atomicity vs. Weak Atomicity. A transactional memory guarantees that the effect of each transaction is either seen completely by other tasks or not at all. This concept is called *atomicity*. Also TLS systems want the individual tasks to execute *atomically*. There are two degrees of atomicity: A strongly atomic system guarantees atomicity with respect to all tasks, independent of whether they are using the same runtime system or not. Strong atomicity in general requires hardware support or special operating system support in order to prevent concurrent code from seeing partial updates during commit. Software TM or TLS solutions typically provide *weak atomicity* only, meaning that atomicity is only provided for other tasks using the same runtime system. If all memory operations for example are executed via the respective STM functions, then tasks observing inconsistent state are detected and re-executed, providing weak atomicity for all the committed tasks.

- Single Global Lock (SGL) Semantics. This is the most simple semantics for executing multiple critical sections in parallel threads. The semantics is as if a single global lock would be taken before entering a section, and released then leaving it. This definition makes it very easy to reason about the semantics of a parallel program, as race conditions are excluded and the amount of nondeterminism is reduced significantly.

(Ir-)Regular Data Structure. Regular data structures are data structures with a well-defined shape in memory, like C-strings and arrays. As those structures occupy contiguous bytes in memory, they are typically easy to analyze statically.

Irregular data structures on the other hand are scattered over the memory space (often in the heap) and connected via pointers. Since pointers to different objects might be placed in the same memory, static analyses often have to overapproximate, making accesses to disjoint parts of the irregular data structure undistinguishable. Those data structures therefore cause problems for automatic parallelizers. If corresponding program locations are to be parallelized anyway, memory speculation is a resort.

### 1.3 Publications

This thesis builds on the following publications (in chronological order):

- Thread-Level Speculation with Kernel Support. In Proceedings of the 25th International Conference on Compiler Construction (CC), March 2016. Clemens Hammacher, Kevin Streit, Andreas Zeller, and Sebastian Hack.

- Generalized Task Parallelism. In ACM Transactions on Architecture and Code Optimization (TACO), Volume 12, Number 1, January 2015. Kevin Streit, Johannes Doerfert, Clemens Hammacher, Andreas Zeller, and Sebastian Hack.

- Sambamba: Runtime Adaptive Parallel Execution. In Proceedings of the 3rd International Workshop on Adaptive Self-Tuning Computing Systems (ADAPT), January 2013. Kevin Streit, Clemens Hammacher, Andreas Zeller, and Sebastian Hack.

- SPolly: Speculative Optimizations in the Polyhedral Model. In Proceedings of the 3rd International Workshop on Polyhedral Compilation Techniques (IMPACT), January 2013. Johannes Doerfert, Clemens Hammacher, Kevin Streit, and Sebastian Hack.

- Sambamba: A Runtime System for Online Adaptive Parallelization. In Proceedings of the 21st International Conference on Compiler Construction (CC), March 2012. Kevin Streit, Clemens Hammacher, Andreas Zeller, and Sebastian Hack.

- Profiling Java Programs for Parallelism. In Proceedings of the ICSE Workshop on Multicore Software Engineering (IWMSE), 2009. Clemens Hammacher, Kevin Streit, Sebastian Hack, and Andreas Zeller.

## CHAPTER 2

# STATE OF THE ART

In this chapter we investigate the state of the art in the field of speculative parallelization. To this end, we first review the most prominent and also recent automatic parallelization approaches, and then specifically focus on speculative parallelization and the runtime systems used during the execution of the resulting programs.

### 2.1 Automatic Parallelization

As there have been decades of research on parallelization, we focus on work which is relevant and related to the topic of this thesis. We thus exclude any languages or language extensions for manual parallelization, even if automatisms for extracting or enhancing parallelism were presented (like e.g. Galois [57] or PetaBricks [3]). As we focus on statically compiled languages, we also exclude previous work for languages which are executed in an interpreter or virtual machine (like e.g. Jrpm [18]). In automatic parallelization, an essential step is determining the data dependencies and control dependencies within a program. In 1987, Ferrante et al. [33] came up with the notion of a *program dependence* graph (PDG) which encapsulates those dependencies and has since then often been used as the basis for parallelization and other program optimizations. If the nodes in the PDG carry information about the actual operation to be performed, it fully describes the semantics of a program, and can thus be used as an alternative representation.

Burke et al. [13] use the PDG to statically detect fork-join based parallelism. In contrast to other authors they not only focus on loops, but also detect parallelization opportunities in straight-line code. As their output is a source-code program again, they describe a Fortranlike target language featuring a DOALL construct for parallelizing loops and the COBEGIN and COEND keywords for marking parallel code sections. In order to remove some data dependencies they include a privatization analysis. Their parallelization algorithm works by first marking everything to be parallel, and then handling each data dependency by either privatizing the corresponding memory or serializing the respective tasks. They also consider low-level synchronization primitives to fulfill data dependencies between parallel tasks, but decide against them for performance and simplicity reasons.

Sarkar [101] describes a quite similar system which also statically generates structured parallelism from Fortran programs by partitioning the PDG. In contrast to Burke et al., Sarkar allows for data dependencies between parallel tasks and adds explicit synchronization via the WAITING keyword. He also discusses the trade-off between *ideal parallelism* exploiting all the parallelism in the program and *useful parallelism* excluding certain non-profitable opportunities. His solution is the definition of a *cost function* containing overhead for task spawning and synchronization, and also includes profile data like loop frequencies and branch probabilities [102]. Based on this objective function, he iteratively merges parallel tasks if this decreases the predicted *parallel execution time*.

Saltz et al. [100] detect wavefront-parallelizable loops by using a combination of static and dynamic analyses. They statically detect so called *start-time schedulable* loops, for which the access pattern does not depend on any values computed inside the loop. Then they extract *inspector code* which assigns a wavefront number to each loop iteration, such that each iteration only has dependencies to iterations with smaller wavefront ids. They place code to execute the wavefronts in increasing order, and parallelize the inner loop, which executes all iterations within that wavefront. Overall, this builds a dynamic variant of *loop skewing*.

In 1994, the SUIF compiler infrastructure [123] is presented. It features its own intermediate representation (IR) and contains several analyses and transformations, including a loop parallelizer. It is based on an *array dependence analysis*, and optimizes for both parallelism and locality. For code generation, it translates back to C code, which is compiled by a traditional compiler and linked against a runtime library featuring parallel execution. Hall et al. [38] later extend this approach with a better parallelization analysis, including reduction and privatization detection.

Still in 1994, Rauchwerger and Padua publish the first *dynamic* and *speculative* parallelization approach, called the *privatizing DOALL* test [87]. They statically extract *inspector code* from loops which

determines whether there are any cross-iteration dependencies. If this is the case at runtime, the loop is executed sequentially. Otherwise, it is executed as a DOALL loop. They later extend this approach to also detect *partially* parallel loops [85]. Based on the information computed by the inspector code, the *scheduler* dynamically generates an execution schedule, which is then executed by the *executor code*. Their approach is also able to detect privatization and reduction opportunities during inspection. The applicability, however, is limited: In order to generate inspector code, the accessed memory locations must be known before entering the loop. They mainly focus on applications operating on one *shared array*, where only the subscripts of the array accesses need to be recorded.

One year later, they come up with an improved scheme known as the *LRPD test* [86]. It does not inspect the loop before executing it, but rather speculatively executes it as a DOALL loop and at the same time keeps track of the accessed memory locations (i.e. array subscripts). Afterwards it checks whether the loop was in fact fully parallel, and otherwise rolls back and re-executes sequentially. The problem of restoring the non-speculative state, however, is not addressed. They briefly discuss ideas how to solve this in software, but in the evaluation they instrument all programs manually.

Another important model, which can also be used for parallelization purposes, is the *polytope model* [29, 30, 76]. It describes a perfect loop nest of depth k as a convex k-dimensional polytope, where each integer point corresponds to one iteration of the innermost loop, and its position determines the values of the iteration variables of the surrounding loops. Also the dependencies between loop iterations are described by polyhedra. This allows to model most of the classical loop transformations as affine transformations of these polyhedra. In fact, the problem of optimally *scheduling* the execution of a polyhedron subsumes most of these transformations. The scheduler often tries to minimize an objective function over the polyhedra. This way, also parallelization can be included in the output model of the scheduler, and can thus be seen as an optimization problem in the polytope model, as shown by Lengauer [60]. Beside generating maximum parallelization, the objective function can also include other factors like locality in the memory accesses, or it can be restricted by adding resource constraints. Also Feautrier explicitly describes automatic parallelization in the polytope model [28] and provides a nice summary of previous work. Others build on this work by also integrating loop splitting [22] or porting it to modern concepts like OpenMP-based parallelization [10].

Lim and Lam describe a similar system [62] which also maps iterations of a loop nest to a new domain using affine expressions, subsuming many existing loop transformations. In contrast to polyhedral techniques, they explicitly focus on parallelization, and they also support pipeline parallelism. Also, they do not overapproximate dependencies by dependence vectors.

In 1999, Rugina and Rinard [91] approach the problem of inaccuracies in state-of-the-art points-to analyses when it comes to pointer arithmetic and recursive algorithms. They generate a symbolic expression for each memory access, and propagate the expressions up to the method start. Using a fixed-point analysis, they recursively inline the expressions for called functions into the callee. They then analyze whether the memory accesses of adjacent function calls are disjoint, and parallelize independent function calls accordingly. The evaluation demonstrates that this approach can be used for many classical divide-and-conquer algorithms like matrix multiplication or mergesort.

Rus et al. in 2003 describe a hybrid static and dynamic analysis to detect DOALL loops [95]: They statically construct the symbolic dependence set for a loop, and either prove it empty statically, or generate code to do the test dynamically when the actual input values are known. In 2007, they improve the approach by statically generating a disjunction of predicates which prove the dependence set empty [94], and then generate code to check the predicates at runtime. This improves the performance compared to the full emptiness check they were performing before.

Bhowmik and Franklin [6] build on the SUIF platform [38, 123] to create a *speculative parallelization framework*. They argue that speculation is absolutely necessary in order to extract larger amounts of thread-level parallelism from general-purpose applications. Using profile information, they statically find the best spawn point for each basic block and loop iteration. For the speculative execution they assume hardware support for lightweight thread spawning, detecting memory conflicts, and rollback. Even though they make optimistic assumptions about the performance of such hardware extensions, they also note that the *thread formation* is essential for guaranteeing success. After all, already in 1986 Sarkar and Hennessy showed that finding the optimal thread partitioning of a program is NP-complete [103].

Another important work is *decoupled software pipelining* (DSWP), as described by Rangan et al. in 2004 [84]. The original idea is a

hardware extension which can be used for (manual) parallelization. It allows to efficiently forward values from one thread to another in a FIFO manner, and is designed to efficiently implement pipeline parallelism. Parallel threads just issue produce and consume instructions annotated by an integer tag, where a *consume* returns the first unused produced value with the same tag, or blocks until such a value is produced by another thread. The proposed programming model would be to split a loop into several *pipeline stages* where each stage only has dependencies to previous stages or to itself. By explicitly forwarding the values for each dependence, the sequential semantic is preserved. Ottoni et al. [74] describe how to automatically generate such parallel programs using static analyses and transformations. Later extensions include support for multiple parallel instances of individual pipeline stages in order to compensate unbalanced stages and provide more parallelism [83]. Vachharajani et al. [117] add speculation support, but it only allows for control-flow speculation and assumes *versioned memory* for efficient rollbacks. Huang et al. [50] propose to parallelize individual pipeline stages using other independent parallelization techniques, and in other work propose to also parallelize iterations of different loops [49]. Even though no paper explicitly mentions this, later work like Parcae [82] suggests that DSWP now also works without special hardware support. Parcae itself, however, does not focus on parallelization, but on the automatic platform-wide tuning of parallelization in order to maximize overall throughput.

POSH [63], built on top of gcc, also assumes special hardware with support for thread level speculation (TLS). Using profiling data, it speculatively spawns loop iterations, loop continuations, function calls or their continuation before reaching their actual sequential execution point. The assumption here is that the programmer gave enough structure to the program by encapsulating independent computations in subroutines or computing independent values in disjoint loop iterations. Thus, no loop transformations or preprocessing on basic block or instruction level is performed. If data dependencies are not fulfilled at the time when a speculative task is spawned, value prediction provides a probable input value.

Zhong et al. present another approach for speculative DOALL execution of loops [124]. They increase the amount of parallelism detected by identifying privatization and reduction opportunities and speculatively apply loop fission and other transformations. Also, they ignore long-distance cross-iteration data dependencies, as they are unlikely to cause rollbacks at runtime. During execution, they assume full hardware support for TLS, covering both the memory and register values. Additionally, they assume a hardware network to efficiently send register values between different cores.

In 2010, Vandierendonck et al. describe the Paralax [118] infrastructure, which aims to automatically parallelize irregular pointer- and control-intensive C applications. As static analyses are not good enough to precisely analyze such applications, they often have to fall back to overapproximations. Therefore, a set of annotations is proposed which can be used by the programmer to facilitate alias analysis or dependence analysis. Using the information provided via these annotations in combination with powerful analyses like the *data structure analysis* (DSA) [59], the authors are able to extract a substantial amount of pipeline parallelism from programs like bzip2 that were previously considered as hard to parallelize. Campanoni et al. provide an interesting new usage for sibling processors sharing the same first-level cache (as in hyper-threading on Intel architectures). Their HELIX [16] system is a classic loop parallelizer with explicit synchronization for control and data dependencies. They noticed that processors often stall while waiting for a cache line which was previously written by another core. This not only happens when forwarding values between parallel tasks, but also when acquiring a lock which was previously released by another core. In order to reduce these stalls, they use the second (virtual) core for prefetching values needed by the first core. This allows the first core to execute the actual code much faster since the chances for the accessed data to be present in the cache are increased. Later, they propose to add an explicit hardware mechanism for implementing locks more efficiently [15]. To that end, they propose an ISA extension with signal and wait instructions and a ring architecture which proactively forwards the state of locks to all other cores. This improves performance especially for short-running parallel loop iterations.

# 2.2 Runtime Systems for Speculative Parallelization

This thesis focuses on a specific kind of speculation, namely *memory* speculation. This kind of speculation optimistically ignores certain memory dependencies during parallelization (cf. Section 1.2). In the presence of irregular data structures, it is often a key technique for being able to extract any parallelism. This was discovered and described in many publications by different authors during the last decades (e.g. [6, 63, 110, 119]).

Memory speculation, however, requires *runtime support* to *dynamically check the validity* of the speculative execution. In order to detect overlaps in the accessed memory locations, every access to potentially shared memory needs to be tracked and compared against accesses by concurrent tasks. There are several options for implementing these runtime systems. The most important and most prominent options are discussed in this section.

### 2.2.1 Software Transactional Memory

Even before the potential of thread-level speculation for automatic parallelization was discovered in the late 1990s (e.g. [73, 110], see Section 2.2.4), a quite similar concept was introduced as transactional memory (TM) by Herlihy and Moss in 1993 [44]. It was designed as an alternative to lock-based programming, which is known to be prone to many kinds of errors, like priority inversion, where a high-priority task has to wait for a lower-priority task which holds a lock, convoying, where a task holding a lock is interrupted for a longer time by a page fault or any system call, and hence other tasks waiting for the lock cannot proceed either, and—probably most well known—deadlocks, which happen if two tasks take the same locks in different order.

Because of these problems, and also for efficiency reasons, researchers proposed to use *lock-free* (or *non-blocking*) concurrent data structures [35, 42, 46, 58, 111]. These are often hard to implement using the single word *compare-and-swap* (CAS) operation. TM provides the same semantics as CAS, but on a much larger number of independent memory locations. Therefore, one of its first uses was implementing

lock-free concurrent data structures. In this setting, critical sections are most often rather short, and just a few memory locations are accessed. Therefore, the original design only features these short critical sections.

*Memory transactions* are often compared to database transactions, featuring the ACID properties: Atomicity guarantees that each transaction appears to either have executed completely, or not at all. This is given for TM because each transaction either commits all its changes, or it rolls back, discarding all changes to visible state. In concurrent systems, atomicity also implies that no intermediate state is observable at any time. Here, the literature differentiates *weak atomicity*, where only concurrently executing speculative tasks are not allowed to observe intermediate states, and strong atomicity where this also extends to non-transactional code. The latter is hard to achieve without hardware support, since multiple independent memory locations cannot be written simultaneously in software. Consistency defines the property that each transaction transfers the system from one valid state to another valid state. In TM, this property strongly depends on the semantics of the individual tasks: If they are consistent under the single global lock semantics, however, TM guarantees consistency, too. *Isolation* means that there exists a total order in which the critical sections would have produced the same outcome if executed sequentially. This feature requires atomicity, but provides more guarantees. Especially, it requires the effects of all transactions to be applied to the global state in the end. The *durabil*ity feature defines that state changes by committed transactions will be persistent even in the case of hardware failures or other events. It does not apply to TM since all changes remain in main memory.

Even though it was designed as an alternative to lock-based parallel programming, TM can also be used to implement thread level speculation (TLS) [66, 96, 97]. Since transactional memory in general does not impose any ordering between transactions executing in parallel, special care has to be taken by the generated code to ensure correctness. Some approaches require a TM system which provides a global *commit order*, others establish a commit order themselves. In the remainder of this section, we review the evolution and the state of the art in TM implementations in software. The next section will introduce hardware implementations and discuss their use for TLS.

After the introduction of the concept of transactional memory, Shavit and Touitou describe and implement the first pure software implementation in 1995, since then called STM [106]. It already features word-level conflict detection and hence can be used for any imperative language—in contrast to all the approaches for object-oriented languages, where transactional metadata can easily be stored in the object header [40, 41, 90, 121, 122]. The authors provide proofs for the correctness and the liveness of their implementation. However, it is specialized to so called *static transactions*, where the full data set the transaction operates on is known in advance, making it easy to privatize and access speculative state. As an example application, they implement a *k-word compare-and-swap* using their STM.

In 2003, Herlihy et al. describe the first *dynamic* STM implementation, called DSTM [43]. It supports an arbitrary and unknown number of objects to be accessed by each transaction. It is however still not tailored towards automatic application by a compiler, since objects accessed transactionally need to be accompanied by a *TMObject* object with the same live range, making this system an *object-based*

STM system. If transactions work on irregular data structures like trees or linked lists, these data structures need to be changed to also include the *TMObject* objects.

In 2006—after the rise of multi-core processors—several new designs and implementations were proposed: Saha et al. present McRT-STM [99], a dynamic word-based STM implementation which is executed inside the Multi-Core RunTime (McRT) environment. In contrast to DSTM, transactional metadata is not stored within individual objects, but in a global data structure indexed by the *cacheline address* of the accessed object. This allows for a straight-forward code instrumentation via a compiler, but raises other issues like *false* sharing, leading to false conflicts. McRT-STM allows for different STM configurations: In the *reader locking* configuration, each memory location is associated with a reader-writer lock, which is taken on each transactional access. In read versioning on the other hand, no locks are taken on reading accesses, instead the read version number is recorded and compared against the current state on commit. A second choice is *write buffering*, where speculative changes are stored in private memory and only written back during commit, versus *undo logging*, where changes are written to main memory directly and the original value is kept in private memory for restoring it during rollback. For different applications different configurations perform best, depending on the access patterns of the speculative tasks, but also on the execution platform. In their evaluation, read versioning and undo logging performed best. However, McRT-STM leverages the scheduler of the McRT system to increase performance and avoid deadlocks, so it can only be used within that system. McRT-STM also provides object-based conflict detection like the other approaches

mentioned before, but in a statically compiled language, which is not strictly object-oriented. This is achieved by modifying the McRT internal memory allocator, so it is only applicable to objects on the heap, and only works within the McRT execution environment.

Still in 2006, Riegel et al. [89] as well as Dice et al. [24] introduce the concept of a global version-clock (or timestamp) to efficiently revalidate the read set and to detect read-after-write (RAW) violations (missing an update from an already committed transaction). Just as Saha et al., they are using a single global array of locks for write locking and storing version numbers. For assigning locks to memory stripes, they generally use simple hash functions.

Dice et al. [24] implement these techniques in their *Transactional Locking II* (TL2) system, which since then serves as a reference implementation that many follow-up approaches compare against. In contrast to Saha et al. (see above), they are using write-buffering and commit-time locking. Write-buffering simplifies the rollback process, but introduces overhead at each memory load, since the write-log has to be searched for an entry before reading from main memory. Commit-time locking again reduces the rollback cost and ensures that write locks are held as shortly as possible, but delays the detection of memory conflicts and requires to re-validate the read set after acquiring all write locks.

Riegel et al. [89] call their approach *Lazy Snapshot Algorithm* (LSA) and provide an implementation called TinySTM [31, 32]. They use a global timestamp to establish a *validity range* for each transaction. This range is narrowed on a memory read which is younger (i.e. larger version number) than the start of the range. Once the validity range

becomes empty, the read-log is re-validated to make sure that the transaction operates on any valid "memory snapshot" (hence the name LSA). TinySTM can be configured for either undo-logging or writebuffering (also called write-through and write-back), and commit-time or encounter-time locking<sup>1</sup>. In the performance evaluation, TinySTM outperforms TL2 in all configurations, especially if the benchmark shows high contention rates. This is because encounter-time locking detects memory conflicts earlier and thus avoids useless work.

In 2007, Wang et al. [120] extend McRT-STM by a timestamp mechanism similar to that of TL2, and introduce language constructs for using STM in C and C++ programs. They also describe the compiler transformations and optimizations to generate efficient transactional programs.

In 2009, Mehrara et al. propose the STMlite system [66], which is the first STM system specifically targeted at *automatic parallelization*, in this case focusing on loops only. They use a central commit unit called *transaction commit manager* (TCM), which checks for conflicts between transactions. Additionally, each transaction stores *read-* and *write-signatures* similar to bloom filters [8], but—in contrast to earlier proposals [17]—implemented entirely in software. Those signatures are then also transferred to the TCM for conflict detection. This ensures fast transactional reads and writes, since only thread-local data structures are updated. In return, one single processing unit—the TCM—has to do all conflict checking, which might become a bottleneck. STMlite uses lazy updates (write-back) in combination with lazy conflict detection (at commit time). This adds the risk of

$<sup>^1\</sup>mathrm{Commit-time}$  locking was added to TinySTM after the papers  $[31,\,32]$  were published.

"zombie transactions", which are defeated by periodically checking the incomplete read- and write-signatures for conflicts with already committed transactions.

Even though STMlite specifically targets automatically parallelized programs, the specific requirements that those applications pose to STMs are not further investigated. In the evaluation, they use the standard STAMP [80] benchmark suite and several smaller applications from different domains, but it remains unclear how STMlite would perform on larger programs.

In the same year, Dragojević et al. present another word-based STM implementation called SwissTM [27]. It was designed with a focus on good performance on a broad range of atomic sections, especially long running ones. The authors claim that especially non-expert programmers and automatically parallelizing compilers might produce those large transactions. Similarly to TL2 and TinySTM, SwissTM uses a *global lock table* of fixed size to resolve read-after-write and write-after-write conflicts. Beside the usual STAMP benchmarks, the authors also evaluate SwissTM on Lee-TM [2], STMBench7 [37] and a red-black tree implementation. In these benchmarks, SwissTM performs better than any other tested STM system.

In 2010, Dalessandro et al. publish about an STM design without any ownership records (like for example locks), which are typically used in STM systems for tagging which transaction holds speculative writes on specific memory locations. The proposed NOrec [21] system instead validates the entire read set after each commit of any concurrent transaction, using value-based validation. They later extend their system [20] to also include hardware transactions utilizing the HTM

features of Sun's prototype Rock processor, and AMD's proposed advanced synchronization features (ASF).

In the same year, Gottschlich et al. develop another implementation called InvalSTM [36]. Instead of validating the read set before committing, they use the opposite approach of invalidating concurrently executing transactions before committing any transaction. They use bloom filters to store the read and write sets, which enables efficient lookup and intersection. This approach is later extended by incorporating hardware transactions by Calciu et al. [14]. By some modifications to the STM system and careful design of the hardware transactions utilizing Intel's RTM technology, they allow for concurrent execution of hardware transactions and software transactions based on InvalSTM. Transactions are first executed in the HTM setting, and if this fails repeatedly, the STM is used as a fallback.