# **Store Buffer Reduction Theorem and Application**

Dissertation zur Erlangung des Grades des Doktors der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

vorgelegt von

**Geng Chen**

Saarbrücken, Mai 2016

Institut für Rechnerarchitektur und Parallelrechner, Universität des Saarlandes, 66123 Saarbrücken

**Tag des Kolloquiums** 11. Mai 2016

Dekan

Prof. Dr. Frank-Olaf Schreyer

Prüfungsausschuss

Vorsitz Prof. Dr. Antonio Krüger

1. Gutachter Prof. Dr. Wolfgang J. Paul

2. Gutachter Prof. Dr. Andreas Podelski

Akademischer Mitarbeiter Dr. Qanru Sun

Copyright © by Geng Chen 2016. All rights reserved. No part of this work may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photography, recording, or any information storage or retrieval system, without permission in writing from the author. An explicit permission is given to Saarland University to reproduce up to 100 copies of this work and to publish it online. The author confirms that the electronic version is equal to the printed version.

### **Abstract**

#### **Short Abstract**

The functional correctness of multicore systems can be shown through pervasive formal verification, which proves the simulation between the system software computation and the corresponding hardware computation. In the implementation of the system software, the sequential consistency (SC) of memory is usually assumed by the system programmers. However, most modern processors (x86, Sparc) provide the total store order (TSO) memory model for greater efficiency. A store buffer reduction theorem was presented by Cohen and Schirmer [CS10a] to bridge the gap between the SC and the TSO. Nevertheless, the theorem is not applicable to programs that edit their own page tables. The reason is that the MMU can be treated neither as a part of the program thread nor as a separate thread. This thesis contributes to generalize the Cohen-Schirmer reduction theorem by adding the MMUs.

As the first contribution of this thesis, we present a programming discipline which guarantees sequential consistency for the TSO machine with MMUs. Under this programming discipline, we prove the store buffer reduction theorem with MMUs.

For the second contribution of this thesis, we apply the theorem to the ISA level and the C level. By proving a series of simulation theorems, we apply our store buffer reduction theorem with MMU to the ISA named MIPS-86. After that, we introduce the multicore compiler correctness theorem to map the programming discipline to the parallel C level.

#### Kurzzusammenfassung

Die funktionale Korrektheit von Mehrkern-Systemen kann durch durchgängige formale Verifikation sichergestellt werden, in welcher die Simulation zwischen Berechnungen der Systemsoftware und der entsprechenden Hardwareberechnungen bewiesen wird. Für die Implementierung der Systemsoftware wird vom Systemprogrammierer im Normalfall das Berechnungsmodell der Sequentiellen Konsistenz (SC) zugrundegelegt. Die meisten modernen Prozessoren (x86, Sparc) bieten jedoch aus Effizienzgründen stattdessen das Berechnungsmodell der Totalen-Schreibzugriff-Ordnung (TSO) an. Cohen und Schirmer [CS10a] präsentieren ein Schreibpufferreduktionstheorem, welches die Lücke zwischen SC und TSO schließt. Dieses Theorem kann allerdings nicht auf Programme angewendet werden, die ihre eigenen Seitentabellen bearbeiten. Der Grund dafür ist, dass die Speicherverwaltungseinkeit (SVE) weder als Teil des Programmfadens noch als separater Faden behandelt werden kann. Diese Dissertation liefert einen Beitrag zur Verallgemeinerung des Cohen-Schirmer Reduktionstheorems, in dem die SVE hinzugenommen wird.

Als ersten Beitrag dieser Dissertation präsentieren wir eine Programmierdisziplin welche Sequentielle Konsistenz auf einer TSO Maschine mit SVE garantiert. Unter dieser Programmierdisziplin beweisen wir das Schreibpufferreduktionstheorem mit SVE.

Als zweiten Beitrag dieser Dissertation wenden wir das Theorem auf der Ebene der Befehlssatzarchitektur und der C Ebene an. Durch eine Reihe von Simulationstheoremen wenden wir unser Schreibpufferreduktionstheorem mit SVE auf die Befehlssatzarchitektur MIPS-86

| n. Danach führen wir ein Mehrkern-Compiler Korrektheitstheorem ein, welches<br>nierdisziplin auf die Ebene von parallelem C abbildet. | die Program- |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

|                                                                                                                                       |              |

## Acknowledgements

First and foremost, I would like to thank Prof. Wolfgang Paul for offering me an opportunity to study and work with top scientists and patiently advising this thesis. I learned a lot from Prof. Paul's "karate style" of teaching. Working in Prof. Paul's chair is a valuable and unforgettable experience in my life.

I would like to thank all my past and present colleagues. I am especially indebted to Dr. Mikhail Kovalev, as a co-author of the SB reduction theorem who helped me a lot in writing the long paper-and-pencil proof.

I am also very grateful to my parents for supporting me during all these years. Last but not least, thank the Chinese government for offering me the scholarship.

Saarbrücken, December 16th, 2015

Geng Chen

# **Contents**

| 1 | Intro | ductio  | n                                         | 1  |

|---|-------|---------|-------------------------------------------|----|

|   | 1.1   | Relate  | d Work                                    | 3  |

|   |       | 1.1.1   | System Software Formal Verification       | 3  |

|   |       | 1.1.2   | Weak Memory Model                         | 3  |

|   | 1.2   | Outline | e                                         | 4  |

|   | 1.3   | Notatio | on                                        | 6  |

|   |       | 1.3.1   | Basic Notation                            | 6  |

|   |       | 1.3.2   | Automaton                                 | 8  |

|   |       | 1.3.3   | Binary Arithmetic                         | 9  |

| 2 | Stor  | e Buffe | er Reduction with MMU – Theorem and Proof | 11 |

|   | 2.1   | Progra  | mming Discipline                          | 11 |

|   | 2.2   | Forma   | lization                                  | 13 |

|   |       | 2.2.1   | MMU Abstraction                           | 14 |

|   |       | 2.2.2   | Instructions                              | 15 |

|   |       | 2.2.3   | Abstract Machine                          | 17 |

|   |       |         | Configuration                             | 17 |

|   |       |         | Ownership Transfer                        | 18 |

|   |       |         | Semantics                                 | 19 |

|   |       |         | Safety Condition                          | 23 |

|   |       | 2.2.4   | Store Buffer Machine                      | 25 |

|   |       |         | Configuration                             | 26 |

|   |       |         | Semantics                                 | 27 |

|   | 2.3   | Store I | Buffer Reduction                          | 30 |

|   |       | 2.3.1   | Coupling Relation                         | 31 |

|   |       | 2.3.2   | Reduction Theorem                         | 34 |

|   |       | 2.3.3   | Safety of the Delayed Release             | 35 |

|   |       | 2.3.4   | Invariants                                | 37 |

|   |       |         | Ownership Invariants                      | 38 |

|   |       |         | Sharing Invariants                        | 38 |

|   |       |         | Invariants on Temporaries                 | 39 |

|   |       |         | Data Dependency Invariants                | 39 |

|   |       |         | History Invariants                        | 40 |

|   |       |         | MMU Invariant                             | 41 |

|   |       |         | Page Table Invariants                     | 41 |

|   |       | 2.3.5   | Assumptions on Program Steps              | 42 |

|   |       | 2.3.6   | Proof Strategy                            | 42 |

|   | 2.4   | Mainta  | aining Invariants                         | 43 |

|   |       |         | SR Stens                                  | 43 |

|   |               | 2.4.2                                                                  | Commutativity of SB Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                                                           |

|---|---------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   |               | 2.4.3                                                                  | Program Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                           |

|   |               | 2.4.4                                                                  | Memory Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58                                                                                                           |

|   |               |                                                                        | RMW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                           |

|   |               |                                                                        | Read and Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                                                                           |

|   |               | 2.4.5                                                                  | MMU and PF Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                                                                           |

|   | 2.5           | Provin                                                                 | g Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                                                                                           |

|   |               | 2.5.1                                                                  | SB Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                                                           |

|   |               | 2.5.2                                                                  | Program Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92                                                                                                           |

|   |               | 2.5.3                                                                  | MMU and PF Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                           |

|   |               | 2.5.4                                                                  | Memory Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96                                                                                                           |

|   |               |                                                                        | FENCE, INVLPG, SWITCH and WritePTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96                                                                                                           |

|   |               |                                                                        | RMW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97                                                                                                           |

|   |               |                                                                        | Read and Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 99                                                                                                           |

|   | 2.6           | Provin                                                                 | g Safety of the Delayed Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 04                                                                                                           |

|   |               | 2.6.1                                                                  | Intuition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 05                                                                                                           |

|   |               | 2.6.2                                                                  | "Undoing" a Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 06                                                                                                           |

|   |               | 2.6.3                                                                  | Reconstructing Safety Violation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                                           |

|   |               | 2.6.4                                                                  | Simulation Theorem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                                                                                           |

|   |               |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

|   |               |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

| 3 |               |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                           |

| 3 | <b>Inst</b> a | MIPS                                                                   | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                           |

| 3 |               |                                                                        | ISA        1         Processor Core        1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17<br>18                                                                                                     |

| 3 |               | MIPS                                                                   | ISA       1         Processor Core       1         Instruction Layout Overview       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17<br>18<br>19                                                                                               |

| 3 |               | MIPS                                                                   | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17<br>18<br>19                                                                                               |

| 3 |               | MIPS                                                                   | ISA       1         Processor Core       1         Instruction Layout Overview       1         Auxiliary Definitions for Instruction Execution       1         Definition of Instruction Execution       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117<br>118<br>119<br>119                                                                                     |

| 3 |               | MIPS                                                                   | ISA       1         Processor Core       1         Instruction Layout Overview       1         Auxiliary Definitions for Instruction Execution       1         Definition of Instruction Execution       1         Auxiliary Definitions for Triggering of Interrupts       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117<br>118<br>119<br>119<br>127<br>127                                                                       |

| 3 |               | MIPS                                                                   | ISA       1         Processor Core       1         Instruction Layout Overview       1         Auxiliary Definitions for Instruction Execution       1         Definition of Instruction Execution       1         Auxiliary Definitions for Triggering of Interrupts       1         Definition of Interrupt Execution       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 117<br>118<br>119<br>119<br>127<br>127<br>130                                                                |

| 3 |               | MIPS 3.1.1                                                             | ISA1Processor Core1Instruction Layout Overview1Auxiliary Definitions for Instruction Execution1Definition of Instruction Execution1Auxiliary Definitions for Triggering of Interrupts1Definition of Interrupt Execution1Processor Core Transition Function1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 117<br>118<br>119<br>119<br>127<br>127<br>130<br>131                                                         |

| 3 |               | MIPS 3.1.1                                                             | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>119<br>127<br>127<br>130<br>131                                                         |

| 3 |               | 3.1.1<br>3.1.2<br>3.1.3                                                | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>119<br>127<br>127<br>130<br>131<br>131                                                  |

| 3 |               | 3.1.2<br>3.1.3<br>3.1.4                                                | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132                                                  |

| 3 |               | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                       | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>119<br>127<br>130<br>131<br>131<br>132<br>132<br>137                                    |

| 3 | 3.1           | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                              | ISA 1 Processor Core 1 Instruction Layout Overview 1 Auxiliary Definitions for Instruction Execution 1 Definition of Instruction Execution 1 Auxiliary Definitions for Triggering of Interrupts 1 Definition of Interrupt Execution 1 Processor Core Transition Function 1 Memory 1 Store Buffer 1 Translation Lookaside Buffer 1 Sequential MIPS 1 Multicore MIPS-86 1                                                                                                                                                                                                                                                                                                                                                                                                                         | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132<br>132<br>137<br>142                             |

| 3 |               | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Instant                   | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>119<br>127<br>130<br>131<br>131<br>132<br>132<br>137<br>142<br>143                      |

| 3 | 3.1           | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Instant<br>3.2.1          | ISA       1         Processor Core       1         Instruction Layout Overview       1         Auxiliary Definitions for Instruction Execution       1         Definition of Instruction Execution       1         Auxiliary Definitions for Triggering of Interrupts       1         Definition of Interrupt Execution       1         Processor Core Transition Function       1         Memory       1         Store Buffer       1         Translation Lookaside Buffer       1         Sequential MIPS       1         Multicore MIPS-86       1         tiation       1         Instantiation of Basic Signatures       1                                                                                                                                                                 | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132<br>132<br>132<br>142<br>143<br>146               |

| 3 | 3.1           | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Instant<br>3.2.1<br>3.2.2 | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132<br>132<br>137<br>142<br>143<br>146<br>147        |

| 3 | 3.1           | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Instant<br>3.2.1          | ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132<br>132<br>132<br>142<br>143<br>146<br>147<br>149 |

| 3 | 3.1           | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Instant<br>3.2.1<br>3.2.2 | ISA       1         Processor Core       1         Instruction Layout Overview       1         Auxiliary Definitions for Instruction Execution       1         Definition of Instruction Execution       1         Auxiliary Definitions for Triggering of Interrupts       1         Definition of Interrupt Execution       1         Processor Core Transition Function       1         Memory       1         Store Buffer       1         Translation Lookaside Buffer       1         Sequential MIPS       1         Multicore MIPS-86       1         tiation       1         Instantiation of Basic Signatures       1         Instantiation of Auxiliary Functions, Predicates, and Relations       1         Instantiation of Transition Functions       1         MMU Model       1 | 117<br>118<br>119<br>127<br>127<br>130<br>131<br>131<br>132<br>132<br>137<br>142<br>143<br>146<br>147        |

| 4 |                                         | , 5                                                                          | 155 |  |  |

|---|-----------------------------------------|------------------------------------------------------------------------------|-----|--|--|

|   | 4.1                                     |                                                                              | 155 |  |  |

|   |                                         | $\epsilon$                                                                   | 156 |  |  |

|   |                                         | $\boldsymbol{\mathcal{C}}$                                                   | 157 |  |  |

|   |                                         |                                                                              | 158 |  |  |

|   |                                         | 4.1.4 Semantics                                                              | 159 |  |  |

|   |                                         | 1 1                                                                          | 160 |  |  |

|   |                                         | 1 2                                                                          | 161 |  |  |

|   | 4.2                                     | SB Reduced MIPS-86 Instantiation                                             | 169 |  |  |

|   | 4.3                                     | Application of SB Reduction with MMU to MIPS-86                              | 174 |  |  |

|   |                                         | 4.3.1 Interleaving Reduction of Abstract Machine Computation                 | 174 |  |  |

|   |                                         | 4.3.2 Simulation Theorem Between Abstract Machine and <i>Cosmos</i> Machine. | 187 |  |  |

|   |                                         | Safety Property Instantiation                                                | 187 |  |  |

|   |                                         | Coupling Relation                                                            | 188 |  |  |

|   |                                         | Simulation Theorem                                                           | 189 |  |  |

|   |                                         | Safety Transfer                                                              | 217 |  |  |

| 5 | Applying Store Buffer Reduction to C-IL |                                                                              |     |  |  |

|   | 5.1                                     |                                                                              | 222 |  |  |

|   | 5.2                                     |                                                                              | 223 |  |  |

|   |                                         |                                                                              | 223 |  |  |

|   |                                         | <u> </u>                                                                     | 224 |  |  |

|   | 5.3                                     | •                                                                            | 225 |  |  |

|   |                                         |                                                                              | 225 |  |  |

|   | 5.4                                     | 1                                                                            | 226 |  |  |

|   |                                         | ** *                                                                         | 226 |  |  |

|   |                                         |                                                                              | 226 |  |  |

|   |                                         | · · · · · · · · · · · · · · · · · · ·                                        | 227 |  |  |

|   |                                         | 1                                                                            | 228 |  |  |

|   |                                         |                                                                              | 229 |  |  |

|   |                                         | 11                                                                           | 230 |  |  |

|   |                                         |                                                                              | 230 |  |  |

|   | 5.5                                     |                                                                              | 233 |  |  |

|   | 0.0                                     | 5.5.1 Interleaving Point Schedules                                           | 233 |  |  |

|   |                                         |                                                                              | 235 |  |  |

|   |                                         | · ·                                                                          | 235 |  |  |

|   |                                         |                                                                              | 235 |  |  |

|   | 5.6                                     |                                                                              | 236 |  |  |

|   | 2.0                                     |                                                                              | 236 |  |  |

|   |                                         | ·                                                                            | 237 |  |  |

|   |                                         |                                                                              | 238 |  |  |

|   |                                         |                                                                              | 240 |  |  |

|   |                                         |                                                                              | 241 |  |  |

|   |                                         | 1                                                                            | 243 |  |  |

|   |                                         | 1108141110                                                                   |     |  |  |

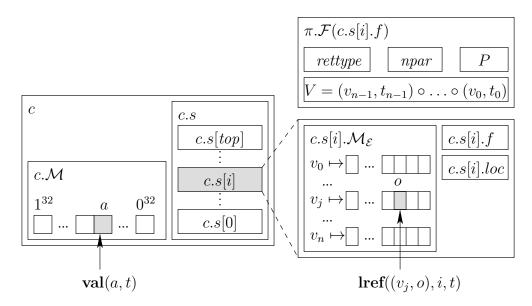

|   |     |         | Configurations                                                | 245 |

|---|-----|---------|---------------------------------------------------------------|-----|

|   |     |         | Transition Function                                           | 252 |

|   |     |         | C-IL Calling Convention                                       | 255 |

|   |     |         | Compilation and Stack Layout                                  | 256 |

|   |     | 5.6.2   | C-IL Instantiation                                            | 260 |

|   | 5.7 | Simula  | ation Theorem for <i>Cosmos</i> machine                       | 270 |

|   |     | 5.7.1   | Block Machine Semantics                                       | 271 |

|   |     | 5.7.2   | Generalized Sequential Simulation Theorems                    | 272 |

|   |     | 5.7.3   | Instantiation of Sequential Simulation Framework              | 277 |

|   |     |         | Compiler Consistency Points and Compiler Consistency Relation | 277 |

|   |     |         | Software Condition, Well-formedness, and Well-behaving        | 282 |

|   |     |         | Instantiation                                                 | 282 |

|   |     | 5.7.4   | Cosmos Model Simulation                                       | 284 |

|   |     |         | Consistency Blocks and Complete Block Machine Computations    | 284 |

|   |     |         | Requirements on Sequential Simulation Relations               | 285 |

|   |     | 5.7.5   | Simulation Theorem                                            | 288 |

|   |     | 5.7.6   | Applying the Order Reduction Theorem                          | 290 |

|   |     | 5.7.7   | Property Transfer and Complete Block Simulation               | 291 |

|   |     |         | Simulated <i>Cosmos</i> machine Properties                    | 292 |

|   |     |         | Property Transfer                                             | 293 |

|   |     | 5.7.8   | Instantiations                                                | 294 |

|   |     |         | Shared Invariant and Concurrent Simulation Assumptions        | 294 |

|   |     |         | Proving Safety Transfer                                       | 295 |

| 6 | Con | clusior | n and Future Work                                             | 299 |

|   | 6.1 | Conclu  | asion                                                         | 299 |

|   | 6.2 | Future  | Work                                                          | 300 |

Introduction

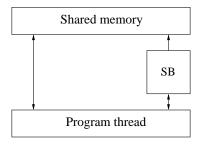

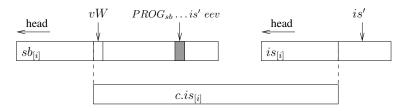

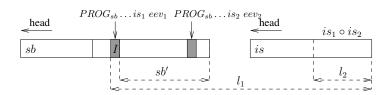

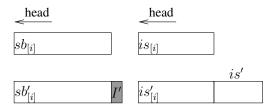

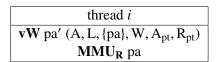

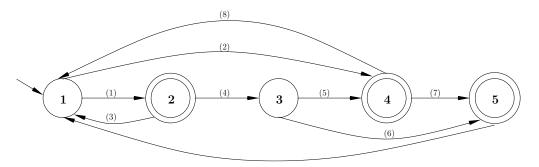

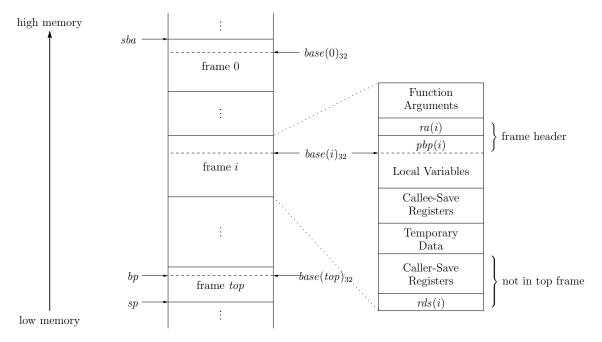

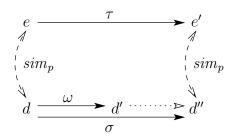

Sequential consistency (SC) [Lam79] is an intuitive and widely used memory model in parallel programming. However, processor designers often apply hardware optimizations for higher performance. A common optimization illustrated in Fig 1.1 is to introduce a FIFO store buffer (SB) between the processor and the shared memory system. When the processor executes a store instruction, the store first enters the SB. This store is visible to other processors only after it exits the SB and is applied to the shared memory. For greater efficiency, loads forward from the most recent store of the same address in the SB if possible. This kind of memory model is called total store order (TSO) because each processor sees the same global ordering of stores. In the following example, we will present that the TSO execution violates the sequential consistency. Initially, a1 and a2 are both 0.

In an SC execution, only one thread is allowed to enter the critical section. However, under TSO, if the updating of a1 and a2 both reside in their SBs then both threads are allowed to enter the critical section.

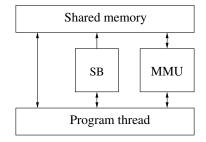

Another complication arises when we consider the programs that modify the page tables. In this case, the memory management units (MMU) are visible and race with processors. The MMU can not be modeled as a processor because:

• it communicates with the processor via the Translation Lookaside Buffer (TLB) which is a local component of the processor. However, processors communicate with each other through shared memory.

Figure 1.1: Abstract view of TSO.

• it bypasses the SB to access the memory directly.

The following example is from our paper [CCK14]. It shows the presence of MMU violates the SC. Assuming the page table entry (PTE) pte1 points to the PTE pte2, the present bit in both entries is set, and the access bit of pte1 is 0. t0 and t1 are read temporaries in T1 and MMU1 respectively.

T1: MMU1:

1: pte2.p:=0 3: pte1.a:=1

2: t0:=pte1.a 4: t1:=pte2

Consider a TSO execution where the steps of the T1 are executed before the steps of the MMU1, and the write to pte2 resides in the SB. After the execution, t0 is 0 and the MMU reads pte2 with the present bit set. As a result, the MMU gets an address translation that goes through pte1 and pte2. However, such a TSO execution can not be reproduced under SC. In an SC execution, if we step the MMU1 before T1, the execution ends with t0 = 1. However, if we step the T1 before MMU1, since the present bit of pte2 is 0 and can not be used for address translation, the execution ends with a page fault. To find an SC execution which ends with t0 equals to 0 and pte2 is 1, the statement 4 needs to be executed before the statement 1 and the statement 2 needs to be executed before the statement 3 while maintaining the programming order. It is impossible to find such an SC execution.

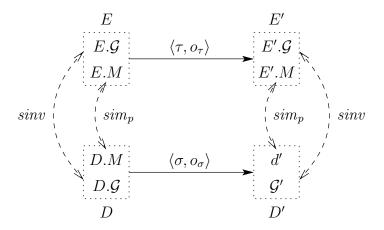

The problems presented above create a gap in multicore system verification. As stated in [CPS13], the correctness theorem of the multicore system includes a simulation theorem between the system implementation and the execution as well as the functional correctness of the system implementation. Most multicore systems are implemented in concurrent C plus assembly code. The multicore compiler correctness theorem in [Bau14] gives the simulation between the implementation and a simplified instruction set architecture (ISA) execution. In the simplified ISA, architectural details like MMUs and SBs should be transparent, and concurrent programs should see sequentially consistent memory. We call this kind of ISA ISA-u (the user's perspective of ISA). During the execution, the complied code runs on an ISA with MMUs and SBs, which we call ISA-sp (the system programmer's perspective of ISA). A TSO memory is provided by ISA-sp. Based on the previous arguments, there exists a gap in the simulation between ISA-u and ISA-sp.

The main goal of this thesis is to find a simulation theorem between ISA-u and ISA-sp. We made the following contributions:

- Propose a programming discipline that guarantees SC for TSO machine with MMU.

- Under the programming discipline, prove a simulation theorem between TSO machine with MMU and SC machine with MMU.

- Apply the SB reduction theorem with MMU to an ISA named MIPS-86.

- Map the programming discipline to parallel C level for user programs.

Chapter 2 of this thesis is a joint work with Ernie Cohen and Mikhail Kovalev. Ernie Cohen and Mikhail Kovalev contributed to building the programming discipline, the machine models

and extending the ownership theorem in [CS10a]. Mikhail Kovalev and the author of this thesis extracted the full paper-and-pencil proof of the SB reduction theorem in [CS10a] from the Isabelle code. The proof in Chapter 2 is largely based on that proof. To adapt to other works in this thesis, the author also changed the notations by adding an explicit ownership generation function to the model and attaching the ownership annotations to volatile operations and read modify writes.

Our initial goal was not only to map the programming discipline for the parallel C user programs but also for the system program that is written in parallel C and modifies the page table. However, currently, we do not have the multicore compiler correctness theorem with MMU. As a consequence, we regard the mapping of programming discipline to system code as our possible future work.

#### 1.1 Related Work

#### 1.1.1 System Software Formal Verification

A survey of operating system verification [Kle09] was published by Klein. The first attempt in pervasive system verification is the CLI stack project [BHMY89]. Since the correct execution of a program depends on the correct translation between high-level language and the machine code, several system components were verified: a code generator for a high-level language, an assembler and linking loader, an operating system kernel, and a microprocessor design.

The Verisoft [Ver07] and VerisoftXT [Ver10] aims at formally verify of an entire computer system from the hardware level up the application software level. [HP08] gives an overview of the verification technology and approach. For the hardware, in [BJK+06] Beyer et al. designed and functionally verified a sequential processor named VAMP. The verification had been carried out in the theorem proving system PVS [ORS92]. In order to bridge the gap between the software and the verified hardware in the Verisoft project, in [LP08] Leinenbach et al. implemented and formally verified a non-optimizing C0 compiler which supports mixing inline assembly with C0 code. In [GHLP05a, APST10], Paul et al. implemented and formally verified a generic operating system kernel called CVM (Communicating Virtual Machines) which formalizes concurrent user processes interacting with an operating system kernel. According to [Kle09], the Verisoft projects demonstrated the most comprehensive and detailed implementation correctness statement of the system software. They made substantial progresses in pervasive verification.

The L4.verified project [KEH+09] focuses on a machine-checked verification of the seL4 microkernel [EKD+07] from an abstract specification down to its C implementation. The goal of the project is to formally guarantee the functional correctness of the C implementation, which means the implementation always fulfills the specification. Instead of the pervasive verification, the correctness of compiler, assembly code, and hardware are assumed.

#### 1.1.2 Weak Memory Model

The sequential consistent (SC) memory model as the most intuitive memory model for a multi-core machine was defined in [Lam79] by Lamport. After that, much research has been done in the field of memory models. The survey paper [AG96] focuses on consistency models proposed

for hardware-based shared memory systems. It also describes the models in terms of program behavior. One of the memory model presented in [AG96] is the TSO model. The TSO model was first introduced in [WG94] SPARC V8 processor. In [OSS09], Owens et al. formally described a TSO memory model for x86 named x86-TSO. However, their model did not cover the MMU and the page-table changes.

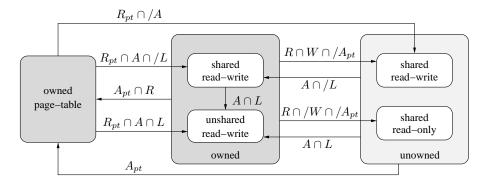

[CS10b] is the starting point of this thesis. In [CS10b], Cohen et al. presented a programming discipline for concurrent programs and have formally proven that it ensures sequential consistency on TSO machines. Instead of applying lock-based techniques, they classify the memory with the ownership sets (shared, read-only and owned). The store buffer should be flushed between a shared write and a subsequent shared read. Based on the above programming discipline, they proved the simulation theorem between TSO computations and the SC computations in Isabelle [NPW02].

[GMY12] considers a way to reason formally about the interoperability between a data-race free (DRF) client and a library written for the TSO memory model. They provide a simulation relation named TSO-to-SC linearizability to fix the correspondence between the TSO execution and an SC execution of the library. They also proved that the properties of a client are preserved by replacing the TSO library with a TSO-to-SC linearized SC library. In order to get the linearized SC library, the shared variable reads and flushes of the SB are required to be protected by locks <sup>1</sup> which introduce more SB flushes than the programming discipline in [CS10b]. At the end of the paper, they proved a more flexible rule that if a program is quadrangular-race free (QRF) then it is sequentially consistent. The QRF requires fewer SB flushes than our programming discipline, but they did not consider the MMU. Also, the QRF can not be used to simplify establishing TSO-to-SC linearizability, because transforming a QRF TSO trace into an SC one can break the linearizability.

Oberhauser [Obe] improved the programming discipline in [CS10b] to avoid the unnecessary SB flush in the following case: let *x* be a shared address then

```

T1: store x T2: store x load x

```

Oberhauser also gives a short proof (less than 30 pages without dealing the MMU). At the end of [Obe], Oberhauser gives a sketch on how to treat MMUs.

#### 1.2 Outline

Note that in this thesis, we introduce four kinds of ISAs.

- First, to apply the SB reduction theorem with MMU to ISA level, we introduce an ISA named MIPS-86, which is a MIPS core extended with x86/x64 like architecture features (with MMU and SB).

- After applying the SB reduction theorem with MMU to MIPS-86, we get an ISA without SB but with MMU. We call it the SB reduced MIPS-86.

<sup>&</sup>lt;sup>1</sup>The shared variable reads and flushes occur within a *lock...unlock* block. The *lock* suspends other CPU's execution until the *unlock* command and the *unlock* flushes the SB.

- When we apply the SB reduction theorem to parallel C level for user programs, we first apply the SB reduction theorem to ISA level, then apply the multicore compiler correctness theorem to map the programming discipline to the parallel C level. Since, the MMU and interrupts are invisible to user programs, we need an ISA without MMU and interrupts. We call it SB MIPS, which is MIPS-86 without MMU and interrupts.

- After applying the SB reduction theorem on SB MIPS, we get an ISA without MMU, SB and interrupts. We call it the MIPS ISA.

The remainder of this dissertation is structured as follows.

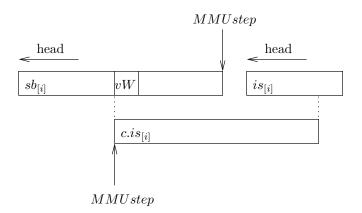

In Chapter 2, we will first introduce the programming discipline, the ownership policy and formally define the models of store buffer machine and abstract machine as well as the safety conditions for the abstract machine, which makes the reduction theorem to go through. Then, we will introduce the coupling relation, invariants and the SB reduction theorem with MMU. At the last portion of Chapter 2, we will present the full paper-and-pencil proof of the theorem.

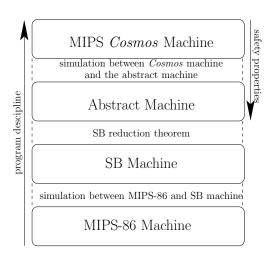

In Chapter 3, first, we will introduce the MIPS-86 ISA as well as the SB reduced MIPS-86 ISA. Then, we will instantiate our abstract machine model and SB machine model with an ISA, which is very alike to MIPS-86. The main difference is that in the instantiated machine models, the execution of one instruction is divided up to five phases, however, in MIPS-86, the execution of each instruction is atomic. As a consequence, to apply the SB reduction theorem with MMU to MIPS-86, we need to prove the two simulation theorem: (i) each computation of the MIPS-86 machine can be simulated by a computation of the instantiated SB machine. This simulation theorem is trivial and omitted in this thesis because the instantiated SB machine has more interleavings. (ii) Each computation of the instantiated abstract machine can be simulated by a computation of an SB reduced MIPS-86 machine. This simulation will be proved in the Chapter 4.

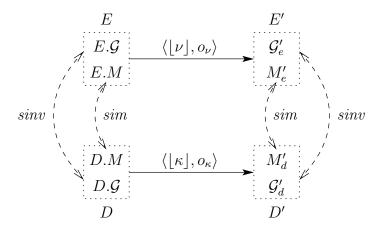

In Chapter 4, we will apply the SB reduction theorem with MMU to MIPS-86 level. The main portion of this chapter is proving the second simulation theorem mentioned in the last paragraph. Since the ownership is included in the semantics of the abstract machine and the SB machine, first, we need to provide the semantics with ownership to the SB reduced MIPS-86 machine. We introduce a model named *Cosmos* which gives us the abstract semantics with ownership. Then, we will instantiate the *Cosmos* model with SB reduced MIPS-86. Because the instantiated abstract machine has more interleavings than the *Cosmos* SB reduced MIPS-86 machine, before proving the simulation, we will reduce the number of interleavings of the instantiated abstract machine by reordering each execution phase of the same instruction into one block. At last, we will prove a simulation theorem between the instantiated abstract machine and the SB reduced MIPS-86 *Cosmos* machine. Moreover, we have to maintain the safety conditions in the simulation theorem.

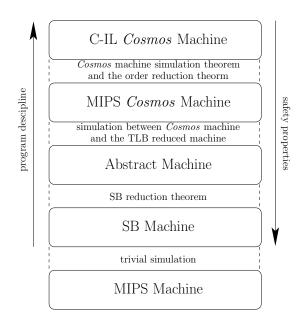

In Chapter 5, we will apply the SB reduction theorem to parallel C level for user programs. Since the interrupts and address translations are invisible for the user program, we will first introduction the two simplified ISAs without MMU and interrupt. The one with SB is called SB MIPS ISA, and the other one without SB is called MIPS ISA. Then, we will simplify the SB reduction theorem to get rid of MMUs. We overload the name SB machine and abstract machine in this chapter. Analogous to Chapter 3, we instantiate the abstract machine and the SB machine model with an ISA very alike to MIPS. Also analogous to Chapter 4, we simplify the *Cosmos*

model to get rid of the MMU steps and instantiate it with MIPS ISA. We will prove a simulation theorem between the instantiated abstract machine and the MIPS *Cosmos* machine. In the last portion of this thesis, we will apply the multicore compiler correctness theorem and map the programming discipline to parallel C level. The multicore compiler theorem is defined base on the *Cosmos* model and consists two part: (i) the order reduction theorem that reorders the arbitrary-interleaved ISA computation into a block-scheduling computation. Each block starts with a compiler consistency point. (ii) the sequential compiler correctness theorem. First, we will introduce the order reduction theorem. Then, we will introduce the C intermediate language (C-IL) and the sequential compiler correctness theorem of C-IL. Moreover, we instantiate the *Cosmos* machine with C-IL and simulate the MIPS *Cosmos* machine with the C-IL *Cosmos* machine, which is the application of the multicore compiler correctness theorem.

#### 1.3 Notation

In the scope of this document we use the following notations from [Sch13] and [Bau14].

#### 1.3.1 Basic Notation

#### • Numbers

The set of integers is denoted by  $\mathbb{Z}$ . The set of natural numbers is denoted by  $\mathbb{N}$  and the set of boolean values  $\{0,1\}$  by  $\mathbb{B}$ . Given a Boolean value  $A \in \mathbb{B}$  and values  $x,y \in \mathbb{N} \cup \mathbb{Z}$ , the value of the ternary operator is defined as follows:

$$A?x: y = \begin{cases} x & A = 1\\ y & A = 0 \end{cases}$$

#### • Records

Let A be a set which is the Cartesian product of sets  $A_1, A_2, ..., A_k$  and let  $n_1, n_2, ..., n_k$  be names for the individual tuple elements of A. Then, given a tuple

$$c \in A = A_1 \times A_2 \times \ldots \times A_k$$

$c = (a_1, a_2, \ldots, a_k)$

$c.n_i$  is used to refer to  $a_i$  – the *i*-th name refers to the *i*-th record field of the tuple. The term record is used to refer to such a named tuple. Records  $c \in A$  is also introduced by defining

$$c = (c.n_1, c.n_2, \ldots, c.n_k)$$

followed by a definition of the types of record fields of c. A record update is denoted as

$$c[n_i := v] = c'$$

where  $\forall j \neq i : c'.n_j = c.n_j$  and  $c'.n_i = v$ . If k = 2, the record  $c = (a_1, a_2)$  is also called a *pair*. We define the following functions to get the first and second component of a pair.

$$fst(c) = c.a_1$$

$snd(c) = c.a_2$

#### • Lists

Let  $l = [x_0x_1x_2...x_{n-1}]$  then

$$hd(l) = x_0$$

$$tl(l) = [x_1 x_2 ... x_{n-1}]$$

$$last(l) = x_{n-1}$$

hd and last are used to return the first element and last element of a list respectively. tl returns the list without the first element. The i-th element of the list l is identified by

$$l[i] = \begin{cases} x_i & i \in [0:n-1] \\ \bot & otherwise \end{cases}$$

l[i] can also be written as  $l_{[i]}$  in this thesis. The length of list l is defined as follows:

$$|l| = \begin{cases} n & l = [x_0 x_1 ... x_{n-1}] \\ 0 & l = [] \end{cases}$$

The concatenation of two lists is defined as follows:

$$a \circ b = l$$

where:

$$l[i] = \begin{cases} a[i] & i \in [0:|a|-1] \\ b[i-|a|] & i \in [|a|:|a|+|b|-1] \\ \bot & otherwise \end{cases}$$

Let  $l_1 = [x_0x_1...x_{n-1}]$  and  $l_2 = [y_0y_1...y_{n-1}]$  then the combination of  $l_1$  and  $l_2$  is defined as:

$$\langle l_1, l_2 \rangle \stackrel{def}{=} l$$

where:

$$l[i] = \begin{cases} (x_i, y_i) & i \in [0: n-1] \\ \bot & otherwise \end{cases}$$

Two lists can be combined only if they have identical length

#### • Sets

Given a set A, the Hilbert-choice-operator  $\epsilon$  chooses an element from A:

$$\epsilon A \in A$$

This is particularly useful when the set consists of a single element, i.e.

$$\epsilon\{x\} = x$$

or when a definition does not depend on the specific element chosen. Given a set A,

$$2^A = \{B \mid B \subseteq A\}$$

denotes the power set of A, i.e. the set of all subsets of A.

#### • Functions

Given two sets A and B,

$$f \in A \rightharpoonup B$$

denotes that f is a partial function from set A to set B, i.e.  $\exists A' \subseteq A$ .  $f \in A' \to B$ . Given  $g \in A \to B$  and  $X \subseteq A$ , the restriction of g to X is defined as :

$$g \upharpoonright_X = \lambda x \in X$$

.  $g(x)$

The function g at entry  $x \in A$  can be updated with a new value  $v \in B$  as follows:

$$g(x \mapsto v) \stackrel{def}{=} \lambda y \in A. \begin{cases} v & y = x \\ g(y) & otherwise \end{cases}$$

The composition of partial functions  $f, f' : A \to B$  with disjoint domains is denoted by  $f \uplus f'$ , where  $dom(f) \cap dom(f) = \emptyset$  and  $dom(f \uplus f') = dom(f) \cup dom(f')$ .

$$f \uplus f' = \lambda a \in dom(f) \cup dom(f'). \begin{cases} f(a) & : \quad a \in dom(f) \\ f'(a) & : \quad a \in dom(f') \end{cases}$$

By adding " $\perp$ " to the image set in order to denote undefined results, any partial function  $f: A \to B$  can be turned into a total function  $f: A \to B \cup \{\bot\}$ , given that  $\bot \notin B$ .

#### 1.3.2 Automaton

Given

- a set Z of states,

- a set A of input alphabet symbols,