## Formal Specification and Verification of a Microkernel

#### Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

Jan Dörrenbächer

jandb@wjpserver.cs.uni-saarland.de

Saarbrücken, November 2010

Tag des Kolloquiums: 23.11.2010

Dekan: Prof. Dr. Holger Hermanns

Vorsitzender des Prüfungsausschusses: Prof. Dr.-Ing. Philipp Slusallek

Berichterstatter: Prof. Dr. Wolfgang J. Paul

Berichterstatter: Prof. Dr. Bernhard Beckert

Berichterstatter: PD Dr. Werner Stephan

akademischer Mitarbeiter: Dr. Eyad Alkassar

### Eidesstattliche Versicherung

Hiermit versichere ich an Eides statt, dass ich die vorliegende Arbeit selbstständig und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in einem Verfahren zur Erlangung eines akademischen Grades vorgelegt.

Saarbrücken, November 2010

#### Danksagung

Ich möchte mich an dieser Stelle bei allen bedanken, die zum Gelingen dieser Arbeit beigetragen haben.

An erster Stelle gilt dieser Dank meiner Familie, deren Unterstützung ich mir immer sicher sein konnte und die mir stets mit Rat und Tat zur Seite stand.

Herrn Prof. Wolfgang Paul danke ich für die Möglichkeit zur Promotion und für die wissenschaftliche Betreuung der Arbeit.

Ein großer Dank geht an meine Kollegen für die interessanten und fruchtbaren, manchmal aber auch anstrengenden Diskussionen, die zum Gelingen dieser Arbeit von unschätzbarem Wert waren. Im Besonderen Eyad Alkassar, Sebastian Bogan, Matthias Daum, Mark Hillebrand, Norbert Schirmer und Burkhardt Wolff. Insgesamt möchte ich mich bei allen Mitarbeitern am Lehrstuhl Paul für die gute Arbeits- und Feierabendatmosphäre bedanken.

Nicht zuletzt möchte ich mich bei meinen Freunden bedanken, die mich nicht nur tatkräftig unterstützt haben, sondern mich stets aufbauten und für die erforderliche Abwechslung sorgten.

Diese Arbeit wurde teilweise im Rahmen des Verisoft Projekts vom Bundesministerium für Bildung und Forschung (BMBF) unter dem Förderkennzeichen 01 IS C38 gefördert.

This work has been partially funded by the German Federal Ministry of Education and Research (BMBF) in the framework of the Verisoft project under grant 01 IS C38.

#### Abstract

This thesis basically splits up into two parts. The first part introduces the abstract model of the VAMOS kernel. The VAMOS kernel provides the infrastructure for process and memory management, priority-based round-robin scheduling, communication with external devices, as well as inter-process communication. In the second part, we formulate a simulation theorem between the abstract VAMOS model and the concrete VAMOS implementation. The crucial points of the theorem are, on the one hand, the abstraction relation connecting the datastructures of the implementation with those of the model and, on the other hand, the implementation invariant formulating validity statements on the datastructures. Besides the exact formal definitions of the abstraction relation and the implementation invariant, we prove substantial parts of the simulation theorem.

This work is part of the Verisoft project which aims at the pervasive formal verification of computer systems. For the modelling and the verification of the VAMOS kernel this entails the integration of various computational models, for instance, *Communicating Virtual Machines* (CVM) encapsulating the hardware-specific low-level functionality, and devices.

The models and proofs presented in this thesis are formalized in the uniform logical framework of the interactive theorem prover Isabelle/HOL, and hence, it is rigorously checked that all verification results fit together.

### Zusammenfassung

Die vorliegende Arbeit teilt sich im Wesentlichen in zwei Teile auf. Im ersten Teil wird das abstrakte Modell des VAMOS-Kernels vorgestellt. Der VAMOS-Kernel liefert die Infrastruktur für Prozess- und Speicherverwaltung, prioritäts-basiertes Round-Robin-Scheduling, Kommunikation mit externen Geräten, sowie Interprozesskommunikation. Im zweiten Teil der Arbeit formulieren wir ein Simulationstheorem zwischen dem abstrakten VAMOS-Modell und der konkreten VAMOS-Implementierung. Kernpunkte dieses Theorems sind zum einen die Abstraktionsrelation, die die Datenstrukturen der Implementierung mit denen des Modells in Beziehung setzt und zum anderen die Implementierungsinvariante, die Gültigkeitsaussagen über die Datenstrukturen trifft. Neben den exakten Definitionen der Abstraktionsrelation und der Implementierungsinvariante, werden wesentliche Teile dieses Simulationstheorems bewiesen.

Die Arbeit wurde im Rahmen des Verisoft Projekts angefertigt, das die durchgängige formale Verifikation von Computersystemen zum Ziel hat. Für die Modellierung und Verifikation des VAMOS-Kernels hat dies zur Folge, dass diverse Berechnungsmodelle integriert werden müssen, unter anderem das Gerätemodell und Communicating Virtual Machines (CVM), das die

hardwarespezifische und systemnahe Funktionalität kapselt.

Alle Modelle und Beweise, die in dieser Arbeit vorgestellt werden, sind in dem interaktiven Theorembeweiser Isabelle/HOL formalisiert worden, womit sichergestellt ist, dass alle Ergebnisse der Verifikation zusammenpassen.

#### Ausführliche Zusammenfassung

Die zunehmende Komplexität und Vernetzung heutiger Computersysteme stellt immer höhere Anforderungen an die Verlässlichkeit und Fehlerfreiheit der Systeme und ihrer Komponenten. Der sicherste Ansatz, um schon beim Systementwurf konzeptionelle und menschliche Unzulänglichkeiten auszumerzen, stellt die durchgängige formale Verifikation dar.

Das Verisoft Projekt, in dessen Rahmen diese Arbeit entstanden ist, verfolgt genau diesen Ansatz. Zu diesem Zweck wird jede einzelne Schicht des betrachteten Systems durch ein mathematisches Modell beschrieben. Durch sogenannte Simulationsbeweise wird bewiesen, dass die jeweiligen Schichten tatsächlich diesen Modellen genügen. Durchgängigkeit bedeutet, dass zum Schluss eine Korrektheitsaussage über das Gesamtsystem steht, die alle Schichten einbezieht, wobei Annahmen in höheren Schichten durch die darunterliegenden entlastet werden. Dadurch, dass alle Beweise durch einen Computer überprüft werden, sprechen wir von formaler Verifikation.

Betriebssysteme gehören unzweifelhaft zu den essentiellen Komponenten von Computersystemen und tragen somit wesentlich zur Verlässlichkeit der Gesamtsysteme bei.

In dieser Arbeit beschreiben wir die Modellierung und formale Verifikation des Betriebssystemkernels VAMOS in einem durchgängigen Kontext. Die Funktionalität des VAMOS-Kernels umfasst Prozess- und Speicherverwaltung, prioritäts-basiertes Round-Robin-Scheduling, Kommunikation mit externen Geräten, sowie Interprozesskommunikation. Ein mathematisches Modell liefert die Spezifikation des Kernels. Dass die VAMOS-Implementierung tatsächlich diesem Modell genügt wird duch einen Simulationsbeweis gezeigt. Um die Datenstrukturen der Implementierung mit denen des Modells in Beziehung zu setzen, definieren wir eine Abstraktionsrelation. Desweiteren definieren eine Implementierungsinvariante, die Gültigkeitsaussagen über die Datenstrukturen trifft. Basierend darauf werden wesentliche Teile des Simulationstheorems bewiesen.

Die Tatsache, dass das VAMOS-Modell eine gültige Spezifikation des VAMOS-Kernels darstellt, liefert die Grundlage dafür, dass das Modell verlässlich in höheren Schichten benutzt werden kann. So werden zum Beispiel Definitionen des VAMOS-Modells direkt von Bogan [15] benutzt, um ein einfaches Betriebssystem zu spezifizieren. Desweiteren wird in [25] der Beweis erbracht, dass der VAMOS Scheduler fair ist.

Zusammengefasst umfasst die Arbeit drei Teile. Im ersten Teil beschreiben wir allgemein den Ansatz zur durchgängigen formalen Verifikation im Verisoft Projekt. Desweiteren führen wir die Berechnungsmodelle ein, die in das Vamos-Modell integriert werden. Unter anderem ein generisches Modell für externe Geräte und *Communicating Virtual Machines* (CVM), das die hardwarespezifische und systemnahe Funktionalität kapselt.

Im zweiten Teil definieren wir das Vamos-Modell als Übergangssystem, das die Basis für den Simulationsbeweis darstellt, mit dem wir uns im dritten Teil dieser Arbeit beschäftigen.

Alle Modelle und Beweise, die in dieser Arbeit vorgestellt werden, sind in dem interaktiven Theorembeweiser Isabelle/HOL formalisiert worden, womit sichergestellt ist, dass alle Ergebnisse der Verifikation zusammenpassen.

## Contents

| 1 | Intr | oduction                               | 19 |

|---|------|----------------------------------------|----|

|   | 1.1  | Document Outline                       | 20 |

|   | 1.2  | Related Work                           | 21 |

|   | 1.3  | Motivation and Contribution            | 25 |

|   | 1.4  |                                        | 27 |

| 2 | Bac  | kground                                | 29 |

|   | 2.1  | The Academic System: Software Stack    | 30 |

|   | 2.2  | The Academic System: Semantic Stack    | 31 |

|   |      | 2.2.1 The Language C0                  | 32 |

|   |      | 2.2.2 The Vamp Assembly Language       | 33 |

|   |      |                                        | 35 |

|   | 2.3  | Devices                                | 38 |

|   | 2.4  | Communicating Virtual Machines         | 39 |

|   |      | 2.4.1 CVM State                        | 40 |

|   |      | 2.4.2 CVM Transitions                  | 41 |

|   |      | 2.4.3 CVM Primitives                   | 42 |

|   |      | 2.4.4 CVM in Isabelle/Simpl            | 42 |

|   | 2.5  | ·                                      | 43 |

|   |      |                                        | 45 |

|   |      |                                        | 50 |

| 3 | The  | Abstract System Layer                  | 57 |

|   | 3.1  | The Overall System - A Bird's Eye View | 57 |

|   | 3.2  | Abstract Types                         | 59 |

|   | 3.3  | The VAMP Assembly Process Model        | 61 |

|   |      | 3.3.1 Process Initialization           | 62 |

|   |      |                                        | 62 |

|   |      |                                        | 65 |

|   |      |                                        | 69 |

| 4 | The | Vamo    | os Model                                             | 73  |

|---|-----|---------|------------------------------------------------------|-----|

|   | 4.1 | The $V$ | VAMOS State Space                                    | 73  |

|   |     | 4.1.1   | Virtual User Machines                                | 74  |

|   |     | 4.1.2   | Priorities                                           | 75  |

|   |     | 4.1.3   | Scheduling Data Structures                           | 75  |

|   |     | 4.1.4   | Rights Datastructures                                | 77  |

|   |     | 4.1.5   | Send Status Database                                 | 78  |

|   |     | 4.1.6   | Device Data Structures                               | 79  |

|   |     | 4.1.7   | Initial Vamos States                                 | 79  |

|   | 4.2 |         | Output Function                                      | 81  |

|   | 4.3 |         | Transition Function                                  | 82  |

|   | 4.4 | Vamo    | os Trap Handler                                      | 82  |

|   |     | 4.4.1   | Access Control                                       | 84  |

|   |     | 4.4.2   | Memory Management                                    | 85  |

|   |     | 4.4.3   | Process Management                                   | 90  |

|   |     | 4.4.4   | Scheduling Mechanism                                 | 100 |

|   |     | 4.4.5   | Device Driver Support                                | 101 |

|   |     | 4.4.6   | Inter-Process Communication                          | 105 |

|   |     | 4.4.7   | Read Kernel Information                              | 128 |

|   | 4.5 | Vamo    | os Scheduler                                         | 128 |

|   | 4.6 | VAMO    | os Interrupt Delivery                                | 131 |

| 5 | Van | nos Co  | orrectness                                           | 133 |

|   | 5.1 | Data .  | Abstraction                                          | 134 |

|   |     | 5.1.1   | Abstracting the User Processes                       | 135 |

|   |     | 5.1.2   | Abstracting the Scheduling Datastructures            | 136 |

|   |     | 5.1.3   | Abstracting the Priorities                           | 137 |

|   |     | 5.1.4   | Abstracting the Send Status Database                 | 138 |

|   |     | 5.1.5   | Abstracting the Rights Datastructures                | 138 |

|   |     | 5.1.6   | Abstracting the Device Datastructures                | 141 |

|   |     | 5.1.7   | The Vamos Abstraction Relation                       | 142 |

|   | 5.2 | Imple   | mentation Invariant                                  | 143 |

|   |     | 5.2.1   | Value Bounds                                         | 144 |

|   |     | 5.2.2   | Validity and Consistency Requirements                | 144 |

|   |     | 5.2.3   | Miscellaneous Requirements                           | 151 |

|   |     | 5.2.4   | Summing Up                                           | 156 |

|   | 5.3 | The S   | Simulation Theorem                                   | 156 |

| 6 | Imp | olemen  | ntation Correctness                                  | 159 |

|   | 6.1 | Weak    | ening the Abstraction Relation                       | 161 |

|   | 6.2 |         | iary Functions                                       |     |

|   | 6.3 |         | ctness of the Timer-Interrupt Handler                |     |

|   |     | 6.3.1   | Implementation Correctness of check_elapsed_timeouts |     |

|   |     | 6.3.2   | Implementation Correctness of handle_timer           |     |

|   |     |         |                                                      |     |

|   | 6.4                    | Correctness of the Trap Handler                             | 169 |

|---|------------------------|-------------------------------------------------------------|-----|

|   |                        | 6.4.1 Implementation Correctness of Function set_privileges | 170 |

|   |                        | 6.4.2 Implementation Correctness of Function                |     |

|   |                        | process_change_scheduling_param                             | 172 |

|   |                        | 6.4.3 Implementation Correctness of IPC                     | 174 |

|   |                        | 6.4.4 Implementation Correctness of Function                |     |

|   |                        | dispatcher_kernel_call                                      | 181 |

|   | 6.5                    | Correctness of the VAMOS Top-level Function                 | 184 |

|   | 6.6                    | Correctness of a System Step                                | 187 |

| 7 | Coı                    | nclusion                                                    | 189 |

|   | 7.1                    | Future Work                                                 | 192 |

| 8 | $\mathbf{A}\mathbf{p}$ | pendix                                                      | 193 |

|   | 8.1                    | Formal Specification of the VAMOS Trap Dispatcher           | 193 |

| B | iblio                  | graphy                                                      | 206 |

# List of Figures

| 1.1 | Kernel step refinement (simplified)                          | 26 |

|-----|--------------------------------------------------------------|----|

| 2.1 | System stack                                                 | 30 |

| 2.2 |                                                              | 31 |

| 2.3 | Simpl function system_step, which represents a combined step |    |

|     | of CVM and VAMOS                                             | 44 |

| 2.4 | The kernel-dispatcher function of VAMOS                      | 55 |

| 3.1 | The input/output automata of the abstract system layer and   |    |

|     | their relationship                                           | 57 |

| 4.1 | Memory Management in the Overall System                      | 85 |

| 5.1 | Simulation between implementation and model 1                | 33 |

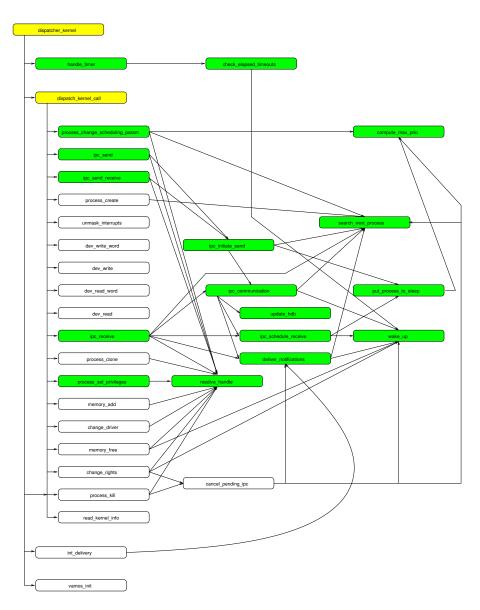

| 6.1 | Call Graph of the VAMOS Implementation                       | 60 |

| 6.2 | Data abstraction in the case of trap handling                | 61 |

| 6.3 | Function handle_timer                                        | 67 |

## List of Tables

| 2.1 | Application binary interface of the | VAMOS | kernel | l . |  |  | 46     |

|-----|-------------------------------------|-------|--------|-----|--|--|--------|

| 2.2 | General Datastructures in VAMOS     |       |        |     |  |  | 51     |

| 2.3 | Process-specific Data in VAMOS      |       |        |     |  |  | <br>53 |

## Chapter 1

## Introduction

| $\alpha$ | 4  |    | 4                      |

|----------|----|----|------------------------|

| $C_0$    | nt | en | $\mathbf{t}\mathbf{s}$ |

| 1.1 | Document Outline               |

|-----|--------------------------------|

| 1.2 | Related Work                   |

| 1.3 | Motivation and Contribution 25 |

| 1.4 | Preliminaries                  |

|     |                                |

Without a doubt, there is a steadily growing impact of computers on our daily life. A couple decades ago, only a few people – mostly for professional reasons – were confronted with the phenomenon "computer". That has certainly changed. Meanwhile, while driving a car various programs – from the entertainment system to the airbag control – assist us and usually ensure that we reach our destination safely. We use computers for banking transactions and the state-of-the-art-technology already deals with computers assisting physicians during difficult surgeries. Even the leisure sector observes an increasing entry of technology. It seems that nowadays nearly nobody is able to ride a bike without tracking the route by GPS or run without listening to music. Not to mention that the thereby achieved performances are immediately shared with the rest of the world via social networks like Facebook.

A reason for the triumphal procession of these new technologies is that – most of the time – they ease our lives and work properly. And when sometimes things go wrong, this is annoying, but usually no severe or even live-threatening consequences are entailed.

However, there are definitely computer systems where malfunctions could result in dramatic consequences. One just has to think of systems flying airplanes, controling nuclear power plants or pacemakers dictating the beat of human hearts. Thanks to outstanding engineering skills, until now, we remained widely spared from any severe scenarios. Nevertheless, it is no longer a rarity that the media reports on flaws in computer systems with

20 1. Introduction

far-reaching consequences. At the beginning of the year 2010, for instance, nearly 30 million bank customers in Germany were incapable of withdrawing money at cash points. The reason for that could be traced back to a programming error in a security chip on the bank cards. Another software bug was recently reported in conjunction with the acceleration mechanism in vehicles of Toyota's model Prius. Such occurrences certainly scratch on the image of the companies concerned, without mentioning the financial drawbacks.

There is some indication that such reports will accumulate in the future. That is not because the system engineers today are worse than in the past or became lazy in testing their systems. The reason is simply founded in the increasing complexity of such systems which makes it more and more difficult for human beings to keep the overview. Furthermore, the new technologies reach out into new areas. A few years ago it would have been unthinkable that computers assist in medical surgeries or computer-controlled robots even accomplish them. Today we accept computer-assisted surgical planning as normal.

If, however, such a system fails, severe consequences are possible. Therefore, it is expected that the demand for truly robust, safe, and secure systems will constantly grow in the next years. In order to achieve this, a detailed and profound analysis of such computer systems is required. Previous approaches to satisfy the desire for reliable systems often focused on exhaustive testing of the systems. However, only limited reliability can be achieved this way, because testing never proves the absence of errors and often relies on assumptions on other system components (e. g., underlying system software) which may behave differently than expected.

A different approach constitutes the pervasively formalization and verification of computer systems. In [55], J. S. Moore, principal researcher of the CLI stack project [12], declares the formal verification of a "practical computing system" as a grand challenge problem.

The Verisoft projects exactly tackles this problem and aims at the pervasive modeling, implementation, and verification of a complete computer system reaching from gate-level hardware to applications running on top of an operating system. Certainly, a corner stone of this system is the microkernel constituting the interface between the hardware and the operating system.

In this thesis, we describe the modeling and verification of the microkernel in a pervasive context.

#### 1.1 Document Outline

In the remainder of this chapter, we discuss related work and present the motivation and contribution of this thesis. It concludes with some basic no1.2. Related Work

tation. Chapter 2 describes background information about the context and prerequisites of this thesis. It introduces the languages C0 and assembly which are used to implement the kernel and sketches the verification approach. Furthermore, it presents the computational models for the devices and the communicating virtual machines (CVM). The chapter concludes with an overview on the design and implementation of the VAMOS kernel.

Chapter 3 gives a bird's eye view on the abstract system layer, which is concretized in Chapter 4 with the model of the VAMOS kernel.

Chapter 5 states the VAMOS correctness theorem and Chapter 6 deals with the actual proofs.

We conclude in Chapter 7 with a summary and an outlook on future work.

#### 1.2 Related Work

Early attempts regarding the formal verification of operating system kernels already took place in the 1970s and early 1980s. The Provably Secure Operating System (Psos) comprised hardware and software and aimed at a useful general purpose operating system with demonstrable security properties, as a retrospective report [58] from 2003 describes. Even if no code proofs were undertaken, Psos introduced concepts for OS verification and aimed at applying formal methods throughout the whole implementation of the OS.

The verification of a kernel supporting threads, a capability-based access control, virtual memory, and device accesses, was the aim of the UCLA Secure Unix project [79]. It relied on the assumptions that the compiler and the hardware work correct. They report that about 90% of the specifications and 20% of the code proofs were completed.

The KIT kernel [11, 12, 55] is the first kernel that can be considered as formally verified. However, it can only be referred as groundbreaking to the area of pervasive operating-system verification. The main difference to more recent verification attempts of "real software" is that it relies on a LISP execution model that is nowadays considered fairly abstract. Moreover, the corner stone theorem of this work is on memory separation of processes.

While they pioneered the field, none of the above projects comes up with a realistic operating system kernel (written in an imperative language) with full implementation proofs. The main reason for this were the missing or to a large extend underdeveloped tool environments. It took until the early 2000s to remedy this deplorable state of affairs, before projects again engaged in increasing the confidence in system software by means of formal methods. Various approaches cover only specific aspects of an operating system kernel and apply formal methods to it. Though these approaches are promising, they would not produce a formally verified operating system kernel. Thus,

22 1. Introduction

we do not consider them in the context of this thesis but rather concentrate on the approaches examining complete kernels. Subsequently, we refer to the most prominent projects. For the interested reader, we also recommend the excellent and comprehensive overview by Klein [43].

Most of the projects deal with the verification of an operating system kernel by following the single-layer approach. They apply formal methods to the kernel layer with the aim to show, that this layer fulfills a certain specification and (possibly) some properties. In contrast to the pervasive approach (we are aiming at), the lower layers are considered as correct and respective properties are assumed to hold. Additionally, while defining the particular specifications, it is usually not ensured (at least not apparently) how these specifications could be integrated or used in higher layers, for instance, in order to specify an operating system.

An exponent of the single-layer approach is the MASK project [54] standing for mathematically analyzed separation kernel. It guarantees a separation property that is provided by construction in the highest-level model, and by multiple formal refinement proofs down to a low-level design, which is close to an implementation. Code proofs, however, were not attempted.

The VFIASCO project [39] aims at the verification of the microkernel Fiasco implemented in a subset of C++. Besides model checking of basic safety properties in Spin [31] for a strongly limited and simplified version of Fiasco IPC, three properties concerning ready and waiting lists have been verified in PVS [67]. However, this work is less than full code verification since C++ code was transformed (only for this purpose) into PVS without defining a formal semantics of the used C++ subset. Even some functions were only described by their semantical effects, and hence the obtained implementation model is rather a specification.

With Eros/Coyotos [70], Shapiro and Weber define a capability based kernel system and prove certain security policies to hold. For the successor project COYOTOS, a complete formal specification of the microkernel and the used programming language BitC has been finished. No formal proofs have been reported yet.

Other projects, for instance, EMBEDDED DEVICE [37, 36], were successful in the verification but did not reach down to the implementation level. In the FLINT project [60], an assembly code verification framework is developed and code for context switching on a x86 machine was formally proven to be correct. The presented code is in functionality and size very similar to the process switch implemented in the CVM, and also reported verification efforts are comparable to those in Verisoft. Although a verification logic for assembler code is presented, no integration of results into high level programming languages has been undertaken yet.

Besides the verification of the VAMOS kernel, the Verisoft project also dealt with the correctness of the real-time operating system OLOS. The functional correctness of this tiny real-time operating system also relies on

1.2. Related Work

the CVM layer and has completely been shown [29]. Compared to the VAMOS kernel, however, the complexity of OLOS with only three rather low-level system calls is much lower.

Further verification projects are L4.VERIFIED and VERISOFT XT both aiming at the complete code-level verification of operating system kernels.

**L4.verified.** L4.VERIFIED focuses on the seL4 kernel [35], which is based on the ARM11 platform. It is a third generation microkernel of L4 provenance and comprises 8,700 lines of C and 600 lines of assembly code. Relying on [42, 44], the L4.VERIFIED project is providing a machine-checked proof of the functional correctness of the seL4 microkernel with respect to a high level, formal description of its expected behaviour.

The lowest level of the verification and of the refinement is a highperformance C and ARM assembly implementation of the seL4 microkernel. The next level up, the low-level design, is a detailed, executable specification of the intended behaviour of the C implementation. This executable specification is derived automatically from a prototype of the kernel which was written in the high-level, functional programming language Haskell. While trying to avoid messy specifics of how data structures and code are optimized in C, the executable specification still represents a pretty concrete view on the kernel implementation. For instance, it still contains doubly-linked lists, i.e., pointer structures. The highest refinement layer is the high-level design, an abstract, operational specification of the kernel. Usually, this is accompanied with a high level of abstraction. It is reported, however, that this layer precisely describes argument formats, encodings and error reporting. Thus, for instance, some of the C-level size restrictions become visible on this level. On the other hand, the specification uses non-determinism in order to avoid an explicit description of the system. For example, neither a scheduling policy is defined at the abstract level nor the correctness of the interrupt controller management is modeled in detail. The refinement proofs are machine-checked in the interactive theorem prover Isabelle/HOL.

In [18, 30], they also defined an abstract access control model of seL4 that captures how capabilities (the kernel's access control mechanism) are distributed in the system and showed the isolation of security domains based on this model. The access control model, however, is not formally connected to the high-level design of seL4 which is used in the refinement proof.

Without doubt, the results of the L4.VERIFIED project are very promissing. However, the following issues have to be observed: Firstly, the approach assumes the correctness of the C compiler, the assembly code, and the hardware. Furthermore, in contrast to the Verisoft project, there is no obvious technology to integrate and combine all these entities into one coherent theory. Secondly, the abstraction level of the high-level design seems to be comparatively low (which reduces the effort regarding the refinement proof)

24 1. Introduction

and unsuitable to show, for instance, properties of the access control mechanism. Instead, these proofs rely on a (probably) more abstract model which is not formally connected to the high-level design in the refinement proof. Thirdly, the abstract models are not applied, in the sense that they are used to specify an operating system, for instance.

Based on these issues, we define the scope of our work. The model of the VAMOS kernel presented in this work is completely integrated into a model stack reaching from applications down to the hardware. Relying literally on definitions of the lower layers, on the one hand, the VAMOS model exports definitions to higher layers, on the other hand. Bogan [15], for instance, based his operating system model on VAMOS and uses definitions from it literally.

The seamless integration into the model stack is not the only remarkable difference between the high-level design of seL4 and the VAMOS model. Similar as above, the VAMOS model serves as basis for the functional correctness of the VAMOS implementation. Thereby, the model establishes an abstraction level that is high enough, such that it can be used to show a pretty complex property of the VAMOS kernel, namely the fairness of the VAMOS scheduler [25, 27].

**Verisoft XT.** The Verisoft XT project aims at the complete code-level verification of the following operating system kernels:

PIKEOS kernel [41]. This L4-derivate comprises 6,000 lines of code (loc) and is part of a commercial product available for Intel's x86, PowerPC, and ARM. The proofs are carried out by the VCC verification environment [21] (a descendant of the Spec# program-verification environment of Microsoft Research), which uses a trusted tool chain comprising the automatic verifier for concurrent C code VCC, the verification condition generator Boogie [16, 17], and the automated theorem prover Z3 [56]. The supported C fragment is a large fragment of ANSI C.

Recent publications [8, 7] mainly introduce the tool chain and methodology. Apart from the verification of a simple system call which changes the priority of a thread, there are no reports yet on the portion of verified code.

HYPER-V [66]. The kernel comprises 100,000 lines of C and 5,000 lines of assembly code and is part of a commercial virtualization environment. The hypervisor turns a single real multi-processor x64 machine (with AMD SVM or Intel VMX virtualization extensions) into a number of virtual multi-processor x64 machines. The verification is realized by the VCC verification environment (see above); the supported C fragment is a large fragment of ANSI C. Recent publications [20, 22,

23] in this context mainly focus on the methodology of VCC and its application.

Baby Hyper-V. Alkassar et al. [5], report on the successful verification of the so-called baby hypervisor. In comparison to the Hyper-V, the baby hypervisor and the architecture it virtualizes are very simple because it only includes the initialization of the guest partitions and a simple shadow page table algorithm for memory virtualization. However, it played an important role of driving the development of the VCC technology and applying it to system verification.

The VCC technology [22] demands a high level of trust: The current VCC version uses an axiomatization of the execution model consisting of various axioms, which introduce some rather abstract concepts like concurrency and ownership of references. Though critical subproblems of the foundation are tackled by informal as well as formal proof methods, the integration into a uniform foundational theory is significantly less prioritized. In this respect, the tool chains, methodologies etc. are driven by the need to deal with the existing code that can only be changed, if errors have been revealed.

#### 1.3 Motivation and Contribution

Summing up the last section, we can state that real system-code verification represents a grand challenge. Current approaches – including ours – compromise in one way or the other: the logical foundations are quite problematic, the computer architectures are simpler than industrial-strength processors, the code size is fairly small, or the underlying execution model of C and assembly makes severe simplifications. In addition, we have to deal with an ambiguous notion of functional correctness which mainly concerns the abstract model, the functional correctness relies on. Thus, we have to be aware of the following issues:

- is the abstract model confirmed by underlying models or is it based on the informal understanding of the lower layers and respective properties

- which level of abstraction provides the model and which parts of the concrete system are actually modeled

- is the model tailor-made to show a particular system property, or is it able to serve as basis for higher layers, e.g., an operating system model

Taking up these issues, the abstract model for the VAMOS kernel, which we present in this thesis, is completely integrated into a model stack reaching

26 1. Introduction

Figure 1.1: Kernel step refinement (simplified)

from applications down to the hardware (cf. Section 2.1). While defining the model, we literally use definitions from the lower layers, for instance, in order to describe visible parts of the processor. The abstraction level of the VAMOS model is so high, that it is possible to show a pretty complex property of the VAMOS kernel, namely the fairness of the scheduler [25, 27]. In addition, Bogan [15] based his operating system model on VAMOS and uses definitions from it literally. The integration into the overall model stack certainly justifies the relevance of the VAMOS model. This relevance, however, will be further backed by a simulation proof establishing the relation between this abstract model and the concrete, fairly realistic implementation of the VAMOS kernel.

The availability of a hardware-processor model represents the foundational layer of our work. This model describes, at gate level, the transitions of the RISC processor VAMP. A small piece of software executed on the VAMP, called CVM, provides an abstract layer running concurrently a system process as well as a number of user processes. The implemented microkernel VAMOS is executed as this system process. Its implementation uses the C fragment C0, which can be translated into assembly code by a verified compiler [49, 48]. VAMOS provides a process scheduler, an infrastructure for communication with hardware devices, and message passing between processes. All software layers are formally specified; simulation relations correlate the adjacent layers such that eventually, all specification layers can be mapped down to our hardware-processor model. The whole model stack is formalized in the theorem prover Isabelle/HOL [61].

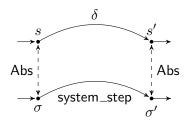

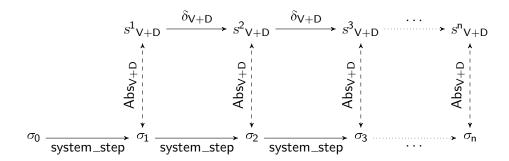

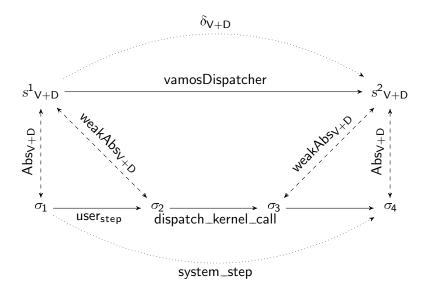

In more detail, CVM and the VAMOS implementation together realize an abstract transition  $\delta$  by an implementation function system\_step as shown in Figure 1.1. The transition function  $\delta$  represents the execution of a non-empty portion of a user process including a possible process switch. The simulation proof establishes that the implementation with its underlying state  $\sigma$  indeed realizes the high-level state transition  $\delta$  over the corresponding abstract state s, where abstract and concrete states are linked via a formally defined abstraction relation Abs.

To our knowledge, such a proof based on a model stack of this concrete level of detail and with such a clean, seamless logical foundation has been 1.4. Preliminaries

undertaken for the first time.

#### 1.4 Preliminaries

The formalizations presented in this thesis are mechanized and checked within the generic interactive theorem prover Isabelle[62]<sup>1</sup>. Isabelle is called generic as it provides a framework to formalize various *object logics* that are declared via natural deduction style inference rules within Isabelle's metalogic Pure. The object logic that we employ for our formalization is the higher order logic of Isabelle/HOL[61].

This thesis is written using Isabelle's document generation facilities, which guarantees that the presented theorems correspond to formally proven ones. We distinguish formal entities typographically from other text. We use a sans serif font for types and constants (including functions and predicates), e.g., replicate, a slanted serif font for free variables, e.g., x, and a slanted sans serif font for bound variables, e.g., x. Small capitals are used for data type constructors, e.g., Foo. HOL keywords are typeset in type-writer font, e.g., let.

As Isabelle's inference kernel manipulates rules and theorems at the Pure level the meta-logic becomes visible to the user and also in this article when we present theorems and lemmas. The Pure logic itself is intuitionistic higher order logic, where universal quantification is  $\bigwedge$ , implication is  $\Longrightarrow$  and equality is  $\equiv$ . Nested implications like  $P_1 \Longrightarrow P_2 \Longrightarrow P_3 \Longrightarrow C$  are abbreviated with  $[\![P_1; P_2; P_3]\!] \Longrightarrow C$ , where we refer to  $P_1, P_2$ , and  $P_3$  as the premises and to C as the conclusion.

In the object logic HOL universal quantification is  $\forall$ , implication is  $\longrightarrow$  and equality is =. Isabelle/HOL provides a library of standard types like Booleans, natural numbers, integers, total functions, pairs, lists, and sets as well as packages to define new data types and records. We only present them shortly in the following.

**Functions.** In HOL all functions are total. An unamed function can be specified using the  $\lambda$ -operator, e. g.,  $\lambda x$ . x is the identity function. In general, we prefer curried functions over functions taking an n-tupel as argument, e. g., f a b instead of f(a, b). Note that function application binds tighter than any other operator, i. e., f i + g j means (f i) + (g j). Function update is  $f(y := v) \equiv \lambda x$ . if x = y then v else f x and function composition is  $f \circ g \equiv \lambda x$ . f (g x). Partial functions are usually formalized in HOL with an optional type. This type is a data type with two constructors, one to inject values of the base type, e. g.,  $\lfloor x \rfloor$ , and the additional element  $\bot$ . With  $\lceil y \rceil$ , the original base value x can be obtained such that y = |x|. There

<sup>&</sup>lt;sup>1</sup>For taming Isabelle's powerful document-generation mechanism in general, and in particular for the major part of this section, we are indebted to Schirmer *et al.* [69, 4]

28 1. Introduction

is no base value x iff  $y = \bot$ . As HOL is a total logic the term  $\lceil \bot \rceil$  is still a well-defined yet unspecified value. Partial functions can be represented by the type  $a \Rightarrow b$  option, abbreviated as  $a \to b$ . For an update of a partial function, we write  $f(y \mapsto x)$ . For data types, we write the structural case distinction over some value x as x as x as x and x as x as x as x and x as x as x as x as x as x as x and x as x as x and x as x as x and x are the following partial functions, we may write x as x and x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functions are the following partial functions as x and x are the following partial functions are the following partial functio

**Sets and Intervalls.** Sets come along with the standard operations for union, i.e.,  $A \cup B$ , intersection, i.e.,  $A \cap B$  and membership, i.e.,  $x \in A$ . The set image f ' A yields a new set by applying function f to every element in set A.

We denote the intervall of the numbers a and b excluding the endpoints by  $\{a<...< b\}$ , and including the endpoints by  $\{a..b\}$ . Furthermore, we write  $a \le c < b$  to denote that a number c is in the interval  $\{a...< b\}$ .

**Records and Tupels.** A record is constructed by assigning all of its fields, e.g., ( $|\mathsf{fld}_1 = v_1, \mathsf{fld}_2 = v_2|$ ). Field  $\mathsf{fld}_1$  of record r is selected by  $r.\mathsf{fld}_1$  and updated with a value x via  $r(|\mathsf{fld}_1 := x|)$ .

The first and second component of a pair can be accessed with the functions fst and snd. Tuples with more than two components are pairs nested to the right.

### Chapter 2

## Background

| 2.1 | The Academic System: Software Stack          | 30 |

|-----|----------------------------------------------|----|

| 2.2 | The Academic System: Semantic Stack          | 31 |

| 2.3 | Devices                                      | 38 |

| 2.4 | Communicating Virtual Machines               | 39 |

| 2.5 | Vamos Microkernel: Design and Implementation | 43 |

|     |                                              |    |

The present work was done in the context of the German Verisoft project, a large scale effort bringing together industrial and academic partners to push the state of the art in formal verification for realistic computer systems, comprising hard- and software. Our microkernel belongs to Verisoft's so-called Academic System (as opposed to systems in subprojects with partners from industry), which is a distributed computer system for the exchange and management of signed and encrypted e-mails. This computer system is designed as part of an open network with a number of trusted computers. While the system is open to receive e-mails from arbitrary computers in the network, each trusted computer uses identical hardware and the same operating-system software. As application software, we implemented and verified an e-mail client [10, 9], an e-mail server [45, 46], and a cryptography server that run on top of this operating system. These applications might be arbitrarily distributed over the trusted computers in the network.

This section continues with a short introduction of the implementation layers in our computer system. Furthermore, we summarize the general verification approach that has been developed for sequential programs within Verisoft in Section 2.2. A key feature of this approach is, that it can cope with mixed-language implementations as they frequently occur in system-level software. In our case, these languages are C0 and assembly. Assembly is used in the lowest software layer, a low-level microkernel. The device

30 2. Background

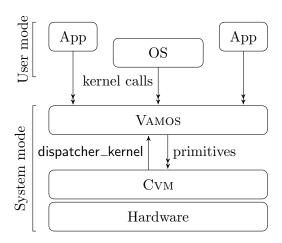

Figure 2.1: System stack

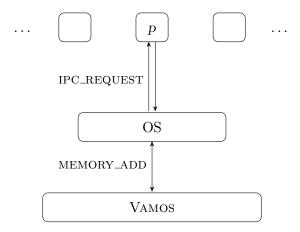

model in Section 2.3 together with the computational model Communicating Virtual Machines (CVM) introduced in Section 2.4, abstract from this lowest software layer. On top of it, Section 2.5 introduces the VAMOS microkernel which is completely implemented in C0. It relies on the CVM framework and represents the top-level microkernel with utilities like interprocess communication, memory management and process scheduling.

#### 2.1 The Academic System: Software Stack

Figure 2.1 depicts the hard- and software layers of a single computer in the system. The lowest software layer is called *communicating virtual machines* (CVM). This layer encapsulates all the hardware-specific low-level kernel functionality, which uses inlined assembly. Technically, this software constitutes the interrupt-service routine of the processor. CVM's major task is memory virtualization and process separation. Hence, CVM includes a page-fault handler with a simple memory swapping facility [6]. The remaining functionality of our microkernel is implemented by the hardware-independent kernel part. CVM exports an interface of so-called *primitives* for the access to and manipulation of user processes to this kernel part. We have thereby established a solid framework for microkernel construction.

Using this framework, we have implemented our microkernel VAMOS in the C variant  $C\theta$  without inlined assembly. When an interrupt occurs, CVM preserves the old processor context, establishes a suitable C0 environment and calls the function dispatcher\_kernel of VAMOS. For the manipulation of the user memory or registers, VAMOS may call the primitives of CVM. The return value of dispatcher\_kernel determines which process resumes when the kernel execution finishes.

While CVM and VAMOS run in the privileged system mode of the proces-

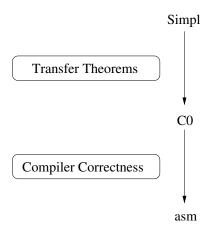

Figure 2.2: Semantic Stack

sor, processes run in the unprivileged user mode. In the figure, we labeled one process "OS" for the operating system and the others "App" as abbreviation for application (e.g., e-mail client or server). The OS process constitutes the highest layer of the operating system [15]. It features an advanced rights management with different users, implements a sophisticated access control to kernel services like process creation and provides further services like file-system and network access. All processes interact with the kernel via kernel calls. The instruction set architecture (ISA) provides a special instruction TRAP causing an exception, which is handled in VAMOS. VAMOS can examine and alter the state of the process using CVM primitives, thus identifying the process's specific request and storing the kernel's corresponding response.

### 2.2 The Academic System: Semantic Stack

As Figure 2.1 depicts, a computer system comprises a stack of hardware and software layers. Along the implementation layers, we assemble computational models which we use to specify and verify the system. Each of these layers introduce a higher abstraction level to improve the effectiveness of reasoning. In addition, these layers often employ different implementation languages. CVM, for example, provides the abstraction of separate processes with virtual memory, and is implemented in a mixture of C0 and inlined assembly. The reason for two implementation languages is apparent: C0 is a C-like high-level programming language and can be comfortably employed at a reasonable abstraction layer for most programming tasks. Specific low-level functionality, however, cannot be expressed in C0. For these tasks, we employ the assembly language.

In a large-scale verification project, the key to success is a verification ap-

32 2. Background

proach that follows the system design. Applied to the Verisoft project, this means that verification does not only extend along the software levels but also takes into account the mixed-language architecture [3]. The verification approach is two-dimensional: The first axis, called system stack, traces the different implementation layers. Along the implementation layers, we assemble computational models which we use to specify and verify the system. Figure Figure 2.2 depicts the so-called *semantics stack* [4] combining all the different language semantics.

The assembly language marks the bottom layer, followed by C0 and Simpl at the top. Despite of the former two, Simpl is a generic programming language model for sequential imperative programming languages. This generic model provides the basis for the versatile verification environment Isabelle/Simpl. The major challenge of a pervasive verification is to develop a coherent theory that allows to transfer the correctness results down to the lowest layer. Thus, an important result of the Verisoft project is the correctness theorem of a simple non-optimizing compiler that links C0 and the assembly language [49, 63, 50]. Furthermore, transfer theorems [69] establish an embedding of C0 into the generic programming model Simpl.

In the following sections, we present the – for microkernel programming relevant – implementation languages C0 and VAMP assembly. The chapter concludes with the introduction of the verification environment Isabelle/Simpl which is used to conduct the actual proofs.

In the scope of this work, we solely focus on the correctness proofs performed in Isabelle/Simpl. Mapping down the results achieved would rely on the previously mentioned transfer theorems and the compiler correctness. Starostin [72] already successfully applied the semantic stack in the context of the formal verification of the demand paging mechanism in CVM.

#### 2.2.1 The Language C0

ANSI C has a complex and highly underspecified semantics. However, low-level kernel programs such as drivers explicitly use properties of a particular compiler on a target hardware, for example, its little-endian-ness or a particular atomicity of assembly operations. They can therefore not be verified based only on the vague ANSI C semantics. In our approach, we constrained ourselves to the C-like imperative language  $C\theta$ , which has sufficient features to implement low-level software, but which is interpreted by a mathematically well-defined semantics. It is type safe and designed with verification in mind. An elaborate description of the big-step semantics is given in [69] and the small-step semantics is introduced in [48]. An overview on the simulation theorems between the semantical layers can be found in [3].

C0's most important limitations compared to ANSI C are:

• expressions must be free of side effects and do not contain function calls,

- there are no implicit type conversions, especially not from arrays to pointers,

- pointers are strongly typed and must not point to functions or stack variables (i. e., there are neither void pointers nor pointer arithmetic), and

- low-level data types (like unions and bit fields) and control-flow statements (like switch and goto) are not supported.

**Syntax.** C0 supports fundamental types, aggregate types and pointers. The first category comprises Booleans, 8-bit-wide characters, as well as signed and unsigned 32-bit integers. Aggregate types in C0 are arrays and structures. Pointers may point to all types of data but not to functions.

Expressions are variable names and literals. Moreover, if e and i are expressions and n is a component name, array access e[i], access to structure components e.n, dereferencing \*e, and the 'address-of' operation &e are expressions. Additionally, C0 supports the usual unary and binary operators.

Finally, C0 supports statements for assignments, dynamic memory allocation, sequential composition, conditional and repeated execution, inline assembly, function calls and returns from functions.

Small-step Semantics. C0 programs are statically represented by the program environment  $\Gamma$ , which comprises a symbol table of global variables, a type-name environment, and a function table. The symbol table is a list of pairs of variable names and types. The type-name environment maps type names to types. The function table maps function names to functions, which are represented by a tuple consisting of (a) a symbol table for the function's parameters, (b) a symbol table for the stack variables, (c) the function's return type, and (d) a statement representing the function body.

The dynamically changing state  $s_{\mathsf{C0}}$  of a C0 program in execution comprises:

- the remaining program  $s_{C0}$ . proq. and

- the current state of the program variables  $s_{C0}.mem$ .

The transition relation  $\delta_{C0}$  of this semantics is deterministic, i. e., a partial function.

#### 2.2.2 The Vamp Assembly Language

The DLX architecture [38] lays the foundation of the VAMP architecture which was initially presented in [57]. An implementation of the VAMP has been formally verified [13, 14]. Since then, the VAMP has been extended with address translation and support for I/O devices [24, 1, 77].

There are three models [4, 77] related to the VAMP architecture. The most concrete one is the gate-level implementation followed by the instruction set architecture (ISA) specification and the assembly-language speci-

34 2. Background

fication. The adjacent models are related via simulation proofs, such that properties shown at the assembly level can eventually be transferred down to the gate-level.

In the context of this work, we only rely on the VAMP assembly language specification. Details on the gate-level implementation and its verification can be found in [77].

The VAMP assembly language is the target language of the verified C0 compiler and represents a convenient layer for the implementation and the verification of hardware-dependent programs. Its specification abstracts from certain aspects of the lower layers, which are irrelevant for these purposes. For instance, the VAMP assembly machine employs a linear memory model with a conventional memory semantics, i.e.,. it abstracts from memory-mapped device I/O and the paging mechanism of the processor. This abstraction is useful for assembly code executed in the untranslated system mode as well as in the user mode with a transparent handling of address translation and page faults.

Furthermore, the bit vectors from the ISA specification are superceded in the VAMP assembly machine (a) by integers for data, (b) by naturals for addresses, and (c) by a tailored abstract data type for instructions. While this representation is optimized for assembly programs working with integers, arguments regarding naturals and bit-vector operations require the conversion from / to integers. Thus, we define, for instance, the two functions to\_int32 and to\_nat32 converting between 32-bit integers and naturals.

**Assembly Semantics.** An assembly state  $s_{asm}$  is a record with the following components:

- two program counters s<sub>asm</sub>.dpc and s<sub>asm</sub>.pcp for implementing the delayed branch mechanism, which hold the byte addresses of the current and next instruction,

- general purpose and special-purpose register files  $s_{\mathsf{asm}}.\mathsf{gprs}$  and  $s_{\mathsf{asm}}.\mathsf{sprs}$  both holding lists of data, and

- main memory  $s_{asm}$ .mm, which is a map from word addresses to data.

A VAMP assembly configuration is called *valid*, if it fulfills certain basic well-formedness conditions: (a) the program counters must be 32-bit naturals, (b) register files must contain 32 registers, and (c) all registers and memory cells must be 32-bit integers <sup>1</sup>. Formally, the predicate is\_ASMcore encapsulates these well-formedness conditions:

<sup>&</sup>lt;sup>1</sup>Note that register  $s_{asm}.gprs$  ! 0 is always 0 and can thus be represented as 32-bit integer.

```

is_ASMcore s_{\mathsf{asm}} \equiv 0 \le s_{\mathsf{asm}}.\mathsf{dpc} < 2^{32} \land 0 \le s_{\mathsf{asm}}.\mathsf{pcp} < 2^{32} \land \mathsf{length} \ s_{\mathsf{asm}}.\mathsf{gprs} = 32 \land \mathsf{length} \ s_{\mathsf{asm}}.\mathsf{sprs} = 32 \land (\forall i \in \{0 < ... < 32\}. \ -2^{31} \le s_{\mathsf{asm}}.\mathsf{gprs} \ ! \ i < 2^{31}) \land (\forall i \in \mathsf{used\_sprs}. \ -2^{31} \le s_{\mathsf{asm}}.\mathsf{sprs} \ ! \ i < 2^{31}) \land (\forall \mathit{ad}. \ -2^{31} \le s_{\mathsf{asm}}.\mathsf{mm} \ \mathit{ad} < 2^{31})

```

Instructions are represented by an abstract data type and converted on instruction fetch from memory cells using the conversion function cell2instr. Thus, the function

```

current_instr s_{asm} \equiv cell2instr (s_{asm}.mm (s_{asm}.dpc div 4))

```

denotes the instruction that is executed next in the assembly machine. Note that the byte address  $s_{\mathsf{asm}}.\mathsf{dpc}$  is divided by 4 in order to get the word address of the current instruction in the main memory of  $s_{\mathsf{asm}}$ .

The assembly semantics can equally be employed in user- and system mode. The mode is determined by the special-purpose register SPR\_MODE. In user mode, it is illegal to access the special-purpose registers and solely the page-table length register SPR\_PTL is relevant for us. It determines the size of the main memory in pages of 1024 words. For convenience, we encapsulate this fact in the function size<sub>asm</sub> and define:

```

size_{asm} s_{asm} \equiv to\_nat32 (s_{asm}.sprs ! SPR\_PTL + 1)

```

The page table length is incremented by 1 because it is initially set to -1 which denotes that no virtual memory is allocated for the process.

A memory access beyond the specified size generates an exception in the real system and an illegal exception in the assembly semantics.

The VAMP assembly transition function  $\delta_{asm}$  computes for a given assembly state  $s_{asm}$  the next state. Essentially, the transition is specified by a case distinction over current\_instr  $s_{asm}$ .

#### 2.2.3 Isabelle/Simpl - A Verification Environment for C0

For the verification of C0, we use a general program-verification framework for sequential imperative programming languages: Isabelle/Simpl [68, 69]. It is built as a conservative extension on top of Isabelle/HOL. The key feature of Isabelle/Simpl is the notion of a Hoare-Triple:

```

\Gamma \vdash P \ c \ Q

```

In a procedure environment  $\Gamma$ , this statement claims that under the assertion P on the original program state, the assertion Q will hold after the execution of the code c given in the Simpl language. The assertions P and Q are simply sets of states. In principle, Isabelle/Simpl is polymorphic over the state space; we use records but hide the details by an Isabelle syntax, such that  $\{\sigma, \sigma^{\text{var}} = 5\}$  denotes the assertion that the value of program variable var in state  $\sigma$  is five. Whenever we implicitly refer to the state, the name

36 2. Background

will be decorated by the acute prefix '. For example, 'x will refer to field x in the state record.

Expressions in Simpl are HOL expressions. In addition to the HOL operations, we have defined bitwise conjunction  $x \wedge_u y$  and disjunction  $x \vee_u y$  over natural numbers (unsigned integers) x and y. Both operators first convert the natural numbers x and y into bit vectors of the same length. Afterwards, the corresponding bitwise operation is applied to the particular bits resulting in a bit vector which is finally converted into a natural number again. While the conjunction as well as the disjunction work on arbitrary natural numbers, the result of a bitwise negation depends on the width of the data type. Thus,  $\neg_{u/32} x$  denotes the bitwise negation of a 32-bit natural number x. As above, x is first converted into a bit vector of length 32. Afterwards, the particular bits are negated and the resulting bit vector is converted into a natural number again. In a similar way, we proceed with shift operations. With  $x \ll_{u/32} y$  we define a left shift of the 32-bit natural number x by y bits. Similarily, we define a right shift  $x \gg_{u/32} y$ .

In contrast to expressions, statements are represented by an abstract datatype. The statement syntax is highly abstract, e.g., Basic f represents a state update using function f. In order to present programs in conventional terms, we employ Isabelle's powerful syntax translation machinery and denote a program variable by 'var, an assignment by 'var :== 5, a conditional by IF b THEN  $s_1$  ELSE  $s_2$  FI, a procedure call by 'var :== CALL update(5), etc. The index g is used to instruct the parser to generate guards that protect against runtime faults like overflows.

The procedure environment  $\Gamma$  is a partial function from procedure names to statements. These statements constitute the procedure body and are defined by the Isabelle/Simpl command **procedures**. The following command, for instance, defines the procedure update:

```

\begin{array}{l} \mathbf{procedures} \ \mathsf{update}(\mathsf{var} \mid \mathsf{res\_nat}) = \\ \mathsf{'res\_nat} :==_{\mathsf{g}} \ \mathsf{'var} \end{array}

```

It has one formal parameter called var and the result to return to the calling function is held in variable res\_nat, i. e., the bar separates input and output parameters. When formally specifying the functionality of the procedure, we write 'res\_nat :== PROC update('var) as shorthand for the code of procedure update.

The Hoare-Triple

```

\Gamma \vdash \{\sigma. \ \sigma \text{var} = x\} \ \text{res\_nat} :== \mathbf{PROC} \ \mathsf{update}(\text{var}) \ \{\tau. \ \tau \text{res\_nat} = x\}

```

states that procedure update assigns the value of its argument to the return variable.

The framework includes a big-step semantics, a Hoare logic for partial as well as total correctness and an automated verification-condition generator for Simpl. Within this sequential core language, assembly fragments as well

as the C fragment C0 are embedded. The embedding is based on a compiler converting C0-constructs in terms of operations provided by the small-step semantics of the VAMP machine. A correctness proof for this compiler, which links the small-step semantics to the Simpl big-step semantics, is also provided [3]. This correctness theorem about the embedding of C0 into Simpl allows for mapping low-level properties to more abstract ones formulated on the big-step semantics of C0. Thus, throughout this paper, we will present all algorithms in Simpl (so that we can rely on a uniform Isabelle/HOL foundation); note that this Simpl code is the result of an automatic translation from the C0 code that is actually compiled and runs on the machine.

We employ the HOL type system to model C0 programming language types. Isabelle's type inference then takes care of typing constraints that would otherwise have to be explicitly maintained in the assertions. Propositions that explicitly refer to the memory layout or to hardware device registers cannot be proven on the C0-Hoare-Logic level; in these situations, the verification necessarily descends down to the VAMP level. Our approach is to abstract the effect of those low-level computations into atomic XCalls (extended calls) in all our semantic layers. In particular, the state-space of C0 is augmented with an additional component that represents the state of the external component, e.g., a device. An XCall is a procedure call that performs a transition on this external state and communicates with C0 via parameter passing and return values. With this model, it is straightforward to integrate XCalls into the semantics and into Hoare logic reasoning. XCalls are typically implemented in assembly.

#### Code Verification in Isabelle/Simpl

The introduction presents a bird's eye view on the refinement, as depicted in Figure 1.1. In principle, we can reformulate the depicted claim in Isabelle/Simpl as follows:

$$\Gamma \vdash \{\sigma. \text{ Abs } \sigma s\} \text{ PROC system\_step}() \{\tau. \text{ Abs } \tau (\delta s)\}$$

Assuming an abstraction relation Abs that holds for a concrete state  $\sigma$  and an abstract state s, the relation is preserved by the transitions system\_step on the concrete level and  $\delta$  on the abstract level. Just like the figure, this statement is an over-simplification. We postpone the details to Chapter 5.

Our approach to code verification combines refinement and code correctness, i.e., contracts are specified in terms of the abstract states. As a simple example, we assume a library function append, which appends an element to a singly-linked list. In the implementation, the list is represented as a pointer structure described by the variables head and next. In order to prove that a specific pointer structure in the state  $\tau$  after a function invocation indeed denotes a list, it is useful to know that the original pointer

structure in state  $\sigma$  already denoted a list. We encapsulate the list property in a predicate inv<sub>list</sub> over the pointer variables and formulate correctness of append(head, elem) as follows:

```

\Gamma \vdash \{\sigma. \text{ inv}_{\mathsf{list}} \text{ }^{\sigma} \text{head } \text{ }^{\sigma} \text{next } \land \text{ abs\_rel}_{\mathsf{list}} \text{ }^{\sigma} \text{head } \text{ }^{\sigma} \text{next } xs \} \text{ PROC append('head,'elem)} \\ \{\tau. \text{ inv}_{\mathsf{list}} \text{ }^{\tau} \text{head } \text{ }^{\tau} \text{next } \land \text{ abs\_rel}_{\mathsf{list}} \text{ }^{\tau} \text{head } \text{ }^{\tau} \text{next } (xs @ [\sigma \text{elem}]) \}

```

i.e., we express the effect of the function in terms of its abstract representation, which is a concatenation of lists.

#### 2.3 Devices

Devices may communicate with an external environment and the processor. The former is used to model non-determinism and communication; a network interface card, for example, sends and receives network packets. The processor accesses a device by reading or writing special addresses. The devices, in turn, can signal interrupts to the processor. So far, direct memory access (DMA) is not supported.

Device communication happens on many different layers throughout our system. In Verisoft, we established a uniform way of interacting with devices by developing a generic device framework featuring standardized transition functions for all layers. The detailed discussion of this model goes far beyond the scope of this work and it is not necessary for the further developing. Alkassar and Hillebrand [2] describe the model in detail.

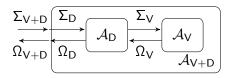

In a nutshell, the device model is pseudo-parallel in the sense that we either do an internal step – the device consumes a processor input – or an external step – the device consumes an external input, but never both at the same time. We use the automaton

$$\mathcal{A}_{D} = (\mathcal{S}_{D},\,\mathcal{S}_{D}^{0},\,\Sigma_{int},\,\Omega_{int},\,\omega_{D},\,\delta_{Dint},\,\Sigma_{ext},\,\Omega_{ext},\,\delta_{Dext})$$

to describe the devices. The state  $\mathcal{S}_D$  of the device system subsumes the particular device configurations with  $\mathcal{S}_D^0 \subset \mathcal{S}_D$  representing the set of the initial configurations. Devices communicate with the kernel resp. the processor by using the alphabet  $\Sigma_{int}$  (from the device subsystem to the processor) and the alphabet  $\Omega_{int}$  (from the processor to the devices). Our kernel uses memory-mapped I/O for device communication. Hence, the output alphabet  $\Omega_{int}$  comprises read and write accesses to device addresses whereas the input alphabet  $\Sigma_{int}$  consists of interrupt lines and optionally incoming data. The kernel can access the device system by means of the output function  $\omega_D$  which returns the interrupt vector of currently active interrupts. Kernelinitiated communication is performed by the transition function  $\delta_{Dint}$ . Based on an input from the kernel, it does not only yield a successor device state, but also output to the kernel and, potentially, to the environment.

The communication with the environment is based on an *external inter*face in order to receive keystrokes, for example, or send network packages. It is defined by the alphabets  $\Sigma_{ext}$  and  $\Omega_{ext}$ . Inputs from the environment consist of a device ID and an external device input. The external transition function  $\delta_{Dext}$  takes this input and computes the next state. While internal steps may result in both external and internal output, external steps only produce external output.

## 2.4 Communicating Virtual Machines

Virtually every modern operating system kernel is devided in a hardware-dependent and a hardware-independent part. Usually, the former part is small but employs inline assembly code, while the latter one is larger in size but written in a high-level programming language. From the verification perspective, inline assembly code requires a logic with much more machine details than that of a well-designed high-level language. Hence, the partitioning regarding functionality is very useful for our intended verification as well.

Based on these observations, we encapsulate all hardware-specific low-level functionality, which is possibly using inline assembly, in the layer of communicating virtual machines (CVM), which was first introduced in [34] and further developed in [65, 76]. We identify three major tasks for this abstraction layer: memory virtualization [72, 6], switching between different threads of execution [74], and data exchange [76]. For the hardware-independent part, CVM provides the means for access and manipulation of user machines by so-called primitives [73]. Examples are cvm\_copy, for copying data between two user machines, cvm\_alloc for increasing the virtual memory space, and cvm\_get\_gpr for reading a general purpose register of a user machine. The CVM primitives are simply functions that operate on CVM data structures and might possibly contain inline assembly. From the programmer's view, we have thus established a solid framework for microkernel construction [40]. Programmers can implement microkernels using CVM primitives and plain C0 without extra inline-assembler portions.

From the verification perspective, we established a semi-parallel model of computation that formalizes concurrent user machines interacting with a kernel. These user machines are abstract processors with virtual memory. The so-called abstract kernel is represented as an abstract C0 machine with typed memory. In addition to usual C0 functions, the kernel code might call CVM primitives. Hence, the primitives must have been declared in the C0 machine. Moreover, a function called dispatcher\_kernel must be defined, which CVM will call when an interrupt occurs. In order to obtain an executable, we have to link the CVM implementation with the abstract kernel [65]. We call the resulting executable the concrete kernel.

In the following, we will only briefly summarize the formal model of CVM. Apart from that, we refer to the mentioned literature.

#### 2.4.1 Cvm State

A CVM state  $s_{\text{CVM}}$  is a record with the following components:

- the abstract kernel cvm\_kernel,

- the virtual user processes cvm\_up, and

- the state of the device system cvm\_devs.

In CVM, the abstract kernel cvm\_kernel is modelled as a C0 machine. The component cvm\_up contains information on the virtual machines of the user processes. We denote the number of user processes including the kernel that are allowed to run in our system by the constant PID\_MAX = 128. For identifiers of user processes, we introduce the data type procnumT =  $\{1...<PID\_MAX\}$ , whereas identifier 0 is used for the kernel. CVM applies the VAMP assembly semantics to model the virtual user machines. Accordingly, component cvm\_up.userprocesses provides a mapping between process identifiers and VAMP assembly states. The component cvm\_up.currentp holds the identifier of the current process, which is determined by the process identifier  $\lfloor pid \rfloor$ , if process pid is running and  $\bot$ , if the kernel is running. Common to all processes is the interrupt mask cvm\_up.statusreg which is represented as a 32-bit natural number.

Initial Cvm State. An initial CvM state represents the situation after a reset and is described by the function init\_cvm\_sys. As the abstract kernel as well as the devices are parameters of the CvM model, they have to be provided as input:

```

init_cvm_sys ak \ devs \equiv (|cvm_kernel = init_cvm ak, cvm_up = init_cvmup, cvm_dev = init_dev devs)

```

In a nutshell, init\_cvm initializes the local stack and the program rest of the abstract C0 kernel machine ak, whereas init\_dev initializes the devices devs. Function init\_cvmup is used to initialize the abstraction of the virtual user processes, i.e., the program counters are set to 0, and the memory as well as the general- and most of the special-purpose registers are filled with zeroes. However, the page table origin in register SPR\_PTO is process-specific, whereas the page table length in register SPR\_PTL is set to -1, which denotes that no virtual memory is allocated for the process so far. In addition, the SPR\_MODE register is set to 1 intending that the machine runs in user mode.

So far, no process is running, i.e., the current process identifier is set to  $\bot$ . Finally, the status register enables the interrupts for illegal instructions, misalignment, page faults, traps, and the timer device.

For more formal details, we refer to [65, 76].

Valid Virtual Machines. In the remainder of this thesis and, in particular, in the correctness proof of our kernel, we rely on certain validity requirements for the virtual machines. Predicate is\_valid\_cvmup formally encapsulates these requirements:

```

is_valid_cvmup up \equiv \forall i. is_ASMcore (up.userprocesses i) \land (up.userprocesses i).sprs ! SPR_MODE \neq 0 \land -1 \leq (up.userprocesses i).sprs ! SPR_PTL < to_int32 TVM_MAXPAGES

```

First of all, each virtual machine represents a VAMP assembler machine in terms of is\_ASMcore and runs in user mode. Furthermore, a virtual machine is either occupied with no memory, i. e., its page table length equals -1, or the number of pages is less than TVM\_MAXPAGES.

#### 2.4.2 Cym Transitions

A CVM transition  $\delta_{\text{CVM}}$  takes a CVM state  $s_{\text{CVM}}$  and an external device input  $din_{\text{ext}}$  as parameters, yielding either a next configuration  $\lfloor s_{\text{CVM}}' \rfloor$  or  $\perp$ , if a run-time error has occurred, and potentially a device output to the environment.

Depending on the external device input  $\mathit{din}_{ext}$  and the current-process identifier  $s_{CVM}.cvm\_up.currentp$ , the CVM transition function  $\delta_{CVM}$  distinguishes three cases<sup>2</sup>:

- 1. If  $din_{\mathsf{ext}} \neq \bot$ , a device step is performed. In this case, only the device component of  $s_{\mathsf{CVM}}$  is updated with the new device configuration (obtained by  $\delta_{\mathsf{Dext}}$ ). Additionally, a device output to the environment might be generated.

- 2. If there is no external device input and the current process identifier is ⊥, the abstract kernel makes a step.

- 3. Otherwise, the current process makes a step.

In the latter case, CVM distinguishes three sub-cases: (a) an user step without interrupts, (b) an user step with an interrupt that aborts the user execution (illegal instruction, misalignment, etc.), and (c) an user step with an interrupt, but one which allows the current process to take a step (external interrupts, trap, and overflow).

User steps without interrupts boil down to an application of the VAMP assembly transition function  $\delta_{asm}$  to the virtual machine of the current process. Steps with interrupts result in an invocation of the abstract kernel.

<sup>&</sup>lt;sup>2</sup>Note that, in this context, we only consider *live* executions meaning that the kernel, the user processes and the devices are executed infinitely often. Thus, it may not happen that, for instance, device steps might block the kernel forever.

Whether thereby the current process takes a step depends on the kind of interrupts. In case of a runtime error, i.e., the user execution is aborted, the virtual machine of the current process remains unchanged. Otherwise, the current process makes a step according to  $\delta_{asm}$ .