# On the Formal Foundation of a Verification Approach for System-Level Concurrent Programs

# Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

# Matthias Daum

md11@wjpserver.cs.uni-saarland.de

Saarbrücken, 10. August 2010

# **Eidesstattliche Versicherung**

Hiermit versichere ich an Eides statt, dass ich die vorliegende Arbeit selbständig und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet.

Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in einem Verfahren zur Erlangung eines akademischen Grades vorgelegt.

Saarbrücken, den 26. Februar 2010

Tag des Kolloquiums: 28. Juni 2010

Dekan: Prof. Dr. Holger Hermanns

Vorsitzender des Prüfungsausschusses: Prof. Dr. Raimund Seidel

Berichterstatter: Prof. Dr. Wolfgang J. Paul

Berichterstatter: Prof. Dr. Burkhart Wolff

3. Berichterstatter: Prof. Dr. Reinhard Wilhelm

akademischer Mitarbeiter: Dr. Eyad Alkassar

In memoriam

RICHARD PRASSE 1915-2008

I wake up every morning, and I still haven't finished the book.

Donald Knuth about "The Art of Computer Programming"

# **Acknowledgments**

During graduation, many people have supported me, and though I cannot name everyone, I am grateful to all of them. In particular, I am indebted to Prof. Wolfgang Paul for the opportunity to work at his chair. Furthermore, I thank my colleagues, who devoted much time to many lively and fruitful discussions, among them Sebastian Bogan, Jan Dörrenbächer, Mark Hillebrand, Dirk Leinenbach, Norbert Schirmer, Mareike Schmidt, and Burkhart Wolff. Last but not least, I am much obliged to my family and friends who never grew tired in encouraging me.

This work has been partially funded by the German Federal Ministry of Education and Research (BMBF) in the framework of the Verisoft project under grant 01 IS C38.

#### **Abstract**

Though program verification is known and used since decades, the verification of a complete computer system still remains a grand challenge. In essence, this challenge stems from the interaction of various programs. Different techniques have been proposed for the verification of communicating programs. Common to all, however, is that they rely on several (usually implicit) assumptions about the underlying system. Typically, such assumptions include compiler correctness, scheduler fairness, and a certain non-interference between the local program behavior and its environment. This thesis aims at discharging these assumptions for the processes of the microkernel VAMOS. More specifically, this work formally justifies the abstraction from a kernel model with explicit, deterministic scheduling to a concurrent process system with non-deterministic but temporally fair scheduling. Our formal results form the foundation of a verification approach for system-level concurrent programs. We outline this approach on example properties of a user-mode operating system.

# Kurze Zusammenfassung

Obwohl es schon jahrzehntelang Programmverifikation gibt, wird die Verifikation eines kompletten Computersystems auch heute noch als eine große Herausforderung angesehen. Im Wesentlichen ergibt sich diese Herausforderung aus der vielfältigen Interaktion von Programmen. Verschiedene Techniken wurden für die Verifikation kommunizierender Programme vorgeschlagen. Alle haben jedoch gemein, dass sie sich auf mehrere (meist implizite) Annahmen über das zugrunde liegende System stützen. In der Regel sind solche Annahmen Compiler-Korrektheit, Scheduler-Fairness und eine gewisse Störfreiheit des lokalen Programmverhaltens vom Verhalten seiner Umgebung. Die vorliegende Dissertation beschäftigt sich mit der Entlastung dieser Annahmen für die Prozesse des Mikrokerns VAMOS. Genauer gesagt, rechtfertigt diese Arbeit formal die Abstraktion von einem Kernmodell mit explizitem, deterministischem Scheduling zu einem nebenläufigen Prozesssystem mit nicht-deterministischem, aber temporal fairem Scheduling. Die formalen Ergebnisse bilden die Grundlage eines Verifikationsansatzes für nebenläufige, systemnahe Programme. Dieser Ansatz wird am Beispiel von Eigenschaften eines User-Mode-Betriebssystems erläutert.

# Ausführliche Zusammenfassung

Werden Computer in sicherheitskritischen Bereichen eingesetzt, spielt Robustheit – und insbesondere die Vermeidung menschlicher Irrtümer – eine entscheidende Rolle. Verifikation ist die sicherste Technik zum Ausschluss systematischer Fehler beim Systementwurf. Dazu wird das korrekte Verhalten des untersuchten Systems durch ein mathematisches Modell spezifiziert und ein Beweis dafür entwickelt, dass der Systementwurf dieser Spezifikation genügt. Von formaler Verifikation sprechen wir, wenn der Beweis durch einen Computer überprüft wird.

In der Regel werden Computersysteme in mehreren Ebenen realisiert: Schon die Hardware ist auf den verschiedenen Abstraktionsebenen modelliert; das Betriebssystem stützt sich auf die abstrakteste Hardware-Schicht, und dieses bietet wiederum eine Abstraktion an, auf deren Basis schließlich die Benutzerprogramme implementiert werden. Will man alle systematischen Fehler im kompletten Systementwurf sicher ausschließen, muss man alle Ebenen in die Verifikation mit einbeziehen. Die Verifikation eines Systems über mehrere Abstraktionsebenen hinweg nennen wir durchgängig.

Obwohl Programmverifikation seit Jahrzehnten bekannt ist und vielfach eingesetzt wird, bleibt die durchgängige formale Verifikation eines vollständigen Computersystems – angefangen vom Hardware-Design bis hinauf zu den Benutzerprogrammen – nach wie vor eine große Herausforderung [Moo02]. Ein ganz wesentlicher Aspekt dieser Herausforderung besteht darin, dass reale Programme vielfältig miteinander kommunizieren. Selbst einfachste Beispiele wie ein "Hallo Welt"-Programm erzeugt Ausgabedaten; in der Regel wird das Betriebssystem angewiesen, diese Daten an ein Ausgabegerät zu übertragen.

Betriebssystemkerne stellen Benutzerprogrammen eine Prozessorabstraktion mit exklusivem Zugang zu Ressourcen wie Registern und Speicher zur Verfügung. Diese Abstraktion wird üblicherweise *Prozess* genannt [Kno74]. Ein wichtiges Merkmal von Prozessen ist ein Mittel zur Kommunikation mit dem Kern zur Anfrage weiterer Dienste. Da die meisten Programme kompiliert werden, um schließlich als Prozess unter einem Betriebssystemkern zu laufen, verallgemeinern wir den üblichen Prozessbegriff etwas auf eine Programmsemantik mit Primitiven zur Kommunikation mit einem Kern.

Zur Verifikation kommunizierender Programme wurden verschiedene Techniken vorgeschlagen. Allen gemeinsam ist jedoch, dass sie auf mehreren (meist impliziten) Annahmen über das zugrunde liegende System beruhen. Häufig schließen diese Annahmen Compiler-Korrektheit, Scheduler-Fairness und eine gewisse Störfreiheit des lokalen Programmverhaltens vom Verhalten seiner Umgebung ein. Die vorliegende Dissertation beschäftigt sich mit der Entlastung dieser Annahmen für die Prozesse des Mikrokerns VAMOS. Genauer gesagt, rechtfertigt diese Arbeit formal die Abstraktion von einem Kernmodell mit explizitem, deterministischem Scheduling zu einem nebenläufigen Prozesssystem mit nicht-deterministischem, aber temporal fairem Scheduling.

Im Rahmen der vorliegenden Arbeit wurde der VAMOS-Kern verbessert, indem sowohl Beschränkungen der maximalen Laufzeit des Kerns aufgehoben wurden, als auch die Fairness des Scheduling-Algorithmus hergestellt wurde.

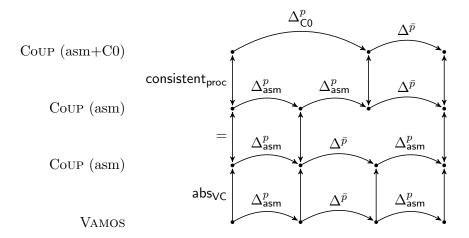

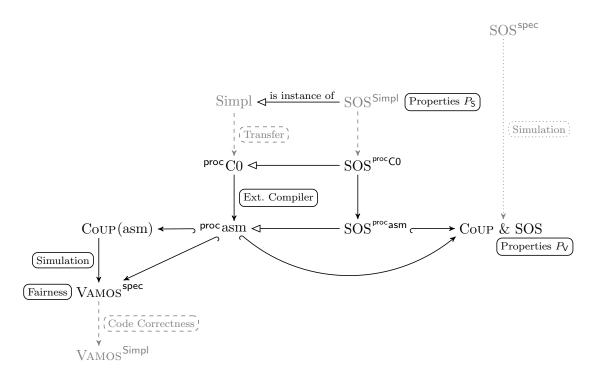

Darüber hinaus wurde ein Compiler-Satz für sequentielle Sprachen auf die Semantik von Prozessen erweitert. Dieses Ergebnis basiert auf dem von Leinenbach & Petrova [LP08] formal verifizierten Compiler. Dieser Compiler übersetzt aus dem C-Dialekt C0 in Assembler. Darauf aufbauend wurden (a) die Kommunikationsprimitive des VAMOS-Kerns formalisiert, (b) C0- und Assembler-Prozesse spezifiziert, indem die sequentiellen Sprachen um die Kommunikationsprimitive erweitert wurden und (c) ein Simulationstheorem entwickelt, das die Prozessmodelle verbindet und den ursprünglichen, sequentiellen Compiler-Satz erweitert.

Die Prozessmodelle werden in zwei Kernmodellen verwendet: ein deterministisches Modell, welches das genaue Verhalten von Vamos einschließlich seines Schedulers spezifiziert, und ein nicht-deterministisches, nebenläufiges Modell kommunizierender Prozesse, das vom Scheduler abstrahiert. Zur Entwicklung des ersteren haben wir wesentlich beigetragen, das letztere haben wir allein entwickelt. In einem noch laufenden Verifikationsversuch wird das deterministische Modell benutzt, um die korrekte Implementierung von Vamos zu zeigen [DDW09, Sect. 6]. Teil der vorliegenden Arbeit war es dagegen, die Simulation zwischen dem deterministischen und dem nebenläufigen System zu zeigen.

Schließlich wurde ein Begriff temporaler Fairness definiert. Basierend auf der Kernspezifikation wurde dann formal gezeigt, dass der Vamos-Scheduler dieser Definition gerecht wird.

Zusammengefasst umfasst die Arbeit drei formale Hauptergebnisse: (a) einen Ansatz zum Erweitern von Compiler-Korrektheit von rein sequentiellen Sprachen auf Prozesse, (b) einen Simulationssatz zwischen einem Vamos-Modell mit explizitem Scheduler und einem nebenläufigen Kernmodell und (c) einen formalen Beweis für das temporal faire Scheduling von Prozessen in Vamos. Gemeinsam bilden diese Ergebnisse die Grundlage eines Verifikationsansatzes für nebenläufige, systemnahe Programme. Dieser Ansatz wird am Beispiel von Eigenschaften eines User-Mode-Betriebssystems erläutert.

# **Contents**

| 1 | Intr | oduction                                               | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Notation                                               | 3  |

|   | 1.2  | Basic Concepts                                         | 5  |

|   |      | 1.2.1 Kleene Algebras and the Kleene Star              | 5  |

|   |      | 1.2.2 Future-Time Linear Temporal Logic                | 6  |

|   | 1.3  | Related Work                                           | 7  |

|   |      | 1.3.1 Verification Methods for Concurrent Programs     | 8  |

|   |      | 1.3.2 Verification Frameworks for Concurrent Programs  | 9  |

|   |      | 1.3.3 Kernel Verification                              | 10 |

|   |      | 1.3.4 Operating-System Verification                    | 11 |

| 2 | Fun  | damentals                                              | 13 |

|   | 2.1  | Implementing the Academic System: The Software Stack   | 14 |

|   | 2.2  | · ·                                                    | 15 |

|   | 2.3  | The Language C0                                        | 16 |

|   | 2.4  |                                                        | 18 |

|   | 2.5  |                                                        | 20 |

|   | 2.6  |                                                        | 25 |

|   | 2.7  | Extending the Language Stack: a Roadmap to Concurrency | 25 |

| 3 | The  | VAMOS Microkernel: Design and Implementation           | 27 |

|   | 3.1  | · · · · · · · · · · · · · · · · · · ·                  | 28 |

|   | 3.2  |                                                        | 28 |

|   |      | 3.2.1 Inter-Process Communication                      | 30 |

|   |      | 3.2.2 Process Scheduling                               | 31 |

|   | 3.3  |                                                        | 31 |

|   | 3.4  | Conclusion                                             | 34 |

| 4 | Pro  | cess Abstraction                                       | 35 |

|   | 4.1  | Motivation                                             | 36 |

|   | 4.2  |                                                        | 37 |

|   | 4.3  |                                                        | 43 |

|   | 4.4  | · · · · · · · · · · · · · · · · · · ·                  | 47 |

|   | 4.5  |                                                        | 55 |

|   | 4.6  | Conclusion                                             | 62 |

| 5 | Add | ling Concurrency: The Kernel Models                                    | 63          |

|---|-----|------------------------------------------------------------------------|-------------|

|   | 5.1 | Overview of the Model Components                                       | 64          |

|   | 5.2 | A Simple Kernel Call: Set_Privileged Revisited                         | 67          |

|   | 5.3 | Process Termination                                                    | 68          |

|   | 5.4 | Inter-Process Communication                                            | 71          |

|   |     | 5.4.1 IPC Rights Management                                            | 71          |

|   |     | 5.4.2 Specifying IPC in the VAMOS Model                                | 72          |

|   |     | 5.4.3 IPC in CoUP                                                      | 76          |

|   | 5.5 | The Scheduler Specification                                            | 78          |

|   | 5.6 | Invariants over Execution Traces                                       | 81          |

|   | 5.7 | Conclusion                                                             | 85          |

| 6 | Sim | ulation: Formally Relating the Kernel Models                           | 87          |

|   | 6.1 | Kernel-Model Simulation                                                | 87          |

|   | 6.2 | Abstracting Concurrent Assembly Processes to C0 Processes              | 90          |

|   |     | 6.2.1 On the Commutability of Transitions: From Trace Theory to Kleene | <b>A</b> l- |

|   |     | $\operatorname{gebra}$                                                 | 91          |

|   |     | 6.2.2 Process Simulation Meets True Concurrency                        | 92          |

|   |     | 6.2.3 Commuting Transitions in CoUP                                    | 93          |

|   | 6.3 | Conclusion                                                             | 95          |

| 7 | АТ  | emporal Property: Scheduler Fairness                                   | 97          |

|   | 7.1 | An Introductory Scheduling Example                                     | 97          |

|   | 7.2 | Common Notions of Fairness                                             |             |

|   | 7.3 | Developing and Proving Prioritized Fairness                            |             |

|   | 7.4 | Rephrasing the Temporal Property in LTL                                | 103         |

|   | 7.5 | Conclusion                                                             | 104         |

| 8 | Tow |                                                                        | 107         |

|   | 8.1 | Non-Termination                                                        |             |

|   | 8.2 | Fair Scheduling of Applications                                        |             |

|   |     | 8.2.1 Priorities in the SOS                                            |             |

|   |     | 8.2.2 Applying Scheduler Fairness to Applications                      |             |

|   | 8.3 | Conclusion                                                             | 112         |

| 9 | Con |                                                                        | 115         |

|   | 9.1 | Formal Results                                                         |             |

|   | 9.2 | Measuring the Formal Verification Effort                               | 117         |

|   | 9.3 | Outlook                                                                | 118         |

# 1 Introduction

#### What is truth?

Pilate, according to John, 18:38

### Contents

| 1.1 | Notation                            |               |         |     |      |  |  |  | 3  |

|-----|-------------------------------------|---------------|---------|-----|------|--|--|--|----|

|     | Basic Concepts                      |               |         |     |      |  |  |  |    |

|     | 1.2.1 Kleene Algebras and the Kle   | eene Star .   |         |     | <br> |  |  |  | 5  |

|     | 1.2.2 Future-Time Linear Tempora    | al Logic      |         |     | <br> |  |  |  | 6  |

| 1.3 | Related Work                        |               |         |     | <br> |  |  |  | 7  |

|     | 1.3.1 Verification Methods for Cor  | ncurrent Prog | grams . |     | <br> |  |  |  | 8  |

|     | 1.3.2 Verification Frameworks for   | Concurrent I  | Program | s . | <br> |  |  |  | 9  |

|     | 1.3.3 Kernel Verification           |               |         |     | <br> |  |  |  | 10 |

|     | 1.3.4 Operating-System Verification | on            |         |     | <br> |  |  |  | 11 |

If computers are used in a highly secure or even safety-critical context, robustness – and in particular the avoidance of human errors – plays an essential role. *Verification* is the most rigorous technique for the exclusion of systematic design errors. This approach specifies the correct behavior of the examined system by a mathematical model and develops a proof that the system design meets this specification. We speak of *formal* verification if the proof is checked by a computer.

Usually, computer systems are implemented in several layers: Even the hardware is modeled at different levels of abstraction, the operating system is based on the hardware layer, and on top of that, the user programs are implemented. In order to safely exclude all systematic errors in the design of the complete system, all layers must be regarded. If a verification attempt spans over multiple layers of a system, we call it *pervasive*.

While program verification has been known and used over decades, the pervasive, formal verification of a complete computer system from the hardware design up to application programs still remains a grand challenge [Moo02]. In essence, the challenge stems from the interaction of various programs in a real system – even a simplistic "Hello World"-program produces output data, usually instructing the operating system to transfer the data to the output peripheral.

Operating-system kernels provide a processor abstraction to user programs with the exclusive access to resources like registers and memory. This abstraction is commonly referred to as a *process* [Kno74]. An important feature of processes is a means to communicate with the kernel to request further services. As most programs are eventually

compiled to run as a process under a kernel, we slightly generalize the common process notion to a program semantics with primitives for the communication with a kernel.

Different techniques have been proposed for the verification of communicating programs. Common to all, however, is that they rely on several (usually implicit) assumptions about the underlying system. Typically, such assumptions include compiler correctness, fairness, and a certain non-interference between the local program behavior and its environment. This thesis aims at discharging these assumptions for the processes of the microkernel VAMOS. More specifically, this work formally justifies the abstraction from a kernel model with explicit, deterministic scheduling to a concurrent process system with non-deterministic but temporally fair scheduling.

In the course of our work, we have improved the VAMOS kernel by overcoming limitations of the maximal runtime, on the one hand, and by enabling fair scheduling, on the other hand.

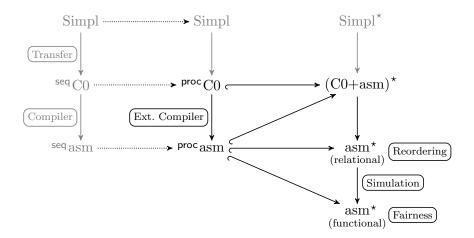

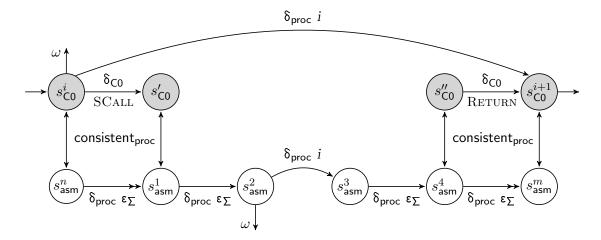

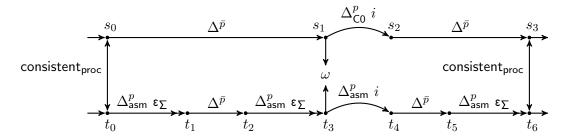

Furthermore, we have extended a compiler theorem for sequential languages to processes. In particular, our work is based on Leinenbach & Petrova's [LP08] formally verified compiler. Their compiler translates from the C dialect C0 into assembly language. We have (a) formalized the communication primitives of the VAMOS kernel, (b) specified C0 and assembly processes by enriching the sequential languages with communication primitives, and (c) formally stated a simulation theorem relating the process models, which extends the original compiler-correctness theorem that relates the sequential semantics.

The process models are used in two kernel models: a deterministic model specifying the exact VAMOS behavior, and a non-deterministic, concurrent model of communicating processes, which abstracts from the scheduler. We have contributed to the former and have developed the latter. While an ongoing verification attempt uses the deterministic specification to show that VAMOS is correctly implemented [DDW09, Sect. 6], we have shown that the concurrent model indeed simulates the kernel specification.

Finally, we have defined a temporal fairness notion. Based on the kernel specification, we have formally shown that the VAMOS scheduler is fair according to this definition.

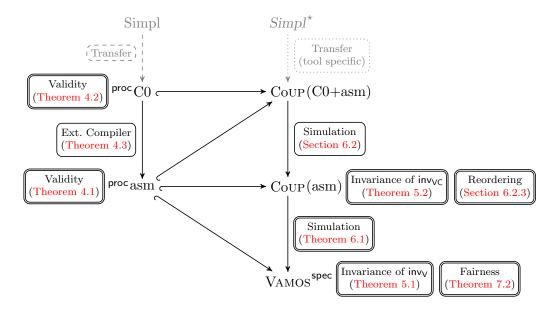

Summarizing, this thesis presents three main results: (a) an approach to extend compiler correctness from purely sequential languages to processes, (b) a simulation theorem from a VAMOS model with explicit scheduling to a concurrent kernel model, and (c) a formal proof for the fair scheduling of processes in VAMOS. These results form the foundation of a verification approach for system-level concurrent programs. We sketch this approach on example properties of a user-mode operating system.

**Outline.** The remainder of this chapter introduces notation, recapitulates general mathematical and logical concepts, and presents related work. The next chapter, in contrast, describes specific background information about the context and prerequisites of this thesis. It concludes with a detailed overview of the actual thesis work.

The main part of this thesis starts in Chapter 3, which provides an insight into the design principles of the VAMOS kernel and exemplifies an implementation challenge. Chapter 4 details the kernel communication primitives and the semantics of assembly and C0

processes. Furthermore, compiler correctness is extended to processes with communication primitives. Chapter 5 then introduces two kernel models describing the interleaved execution of processes in the kernel. Chapter 6 sketches the proof of independence of process transitions in an interleaved execution between adjacent communication points as well as the embedding of C0 processes into a concurrent kernel model. Chapter 7 reports on the verification that the scheduler of our microkernel is indeed fair. Finally, Chapter 8 exemplifies how the provided models can be used for the verification of a user-mode operating system. We conclude in Chapter 9 and present future work.

# 1.1 Notation<sup>1</sup>

The formalizations presented in this thesis are mechanized and checked within the generic interactive theorem prover Isabelle [Pau94]. Isabelle is called generic as it provides a framework to formalize various object logics that are declared via natural-deduction-style inference rules within Isabelle's meta-logic Pure. The object logic that we employ for our formalization is the higher-order logic of Isabelle/HOL [NPW02], which is based on the typed  $\lambda$ -calculus.

This article is written using Isabelle's document-generation facilities, which guarantees that the presented theorems correspond to formally proven ones. We distinguish formal entities typographically from other text. We use a sans-serif font for types and constants (including functions and predicates), e. g., replicate, a slanted serif font for free variables, e. g., x, and a slanted sans-serif font for bound variables, e. g., x. Small capitals are used for data-type constructors, e. g., Foo. Keywords are set in type-writer font, e. g., let.

As Isabelle's inference kernel manipulates rules and theorems at the Pure level, the meta-logic becomes visible to the user and also in this document when we present theorems and lemmas. The Pure logic itself is intuitionistic higher-order logic, where universal quantification is  $\bigwedge$ , implication is  $\Longrightarrow$ , and equality is  $\equiv$ . Nested implications like  $P_1 \Longrightarrow P_2 \Longrightarrow P_3 \Longrightarrow C$  are abbreviated with  $[P_1; P_2; P_3] \Longrightarrow C$ , where we refer to  $P_1, P_2$ , and  $P_3$  as the premises and to C as the conclusion. We may also write:

$$\frac{P_1 \qquad P_2 \qquad P_3}{C}$$

In the object logic HOL, universal quantification is  $\forall$ , implication is  $\longrightarrow$ , and equality is =. We sometimes use the abbreviation  $P \longleftrightarrow Q$  for  $(P \to Q) \land (Q \to P)$ . The other logical and mathematical notions follow the standard notational conventions with a bias towards functional programming. Isabelle/HOL provides a library of standard types like Booleans, natural numbers, integers, total functions, pairs, lists, and sets as well as packages to define new data types and records. We only present them shortly in the following.

<sup>&</sup>lt;sup>1</sup>For taming Isabelle's powerful document-generation mechanism in general, and in particular for the major part of this section, I am indebted to Schirmer *et al.* [Sch06, AHL<sup>+</sup>09]

Partial functions are usually formalized in HOL with the option type. This type is a data type with two constructors, one to inject values of the base type, e.g.,  $\lfloor x \rfloor$ , and the other one is simply the additional element  $\bot$ . With  $\lceil y \rceil$ , the original base value x can be obtained such that  $y = \lfloor x \rfloor$ . Note that there is no base value x iff  $y = \bot$ . As HOL is a total logic, the term  $\lceil \bot \rceil$  is nevertheless a well-defined yet unspecified value. For an update of a partial function, we write  $f(y \mapsto y)$ .

For data types, we write the structural case distinction over some value v as **case** v **of**  $\bot \Rightarrow g \mid \lfloor x \rfloor \Rightarrow f$  x. Some data types might have many constructors, which are all treated in the same fashion in a certain situation. In this situation, we may write **case** v **of** Foo  $\Rightarrow x \mid \_ \Rightarrow y$ , which means value x if v has the value Foo, and otherwise value y.

**Sets, Intervals, and Relations.** Sets come along with the standard operations for union, i.e.,  $A \cup B$ , intersection, i.e.,  $A \cap B$  and membership, i.e.,  $x \in A$ . We denote the interval of the numbers a and b excluding the endpoints by  $\{a<...< b\}$ , and including the endpoints by  $\{a..b\}$ . Furthermore, we write  $a < c \le b$  to denote that a number c is in the interval  $\{a<..b\}$ . Relational composition is written as  $R_1 \circ R_2$ .

**Lists.** The syntax and the operations for lists are similar to functional programming languages like ML or Haskell. The empty list is [] and by  $x \odot xs$  the list xs is preceded with the element x. We write [a, b, c] instead of  $a \odot b \odot c \odot$  []. With  $xs \odot ys$ , list ys is appended to list xs. The function concat takes a list of lists as argument and returns the concatenation of these lists. The length of a list xs is written |xs|, the n-th element of a list can be selected with xs ! n and updated via xs[n := v]. With xs we obtain the set of elements in list xs. Filtering those elements from a list, for which predicate xs holds, is achieved by xs with xs with replicate xs we denote a list that consists of xs elements xs.

**Records.** A record is constructed by assigning all of its fields: ( $|f|d_1 = v_1$ ,  $f|d_2 = v_2$ ). Field  $f|d_1$  of record r is selected by  $r.f|d_1$  and updated with value x via  $r(|f|d_1 := x)$ .

# 1.2 Basic Concepts

#### 1.2.1 Kleene Algebras and the Kleene Star

In automata theory as well as in the theory of formal languages, *Kleene algebras* are an important class of algebraic structures. Various inequivalent definitions can be found in the literature; we adopt the one by Kozen [Koz90].

**Definition 1.1** (Semiring). An algebraic structure  $(U, +, \cdot)$  with the universe U and the binary operators + (addition) and  $\cdot$  (multiplication) is a *semiring* if it satisfies the following constraints:

- 1. (U, +) is a commutative monoid with identity element 0, i. e.,

- a) (a+b) + c = a + (b+c)

- b) 0 + a = a

- c) a + b = b + a

- 2.  $(U, \cdot)$  is a monoid with identity element 1, i. e.,

- a)  $(a \cdot b) \cdot c = a \cdot (b \cdot c)$

- b)  $1 \cdot a = a$

- c)  $a \cdot 1 = a$

- 3. Multiplication distributes over addition:

- a)  $(a+b) \cdot c = a \cdot c + b \cdot c$

- b)  $a \cdot (b+c) = a \cdot b + a \cdot c$

- 4. 0 annihilates U with respect to multiplication:

- a)  $0 \cdot a = 0$

- b)  $a \cdot 0 = 0$

**Definition 1.2** (Idempotent Semiring). We call a semiring  $(U, +, \cdot)$  idempotent if its addition is idempotent, i.e., a + a = a.

**Definition 1.3** (Kleene Algebra). An idempotent semiring  $(U, +, \cdot)$  is called a *Kleene algebra* iff

- 1. the universe U is partially ordered such that  $a \leq b \equiv a + b = b$ , and

- 2. a unary operation  $\star$  is defined satisfying the following axioms:

- a)  $1 + a \cdot a^* \le a^*$

- b)  $1 + a^{\star} \cdot a \leq a^{\star}$

- c)  $a \cdot x \le x \implies a^{\star} \cdot x \le x$

- d)  $x \cdot a \le x \implies x \cdot a^* \le x$

The operation \* is also called *Kleene star*. Often, it is defined as the sum over all powers of the operand, i. e.,  $a^* \equiv \sum_{n \geq 0} a^n$  where  $a^0 \equiv 1$  and  $a^{n+1} \equiv a \cdot a^n$ . Depending on the application field, the Kleene star has different interpretations: In programming-language theory, it might be used as "iteration" (where multiplication means "sequencing"). In the context of concurrency, in contrast, the star often symbolizes a varying number of concurrent treads of control (with multiplication meaning "concurrency").

#### 1.2.2 Future-Time Linear Temporal Logic

Linear temporal logic (LTL) [Lam80b, EH86] is a modal logic [Pri57], which features modalities of time like in the statements "property P has been true" and "P will be true". In this document, however, we are only interested in the future modality. Furthermore, we are only concerned with the LTL language but do not define any proof rules. Below, we introduce the syntax, specify its semantics, and shortly reflect on practical aspects.

**Syntax.** We define the syntax of LTL recursively. An LTL formula is one of:

- 1. a propositional variable P,

- 2. a negated LTL formula  $\neg \varphi$ ,

- 3. a conjunct of two LTL formulae  $\varphi \wedge \psi$ ,

- 4. the unary next operation applied to an LTL formula  $\mathcal{N}\varphi$ , or

- 5. the binary until operation of two LTL formulae  $\varphi \mathcal{U} \psi$ .

**Semantics.** Temporal logics are traditionally interpreted in terms of *Kripke structures*, a type of non-deterministic finite-state machine proposed by Saul Kripke [Kri63] in 1963. A Kripke structure is a triple  $(S, \Delta, L)$  with a set S of states, a binary relation  $\Delta \in S \times S$ , and a set L of propositions over S. Temporal logics formulate properties on state sequences of such finite-state machines.

In Isabelle/HOL, we define the LTL semantics over sets of infinite state sequences, or traces, and represent a trace as a function t from natural numbers to states. In particular, the validity of a formula at time t of a trace t is defined by structural induction:

```

\begin{aligned} &(t,j) \models P \equiv P \ (t \ j) \\ &(t,j) \models \neg \varphi \equiv \neg \ ((t,j) \models \varphi) \\ &(t,j) \models \varphi \land \psi \equiv ((t,j) \models \varphi) \land ((t,j) \models \psi) \\ &(t,j) \models \mathcal{N} \varphi \equiv (t,j+1) \models \varphi \\ &(t,j) \models \varphi \ \mathcal{U} \ \psi \equiv \exists k \geq j. \ ((t,k) \models \psi) \land (\forall i \in \{j... < k\}. \ (t,i) \models \varphi) \end{aligned}

```

with propositions P over states and LTL formulae  $\varphi$  and  $\psi$ . Furthermore, we define the validity of formula  $\varphi$  for a set K of traces (usually specified by a Kripke structure) as follows:

$$K \models \varphi \equiv \forall t \in K. \ (t,0) \models \varphi$$

Ultimately, we specify the term  $\langle S^0, \Sigma, \delta \rangle_{A}$  describing an action Kripke structure with input. This structure specifies the set of all traces that can be produced by the set of initial states  $S^0$ , the input alphabet  $\Sigma$ , and the transition function  $\delta$ . Each trace in this set is a function from natural numbers to triples (i, s, n), where i is the input for the transition, s is the current state, and n is the next state. Formally, we define:

```

\begin{split} \langle \mathcal{S}^0, \ \varSigma, \ \delta \rangle_{\mathsf{A}} &\equiv \\ \{t. \ (\exists i \ s \ n. \ t \ 0 = (i, \ s, \ n) \ \land \ s \in \mathcal{S}^0) \ \land \\ (\forall j. \ \exists i \ s \ n. \\ t \ j &= (i, \ s, \ n) \ \land \\ i \in \varSigma \land \delta \ i \ s &= n \land (\exists i' \ s' \ n'. \ t \ (j+1) = (i', \ s', \ n') \land s' = n))\} \end{split}

```

**Abbreviations.** For succinctness, we define the usual logical abbreviations truth  $\top_{\mathsf{L}}$ , falsehood  $\bot_{\mathsf{L}}$ , disjunct  $\varphi \lor \psi$ , implication  $\varphi \longrightarrow \psi$ , as well as the following specifically temporal-logical abbreviations:

- the unary eventually operation:  $\Diamond \varphi \equiv \top_{\mathsf{L}} \mathcal{U} \varphi$ ,

- the unary always operation:  $\Box \varphi \equiv \neg \Diamond \neg \varphi$ ,

- the binary release operation:  $\varphi \mathcal{R} \psi \equiv \neg(\neg \varphi \mathcal{U} \neg \psi)$ , and

- the binary weak until operation:  $\varphi \mathcal{W} \psi \equiv \varphi \mathcal{U} \psi \vee \Box \varphi$ .

The first two operations can be perceived as existential and universal quantifier over traces. Release and weak until are both variations of the until operation.

Common to all formal logics is that they precisely define certain terms of everyday language. In temporal logic, this is particularly true for the temporal conjunction until: In everyday language, it is unclear whether the terminating event must occur. A statement  $\varphi \mathcal{U} \psi$ , however, is definitely false if  $\psi$  never becomes true. Some authors therefore call this operator the *strong until*. For the weaker statement that the formula  $\varphi$  remains valid as long as the formula  $\psi$  is not satisfied, we denote:  $\varphi \mathcal{W} \psi$  (weak until). A similar statement is expressed by the release operator, where, in contrast to weak until, both substatements must simultaneously hold in the terminating state, i. e.,

$$(K \models \varphi \ \mathcal{R} \ \psi) \longleftrightarrow (K \models \psi \ \mathcal{W} \ \psi \land \varphi)$$

which easily follows from the definitions of the involved operations.

**Terminology.** Certainly, the operations might be combined, e.g.,  $\Box \Diamond \varphi$ . In the context of temporal logics, it is custom to state that property  $\varphi$  holds always eventually. In natural language, such a statement might confuse. Note that temporal logics implicitly refers to a trace, such that always can be understood as on any suffix of a trace. You may equally refer to  $\Box \Diamond \varphi$  as infinitely often  $\varphi$ .

**Application Domain.** LTL is usually employed to show certain kinds of properties:

Safety properties claim that a certain property holds for all states in a trace:  $\Box P$  Liveness properties claim that some property is eventually satisfied:  $\Diamond P$  Fairness properties claim that a property holds infinitely often in a trace:  $\Box \Diamond P$  Persistence properties claim that a property is established once and for all:  $\Diamond \Box P$ .

Certainly, hybrid forms are possible like a fairness property relying on some persistence:  $\Diamond \Box P \longrightarrow \Box \Diamond Q$ . We may view partial correctness of a program as a safety property: Given that a terminating state is reached, the computational result should have some form or value:  $\Box(\lambda s. \text{ terminated } s \longrightarrow \text{corr\_res } s)$ . Program termination, in contrast, is a liveness property:  $\Diamond \text{terminated}$ .

#### 1.3 Related Work

The work in this thesis is mainly related to two research areas: the verification of concurrent programs and the pervasive verification of operating systems. Both research

areas can further be subdivided. In the former, we distinguish abstract verification methods and formal verification frameworks implementing such methods. In the latter, we regard the verified layer: Most operating systems cope with the vast complexity of their task by separating their core functionality, which runs in the privileged system mode of the processor, from additional services, which run in the unprivileged user mode. Consequently, we divide verification efforts into those targeting the core or kernel and those aiming for correct user-mode components. Note that this thesis draws upon a verified operating-system kernel and provides the necessary basis to pervasively verify the user-mode parts of an operating system. We summarize important advances in all four research areas.

#### 1.3.1 Verification Methods for Concurrent Programs

Numerous methods have been proposed for reasoning about concurrent programs. Most notably, the methods vary in the means of communication between different threads of execution. In practice, we distinguish communication via synchronous message passing and shared memory with atomic operations. Note, however, that in principle, both concepts are equivalent, i.e., a message passing system can be transformed into one with shared memory and vice versa [LS84].

Logics for message-passing systems are Hoare's Communicating Sequential Processes [Hoa85] and Milner's Calculus of Communicating Systems [Mil82]. These logics are based on the fact that the observable behavior of a communicating thread of execution is solely determined by the messages it sends and receives. Thus, they describe a thread by its communication pattern and without an internal state. Certainly, the internal state is theoretically irrelevant unless reflected by the communication pattern. Practically, however, programs have state and justifying the transformation of a program into its stateless communication pattern is a most complex task. Hence, we rather prefer a process description with an internal state.

There are several verification methods for reasoning about concurrent programs with shared memory and atomic operations. Owicki & Gries [OG76] have proposed a method, where the program is annotated with assumptions on the shared variables between each atomic operation. These assumptions are required to remain stable on every operation of the other threads. This dependency on the other threads, however, makes the Owicki-Gries method effectively non-modular because the inference step, i. e., the combination of proof results for two threads, becomes extremely laborious.

Ashcroft [Ash75] has suggested to formulate a huge, single state invariant to verify concurrent programs. This method disposes of the inference step, making verification completely thread-modular. Jones [Jon83], in contrast, has recommended to abstract the intermediate assumptions of the Owicki-Gries method into global rely-guarantee conditions, which substantially simplifies the inference step and hence supports thread-modular reasoning to some extent, as well. Our process model specifies sequences of atomic transitions and features a quite general global invariant, which constrains the process inputs and outputs (see the process-validity constraints in Section 4.2 as well as the validity of process inputs in Section 4.5).

Note that though thread-modular, the methods of Ashcroft and Jones are not data-modular. Recently, Vafeiadis & Parkinson [VP07] have proposed a "marriage" of the rely-guarantee method with separation logic. Originally, Reynolds & O'Hearn [Rey02, O'H04] have developed separation logic to improve data modularity when reasoning about sequential programs with pointers. The key concept are separable assumptions about disjoint chunks of the heap memory, which can be combined with a *separating-conjunction* operator according to a so-called *frame rule*. The combination of relyguarantee and separation logic yields a thread- and data-modular verification method.

Though all these verification methods differ in the basic means of communication from our process model, they share the notion of an internal state with our approach. It might be worthwhile to reuse these models with an adapted communication mechanism when reasoning about complex protocols between processes.

#### 1.3.2 Verification Frameworks for Concurrent Programs

Langenstein et al. [LNRS07a, LNRS07b] report on a verification framework for reactive systems, which is based on an interaction-centered rely-guarantee reasoning and refinement. The basic building block of their method is the concept of communicating transition systems, whose behavior is specified by finite interaction sequences. An interaction sequence is called *history*, and collects assumptions on the inputs from the environment, on the one hand, as well as guarantees on the output of a transition system, on the other hand. In order to distinguish assumptions from guarantees in the history, the transition system as well as each interaction event in the history bear an identifier. If both coincide, the event is a guarantee, otherwise an assumption. The verification framework supports the extension of a history along with an inductive reasoning—similar to our LTL-based approach (see Chapter 8). A transition system can be refined by decomposition into communicating subsystems. These subsystems then share the same history specification—each subsystem, however, regards different events in the history as its guarantees. The verification of these subsystems supports the same kind of modularity as our approach. Langenstein's verification framework, however, does not support propositions about states, which is an elementary prerequisite for the integration with a classic Hoare logic for program verification. Furthermore, the verification method relies on "a kind of simulation theorem ... established by looking at the C0 execution mechanism" [LNRS07a, Section 2.2]. Our approach, in contrast, fits into the existing verification infrastructure for sequential reasoning and facilitates the formal verification of a simulation theorem as opposed to Langenstein's educated guess.

A currently active research field is the use of separation logic for concurrent programs. Hobor et al. [HAN08] have formalized such a system in the theorem prover Coq. They have extended a sequential operational semantics for a C dialect with shared memory, spawnable threads and locks. Their approach allows for a so-called modular reasoning, i. e., arguments about sequential control and data-flow can be separated from arguments about concurrency. Their research, however, focusses around the specific problems of optimizing compilation of concurrent programs with shared memory. When they claim that properties proven in their concurrent separation logic are true for the program that

Prensa Nieto [Pre02] has formalized the Owicki/Gries method for correctness proofs of concurrent imperative programs with shared variables in the theorem prover Isabelle/HOL. Syntax, semantics and proof rules are defined in higher-order logic. Furthermore, the correctness of the proof rules is proven with respect to the semantics. Though this proof method currently lacks the support for procedures, the general approach can be applied to the Hoare logic of Schirmer [Sch05], which we use for the verification of C0 programs. Thus, Prensa Nieto's approach provides a promising technique to construct a concurrent Hoare logic, whose verification results can be formally transferred down to our low-level kernel model with the help of our foundational work.

#### 1.3.3 Kernel Verification

We are indebted to Klein for a comprehensive article [Kle09] on past and present approaches to the verification of operating-system kernels. Summarizing, Klein only presents a single, fully verified kernel: KIT, a small assembly program, that provides task isolation, device I/O, and single-word message passing. This verification project can only be referred to as groundbreaking in the area of pervasive verification. KIT is very far from any real system and the verification is based on a fairly abstract LISP execution model. Moreover, the corner-stone theorem of this work is limited to memory separation of processes.

Several past verification projects concentrated on the specification but fell short on the actual verification, e.g., UCLA Secure Unix [WKP80] or VFiasco/Robin [Tew07]. Other projects, like Embedded Device [HALM06], were successful in the verification but did not reach down to the code level. Furthermore, the Flint project [FSDG08] verified the correctness of certain low-level assembly fragments but did not yet reach full code coverage.

Since the publication of Klein's article, two verification projects announced their success: First, functional correctness has been shown [DSS09] for the tiny real-time operating system OLOS, which fully runs in system mode. The correctness theorem extends over unbounded execution traces, and the verification comprises boot-up and assembly code. Second, the L4.verified project [ $\rm HEK^+07$ ,  $\rm KEH^+09$ ] completed the world's first refinement proof for a general-purpose microkernel. Their verification target, seL4, is a third-generation microkernel of L4 provenance comparable to other high-performance L4 kernels. It comprises 8,700 lines of C and 600 lines of assembly code. Note that neither boot-up nor any assembly code have been verified; furthermore, the proof relies on a certain standard behavior of memory.<sup>3</sup>

Among ongoing verification projects is Verisoft [Pau08, HP07] and its successor, Verisoft XT.<sup>4</sup> The former has not only proven functional correctness of olos but applies the same techniques to the larger VAMOS microkernel [DDW09, Sect. 6]. Though the

<sup>&</sup>lt;sup>2</sup>Certainly, it is possible to build a distributed system, where each thread exclusively runs on its own processor. If, however, several threads share a processor, a thread switch is required.

<sup>&</sup>lt;sup>3</sup>For proof assumptions, see also http://ertos.nicta.com.au/research/14.verified/proof.pml.

<sup>&</sup>lt;sup>4</sup>More information about this project is available at http://verisoftxt.de/.

verification is not yet completed, it has reached a mature state. Note that the thesis at hand hinges on the correctness of VAMOS.

The latter project aims, amongst others, at the verification of the PikeOS kernel [Kai07, BBBB09] and the virtualization environment HYPER-V [Sam08, LS09]. Both verification targets are part of commercial products. PikeOS is available for Intel's x86, PowerPC, and ARM, and has an L4-like kernel with about 6,000 lines of code. The HYPER-V, in contrast, comprises over 50,000 lines of kernel code and is based on Intel's x86. The proofs in Verisoft XT are carried out by the VCC verification environment [CMST09, CDH $^+$ 09, DMS $^+$ 09], which uses a trusted tool chain comprising the C translator VCC, the verification condition generator Boogie, and the automated theorem prover Z3.

#### 1.3.4 Operating-System Verification

Bogan [Bog08] provides a comprehensive overview of advances in operating-system verification. Thus, we just highlight a few results. Verification has a long tradition for improving the confidence in very complex operation-systems functionality but seldom attempts full code coverage. A fruitful target for verification have been, for instance, file systems [AZKR04] and network protocols [Smi96]. Furthermore, the level of abstraction and the verified property vary widely. Bevier et al. [BCT95], for instance, have specified the interface of the Synergy file system on a very abstract level while Yang et al. [YTEM06] used model checking to systematically check implementations for specific file-system errors.

Reliable software is particularly important for security-sensitive applications. Secure system architectures are specifically developed for such applications. These architectures are usually based on a microkernel that facilitates the separation of legacy operating-system functionality from security-sensitive services, thus limiting the trusted computing base for security-sensitive applications while providing the same functionality as traditional operating systems. This approach has been taken by the Perseus security framework [PRS+01] as well as the Nizza secure-system architecture [HHF+05].

In spite of the high relevance of reliance, formal verification for these architectures has to our knowledge yet been limited to the used operating-system kernel. Both architectures are based on the Fiasco kernel, whose verification has been attempted in VFiasco/Robin (see above). Beyond that, the PERSEUS project aims at an evaluation "according to the Common Criteria at a later date". The PERSEUS framework is the basis for the Turaya security platform [LP06]. In the scope of the Verisoft XT project, some security-critical functionality of this platform has been verified but unfortunately, the results have not yet been published.

<sup>&</sup>lt;sup>5</sup>The announcement has been found on the project's homepage, http://www.perseus-os.org/content/pages/Evaluation.htm.

# 2 Fundamentals

#### Jedem Anfang wohnt ein Zauber inne.

Hermann Hesse in: "Stufen"

## Contents

| 2.1 | Implementing the Academic System: The Software Stack                             | 14 |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | Verifying Sequential Imperative Programs in Verisoft                             | 15 |

| 2.3 | The Language C0                                                                  | 16 |

| 2.4 | The VAMP Assembly Language                                                       | 18 |

| 2.5 | On a Correct Compiler                                                            | 20 |

| 2.6 | $Is abelle/Simpl-a\ Verification\ Environment\ for\ C0\ \dots \dots \dots \dots$ | 25 |

| 2.7 | Extending the Language Stack: a Roadmap to Concurrency                           | 25 |

|     |                                                                                  |    |

Our work belongs to the Verisoft project, a large-scale research project with partners from industry and academia, funded by the German government. The project adheres to the very idea of pervasive formal verification [BHMY89] of computer systems: Each abstraction layer is justified by simulation theorems that permit transferring the results to the low-level models. All theory development is mechanized in the uniform logical framework of the interactive theorem prover Isabelle/HOL, and hence, it is rigorously checked that all verification results fit together.

The general focus of the Verisoft project is threefold: First, methods and tools should be created that permit the pervasive formal verification of computer-system designs. Second, the project pursues an increase of industrial productivity and quality. Third, Verisoft aims at a prototypical implementation and verification of four specific computer systems, three of which are from the industrial sector.

More specifically, this thesis belongs to the so-called *Academic System* (as opposed to the industrial systems), which is a computer system for the secure management and exchange of signed and encrypted e-mails. This computer system is designed as part of an open network with a number of trusted computers. While the system is open to receive e-mails from arbitrary computers in the network, each trusted computer uses identical hardware and the same operating-system software. As application software, an e-mail client [BHW06, BB04], an e-mail server [LNRS07a, LNRS07b], and a cryptography server run on top of this operating system. These applications might be arbitrarily distributed over the trusted computers in the network.

This chapter continues with a short introduction of the implementation layers in the computer system. Furthermore, we summarize the general verification approach that has

been developed for sequential programs within Verisoft. A key feature of this approach is that it can cope with mixed-language implementations as they frequently occur in system-level software. More specifically, these languages are C0 [Lei08] and VAMP assembly [MP00]. We dedicate a subsection to each language. Afterwards, we sketch the compiler-correctness theorem, and introduce the verification environment *Isabelle/Simpl*. Finally, we present an overview of the actual task of the work at hand: the extension of the existing verification technology to concurrently executed processes.

# 2.1 Implementing the Academic System: The Software Stack

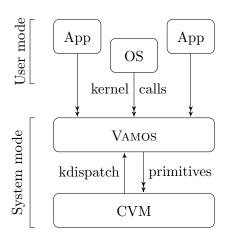

Figure 2.1 depicts the software layers of the academic system. The lowest software layer is called communicating virtual machines (CVM) [GHLP05, IT08], a generic programming framework for the implementation of operating-system kernels on the VAMP processor [MP00]. This layer encapsulates the hardware-specific low-level functionality, which employs inlined assembly. Using this framework, the microkernel VAMOS [DDB08] is implemented in C0 without extra portions of inlined assembly. Both layers interact via C0 function calls: The CVM framework calls the kdispatch function of VAMOS, and VAMOS calls CVM primitives to access low-level functionality. While these two layers run in the privileged system mode of the processor,

Figure 2.1: Software stack

processes run in the unprivileged user mode. In the figure, we labeled one process "OS" for the operating system and the others "App" abbreviating application (e.g., e-mail client or server). All processes communicate with VAMOS via so-called *kernel calls*.

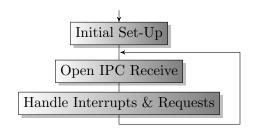

CVM's major task is process separation and memory virtualization. Hence, CVM includes a page-fault handler with a simple memory-swapping facility [ASS08]. All remaining kernel functionality is to be implemented in the hardware-independent part, the so-called abstract kernel. Technically, the CVM framework consists of the interrupt-service routine (ISR), on the one hand, and the primitives, on the other hand. The ISR is stored at a specific memory address and the processor executes the code at this address whenever an interrupt occurs. CVM's ISR saves the old processor context, establishes a suitable C0 environment and calls the C0 function kdispatch of the abstract kernel. The CVM primitives are C0 functions employing inlined assembly code to provide low-level functionality to the abstract kernel, e.g., for the manipulation of process memory or registers. The return value of kdispatch instructs CVM, which process is to resume when the kernel execution finishes.

The functionality of Vamos is accessible for processes via *kernel calls*. Technically, a kernel call is implemented using the special instruction trap: The sole effect of this instruction is an exception similar to, e.g., an arithmetic overflow. *Exceptions* are a

special class of interrupts that are generated as a direct result of the program execution (as opposed to the so-called external or device interrupts that are caused by the peripherals). Thus, the exception causes – like any interrupt – a jump to CVM's ISR, which eventually invokes VAMOS. VAMOS can examine and alter the state of the process using CVM primitives. That means, the calling process can store parameters to a kernel call in registers and memory in order to describe its specific demand from VAMOS. VAMOS, in turn, interprets the inquiry by examining the process state and in response, it alters the process state accordingly. The application binary interface (ABI) precisely defines this interaction between kernel and processes by assigning a kernel-call semantics to register values and memory contents.

The OS process constitutes the highest layer of our operating system. This process is initially started by VAMOS, equipped with more permissions than applications, and in charge to set up any additionally required devices and processes. Sebastian Bogan [Bog08] has designed, implemented, and formally specified the *Simple Operating System* (SOS) for this purpose. The SOS features an advanced rights management with different users, implements a sophisticated access control to kernel services like process creation, and provides further services like file-system and network access. Initially, the SOS sets up virtual terminals with login processes that wait for keyboard input.

# 2.2 Verifying Sequential Imperative Programs in Verisoft

A typical computer system comprises a stack of hardware and software layers. Each layer provides a different level of abstraction and potentially employs several implementation languages. CVM, for example, provides the abstraction of separate processes with virtual memory, and is implemented in a mixture of C0 and VAMP assembly. The reason for two implementation languages is apparent: C0 is a C-like high-level programming language and provides a comfortable abstraction layer for most programming tasks. Specific low-level functionality, however, like the access to special-purpose registers, cannot be expressed in C0. The resort for these tasks is the assembly language.

Verisoft takes this mixed-language architecture [AHL<sup>+</sup>09] into account by using a two-dimensional verification approach: The first axis, called *system stack*, traces the different implementation layers. The behavior of each implementation layer is specified by a corresponding computational model. The second axis follows the language semantics and, hence, we name it *language stack*.

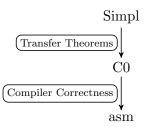

While the full language stack reaches down to the instruction-set architecture (ISA), we are only concerned with the languages depicted in Figure 2.2. At the lower end, we find VAMP assembly (denoted "asm" for short), above it C0, and at the top, the language *Simpl*. The latter is a generic programming model for sequential imperative programming languages. This generic model provides the basis for the versatile verification environment

Figure 2.2: Language stack

Isabelle/Simpl.

The major challenge of a pervasive verification effort is the integration of the various verification results into a coherent theory. Thus, an important result of the Verisoft project is a compiler-correctness theorem [LP08] that links C0 and the VAMP assembly language. Furthermore, transfer theorems [Sch06] establish an embedding of C0 into the generic programming model Simpl and facilitate the transfer of properties proven in Simpl down to the C0 semantics.

In the following sections, we present the languages C0 and VAMP assembly in detail, we sketch the compiler-correctness theorem, and introduce Isabelle/Simpl.

# 2.3 The Language C0

ANSI C [Ame99] has a complex and highly underspecified semantics. Low-level programs such as device drivers, however, explicitly use properties of a particular compiler on a target hardware, like register bindings or the internal representation of data types. They can therefore not be verified based only on the vague ANSI C semantics. In Verisoft, we constrained ourselves to the C-like imperative language C0 [Lei08], which has sufficient features to implement low-level software but is interpreted by a more concrete semantics. C0's most important limitations compared to ANSI C are:

- expressions must be free of side effects and do not contain function calls,

- there are no implicit type conversions, especially not from arrays to pointers,

- pointers are strongly typed and must not point to functions or stack variables (i. e., there are neither void pointers nor pointer arithmetic), and

- low-level data types (like unions and bit fields) and control-flow statements (like switch and goto) are not supported.

**Syntax.** C0 supports fundamental types, aggregate types and pointers. The first category comprises Booleans, 8-bit-wide characters, as well as signed and unsigned 32-bit integers. Aggregate types in C0 are arrays and structures. Pointers may point to all types of data but not to functions.

LIT v literal values v VARACC vn access of variable vn

Arrace  $e_a$  e indexing array  $e_a$  with index e

Structacc e cn selecting component cn of structure e

BINOP  $bop \ e_1 \ e_2$  binary operation LAZYBINOP  $lbop \ e_1 \ e_2$  lazy binary operation UNOP  $uop \ e$  unary operation

Address of left-expression  $e_1$

Deref e dereferencing e

Table 2.1: C0 expressions e

The statements in C0 permit assignments, dynamic memory allocation, sequential composition, conditional and repeated execution, inlined assembly, function calls, and returns from functions.

In Isabelle/HOL, C0 expressions e and statements s are represented as data types. Their constructors are listed in the Tables 2.1 and 2.2. Only a few of them are of special interest in this thesis:

- Variable accesses VARACC vn are used to read or write the value of variables vn.

- The dereferencing operator Deref e transforms the pointer expression e into a left expression.

- Furthermore, the function-call statement SCALL vn fn es sid calls a C0 function named fn with the argument list es. The returned result is stored to a (global or stack) variable called vn. The statement identifier sid is used in the compiler correctness theorem.

- Finally, the empty statement Skip does nothing.

**Small-Step Semantics.** A C0 program is formally defined by a symbol table gst of global variables, a type-name table tt, and a function table ft. A symbol table is a list of pairs of variable names and the corresponding data types. The type-name table lists pairs of type names and the corresponding data types. And finally, the function table

SKIP the empty statement COMP  $s_1$   $s_2$  sequential composition

Ass  $e_l e sid$  assignment of expression e to left-expression  $e_l$

PALLOC  $e_l$  to sid allocation of an object of type name to and assignment to  $e_l$  SCALL vn fn es sid call of function fn with arguments es and result variable vn

RETURN  $e \ sid$  return from a function IFTE  $e \ s_1 \ s_2 \ sid$  if-then-else with condition e

LOOP  $e \ s \ sid$  while loop with condition e and body s ASM  $ls \ sid$  inlined assembly with instruction list ls

Table 2.2: C0 statements s

lists pairs of function names and the corresponding functions definitions.

A function definition is represented by a record fd consisting of (a) a statement fd.body that represents the function body, (b) a symbol table fd.params of the function's parameters, (c) the function's return type fd.rettype, and (d) a symbol table fd.stack\_vars of the stack variables.

In contrast to the static program definition, the program state evolves during the execution of a C0 program. A program state  $s_{C0}$  comprises:

- the statement  $s_{C0}$ .prog of the program that remains to be executed, and

- the current state  $s_{C0}$ .mem of the program variables and the heap objects.

The memory model of the C0 small-step semantics is quite complex. As C0 is perfectly type-safe, the memory is typed. Moreover, the model separates the global variables, the variables in the various stack frames, and the heap objects. Each of these memory parts has its own symbol table. The symbol table of the global variables can be extracted from a memory state with the function gm\_st.

For the work at hand, the memory internals are not relevant. We just use an evaluation function  $mem\_read$  for the look-up, and an update function  $mem\_write$  for the manipulation of memory objects. The function  $mem\_read$  tt m e evaluates the expression e in the memory state m based on the type-name table tt. Similarly, the function  $mem\_write$  tt m e<sub>l</sub> v updates the object denoted by the left-expression e<sub>l</sub> in memory m by the new value v.

Note, however, that the expression evaluation and consequently the memory update may fail, e.g., because of an uninitialized variable or a dereferenced null pointer. Thus, the functions are partial. Furthermore, we want to update certain expressions at the same time, i.e., all left expressions are evaluated before the memory is updated. The corresponding update function is called  $mem\_writes$  tt m evs and parametrized over a type-name table tt, a memory state m, and a list evs of pairs of an expression and the corresponding new value.

The transition relation  $\delta_{C0}$  of this semantics is deterministic, i.e., a partial function.

# 2.4 The VAMP Assembly Language

We regard the assembly language developed for the VAMP architecture. The VAMP architecture is based on the DLX architecture [HP96] and was initially presented by Mueller & Paul [MP00]. An implementation of the VAMP has been formally verified in 2003 [BJK<sup>+</sup>03, BJK<sup>+</sup>06]. Since then, the VAMP has been extended with address translation and support for I/O devices [DHP05, AHK<sup>+</sup>07, TS08].

Three models [AHL<sup>+</sup>09, TS08] are related to this processor. From the most concrete to the most abstract one, these are: the gate-level implementation, the instruction set architecture (ISA) specification, and the assembly-language specification. Simulation proofs relate the adjacent models such that properties shown at the assembly level can finally be transferred down to the gate-level.

The VAMP assembly language is the target language of Leinenbach & Petrova's verified C0 compiler. At the same time, its specification is intended to be a convenient layer

for the implementation and the verification of hardware-dependent programs. Thus, the language specification abstracts from certain aspects of the lower layers, which are irrelevant for these purposes.

Most notably, the VAMP assembly machine employs a linear memory model with a conventional memory semantics, i.e., it abstracts from memory-mapped device I/O and the paging mechanism of the processor. This abstraction is useful for assembly code executed in the untranslated system mode as well as in the user mode with a transparent handling of address translation and page faults.

Furthermore, interrupts are not modeled in the VAMP assembly machine. This abstraction extends the very idea of the previous one: We implicitly assume that interrupts can either be handled transparently to the running program (like device interrupts and page faults) or are programming errors (like misaligned memory accesses and undecodable instructions), which should not occur at all. The simulation theorem between the ISA and the assembly-language specification simply holds unless exceptions are generated during the execution of instructions. As part of compiler correctness, it has been shown that a compiled C0 program does not generate exceptions if there are sufficient resources. Note that this separation of matters is equally welcome when verifying inlined assembly code. Besides, the abstraction from interrupts is a reversible convenience – we re-introduce an exception semantics tailored for assembly processes in Section 4.3.

Finally, the bit vectors from the ISA specification are superseded in the VAMP assembly machine (a) by integers for data, (b) by naturals for addresses, and (c) by a tailored abstract data type for instructions. This representation is optimized for assembly programs working with integers; arguments regarding naturals and bit-vector operations require conversions. The two functions to\_nat32 and to\_int32, for example, convert between 32-bit integers and naturals.

**Formal Semantics.** An assembly state  $s_{\mathsf{asm}}$  is a record with the following components:

- two program counters  $s_{\mathsf{asm}}.\mathsf{dpc}$  and  $s_{\mathsf{asm}}.\mathsf{pcp}$  for implementing the delayed-branch mechanism, which hold the addresses of the current and next instruction,

- the general-purpose and special-purpose register files  $s_{asm}$ .gprs and  $s_{asm}$ .sprs, which are both lists of data, and

- the word-addressable main memory  $s_{\mathsf{asm}}.\mathsf{mm}$ , mapping addresses to data.

Note that some well-formedness constraints are not enforced by the record type. We call an assembly state *valid* iff the program counters are 32-bit naturals, the register files contain 32 registers, and all registers and memory cells are 32-bit integers. We subsume these well-formedness constraints in predicate valid\_asm:

Instructions are represented by an abstract data type and converted on instruction fetch from memory cells using the conversion function to\_instr. Thus, the function

current\_instr  $s_{asm} \equiv to_{instr} (s_{asm}.mm (s_{asm}.dpc div 4))$  denotes the instruction that is executed next in the assembly machine.

The assembly semantics can equally be employed in user- and system mode. The mode is determined by the special-purpose register MODE:

```

is_system_mode s_{\mathsf{asm}} \equiv s_{\mathsf{asm}}.\mathsf{sprs} \; ! \; \mathsf{MODE} = 0

```

In the course of this thesis, we do not regard the system mode. In user mode, it is illegal to access most of the special-purpose registers and solely the page-table length register PTL is relevant for us: It determines the size of the main memory in pages of 1024 words. For technical reasons, the register value is a signed integer with an offset of -1, i. e., -1 denotes a size of 0 pages. We encapsulate this fact in the function  $mm\_size$  and define:

```

mm_size s_{asm} \equiv to_nat32 (s_{asm}.sprs ! PTL + 1)

```

A memory access beyond the specified size generates an exception in the real system – an illegal case in the assembly semantics.

The VAMP-assembly transition function  $\delta_{\mathsf{asm}}$  computes for a given assembly state  $s_{\mathsf{asm}}$  the next state  $s'_{\mathsf{asm}}$ . In illegal cases, the transition function gets stuck. Otherwise, the transition is specified by a simple case distinction on current\_instr  $s_{\mathsf{asm}}$ . We use the notation  $\delta_{\mathsf{asm}}^n s_{\mathsf{asm}}$  to denote the result of executing n steps of the assembly machine starting in state  $s_{\mathsf{asm}}$ .

# 2.5 On a Correct Compiler

Most software in Verisoft has been implemented and verified at the C0 level. The C0 programs are translated to assembly code in order to be executed on the target machine. Leinenbach & Petrova have developed and verified a non-optimizing compiler from C0 to VAMP assembly [LPP05, Pet07, LP08]. Below, we summarize their results.

Compiler correctness is formulated as a simulation theorem. In essence, the compiler-simulation theorem states that every step i of the source program executed on the C0 small-step semantics simulates a certain number  $s_i$  of steps of the VAMP assembly machine executing the compiled code. For the property transfer from the C0 to the VAMP assembly layer, the simulation theorem has to meet special requirements. In particular, the simulation theorem is formulated based on the small-step semantics, which permits the reasoning about non-terminating programs and interleaved executions. Additionally, the compiler-correctness proof considers resource restrictions at the assembly layer and allows to discharge them at the C0 layer.

At first, we present the simulation relation:

**Definition 2.1** (C0 Simulation Relation). The simulation relation consistent states that a VAMP assembly state  $s_{asm}$  encodes a C0 state  $s_{C0}$ . The relation is parametrized over

<sup>&</sup>lt;sup>1</sup>Technically, we avoid extra case distinctions for the detection of all possible invalid cases but sort out those cases before we apply the transition function. Though the transition function might sometimes not get stuck, it is simply meaningless in illegal cases.

an allocation function alloc, which maps all variables and heap objects in the C0 state to their allocated address in the main memory of the assembly state. For a C0 program with the type-name table tt and the function table ft, the relation consistent tt ft  $s_{\text{C0}}$  alloc  $s_{\text{asm}}$  correlates

- the currently remaining program s<sub>CO</sub>.prog to the value of the program counters in the assembly state s<sub>asm</sub> (called control consistency),

- the code of the C0 program, which is computed from the type-name table tt, the function table ft, and the global symbol table  $gtarrow (gm_st s_{C0}.mem)$ , to the corresponding memory region in  $s_{asm}$  (code consistency), and

- the values of variables and heap objects in the C0 state  $s_{C0}$  to their corresponding memory values in  $s_{asm}$  (data consistency).

The formal specification of the simulation relation is a conjunction of three predicates for control, code, and data consistency. We present only the code-consistency predicate:

with the compiled program codegen\_program tt ft (gm\_st  $s_{C0}$ .mem), the predicate decodable determining whether an integer can be interpreted as an instruction, and the conversion function to\_instr realizing this interpretation. The constant program\_base is a compiler parameter permitting a variable displacement of the program code in the memory. This displacement is used in the kernel implementation to provide space for some low-level functionality of CVM. For user programs, the displacement is not needed and hence set to 0.

Certainly, we need an initial assembly state for a C0 program. For the support of various use cases, the compiler-correctness theorem does not construct a particular initial state but rather formulates the necessary requirements on an assembly state to serve as an initial state for a specific C0 program.

**Definition 2.2** (Initial Assembly States for a C0 Program). For a given C0 program (tt, ft, gst), each corresponding initial assembly state  $s_{\mathsf{asm}}$  is well-formed, its program counters point to the beginning of the code, the assembly state is code consistent with the corresponding initial C0 state (denoted by init\_C0 ft gst), and the memory containing the global variables is zero-initialized.

The formal requirements are collected in the predicate is\_initial\_asm tt ft gst s<sub>asm</sub>:

<sup>&</sup>lt;sup>2</sup>Note that—though constant during the program execution—the symbol table of the global memory is extracted from the current C0 state's memory component  $s_{C0}$ .mem.

```

is_initial_asm tt ft gst s_{asm} \equiv valid_asm s_{asm} \wedge s_{asm}.dpc = 4 \cdot program_base \wedge s_{asm}.pcp = s_{asm}.dpc + 4 \wedge code_consistent <math>tt ft (init_C0 ft gst) s_{asm} \wedge (\forall i \in gm\_range \ tt \ ft \ gst. \ s_{asm}.mm \ i = 0)

```

Recall that certain executions in the assembly semantics are not legal, e.g., if an instruction accesses memory beyond the available size. Compiler correctness is even more demanding with respect to the accessible memory: It distinguishes read-only code regions in the memory from writable data regions in order to prevent self-modifying code. The non-optimizing compiler furthermore maintains that the assembly machine is not in a delay slot between two compiled C0 statements<sup>3</sup>, i.e., we require  $s_{asm}.pcp = s_{asm}.dpc + 4$ . Finally, we assume a well-formed assembly state, i.e., valid\_asm  $s_{asm}$  (see page 19).

A few auxiliary predicates help to formally specify whether a compiled C0 program is successfully executed on the VAMP assembly level: The predicate mem\_write\_inside\_range holds iff the current instruction writes into a specified memory range, the predicate is\_exception holds iff an exception is generated during the execution of the current instruction, and finally, inside\_range (l, h) i is defined as  $l \leq i \land i < h$ .

**Definition 2.3** (Successful Execution of Assembly Code). We call a computation of the VAMP assembly machine from a state  $s_{\mathsf{asm}}$  in n steps to  $s'_{\mathsf{asm}}$  a successful execution with respect to a code range crange and an address range arange iff

- the memory contents in *crange* has not been overwritten,

- all instructions are only fetched from *crange*,

- all accessed memory addresses are in *arange* (encapsulated in mem\_access\_inside\_range),

- no exceptions are generated, and

- all executed instructions are legal (denoted by is\_legal\_instr).

Formally, the successful execution of assembly code is defined as

```

\begin{array}{l} (crange,\,arange) \vdash_{\mathsf{asm}} s_{\mathsf{asm}} \to^n s'_{\mathsf{asm}} \equiv \\ \delta^n_{\mathsf{asm}} \ s_{\mathsf{asm}} = s'_{\mathsf{asm}} \wedge \mathsf{valid\_asm} \ s'_{\mathsf{asm}} \wedge s'_{\mathsf{asm}}.\mathsf{pcp} = s'_{\mathsf{asm}}.\mathsf{dpc} + 4 \wedge \\ (\forall m < n. \ \neg \ \mathsf{mem\_write\_inside\_range} \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}).\mathsf{dpc} \wedge \\ \mathsf{inside\_range} \ crange \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}).\mathsf{dpc} \wedge \\ \mathsf{mem\_access\_inside\_range} \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}) \ arange \wedge \\ \mathsf{\neg} \ \mathsf{is\_exception} \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}) \wedge \\ \mathsf{is\_legal\_instr} \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}) \ (\mathsf{current\_instr} \ (\delta^m_{\mathsf{asm}} \ s_{\mathsf{asm}}))) \\ \end{array}

```

Note that the successful execution of assembly code depends on two implicit assumptions: The initial assembly configuration  $s_{asm}$  needs to be well-formed, and the program counters must not start in a delay slot. These two conditions are invariant under a successful execution. For a particular C0 program (tt, ft, gst), the corresponding code