## The Correctness of a Distributed Real-Time System

# Dissertation

Zum Erlangen des Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

# Steffen Knapp

sknapp@wjpserver.cs.uni-sb.de

Saarbrücken, Juli 2008

| Tag des Kolloquiums:                                                                  | 07.07.2008                                                                       |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Dekan:                                                                                | Prof. Dr. Joachim Weickert                                                       |

| Vorsitzender des Prüfungsausschusses:<br>1. Berichterstatter:<br>2. Berichterstatter: | Prof. Dr. Reinhard Wilhelm<br>Prof. Dr. Wolfgang Paul<br>Prof. Dr. Wolfgang Kunz |

| akademischer Mitarbeiter:                                                             | Dr. Mark Hillebrand                                                              |

Hiermit versichere ich an Eides statt, dass ich die vorliegende Arbeit selbstständig und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in einem Verfahren zur Erlangung eines akademischen Grades vorgelegt.

Saarbrücken, Juli 2008

Steffen Knapp

#### Zitat:

"Man kann niemanden überholen, wenn man in seine Fußstapfen tritt." Francois Truffaut

#### Danke

An dieser Stelle möchte ich mich bei Allen bedanken, die zum Gelingen dieser Arbeit beigetragen haben:

Zuerst Herrn Professor Dr. Wolfgang J. Paul für die Vergabe des spannenden und herausfordernden Themas und die wissenschaftliche Unterstützung meiner Promotion.

Außerdem danke ich meiner Freundin Kerstin Hahn für die ständige Ermutigung und Ermunterung insbesondere in der heißen Schlussphase: Ohne Egon und Eulilie sähe die Welt ganz anders aus!

Mein Dank gilt auch meinen (ehemaligen und derzeitigen) Arbeitskollegen am Lehrstuhl von Herrn Paul. Stellvertretend seien hier Peter Böhm, Mark Hillebrand und Dirk Leinenbach genannt. Insbesondere möchte ich mich bei Eyad Alkassar bedanken, der es nun schon viele Jahre mit mir in einem Zimmer ausgehalten hat :-)

Ich danke meinen Freunden Daniel Schmitt, Verena Kremer, Benedikt Grundmann und Ulrich Seyfarth für die Unterstützung sowie die nötige Ablenkung: "We rocked the Garage!"

Und – last but not least – danke ich meiner Familie für die volle Unterstützung in allen Lebenslagen.

Die vorliegende Arbeit wurde teilweise von der International Max Planck Research School for Computer Science (IMPRS) sowie im Rahmen des Projektes Verisoft vom Bundesministerium für Bildung und Forschung (BMBF) unter dem Förderkennzeichen 01 IS C38 gefördert. Die Verantwortung für den Inhalt dieser Arbeit liegt bei mir.

#### Abstract

In this thesis we review and extend the pervasive correctness proof for an asynchronous distributed real-time system published in [KP07a]. We take a two-step approach: first, we argue about a single electronic control unit (ECU) consisting of a processor (running the OSEKtime-like operating system OLOS) and a FlexRay-like interface called automotive bus controller (ABC). We extend [KP07a] among others by a local OLOS model [Kna08] and go into details regarding the handling of interrupts and the treatment of devices.

Second, we connect several ECUs via the ABCs and reason about the complete distributed system, see also [KP07b]. Note that the formalization of the scheduling correctness is reported in [ABK08b]. Through several abstraction layers we prove the correctness of the distributed system with respect to a new lock-step model COA that completely abstracts from the ABCs. By establishing the DISTR model [Kna08] it becomes possible to literally reuse the arguments from the first part of this thesis and therefore to simplify the analysis of the complete distributed system. To illustrate the applicability of DISTR, we have formally proven the top-level correctness theorem in the theorem prover Isabelle/HOL.

Throughout the thesis we tie together theorems regarding: processor, ABC, compiler, micro kernel, operating system, and the worst case execution time analysis of applications and systems software.

#### Zusammenfassung

In dieser Arbeit betrachten und erweitern wir den durchgängigen Korrektheitsbeweis für ein asynchrones verteiltes Echtzeitsystem aus [KP07a]. Wir gehen in zwei Schritten vor: Zuerst betrachten wir eine einzelne elektronische Kontrolleinheit (ECU) bestehend aus einem Prozessor (welcher das OSEKtime ähnliche Betriebsystem OLOS ausführt) und einem FlexRay ähnlichem Interface, auch automobiler Bus Controller (ABC) genannt. Wir erweitern [KP07a] unter anderem um ein lokales OLOS Model [Kna08] und detaillieren die Behandlung von Interrupts sowie den Umgang mit Geräten.

Im zweiten Schritt verbinden wir mehrere ECUs durch die ABCs und argumentieren über das gesamte System, siehe auch [KP07b]. Über die Formalisierung der Scheduler Korrektheit wird in [ABK08b] berichtet. Über mehrere Abstraktionsebenen beweisen wir die Korrektheit des verteilten Systems bezüglich eines neuen gleichgetakteten Modells COA in dem vollständig von den ABCs abstrahiert wird. Durch die Einführung des DISTR Models [Kna08] ist es möglich die Argumente aus dem ersten Teil dieser Arbeit in der Analyse des gesamten verteilten Systems wörtlich wieder zu verwenden. Um die Anwendbarkeit von DISTR zu verdeutlichen haben wir formal die oberste Korrektheits-Aussage im Theorembeweiser Isabelle/HOL beweisen.

Im Zuge dieser Arbeit verbinden wir Theoreme bezüglich: Prozessor, ABC, Compiler, Mikrokern, Betriebsystem und der Worst-Case Laufzeit Analyse von Applikationen und System Software.

#### **Extended Abstract**

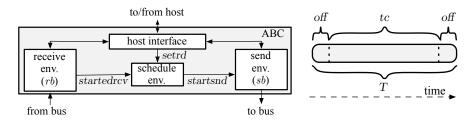

In this thesis we consider a distributed system consisting of several electronic control units (ECUs) based on [KP07a]. An ECU consists of a DLX processor called VAMP [BJK<sup>+</sup>03, DHP05, BJK<sup>+</sup>05], and a FlexRay-like interface [Fle08] called automotive bus controller (ABC). System software is a C0 compiler [LP08] and the OSEKtime-like [OSE08b] operating system OLOS [Kna05, IdRK05, Kna08]. The latter is realized using the generic micro-kernel CVM [GHLP05, KP07a, IdRT08]. Applications are compiled C0 programs that are communicating via a FTCom-like [OSE08a] message buffer of the operating system. Drivers for the ABC are part of OLOS.

Several ECUs are connected by a bus via the ABCs. Communication is done in a time-triggered fashion similar to the static segment of the FlexRay protocol [Fle06]. Time is divided into rounds each consisting of a fixed number of slots. In each slot one ECU is allowed to broadcast one message according to a fixed slot-based schedule.

We clearly split the argumentation about this distributed system in two separate issues: the inter-ECU communication and the local computations on the ECUs. We present a verification approach that separates the argumentation for both issues and combines the results later on in an overall correctness statement.

In the first part of this thesis we argue about a single ECU only. We outline the specification of the DLX instruction set [HP96, MP00] including the handling of interrupts. Using the VAMP [BJK $^+$ 05] as an example, we explain how to verify hardware designs of complex processors with internal and external interrupts, as reported in [Bey05, Dal06, Tve08]. The resulting correctness proofs are based on the scheduling functions introduced in [SH98, KMP00, MP00].

After this we introduce an I/O device theory. We show how to specify an I/O device and explain how to integrate it into the processor [HIP05, AHK<sup>+</sup>07]. Furthermore, we extend the processor correctness theorem to deal with a device.

An extension of the VAMP processor by memory management units (MMUs) gives the hardware support for multi-processing operating system kernels and for virtual machine simulation [Hil05, Dal06].

Then we survey a correctness proof for a compiler from the high-level C-like programming language C0 to the DLX instruction set, as reported in [Pet07, LP08, Lei08]. We show how to extend the C0 language by permitting portions of inline assembly code. The resulting language is called  $CO_A$ .

We describe the generic operating system kernel called CVM [GHLP05, KP07a, IdRT08]. Seen from the programmers perspective, it consists of a so-called abstract kernel and a set of user processes. The user processes are virtual DLX machines. The abstract kernel is a C0 program that can execute special statements called CVM primitives. These primitives allow the transport of data between kernel and user processes. The CVM correctness proof uses the virtual machine simulation, compiler correctness, and the arguments regarding inline assembly code.

Next we specify the OSEKtime-like operating system OLOS [Kna05, IdRK05, Kna08]. The user processes running under OLOS are C0 programs. These programs can communicate via FTCom-like message buffers with user processes running on the same *or* on remote ECUs. We have implemented an initial version of OLOS by instan-

tiating the abstract CVM kernel. The correctness of the implementation is proven on paper with respect to the OLOS specification.

The main extensions done in the first part (compared to [KP07a]) are the local OLOS specification and a more detailed argumentation regarding the treatment of devices and the handling of interrupts throughout the model stack.

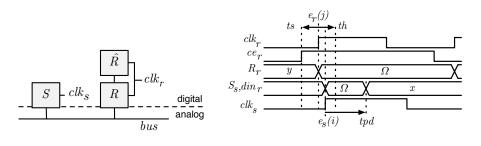

In the second part of this thesis we argue about the complete distributed system. Since the ECUs are running with local oscillators of almost but not exactly equal clock frequency, we cannot guarantee that set-up and hold times of registers are respected when data is being transmitted between ECUs. In such situations serial interfaces are used for data transmission. We review a correctness proof for a serial interface from [BBG<sup>+</sup>05].

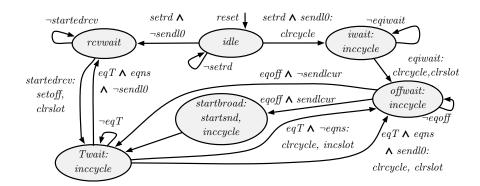

Next we introduce our automotive bus controller (ABC) implementation which has been inspired by [Pau05]. It consists among other things of a message buffers, a serial interface, and a local timer. We show how to prove the correctness of the ABC [BBG<sup>+</sup>05, KP07b]. Note that we have already reported on the formalization of the scheduling correctness in [ABK08b]. Then we connect our ABC implementation to the processor implementation, using techniques from [HIP05, AHK<sup>+</sup>07].

The desired communication behavior is specified in a parameterized model called DISTR [Kna08]. This model provides the basis for the separation of the arguments for the inter-ECU communication and the local computations.

We show how to prove the correctness of the inter-ECU communication with respect to the DISTR model. Note that this proof combines arguments regarding asynchronous bit-level transmission with arguments regarding the clock synchronization mechanism at the gate level.

By instantiating the DISTR model with each model of the local stack established in Part I we obtain a distributed version of this stack. When proving correctness, we run into a problem regarding the timer interrupts generated by the ABC: timer interrupts occur in fixed time intervals. At the gate level it is trivial to determine in which cycle such an interrupt is generated. But when we proceed up the model stack we have to argue about the corresponding instruction that gets interrupted on the instruction set architecture (ISA) level. This can inherently not be done at the ISA level alone. The execution time of an instruction depends on cache hits and cache misses, but the memory hierarchy is not visible at the ISA level. Only if we are allowed to look inside the hardware at the gate level, the occurrence of timer interrupts is well-defined.

To solve this problem we first prove the correctness of our ABC implementation with respect to the DISTR model being instantiated with a processor implementation. Then we combine classical program correctness proofs at the ISA level, worst case execution time (WCET) analysis at the gate level, and processor correctness proofs into a pervasive correctness proof for our real-time system from the gate level to the ISA level.

Once we have reached the ISA level we can reuse the local simulation theorems introduced in the first part of this thesis to prove the correctness of the corresponding upper layers.

Finally, we define an automata-theoretic lock-step model called communicating OLOS automata (COA). This model completely abstracts from the devices; commu-

nication is done via the local message-buffers of the operating system directly. In the end, we revise our formal correctness proof of DISTR instantiated with our local OLOS model with respect to the COA model, as reported in [Kna08]. Note that this proof has been formalized in Isabelle/HOL [NPW02].

So, using DISTR, we extended [KP07a] by a more detailed analysis of the interrupt sampling, of all distributed models themselves, and of the propagation of the WCET throughout the distributed model stack resulting in the easy to use COA model.

By that we have established a distributed model stack in which all layers are linked by simulation theorems. To do so, we tie together theorems regarding processor correctness [Bey05, Dal06, Tve08], I/O device integration [HIP05, AHK<sup>+</sup>07], scheduling correctness [KP07b, ABK08b], message transmission correctness [BBG<sup>+</sup>05, KP07b], compiler correctness [Pet07, Lei08], micro kernel correctness [GHLP05, IdRT08], operating system correctness [Kna05, IdRK05, Kna08], and the worst case execution time analysis [KP07b] of applications and systems software.

## Contents

| 1 | Introduction                                                  | 18   |

|---|---------------------------------------------------------------|------|

| 2 | Related Work                                                  | 20   |

| I | Single Electronic Control Unit (ECU)                          | 22   |

| 3 | Notation                                                      | 22   |

| 4 | Instruction Set Architecture (ISA)                            | 23   |

|   | 4.1 ISA Configuration                                         | . 23 |

|   | 4.2 Instruction Decoding                                      | . 24 |

|   | 4.3 ISA Transition Function                                   | . 25 |

|   | 4.4 Extended ISA Configuration                                |      |

|   | 4.5 Dealing with Interrupts                                   | . 26 |

|   | 4.5.1 Trap Instructions                                       |      |

|   | 4.6 ISA Transition Function with Interrupts                   |      |

| 5 | Processor Hardware (H)                                        | 28   |

|   | 5.1 Hardware Configuration                                    | . 28 |

|   | 5.2 Hardware Transition Function                              | . 29 |

|   | 5.3 Scheduling Functions                                      | . 29 |

|   | 5.4 Processor Correctness Theorem                             | . 31 |

|   | 5.4.1 Synchronization Conditions                              | . 32 |

|   | 5.5 Dealing with Interrupts                                   | . 33 |

| 6 | Devices (D)                                                   | 33   |

|   | 6.1 Device Configuration                                      | . 34 |

|   | 6.2 Integration of a Device in General                        | . 34 |

|   | 6.3 Integration of a Device into the Processor Implementation | . 35 |

|   | 6.4 Implementation Semantics                                  | . 36 |

|   | 6.5 Implementation Semantics for a Stable Device              | . 37 |

|   | 6.6 Integration of a Stable Device into the ISA               |      |

|   | 6.7 Processor Correctness Theorem with Devices                | . 39 |

| 7 | Memory Management (MM)                                        | 40   |

|   | 7.1 Physical Machine Configuration                            |      |

|   | 7.2 Address Translation, Physical and Virtual Machines        | . 41 |

|   | 7.3 Physical Machine Transition Function                      | . 42 |

|   | 7.4 Virtual Memory Correctness Theorem                        | . 42 |

| 8  | The   | Programming Language C0                        | 43 |

|----|-------|------------------------------------------------|----|

|    | 8.1   | C0 Types Expressions and Statements            | 43 |

|    | 8.2   | C0 Machine Configuration                       | 44 |

|    |       | 8.2.1 C0 Variables                             | 44 |

|    | 8.3   | C0 Machine Transition Function                 | 45 |

|    | 8.4   | Compiler Correctness Theorem                   | 46 |

| 9  | Inlin | e Assembly Code (C0 <sub>A</sub> )             | 47 |

| 10 | Com   | municating Virtual Machines (CVM)              | 49 |

|    | 10.1  | CVM Configuration                              | 49 |

|    | 10.2  | CVM Transition Function                        | 50 |

|    |       | 10.2.1 User Transition                         | 50 |

|    |       | 10.2.2 Kernel Transition                       | 50 |

|    | 10.3  | Binary Kernel Interface                        | 52 |

|    |       | 10.3.1 Binary Kernel Interface Implementation  | 53 |

|    | 10.4  | CVM Implementation                             | 54 |

|    | 10.5  | Concrete Kernel Simulation Relation            | 54 |

|    |       | 10.5.1 Concrete Kernel Data Structures         | 55 |

|    |       | 10.5.2 Entering System Mode after an Interrupt | 55 |

|    |       | 10.5.3 Leaving System Mode                     | 56 |

|    |       | 10.5.4 Process Virtualization                  | 56 |

|    |       | 10.5.5 Implementation of the CVM Primitives    | 56 |

|    | 10.6  | CVM Correctness Theorem                        | 57 |

| 11 | Auto  | omotive Bus Controller (ABC)                   | 58 |

| 11 |       | Stable ABC Specification Configuration         | 58 |

|    | 11.1  |                                                | 20 |

| 12 |       | Ktime Like Operating System (OLOS)             | 59 |

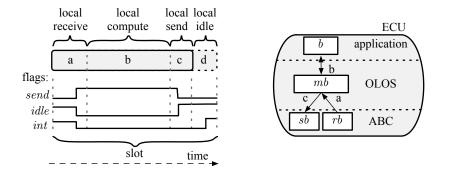

|    | 12.1  | Message Buffers, Applications and Schedules    | 59 |

|    | 12.2  | OLOS Configuration                             | 60 |

|    |       | Local Configurations (LC) and Transitions      | 61 |

|    | 12.4  | OLOS Transition Function                       | 62 |

|    |       | 12.4.1 Local OLOS Receive Phase (a)            | 62 |

|    |       | 12.4.2 Local OLOS Compute Phase (b)            | 63 |

|    |       | 12.4.3 Local OLOS Send Phase (c)               | 63 |

|    |       | 12.4.4 Local OLOS Idle Phase (d)               | 63 |

|    |       | OLOS Implementation Data Structures            | 64 |

|    |       | OLOS Simulation Relation                       | 64 |

|    | 12.7  | OLOS Correctness Theorem for One Slot          | 65 |

|    |       |                                                |    |

## **II** Distributed ECUs

| 13 ABC Implementation                            | 68 |

|--------------------------------------------------|----|

| 13.1 Host Interface                              | 69 |

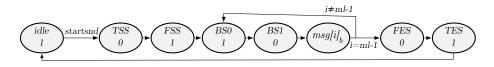

| 13.2 Send Environment                            | 70 |

| 13.3 Receive Environment                         | 70 |

| 13.4 Schedule Environment                        | 71 |

| 13.5 Hardware Construction                       | 72 |

| 14 ABC Verification                              | 73 |

| 14.1 Clocks                                      | 74 |

| 14.2 Hardware Model with Continuous Time         | 74 |

| 14.3 Continuous Time Lemmata for the Bus         | 75 |

| 14.4 Message Broadcast Correctness               | 76 |

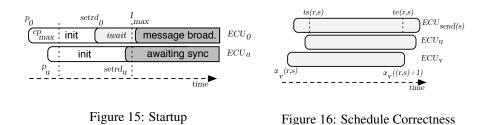

| 14.5 Startup                                     | 78 |

| 14.6 Scheduling Correctness                      | 78 |

| 14.7 Extensions Towards Fault-Tolerance          | 81 |

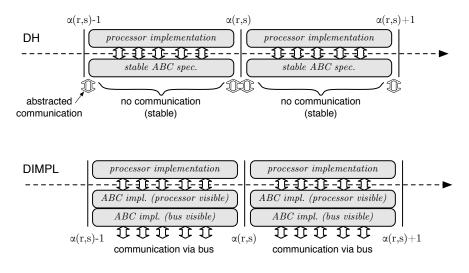

| 15 Distributed Implementation (DIMPL)            | 81 |

| 15.1 DIMPL Properties                            | 82 |

| 16 Distributed Framework (DISTR)                 | 83 |

| 16.1 DISTR Configuration                         | 83 |

| 16.2 DISTR Transition Function                   | 83 |

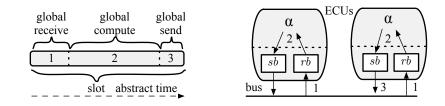

| 16.2.1 Global DISTR Receive Phase (1)            | 84 |

| 16.2.2 Global DISTR Compute Phase (2)            | 84 |

| 16.2.3 Global DISTR Send Phase (3)               | 84 |

| 16.2.4 DISTR Notation                            | 85 |

| 17 Distributed Hardware (DH)                     | 85 |

| 17.1 DH Configuration                            | 87 |

| 17.2 DH Transition Function                      | 87 |

| 17.3 DIMPL Correctness                           | 87 |

| 18 Distributed ISA (DISA)                        | 90 |

| 18.1 DISA Configuration                          | 90 |

| 18.2 DISA Transition Function                    | 90 |

| 18.3 DISA Correctness                            | 91 |

| 18.3.1 DISA Interrupt Sampling                   | 92 |

| 18.3.2 Worst Case Execution Time                 | 94 |

| 18.4 Pervasive Program and Processor Correctness | 96 |

| 19 Distributed CVM (DCVM)                        | 97 |

| 19.1 DCVM Configuration                          | 97 |

| 19.2 DCVM Transition Function                    | 97 |

| 19.3 DCVM Correctness                            | 97 |

| 19.4 Pervasive DCVM Correctness                  | 99 |

| 20 | Distributed OLOS (DOLOS)             | 100 |

|----|--------------------------------------|-----|

|    | 20.1 DOLOS Configuration             | 100 |

|    | 20.2 DOLOS Transition Function       | 100 |

|    | 20.3 DOLOS Correctness               | 102 |

|    | 20.4 Pervasive DOLOS Correctness     | 103 |

| 21 | Communicating OLOS Automata (COA)    | 105 |

|    | 21.1 COA Configuration               | 105 |

|    | 21.2 COA Transition Function         | 106 |

|    | 21.2.1 Global COA Receive Phase (i)  | 106 |

|    | 21.2.2 Global COA Compute Phase (ii) | 106 |

|    | 21.2.3 Global COA Send Phase (iii)   | 107 |

|    | 21.2.4 COA Notation                  | 107 |

|    | 21.3 COA Correctness                 | 107 |

|    | 21.4 Pervasive COA Correctness       | 109 |

| 22 | Conclusion                           | 111 |

| 23 | Future Work                          | 112 |

| 24 | Abbreviations                        | 113 |

## List of Figures

| 1  | DLX Instruction Types                       | 24  |

|----|---------------------------------------------|-----|

| 2  | Processor Pipeline                          | 29  |

| 3  | Illustration of Scheduling Functions        | 30  |

| 4  | Memory System                               | 31  |

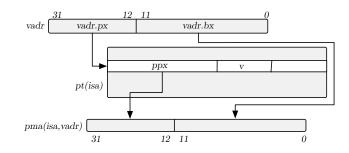

| 5  | Page Table Entry                            | 41  |

| 6  | Address Translation                         | 42  |

| 7  | Execution of Inline Assembly Code           | 48  |

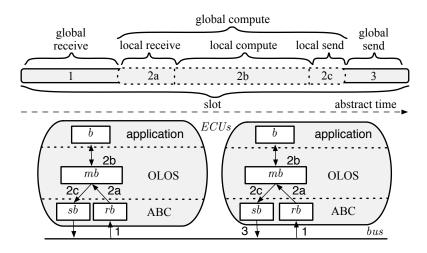

| 8  | OLOS: Slot Partitioning and Data-Flow       | 62  |

| 9  | ABC Schematics                              | 69  |

| 10 | ABC Slots                                   | 69  |

| 11 | Automaton for the Message Encoding          | 70  |

| 12 | Schedule Automaton                          | 71  |

| 13 | Serial Interface                            | 74  |

| 14 | Clock Edges                                 | 74  |

| 15 | Startup                                     | 78  |

| 16 | Schedule Correctness                        | 78  |

| 17 | DISTR: Slot Partitioning and Data-Flow      | 84  |

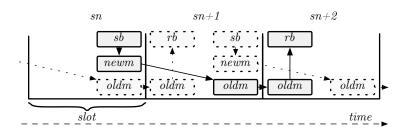

| 18 | Communication Delay in DISTR                | 85  |

| 19 | Abstraction of ABC from DIMPL to DH         | 86  |

| 20 | DOLOS: Slot Partitioning and Data-Flow      | 101 |

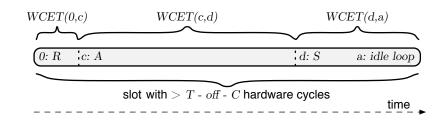

| 21 | Worst Case Execution Time (WCET) Constraint | 104 |

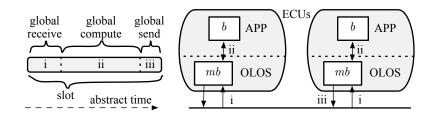

| 22 | COA: Slot Partitioning and Data-Flow        | 106 |

### **1** Introduction

More and more safety-critical functions in modern automobiles are controlled by applications running on embedded distributed computer systems. The growing complexity of these systems reduces the coverage of simulation and testing. Both techniques, however useful they are for debugging and evaluation of designs, are "hopelessly inadequate" for proving the absence of errors [Dij72]. Formal verification emerges as the only technique to ensure the demanded degree of reliability.

When analyzing the correctness of the applications, it is desirable to argue in a synchronous model of distributed electronic control units (ECUs) broadcasting messages in lock-step. However, such models are implemented at gate level as highly asynchronous systems. To bridge this gap, it does not suffice to verify certain aspects of a system, such as algorithms or protocols in isolation.

Correctness is shown with respect to some given specification model. Even slight incompatibilities in the used models can allow fatal errors to creep in. With the number of system components increasing, such errors proliferate.

Therefore, the verification objective must tie together the correctness of applications, the operating system, and the hardware implementation itself. The only solution is *pervasive* verification, also called systems or end-to-end verification [BHMY89, Moo03]. To achieve pervasiveness and hereby to minimize the chance of an undiscovered error, we develop a model stack that reaches from the hardware gate level up to an automata-theoretic model of communicating applications. The term "pervasiveness" expresses the fact that parts of the system are not picked out and verified in isolation from the rest. Instead, the correctness of the system is shown by simulation theorems between adjacent models in the model stack.

Note that the verification techniques introduced in this thesis are not limited to the automotive sector. Other sectors like avionics or robotics in which time-triggered system are being used, would benefit from the application of these techniques, too.

#### Overview

We start with a discussion of related work in Section 2 and an introduction to our notation in Sections 3. The thesis splits in two parts:

In Part I, we discuss the correctness of a *single* electronic control unit (ECU) based on [KP07a]. The instruction set architecture (ISA) of the DLX processor is introduced in Section 4. We show how to implement a processor based on boolean gates and how to prove the correctness of the implementation with respect to the ISA in Section 5. In Section 6, we specify an I/O device and integrate it in both the ISA and the processor using techniques from [HIP05, AHK<sup>+</sup>07]. This requires an adaptation of the processor correctness theorem from Section 5.

By extending the processor with memory management units, as done in [Hil05, Dal06], and reviewing the correctness proof of the virtualization mechanism in Section 7, we lay a basis for the process separation featured by our operating system.

In Section 8, we introduce the semantics for a high-level C-like programming language and sketch the compiler correctness theorem, see also [Pet07, LP08, Lei08]. In

#### 1 INTRODUCTION

Section 9, we extend the language by an additional statement allowing the execution of inline assembly code.

In Section 10, we show how to specify, implement, and prove the correctness of the CVM, a generic micro-kernel [GHLP05, KP07a, IdRT08]. We extend existing literature by going into details regarding the treatment of devices and the handling of timer interrupts.

In Section 11, the general device model from Section 6 is instantiated with a specification of a single automotive bus controller (ABC). In Section 12, we specify our OSEKtime-like operating [OSE08b] system OLOS from [Kna05] and show how to prove its correctness. Both, the local ABC specification from Section 11 and the local OLOS specification were first reported in [Kna08].

In Part II, we argue about the complete distributed system. In Sections 13 and 14, we introduce our ABC implementation that is based on boolean gates (being inspired by [Pau05]). Then we detail the verification approach of our implementation [BBG<sup>+</sup>05, KP07b]. In particular, we deal with the formalization of the scheduling correctness which we have already reported in [ABK08b]. We combine arguments regarding asynchronous bit-level transmission with the arguments regarding the clock synchronization at gate level. In Section 15, the ABC implementation is connected to the processor implementation.

In Section 16, we specify the desired inter-ECU communication behavior in DISTR [Kna08], a synchronous parameterized model that uses the specification of a single ABC from Section 11. By instantiating DISTR with a hardware model, as done in Section 17, a distributed hardware (DH) model is obtained. We prove the correctness of the implementation with respect to this DH model.

As the notion of time is indicated to the processor by means of interrupts, the point of view on the time might differ slightly between the processor and the ABC implementation due to the interrupt sampling policy of the processor. Thus, in Section 18, we introduce a distributed ISA (DISA) model representing the processor's point of view.

In the correctness proof of the DISA model we run into a problem regarding timer interrupts generated by the ABC. While the occurrence of interrupts is well-defined at gate level, the instructions being interrupted at the ISA level can inherently not be determined at the ISA level alone. The execution time of an instruction depends on cache hits and cache misses, but the memory hierarchy is not visible at the ISA level. To solve this problem we combine classical program correctness proofs at the ISA level, worst case execution time (WCET) analysis at the gate level, and a processor correctness proof into a pervasive correctness proof for our real-time system from the gate level to the ISA level.

By instantiating the DISTR model from Section 16 with the other local models from Part I we obtain the corresponding distributed model stack: the distributed CVM (DCVM) in Section 19 and the distributed OLOS (DOLOS) in Section 20.

To prove the correctness of all remaining distributed models we can reuse the local correctness theorems from Part I to a large extent. This is due to the definition of the DISTR model. Note that we were able to extend the arguments from [KP07a] by a more detailed analysis of the interrupt sampling, of all distributed models themselves, and of the propagation of the WCET throughout the distributed model stack.

Finally, in Section 21, we review the automata-theoretic model called communicating OLOS automata (COA) that completely abstracts from the devices. We report on our formal correctness proof of the DISTR model being instantiated with our local OLOS model with respect to the COA model that serves as our top-level specification, see also [Kna08]. Note that this proof has been formalized in Isabelle/HOL [NPW02].

We conclude in Section 22 and point out some future work in Section 23. In Section 24, the important abbreviations for all configurations and transition functions that are used throughout the thesis are summarized.

## 2 Related Work

*Pervasive verification* or *systems verification*, i.e. the verification of a system over several layers of abstraction, was introduced in the context of the CLI stack project [BHMY89]. However, the application of such verification-techniques to an industrial scenario without setting too harsh restrictions, e.g. on the programming languages, poses a "grand challenge" according to Moore [Moo03].

Single system layers were addressed in several other attempts. Usually the micro kernel layer is being considered. Recent candidates in this category are L4.verified [HEK<sup>+</sup>07, EKD<sup>+</sup>07], VFiasco [HTS02, HT05], and Eros [SW00]. All three projects have established semantics for C variants and have verified some properties on source-code level. However, hardware specific parts as well as the communication with I/O devices have been left out in the argumentation so far. All properties that are considered are purely local in the sense that they argue about a single instance of the system only.

Within the Flint project [NYS07], a verification framework for assembly code was developed. Using this framework and a formalization of a subset of the x86 instruction set, the correctness of context-switching code was formally proven.

There have also been severe efforts to argue about communication systems themselves. In particular, the formal verification of clock synchronization in timed systems has a long history [LMS85, Sha92, PSvH99]. But almost all approaches focused on algorithmic correctness, rather than on concrete system or even hardware correctness. As an exception, Bevier and Young [BY91] described the verification of a low-level hardware implementation of the "Oral Message" algorithm. The presented hardware model is quite simplified, as synchronous data transmission is assumed.

A formal proof of a clock-synchronization circuit was reported by Miner [MJ96]. Based on abstract state machines, a correctness proof of a variant of the Welch-Lynch algorithm [WL88] has been carried out in PVS [ORS92]. However, the algorithm was only manually translated to a hardware specification, which was finally refined semiautomatically to a gate-level implementation. No formal link between both is reported and the low-level bit transmission is not covered in the formal reasoning at all. Note that we explicitly show how to integrate such low-level results into the argumentation.

Rushby proposes the separation of the verification of timing-related properties (as clock synchronization) and protocol specifications [Rus99]. A set of requirements is identified which an implementation of a scheduler (e.g. in hardware) has to obey. In short, (i) clock synchronization and (ii) a round offset large enough to compensate the maximum clock drift between synchronization events are assumed. The central result

#### 2 RELATED WORK

is a formal and generic PVS simulation proof between the real-time system and its lock-step and synchronous specification. However, the required assumptions have not been discharged for concrete hardware.

Rushby gives an overview of the formal verification of the Time-Triggered Architecture [SHS<sup>+</sup>97] in [Rus02] and also formally proves the correctness for some key algorithms, e.g. a clock synchronization algorithm based on the Welch-Lynch algorithm [WL88]. Nevertheless, this remains isolated work. Even Rushby himself states that "some of these algorithms pose formidable challenges to current techniques and have been formally verified only in simplified form or under restricted fault assumptions".

A proof of the Biphase-Mark protocol was proposed by Brown and Pike [BP06]. Their models include metastability but verification is only done at specification level, rather than at the concrete hardware. The models were extracted manually.

Pike [Pik07] corrects and extends Rushby's work and instantiates the new framework with SPIDER, a *fly-by-wire* communication bus used by NASA. His model was extracted from the hardware design by hand, too. Neither of these approaches proved the correctness of any gate-level hardware.

Assuming correct clock synchronization, Zhang verified properties of the FlexRay bus guardian [Zha06]. He did not deal with any hardware implementation.

Serial interfaces were subject to formal verification in the work of Berry *et al.* [BKS03]. They specified a universal asynchronous receiver transmitter (UART) model in a synchronous language and proved a set of safety properties regarding FIFO queues. Based on that a hardware description can be generated and run on a FPGA. However, data transmission was not analyzed.

Neither of these approaches covers all aspects of the whole distributed system. Note that due to the differences in the formalisms being used it would be very cumbersome to combine the approaches into a single unified theory.

## Part I Single Electronic Control Unit (ECU)

## **3** Notation

Given a bit-string  $a = a[n-1:0] \in \mathbb{B}^n$  we denote the natural number with binary representation a by  $\langle a \rangle_n$ , where  $\langle . \rangle_n : \mathbb{B}^n \to \mathbb{N}$ :

$$\langle a \rangle_n = \sum_{i=0}^{n-1} a_i \cdot 2^i$$

We use the shorthand  $\langle a \rangle$  instead of  $\langle a \rangle_n$  if the length of the bit-string is clear from the context.

For numbers  $x \in \{0, ..., 2^n - 1\}$  the binary representation of length n is the bitstring  $bin_n(x)$  where  $bin_n : \mathbb{N} \to \mathbb{B}^n$  is defined by:

$$bin_n(x) = y \Leftrightarrow \langle y \rangle = x$$

We denote the *n*-bit binary addition by  $+_n$  where  $+_n : \mathbb{B}^n \times \mathbb{B}^n \to \mathbb{B}^n$  is defined by:

$$a +_n b = bin_n(\langle a \rangle_n + \langle b \rangle_n \mod 2^n)$$

Bit string concatenation is denoted by  $\circ$ . For bit-strings x and natural numbers  $n \ge 1$  we denote by  $x^n$  the bit-string obtained by concatenating x exactly n times with itself:

$$\begin{array}{rcl} x^1 & = & x \\ x^n & = & x^{n-1} \circ x \end{array}$$

Throughout the thesis we define various configurations and transition functions on these configurations. Given a configuration c and its transition function  $\delta_{\rm C}$ , we call the configuration after the application of  $\delta_{\rm C}$  the next configuration and denote it by c':

$$c' = \delta_{\rm C}(c)$$

Transition functions are defined by their effect on c, i.e. we define how to get c' from c. We stick to the following notation. An update of a function f at position a with the value x is denoted by:

$$f'(a) = x$$

Typically, configurations are records, e.g. c.b denotes the record component b in configuration c. A record update of the component c.b with the value y is denoted by:

$$c'.b = y$$

To shorten notation we only write down configuration components that are indeed changed. All unmentioned components remain unchanged unless explicitly stated otherwise. Memories *m* are defined using functions. The content of a memory *m* at address *a* is denoted by m(a). For 32-bit addresses *a* and natural numbers  $x \ge 1$  we denote by  $m_x(a)$  the concatenation of *x* memory entries starting at address *a* in little endian order:

$$m_1(a) = m(a) m_x(a) = m_{x-1}(a + 32 1) \circ m(a)$$

Updates a whole memory regions are denoted by:

$m'_x(z) = u$

Note that x must coincide with the number of memory entries in u.

## 4 Instruction Set Architecture (ISA)

Every processor can execute a specific set of instructions. The set of all these instructions and their effects on the processor are called the instruction-set architecture (ISA).

In this section we introduce the ISA for the DLX processor (see [MP00, HP96]). The DLX is a 32-bit reduced instruction set computing (RISC) processor with 32 general purpose registers (GPR) and a byte-adressable memory.

#### 4.1 ISA Configuration

Although a 32-bit architecture with a byte-addressable memory can address up to  $2^{32}$  memory bytes, the available build-in memory is often much smaller in reality.

Let the available number of bytes be given by nb. The set of available memory addresses Ma contains all binary addresses smaller than nb starting from address 0:

$$Ma = \{a \mid 0 \le \langle a \rangle < nb\}, \text{ where } 0 < nb \le 2^{32}$$

To simplify the argumentation regarding word accesses and paging later on we require that nb is a multiple of  $2^{12} = 4K$ .

An ISA configuration *isa* has the following components:

- a program counter  $isa.pc \in \mathbb{B}^{32}$ ,

- a delayed program counter  $isa.dpc \in \mathbb{B}^{32}$  used to specify the delayed branch mechanism (for details see [MP00]),

- a general purpose register file  $isa.gpr : \mathbb{B}^5 \to \mathbb{B}^{32}$  containing 32 registers each 32 bit wide, and

- a byte addressable memory  $isa.m: Ma \to \mathbb{B}^8$ .

|         | 31 | 26  | 21  | 16  | 11  | 0 |

|---------|----|-----|-----|-----|-----|---|

| R -type |    | opc | RS1 | RS2 | RD  |   |

| I -type |    | opc | RS1 | RD  | imm |   |

| J -type |    | opc | imm |     |     |   |

Figure 1: DLX Instruction Types

#### 4.2 Instruction Decoding

The instruction executed in configuration isa is denoted by I(isa). It is the memory word addressed by the delayed PC:

$$I(isa) = isa.m_4(isa.dpc)$$

Instruction decoding is formalized by predicates on the instruction word I(isa). The six high-order bits of the instruction word constitute the opcode *opc*:

$$opc(isa) = I(isa)[31:26]$$

In some cases it suffices to inspect the opcode to decode an instruction. For instance, the current instruction is a load word lw instruction if the opcode is 100011:

$$lw(isa) \Leftrightarrow opc(isa) = 100011$$

DLX instructions are divided in three instruction types as shown in Figure 1. The type of an instruction defines how the rest of the instruction word is interpreted. An occurrence of R-type instructions is for instance specified by:

$$rtype(isa) \Leftrightarrow opc(isa) = 000000$$

We denote I-type and J-type instructions by itype(isa) and jtype(isa). Their corresponding definitions are stated in [MP00]. Depending on the instruction type certain fields might have different positions within the instruction word. We illustrate this by giving some of the definitions as examples.

The operand RS1 denotes the first register source. It is given by:

$$RS1(isa) = I(isa)[25:21]$$

The operand RD denotes the register destination and is given by:

$$RD(isa) = \begin{cases} I(isa)[20:16] & itype(isa) \\ I(isa)[15:11] & otherwise \end{cases}$$

The immediate constant *imm* is given by:

$$imm(isa) = \begin{cases} I(isa)[15:0] & itype(isa) \\ I(isa)[25:0] & \text{otherwise} \end{cases}$$

We compute the effective address ea of a load or store operation by adding up the content of the register addressed by the RS1 operant isa.gpr(RS1(isa)) and the sign extended immediate constant imm(isa).

The addition is performed modulo  $2^{32}$  with two's complement arithmetic. We define the sign extension of the immediate constant by:

$$sxt(imm(isa)) = \begin{cases} imm(isa)[15]^{16} \circ imm(isa) & itype(isa) \\ imm(isa)[26]^5 \circ imm(isa) & \text{otherwise} \end{cases}$$

This operation turns the immediate constant into a 32-bit constant while preserving the value as a two's complement number (see [MP00] for details). The effective address is thus defined by:

$$ea(isa) = isa.gpr(RS1(isa)) +_{32} sxt(imm(isa))$$

This definition is possible since n bit two's complement numbers and n bit binary numbers have the same value modulo  $2^n$ . For details see Chapter 2 of [MP00].

#### **4.3 ISA Transition Function**

Using the above definitions we define the next configuration isa' as the configuration after the execution of I(isa). This formalizes the instruction set in terms of a transition function  $\delta_{isa}$ :

$$isa' = \delta_{isa}(isa)$$

In the definition of isa' we split cases depending on the instruction to be executed. As an example we specify the next configuration for a load word and a store word instruction.

As the main effect of a load word instruction lw, the general purpose register addressed by the RD field is updated with the memory word addressed by the effective address ea. Furthermore, the PC is incremented by four using 32-bit binary arithmetic and the old PC is copied into the delayed PC:

$$lw(isa) \Rightarrow \begin{cases} isa'.gpr(RD(isa)) &= isa.m_4(ea(isa))\\ isa'.pc &= isa.pc + 32 bin_{32}(4)\\ isa'.dpc &= isa.pc \end{cases}$$

This update of the program counters is identical for all instructions except control instructions.

As the main effect of a store word instruction sw, the general purpose register content addressed by RD is copied into the memory word addressed by ea:

$$sw(isa) \Rightarrow \begin{cases} isa'.m_4(ea(isa)) &= isa.gpr(RD(isa))\\ isa'.pc &= isa.pc + {}_{32}bin_{32}(4)\\ isa'.dpc &= isa.pc \end{cases}$$

The entire definition of  $\delta_{isa}$  is obtained by formalizing all instructions in the above formalism. Since this formalization is not important for our work, we do not give it here but refer to a similar definition in [MP00].

#### 4.4 Extended ISA Configuration

Interrupts provide the means to break the execution of a sequential program. As we will see later on in Section 10.3, they can be used by applications to request special services from an operating system.

In order to define the interrupt semantics at the ISA level, we extend the ISA configuration *isa* by a special purpose register file (SPR):

• the special purpose register file  $isa.spr : \mathbb{B}^5 \to \mathbb{B}^{32}$  contains 32 single registers each 32 bit wide.

We use the following abbreviations to refer to particular registers of the special purpose register file (see [MP00]):

- the status register isa.sr = isa.spr[0] stores an interrupt mask,

- the exception cause register  $isa.eca = isa.spr[bin_5(2)]$  stores the masked cause of an interrupt, and

- the exception data register *isa.edata* = *isa.spr*[*bin*<sub>5</sub>(5)] stores additional information regarding the current interrupt.

#### 4.5 Dealing with Interrupts

Interrupts are triggered by interrupt event signals that might be internally generated (like illegal instruction, misalignment, and overflow) or externally generated (like reset and timer interrupt). Interrupts are numbered using indices  $j \in \{0, ..., 31\}$ . We classify the set of these indices in two categories:

- maskable or not maskable interrupts; the set of indices of maskable interrupts is denoted by *M*.

- external or internal interrupts; the set of indices of external interrupts is denoted by *E*.

We denote external event signals by eev[j] with  $j \in E$  and we denote internal event signals by iev[j] with  $j \notin E$ . External event signals are gathered into a vector eev and internal event signals into a vector iev.

Formally these signals must be treated in a very different way. Whether an internal event signal iev[j] is activated in configuration *isa* is determined by the configuration only.

Let j = 1 be used for the illegal instruction interrupt and let  $LI \subset \mathbb{B}^{32}$  denote the set of bit patterns not coding an instruction of the ISA. Then the illegal instruction interrupt is given by:

$$iev(isa)[1] \Leftrightarrow I(isa) \notin LI$$

While the internal event signals are functions of the current processor configuration *isa*, external interrupts are external inputs to the transition function. Before we can argue about the interrupt handling we need some more auxiliary functions. The cause vector ca of all event signals is a function of the processor configuration *isa* and the external input *eev*:

$$ca(isa, eev)[j] = \begin{cases} eev[j] & j \in E\\ iev(isa)[j] & \text{otherwise} \end{cases}$$

The masked cause vector mca is computed from ca using the interrupt mask isa.sr. An interrupt j is masked out if it is maskable and sr[j] = 0:

$$mca(isa, eev)[j] = \begin{cases} ca(isa, eev)[j] \land isa.sr[j] & j \in M \\ ca(isa, eev)[j] & \text{otherwise} \end{cases}$$

The jump to interrupt service routine *JISR* signal is turned on if any of the masked cause bits equals 1:

$$JISR(isa, eev) = \bigvee_{j} mca(isa, eev[j])$$

It is important to know the smallest index of an active bit in the mca since several interrupt signals might become active simultaneously. This index is called the interrupt level il. It specifies the interrupt of highest priority that is handled immediately:

$$il(isa, eev) = \min\{j \mid mca(isa, eev)[j] = 1\}$$

#### 4.5.1 Trap Instructions

The DLX instruction set contains a special trap instruction that allows the programmer to generate an internal interrupt. It is of J-type format with opcode 111110. We assign the trap instruction the internal event number 5:

$$iev(isa)[5] \Leftrightarrow opc(isa) = 111110$$

A trap interrupt needs to be handled if this event signal is the active signal with highest priority:

$$trap(isa, eev) \Leftrightarrow il(isa, eev) = 5$$

#### 4.6 ISA Transition Function with Interrupts

We extend the ISA transition function  $\delta_{isa}$  to deal with interrupts:

$$isa' = \delta_{isa}(isa, eev)$$

We case split on *JISR*. If no interrupt needs to be handled, i.e. *JISR* does not hold, we use the simple transition function from Section 4.3. The special purpose register file remains unchanged:

$$\neg JISR(isa, eev) \Rightarrow isa' = \delta_{isa}(isa)$$

Otherwise the PCs are forced to point to the start addresses of the interrupt service routine (ISR); we assume it starts at (binary) address 0:

$$JISR(isa, eev) \Rightarrow \begin{cases} isa'.dpc &= bin_{32}(0) \\ isa'.pc &= bin_{32}(4) \end{cases}$$

All maskable interrupts are masked and the masked cause register is saved into the exception cause register:

$$JISR(isa, eev) \Rightarrow \begin{cases} isa'.sr &= bin_{32}(0) \\ isa'.eca &= mca(isa, eev) \end{cases}$$

By ed(isa) we denote the sign-extended immediate constant in case of a trap interrupt and the effective address otherwise:

$$ed(isa, eev) = \begin{cases} sxt(imm(isa)) & trap(isa, eev) \\ ea(isa) & \text{otherwise} \end{cases}$$

Auxiliary data for the interrupt handling (in form of *ed*) is stored in the exception data register *edata*:

$$isa'.edata = ed(isa, eev)$$

Note that in case of a trap the *edata* registers keeps the sign-extended immediate constant that was specified by the programmer as part of the instruction word.

This summary suffices for our purposes. A complete definition of the interrupt mechanism in a similar formalism is given in Chapter 5 of [MP00].

## **5 Processor Hardware (H)**

The ISA defined above constitutes the specification for the behavior of a processor. In this section we show how to implement a processor that provably implements this ISA.

#### 5.1 Hardware Configuration

The processor is implemented using a standard digital hardware model. A hardware configuration h consists of:

- 32 bit registers, one for each specification register (comp. Sections 4.1 and 4.4), i.e. h.pc, h.dpc ∈ B<sup>32</sup>, h.gpr : B<sup>5</sup> → B<sup>32</sup>, and a multi-port register file h.spr as defined in [MP00],

- an additional set of implementation specific registers, and

- an  $(a \times d)$ -random access memory (RAM), i.e.  $h.m : \mathbb{B}^a \to \mathbb{B}^d$ .

Figure 2: Processor Pipeline

#### 5.2 Hardware Transition Function

Registers and RAMs are connected by Boolean circuits. We denote the value of a signal s in configuration h by s(h). The hardware transition function  $\delta_{\rm h}$  depends on an external hardware event vector *heev*. It maps a hardware configuration h to the hardware configuration  $h' = \delta_{\rm h}(h, heev)$ , i.e. the configuration after the next clock cycle. For registers h.r with clock enable signal *rce* and input *rin* we define:

$$h'.r = \begin{cases} rin(h) & rce(h) \\ h.r & \text{otherwise} \end{cases}$$

A multi-port register file which allows the simultaneous update of several register is defined in [MP00].

For a RAM h.m with address signal addr, data input din, and the write signal w we define:

$$h'.m(x) = \begin{cases} din(h) & x = addr(h) \land w(h) \\ h.m(x) & \text{otherwise} \end{cases}$$

Hardware computations are defined in the usual way as sequences of configurations. Hardware computations must satisfy for all cycles t:

$$h^{t+1} = \delta_{\rm h}(h^t, heev^t)$$

A superscript t in this model is read as 'during cycle t'.

In general, processor correctness theorems state that hardware defined in a hardware model simulates in some sense the ISA. In the following sections we state more precisely in which sense.

#### 5.3 Scheduling Functions

The processor correctness proof considered here is based on the concept of scheduling functions *s* as in [KMP00, MP00]. The hardware of pipelined processors, supporting

Figure 3: Illustration of Scheduling Functions

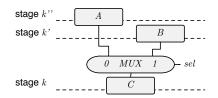

out-of-order execution [Kro01], consists of many stages as sketched in Figure 2, e.g. instruction fetch (IF) stage, issue stage, reservation stations (RS), reorder buffer (ROB), write back (WB) stage.

Stages can be full or empty due to pipeline bubbles. The hardware keeps track of this with the help of full bits  $full_k$  for each stage k as defined in [MP00]. The value of the full bit of stage k in cycle t is denoted by  $full_k(h^t)$ . To shorten notation we simply write  $full_k^t$ . Note that the instruction fetch stage IF is always full, since new instructions can be fetched at any time, i.e.  $\forall t. full_{IF}^t = 1$ .

For stages k that are full during hardware cycle t, i.e.  $full_k^t$  holds, the value of the scheduling function s(k,t) is the index i of the instruction that is in stage k during cycle t. If the stage is not full, s(k,t) is the index of the instruction that was in stage k in the last cycle before t when the stage was full. Initially s(IF, 0) = 0 holds.

In the definition of scheduling functions we use a simple idea: We imagine the hardware having registers that can hold integers of arbitrary size. We augment each stage with such a register and use it to store the index of the instruction currently being executed in that stage.

Note that these indices are computed exactly as the tags in a Tomasulo scheduler. The only difference is that the indices have unbounded size because we count up to arbitrarily large indices. In real hardware this is not possible and not necessary. Nevertheless, in this abstract mathematical model there is no problem to do this.

Each stage k of the processors under consideration has an update enable signal  $ue_k$ . Stage k gets new data in cycle t if the update enable signal  $ue_k$  equals one in cycle t-1. We fetch instructions in order and define for the instruction fetch stage IF:

$$s(IF,t) = \begin{cases} s(IF,t-1) + 1 & ue_{IF}^{t-1} \\ s(IF,t-1) & \text{otherwise} \end{cases}$$

Other stages k can get data belonging to a new instruction from one or more stages. Examples for stages with more than one predecessor are: cycles in the data path of a floating point unit performing iterative division, or the producer registers connected to the common data bus of a Tomasulo scheduler. In this situation we define for each stage k a predicate trans(k', k, t) indicating that in cycle t data is transmitted from stage k' to stage k. In the example in Figure 3 we use the select signal *sel* of the multiplexer *MUX* and define:

$$trans(k',k,t) = ue_k^t \wedge sel^t$$

Figure 4: Memory System

If trans(k', k, t - 1) holds for some k' we set s(k, t) = s(k', t - 1) for that k'. Otherwise s(k, t) = s(k, t - 1).

#### 5.4 Processor Correctness Theorem

The simulation relation isasim(h, isa) between some hardware configuration h and some ISA configuration isa requires that specification registers  $r \in \{pc, dpc, gpr, spr\}$  have identical values:

h.r = isa.r

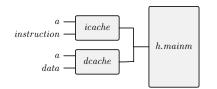

We would like to define something similar for the memory. However, this cannot work, since the user visible processor memory is simulated in the hardware by a memory system consisting among others of an instruction cache *icache*, a data cache *dcache*, and a main memory *mainm* as shown in Figure 4.

There exists a non-trivial function  $m(h) : Ma \to \mathbb{B}^8$  specifying the memory simulated by the memory system. This function can be defined in the following way [Pau08]: Imagine we have an abstract cache *ac*. This abstract cache stores content of the size of the main memory *ac.con* :  $Ma \to \mathbb{B}^8$  and a valid bit *ac.v* :  $Ma \to \mathbb{B}$ .

We use two abstract caches to specify the memory that is simulated by the memory system in the hardware configuration h, one for data dac(h) and one for instructions iac(h). Let ihit(h, a) denote a hit in the instruction cache for an address a and let dhit(h, b) denote a hit in the data cache for an address b. Then the valid bits are defined as follows:

$$dac(h).v(a) = dhit(h, a)$$

$$iac(h).v(b) = ihit(h, b)$$

The content fields simply map addresses a to the content of the corresponding hardware caches at address a.

Note that in the processor under consideration the caches snoop on each other. Hence the data of address a is only in at most one cache [BJK<sup>+</sup>03, Bey05]. Thus we define:

$$m(h)(a) = \begin{cases} iac(h).con(a) & iac(h).v(a) \\ dac(h).con(a) & dac(h).v(a) \\ h.mainm(a) & \text{otherwise} \end{cases}$$

Using this definition we additionally require in the simulation relation isasim(h, isa):

$$m(h)(a) = isa.m(a)$$

In a pipelined machine this simulation relation almost never holds. In one cycle different hardware stages k usually hold data from different ISA configurations; after all this is the very idea of pipelining. There is however an important exception when the pipeline is drained and thus all hardware stages except the instruction fetch stage are empty:

$$drained(h^t) \Leftrightarrow \forall k \neq IF. \neg full_k^t$$

This happens to be the case after interrupts, in particular initially after reset.

First, we ignore the interrupt event signals (which brings us formally back to an ISA computations defined by  $isa^{i+1} = \delta_{isa}(isa^i)$ ).

Each user visible register  $isa.r \in \{pc, dpc, gpr, spr\}$  of the processor has a counter Part h.r belonging to some stage k = stage(r) of the hardware. We have to show by induction on t that for all registers r in stage k = stage(r), the value of the hardware register r in cycle t equals the value of the ISA register r for the instruction scheduled in stage k in cycle t:

$$h^t r = isa^{s(k,t)} r$$

For the memory we have to consider the memory unit of the processor consisting of two stages *mem* and *mem1*. Stage *mem* contains hardware for the computation of the effective address. The memory  $m(h^t)$  simulated by the memory hierarchy of the hardware in cycle t is identical with the ISA memory  $isa^{s(mem1,t)}.m$  for the instruction scheduled in stage *mem1* in cycle t:

$$m(h^t)(a) = isa^{s(mem1,t)}.m(a)$$

We combine both statements in a processor correctness theorem.

**Theorem 1 (Processor Correctness)** Let the pipeline be drained and let the simulation relation hold initially, i.e.  $drained(h^0)$  and  $isasim(h^0, isa^0)$ . Then for all cycles t and for all registers  $r \in \{pc, dpc, gpr, spr\}$  in stage k = stage(r):

$$\begin{array}{rcl} h^t.r &=& isa^{s(k,t)}.r\\ m(h^t)(a) &=& isa^{s(mem1,t)}.m(a) \end{array}$$

The theorem is proven by induction on the hardware cycle t using additional statements on the implementation registers. Furthermore, restrictions for the software to be executed by the processor are needed, as detailed below.

For complex processors this requires hundreds of pages of paper and pencil proofs (see [MP00]). A formal correctness proof is described in [Bey05, BJK<sup>+</sup>05].

#### 5.4.1 Synchronization Conditions

If the hardware implementation of a physical machine is pipelined or if instructions are executed out of order the following situation might occur: An instruction  $I(isa^i)$  that is in the memory stage may modify a later instruction  $I(isa^j)$  for j > i after it has been fetched. This situation is called a read after write (RAW) hazard. Instruction  $I(isa^i)$  may overwrite the instruction itself or change the operating mode.

On a RAW hazard an instruction fetch (in particular a translated fetch implemented by a memory management unit) would not work correctly. It is possible to detect such data dependencies in hardware and to roll back the computation if necessary.

Alternatively, the software to be run on the processor must adhere to certain *software synchronization conventions*. Let  $iaddr(isa^j)$  denote the address of instruction  $I(isa^j)$ . If  $I(isa^i)$  writes to address  $iaddr(isa^j)$ , then an intermediate instruction  $I(isa^k)$  for i < k < j must drain the pipe.

#### 5.5 Dealing with Interrupts

When dealing with interrupts the hardware gets external inputs called the hardware external event signals *heev*. Their value in hardware cycle t is denoted by *heev*<sup>t</sup>. Based on these we construct a sequence of external ISA event signals  $eev^i$  such that the ISA computation satisfying  $isa^{i+1} = \delta_{isa}(isa^i, eev^i)$  simulates a hardware computation  $h^{t+1} = \delta_h(h^t, heev^t)$ .

For non-memory operations the processor hardware samples external event signals in the write back stage WB as detailed in [Tve08]. Since WB is the last stage in the pipeline it cannot be stalled. Thus for every instruction i there is exactly one hardware cycle t when the instruction is written back:

$$t = WB(i) \Leftrightarrow s(WB, t) = i \wedge full_{WB}^{t}$$

In Part II of this thesis we will argue that in the distributed system under consideration the external interrupts occur only if the processor executes non-memory operations. Thus the external ISA event signal observed by instruction i is:

$$eev^i = heev^{WB(i)}$$

Note that a hardware event signal  $heev^t$  is not visible to the ISA computation if the write back stage in cycle t is empty. With this new definition of the ISA-/hardware computation Theorem 1 still holds. More details regarding a formal processor correctness proof dealing with external event signals are given in [Bey05, Dal06].

Later on we argue about hardware cycles in which the pipeline is drained. To do so, we use the signal JISR(h, heev) that indicates if an interrupt needs to be handled in the given hardware configuration. The predicate is defined by applying the definitions from Section 4.6 to hardware configurations. Note that once the JISR predicate holds, the pipeline is *drained* in the next hardware cycle:

$$JISR(h^t, heev^t) \Rightarrow drained(h^{t+1})$$

## 6 Devices (D)

In this section we introduce a framework for the integration of a device into the model stack. This framework will later on be instantiated with an automotive bus controller (see Sections 11 and 13).

The communication between the processor and the device is done via memory mapped I/O. The device is assigned a set of device addresses. These addresses, called

I/O ports, are mapped into the processors memory above the maximal physical byte address nb. Via read and write operations to these I/O ports the processor can communicate with the device.

In the remainder of this section we show how to integrate a device into the processor implementation and into the ISA.

#### 6.1 Device Configuration

In general, a device has more state than is visible through the I/O ports. A device configuration d has the following components:

• a word addressable port RAM *d.m* where the number of the addresses is given by the page size *K*, as defined in Section 4:

$$d.m: \mathbb{B}^{10} \to \mathbb{B}^{32}$$

- a boolean interrupt flag *d.int* indicating if an interrupt was generated but has not been cleared, yet.

- some device specific 'internal' state d.z.

We assign the external event 13 to the device. As we are dealing with a single device only, the external event vector eev is computed as follows:

$$eev(d) = 0^{13} \circ d.int \circ 0^{18}$$

#### 6.2 Integration of a Device in General

The I/O ports of a device can be divided into three categories:

- control ports are only written from the processor,

- status ports are only read by the processor, and

- data ports can be written or read from both the processor and the outside world.

Inputs from and outputs to the outside world are device specific: network devices have inputs and outputs, monitors produce only outputs, keyboards take only inputs, disks neither produce outputs nor consume external inputs. Thus, in general, the classical synchronization issues of shared memory arise.

In the following section we show how to integrate a device into the processor implementation. Therefore we extend the transition function by an external input from the outside world. We use a device specific stable predicate which indicates if all the I/O ports are not altered by the outside world and thus have memory semantics. In Section 15 we will instantiate the device with our concrete automotive bus controller (ABC) implementation.

In Section 6.5, we define the semantics of a purely stable device at the gate level. In the remaining sections of Part I we will deal with a stable device only. The resulting theorems will be applied later on in Part II for a bounded interval in which the real device is indeed stable.

We justify the usage of the stable device semantics in Section 17. There we will prove a simulation theorem between our possibly unstable device implementation and an extended semantics which is based on the stable device semantics from 6.5. Note that our device implementation behaves most of the time like a stable device. Only in well-defined cycles the device alters the data-ports. In the interval between those cycles the device is stable and we can use the semantics developed throughout Part I in our argumentation.

#### 6.3 Integration of a Device into the Processor Implementation

We integrate a device into the processor implementation by combining the processor configuration with the device configuration. We denote the combined configuration by impl. It has the following components:

- a processor configuration *impl.p* being a hardware configuration h as defined in Section 5, and

- a device configuration *impl.d* as defined above.

The device takes inputs from and produces output to the processor side and the outside world. Inputs from the processor side are like inputs for the RAM and consist of: data input din(impl.p), address adr(impl.p), a write signal dw(impl.p) and a read signal dr(impl.p). Outputs to the processor side consists of data output dout(impl.d) and an external interrupt signal. Inputs to and outputs from the processor side are device specific.

Let address adr(impl.p) be the address of a memory operation in analogy to the effective address ea in the ISA.

The device is mapped into the processors memory starting at some base address ba which we assume to be  $1^{20}0^{12}$ . Using an address decoder the memory system decides if a read or write access to the memory is a device access. The read signal dr(impl.p), which indicates a read-access to the device, is activated if the operation is a load word operation lw(impl.p) and the memory address is greater or equal to the base address ba. The latter is implemented by an equality check of the upper most bits of the address:

$$dr(impl.p) \Leftrightarrow (lw(impl.p) \land adr(impl.p)[31:12] = 1^{20})$$

The write signal dw(impl.p), which indicates a write-access to the device, is activated if the operation is a store word operation sw(impl.p) and the memory address is greater or equal to the base address ba.

$$dw(impl.p) \Leftrightarrow (sw(impl.p) \land adr(impl.p)[31:12] = 1^{20})$$

Using these two signals we define a predicate daccess(impl) which indicates if the processor is accessing the device:

$$daccess(impl) = (dw(impl.p) \lor dr(impl.p))$$

In case of a device access, the lower bits of the memory address code the port, i.e. the word-address within the address range of the device:

$$port(impl) = adr(impl.p)[11:2]$$

Note that the cache system must be designed in a way that it does not cache accesses to I/O ports.

### 6.4 Implementation Semantics

Next we define the transition function  $\delta_{impl}$  for the combined configuration *impl*. In addition to the configuration itself it takes a device specific input x from the outside world:

$$impl' = \delta_{impl}(impl, x)$$

Being at the gate level, the processor implementation and the device are clocked in lock-step.

If the processor does not access the device, i.e.  $\neg daccess(impl)$ , the processor configuration is updated according to the old transition function  $\delta_h$  from Section 5.2:

$$\neg daccess(impl) \Rightarrow impl'.p = \delta_{h}(impl.p)$$

To define the transition function  $\delta_{impl}$  in case of a device access, we use the predicate stable(impl) which indicates if:

• the I/O ports of the ABC implementation have memory semantics. Thus for a read operation from the device it holds that:

$daccess(impl) \land dr(impl.p) \Rightarrow dout(impl.d) = impl.d.m(port(impl))$

For a write operation to the device it holds that:

$$daccess(impl) \wedge dw(impl.p) \Rightarrow$$

$$impl'.d.m(x) = \begin{cases} din(impl.p) & x = port(impl)\\ impl.d.m(x) & \text{otherwise} \end{cases}$$

• a write to a special device address, called *command port*, has the side-effect that the interrupt flag of the device is cleared. We assume w.l.o.g. that this port has the device address *cmd*:

$$daccess(impl) \land dw(impl.p) \land (port(impl) = cmd) \Rightarrow impl'.d.int = 0$$

In case of a device access, i.e. daccess(impl), the transition function  $\delta_{impl}$  is defined as follows: if the device is being accessed by a read operation and the device is stable, the output dout(impl.d) from the device to the processor is the content of the I/O port being addressed:

$$daccess(impl) \land dr(impl.p) \land stable(impl) \Rightarrow dout(impl.d) = impl.d.m(port(impl))$$

The processor component is updated using the output dout(impl.d) from the device.

If the device is being accessed by a write operation and the device is stable, the ports behave like a RAM:

$$daccess(impl) \land dw(impl.p) \land stable(impl) \Rightarrow$$

$$impl'.d.m(x) = \begin{cases} din(impl.p) & x = port(impl)\\ impl.d.m(x) & \text{otherwise} \end{cases}$$

Furthermore, if the device is stable, a write to the command port *cmd* has the side-effect that the interrupt flag is cleared:

$$\begin{aligned} access(impl) \wedge dw(impl.p) \wedge stable(impl) \wedge (port(impl) = cmd) \Rightarrow \\ impl'.d.int = 0 \end{aligned}$$

If the device is not stable, the ports might be read or modified by the device side in a device specific way using the external input x. The effect of writing to a non-stable device is left undefined. The processor side learns about changes in the stable predicate by an interrupt generated by the device.

Note that according to the above definitions the device is unusually fast: it updates a port in a single cycle of the processor hardware. Devices are usually slower and thus require a busy signal indicating if a read or write access is in progress. The above definitions could be extended in this way using a memory protocol like the one from [MP00].

### 6.5 Implementation Semantics for a Stable Device

In this section we show how to integrate a stable device into the processor hardware. This device simply behaves like an additional memory.

We denote the combined configuration by hd. It has the following components:

- a hardware configuration hd.p as defined in Section 5, and

- a device configuration hd.d.

Note that the configuration hd has basically the same components as the configuration *impl*. However, the transition function for hd does explicitly model the behavior of a stable device. In Section 17 we show that in bounded cycle intervals the hdconfiguration and transition function can be used to argue about the implementation configuration *impl*.

Next we define the transition function  $\delta_{hd}$  for the combined configuration hd. Note that this transition function does not take any external input:

$$hd' = \delta_{hd}(hd)$$

If the processor does not access the device, i.e.  $\neg daccess(hd)$ , we reuse the old transition function  $\delta_h$  from Section 5.2. The device remains unchanged:

$$\neg daccess(hd) \Rightarrow \begin{cases} hd'.p = \delta_{h}(hd.p) \\ hd'.d = hd.d \end{cases}$$

If the device is being accessed by a read operation, the output dout(hd.d) from the device to the processor is the content of the I/O port being addressed:

$daccess(hd) \land dr(hd.p) \Rightarrow dout(hd.d) = hd.d.m(port(hd))$

The processor component is updated using the data output dout(hd.d) from the device.

If the device is being accessed by a write operation, the ports behave like a RAM:

$$daccess(hd) \land dw(hd.p) \Rightarrow hd'.d.m(x) = \begin{cases} din(hd.p) & x = port(hd) \\ hd.d.m(x) & \text{otherwise} \end{cases}$$

A write to the command port, has the side-effect that the interrupt flag of the device is cleared:

$$daccess(hd) \land dw(hd.p) \land (port(hd) = cmd) \Rightarrow hd'.d.int = 0$$

Note that if the stable predicate *stable* holds, the  $\delta_{hd}$  transition function can be used instead of the  $\delta_{impl}$  transition function:

**Lemma 1 (Stable Semantics)** If the stable predicate stable(impl) holds, the  $\delta_{hd}$  semantics corresponds to the  $\delta_{impl}$  semantics:

$$\forall x. stable(impl) \Rightarrow \begin{cases} (\delta_{impl}(impl, x)).p &= (\delta_{hd}(impl)).p \\ (\delta_{impl}(impl, x)).d.m &= (\delta_{hd}(impl)).d.m \\ (\delta_{impl}(impl, x)).d.int &= (\delta_{hd}(impl)).d.int \end{cases}$$

This lemma is proven using the definition of the stable predicate from Section 6.4.

### 6.6 Integration of a Stable Device into the ISA

We integrate a stable device into the ISA by combining the two configurations. The combined configuration *isad* has the following components:

- an ISA configuration *isad*.*p* as defined in Section 4.4, and

- a device configuration *isad.d* as defined above.

The predicate daccess(isad) indicates if the processor is accessing the device. It is true if the processor performs a store word or a load word operation and the effective address equals or is greater than the base address ba which is in our case  $1^{20}0^{12}$ :

$$daccess(isad) = (lw(isad.p) \lor sw(isad.p)) \land (ea(isad.p)[31:12] = 1^{20})$$

If the predicate daccess(isad) holds, the lower bits of the effective address code the port address port(isad), i.e. the word-address within the address range of the device:

$$port(isad) = ea(isad.p)[11:2]$$

Using these two functions, the transition function  $\delta_{isad}$  for the combined configuration *isad* is defined as follows:

$$isad' = \delta_{isad}(isad)$$

This transition function will only be applied for intervals in which the device is stable and thus behaves like an ordinary RAM.

If the device is not accessed or an interrupt needs to be handled, the old transition function from Section 4.6 is reused. The state of the device is not altered:

$\begin{aligned} \neg daccess(isad) \lor JISR(isad.p, eev(isad.d)) \Rightarrow \\ \begin{cases} isad'.p &= \delta_{isa}(isad.p, eev(isad.d)) \\ isad'.d &= isad.d \end{cases}$

If the processor is accessing the device via a memory operation and no interrupt needs to be handled, an extended load word or store word semantics is used. In case of a load word from a device address the return destination register RD is updated with the content of the accessed device memory:

$daccess(isad) \land \neg JISR(isad.p, eev(isad.d)) \land lw(isad.p) \Rightarrow isad'.p.gpr(RD(isad.p)) = isad.d.m(port(isad))$

In case of a store word to a device address, the accessed ports behave like a RAM:

$\begin{aligned} & access(isad) \wedge \neg JISR(isad.p, eev(isad.d)) \wedge sw(isad.p) \Rightarrow \\ & isad'.d.m(x) = \begin{cases} isad.p.gpr(RD(isad.p)) & x = port(isad) \\ isad.d.m(x) & \text{otherwise} \end{cases} \end{aligned}$

A write to the command port cmd has the side-effect that the interrupt flag is cleared:

$$daccess(isad) \land \neg JISR(isad.p, eev(isad.d)) \land sw(isad.p) \land (port(isad) = cmd) \Rightarrow isad'.d.int = 0$$

### 6.7 Processor Correctness Theorem with Devices

Next, we extend the processor correctness (Theorem 1) to deal with a stable device. Although we will quantify in the following theorem over all cycles t it will only be applied for a bounded computation in which the device indeed behaves like an ordinary RAM (see Section 17).

In the hardware the device is placed parallel to the normal memory system in stage mem1, thus we can use the same scheduling functions as for the memory.

By extending the simulation relation from Section 5.4 we get a new simulation relation isadsim(hd, isad). We additionally require that the device configuration be the same:

isasim(hd.p, isad.p)hd.d = isad.d

The processor correctness theorem dealing with devices is stated as follows:

**Theorem 2 (Processor Correctness with Devices)** Let the pipeline be drained and let the simulation relation hold initially, i.e. drained  $(hd.h^0)$  and  $isadsim(hd^0, isad^0)$ .

Then for all hardware cycles t, for all processor stages k and for all specification registers  $r \in \{pc, dpc, gpr, spr\}$  with stage(r) = k:

$$\begin{array}{rcl} hd^t.p.r &=& isad^{s(k,t)}.p.r\\ m(hd^t.p) &=& isad^{s(mem1,t)}.p.m\\ hd^t.d &=& isad^{s(mem1,t)}.d \end{array}$$

The theorem is proven by induction on the hardware cycle t using additional statements on the implementation registers as well as the software conditions from Section 5.4.1. Since we are using the same device model for the ISA level as for the gate level, the external event signals correspond to the translation from Section 5.5: