## Dissertation

Zur Erlangung des Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I

der Universität des Saarlandes

# ILP-based Path Analysis on Abstract Pipeline State Graphs

von Diplom-Informatiker

Ingmar Jendrik Stein

aus Saarbrücken

Saarbrücken 2010

**Tag des Kolloquiums:** 28. Mai 2010

**Dekan:** Prof. Dr. Joachim Weickert **Vorsitzender:** Prof. Dr. Raimund Seidel

Gutachter: Prof. Dr. h. c. mult. Reinhard Wilhelm

Prof. Dr. Sebastian Hack

Akademischer Mitarbeiter: Dr.-Ing. Philipp Lucas

#### **Impressum**

Copyright © 2010 by Ingmar Stein Herstellung und Verlag: epubli GmbH, Berlin, http://www.epubli.de Printed in Germany

ISBN: 978-3-86931-538-6

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

# **Abstract**

This thesis presents a novel approach to path analysis which is an integral part of the WCET analysis. Up to now, there have been two different methods for this step, each with its respective advantages and disadvantages. The new ILP-based path analysis on abstract pipeline state graphs supersedes the existing ones and combines the positive aspects of both but does not introduce new limitations. It provides high precision and the flexibility of user-provided annotations at the same time while opening up new possibilities for optimizations such as a new kind of persistence analysis.

# Zusammenfassung

Diese Arbeit präsentiert einen innovativen Ansatz für die Pfadanalyse, ein integraler Bestandteil der WCET-Analyse. Bisher gab es zwei verschiedene Methoden für diesen Schritt, jede mit ihren spezifischen Vor- und Nachteilen. Die neue ILP-basierte Pfadanalyse auf abstrakten Pipelinezustandsgraphen ersetzt die beiden existierenden und kombiniert die positiven Aspekte, ohne neue Beschränkungen einzuführen. Sie bietet sowohl eine hohe Präzision als auch die Flexibilität benutzerbestimmter Annotationen. Darüber hinaus bietet sie neue Optimierungsmöglichkeiten wie zum Beispiel eine neuartige Persistenzanalyse.

# Acknowledgements

First of all, I very much thank Prof. Dr. h. c. mult. Reinhard Wilhelm for the opportunity to write my thesis about this challenging and interesting topic. He provided me with a lot of freedom for approaching my goals.

Thanks go to Prof. Dr. Sebastian Hack for his willingness to examine this work. I am also indebted to Dr.-Ing. Philipp Lucas and Dr. Reinhold Heckmann for proof-reading parts of this work and giving valuable hints. Dr.-Ing. Florian Martin had the initial vision of the topic and had good ideas for future enhancements and improvements. Furthermore, I thank all colleagues at AbsInt Angewandte Informatik GmbH for a very pleasant working atmosphere.

Last but not least, I would like to thank my family for their support during the time of my research.

# **Contents**

| Αŀ | ostra | ct – iii |                                 |

|----|-------|----------|---------------------------------|

| Zι | ısam  | menfa    | ssung – ${f v}$                 |

| Αc | kno   | wledge   | ments - vii                     |

| 1  | Int   | roduct   | ion - 1                         |

| 2  | Ov    | erview   | - 5                             |

|    | 2.1   | The a    | aiT Toolchain - 5               |

|    |       | 2.1.1    | Control-flow Reconstruction - 6 |

|    |       | 2.1.2    | Loop Analysis - 8               |

|    |       | 2.1.3    | Value Analysis - 8              |

|    |       | 2.1.4    | Cache/Pipeline Analysis - 8     |

|    |       | 2.1.5    | Path Analysis - 10              |

|    | 2.2   | Callir   | ng Contexts - 13                |

| 3  | Th    | eoretic  | al Background - 15              |

|    | 3.1   | Lattic   | ce Theory - 15                  |

|    | 3.2   | Fixed    | Point Iteration - 18            |

|    | 3.3   | Galoi    | s Theory - 20                   |

|    | 3.4   | Abstı    | ract Interpretation - 21        |

|    | 3.5   | Integ    | er Linear Programming - 24      |

|    |       | 3.5.1    | Linear Programs - 24            |

|    |       | 3.5.2    | Simplex Algorithm - 26          |

```

3.5.4 Branch and Bound Algorithm - 28

ILP-based Path Analysis - 31

4.1 ILP - 31

4.1.1 Objective Function - 31

4.1.2 Program Start Constraints - 33

4.1.3 Structural Constraints - 33

4.1.4 Loop Constraints - 34

4.1.5 Time-based Loop Constraints - 36

4.1.6 User Added Constraints - 37

Implementation - 40

4.2

Path Analysis on Abstract Pipeline State Graphs - 41

5.1

Prediction Files - 43

Implementation - 47

5.2

ILP-based Path Analysis on Abstract Pipeline State Graphs - 49

Graph Compression - 50

6.1.1 Chain Compression - 51

6.1.2 Basic Block Compression - 54

6.1.3 Infeasible Nodes - 57

6.1.4 \varepsilon-transition Elimination – 58

6.1.5 Buddy Nodes - 58

6.1.6 Chain Combination - 62

6.1.7 Fixed Point - 65

6.1.8 Lossy Compression - 66

6.1.9 Inter-block Compression - 66

6.2 Loop and User Constraints - 67

6.3

Predictability - 68

Cache Persistence Analysis - 69

Cache Analysis - 69

Must Analysis - 71

7.1.2

May Analysis - 71

```

3.5.3 Integer Linear Programs - 28

## 7.1.3 Persistence Analysis - 72 Precise Use of Cache Persistence Analysis - 74 7.3 Automatic Persistence Scopes - 75

- 7.4 **Persistence Constraints - 75**

- Generalization 76 7.5

7.2

#### Implementation and Evaluation - 79

- Implementation 79

- 8.1.1 Platforms 80

- 8.1.2 Prediction File Library 81

- 8.1.3 ILP Solvers 81

- 8.1.4 ILP Solver Optimization 84

- 8.1.5 Visualization 85

- 8.1.6 Memory Usage 86

- 8.2 Evaluation 88

- 8.2.1 Precision 88

- 8.2.2 Graph Compression 89

- 8.2.3 ILP Complexity 93

- 8.2.4 ILP Solver Comparison 94

- 8.2.5 Cache Persistence Analysis 95

- 8.2.6 Features 96

- 9 Outlook 97

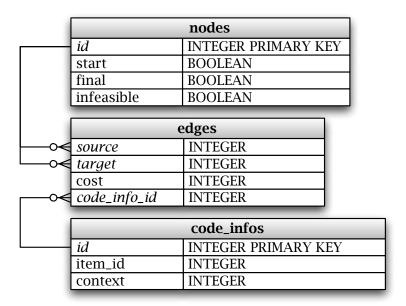

- **SQL-based Node Storage** 97 9.1

- 9.2 More Architectures 98

- 9.3 More Constraints 99

- 9.4 Parallelization 99

- 9.5 **Detecting Timing Anomalies - 100**

- 9.6 **Best-Case Execution Time - 100**

- 10 Summary 101

- A Examples 103

- **CRL2 File 103 A.**1

- A.2 Prediction File 109

A.3 ERG File - 111

**A.4 GDL** File - 112

A.5 Abstract Pipeline State - 115

List of Tables - 119

**List of Figures** - 121

Listings - 123

List of Algorithms - 125

Bibliography - 127

Index - 135

#### Chapter

# 1 Introduction

Today, microprocessors are pervasive not only in personal computers, but also in cars, planes and entertainment electronics. The information processing systems contained therein are called *embedded systems*. The programming of these systems differs significantly from ordinary application development. For example, many embedded systems have to fulfill *real-time requirements*, i. e. programs must guarantee to finish within a given timespan (deadline). If embedded systems with real-time requirements fulfill tasks relevant to security, they are subject to *hard* real-time requirements, because it may have catastrophic consequences if the maximum response time is exceeded. For example, the electronic control unit of a thrust-reverser has to comply with hard real-time, because a failure can lead to a plane crash.

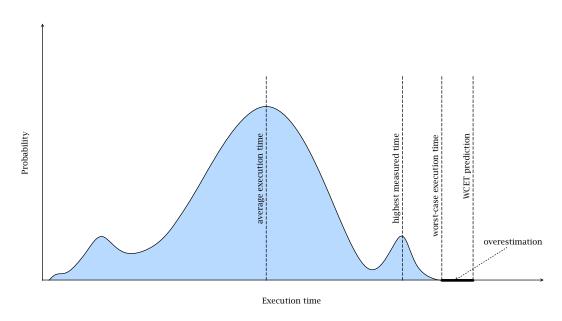

To make sure that such systems work correctly, it is essential to find upper bounds for the execution time (worst-case execution time, *WCET*) of programs. In the majority of cases, it is not sufficient to only measure the runtime of a program with a given input because it is usually impossible to prove that this input leads to the maximum execution time (cf. figure 1.1). Similarly, it is often not feasible to measure the program with all possible inputs because the set of inputs may be prohibitively large. Therefore, an analysis is needed which determines the maximum runtime of a program *statically*, i. e. an analysis which calculates an upper bound for the runtime without actually running the program with any particular input. However, modern processors employ

Figure 1.1.: Typical probability of observed execution times

different techniques to enhance performance that make such an analysis difficult: caches, pipelines and branch prediction. The state-of-the-art of solving this problem is a combination of abstract interpretation and integer linear programming (ILP) as it is used in the aiT component of the  $a^3$  analysis framework by AbsInt Angewandte Informatik GmbH.

The new tool presented in this thesis enhances aiT by providing a better path analysis which replaces the existing one. It improves the precision of the worst-case execution time estimation, i. e. it reduces the amount of overestimation by up to 20%. At the same time, it offers a high level of versatility and opens up new opportunities for further optimizations of the WCET prediction precision.

This thesis is structured as follows: the next chapter 2 presents an overview over this work and the analysis framework it is integrated into, followed by chapter 3 with the mathematical fundamentals which constitute the theoretical foundation for the following chapters. The next two chapters 4 and 5 describe the existing path analysis methods—the classical ILP-based path analysis and

its counterpart which works on abstract pipeline state graphs. A detailed description of the new analysis which improves upon the former can be found in chapter 6. Chapter 7 introduces a method to improve the WCET precision by using the results of a cache persistence analysis within the new path analysis. Implementation details, an evaluation and test results are contained in chapter 8. Chapter 9 gives an outlook on possible future work and extensions. Finally, chapter 10 summarizes the findings of this work. Appendix A includes some selected examples.

### Chapter

# 2 Overview

The focus of this work is a novel approach to *path analysis*, which is an integral part of the WCET analysis. So far, there existed two different methods for this step, each with its respective advantages and disadvantages. The new approach tries to supersede the existing ones and combines the positive aspects of both but does not introduce new limitations.

#### 2.1. The aiT Toolchain

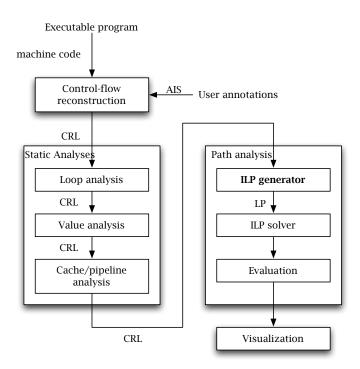

The new path analysis method is a part of aiT, a modular WCET analysis framework. Figure 2.1 on page 10 depicts the components it is comprised of and shows how they interact. The individual framework modules as described in [Ferdinand and Heckmann, 2008] are:

- **Control-flow reconstruction** decodes, i.e. identifies instructions and reconstructs the control-flow graph (CFG) from the binary program.

- Loop analysis determines upper bounds for the number of iterations of loops.

- **Value analysis** computes value ranges for registers and memory cells and address ranges for instructions accessing memory.

- Cache/pipeline analysis classifies memory references as cache misses or cache hits and predicts the behavior of the program on the processor pipeline.

- **ILP generator** transforms the basic block execution times and the control flow into an integer linear program (ILP).

- **II.P solver** solves the II.P.

- **Evaluation** computes the worst-case execution path of the input program from the optimal ILP solution and computes the WCET contributions of the individual routines.

- **Visualization** generates a graph in the graph description language (GDL) to visualize the WCET path.

#### 2.1.1. Control-flow Reconstruction

The result of this phase is a control flow graph stored in a CRL2 file. The CRL2 format is used as the data exchange format of the different phases.

CRL2 stands for Control Flow Representation Language Version 2. This language was developed by the *Transferbereich 14* and describes the control flow graph of a program in a textual form. Design goals were efficient support of analyses and optimizations. The underlying structure is organized hierarchically: a graph consists of operations, instructions, basic blocks (cf. definition 2.1.2) and routines where the former are always contained within the latter. Example A.1.1 shows how a decoded binary program looks like when it is stored in CRL2 format.

**Definition 2.1.1** (Control Flow Graph (CFG)). A *control flow graph* is a fourtuple K = (V, E, s, x) with a set of nodes V, a set of directed edges  $E \subseteq V \times V$ ,

a unique start node s and a unique end node x. The start node s fulfills:

$$\forall u \in V : (u, s) \notin E$$

The end node x fulfills:

$$\forall u \in V : (x, u) \notin E$$

Furthermore, a function  $F:V\to P$  must exist to map nodes to program fragments. P designates the set of program fragments, e.g. given by the syntax tree representation.

*Remark.* The requirement for unique start and end nodes is no restriction, because each graph can simply be extended by two additional nodes. The construction of control flow graphs is described at length in [Allen, 1970].

**Definition 2.1.2** (Basic Block). Let K = (V, E, s, x) be a control flow graph. A sequence of nodes  $(n_1, ..., n_k)$  forms a *basic block*, if  $\forall i \in \{1, ..., k-1\}$ :

```

n_i is the only predecessor of n_{i+1}

\land \quad n_{i+1} is the only successor of n_i

```

**Definition 2.1.3** (Maximal Basic Block). A basic block is called *maximal* if it cannot be extended by including adjacent nodes without violating definition 2.1.2.

In the following, basic blocks are always assumed to be maximal.

*Remark.* A basic block has a single entry point and a single exit point. The start of a basic block may be the target of more than one branch instruction. The end of a basic block is either a branch instruction or the instruction preceding the destination of a branch instruction.

#### 2.1.2. Loop Analysis

WCET analysis requires that upper bounds for the iteration numbers of all loops be known. aiT tries to determine the number of loop iterations by *loop bound analysis*. The loop bound analysis consists of two parts: a pattern matcher which recognizes loop patterns as generated by the most commonly used compilers and a data flow analysis which interprets the machine instructions in loop bodies to derive loop bounds [Cullmann, 2006]. Bounds for the iteration numbers of the remaining loops must be provided as user annotations.

#### 2.1.3. Value Analysis

Value analysis tries to determine the values in the processor memory for every program point and execution context [Sicks, 1997, Fritz, 2001]. Its results are used to determine possible addresses of indirect memory accesses—important for cache analysis. The precision of the value analysis is usually so high that only a few indirect accesses cannot be determined exactly. Address ranges for these accesses may be provided by user annotations.

#### 2.1.4. Cache/Pipeline Analysis

Pipeline analysis models the pipeline behavior to determine execution times for basic blocks of instructions. It takes into account the current pipeline state(s), in particular resource occupancies, contents of prefetch queues, grouping of instructions, and includes a cache analysis for the classification of memory references. The result is an execution time for each basic block in each distinguished execution context.

The cache/pipeline analysis uses abstract interpretation—a concept that will be described in greater detail in section 3.4. Basically, the cache/pipeline

analysis models the behavior of the pipeline of a specific processor by using abstract descriptions for the concrete pipeline states [Thesing, 2004]. The abstract pipeline states are used to solve a data flow problem on the input program and the result is an abstract pipeline state graph.

**Definition 2.1.4** (Abstract Pipeline State Graph). An *abstract pipeline state graph* is a weighted graph G = (V, E, C),  $C : E \to \mathbb{N}$ , where V consists of the abstract pipeline states for the given input program. An edge weight C((u, v)) describes the costs in CPU cycles associated with the transition from the abstract state u to the abstract state v.

What exactly is abstracted in an abstract pipeline state highly depends on the processor architecture. Usually, the model includes abstractions for internal buffers, caches, jitter and queues. As a reference, the textual representation of an abstract pipeline state for the Motorola MPC755 is given in example A.5.1.

The pipeline analysis *splits* an abstract pipeline state into two or more successor states when it encounters imprecise information. This happens for instance when a memory access cannot be classified as *cache hit* or *cache miss*. How many successor states are generated depends on the *WCET computation mode*:

**Global worst-case:** all successor states are created and the pipeline analysis follows their further evolution.

**Local worst-case:** the pipeline immediately decides which successor likely leads to the worst-case execution time and follows the evolution of this single state. Splits may still occur; they are triggered by situations in which it is not clear which is the locally worst successor state.

The local worst-case computation mode leads to a massive reduction of the runtime of the pipeline analysis, but there is a risk that the successor state that seems to be worst from a local point of view does not lead to the global worst-case execution time.

#### 2.1.5. Path Analysis

Using the results of the micro-architecture analyses, path analysis determines a safe estimate of the WCET by computing a worst-case path through the program.

#### Path Analysis with ILP Generator

The first variant of the path analysis models the program's control flow by an integer linear program so that the optimal solution to the objective function is the predicted worst-case execution time for the input program. Variables in the integer linear program correspond to basic blocks so that execution and traversal counts for every basic block and edge can be computed.

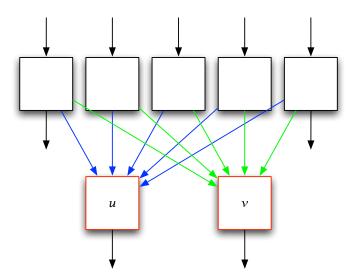

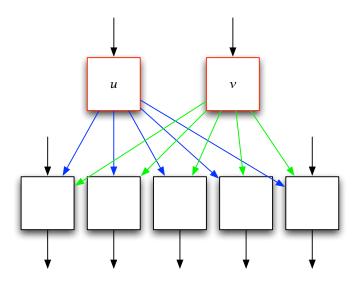

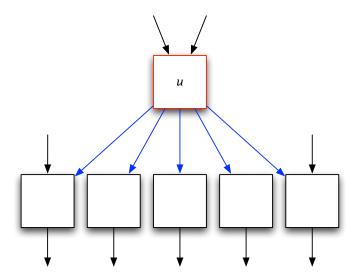

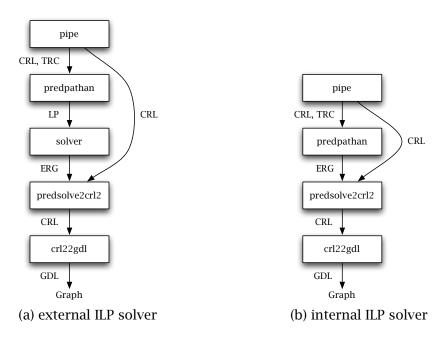

Figure 2.1.: aiT toolchain with ILP generator

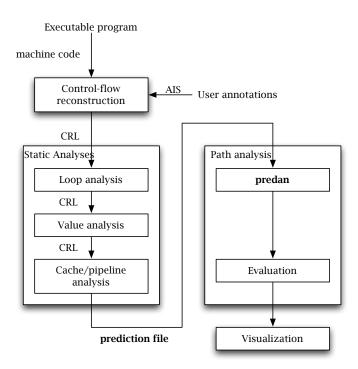

#### Path Analysis on Abstract Pipeline State Graphs

A drawback of the path analysis with an ILP generator is that it uses the worst-case path through the pipeline states for each basic block. It therefore combines execution traces which might not represent an actual execution of the program. The resulting over-estimation can be eliminated by computing the worst-case path right from the pipeline state graph.

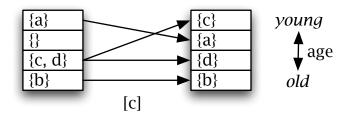

For this method, the toolchain is changed as follows: the ILP generator and ILP solver components are replaced by a single tool called predan which implements the path analysis using the abstract pipeline state graph stored in the so-called prediction file (cf. figure 2.2).

Figure 2.2.: aiT toolchain with prediction file

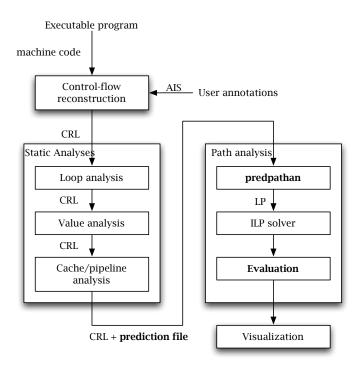

#### **ILP-based Path Analysis on Abstract Pipeline State Graphs**

Both path analysis variants above have some limitations: the ILP-based analysis suffers from inherent imprecisions and the path analysis on abstract pipeline state graphs does not handle loops and user annotations.

The variant that is introduced in this work overcomes these limitations by using the abstract pipeline state graph to generate an ILP which is able to incorporate loop constraints and user annotations while still providing the highest level of precision.

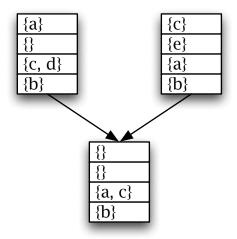

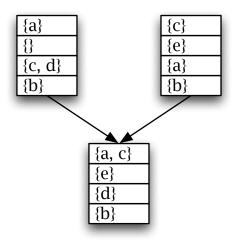

The toolchain is modified from the original ILP-based method as follows: the ILP generator is replaced by the new implementation which reads the prediction file in addition to the control flow graph and the evaluation step is adapted to the changed semantics of the ILP variables (cf. figure 2.3).

Figure 2.3.: aiT toolchain with ILP solver and prediction file

## 2.2. Calling Contexts

In an over-simplified view, a static program analysis computes some abstract information for every program point p. The abstract information for p has to be a correct approximation of the concrete program state at p whenever control reaches p (no matter what happened before). Thus, the abstract information for a program point p in a routine R must approximate all program states at p in all calls of R.

To be more concrete, consider a value analysis that computes an interval of possible values for every register r. The interval for r is a correct approximation of a concrete program state if it contains the value of r in this program state. Suppose now a routine R is called twice, once with parameter 0 and once with parameter 3. Then the best abstract information that can be obtained for the parameter register is the interval [0,3], which indicates that the value of the register might be 0, or 1, or 2, or 3. The precision of the analysis can be improved considerably if the analysis does not compute a single abstract value for each program point in R, but two different ones, one for each call of R. In the example considered above, these are the intervals [0,0] for the call with parameter 0 and [3,3] for the call with parameter 3. The values 1 and 2 are thus excluded successfully.

To be more general again, the analyses compute an abstract information for every pair of a program point p and a possible calling context of p. All program points in a given routine R have the same set of calling contexts. Each calling context indicates a particular way of calling R.

#### Chapter

# 3 Theoretical Background

The path analysis builds upon the results of diverse data flow analyses, one of which is the combined cache/pipeline analysis. A data flow analysis is an application of abstract interpretation on control flow graphs. Thus, this chapter gives an overview over the mathematical foundations of the concepts used in abstract interpretation. For that purpose, it introduces the fundamental terms of lattice theory, Galois theory and fixed point iteration.

The two ILP-based path analysis methods use integer linear programming as a means to solve the path analysis problem. Subsequently to the foundations of abstract interpretation, this chapter describes the structure of linear programs and the  $\mathcal{NP}$ -hard class of integer linear programs and points out some of their important properties. It also outlines algorithms to solve linear and integer linear programs.

# 3.1. Lattice Theory

**Definition 3.1.1** (Partial and Total Order). Let M be a set. A binary relation  $\subseteq \subseteq M \times M$  is called *partial order* of M, if:

1. Reflexivity:

$\forall x \in M : x \sqsubseteq x$

#### 3. Theoretical Background

2. Transitivity:

$$\forall x,y,z \in M : x \sqsubseteq y \land y \sqsubseteq z \implies x \sqsubseteq z$$

3. Antisymmetry:

$$\forall x, y \in M : x \sqsubseteq y \land y \sqsubseteq x \implies x = y$$

The relation is called *total order* of *M*, if additionally:

$$\forall x, y \in M : x \sqsubseteq y \lor y \sqsubseteq x$$

A set *M* together with a partial order  $\sqsubseteq$  is called a *partially ordered set*  $(M, \sqsubseteq)$ .

The relation  $\sqsubseteq$  has a pointwise extension for functions:

$$f \sqsubseteq g \iff \forall x : f(x) \sqsubseteq g(x)$$

**Definition 3.1.2** (Upper/Lower Bound). Let  $(M, \sqsubseteq)$  be a partially ordered set and  $N \subseteq M$ . An element  $x \in M$  is called an *upper bound* of N, if:

$$\forall \gamma \in N : \gamma \subseteq x$$

- 1. *x* is an upper bound of *N*

- 2.  $x \subseteq z$  holds for all upper bounds z of N

$\sqcup$  is called *union*. The least upper bound of two elements x and y is denoted by  $x \sqcup y$ .

**Definition 3.1.3** ( $\omega$ -Chain). Let  $(M, \sqsubseteq)$  be a partially ordered set. An  $\omega$ -chain<sup>1</sup> of a partial order is an ascending chain of elements  $x_0, x_1, x_2, \ldots$  of M with:

$$x_0 \sqsubseteq x_1 \sqsubseteq x_2 \sqsubseteq \cdots \sqsubseteq x_i \sqsubseteq \cdots$$

If an  $\omega$ -chain additionally fulfills:

$$x_0 \sqsubset x_1 \sqsubset x_2 \sqsubset \cdots \sqsubset x_i \sqsubset \cdots$$

then it is called a *strictly ascending*  $\omega$ -chain. Here,  $x \sqsubset y$  is defined by  $x \sqsubset y \iff x \sqsubseteq y \land x \neq y$ .

**Definition 3.1.4** (Complete Partial Order). Let  $(M, \sqsubseteq)$  be a partially ordered set.  $(M, \sqsubseteq)$  is called a *complete partial order* (CPO) if there exists a least upper bound of the set  $\{x_i \mid i \in \omega\}$  for each  $\omega$ -chain  $x_0 \sqsubseteq x_1 \sqsubseteq x_2 \sqsubseteq \cdots \sqsubseteq x_i \sqsubseteq \cdots$  with  $x_i \in M$ .

**Definition 3.1.5** (Ascending Chain Condition). A partially ordered set  $(M, \sqsubseteq)$  fulfills the *ascending chain condition*, if each  $\omega$ -chain is finite, i.e. has only finitely many different elements.

*Remark.* A partially ordered set with ascending chain condition is a complete partially ordered set.

**Definition 3.1.6** (Complete Lattice). A partially ordered set  $(M, \sqsubseteq)$  is called *complete lattice*, if each subset of M has a least upper bound and a greatest lower bound. A lattice is written as a tuple  $(M, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$  with  $\bot = \prod M$  and  $\top = \bigsqcup M$ .

*Remark.* A complete lattice is especially a complete partially ordered set.

<sup>&</sup>lt;sup>1</sup>The ordered set  $(\mathbb{N}, \leq)$  is denoted by  $\omega$ .

**Definition 3.1.7** (Dual Lattice). Let  $(M, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$  be a complete lattice. The *dual lattice* is given by swapping the following symbols:  $\sqsubseteq$  by  $\exists$ ,  $\sqcup$  by  $\sqcap$  and  $\bot$  by  $\top$ .

**Definition 3.1.8** (Monotonic Function). A function  $f: A \to B$  of two partially ordered sets  $(A, \sqsubseteq_A)$  and  $(B, \sqsubseteq_B)$  is called *monotonic*, if:

$$\forall x, y \in A : x \sqsubseteq_A y \implies f(x) \sqsubseteq_B f(y)$$

**Definition 3.1.9** (Distributive Function). A function  $f: A \to B$  of two complete lattices  $(A, \sqsubseteq_A)$  and  $(B, \sqsubseteq_B)$  is called *distributive*, if:

$$\forall x, y \in A : f(x) \sqcup f(y) = f(x \sqcup y)$$

*Remark.* A distributive function is always monotonic.

**Definition 3.1.10** (Continuous Function). A function  $f: A \to B$  of two complete partially ordered sets  $(A, \sqsubseteq_A)$  and  $(B, \sqsubseteq_B)$  is called *continuous*, iff for all  $\omega$ -chains  $x_0 \sqsubseteq_A x_1 \sqsubseteq_A x_2 \sqsubseteq_A \cdots \sqsubseteq_A x_i \sqsubseteq \cdots$  in A holds:

$$\bigsqcup_{i \in \omega} f(x_i) = f\left(\bigsqcup_{i \in \omega} x_i\right)$$

Remark. A continuous function is always monotonic.

#### 3.2. Fixed Point Iteration

In abstract interpretation, recursive systems of equations need to be solved, where the values to be defined also appear on the right side of the equation. For example, this is the case when using abstract interpretation to analyze the behavior of programs that contain loops or recursive functions.

A popular example for such a system of equations is the factorial function

$$fac(n) = \begin{cases} 1 & \text{if } n = 0, \\ n \cdot fac(n-1) & \text{else.} \end{cases}$$

A solution is expected to fulfill the equation. To solve these recursive definitions, there exists a simple, iterative approach: starting with the least element of the solution space  $\bot$ , an element is inserted in the definition equation. This yields the definition for the next greater element. This process is repeated n times and so defines a function on the interval [0, ..., n-1]. The sought-after function of the natural numbers is found by forming the limit for  $n \to \infty$ .

**Definition 3.2.1** (Prefixed Point). Let  $f: M \to M$  be a function. An element  $x \in M$  is called *prefixed point* of f, if:

$$f(x) \sqsubseteq x$$

**Definition 3.2.2** (Fixed Point). Let  $f: M \to M$  be a function. An element  $x \in M$  is called *fixed point* of f, if:

$$f(x) = x$$

**Theorem 3.2.1** (Fixed Point Iteration). Let  $(M, \sqsubseteq)$  be a complete partially ordered set with the least element  $\bot$  and  $f: M \to M$  a continuous function. Let  $fix: (M \to M) \to M$  be defined by:

$$fix(f) = \bigsqcup_{i \in \omega} f^i(\bot)$$

Then fix(f) is a fixed point of f and the least prefixed point of f. Therefore, it holds:

1.

$$f(\operatorname{fix}(f)) = \operatorname{fix}(f)$$

2.

$$\forall x \in M : f(x) \subseteq x \implies fix(f) \subseteq x$$

*Remark.* Because each fixed point is also a prefixed point, it follows that fix(f) is the least fixed point of f.

**Definition 3.2.3** (Least and Greatest Fixed Point). The least fixed point of a function f is also called lfp(f), the greatest fixed point gfp(f).

## 3.3. Galois Theory

Abstract interpretation works with representatives of concrete values. The abstraction of elements of a concrete data space is carried out with the help of concepts from Galois theory. The concepts required for this work are given below. Further information and many examples can be found in [Nielson et al., 1999].

**Definition 3.3.1** (Galois Connection). Let  $(L, \sqsubseteq)$  and  $(M, \sqsubseteq)$  be complete lattices and  $\alpha: L \to M$  and  $\gamma: M \to L$  monotonic functions. The four-tuple  $(L, \alpha, \gamma, M)$  is called *Galois connection* between the two lattices, iff:

```

\cdot \ \gamma \circ \alpha \supseteq id_L

```

$$\cdot \alpha \circ \gamma \subseteq id_M$$

The function  $\alpha$  is also called *abstraction function* and the function  $\gamma$  is also called *concretization function*.

In a Galois connection  $(L, \alpha, \gamma, M)$ , multiple elements M can exist which are an abstraction of the same element of L, because the abstraction function  $\alpha$  is not required to be injective. On the other hand, the lattice M might contain more elements than necessary for the abstraction of L. The following variation of the Galois connection is used in abstract interpretation to avoid this:

**Definition 3.3.2** (Galois Insertion). Let  $(L, \alpha, \gamma, M)$  be a Galois connection. It is

called a Galois insertion, iff:

$$\alpha \circ \gamma = id_M$$

Consequently, no precision is lost when first concretizing and then abstracting an element within a Galois insertion.

## 3.4. Abstract Interpretation

Abstract interpretation is a general concept of program analysis and was first introduced by Cousot and Cousot in 1977 [Cousot and Cousot, 1977, Cousot and Cousot, 1992]. Because data flow analysis can be interpreted as a special case of abstract interpretation, this section presents a short overview over the theoretical framework.

Abstract interpretation aims to replace *concrete semantics* by *abstract semantics*. This is done by replacing concrete values by abstract values in such a way that both have a fixed relation, i. e. for each concrete value k, an abstract value  $\overline{k}$  should exist which describes k. This is expressed by the *abstraction function*:  $\overline{k} = \alpha(k)$ . For each operation *op* within the concrete semantics, an abstraction  $\overline{op}$  must exist, so that it holds:

$$\alpha(k_1 \ op \ k_2) \subseteq (\alpha(k_1)) \ \overline{op} (\alpha(k_2))$$

This ensures that the chosen operation  $\overline{op}$  correctly abstracts the operation op.  $\overline{op}$  is called *abstract operation* on the abstract domain of the abstract semantics which should approximate the corresponding operation on the concrete domain. A big challenge of abstract interpretation is to choose the abstract semantics. It should be designed in such a way that calculations always terminate and that the results allow for usable conclusions on the behavior of the original program.

**Example 3.4.1** (Sign Determination). The following example determines the sign of arithmetic expressions with the help of abstract semantics. Allowed operators are addition (+) and multiplication (×). For the abstract semantics, the abstract domain is chosen to be  $\{neg, zero, pos, ?\}$  where the question mark stands for values with an unknown sign. The abstraction function is given by the signum function  $\sigma$ :

$$\sigma(x) = \begin{cases} neg & x < 0 \\ zero & x = 0 \\ pos & x > 0 \end{cases}$$

The abstract operators  $\oplus$  und  $\otimes$  adhere to the calculation rules given in table 3.1.

| Φ    | pos | zero | neg | ? |

|------|-----|------|-----|---|

| pos  | pos | pos  | ?   | ? |

| zero | pos | zero | neg | ? |

| neg  | ?   | neg  | neg | ? |

| ?    | ?   | ?    | ?   | ? |

| $\otimes$ | pos  | zero | neg  | ?    |

|-----------|------|------|------|------|

| pos       | pos  | zero | neg  | ?    |

| zero      | zero | zero | zero | zero |

| neg       | neg  | zero | pos  | ?    |

| ?         | ?    | zero | ?    | ?    |

Table 3.1.: Calculation rules for  $\oplus$  and  $\otimes$

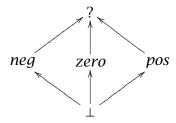

Extended by a smallest element  $\bot$ , the set of abstract values represents a complete lattice. Figure 3.1 illustrates the lattice together with its ordering.

Figure 3.1.: Complete lattice of the abstract values

After the introductory example, abstract interpretation will be formally defined during the course of this section. To begin with, the concept of local consistency is needed:

**Definition 3.4.1** (Local Consistency). Let  $(L, \alpha, \gamma, M)$  be a Galois insertion. A concrete function  $f: L \to L$  and an abstract function  $f': M \to M$  are called *locally consistent*, if it holds that:

$$\forall x \in L : f(x) \sqsubseteq \gamma \left( f' \left( \alpha \left( x \right) \right) \right)$$

Figure 3.2 illustrates this relation.

$$\begin{array}{ccc} \alpha(x) & \stackrel{f'}{\longrightarrow} f'(\alpha(x)) \\ \alpha & & & = \bigvee y \\ x & \stackrel{f}{\longrightarrow} f(x) \end{array}$$

Figure 3.2.: Local consistency

With the help of this notion, abstract interpretation can now be defined as follows:

**Definition 3.4.2** (Abstract Interpretation). An *abstract interpretation* consists of two components:

- · a Galois insertion  $(L, \alpha, \gamma, M)$  and

- a pair of locally consistent functions  $f: L \to L$  and  $f': M \to M$ .

Instead of proving properties of function f, one can now also prove them for its abstraction f'. The two conditions above guarantee for the correctness.

Fixed point iteration is needed to compute a result if f respectively f' contain a recursion. In this regard, the following relation is useful:

**Theorem 3.4.1** (Fixed Point Relation). Given an abstract interpretation by means of the Galois insertion  $(L, \alpha, \gamma, M)$  and the locally consistent functions f and f'. The following relations hold for the fixed points of both functions:

- ·  $lfp(f) \sqsubseteq \gamma(lfp(f'))$

- $gfp(f) \sqsubseteq \gamma(gfp(f'))$

## 3.5. Integer Linear Programming

#### 3.5.1. Linear Programs

This section introduces the structure of Linear Programs. How they can be solved will be shown in the next section.

**Definition 3.5.1** (Comparison of Vectors). Let  $\Delta \in \{\leq, =, \geq\}$  be a comparison operator and let  $a, b \in \mathbb{R}^n$ . Then we define

$$\mathbf{a} \Delta \mathbf{b} \iff \mathbf{a}_i \Delta \mathbf{b}_i \quad \forall i = 1, \dots, n$$

**Definition 3.5.2** (Linear Combination). Let  $\mathbf{x} \in \mathbb{R}^n$  be variable and let  $\mathbf{a} \in \mathbb{R}^n$  be constant. Then  $\mathbf{a}^T \mathbf{x}$  is called a *linear combination* of  $\mathbf{x}$ .

**Definition 3.5.3** (Linear Program). Let  $t \in \mathbb{R}^d$ ,  $b \in \mathbb{R}^m$ ,  $A \in \mathbb{R}^{m \times d}$  be known and constant. A *Linear Program* (LP) is the task to maximize  $t^T x$  in such a way that  $x \in \mathbb{R}^d_{\geq 0} \land Ax \leq b$ . In short, this is written:

$$\max \boldsymbol{t}^{\mathrm{T}} \boldsymbol{x} : A \boldsymbol{x} \leq \boldsymbol{b}, \boldsymbol{x} \in \mathbb{R}^{d}_{\geq 0}$$

**Definition 3.5.4.** In definition 3.5.3 the function  $C : \mathbb{R}^d \to \mathbb{R}$  where  $C(x) = t^T x$  is called *objective function*. The inequalities given by  $Ax \le b$  are called *constraints*. x is said to be a *feasible* solution, if it satisfies  $Ax \le b$ . Let

$P = \left\{ \boldsymbol{x} \in \mathbb{R}^d_{\geq 0} : A\boldsymbol{x} \leq \boldsymbol{b} \right\}$  be the set of feasible solutions.  $\boldsymbol{x}^*$  is said to be an *optimal* solution, if  $\boldsymbol{t}^T \boldsymbol{x}^* = \max \left\{ \boldsymbol{t}^T \boldsymbol{x} : \boldsymbol{x} \in P \right\}$ .

To reduce a problem of minimizing to one of maximizing, the objective function can be multiplied by -1.

There are three cases that can occur when an LP is tried to be solved:

- 1.  $P = \emptyset$ : the LP is infeasible.

- 2.  $P \neq \emptyset$ , but  $\nexists \sup \{ \boldsymbol{t}^T \boldsymbol{x} : \boldsymbol{x} \in P \}$ : the LP is *unbounded*.

- 3.  $P \neq \emptyset$ , and  $\exists \max \{ \boldsymbol{t}^T \boldsymbol{x} : \boldsymbol{x} \in P \}$ : the LP is *feasible* and has a finite solution.

To find the solution of a linear program, upper bounds of the objective function must be computed. The problem of finding the least upper bound is also an LP that is defined as follows.

**Definition 3.5.5** (Primal and Dual Problem). Let  $\max \boldsymbol{t}^T\boldsymbol{x} : A\boldsymbol{x} \leq \boldsymbol{b}, A \in \mathbb{R}^{m \times d}$ ,  $\boldsymbol{x} \in \mathbb{R}^d_{\geq 0}$  be a linear program. Let this program be called *primal problem*. The *dual problem* is the problem of finding the least upper bound of  $\boldsymbol{t}^T\boldsymbol{x}$ , which is defined as follows:  $\min \boldsymbol{y}^T\boldsymbol{b} : \boldsymbol{y}^T\boldsymbol{A} \geq \boldsymbol{t}^T, \boldsymbol{y} \in \mathbb{R}^m_{>0}$ .

The two following theorems hold (Duality Theorems of Linear Programming):

**Theorem 3.5.1** (Weak Duality). Let  $\bar{\boldsymbol{x}}$  be a feasible solution of the primal problem  $\max \boldsymbol{t}^T \boldsymbol{x} : A\boldsymbol{x} \leq \boldsymbol{b}, A \in \mathbb{R}^{m \times d}, \boldsymbol{x} \in \mathbb{R}^d_{\geq 0}$  and let  $\bar{\boldsymbol{y}}$  be a feasible solution of its dual problem  $\min \boldsymbol{y}^T \boldsymbol{b} : \boldsymbol{y}^T A \geq \boldsymbol{t}^T, \boldsymbol{y} \in \mathbb{R}^m_{\geq 0}$ . Then it holds that:

$$\bar{\boldsymbol{v}}^{\mathrm{T}}\boldsymbol{b} \geq \boldsymbol{t}^{\mathrm{T}}\bar{\boldsymbol{x}}$$

*Proof.* Because  $\bar{x} \ge 0$ ,  $\bar{y} \ge 0$  and  $b \ge A\bar{x}$ , it holds that  $\bar{y}^T b \ge \bar{y}^T A\bar{x}$ . Since  $\bar{y}^T A \ge t^T$ , it follows:  $\bar{y}^T b \ge t^T \bar{x}$ .

**Theorem 3.5.2** (Strong Duality). Let  $\mathbf{x}^*$  be a feasible solution of the primal problem  $\max \mathbf{t}^T \mathbf{x} : A\mathbf{x} \leq \mathbf{b}, A \in \mathbb{R}^{m \times d}, \mathbf{x} \in \mathbb{R}^d_{\geq 0}$  and let  $\mathbf{y}^*$  be a feasible solution of its dual problem  $\min \mathbf{y}^T \mathbf{b} : \mathbf{y}^T A \geq \mathbf{t}^T, \mathbf{y} \in \mathbb{R}^m_{\geq 0}$ . Then it holds that:

$$\mathbf{y}^{*\mathsf{T}}\mathbf{b} = \mathbf{t}^{\mathsf{T}}\mathbf{x}^{*} \iff \mathbf{x}^{*} \text{ and } \mathbf{y}^{*} \text{ are optimal}$$

**Corollary 3.5.1.** *If the primal problem is unbounded, the dual problem is infeasible.*

**Corollary 3.5.2.** If there are feasible solutions of the primal and the dual problems, then there is an optimal solution. The values of the objective function of the two problems are equal for the optimal solution.

The following Simplex algorithm exploits that corollary 3.5.2 can be used to check if a solution  $\boldsymbol{x}$  of the primal problem is optimal. Starting with an initial solution, it improves the solution in each iteration until the following conditions imply optimality:  $\boldsymbol{x}$  is optimal iff  $\exists \boldsymbol{y}$  such that

$$Ax \le b$$

(primal feasible) (3.1)

$$\mathbf{y}^{\mathrm{T}} \mathbf{A} \ge \mathbf{t}^{\mathrm{T}}$$

(dual feasible) (3.2)

$$\mathbf{y}^{\mathrm{T}}(\mathbf{A}\mathbf{x} - \mathbf{b}) = 0 \text{ (complementary)}$$

(3.3)

$$(\mathbf{y}^{\mathrm{T}}\mathbf{A} - \mathbf{t}^{\mathrm{T}})\mathbf{x} = 0 \text{ (slackness)}$$

(3.4)

$$(\mathbf{y}^{\mathrm{T}}\mathbf{A} - \mathbf{t}^{\mathrm{T}})_{i} \cdot \mathbf{x}_{i} = 0 \text{ (binding constraints)}$$

(3.5)

# 3.5.2. Simplex Algorithm

This section introduces a non-formal description of the *Simplex* algorithm, created by George Dantzig in 1947. There is a vast amount of literature about LP solving and the Simplex algorithm available for the interested reader, e.g. [Chvátal, 1983, Schrijver, 1996, Nemhauser and Wolsey, 1988].

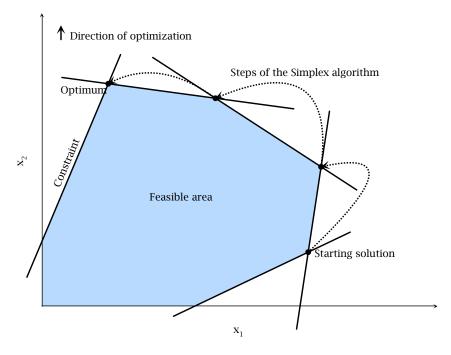

Each constraint of a linear program specifies a half-space in  $\mathbb{R}^d_{\geq 0}$ . Their intersection is the set of all feasible variable assignments. This convex area is either empty, unbounded or a polytope. An optimal solution is found in one of the vertices of this polytope. Starting with an arbitrary vertex, a better solution of the objective function is searched by following one of the outgoing edges of that vertex. This is repeated until no adjacent vertex has a better value, which means that the optimal solution has been found. Figure 3.3 illustrates this algorithm.

Figure 3.3.: The Simplex algorithm in  $\mathbb{R}^2_{\geq 0}$

The Simplex algorithm can be used to solve large problems, since for most constraint systems, its runtime is  $\mathcal{O}(n)$  for n constraints. However, Klee and Minty showed in 1972 that the worst-case runtime is exponential by giving an example (a distortion of an n-dimensional cube) where the Simplex algorithm visits all  $2^n$  vertices before finding the optimal solution (cf. [Chvátal, 1983]), its asymptotic complexity is therefore  $\mathcal{O}(2^n)$ . There are better algorithms from the complexity point of view, e.g. the Ellipsoid method or the Projective

Scaling algorithm by Karmarker, which have polynomial runtime.

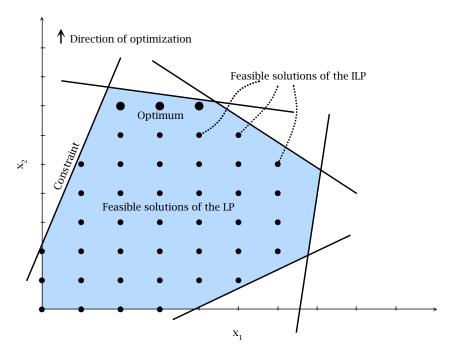

# 3.5.3. Integer Linear Programs

Many problems require the solution of a linear program to be integer, i. e. in definition 3.5.3 on page 24 it must additionally hold that  $\mathbf{x} \in \mathbb{N}_0^d$ .

This type of constraint will be particularly important for the path analysis variants in chapter 4 that use linear programs where the variables of the LP are execution counts of basic blocks or abstract pipeline states, which are naturally integers.

**Definition 3.5.6** (Integer Linear Program). Let  $t \in \mathbb{R}^d$ ,  $b \in \mathbb{R}^m$ ,  $A \in \mathbb{R}^{m \times d}$  be known and constant. An *Integer Linear Program* (ILP) is the task to maximize  $t^T x$  in such a way that  $x \in \mathbb{N}_0^d \wedge Ax \leq b$ .

$$\max \boldsymbol{t}^{\mathrm{T}} \boldsymbol{x} : A \boldsymbol{x} \leq \boldsymbol{b}, \boldsymbol{x} \in \mathbb{N}_0^d$$

The corresponding *relaxed* LP is obtained by omitting the integer requirement:

$$\max \boldsymbol{t}^{\mathrm{T}} \boldsymbol{x} : A \boldsymbol{x} \leq \boldsymbol{b}, \boldsymbol{x} \in \mathbb{R}^{d}_{\geq 0}$$

# 3.5.4. Branch and Bound Algorithm

The basic idea of the Branch and Bound algorithm is to solve the relaxed LP and then split the domain of feasibility into two sub-problems in order to satisfy the demand for integer variables. Each sub-problem is then solved until all variables are integers.

Let  $\Psi$  be an ILP and let  $\Psi'$  be the relaxed problem. If it is feasible, solving  $\Psi'$  yields a solution  $\hat{\mathbf{x}} \in \mathbb{R}^d_{\geq 0}$ .

Figure 3.4.: Domain of feasibility of an ILP (grid points) and the corresponding domain of the relaxed problem (shaded area)

If  $\hat{\boldsymbol{x}} \in \mathbb{Z}^d$ , then  $\hat{\boldsymbol{x}}$  is also a solution for  $\Psi$ . Otherwise, a coordinate  $i \in \{1, ..., n\}$  is chosen such that  $\hat{\boldsymbol{x}}_i \notin \mathbb{Z}$ .  $\Psi'$  is partitioned into the two subproblems  $\tilde{\Psi}_1$  and  $\tilde{\Psi}_2$  by adding one of the following inequalities to  $\Psi'$ :

$$\boldsymbol{x}_i \le \lfloor \hat{\boldsymbol{x}}_i \rfloor \tag{3.6}$$

$$\boldsymbol{x}_i \ge \lceil \hat{\boldsymbol{x}}_i \rceil \tag{3.7}$$

These constraints exclude  $\hat{x}$  as a solution for  $\tilde{\Psi}_1$  and  $\tilde{\Psi}_2$ . This method is repeated until all variables are integers.

#### Chapter

# 4 ILP-based Path Analysis

#### 4.1. ILP

This section describes how an ILP is generated for worst-case path analysis. The first publications about path analysis using implicit path enumeration were [Li et al., 1995, Li and Malik, 1995a, Li and Malik, 1995b]. In the same year, Puschner and Koza compiled a technical report about this topic (*see* [Puschner and Koza, 1995]). The following description is based on the approach that splits the ILP-based path analysis from the micro-architecture analysis. This technique was introduced in [Theiling and Ferdinand, 1998] and improved upon in [Theiling, 2003].

# 4.1.1. Objective Function

The ILP-based path analysis uses nodes  $n \in V$  to represent basic blocks of the source program. Let T((u,v),c) be the length of the longest path from any start state of basic block u to any start state of block v in context c as determined by the combined cache and pipeline analysis (see section 2.1.4). Furthermore, let C(e,c) be the *execution count*, which indicates how often control passes along edge e in context c. If one knows for a specific run of the code the execution counts C(e,c) for each edge e in each context c, then

one can get an upper bound for the time of this run by taking the sum of  $C(e,c) \cdot T(e,c)$  over all edge-context pairs (e,c). Thus, the task of obtaining a global WCET estimation can be solved by finding a feasible assignment of execution counts C(e,c) to edge-context pairs that maximizes the objective function

$$\max: \sum_{(e,c)\in E^*} C(e,c) \cdot T(e,c) \tag{4.1}$$

The value of this sum is then the desired global WCET estimate.

In formula 4.1,  $E^* \subseteq E \times U$  is the set of all edge-context pairs (e, c) that appear in the program, U denotes the set of all contexts. The ILP variables are C(e, c), the values T(e, c) are constant.

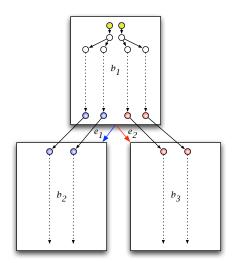

Figure 4.1 illustrates the representation of basic blocks in the integer linear program. It shows three basic blocks  $b_1$ ,  $b_2$  and  $b_3$ , their pipeline state graphs and the edges connecting them. The ILP for this graph would contain variables for the execution counts of the edges  $e_1$  and  $e_2$  in every context c.

Figure 4.1.: Basic blocks with pipeline states and edges

#### 4.1.2. Program Start Constraints

Let  $v_0$  be the start node of the program and  $c_0$  the start context. Since the WCET for *one* execution of the program is to be derived, the sum of the execution counts of all edges leaving  $v_0$  is 1.

$$\sum C((v_0, w), c_0) = 1 \quad \forall (v_0, w) \in E$$

#### 4.1.3. Structural Constraints

For all nodes, we sum up the outgoing and incoming control flow. The following constraints are generated from the CFG:

$$\forall v \in V : \sum_{((u,v),c) \in E^*} C((u,v),c) = \sum_{((v,w),c) \in E^*} C((v,w),c)$$

#### **Infeasible Edges**

The data flow analyses preceding the path analysis are able to find infeasible paths in many cases. For example, the value analysis uses its knowledge about register contents to predict the outcome of conditional branches. If it is able to prove that a branch is either taken or not taken, it marks the other outcome as infeasible.

**Example 4.1.1** (Infeasible Code). Let the input program be the binary program produced by the translation of the following C code:

```

if (i >= 0 && i < 10)

array[i] = i;</pre>

```

#### else

```

printf("Index_out_of_bounds!");

```

Listing 4.1: Infeasible code

Suppose that the register corresponding to the variable i is known to contain a value in the range [0...9] in the analyzed execution context. Then, the basic block corresponding to the else-case is marked as infeasible.

In some cases, the micro-architecture analysis is also able to find infeasible edges, for example if the user tries to resolve a memory access by annotating an address range, but specifies an invalid range. This error will not be detected until the micro-architecture analysis reaches this memory access. As a result, the block containing the invalid access will also be infeasible.

To account for these by preventing that infeasible nodes are considered in the path analysis, an additional constraint is generated for each edge (u, v) leading to a node v that is infeasible in context c:

$$\forall u \in V \text{ s.t.}((u, v), c) \in E^* : C((u, v), c) = 0$$

#### 4.1.4. Loop Constraints

Loop constraints bound the number of iterations of a loop. They are specified as the minimum and maximum number of iterations for each invocation of the loop (i. e. for each calling context c).

**Definition 4.1.1.** Let l be a loop and  $e \in \text{entries}(l)$  one of its entry edges.

The *minimum loop execution count* of l via e in context c is written as  $n_{\min}(e,c)$ .

The *maximum loop execution count* of l via e in context c is written as  $n_{\max}(e,c)$ .

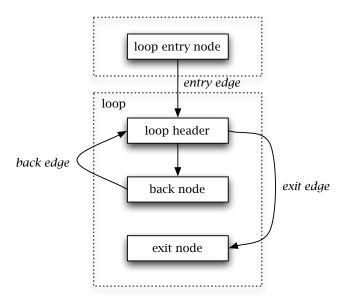

A loop is executed as many times as its header is executed. To limit the number of iterations of the loop per entry, the execution count of the header must be compared to the traversal counts of the loop's entry edges (cf. figure 4.2).

Figure 4.2.: A simple loop with all the important edges

Loop bound constraints are generated as follows for each loop l with loop header h:

$$\sum_{c \in \Gamma(h)} \sum_{n \in \text{succ}(h)} C((h, n), c) \ge \sum_{e \in \text{entries}(l)} \sum_{c \in \Gamma(e)} n_{\min}(e, c) \cdot C(e, c)$$

$$\sum_{c \in \Gamma(h)} \sum_{n \in \text{succ}(h)} C((h, n), c) \le \sum_{e \in \text{entries}(l)} \sum_{c \in \Gamma(e)} n_{\max}(e, c) \cdot C(e, c)$$

where  $\Gamma(n): V \to \mathcal{P}(U)$  is a function that returns the set of possible contexts for a given node in the control flow graph.

The above are simplified loop constraints used to illustrate the concept. The actual implementation uses more complex and more precise constraints which are described in detail in [Theiling, 2003].

# 4.1.5. Time-based Loop Constraints

Some loops cannot be bounded by a fixed number of iterations. Typically, such loops implement some form of busy waiting, i. e. the loops are executed repeatedly while waiting for an external event. A busy waiting loop can be used to block a process until a certain condition is true or to stall the CPU while waiting for an I/O transfer to complete.

```

while (!can_read_io()) {

// wait

}

```

Listing 4.2: Busy waiting loop

In order to bound this type of loop, a user can provide an annotation:

```

snippet routine "main" + 1 loop takes max 42 cycles;

```

For each such annotation, a new constraint is added to the ILP. The constraint bounds a subset of the objective function by the number of cycles given in the annotation.

The final constraint has the form

$$\sum_{x \in L} C(x) \cdot T(x) \le A$$

where A is the time given in the annotation and L contains all edge-context pairs that are reachable when performing a depth-first search starting at the loop's start node and ending at the loop's exit.

#### 4.1.6. User Added Constraints

Users may have additional knowledge about their program which can be used to improve the precision of the WCET analysis, e.g. they might know that two paths are mutually exclusive—a fact which may not be apparent for a static analysis which tries to detect infeasible paths. The framework allows users to add linear constraints to the ILP using annotations which look like the following

flow each

$$c_0 * (pp_0) + ... + c_n * (pp_n)$$

(4.2)

$$= c_{n+1} * (pp_{n+1}) + ... + c_m * (pp_m) + c_{m+1}$$

flow sum  $c_0 * (pp_0) + ... + c_n * (pp_n)$  (4.3)

$$= c_{n+1} * (pp_{n+1}) + ... + c_m * (pp_m) + c_{m+1}$$

Instead of =, the operators  $\leq$  and  $\geq$  may be used as well. The variables  $pp_i$  denote program points given as basic block addresses,  $c_i \in \mathbb{N}$  are constant factors.

The qualifiers each and sum define whether the flow constraint applies to all contexts cumulatively or to each context separately. With sum, the constraint does not apply to the execution counts in individual contexts, but to the sum over the number of executions in all contexts. In contrast, the syntax 4.2 can be used to specify a constraint which applies to each context individually.

## **Example 4.1.2.** Given the following *C* code snippet:

```

if (mode == 0)

do_expensive_calculations();

/* ... */

if (mode == 1)

```

#### do\_other\_stuff();

Listing 4.3: Mode-driven code

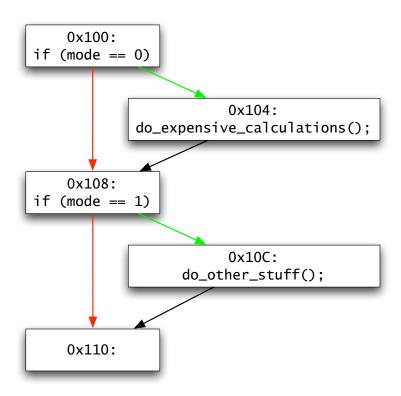

Suppose that the value analysis cannot determine the exact value of the mode variable, e.g. because it is initialized in initialization code which is not part of the analyzed task. The WCET analysis is then unable to deduce that the two calls to do\_expensive\_calculations and do\_other\_stuff are mutually exclusive. The resulting control flow graph is depicted in figure 4.3.

Figure 4.3.: Use-case for user constraints

The worst-case path without additional user-added constraints is given by (0x100, 0x104, 0x108, 0x10C, 0x110) although this path is not feasible (assuming that mode is unchanged in this program). To reduce the overestimation,

the user can add a flow-constraint like

```

flow each (0x104) + (0x10C) = (0x110)

```

The constraint means "in each context, the sum of the execution counts of blocks 0x104 and 0x10C is equal to the execution count of block 0x110". The two possible WCET paths are now (0x100, 0x104, 0x108, 0x110) and (0x100, 0x108, 0x10C, 0x110).

Example 4.1.2 is a common scenario during the analysis of embedded control systems. Many of these systems work in different operating modes such as start-up, stand-by or shut-down. It it also often the case that the same program is deployed on many different systems where each instance uses a different mode which decides which parts of the program should be active for this instance. An introduction to operating mode specific WCET analysis can be found in [Lucas et al., 2009].

A way to detect path exclusions for mode-driven code was presented in [Stein and Martin, 2007] where flow-annotations are generated automatically to improve the precision of the WCET prediction.

Another common use-case for user constraints are non-natural loops, i.e. loops with multiple entry points (rarely generated by compilers, almost only occur with handwritten assembly code). In that case, an annotation

bounds the execution counts of the loop entry points  $entry_i$  by the execution count of a block dom dominating all entries.

# 4.2. Implementation

The ILP-based path analysis in aiT was implemented by Henrik Theiling in 2002 as the tool pathan (short for *path analysis*). It serves as a frontend with a user interface for the libpathan library which contains the algorithms and data structures.

#### Chapter

# 5 Path Analysis on Abstract Pipeline State Graphs

The path analysis on prediction files is a new approach developed by Niklas Matthies in [Matthies, 2006].

A prediction file is an optional output of the pipeline/cache analyzer which describes all possible pipeline states in a condensed form together with the external bus events. This file was mainly meant for comparing hardware traces with aiT predictions.

This abstraction was chosen since using the full representation of the state graphs (including the content of abstract pipeline states) for all basic blocks and all contexts for trace validation seemed to be impossible at that time. It turned out that for applications with moderate size the prediction files might also be used for path analysis, although the graph representation in a prediction file can take more than 1 GB size.

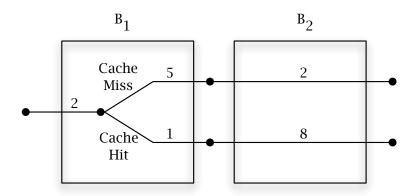

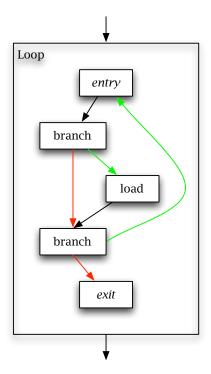

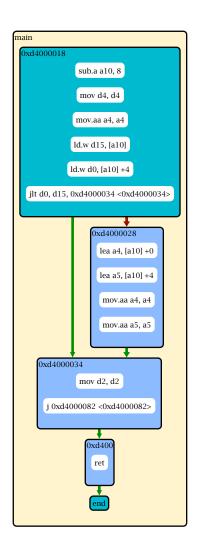

The approach presented in chapter 4 leads to overestimations that result from the way pathan computes the WCET: for each basic block the maximum number of cycles is calculated that are spent in the instructions contained in the basic block. This does not take into account that it might not be possible to spend the maximal number of cycles in each of two consecutive basic blocks (see figure 5.1).

The computed WCET using path analysis on prediction files should always be less or equal the global WCET computed with pathan in combination with an ILP solver. The overestimations which are avoided by the path analysis on prediction files are those, where the cache/pipeline analysis splits the states due to unknown states of the processor, e.g. due to unknown cache states as it can be seen in figure 5.1. The pathan approach for this example calculates a WCET of 2+5+8=15 whereas the method based on prediction files calculates 2+1+8=11.

Figure 5.1.: Split due to unknown cache state

As mentioned in section 2.1.4 on page 8, the local WCET analysis avoids some of the splits due to unknown states and follows only the case taking locally more cycles, which is a cache miss in this example. But in some cases, it is locally undecidable, which decision will be the local worst-case, so there are still some split events left. Table 5.1 on the next page shows in which cases the local WCET analysis also splits, exemplified by the micro-architecture analysis for the Motorola MPC755.

| Event                                                 | Split        |

|-------------------------------------------------------|--------------|

| Cache hit or miss                                     | Х            |

| Cache clash                                           | X            |

| Cache manipulation                                    | $\checkmark$ |

| Inexact jitter                                        | X            |

| Inexact PCI jitter                                    | X            |

| Optiondata-wait=perhaps (not default)                 | $\checkmark$ |

| Unknown SDRAM tag register                            | X            |

| Imprecise SDRAM access                                | $\checkmark$ |

| Instruction DCBT (Data Cache Block Touch)             | $\checkmark$ |

| Instruction DCBTST (Data Cache Block Touch for Store) | $\checkmark$ |

| Instruction DCBST (Data Cache Block Store)            | X            |

| Instruction DCBF (Data Cache Block Flush)             | X            |

| Arithmetic operations (IU1, IU2, SRU)                 | X            |

| Unknown branch prediction                             | ✓            |

Table 5.1.: Splits during local WCET analysis for the MPC755

Due to the fact that the pipeline analysis also splits while computing the local worst-case, the problem described in figure 5.1 may still arise. Thus, the WCET computed by the path analysis on prediction files may be smaller than the WCET computed by pathan using the local worst-case option of the pipeline.

# 5.1. Prediction Files

The state graph generated by the micro-architectural analysis is stored in a so-called *prediction file*. The syntax of this textual file is defined in table 5.2 starting on page 46. It contains a sequence of the following types of elements:

**Normal edges** These elements (non-terminal *normal\_edge*) describe an edge in the abstract pipeline state graph and consist of the IDs of the source

and target nodes, the execution time for this edge (in CPU cycles) and optionally the addresses of the associated basic block and instruction, the execution context as well as a list of events. If the code location for an edge is not specified, it belongs to the same location as the previous edge. The event list is not relevant for path analysis and is used by other tools which work on prediction files.

**Subsume edges** The pipeline analysis connects two states with a subsume edge (non-terminal *subsume\_edge*) if an abstract state is subsumed by another abstract state (i. e. it is a subset of the other state). Subsume edges are similar to normal edges with an execution time of zero.

**Node aliases** Aliases (non-terminal *equal\_node*) are generated by the microarchitectural analysis to identify two nodes with the same abstract state. They consist of two node IDs where the first occurs for the first time and now represents an alias for the second ID. The first node ID is called *alias node*, the second *referenced node*.

**Start/end markers** These elements (*node\_start*, *node\_end*, *edge\_start* and *edge\_end*) represent the start and end of the current CFG item<sup>1</sup>, respectively.

**End of block** This element (non-terminal *basic\_block\_end*) marks the end of the current basic block.

The formal grammar of the prediction file format is given below:

| start | $\rightarrow$ | items      |

|-------|---------------|------------|

| items | $\rightarrow$ | item items |

|       |               | ε          |

| item  | $\rightarrow$ | node       |

|       |               | edge       |

|       | 1             | marker     |

continued on next page

<sup>&</sup>lt;sup>1</sup>here: either a node or an edge in the control flow graph.

## continued from previous page

| node            | $\rightarrow$ | start_node                              |  |  |

|-----------------|---------------|-----------------------------------------|--|--|

|                 |               | equal_node                              |  |  |

|                 |               | keep_node                               |  |  |

|                 |               | final_node                              |  |  |

| start_node      | $\rightarrow$ | S id                                    |  |  |

| equal_node      | $\rightarrow$ | E <i>id1</i> : <i>id2</i>               |  |  |

| keep_node       | $\rightarrow$ | k <i>id</i>                             |  |  |

| final_node      | $\rightarrow$ | F id                                    |  |  |

| marker          | $\rightarrow$ | node_start                              |  |  |

|                 |               | node_end                                |  |  |

|                 |               | edge_start                              |  |  |

|                 |               | edge_end                                |  |  |

|                 |               | basic_block_end                         |  |  |

| node_start      | $\rightarrow$ | n node_id : context                     |  |  |

| node_end        | $\rightarrow$ | N                                       |  |  |

| edge_start      | $\rightarrow$ | t edge_id : context                     |  |  |

| edge_end        | $\rightarrow$ | T                                       |  |  |

| basic_block_end | $\rightarrow$ | В                                       |  |  |

| edge            | $\rightarrow$ | normal_edge                             |  |  |

|                 |               | subsume_edge                            |  |  |

| normal_edge     | $\rightarrow$ | e id1 d id2 c num code_info events      |  |  |

| code_info       | $\rightarrow$ | i adr1                                  |  |  |

|                 |               | i adr1, adr2                            |  |  |

|                 |               | i adr1, adr2, ctx                       |  |  |

| events          | $\rightarrow$ | event events                            |  |  |

|                 |               | ε                                       |  |  |

| event           | $\rightarrow$ | tstart                                  |  |  |

|                 |               | tack                                    |  |  |

|                 |               | aack                                    |  |  |

|                 |               | cache                                   |  |  |

| tstart          | $\rightarrow$ | S a1, a2 1 len access_type segment_type |  |  |

continued on next page

#### continued from previous page

```

access_type

W

segment_type

C

d

tack

|a

| A

aack

cache

→ | c cache_event_list

cache_events

→ cache_event , cache_events

cache_type access_type a1, a2, s1, s2

cache_event

cache_type event_type abstract_cache tag

cache_type

d

event_type

e

1

abstract_cache

s id1 : id2

subsume_edge

```

Table 5.2.: Prediction file syntax

The abstract pipeline state graph G = (V, E, C) can be reconstructed from the prediction file as follows:

- an abstract pipeline state  $v \in V$  is represented by an integer identifier, i. e.  $V \subset \mathbb{N}$ . The actual content of the abstract state including the abstract cache state is not needed for path analysis.

- an edge (u, v) is part of E if either a normal or a subsume edge connect the two state identifiers u and v.

- the cost C(e) of an edge e is either 0 if e is a subsume edge or the number of CPU cycles as given in the prediction file.

# 5.2. Implementation

The implementation of the path analysis on abstract pipeline state graphs in the modular analysis framework aiT is called predan and was described in [AbsInt Angewandte Informatik GmbH, 2006a]. It exploits the facts that the pipeline state graph modulo loops is a *DAG* (directed acyclic graph) and that the edges in the prediction file occur in topological order. Given those two prerequisites, it can employ a very fast algorithm based on depth-first search to find the longest path.

#### Chapter

# 6 ILP-based Path Analysis on Abstract Pipeline State Graphs

Following the introduction of the existing path analyses and the theoretical background, this chapter represents the core of this thesis and presents the newly developed path analysis.

While predan is very fast because it uses a depth-first search on the state graph, it does not allow the user to specify additional constraints in the AIS annotations. The new approach combines the advantages of both methods, i. e. it is now possible to use user constraints together with the path analysis on prediction files.

However, the analysis time is expected to increase by an order of magnitude (dominated by the time it takes the ILP solver to solve the ILP).

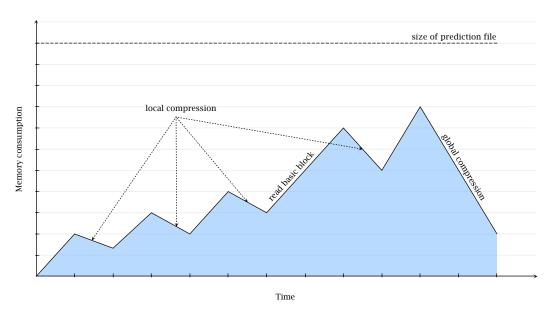

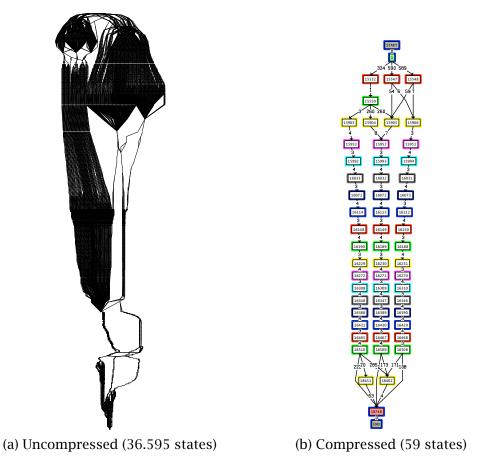

The prediction files can become very large even for medium-sized programs. Therefore, predpathan employs several techniques to compress the pipeline state graph. The compression algorithms reduce the complexity of the state graph (and therefore of the ILP) in ways that do not alter the WCET path. In the absence of user constraints, predpathan produces the exact same result

as the predan approach.

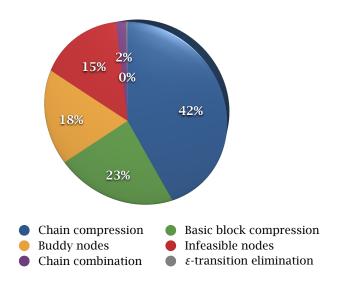

# 6.1. Graph Compression

The following graph compression methods substitute subgraphs of the abstract pipeline state graph  $S \subset G$  with equivalent subgraphs S' so that  $G' = (G \setminus S) \cup S'$  and

$$wcet(G') = wcet(G)$$

(6.1)

**Definition 6.1.1** (In-Edges). The *in-edges* in(n) of a node  $n \in V$  are defined as

$$\operatorname{in}(n) = \{(m, n) \in E\}$$

**Definition 6.1.2** (out-Edges). The *out-edges* out(n) of a node  $n \in V$  are defined as

$$\operatorname{out}(n) = \{(n, m) \in E\}$$

**Definition 6.1.3** (In-Degree). The *in-degree* indeg(n) of a node  $n \in V$  is defined as

$$indeg(n) = |in(n)|$$

**Definition 6.1.4** (Out-Degree). The *out-degree* outdeg(n) of a node  $n \in V$  is defined as

$$\operatorname{outdeg}(n) = |\operatorname{out}(n)|$$

**Definition 6.1.5** (Extended Graph). The *extended graph*  $G^*$  of a graph  $G = G^*$

(V, E) is given by  $G^* = (V^*, E^*)$ , where

```

V^* \coloneqq V \cup \{s, e\}

E^* \coloneqq E

\cup \{(s, s') : s' \in V \land \operatorname{indeg}(s') = 0\}

\cup \{(e', e) : e' \in V \land \operatorname{outdeg}(e') = 0\}

s \notin V

e \notin V

```

That is, the graph *G* is extended by a new start node *s* which has edges to all nodes which have no predecessor and a new end node *e* which is connected to all nodes which have no successor.

For each compression method, a proof is given that condition 6.1 holds by showing that the same is true for the respective extended graphs  $S^*$  and  $S'^*$ .

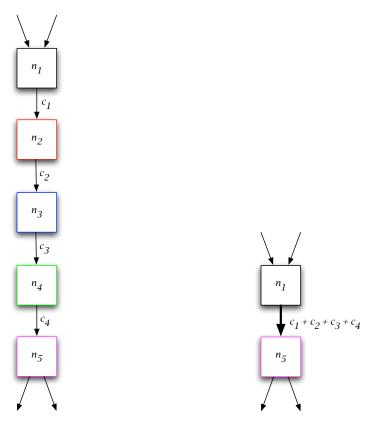

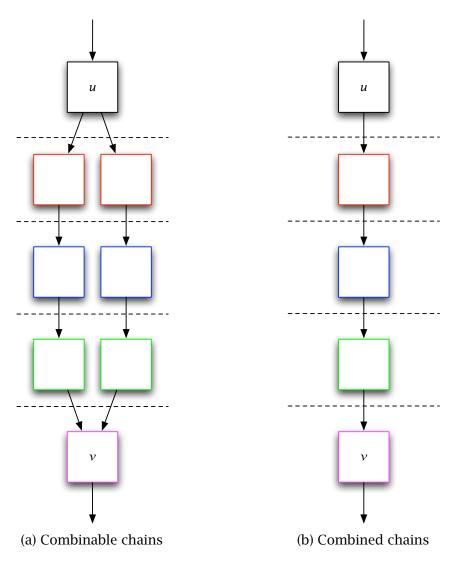

## 6.1.1. Chain Compression

The pipeline analysis can produce long chains of states which resemble the cyclewise evolution of the pipeline. A chain of states which have a single predecessor and a single successor can be merged into two states: one state for the start of the chain and one for the end of the chain. The cost of the edge between the start and end node is the sum of the edge weights on the chain.

**Definition 6.1.6** (Chain Compression). The sequence of nodes  $n_1, \ldots, n_x \in V$

is called a *compressible chain* of length x > 2, iff

$$\operatorname{succ}(n_i) = \{n_{i+1}\} \quad \forall 1 \le i \le x - 1$$

$\operatorname{pred}(n_i) = \{n_{i-1}\} \quad \forall 2 \le i \le x$

A subgraph S for the chain compression consists of the nodes in a compressible chain and the edges connecting them, i. e.

$$S = (\{n_1, \dots, n_x\}, \{(n_i, n_{i+1}) : 1 \le i \le x - 1\})$$

It is replaced by S' where

$$S' = (\{n_1, n_x\}, \{(n_1, n_x)\})$$

and

$$C'((n_1, n_x)) = \sum_{1 \le i \le x-1} C((n_i, n_{i+1}))$$

#### Correctness

Claim.

$$wcet(S^*) = wcet(S'^*)$$

*Proof.* Let  $n_1, \ldots, n_x$  be a chain of length x > 2. Then

$$\begin{aligned} \text{wcet}(S^*) &= \sum_{i \in \text{in}(n_1)} C(i) + \sum_{1 \le i \le x - 1} C((n_i, n_{i+1})) + \sum_{o \in \text{out}(n_x)} C(o) \\ &= \sum_{i \in \text{in}(n_1)} C(i) + C'(n_1, n_x) + \sum_{o \in \text{out}(n_x)} C(o) \\ &= \text{wcet}(S'^*) \end{aligned}$$

#### **Runtime**

In order to find the chains in an abstract pipeline state graph G, the algorithm only needs to look at each node  $n \in V$  once, because it can easily be checked if n is part of a chain. n is removed by the chain compression, iff  $\operatorname{indeg}(n) = \operatorname{outdeg}(n) = 1$ . Therefore, the runtime of the compression method is  $\mathcal{O}(|V|)$ .

**Example 6.1.1.** Figure 6.1 shows the effect of the chain compression.

- (a) Subgraph before applying the chain compression

- (b) Subgraph after applying the chain compression

Figure 6.1.: Chain compression example

# 6.1.2. Basic Block Compression

For each basic block b and one of its contexts c, the basic block graph  $G_{b,c}$  is the part of the state graph that lies in b and belongs to context c. Each basic block graph is a weighted directed acyclic graph (DAG). For the purposes of path analysis, it can be reduced to a graph which consists only of the start and end nodes of the basic block connected by edges which represent the longest paths between them. The DAG-property allows to use a very fast multiple-sources multiple-targets longest-path algorithm.

The algorithm begins by sorting the basic block graph topologically.

**Definition 6.1.7** (Topological Ordering). A *topological ordering* of a graph is a total ordering of its nodes which is compatible with the partial order R induced on the nodes where x comes before y (x R y) if there is a directed path from x to y in the graph.

**Theorem 6.1.1.** A graph has a topological ordering if and only if it is a directed acyclic graph.

The sorting algorithm is based on depth-first search:

## Algorithm 1 Topological sort

- 1: run DFS(G), computing finish time f[v] for each vertex v

- 2: As each vertex is finished, insert it onto the front of a list

- 3: return the list

Runtime  $\Theta(|V| + |E|)$

# Algorithm 2 Depth-first search

```

1: procedure DFS(G)

for all u \in V(G) do

color[u] = white

3:

4:

end for

time = 0

5:

for all u \in V(G) do

6:

if color[u] == white then

7:

DFSVisit(u)

8:

end if

9:

end for

10:

11: end procedure

1: procedure DFSVisit(u)

2:

color[u] = gray

d[u] = ++time

3:

for all v \in adj(u) do

4:

if color[v] == white then

5:

\mathsf{DFSVisit}(v)

6:

7:

end if

color[u] = black

8:

f[u] = ++time

9:

end for

10:

11: end procedure

```

```

Runtime \Theta(|V| + |E|)

```

After sorting the graph, the longest paths can be computed be repeatedly solving the single-source multiple-targets longest-path problem for each start node s with indeg(s) = 0 in the basic block graph:

#### Algorithm 3 Single-source multiple-targets longest-path

```

1: procedure SSMT(G, s)

2:

for all vertex y \in G do

d(s, y) = \infty

3:

▶ initialization

end for

4:

d(s,s) = 0

5:

for all vertex \gamma in a topological ordering of G do

6:

choose edge (x,y) maximizing d(s,x) + C((x,y))

7:

d(s,y) = d(s,x) + C((x,y))

8:

end for

9:

10: end procedure

```

Runtime  $\mathcal{O}(|V| + |E|)$ .

# Algorithm 4 Multiple-sources multiple-targets longest-path

```

procedure MSMT(G)

for all vertex s ∈ G with indeg(s) = 0 do

compute SSMT(G, s)

end for

end procedure

```

Runtime  $\mathcal{O}(|S| \cdot (|V| + |E|))$  where  $S = \{n \in V : \text{indeg}(n) = 0\}$ .

The results of the multiple-sources multiple-targets longest-path algorithm are stored in d(x, y) where  $d(x, y) = \infty$  means that y is not reachable from x, otherwise d(x, y) contains the cost of the longest path from x to y.

Formally, the basic block compression can be defined as follows: let  $G_{b,c} = (V_{b,c}, E_{b,c})$  be the basic block graph. Then,  $G'_{b,c} = (V'_{b,c}, E'_{b,c})$  is derived from

*G* where

$$V'_{b,c} = \{v \in V_{b,c} : \text{indeg}(v) = 0 \lor \text{outdeg}(v) = 0\}$$

$$E'_{b,c} = \{(s,e) \in V^2_{b,c} : \text{indeg}(s) = \text{outdeg}(e) = 0 \land d(s,e) \neq \infty\}$$

$$C'((s,e)) = d(s,e) \quad \forall (s,e) \in E'_{b,c}$$

The correctness of the graph substitution follows directly from the construction and the correctness of the multiple-sources multiple-targets longest-path algorithm.

#### 6.1.3. Infeasible Nodes

The pipeline analysis can mark nodes as infeasible when it finds out that a path results in inconsistent states, that is, abstract states which have no corresponding concrete state. This often occurs when the pipeline analysis handles a branch instruction and splits the abstract pipeline state for each possible successor. When the branch is resolved, all states except the one with the correctly predicted successor are marked as infeasible.

The infeasible nodes are removed from the ILP along with all paths only leading to infeasible nodes, i. e. the infeasible property is propagated backwards:

#### **Algorithm 5** Purge infeasible nodes

```

1: while \exists i \in \text{infeasible do}

V = V \setminus \{i\}

infeasible = infeasible \setminus \{i\}

3:

for all (x, i) \in E do

4:

E = E \setminus \{(x, i)\}

5:

if outdeg(x) = 0 then

6:

infeasible = infeasible \cup \{x\}

7:

end if

8:

end for

9:

10: end while

```

#### 6.1.4. $\varepsilon$ -transition Elimination

Edges with 0 cost (e.g. subsume edges) are removed from the ILP by merging the nodes connected by them.

## 6.1.5. Buddy Nodes

**Definition 6.1.8.** The function pred :  $V \to \mathcal{P}(V)$  computes the *predecessors* of a node  $n \in V$ :

```

pred(n) = \{v : (v, n) \in E\}

```

The *successors* are defined analogously by succ :  $V \rightarrow \mathcal{P}(V)$ :

```

\operatorname{succ}(n) = \{v : (n, v) \in E\}

```

Nodes which have the same set of predecessors or successors with equal edge costs are called *buddy nodes* and can be merged.

$$M_{\text{pred}} = \{(u, v) : u, v \in V \land \text{pred}(u) = \text{pred}(v) \land C_{\text{pred}(u, v)}\}$$

$$M_{\text{succ}} = \{(u, v) : u, v \in V \land \text{succ}(u) = \text{succ}(v) \land C_{\text{succ}(u, v)}\}$$

where the two predicates  $C_{\text{pred}}: V^2 \to \mathbb{B}$  and  $C_{\text{succ}}: V^2 \to \mathbb{B}$  are defined as:

$$C_{\operatorname{pred}(x,y)} \coloneqq \forall z \in \operatorname{pred}(x) : C((z,x)) = C((z,y))$$

$$C_{\operatorname{succ}(x,y)} \coloneqq \forall z \in \operatorname{succ}(x) : C((x,z)) = C((y,z))$$

Update for  $(u, v) \in M_{\text{succ}}$ :

$$V' = V \setminus \{v\}$$

$$E' = E \setminus \{(x, y) \in E : x = v \lor y = v\} \cup \{(x, u) : x \in \operatorname{pred}(v)\}$$

$$C'((x, u)) = \begin{cases} C((x, v)) & x \in \operatorname{pred}(v) \land x \notin \operatorname{pred}(u) \\ \max(C((x, u)), C((x, v))) & x \in \operatorname{pred}(v) \land x \in \operatorname{pred}(u) \end{cases}$$

Analog update for  $(u, v) \in M_{\text{pred}}$ .

#### **Runtime**

In order to find buddy nodes in an abstract pipeline state graph, the algorithm does not need to compare each node  $n \in V$  with each other node to check if they are buddy nodes. Instead, it can test the *in-siblings* and *out-siblings*: