Dissertation

# SIMD Code Generation in Data-Parallel Programming

Nicolas Fritz

Saarbrücken, 01.06.2009

Zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

| Tag des Kolloquiums:      | 21.10.2009                                                               |

|---------------------------|--------------------------------------------------------------------------|

| Dekan:                    | Prof. Dr. Joachim Weickert                                               |

| Prüfungsausschuss:        |                                                                          |

| Vorsitzender:             | JunProf. Dr. Sebastian Hack                                              |

| Gutachter:                | Prof. Dr. Dr. h.c. mult. Reinhard Wilhelm<br>Prof. Dr. Philipp Slusallek |

| Akademischer Mitarbeiter: | Dr. Philipp Lucas                                                        |

Impressum Copyright © 2009 by Nicolas Fritz Herstellung und Verlag: epubli GmbH, Berlin, www.epubli.de Printed in Germany ISBN: 978-3-86931-240-8

Bibliografische Information der Deutschen Nationalbibliothek Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

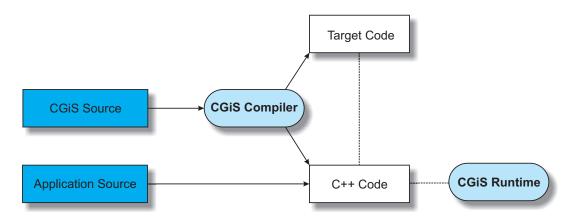

#### Abstract

Today's desktop PCs feature a variety of parallel processing units. Developing applications that exploit this parallelism is a demanding task, and a programmer has to obtain detailed knowledge about the hardware for efficient implementation. CGIS is a data-parallel programming language providing a unified abstraction for two parallel processing units: graphics processing units (GPUs) and the vector processing units of CPUs. The CGIS compiler framework fully virtualizes the differences in capability and accessibility by mapping an abstract data-parallel programming model on those targets. The applicability of CGIS for GPUs has been shown in previous work; this work focuses on applying the abstract programming model of CGIS to CPUs with SIMD (Single Instruction Multiple Data) instruction sets. We have identified, adapted and implemented a set of program analyses to expose and access the available parallelism. The code generation phase is based on selected optimization algorithms tailored to SIMD code generation. Via code generation profiles, it is possible to adapt the code generation strategy to different target architectures. To assess the effectiveness of our approach, we have implemented backends for the two most widespread SIMD instruction sets, namely Intel's Streaming SIMD Extensions and Freescale's AltiVec. Additionally, we integrated a prototypical backend for the Cell Broadband Engine as an example for a multi-core architecture. Our experimental results show excellent average performance gains by a factor of 3 compared to standard scalar C++ implementations and underline the viability of this approach: real-world applications can be implemented easily with CGIS and result in efficient code.

#### Zusammenfassung

Parallelverarbeitung wird heutzutage in handelsüblichen PCs von einer Reihe verschiedener Komponenten unterstützt. Grafikprozessoren (GPUs) und Vektoreinheiten in CPUs sind zwei dieser Komponenten. Da die Entwicklung von Anwendungen, die diese Parallelität nutzen, eine anspruchsvolle Aufgabe ist, muss sich ein Programmierer detaillierte Kenntnisse der internen Hardwarestruktur aneignen. Mit CGIS stellen wir eine datenparallele Programmiersprache vor, die eine gemeinsame Abstraktion für Grafikprozessoren und Vektoreinheiten in CPUs bietet und ein einheitliches Programmiermodell für beide bereitstellt. In vorherigen Arbeiten haben wir bereits die Nutzbarkeit von CGIS für GPUs gezeigt. In der vorliegenden Arbeit bilden wir das abstrakte Programmiermodel von CGIS auf CPUs mit SIMD (Single Instruction Multiple Data) Instruktionssatz ab. Wir haben eine Reihe relevanter Programmanalysen angepasst und implementiert um Parallelität aufzudecken und zu nutzen. Die Codegenerierungsphase basiert auf ausgewählten Optimierungsalgorithmen, die speziell auf die Generierung von SIMD-Code zugeschnitten sind. Durch Profile für verschiedene Architekturen ist es uns möglich, die Codegenierung zu steuern. Um die Effektivität unseres Ansatzes unter Beweis zu stellen, haben wir Backends für die beiden am weitesten verbreiteten SIMD-Instruktionssätze implementiert: Die "Streaming SIMD Extensions" von Intel und AltiVec von Freescale. Zusätzlich haben wir ein prototypisches Backend für den Cell Prozessor von IBM, als Beispiel für eine Multi-Core-Architektur, integriert. Die Ergebnisse unserer Experimente belegen eine ausgezeichnete durchschnittliche Beschleunigung um einen Faktor von 3 im Vergleich zu handgeschriebenen C++-Implementierungen. Diese Resultate untermauern unseren Ansatz: Mittels CGIS lässt sich leistungsstarker Code für SIMD- und Multi-Core-Applikationen generieren.

#### Extended Abstract

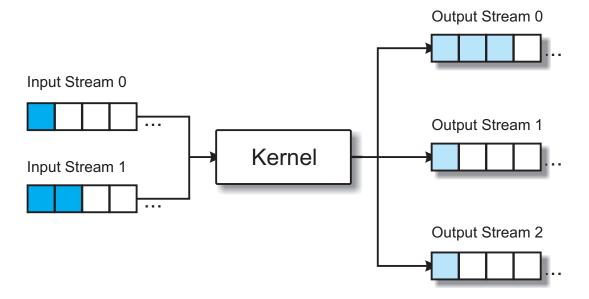

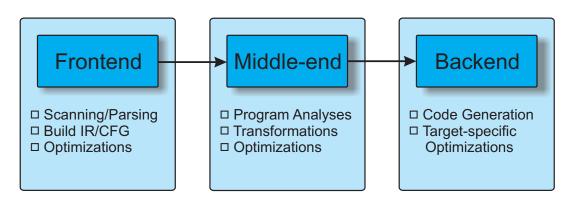

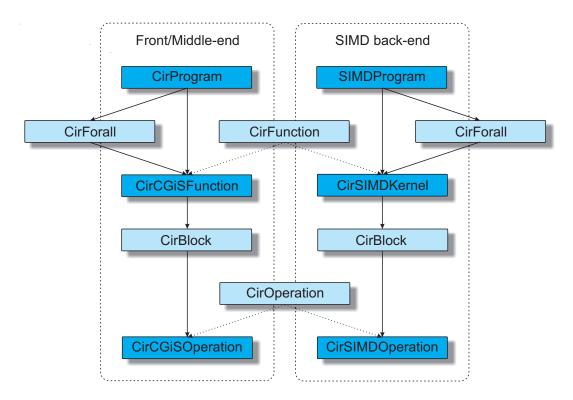

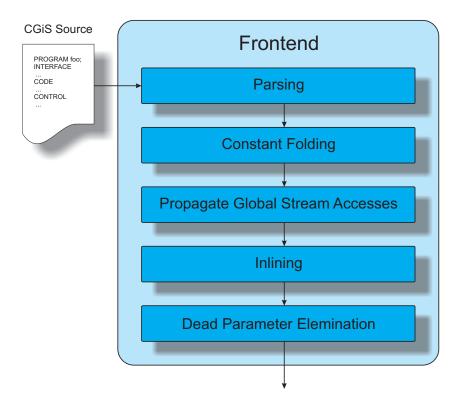

The development of desktop processor technology is moving away from a constant increase in clock rate, towards increased parallelism. Recent PCs contain a set of parallel processing units, the two most prominent of which are the Graphic Processing Units (GPUs), and the SIMD (Single Instruction Multiple Data) units in CPUs. While this parallelism is available, its exploitation is still a demanding task. Compilers for traditional sequential programming languages like C, C++ or Fortran include a multitude of vectorization techniques, i.e. methods to find parallelism inside a sequential program and possibly transform it to fit the parallel hardware while preserving the program's semantics. Yet the success of these methods remains marginal. Direct programming via assembler or intrinsics, on the other hand, requires detailed knowledge of the hardware intricacies, and afflicts maintainability and portability. The source of the problem is the use of a sequential programming language. Therefore we designed a data-parallel programming language based on a stream programming model called CGIS. It offers a unified abstraction for GPUs and the vector processing units of CPUs. The language features explicit parallelism, rendering the search for parallelism and some program transformations to access it, redundant. The task of a CGIS compiler is less finding parallelization opportunities than just mapping them to the hardware. This allows for generating efficient code.

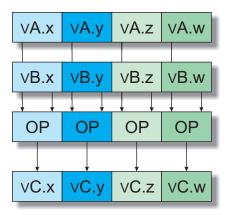

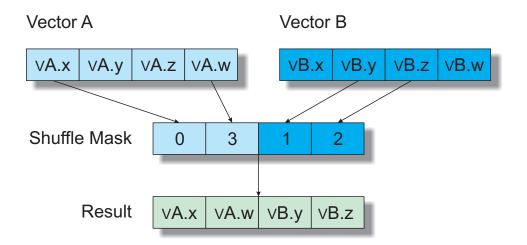

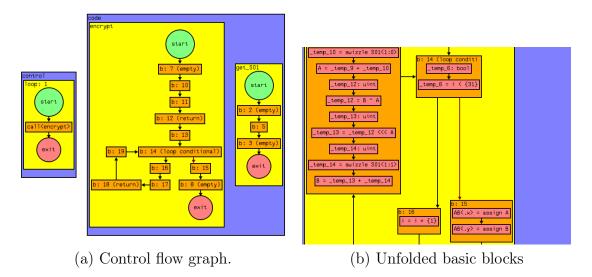

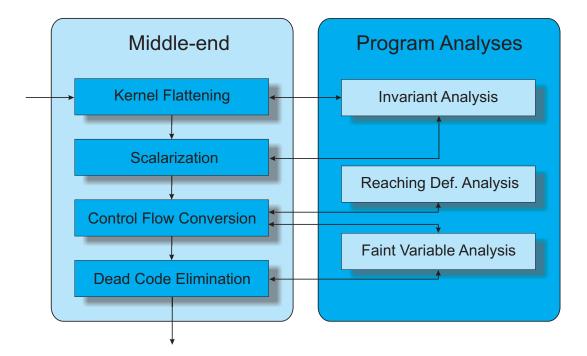

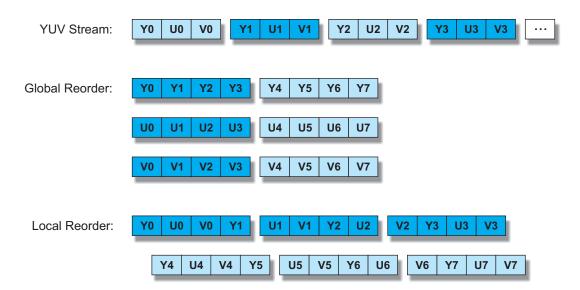

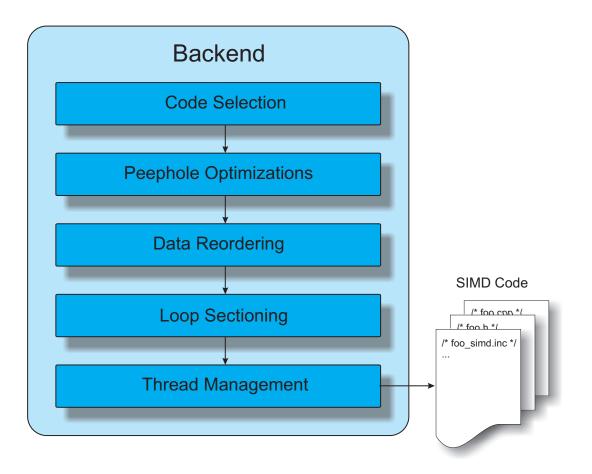

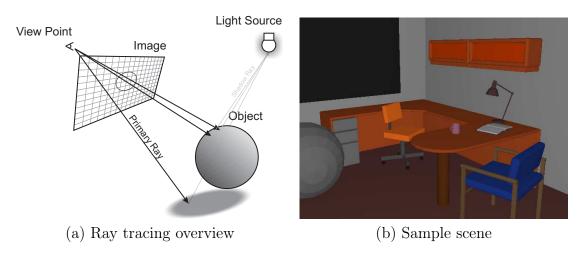

In earlier work we have presented a GPU backend for the CGIS compiler and demonstrated that CGIS is a viable language for data-parallel programming. There are two kinds of parallelism in CGIS: parallel loops iterating over streams and small vectorial data types. The latter stem from CGIS' intended closeness to graphics hardware programming languages. The mapping of these two types of parallelism to GPU hardware is a one-to-one mapping as they contain up to 128 units all working on 4-component data registers. This thesis focuses on CPUs with SIMD units covering the most relevant architectures, namely Intel's Streaming SIMD Extensions and Freescale's AltiVec and, as an example for multi-core architectures, the IBM's Cell Broadband Engine. In contrast to GPUs, the SIMD units presented here only contain the 4-way parallelism introduced by the SIMD registers. We have developed a special transformation called *kernel flat*-

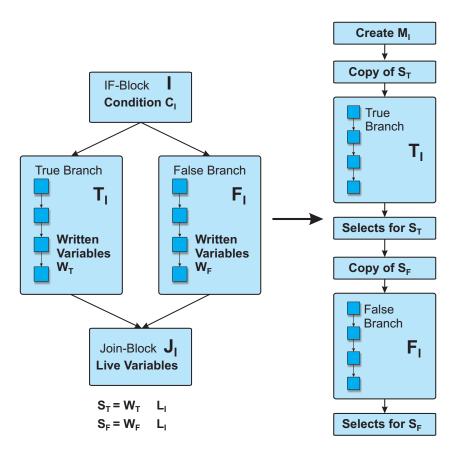

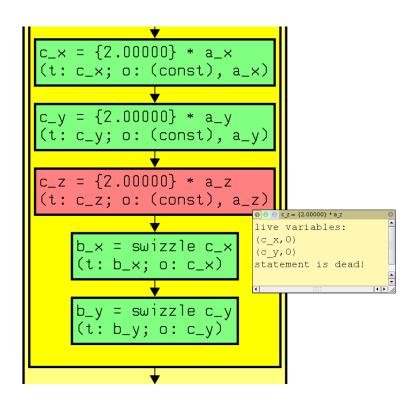

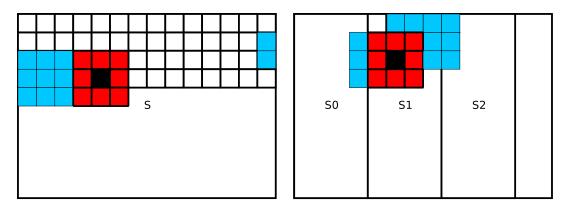

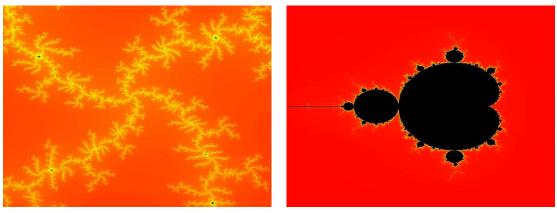

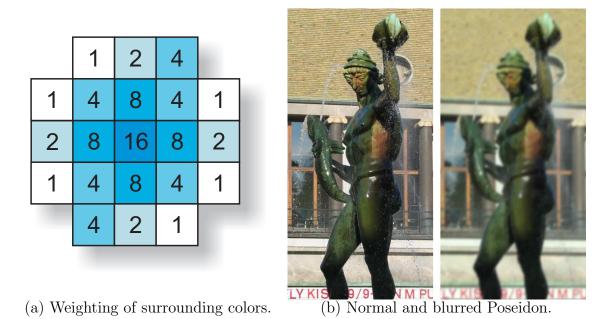

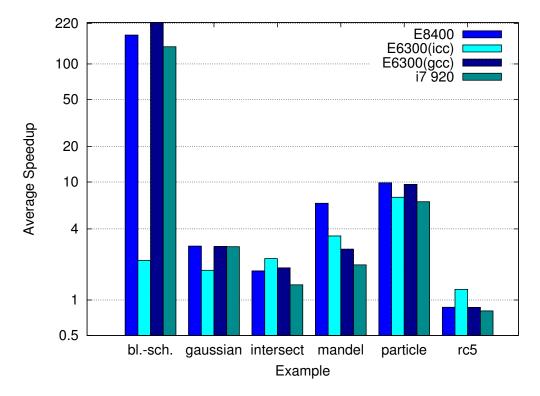

*tening*: by breaking down vector-type data structures and operations to scalar ones, the parallelism induced by parallel stream iterations can be mapped to SIMD hardware. Another difference between SIMD CPUs and GPUs is the presence of caches. GPUs have a fast texture memory attached, while CPUs use caches to hide memory latencies and increase the access speed of re-used data. For algorithms with neighboring operations, e.g. accesses to adjacent stream elements in two-dimensional streams, caches have to be utilized to maintain increased performance with a CGIS implementation. We integrated a form of *loop sectioning* to achieve this goal. In conjunction with kernel flattening the *control flow conversion* becomes crucial, i.e. control dependencies are replaced by data-dependencies. In the SIMD backends of the CGIS compiler, if and loop-constructs are fully converted to enable parallel execution. To show the viability of CGIS for implementing applications for CPUs featuring SIMD units, we examine six real-world examples. These examples comprise data-parallel algorithms from the fields of mathematical exploration, computer graphics, financial simulation, etc. A standard C++ implementation is then compared to parallel implementations generated with the CGIS compiler. Speedups by a factor of 3 and more can be observed.

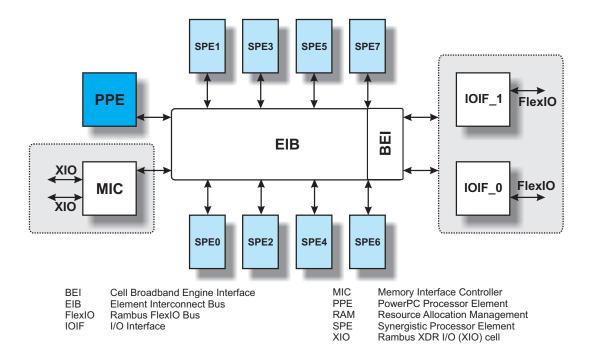

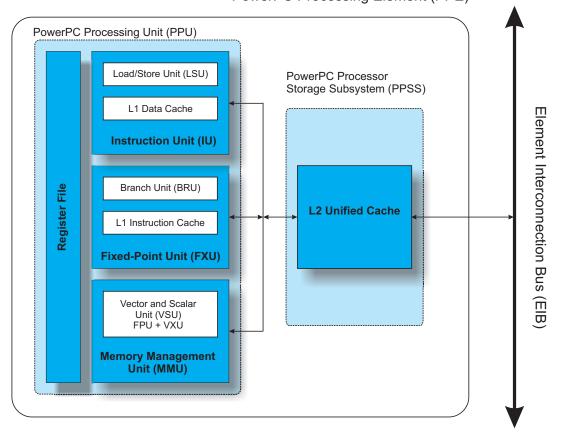

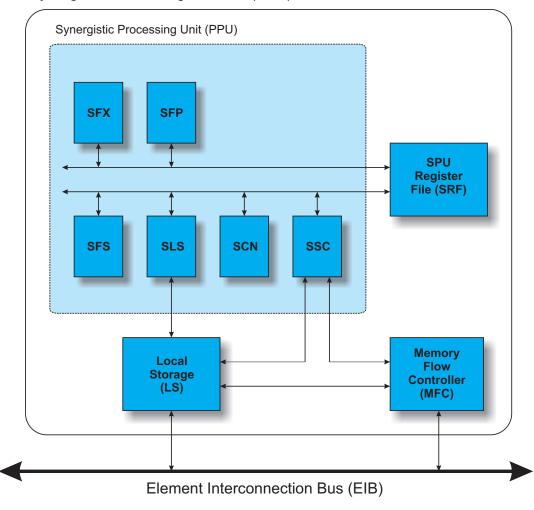

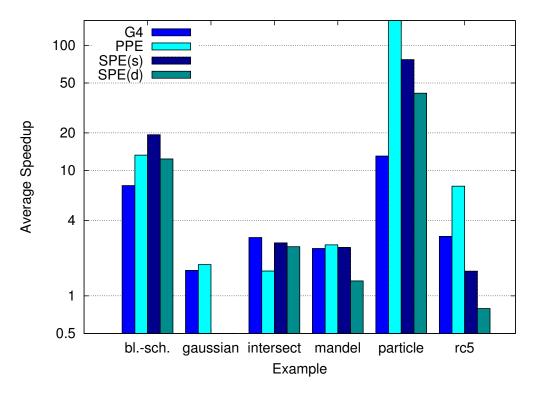

Additionally, we examined the performance of CGIS and its compiler on multi-core architectures. As a representative, the Cell Broadband Engine was chosen. It contains a Power Processing Entity (PPE), which is based on the Power Architecture, and eight Synergistic Processing Elements (SPEs). The SPEs are connected to the PPE, each other and the main memory via the Element Interconnection Bus (EIB) and can work independently. Having so much computational power at hand, the distribution of the computations to the single entities is very important. We have investigated a static and a dynamic approach to balance the work load on the SPEs in threaded execution and compared those to standard execution on the PPE by reutilizing the examples mentioned above. For CGIS multi-core solutions tangible speedups can be observed, ranging from a factor of 1.5 to a factor of 70, depending on the characteristics of the data-parallel algorithm. To be effective very high arithmetic density is needed.

#### Erweiterte Zusammenfassung

In der Entwicklung von Prozessoren (CPUs) für PCs gibt es einen Trend weg von der Erhöhung der Taktrate hin zur Erweiterung der Parallelität. Es gibt verschiedene Arten paralleler Hardware in Arbeitsplatzrechnern. Die beiden bekanntesten sind Grafikprozessoren (GPUs) auf Grafikkarten und SIMD-Einheiten (Single Instruction Multiple Data) in CPUs. Diese parallele Rechenleistung ist zwar vorhanden, ihre Nutzung jedoch ein schwieriges Unterfangen. Handelsübliche Übersetzer für sequentielle Programmiersprachen wie C, C++ oder Fortran besitzen eine Vielzahl verschiedenster Vektorisierungstechniken um Parallelität innerhalb eines sequentiellen Programms aufzudecken und ihn auf die Zielarchitektur abzubilden, ohne dabei die Semantik des Programms zu verändern. Meist bieten diese Methoden allerdings nur geringen Erfolg, da bereits die Benutzung einer sequentiellen Programmiersprache eine schwerwiegende Einschränkung darstellt. Aus diesem Grund haben wir eine datenparallele Programmiersprache mit expliziter Parallelität entworfen, genannt CGIS. Basierend auf einem Datenstrom-Programmiermodell bietet CGIS explizite Parallelität und macht damit das Suchen von Parallelität und damit verbundene Programmtransformationen überflüssig. Die Aufgabe eines Ubersetzers für CGIS-Programme besteht also weniger darin Parallelität aufzudecken als sie auf die Hardware abzubilden.

In vorherigen Arbeiten haben wir ein GPU-Backend vorgestellt und erfolgreich gezeigt, dass CGIS eine sinnvolle Sprache zum Implementieren datenparalleler Algorithmen ist. Die Programmiersprache CGIS weist zwei Arten von Parallelität auf: Einerseits parallele Schleifeniterationen über Datenströme und andererseits Vektordatentypen, beschränkt auf maximal vier Komponenten. Letztere wurden wegen CGIS' Nähe zu Programmiersprachen für Grafikprozessoren eingebaut. Das Abbilden dieser Typen von Parallelität auf Grafik-Hardware ist eine Eins-zu-eins-Abbildung, da dort bis zu 128 Einheiten auf Vektorregistern mit vier Komponenten parallel rechnen.

Die vorliegende Arbeit beschäftigt sich in erster Linie mit SIMD-Einheiten und deckt die wichtigsten Architekturen ab, nämlich Intels Streaming SIMD Extensions (SSE), Freescales AltiVec und, als Beispiel für eine Multi-Core-Architektur, IBMs Cell Broadband Engine. Die hier vorgestellten SIMD-Instruktionssätze umfassen, im Gegensatz zu GPUs, lediglich die von den SIMD-Registern stammende Vierfach-Parallelität. Mit *Kernel Flattening* haben wir eine spezielle Programmtransformation entwickelt, die alle Vektordatentypen und -operationen in skalare Versionen aufbricht. Diese eigens entwickelte Transformation ermöglicht es, die Parallelität der Schleifen über die Datenströme auf die SIMD-Hardware abzubilden.

Während Grafikkarten einen schnellen Texturenspeicher besitzen, verwenden CPUs Caches um die durch die langsame Anbindung an den Hauptspeicher entstehenden Latenzen zu überdecken und den Zugriff auf häufig benutzte Daten zu beschleunigen. Manche datenparallele Algorithmen weisen Operationen auf, die auf benachbarte Elemente im Datenstrom zugreifen, wie z. B. den Zugriff auf angrenzende Elemente in einem zweidimensionalen Feld. Damit SIMD-Implementierungen dieser Algorithmen effizienter sind als sequentielle Lösungen, muss man Caches gezielt nutzen. Wir haben eine Form von *Loop Sectioning*, eine Anpassung der Iterationsfolge, integriert, um diese Aufgabe zu erfüllen.

Eine weitere wichtige Code-Transformation, insbesondere in Verbindung mit Kernel Flattening, ist *Control Flow Conversion*, d. h. bei Schleifen und if-then-else-Konstrukten werden die Kontrollabhängigkeiten durch Datenabhängigkeiten ersetzt. Dadurch wird eine parallele Ausführung dieser Instruktionsfolgen ermöglicht. Wir demonstrieren die Effizienz des mit CGIS erzeugten SIMD-Codes, indem wir sechs Beispielanwendungen untersuchen. Diese stammen aus den verschiedensten Anwendungsgebieten, wie z. B. komplexe mathematische Berechnungen, Computergrafik, Finanzsimulation usw. Eine Standard-C++-Implementierung wird hierbei mit der CGIS-Variante verglichen und wir können eine Leistungssteigerung von Faktor 3 und mehr beobachten.

Zusätzlich haben wir auch die Nutzung von CGIS zur Implementierung von Applikationen für Multi-Core-Architekturen untersucht. Stellvertretend wurde der "Cell Broadband Engine"-Prozessor gewählt. Er umfasst eine "Power Processing Entity" (PPE), basierend auf der Power Architecture, und acht "Synergistic Processing Elements" (SPEs). Die SPEs sind über den "Element Interconnection Bus" (EIB) untereinander, mit der PPE und mit dem Hauptspeicher verbunden. Bei dieser Art von Architektur ist die Verteilung der Berechnungen auf die einzelnen Einheiten besonders wichtig. Wir haben zwei verschiedene Ansätze implementiert, nämlich die statische und die dynamische Verteilung der Berechnungen. Deren Laufzeiten haben wir mit der Standard-C++-Ausführung auf der PPE anhand der oben erwähnten Beispiele verglichen. Für den Cell-Prozessor kann man Leistungssteigerungen beobachten, die von einem Faktor von 1,5 bis zu einem Faktor von 70 reichen, je nach den Eigenschaften des datenparallelen Algorithmus. Zur effizienten Nutzung dieser Multi-Core-Architektur mit CGIS muss ein Algorithmus eine sehr hohe arithmetische Dichte aufweisen.

#### Acknowledgements

First, I want to thank *Reinhard Wilhelm* for allowing me to pursuit this interesting topic. He provided me with vital support whenever needed but, on the other hand, left me enough freedom to find my part in the CGIS project. The same holds for *Philipp Slusallek*.

There were many people involved in the completion of this work. The biggest influence was surely the cooperation with *Philipp Lucas*, many thanks to him. We faced a few obstacles together in the development of CGIS but managed to tackle or bypass most of them. He helped me not to lose focus on my research and I will miss our discussions about the fall of the occident, raiding the coffee dispenser, and making a living as a carpet dealer.

Furthermore, I want to thank the people at the chair for compiler construction and *AbsInt GmbH*, especially *Daniel Kästner* for proof-reading and being very patient in the process. Also, I want to thank *Kate Flynn* for bringing back punctuation to this thesis and *Emilie Cherlet* for improving the German parts.

Last but not least I want to thank my parents, *Walter* and *Ingrid*. Their continuous support, encouragement, and belief in me carried me through some setbacks and helped me find my way.

## Contents

| weite                                            | erte Zusammenfassung                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                                                                                                                                                                                                                                                                     | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Intro</b><br>1.1.                             | oduction<br>SIMD Code Generation for Multi-Media Instruction Sets                                                                                                                                                                                                   | <b>1</b><br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                  | Outline   Outline                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SIM                                              | D: Hardware and Programming                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

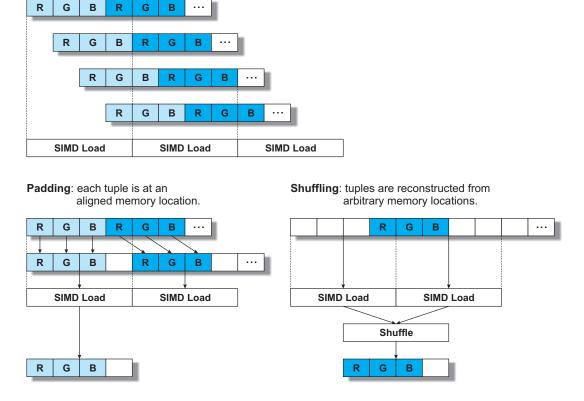

| <ul><li>2.2.</li><li>2.3.</li><li>2.4.</li></ul> | History of SIMD HardwareMulti-Media Instruction Sets2.3.1. Streaming SIMD Extensions (SSE)2.3.2. AltiVecCell Broadband Engine2.4.1. PowerPC Processor Element2.4.2. Synergistic Processor Element2.4.3. Element Interconnection Bus2.4.4. Memory Controller and I/O | $\begin{array}{c} 7\\ 9\\ 10\\ 11\\ 13\\ 14\\ 15\\ 17\\ 19\\ 20\\ 20\\ 20\\ 20\\ 22\\ 24\\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1.<br>3.2.<br>3.3.                             | Programming Assembler and Intrinsics                                                                                                                                                                                                                                | <b>25</b><br>26<br>28<br>30<br>32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                  | <ul> <li>SIM</li> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> <li>2.5.</li> <li>Prog</li> <li>3.1.</li> <li>3.2.</li> <li>3.3.</li> </ul>                                                                                                               | SIMD: Hardware and Programming         2.1. Overview         2.2. History of SIMD Hardware         2.3. Multi-Media Instruction Sets         2.3.1. Streaming SIMD Extensions (SSE)         2.3.2. AltiVec         2.4. Cell Broadband Engine         2.4.1. PowerPC Processor Element         2.4.2. Synergistic Processor Element         2.4.3. Element Interconnection Bus         2.4.4. Memory Controller and I/O         2.5. Characteristics of SIMD Programming         2.5.1. Data Alignment         2.5.2. Available Operations         2.5.3. Precision |

|    | 3.5.                                                          | Other Parallel Programmin | g Languages                         |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 34                                                                                                                                             |

|----|---------------------------------------------------------------|---------------------------|-------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                               | 3.5.1. Brook              |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 34                                                                                                                                             |

|    |                                                               | 3.5.2. RapidMind          |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 34                                                                                                                                             |

|    |                                                               | 3.5.3. SWARC              |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 35                                                                                                                                             |

|    |                                                               | 3.5.4. 1DC                |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 35                                                                                                                                             |

|    | 3.6.                                                          | Evaluation                |                                     |                                                                    |                                                                               |                                       | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                     | •                     | •                                     | 36                                                                                                                                             |

| 4. | CGi                                                           | 5                         |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 39                                                                                                                                             |

|    | 4.1.                                                          | Overview                  |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 39                                                                                                                                             |

|    | 4.2.                                                          | Design Decisions          |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 42                                                                                                                                             |

|    | 4.3.                                                          | INTERFACE Section         |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 44                                                                                                                                             |

|    |                                                               |                           |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 45                                                                                                                                             |

|    |                                                               | • 1                       |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 45                                                                                                                                             |

|    | 4.4.                                                          | CODE Section              |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 46                                                                                                                                             |

|    |                                                               |                           |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 46                                                                                                                                             |

|    |                                                               | 4.4.2. Expressions        |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 48                                                                                                                                             |

|    |                                                               | -                         | ng                                  |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 49                                                                                                                                             |

|    |                                                               | 0                         | · · · · · · · · · · · · · · · · · · |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 51                                                                                                                                             |

|    | 4.5.                                                          | CONTROL Section           |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 55                                                                                                                                             |

|    |                                                               | 4.5.1. Semantics          |                                     |                                                                    |                                                                               |                                       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                       |                                       | 55                                                                                                                                             |