# On the Design of IEEE Compliant Floating-Point Units and Their Quantitative Analysis

Dissertation zur Erlangung des Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Technischen Fakultät im Fachbereich Informatik der Universität des Saarlandes vorgelegt von

Peter-Michael Seidel

Saarbrücken 1999

| Dekan:                    | Prof. Dr. Wolfgang Paul    |

|---------------------------|----------------------------|

| Erster Berichterstatter:  | Prof. Dr. Wolfgang Paul    |

| Zweiter Berichterstatter: | PrivDoz. Dr. Silvia Müller |

| Tag des Kolloquiums:      | 14. Januar 2000            |

# Abstract

This thesis addresses the question of which are the important issues in the design of a high-speed floating-point unit (FPU) that is fully compliant with the IEEE floating-point standard 754-1985 [19]. There are a few choices that need to be made when designing an IEEE compliant FPU, among them: the internal representation of floating-point numbers, the rounding algorithms, handling of denormal results, usage of the same rounding hardware for different units (e.g. adder, multiplier, divider), and the implementations of the adder, the multiplier and the divider. These choices influence both the cost and the performance of the FPU. Nevertheless, these issues have not been discussed in the open literature todate. This work begins to fill this gap by designing, analyzing and comparing 18 different IEEE compliant FPU implementations, that consider design options regarding: (a) the internal representation of floating-point numbers; (b) the rounding algorithms; (c) sharing of a rounding unit, the implementation of gradual step rounding or the implementation of dedicated rounding units for each functional unit; (d) the implementation of the floating-point multiplier; and (e) the implementation of the floating-point divider. The presented FPU designs make also use of the following innovations, that were developed in the context of this work: (a) a fast implementation of variable position rounding integrated into a FP multiplier [37]; (b) to the best of our knowledge the fastest integrated FP addition and rounding algorithm published todate [40], (c) the fastest FP multiplication rounding algorithm published todate [11, 12] and (d) the fastest linear reciprocal approximation implementation published todate. [36, 39]; (e) an efficient integration of single and double precision rounding [9]; (f) a Booth encoded adder-tree with an improved cost formula [30].

All the FPUs designed in this work are fully compliant with the IEEE standard for all implemented operations, support both single and double precision, and deal with denormal values and special cases in hardware. Because to design an IEEE compliant FPU is a complex and error-prone task, all the FPU designs are specified in full detail at gate level and the correctness of the FPU designs (in particular the compliance with the IEEE standard) is proven. The proposed FPU implementations are analyzed and compared regarding the hardware cost, the cycle time and the performance that they achieve on traces of the SPECfp92 benchmark suite [17] integrated into a pipelined RISC processor from [23]. In this quantitative analysis [38] it is demonstrated that the choice of the rounding architecture in the FPU has a larger impact on the performance of the microprocessor than the choice of the FP multiplication or the FP division implementation. In comparison to this the impact of the rounding architecture choice on the cost is relatively small. The rounding architecture that uses dedicated rounding units provides the best performance with only small additional cost, so that this rounding architecture seems to be the best choice in floating-point implementations. The fast implementation of this rounding architecture is only made possible by the fast variable position rounding implementation for multipliers from [37]. This underlines the importance of this technique.

# Kurzzusammenfassung

In dieser Arbeit wird der Frage nachgegangen, welches die wichtigsten Designentscheidungen bei der Implementierung einer schnellen Gleitkommaeinheit (FPU), die dem IEEE Standard 754-1985 [19] genügt, sind. Es gibt verschiedene Entscheidungen, die beim Entwurf einer IEEE konformen FPU getroffen werden müssen, darunter: die internen Darstellungen der Gleitkomma- (FP) Zahlen, die Rundungsalgorithmen, die Art der Behandlung von denormalisierten Ergebnissen, die Mehrfachverwendung von Teilen der Hardware, wie z.B. die Benutzung derselben Rundungshardware für verschiedene Einheiten, und die Implementierungen des FP Addierers, des FP Multiplizierers und des FP Dividierers. Diese Entscheidungen beeinflussen sowohl die Kosten alsauch die Leistung der FPU. Nichtsdestotrotz wurden diese Entscheidungen bislang nicht in der Literatur diskutiert. Die vorliegende Arbeit setzt in dieser Lücke an. Es werden 18 unterschiedliche FPUs vorgestellt, analysiert und verglichen, die Optionen zu den folgenden Entscheidungen betrachten: (a) interne Darstellung der FP Zahlen; (b) Rundungsalgorithmen; (c) Gemeinsame Nutzung einer allgemeinen Rundungseinheit, Aufteilen des Rundens in mehrere Schritte und gemeinsame Realisierung einer Teilmenge dieser Schritte oder vollständige eigene Implementierung des Rundens für jede Funktionseinheit; (d) Implementierung des FP Multiplizierers; (e) Implementierung des FP Dividierers. Die vorgestellten FPU Designs benutzen darüberhinaus folgende Neuerungen, die im Rahmen dieser Arbeit entstanden sind: (a) eine schnelle Rundungsimplementierung für den FP Multiplizierer mit variabler Rundungsposition [37]; (b) nach unserem besten Wissen den bisher schnellsten publizierten Algorithmus zum Addieren und Runden von FP Zahlen [40], (c) den bisher schnellsten publizierten Algorithmus zum Runden bei der FP Multiplikation [11, 12] und (d) die bisher schnellste publizierte Implementierung einer linearen Approximation von Reziproken [36, 39]; (e) eine effiziente Integration des Rundens in single precision und double precision [9]; (f) einen Booth-Multiplizierer mit verringerten Kosten [30].

Alle entworfenen FPUs sind für alle implementierten Operationen vollständig konform zum IEEE FP Standard 754, unterstützen sowohl single alsauch double precision Zahlen, und behandeln selbst denormalisierte Ergebnisse und Spezialfälle in Hardware. Weil der Entwurf von IEEE konformen FPUs eine komplexe und fehleranfällige Aufgabe ist, werden sämtliche entworfenen FPUs detailiert auf Gatterebene spezifiziert und ihre Korrektheit (insbesondere die Konformität zum IEEE FP Standard 754) bewiesen. Die vorgestellten FPU Implementierungen werden bezüglich der Hardwarekosten, der Zykluszeit und der Leistung, die sie integriert in einen gepipelinten RISC Processor aus [23] auf Traces der SPECfp92 Benchmark Suite erbringen, analysiert und verglichen. In dieser quantitativen Analyse (siehe auch [38]) wird demonstriert, daß die Auswahl der Rundungs-Architektur einer FPU einen größeren Einfluß auf die Prozessorleistung hat als die Auswahl der Implementierung der FP Multiplikation oder der FP Division. Im Gegensatz dazu ist der Einfluß der Auswahl einer Rundungs-Architektur der FPU auf die Hardwarekosten vergleichsweise gering. Die Rundungs-Architektur, die vollständige eigene Rundungsimplementierungen für jede Funktionseinheit benutzt, liefert bei weitem die beste Leistung und ist lediglich geringfügig teurer als Varianten mit anderen Rundungs-Architekturen. Demzufolge scheint diese Rundungs-Architektur die beste Wahl in FP Implementierungen zu sein. Die schnelle Implementierung dieser Rundungs-Architektur wurde erst durch die schnelle Rundungsimplementierung für FP Multiplizierer mit variabler Rundungsposition nach [37] ermöglicht. Das unterstreicht die Bedeutung dieser Technik.

# **Extended Abstract**

The importance of floating-point operations is increasing in recent graphic and multimedia applications. Therefore, each modern microprocessor has to contain at least one floating-point unit, that supports and accelerates the floating-point computations. To achieve a well defined behavior during the computations, the floating-point support should be conform with the IEEE floating-point standard 754-1985 [19].

Despite the high demand for floating-point hardware implementations, an answer to the question, how to design a fast IEEE compliant FP unit, rarely can be found in the open literature. Moreover, there are several choices that need to be made when designing an IEEE compliant FPU, among them: the internal representation of floating-point numbers, the rounding algorithms, handling of denormal results, usage of the same rounding hardware for different units (e.g. adder, multiplier, divider), and the implementations of the adder, the multiplier and the divider. These choices influence both the cost and the performance of the FPU. Nevertheless, these issues have not been discussed in the open literature todate. In contrast to this lack of publications about the implementation of fully IEEE compliant FP operations or fully IEEE compliant FPUs, there are many published implementations of specific floating-point operations for the case of normalized operands in a specific precision, e.g. [9, 26, 27, 32, 40, 43, 44], and these implementations are highly optimized for speed. Therefore, it is an important question, how to integrate the implementations of the different FP operations for normalized operands into a floating-point unit that supports more than one precision, denormalized numbers and special value results. This mainly includes the questions of which internal FP representations should be used in a FP unit and how the microarchitecture of a FP unit could be organized.

This work starts to fill these gaps in the open literature and to find answers to these open questions. For this purpose, 18 different implementations of a floating-point unit are designed, quantitatively analyzed and compared in this thesis. All proposed FP designs provide full compliance with the IEEE FP standard 754-1985 for all implemented operations, support both single precision and double precision operands and also consider denormalized numbers, special values, exponent wrapping and floating-point exceptions in hardware. The core of this work is the design and the comparison of three different FPU microarchitectures that consider the following three options:

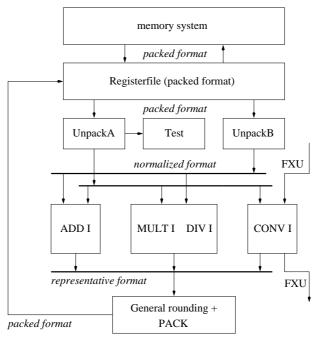

- (I) the use of a shared general rounder for all functional units; A basic specification of such a rounder was first described in [10]. Thereafter, this rounder was implemented by our group, resulting in a version that will be included in [23], where also a rigorous proof of the compliance with the IEEE rounding definition will be found. This rounder was further optimized to be included in this thesis.

- (II) a gradual rounding implementation in two steps, a first rounding step within the functional units assuming the case of a normalized double precision result and a second rounding step within a shared gradual rounder that fixes the result for all

other cases; For the integrated rounding in the functional units assuming normalized, double precision operands and results, several algorithms from literature could be used. The implementation of the gradual rounder is based on the theory from [21] about gradual rounding. This rounding technique is integrated in this thesis for full IEEE compliant rounding including the handling of denormalized results, special values, exceptions and exponent wrapping.

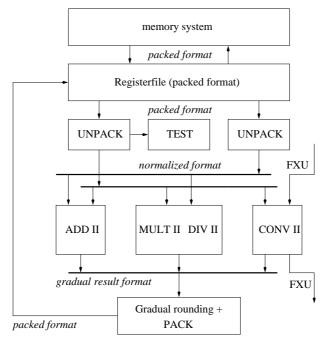

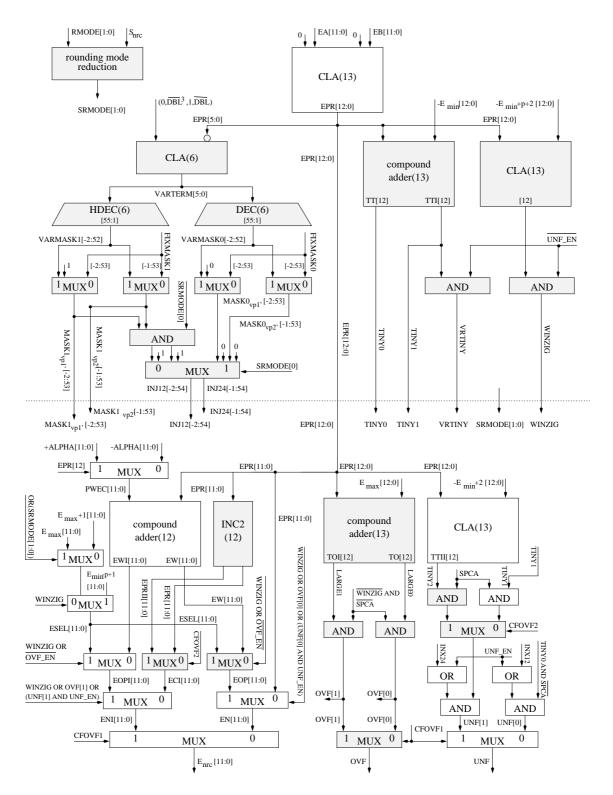

(III) the use of separate fully IEEE compliant rounding implementations for each functional unit, each including the handling of denormalized numbers, special cases, exceptions and exponent wrapping. The implementation of this microarchitecture for a full IEEE compliant FPU with dedicated rounding implementations is completely new in this thesis. Especially the integration of a variable position rounding implementation into the multiplier, that is required to deal with denormalized multiplication results, was one of the main problems for the implementation of this microarchitecture and is one of the main innovations of this work [37].

Directly linked to the choice of the FP microarchitecture is the question of the internal floating-point representations. In this work, five different internal FP representations are defined. These are used to specify the interfaces between the functional units in detail. In addition to the consideration of the three different microarchitectures for the FP implementation, the implementations of the FP-multiplication and the FP-division are chosen among 6(2x3) variants:

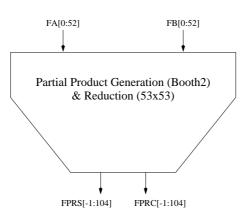

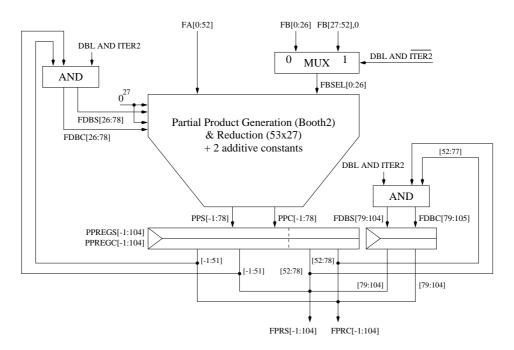

- For the FP multiplication implementation a Booth encoded adder tree is used either in a full-sized version that is able to compute double precision and single precision multiplications in one iteration or in a half-sized version that computes double precision multiplications in two iterations and single precision multiplications in one iteration.

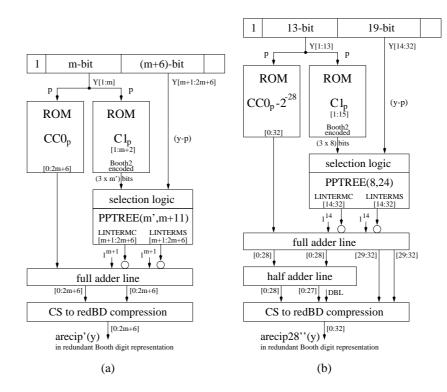

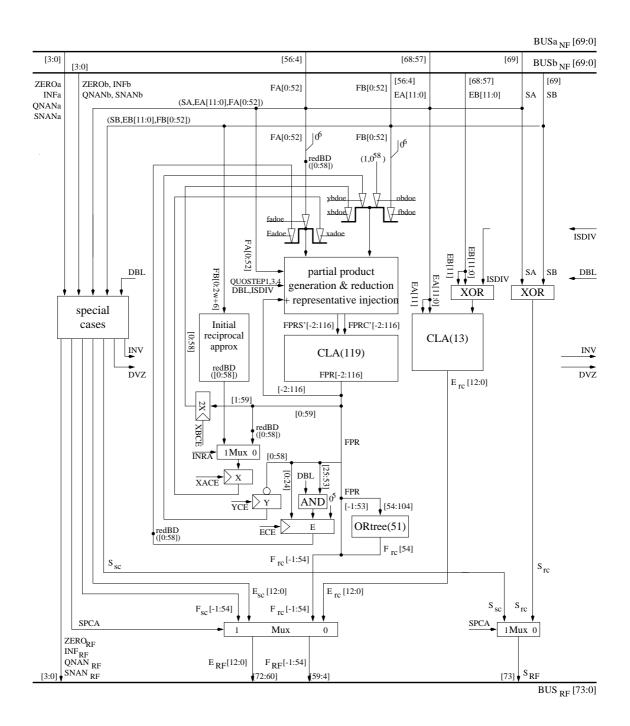

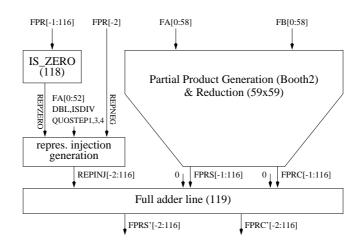

- For the FP division implementation, we consider three different implementations of the Newton-Raphson iteration with an initial reciprocal approximation with an absolute approximation error bounded by  $2^{-8}$ ,  $2^{-16}$ , and  $2^{-28}$ , respectively. For this initial reciprocal approximation a fast implementation of a linear approximation formula using partial compressions was developed [36, 39].

In addition to the different design choices for the internal FP representations, the rounding microarchitecture and the choice of the FP multiplication and the FP division implementation, the presented FPU designs make also use of the following innovations, that were developed in the context of this work:

- (a) a fast implementation of variable position rounding for FP multiplication [37];

- (b) to the best of our knowledge the fastest integrated FP addition and rounding algorithm published todate [40],

- (c) the fastest FP multiplication rounding algorithm published todate [11, 12] and

- (d) the fastest linear reciprocal approximation implementation published todate. [36, 39];

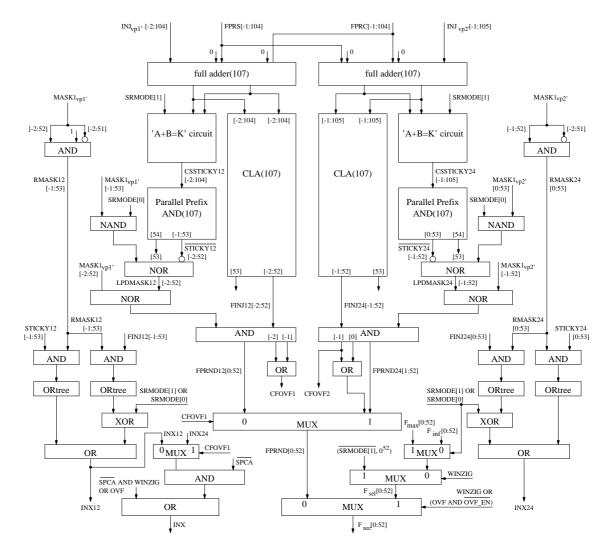

- (e) an efficient integration of single and double precision rounding for FP multiplication [9];

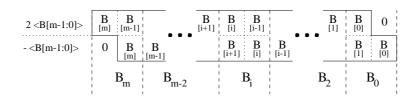

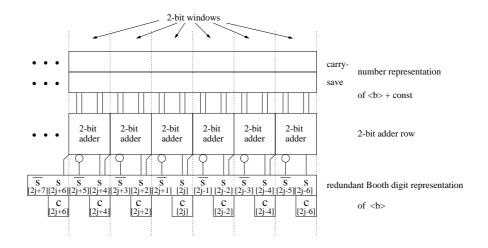

#### (f) a Booth encoded adder-tree with an improved cost formula [30].

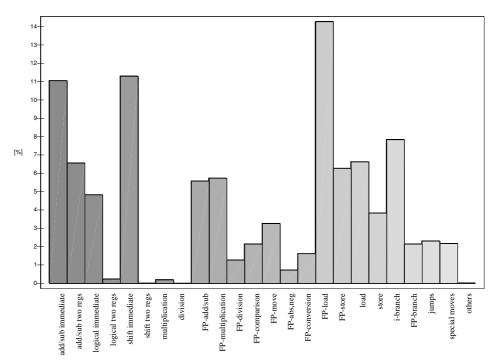

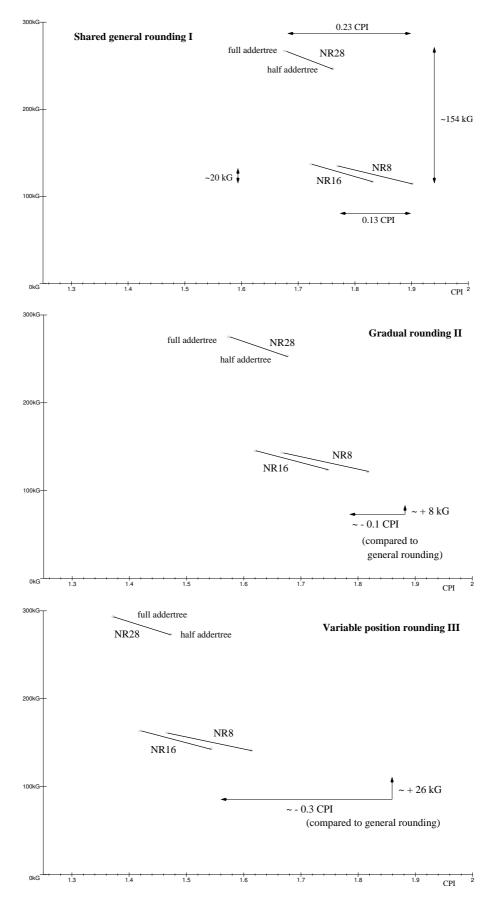

The proposed FPUs are quantitatively analyzed regarding the hardware cost, the cycle time and the performance. The hardware cost and the cycle time are measured using the formal Hardware model from [22]. The performance of the FP units is analyzed on traces of the SPECfp92 Benchmark Suite integrated into a pipelined RISC-processor from [23].

In this quantitative analysis (see also [38]) it is demonstrated that the choice of the rounding microarchitecture in the FPU has a larger impact on the performance of the microprocessor than the choice of the FP multiplication or the FP division implementation. In comparison to this the impact of the microarchitecture choice on the cost is relatively small. The microarchitecture that uses dedicated rounding units provides the best performance with only small additional cost, so that this rounding architecture seems to be the best choice in floating-point implementations.

vi

# Zusammenfassung

Floating-Point Operationen gewinnen in heutigen Grafik- und Multimedia-Anwendungen immer mehr an Bedeutung. Deshalb besitzen aktuelle Mikroprozessoren mindestens eine Floating-Point Einheit, die die Floating-point Berechnungen unterstützt und beschleunigt. Um ein wohldefiniertes Verhalten der Floating-point Berechnungen zu erhalten, sollte die Floating-point Unterstützung konform zum IEEE floating-point Standard 754-1985 [19] sein.

Trotz des großen Bedeutung von Floating-Point Implementierungen in Hardware, gibt es in der offenen Literatur nur spärliche Antworten auf die Frage, wie man eine schnelle IEEE konforme FP Einheit entwirft. Darüberhinaus gibt es verschiedene Entscheidungen, die beim Entwurf einer IEEE konformen FPU getroffen werden müssen, darunter: die Wahl der internen Darstellungen der Gleitkomma- (FP) Zahlen, die Rundungsalgorithmen, die Art der Behandlung von denormalisierten Ergebnissen, die Mehrfachverwendung von Teilen der Hardware, wie z.B. die Benutzung derselben Rundungshardware für verschiedene Einheiten, und die Implementierungen des FP Addierers, des FP Multiplizierers und des FP Dividierers. Diese Entscheidungen beeinflussen sowohl die Kosten alsauch die Leistung der FPU. Nichtsdestotrotz wurden diese Entscheidungen bislang nicht in der Literatur diskutiert.

Im Gegensatz zu diesem Mangel an Publikationen über die Implementierung von IEEE konformen FPUs, gibt es allerdings eine Reihe von publizierten Implementierungen von einzelnen Floating-point Operationen für den Fall von normalisierten Operanden in einer festgelegten Genauigkeit, z.B. [9, 26, 27, 32, 40, 43, 44], und diese Implementierungen sind in Hinblick auf ihre Geschwindigkeit optimiert. Deshalb ist es eine wichtige und interessante Frage, wie diese Implementierungen einzelner FP Operationen für normalisierte Operanden in eine FPU, die mehr als einen FP Typ unterstützt und auch die Behandlung von denormalisierten Zahlen und special values berücksichtigt, integriert werden können. Das beinhaltet hauptsächlich die Fragen, welche internen FP Zahlendarstellungen in einer FP Einheit verwendet werden sollten und wie die Architetur einer FP Einheit zu organisieren ist.

Die vorliegende Arbeit setzt in dieser Lücke an. Zu diesem Zweck werden in dieser Arbeit 18 verschiedene FP Implementierungen entworfen, quantitativ analysiert und verglichen. Alle vorgestellten FPU Entwürfe sind für die FP Operationen, die sie implementieren vollständig konform zu dem IEEE Standard 754-1985, unterstützen sowohl single precision alsauch double precision Operanden und berücksichtigen auch denormalisierte Ergebnisse, special values, Exponenten wrapping und FP exceptions in Hardware. Der Kern dieser Arbeit ist der Entwurf und der Vergleich von drei unterschiedlichen FPU Architekturen, die die folgenden Optionen betrachten:

die Verwendung eines gemeinsamen allgemeinen Runders f

ür alle Funktionseinheiten. Eine grundlegende Spezifikation eines solchen Runders wurde zuerst in [10] beschrieben. Danach wurde dieser Runder in unserer Gruppe in einer Version implementiert, die in [23] vorgestellt werden wird. Dieser Runder wurde für die vorliegende Arbeit weiter optimiert.

- (II) eine Rundungsimplementierung in zwei Schritten (gradual rounding), ein erster Rundungsschritt in den Funktionseinheiten unter der Annahme von normalisierten Ergebnissen in double precision und ein zweiter Rundungsschritt in einem gemeinsamen Gradual Rounder, der das Ergebis für alle anderen Fälle (nicht double precision oder kein normalisiertes Ergebnis) anpaßt. Für das Runden in den Funktionseinheiten unter der Annahme von normalisierten double precision Ergebnissen können unterschiedliche Algorithmen aus der offenen Literatur verwendet werden. Die Implementierung des gradual rounders basiert auf der Theorie aus [21]. Dieses Rundungsprinzip wird in der vorliegenden Arbeit für vollständig IEEE konformes Runden unter Berücksichtigung von denormalisierten Ergebnissen, special values, exceptions und Exponent wrapping integriert.

- (III) die Verwendung von eigenen voll IEEE konformen Rundungsimplementierungen für jede Funktionseinheit, die jeweils eigenständig denormalisierte Ergebnisse, special values, exceptions und Exponent Wrapping gemäß dem IEEE Standard berücksichtigen. Die Implementierung dieser Architektur einer IEEE konformen FPU mit eigenständigen Rundungsimplementierungen ist vollständig neu in dieser Arbeit. Besonders die Integration des Variable Position Rundens in den Multiplizierer, das erforderlich wird, um denormalisierte Multiplikationsergebnisse behandeln zu können, ist eines der Hauptprobleme dieser FPU Architektur und damit ist die beschriebene Implementierung eine der wichtigsten Innovationen der vorliegenden Arbeit [37].

Direkt verbunden mit der Wahl der Architektur der FPU ist die Frage nach den zu verwendenden internen FP Darstellungen. In dieser Arbeit werden fünf verschiedene interne FP Darstellungen definiert. Diese werden dann dazu verwendet um die Schnittstellen zwischen den Funktionseinheiten einfach, aber detailiert zu spezifizieren.

Zusätzlich zur Betrachtung der drei unterschiedlichen FPU Architekturen wählen wir die Implementierungen der FP Multiplikation und der FP Division unter 6(2x3) verschiedenen Varianten aus:

- Für die Implementierung der FP Multiplikation wird entweder ein Booth2 Multiplizierer vollständiger Größe verwendet, der sowohl single alsauch double precision Multiplikationen in einer Iteration berechnen kann oder es wird ein Booth2 Multiplizierer halber Größe verwendet, der single precision Multiplikationen in einer Iteration und double precision Multiplikationen in zwei Iterationen berechnet.

- Für die Implementierung der FP Division betrachten wir drei unterschiedliche Implementierungen der Newton-Raphson Iteration mit einer Startapproximation des Reziproken 1FB mit absolutem Approximationsfehler kleiner als 2<sup>-8</sup>, 2<sup>-16</sup> bzw. 2<sup>-28</sup>. Für diese Approximation des Reziproken wurde eine schnelle Implementierung einer linearen Approximationsformel unter Verwendung einer partiellen Kompression entwickelt [36, 39].

Die vorgestellten FPU Designs benutzen darüberhinaus folgende Neuerungen, die im Rahmen dieser Arbeit entstanden sind:

(a) eine schnelle Rundungsimplementierung für den FP Multiplizierer mit variabler Rundungsposition [37];

- (b) nach unserem besten Wissen den bisher schnellsten publizierten Algorithmus zum Addieren und Runden von FP Zahlen [40],

- (c) den bisher schnellsten publizierten Algorithmus zum Runden bei der FP Multiplikation [11, 12] und

- (d) die bisher schnellste publizierte Implementierung einer linearen Approximation von Reziproken [36, 39],

- (e) eine effiziente Integration des Rundens in single precision und double precision [9];

- (f) einen Booth-Multiplizierer mit verringerten Kosten [30].

Die vorgestellten FPU Implementierungen werden bezüglich der Hardwarekosten, der Zykluszeit und der Leistung, die sie integriert in einen gepipelinten RISC Processor aus [23] auf Traces der SPECfp92 Benchmark Suite erbringen, analysiert und verglichen. In dieser quantitativen Analyse (siehe auch [38]) wird gezeigt, daß die Auswahl der Rundungs-Architektur einer FPU einen größeren Einfluß auf die Prozessorleistung hat als die Auswahl der Implementierung der FP Multiplikation oder der FP Division. Im Gegensatz dazu ist der Einfluß der Auswahl einer Rundungs-Architektur der FPU auf die Hardwarekosten vergleichsweise gering. Die Rundungs-Architektur, die vollständige eigene Rundungsimplementierungen für jede Funktionseinheit benutzt, liefert bei weitem die beste Leistung und ist lediglich geringfügig teurer als Varianten mit anderen Rundungs-Architekturen. Demzufolge scheint diese Rundungs-Architektur die beste Wahl in FP Implementierungen zu sein. х

# Contents

| 1 | Introduction  |         |                                                                                    |    |  |  |  |

|---|---------------|---------|------------------------------------------------------------------------------------|----|--|--|--|

| 2 | IEE           | E Floa  | ating-Point Standard                                                               | 4  |  |  |  |

|   | 2.1           | Notati  | ion                                                                                | 4  |  |  |  |

|   | 2.2           | Numb    | ers and Operations                                                                 | 6  |  |  |  |

|   |               | 2.2.1   | Factorings                                                                         | 6  |  |  |  |

|   |               | 2.2.2   | IEEE Numbers                                                                       | 7  |  |  |  |

|   |               | 2.2.3   | Packed IEEE Floating-Point Format                                                  | 10 |  |  |  |

|   |               | 2.2.4   | Operations                                                                         | 11 |  |  |  |

|   | 2.3           | Round   | ling                                                                               | 14 |  |  |  |

|   |               | 2.3.1   | IEEE Rounding Definition                                                           | 14 |  |  |  |

|   |               | 2.3.2   | Rounding Functions                                                                 | 14 |  |  |  |

|   |               | 2.3.3   | IEEE Rounding Functions                                                            | 15 |  |  |  |

|   | 2.4           | Specia  | l Cases                                                                            | 21 |  |  |  |

|   |               | 2.4.1   | IEEE Flags                                                                         | 21 |  |  |  |

|   |               | 2.4.2   | Exceptions                                                                         | 22 |  |  |  |

|   |               | 2.4.3   | Operations on Special Values                                                       | 24 |  |  |  |

|   |               | 2.4.4   | Summary of IEEE Computations                                                       | 26 |  |  |  |

|   | 2.5           | Round   | ling Computation Utilities                                                         | 29 |  |  |  |

|   |               | 2.5.1   | Representatives                                                                    | 29 |  |  |  |

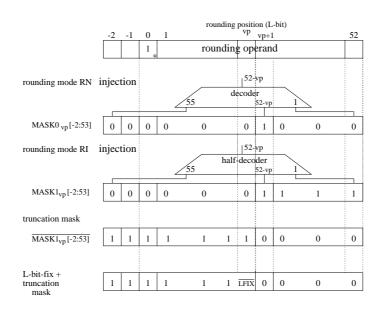

|   |               | 2.5.2   | Injection Based Rounding                                                           | 33 |  |  |  |

|   |               | 2.5.3   | Gradual Rounding                                                                   | 34 |  |  |  |

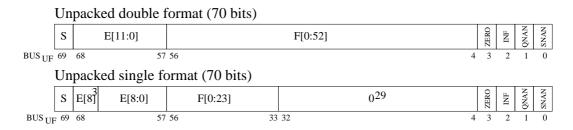

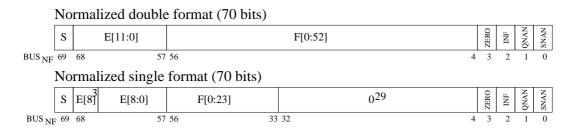

|   | 2.6           | Interna | al Representations                                                                 | 38 |  |  |  |

|   |               | 2.6.1   | Packed Format                                                                      | 38 |  |  |  |

|   |               | 2.6.2   | Unpacked Format                                                                    | 39 |  |  |  |

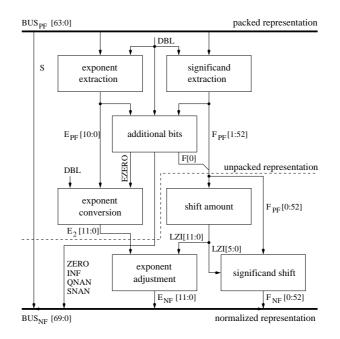

|   |               |         | 2.6.2.1 Packed Format $\longrightarrow$ Unpacked Format $\ldots$ $\ldots$ $\ldots$ | 40 |  |  |  |

|   |               |         | 2.6.2.2 Unpacked Format $\longrightarrow$ Packed Format $\dots$                    | 41 |  |  |  |

|   |               | 2.6.3   | Normalized Format                                                                  | 42 |  |  |  |

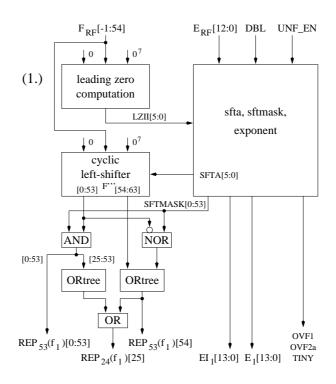

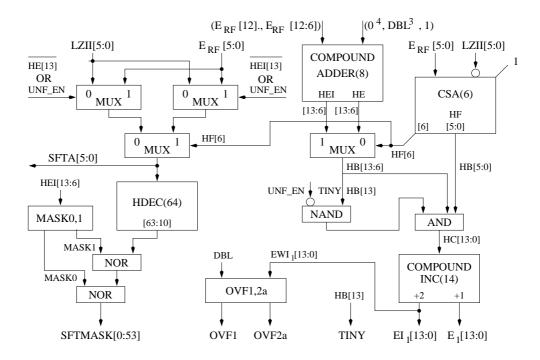

|   |               |         | 2.6.3.1 Unpacked Format $\longrightarrow$ Normalized Format $\ldots \ldots \ldots$ | 42 |  |  |  |

|   |               |         | 2.6.3.2 Normalized Format $\longrightarrow$ Unpacked Format $\ldots \ldots \ldots$ | 43 |  |  |  |

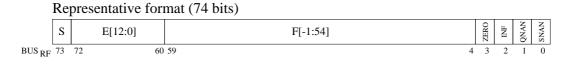

|   |               | 2.6.4   | Representative Format                                                              | 44 |  |  |  |

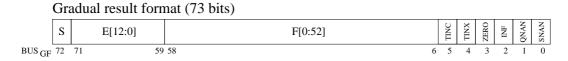

|   |               | 2.6.5   | Gradual Result Format                                                              | 46 |  |  |  |

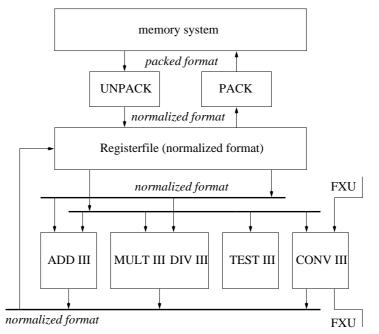

| 3 | $\mathbf{FP}$ | Microa  | architectures                                                                      | 49 |  |  |  |

| 4 | Bas           | ic FP   | Operations                                                                         | 56 |  |  |  |

|   | 4.1           |         | al Format Conversions                                                              | 56 |  |  |  |

|   |               | 4.1.1   | Unpacking I-III (packed $\longrightarrow$ normalized format)                       |    |  |  |  |

|     | 4.1.2  | General Rounding I (representative $\longrightarrow$ packed format) 59                                     |

|-----|--------|------------------------------------------------------------------------------------------------------------|

|     | 4.1.3  | Gradual Rounding II (gradual result $\rightarrow$ packed format)                                           |

|     | 4.1.4  | Packing III (normalized $\rightarrow$ packed format)                                                       |

| 4.2 | Addit  | ion/Subtraction                                                                                            |

|     | 4.2.1  | Addition/Subtraction I (normalized $\rightarrow$ representative format) 79                                 |

|     | 4.2.2  | Addition/Subtraction II (normalized $\rightarrow$ gradual result format) 86                                |

|     | 4.2.3  | Addition/Subtraction III (normalized $\rightarrow$ normalized format) 105                                  |

| 4.3 | Multij | $\operatorname{plication}$ $\cdot$ |

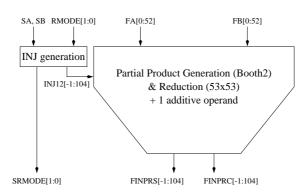

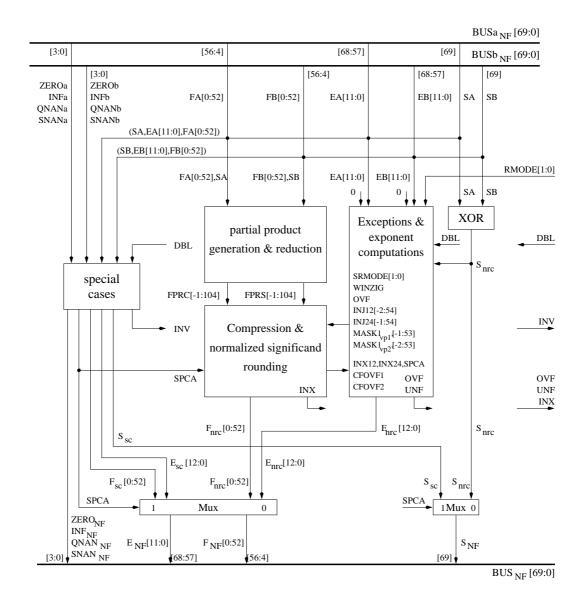

|     | 4.3.1  | Multiplication I (normalized $\rightarrow$ representative format)                                          |

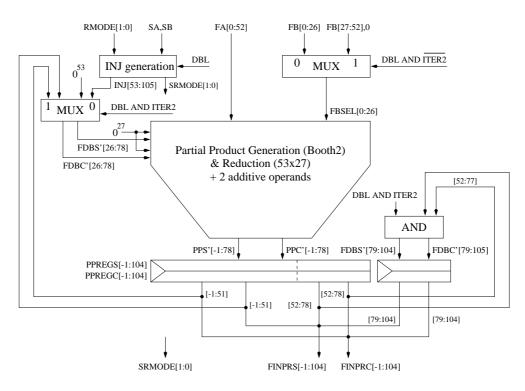

|     | 4.3.2  | Multiplication II (normalized $\rightarrow$ gradual result format)                                         |

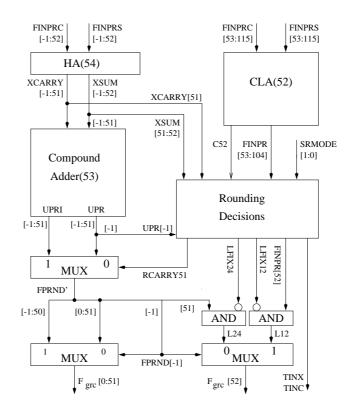

|     | 4.3.3  | Multiplication III (normalized $\rightarrow$ normalized format)                                            |

| 4.4 | Divisi | on                                                                                                         |

|     | 4.4.1  | Initial Reciprocal Approximation                                                                           |

|     |        | 4.4.1.1 Approximation formula                                                                              |

|     |        | 4.4.1.2 Redundant Booth-Digit Representations                                                              |

|     |        | 4.4.1.3 Implementation                                                                                     |

|     | 4.4.2  | Division I (normalized $\rightarrow$ representative format)                                                |

|     |        | 4.4.2.1 Approximation of the quotient (step 1.)                                                            |

|     |        | 4.4.2.2 Computation of the <i>p</i> -representative for $f_{rc}$ (step 2.) 171                             |

|     | 4.4.3  | Division II (normalized $\rightarrow$ gradual result format)                                               |

|     | 4.4.4  | Division III (normalized $\rightarrow$ normalized format) $\ldots \ldots \ldots \ldots 176$                |

|     |        |                                                                                                            |

# 5 Evaluation

181

# Chapter 1 Introduction

The importance of floating-point operations is increasing in recent graphic and multimedia applications. Therefore, each modern microprocessor has to contain at least one floating-point unit, that supports and accelerates the floating-point computations. To achieve a well defined behavior during the computations, the floating-point support should be conform with the IEEE floating-point standard 754-1985 [19]. This IEEE specification could also be achieved by supporting parts of it in software, but for high-performance systems a hardware solution is preferable.

Despite the high demand for floating-point hardware implementations, a full answer to the question, how to design a fast IEEE compliant FP unit, rarely can be found in the open literature. Moreover, there are several choices that need to be made when designing an IEEE compliant FPU, among them: the internal representation of floating-point numbers, the rounding algorithms, handling of denormal results, usage of the same rounding hardware for different units (e.g. adder, multiplier, divider), and the implementations of the adder, the multiplier and the divider. These choices influence both the cost and the performance of the FPU. Nevertheless, these issues have not been discussed in the open literature todate. In contrast to this lack of publications about the implementation of fully IEEE compliant FP operations or fully IEEE compliant FPUs, there are many publications about the implementation of specific floating-point operations for the case of normalized operands in a specific precision, e.g. [9, 26, 27, 32, 40, 43, 44], and these implementations are highly optimized for speed. Therefore, it is an important question, how to integrate the implementations of the different FP operations for normalized operands into a floating-point unit that supports more than one precision, denormalized numbers and special value results. This mainly includes the questions of which internal FP representations should be used in a FP unit and how the microarchitecture of a FP unit could be organized.

We present an answer to this question by developing and comparing three different rounding microarchitectures for a FP unit:

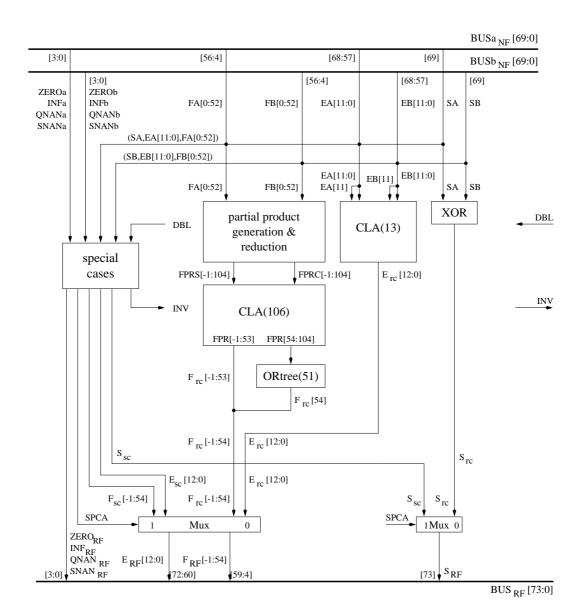

(I) In the first microarchitecture all the rounding computations are concentrated in a shared general rounding unit. This rounding unit considers the rounding for all IEEE results including the exponent wrapping and the FP exceptions for both single and double precision operations. A basic specification of such a rounder was first described in [10]. Thereafter, this rounder was implemented by our group, resulting in a version that will be included in [23], where also a rigorous correctness proof of the compliance with the IEEE rounding definition will be found. This rounder is further optimized in this thesis.

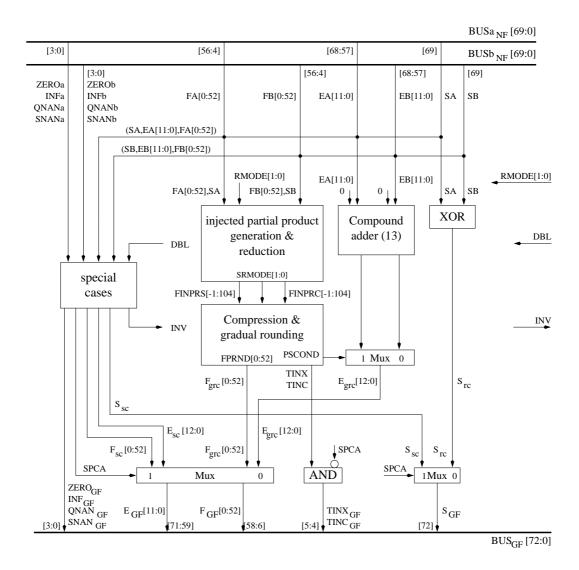

- (II) In the second microarchitecture, the rounding for the case of normalized double precision results is computed within each functional unit and this rounded result is fixed for all the remaining cases in a second rounding step implemented by a shared gradual rounding unit. For the integrated rounding in the functional units assuming normalized, double precision operands and results, several algorithms from literature could be used. The implementation of the gradual rounder is based on the theory from [21] about gradual rounding. This rounding technique is applied in this thesis for full IEEE compliant rounding including the handling of denormalized results, special values, exceptions and exponent wrapping.

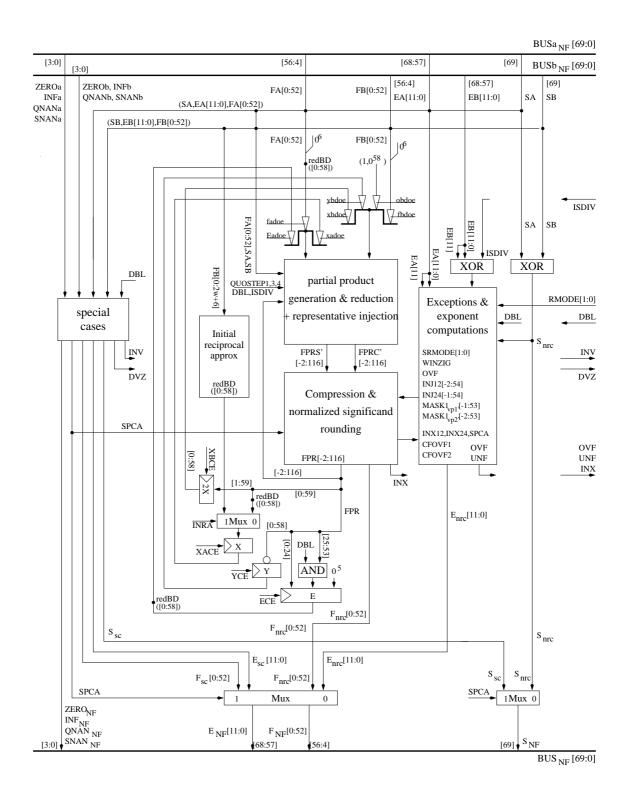

- (III) By the third rounding architecture a completely new architecture for an IEEE compliant FPU is suggested. In this architecture no rounding hardware is shared, but each functional unit contains a dedicated rounding implementation that computes full IEEE rounding considering denormal and special values, exceptions and exponent wrapping. The special problem with the implementation of this microarchitecture is the implementation if the floating-point multiplication. The floating-point multiplier conventionally requires normalized significands in its operands and delivers an almost normalized result. For the fast integration of IEEE rounding into the FP multiplier, the significand has to be rounded in parallel to the mulplication computations. For the case of denormalized results this rounding has to be computed at a variable rounding position, that could be at each position within the significand. The idea, how to integrate such a variable position rounding into the multiplication implementation is the key concept for this microarchitecture. Such an implementation is developed in this work. Because such a multiplication implementation allows to work on normalized FP representations (even for denormalized values) as inputs and outputs, the internal FP representations can eb changed to normalized FP representations for this microarchitecture.

To find out the impact of the microarchitecture choice on the quality of the floatingpoint implementation, we model the performance and the cost of designs that differ by the use of the different microarchitectures. This would already be possible by a comparison of three FP designs, but to improve the expressiveness of the comparison, and to be able to compare the rounding architectures under several conditions, we additionally vary the FP multiplication and FP division implementation for each FP microarchitecture. For this purpose, we choose between two different FP multiplication and three different FP division implementations.

- For the FP multiplication implementation a Booth encoded adder tree is used either in a full-sized version that is able to compute double precision and single precision multiplications in one iteration or in a half-sized version that computes double precision multiplications in two iterations and single precision multiplications in one iteration. For the Booth encoded adder trees the constructions from [30], where we improved cost formula, are used.

- For the FP division implementation, we consider three different implementations of the Newton-Raphson iteration with an initial reciprocal approximation with an absolute approximation error bounded by  $2^{-8}$ ,  $2^{-16}$ , and  $2^{-28}$ , respectively. For this initial reciprocal approximation a fast implementation of a linear approximation formula using partial compressions is used, that we developed in [36, 39].

In combination with the three microarchitectures these options combine to a comparison of 18 different FP implementations.

All the FPUs designed in this work are fully compliant with the IEEE standard for all implemented operations, support both single and double precision, and deal with denormalized values and special cases in hardware. Because to design an IEEE compliant FPU is a complex and error-prone task, all the FPU designs are specified in full detail at gate level and the correctness of the FPU designs (in particular the compliance with the IEEE standard) is proven.

The performance of the designs is measured by a trace-driven run-time simulation of a R3000 like pipelined RISC processor [22, 23] that integrates the proposed floating-point implementations. The simulations are computed on traces of the SPECfp92 Benchmarks suite [17]. The costs of the designs are modeled by counting the gates that are required by the different implementations. Thus, based on the performance and the cost of each FP design, the quality of the FP designs and, in particular, the quality of the rounding microarchitectures can be compared.

This thesis is partitioned into the following chapters. Chapter 2 prepares the definitions of the IEEE FP standard in preparation for the description of the FP implementations. The basic description of the FP standard is similar to the description in [10, 23]. Moreover, in this chapter a general framework for the integrated description of different rounding functions is developed. Rigorous correctness proofs for the partitioning of full IEEE compliant rounding into these rounding functions are given. This chapter also provides computation utilities for the implementation of these rounding function. As one important basic concept, injection-based rounding [9, 40, 11, 12] is introduced. Finally, this chapter prepares the internal FP representations, by that the interfaces between the functional units and the shared rounding hardware are specified. Chapter 3 overviews the requirements on the implementation of a FPU und describes the microarchitectures and the design choices for the proposed FP designs. Chapter 4 describes the implementations of all basic FP operations for all three microarchitectures. In combination with a detailed description of the implementations at gate level, the correctness of the designs and the compliance with the IEEE standard is proven. Finally, in Chapter 5 the proposed FPU implementations are quantitatively analyzed and compared.

# Chapter 2

# **IEEE Floating-Point Standard**

The IEEE floating-point Standard 754-1985 [19] specifies floating-point number formats, operations and exception handling in detail. This chapter presents its information in a slightly different form following [10, 23].

# 2.1 Notation

We denote real values by small-letter names xyz and bit-strings by small capitalized names xyz. The single bits of a bit-string  $xyz \in \{0,1\}^n$  can be indexed by  $xyz[n_2:n_1] = (xyz[n_2], \dots, xyz[n_1])$  with integers  $n_2 = n_1 + n - 1$ . The operation  $\langle xyz[n_2:n_1] \rangle$  defines the binary value of  $xyz[n_2:n_1]$ ,  $\langle xyz[n_2:n_1] \rangle_2$  defines the value of  $xyz[n_2:n_1]$  interpreted as a 2's-complement number, and  $\langle xyz[n_2:n_1] \rangle_{bias_n}$  defines the value of  $xyz[n_2:n_1]$  interpreted as a biased binary number, that includes the bias  $bias_n = 2^{n-1} - 1$ :

$$\langle \operatorname{XYZ}[n_{2}:n_{1}] \rangle = \sum_{i=n_{1}}^{n_{2}} \operatorname{XYZ}[i] \cdot 2^{i} \langle \operatorname{XYZ}[n_{2}:n_{1}] \rangle_{2} = -\operatorname{XYZ}[n_{2}] \cdot 2^{n_{2}} + \sum_{i=n_{1}}^{n_{2}-1} \operatorname{XYZ}[i] \cdot 2^{i} \langle \operatorname{XYZ}[n_{2}:n_{1}] \rangle_{bias_{n}} = \sum_{i=n_{1}}^{n_{2}} \operatorname{XYZ}[i] \cdot 2^{i} - bias_{n}.$$

To avoid negative indizes, we allow the right index of a bit-string to be larger than the left index, like in  $XYZ[n_1 : n_2]$ . Then, we define a second version of the operations  $\langle \rangle$  and  $\langle \rangle_2$ , that interpret the indizes to be multiplied by (-1). These operations are defined by

$$\langle \operatorname{XYZ}[n_1:n_2] \rangle_{neg} = \sum_{i=n_1}^{n_2} \operatorname{XYZ}[i] \cdot 2^{-i}$$

$\langle \operatorname{XYZ}[n_1:n_2] \rangle_{2neg} = -\operatorname{XYZ}[n_1] \cdot 2^{-n_1} + \sum_{i=n_1+1}^{n_2} \operatorname{XYZ}[i] \cdot 2^{-i}.$

The operation  $bin_{\lambda}^{\lambda+n-1}(x) : \mathbb{R} \to \{0,1\}^n$  computes the bit-string of the binary representation of x of length n from bit-position with weight  $2^{\lambda}$  to bit-position with weight  $2^{\lambda+n-1}$ . If x has two different binary representations, we choose the binary representation with finite length, so that in  $x = \sum_i x[i] \cdot 2^i$  the x[i] are unique and  $bin_{\lambda}^{\lambda+n-1}(x)$  can be written by:

$$bin_{\lambda}^{\lambda+n-1}(x) = \mathbf{X}[\lambda+n-1:\lambda].$$

For  $\mathbf{x} \in \{0, 1\}^n$  and  $\mathbf{s} \in \{0, 1\}$  we define

$$\overline{\mathbf{x}} = (\overline{\mathbf{x}[n-1]}, \dots, \overline{\mathbf{x}[0]})$$

and  $\mathbf{x} \oplus \mathbf{s} = (\mathbf{x}[n-1] \oplus \mathbf{s}, \dots, \mathbf{x}[0] \oplus \mathbf{s}).$

Some crucial properties of two's complement numbers are (see [MP95])

$$\begin{array}{rcl} < 0, \mathbf{x}[n-1:0]>_2 &=& < \mathbf{x}[n-1:0]> \\ -< \mathbf{x}[n-1:0]>_2 &=& < \overline{\mathbf{x}[n-1:0]}>_2+1 \\ < \mathbf{x}[n-1], \mathbf{x}[n-1:0]>_2 &=& < \mathbf{x}[n-1:0]>_2 \\ &< x[n-1:0]>_2 &\equiv& < x[n-2:0]> \mod 2^{n-1}. \end{array}$$

From these properties one immediately derives the basic subtraction algorithm for binary numbers. Let  $x, y \in \{0, 1\}^n$  and let  $\langle x \rangle \geq \langle y \rangle$ . Because  $2^n \rangle \langle x \rangle \geq \langle y \rangle$  it suffices to compute the result modulo  $2^n$ . Thus

$$\begin{array}{rcl} <{\rm x}>-<{\rm y}> &=& <0, {\rm x}>_2-<0, {\rm y}>_2\\ &=& <0, {\rm x}>_2+<1, \overline{{\rm y}}>_2+1\\ &\equiv& <{\rm x}>+<\overline{{\rm y}}>+1 \bmod 2^n. \end{array}$$

**Lemma 2.1** Biased number strings  $x[n - 1 : 0] \neq 1^n$  can be converted to two's complement number strings by (i) an increment and the invertation of the sign bit. Using  $\langle Y[n - 1:0] \rangle = \langle x[n - 1:0] \rangle + 1$ , we have:

$$<(0, \mathbf{X}[n-1:0])>_{bias_n} = <(\overline{\mathbf{Y}[n-1]}, \overline{\mathbf{Y}[n-1]}, \mathbf{Y}[n-2:0])>_2.$$

(ii) In the conversion, the sequence of the sign bit inversion and the increment can also be reversed, so that:

$$<(0, \mathbf{x}[n-1:0])>_{bias_n} = <(\overline{\mathbf{x}[n-1]}, \overline{\mathbf{x}[n-1]}, \mathbf{x}[n-2:0])>_2+1.$$

**Proof:** (i):

$$\begin{aligned} < (0, \mathbf{X}[n-1:0]) >_{bias_n} &= < (0, \mathbf{X}[n-1:0]) >_2 - bias_n \\ &= < (0, \mathbf{X}[n-1:0]) >_2 + < (1, 10^{n-2}1) >_2 \\ &= < (0, \mathbf{Y}[n-1:0]) >_2 + < (1, 10^{n-2}0) >_2 \\ &= < (\overline{\mathbf{Y}[n-1]}, \overline{\mathbf{Y}[n-1]}, \mathbf{Y}[n-2:0]) >_2. \end{aligned}$$

(ii):

$$< (0, \mathbf{x}[n-1:0]) >_{bias_n} = < (0, \mathbf{x}[n-1:0]) >_2 + < (1, 10^{n-2}1) >_2 \\ = < (\overline{\mathbf{x}[n-1]}, \overline{\mathbf{x}[n-1]}, \mathbf{x}[n-2:0]) >_2 + 1.$$

**Lemma 2.2** In the other direction, two's complement number strings  $x[n-1:0] \neq (1,0^{n-1})$  can be converted to biased number strings by an inversion and a decrement. Using  $\langle Y[n-1:0] \rangle_2 = \langle (\overline{x[n-1]}, x[n-2:0]) \rangle_2 - 1$ , we have:

$$< \mathbf{X}[n-1:0] >_{2} = < \mathbf{Y}[n-1:0] >_{bias_{n}}.$$

#### **Proof:**

$$\begin{aligned} <\mathbf{x}[n-1:0]>_{2} &= <(\mathbf{x}[n-1],\mathbf{x}[n-1:0])>_{2} + bias_{n} - bias_{n} \\ &= <(\mathbf{x}[n-1],\mathbf{x}[n-1:0])>_{2} + <(0,01^{n-1})>_{2} - bias_{n} \\ &= <(\mathbf{x}[n-1],\mathbf{x}[n-1:0])>_{2} + <(0,10^{n-1})>_{2} - 1 - bias_{n} \\ &= <(\overline{\mathbf{x}[n-1]},\overline{\mathbf{x}[n-1]},\mathbf{x}[n-2:0])>_{2} - 1 - bias_{n} \\ &= <(\overline{\mathbf{x}[n-1]},\mathbf{x}[n-2:0])>_{2} - 1 - bias_{n} \\ &= <\mathbf{x}[n-1],\mathbf{x}[n-2:0]>_{2} - bias_{n} \\ &= <\mathbf{x}[n-1:0]>_{2} - bias_{n} \end{aligned}$$

# 2.2 Numbers and Operations

## 2.2.1 Factorings

Every real number x can be factored into a sign factor (determined by a sign-bit s), a scale factor (determined by an exponent e) and a significand f:

$$x = (-1)^s \cdot f \cdot 2^\epsilon$$

The tripel (s, e, f) is called a *factoring* and the operation

$$x = val(s, e, f) = (-1)^s \cdot f \cdot 2^e$$

computes the value of this factoring.

Although every factoring (s, e, f) is mapped to exactly one real number x by the operation val(s, e, f), every real number x could be represented by infinitely many different factorings, that correspond to the same value

$$x = val(sign(x), 0, |x|) = val(sign(x), -1, 2 \cdot |x|) = \cdots$$

**Definition 2.1** For a set of numbers  $\mathcal{X}$ , we define the set of factorings,  $FACT(\mathcal{X})$ , that represent numbers of  $\mathcal{X}$  by

$FACT(\mathcal{X}) = \{(s, e, f) \mid s \in \{0, 1\}, e \in \mathbb{Z}, f \in \mathbb{R} and val(s, e, f) \in \mathcal{X}\}$

To define a unique factoring representation of a real number, *normalized factorings* are introduced:

**Definition 2.2** A normalized factoring (s', e', f') is a factoring with  $s' \in \{0, 1\}$ ,  $e' \in \mathbb{Z}$ ,  $f' \in [1, 2]$ . The condition  $f' \in [1, 2]$  defines a normalized significand f'.

Thus, every non-zero real value can be represented by a unique normalized factoring.

**Definition 2.3** For all non-zero factorings (s, e, f) with  $f \neq 0$ , we define the operation  $\eta(s, e, f) = (s', e', f')$  to compute the normalized factoring (s', e', f'), so that val(s', e', f') = val(s, e, f). For factorings of zero with f = 0, we define  $\eta$  to compute the identity function:  $\eta(s, e, 0) = (s, e, 0)$ . As in the normalization operation  $\eta$  the exponent range is not limited,  $\eta$  is called an unbounded normalization shift. The result of an unbounded normalization shift, (s', e', f'), is called an unbounded normalized factoring. Note, that from the definition of the unbounded normalization shift for zeros it follows, that also all factorings of zero with f = 0 are unbounded normalized.

**Lemma 2.3** (i) For  $f \neq 0$  and  $k = -\lfloor log(f) \rfloor$ , the unbounded normalization shift  $\eta(s, e, f)$  can be computed by:  $\eta(s, e, f) = (s, e - k, f \cdot 2^k)$ .

(ii) If  $2^{-\gamma} \leq f < 2$ , k can be interpreted as the number of leading zeros lz of the binary representation  $bin_{-\gamma}^0(f)$ , so that  $\eta(s, e, f) = (s, e - lz, f \cdot 2^{lz})$ .

**Proof:** (i) The result of the unbounded normalization shift  $\eta(s, e, f)$  has to be the normalized factoring of (s, e, f). Therefore,  $(s, e - k, f \cdot 2^k)$  has to fulfill the properties (1)  $val(s, e - k, f \cdot 2^k) = val(s, e, f)$  and (2)  $f \cdot 2^k \in [1, 2[:$

(1)  $val(s, e - k, f \cdot 2^k) = (-1)^s \cdot f \cdot 2^k \cdot 2^{e-k} = (-1)^s \cdot f \cdot 2^e = val(s, e, f).$

(2) From  $-log(f) \leq -\lfloor log(f) \rfloor < -log(f) + 1$ , it follows, that

$$\begin{array}{rcl} f \cdot 2^{-log(f)} & \leq & f \cdot 2^{-\lfloor log(f) \rfloor} < f \cdot 2^{-log(f)+1} \\ & f/f & \leq & f \cdot 2^{-\lfloor log(f) \rfloor} < 2f/f, \end{array}$$

and, therefore,  $f \cdot 2^k \in [1, 2]$ , as required.

(ii) We know from (i), that  $f \cdot 2^k \in [1, 2[$ , and therefore,  $f \in [2^{-k}, 2^{-k+1}[$ . From the condition  $f < 2^{-k+1}$ , it follows, that in the binary representation of f,  $f[0:\gamma] = bin_{-\gamma}^0(f)$ , the bits f[0:k-1] have to be zero. From  $f > 2^{-k}$  and  $f[0:k-1] = 0^k$ , it follows, that f[k] = 1. Thus,  $f[0:\gamma]$  contains exactly lz = k leading zeros and the lemma follows.  $\Box$

**Definition 2.4** In contrast to the definition of an unbounded normalization shift, we define a bounded normalization shift of (s, e, f) by the operation  $\lfloor \eta_{\beta} \rfloor (s, e, f) = (s'', e'', f'')$ :

$$\lfloor \eta_{\beta} \rfloor (s, e, f) = \begin{cases} (s', e', f') = \eta(s, e, f) & \text{if } e' \ge \beta \\ (s, \beta, f \cdot 2^{e-\beta}) & \text{otherwise,} \end{cases}$$

(2.1)

i.e., the factoring (s'', e'', f'') is normalized only if the normalization operation does not produce an exponent smaller than  $\beta$ . The result of a bounded normalization shift (s'', e'', f'')is called a bounded normalized factoring. From  $val(s, e, f) = val(s, \beta, f^{e-\beta})$  and definition 2.3, it follows that also the bounded normalization shift does not change the value of the factoring and we have  $val(\lfloor \eta_{\beta} \rfloor (s, e, f)) = val(s, e, f)$ .

#### 2.2.2 IEEE Numbers

Floating-point number types form subsets of the Reals. They can be represented by factorings with limited and discretized value ranges for exponents and significands. The IEEE floating-point types are defined by describing the possible choices for the sign, the exponent and the significand of a factoring and by the definition of some special values, so that each IEEE floating-point type (precision) consists of:

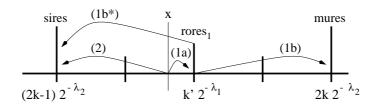

- Normalized numbers are represented by normalized factorings (s', e', f'), where the exponent e' is an integer in the range  $e_{min} \leq e' \leq e_{max}$  and the significand f' belongs to the discrete set  $\langle F'[0:p-1] \rangle_{neg} \in \{1, 1+2^{-p+1}, ..., 2-2^{-p+1}\}$ . The condition  $f' \in [1, 2]$  defines a normalized significand f'.

- Denormalized numbers are represented by factorings (s, e, f), where the exponent is  $e = e_{min}$  and the significand f belongs to the discrete set  $\langle f[0: p-1] \rangle_{neg} \in \{0, 2^{-p+1}, ..., 1-2^{-p+1}\}$ . As  $f \in [0, 1[$ , and thus  $f \notin [1, 2[$ , the significand is called denormalized.

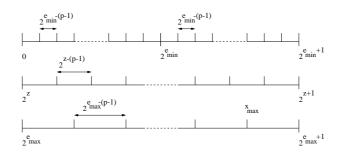

Figure 2.1: Geometry of IEEE floating-point numbers.

• Special values are defined by the set consisting of  $+\infty$ ,  $-\infty$  and two types of Not a Number (NaN): signaling NaN (sNaN) and quiet NaN (qNaN). These values can not be represented by factorings with finite exponents. Therefore, special bit strings for the representation of special numbers are used. Nevertheless, we use the symbols  $(0, e_{\infty}, f_{\infty})$  for the factoring of  $+\infty$  and the symbols  $(1, e_{\infty}, f_{\infty})$  for the factoring  $-\infty$ corresponding to the special bit strings for the IEEE infinity representations. The NaN representations are not unique. Therefore, if it does not matter which representation is chosen, we use the symbols  $(s, e_{sNaN}, f_{sNaN})$  for sNaN factorings and the symbols  $(s, e_{qNaN}, f_{qNaN})$  for qNaN factorings corresponding to an arbitrary IEEE NaN representation. If we want to refer to a specific NaN representation, we index them with a positive number, like in  $(s_1, e_{sNaN1}, f_{sNaN1})$  or  $(s_2, e_{qNaN2}, f_{qNaN2})$ . We define these factorings of special values to be normalized, so that the normalization shifts compute the identity function on them. Moreover, we extend the definition of the function val by  $val(s, e_{\infty}, f_{\infty}) = (-1)^s \cdot \infty$ ,  $val(s, e_{sNaN}, f_{sNaN}) = sNaN$  and  $val(s, e_{qNaN}, f_{qNaN}) = qNaN$ .

The union of normalized numbers and denormalized numbers form the *representable num*bers of an IEEE floating-point type. The geometry of the representable numbers is depicted in figure 2.1 on page 8 and shows the following properties:

- For every exponent value e between  $e_{min}$  and  $e_{max}$  there are two intervals of representable (normalized) numbers:  $[2^e, 2^{e+1}[$  and  $]-2^{e+1}, -2^e]$ . The gaps between consecutive representable numbers in these intervals are  $2^{e-(p-1)}$ .

- As the exponent value increases by one, the length of the interval  $[2^e, 2^{e+1}]$  doubles, and the gaps between the representable (normalized) numbers double as well. Thus, the number of representable numbers per interval is fixed and it equals  $2^{p-1}$ .

- The denormalized numbers are the representable numbers in the interval  $]-2^{e_{min}}, 2^{e_{min}}[$ . The gaps between consecutive representable numbers in this interval are  $2^{e_{min}-(p-1)}$ . Thus, the gaps in the interval  $[0, 2^{e_{min}}[$  equal the gaps in the interval  $[2^{e_{min}}, 2^{e_{min}+1}[$ . This property is called in the literature gradual underflow since the large gap between zero and  $2^{e_{min}}$  is filled with denormalized numbers.

The IEEE definition of normalized and denormalized floating-point numbers includes a definition of their factorings, so that we distinguish between the following sets of factorings of an IEEE floating-point type:

**Definition 2.5** The set of normalized IEEE factorings,  $NORfact_{n,p}$ , the set of denormalized IEEE factorings,  $DENfact_{n,p}$ , and the set of special IEEE factorings, SPEfact:

$$\begin{aligned} NORfact_{n,p} &= \{(s, e, f) \mid s \in \{0, 1\}, e \in \mathbb{Z} \text{ with } (e_{min} \leq e \leq e_{max}), \\ and \ b \in \mathbb{I} \text{ with } (0 \leq b < 2^{p-1}) : \quad f = 1 + b \cdot 2^{-(p-1)} \} \\ DENfact_{n,p} &= \left\{ (s, e_{min}, f) \mid s \in \{0, 1\}, b \in \mathbb{I} \text{ with } (0 \leq b < 2^{p-1}) : f = b \cdot 2^{-(p-1)} \right\} \\ SPEfact &= \{ (0, e_{\infty}, f_{\infty}), (1, e_{\infty}, f_{\infty}), (s, e_{qNaN}, f_{qNaN}), (s, e_{sNaN}, f_{sNaN}) \}. \end{aligned}$$

We define the set of IEEE factorings by

$$IEEE fact_{n,p} = DEN fact_{n,p} \cup NOR fact_{n,p} \cup SPE fact.$$

Accordingly, the following sets of numbers are defined:

**Definition 2.6** For each IEEE floating-point type, the set of normalized numbers,  $\mathcal{NOR}_{n,p}$ , the set of denormalized numbers,  $\mathcal{DEN}_{n,p}$ , and the set of IEEE special values,  $\mathcal{SPE}$ , are defined by

$$\mathcal{NOR}_{n,p} = \{x \mid \exists (s, e, f) \in NORfact_{n,p} : x = val(s, e, f)\}$$

$$\mathcal{DEN}_{n,p} = \{x \mid \exists (s, e, f) \in DENfact_{n,p} : x = val(s, e, f)\}$$

$$\mathcal{SPE} = \{+\infty, -\infty, qNaN, sNaN\}.$$

We define the set of representable numbers of an IEEE floating-point type,  $\mathcal{REP}_{n,p}$ , by

$$\mathcal{REP}_{n,p} = \mathcal{DEN}_{n,p} \cup \mathcal{NOR}_{n,p}.$$

The set of values of an IEEE floating-point type,  $\mathcal{FP}_{n,p}$ , additionaly includes the special values, so that

$$\begin{aligned} \mathcal{FP}_{n,p} &= \mathcal{DEN}_{n,p} \cup \mathcal{NOR}_{n,p} \cup \mathcal{SPE} \\ &= \mathcal{REP}_{n,p} \cup \mathcal{SPE}. \end{aligned}$$

**Lemma 2.4** The sets of denormalized and normalized IEEE numbers/factorings are disjunct:  $\mathcal{NOR}_{n,p} \cap \mathcal{DEN}_{n,p} = \emptyset$  and  $NORfact_{n,p} \cap DENfact_{n,p} = \emptyset$ . Thus, each IEEE floating-point value  $x \in \mathcal{FP}_{n,p}$  has a unique IEEE factoring  $(s, e, f) \in IEEEfact_{n,p}$  with x = val(s, e, f).

**Proof:** For normalized IEEE factorings  $(s_{nor}, e_{nor}, f_{nor}) \in NORfact_{n,p}$ , we have  $e_{nor} \geq e_{min}$  and  $f_{nor} \geq 1$ , so that  $|x_{nor}| = |val(s_{nor}, e_{nor}, f_{nor})| \geq 2^{e_{min}}$ . For denormalized IEEE factorings  $(s_{den}, e_{den}, f_{den}) \in DENfact_{n,p}$ , we have  $e_{den} = e_{min}$  and  $f_{nor} < 1$ , so that  $|x_{den}| = |val(s_{den}, e_{den}, f_{den})| < 2^{e_{min}}$ . Thus, all normalized IEEE factorings have a larger absolute value than each of the denormalized IEEE factorings,  $|x_{nor}| > |x_{den}|$ , so that  $\mathcal{NOR}_{n,p} \cap \mathcal{DEN}_{n,p} = \emptyset$  and  $NORfact_{n,p} \cap DENfact_{n,p} = \emptyset$ . For the second part of the lemma we additionally have to use, that also each special value has a unique factoring representation. This can easily be seen from the definitions of SPE and SPEfact.  $\Box$

**Lemma 2.5** From an arbitrary factoring  $(s, e, f) \in FACT(\mathcal{FP}_{n,p})$  of an IEEE FP number  $x = val(s, e, f) \in \mathcal{FP}_{n,p}$ , the bounded normalization shift  $[\eta_{e_{min}}](s, e, f) = (s'', e'', f'')$  computes the corresponding IEEE factoring  $(s'', e'', f'') \in IEEE fact_{n,p}$  with val(s'', e'', f'') = x = val(s, e, f).

| precision   | p         | n         | $bias_n$ | $e_{min}$     | $e_{max}$    | $ x _{min}$                              | $ x _{max}$                  |

|-------------|-----------|-----------|----------|---------------|--------------|------------------------------------------|------------------------------|

| single      | 24        | 8         | 127      | -126          | 127          | $\approx 1.4 \cdot 10^{-45}$             | $\approx 3.4 \cdot 10^{38}$  |

| single ext. | $\geq 32$ | $\geq 11$ |          | $\leq -1022$  | $\geq 1023$  |                                          | —                            |

| double      | 53        | 11        | 1023     | -1022         | 1023         | $\approx$ 4.9 $\cdot$ 10 <sup>-322</sup> | $\approx 1.8 \cdot 10^{310}$ |

| double ext. | $\geq 64$ | $\geq 15$ |          | $\leq -16382$ | $\geq 16383$ |                                          |                              |

Table 2.1: IEEE floating-point formats.

**Proof:** The proof consists of two parts for the cases: (a)  $val(s, e, f) \in \mathcal{DEN}_{n,p}$  and (b)  $(s, e, f) \in \mathcal{NOR}_{n,p}$ .

(a) For  $val(s, e, f) \in \mathcal{DEN}_{n,p}$ , there is a denormalized IEEE factoring  $(a, b, c) \in DEN fact_{n,p}$  with val(s, e, f) = val(a, b, c). We know already from the definition of the bounded normalization shift 2.4, that also val(s'', e'', f'') = val(s, e, f). From the definition of denormalized IEEE factorings (see definition 2.5), it follows that  $b = e_{min}$ . Therefore, for the proof of (s'', e'', f'') = (a, b, c) and  $(s'', e'', f'') \in DEN fact_{n,p}$ , it suffices to show that  $e'' = e_{min}$ . From  $val(s, e, f) \in \mathcal{DEN}_{n,p}$  it follows, that  $|val(s, e, f)| < 2^{e_{min}}$ . We consider the normalized factoring  $(s, e', f') = \eta(s, e, f)$ . Because  $f' \geq 1$ , and  $2^{e'} \cdot f' < 2^{e_{min}}$ , the exponent  $e' < e_{min}$  is smaller than the exponent bound of the bounded normalization shift. Therefore, it follows from the definition of  $\lceil \eta_{e_{min}} \rceil$  that  $e'' = e_{min}$  and part (a) of the proof is completed.

(b) For  $val(s, e, f) \in \mathcal{NOR}_{n,p}$ , we have to show that (s'', e'', f'') is normalized. From  $val(s, e, f) \in \mathcal{NOR}_{n,p}$ , it follows, that  $|val(s, e, f)| \geq 2^{e_{min}}$ . We consider the normalized factoring  $(s, e', f') = \eta(s, e, f)$ . Because f' < 2, and  $2^{e'} \cdot f' \geq 2^{e_{min}}$ , the exponent  $e' \geq e_{min}$  is larger than or equal to the exponent bound of the bounded normalization shift. Therefore, it follows from the definition of  $\lceil \eta_{e_{min}} \rceil$  that (s'', e'', f'') is the normalized factoring  $(s'', e'', f'') = \eta(s, e, f)$  and also part (b) of the proof is completed.

**Definition 2.7** If an unbounded normalization shift is computed on the factorings from  $FACT(\mathcal{FP}_{n,p})$ , we get a set, that includes the (unbounded) normalized factoring for each IEEE number in  $\mathcal{FP}_{n,p}$ . In this way we define the set of NF factorings NF fact<sub>n,p</sub> by:

$$NFfact_{n,p} = \{(s, e, f) \mid (s, e, f) \in FACT(\mathcal{FP}_{n,p}) \text{ and } (s, e, f) = \eta(s, e, f)\}$$

In the early days of floating-point design, many different formats with different values for  $e_{min}$ ,  $e_{max}$ , n and p were used. The success of the IEEE floating-point Standard 754-1985 [19] reduced the supported FP types to a few: *single*, *double*, *single* extended and *double* extended. The parameters for these precisions are given in table 2.1. In an IEEE compliant FPU-Design only some of these FP-types have to be implemented. We will focus on the implementation of the *single* and *double* precision types, because these types are most commonly used and the integration of additional types would be straight-forward.

#### 2.2.3 Packed IEEE Floating-Point Format

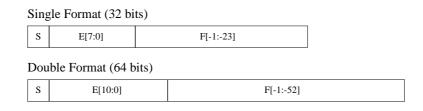

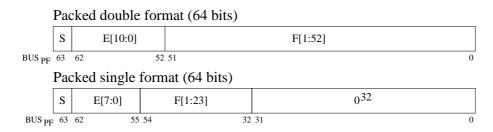

At the bit level, numbers in the single and double formats are composed of three fields corresponding to sign, biased exponent and fraction (significand without first bit) like depicted in figure 2.2. In the biased exponent representation, a bias of  $bias_n = 2^{n-1} - 1$  is used. Because  $bias_n = -e_{min} + 1 = e_{max}$  (see table 2.1 for single and double precision), the

Figure 2.2: Packed IEEE floating-point format.

value of  $e + bias_n$  is in the range  $1 \le e + bias_n \le 2^n - 2$ . Thus, the bit strings for 0 and  $2^n - 1$  do not occur in the *n*-bit biased binary representation  $E[n - 1 : 0] = bin_0^{n-1}(e + bias_n)$ . Therefore, the exponent strings  $E = 0^n$  and  $E = 1^n$  are used for the representation of denormalized numbers and special values.

The significand f of a representable number can be represented with p bits  $F[0:p-1] = bin_{-p+1}^{0}(f)$ . But only the fraction F[1:p-1] is included in the number string, and the hidden bit F[0] does not occur explicitly in the number representation. The hidden bit F[0] equals 1, iff f is normalized, and F[0] equals 0, iff f is denormalized. Because the exponent representation of  $e_{min}$  for denormalized numbers differs from all exponent representations from normalized numbers, the hidden bit F[0] can be extracted from the exponent representation.

The value of a number x represented by the packed representation (S, E[n-1:0], F[1:p-1]) is defined by

- 1. If  $E[n-1:0] = 0^n$  (denormalized numbers), then  $x = (-1)^{\mathbf{S}} \cdot < (0.F[1:p-1]) >_{neg} \cdot 2^{e_{min}}$ .

- 2. If  $E[n-1:0] \neq 0^n$  and  $E[n-1:0] \neq 1^n$  (normalized numbers), then  $x = (-1)^{\mathbf{S}} \cdot \langle (1.F[1:p-1]) \rangle_{neg} \cdot 2^{\langle E[n-1:0] \rangle_{bias_n}}$ .

- 3. If  $E[n-1:0] = 1^n$  (special values), then x is a special value depending on F[1:p-1]:

- If  $F[1:p-1] = 0^{p-1}$ , then x is  $\infty$  and has the sign of  $(-1)^S$ .

- If  $F[1:p-1] \neq 0^{p-1}$ , then x is NaN regardless of s.

The standard does not specify how to distinguish between signaling and quiet NaNs. We follow the specification used in [29] and distinguish between signaling and quiet NaNs by the value of f[1]: If f[1] = 1, then x is a signaling NaN (sNaN), otherwise x is a quiet NaN (qNaN).

#### 2.2.4 Operations

Beside floating-point types, the IEEE FP Standard defines arithmetic operations that have to be implemented in hardware or in software. In this section, we only define exact results of these operations for finite input operands  $x = val(s_x, e_x, f_x) \in \mathcal{REP}_{n,p}$  and  $y = val(s_y, e_y, f_y) \in \mathcal{REP}_{n,p}$ . The computations involving special values will be described later in combination with the exception handling. • Addition/substraction. We use the bit SOP to distinguish between addition (SOP = 0) and substraction (SOP = 1). The exact value of the addition/substraction result is defined by:

$$exact_{ADD/SUB} = x + (-1)^{\text{SOP}} \cdot y$$

The computation of the factoring of this value involves several steps. Therefore, we postpone its specification to the description of the addition implementations.

• Multiplication. The exact product of x and y is denoted by:

$$exact_{MULT} = x \cdot y = (-1)^{s_x + s_y} \cdot (f_x \cdot f_y) \cdot 2^{e_x + e_y}.$$

Thus,  $(s_x \otimes s_y, f_x \cdot f_y, e_x + e_y)$  is a factoring of  $exact_{MULT}$ .

• Division. The exact quotient of x and y is denoted by:

$$exact_{DIV} = x/y = (-1)^{s_x - s_y} \cdot (f_x/f_y) \cdot 2^{e_x - e_y}.$$

Thus,  $(s_x \otimes s_y, f_x/f_y, e_x - e_y)$  is a factoring of  $exact_{DIV}$ .

• Square-root. For non-negative  $x \ge 0$  the exact square-root of x is denoted by:

$$exact_{SQRT} = \sqrt{x} = \sqrt{f_x \cdot 2^{(e_x MOD2)}} \cdot 2^{e_x DIV2}$$

Thus,  $(0, \sqrt{f_x \cdot 2^{(e_x MOD2)}}, e_x DIV2)$  is a factoring of  $exact_{SQRT}$ .

• Remainder. For non-zero y the exact remainder xREMy is defined by:

$$exact_{REM} = x - y \cdot n,$$

where n is the integer nearest the exact value x/y; whenever |n - x/y| = 0.5, then n is even.

• Conversion. In conversions, the input operand has already the exact value of the conversion. This value has than to be converted to the destination's format.

$exact_{CONV} = x.$

In this operation we have to consider, that the input operand could also be an integer  $\langle x \rangle_2$  in two's complement representation. Then,

$$exact_{CONV} = \langle \mathbf{x} \rangle_2.$$

A factoring of  $exact_{CONV}$  is given by  $(s_x, e_x, f_x)$  or  $(sign(\langle x \rangle_2), 0, |\langle x \rangle_2|)$ .

Moreover, the computations of the absolute value  $(s_x := 0)$  and the negative of a floatingpoint number  $(s_x := not(s_x))$  are suggested to be implemented.

The floating-point types are not closed on all of these arithmetic operations. Therefore, the exact result of an operation might not belong to the same floating-point type. To be able to operate on results of operations, nevertheless, it is a basic principle of the IEEE standard to consider the exact result of an operation first and map it to a floating-point number by a selected rounding scheme to get a rounded result in the same floating-point type, finally.

Apart from that, the *test operation* (comparison) delivers a boolean value from two floating-point inputs. There are 26 different comparisons defined by the IEEE standard, which we decode by 5 condition code bits COND[4:0]. The bits COND[3:0] switch the conditions  $\{>, <, =, UNORDERD(?)\}$ , and COND[4] negates the boolean result bit. Only 26 of the 32 possible combinations are required by the standard. These are listed in table 2.2.

| condition    | $\operatorname{cond}[4:0]$ | > | < | = | ? | INV if ? |

|--------------|----------------------------|---|---|---|---|----------|

| =            | 00010                      | F | F | T | F | No       |

| ? <>         | 01101                      | T | T | F | T | No       |

| >            | 01000                      | T | F | F | F | Yes      |

| >=           | 01010                      | T | F | T | F | Yes      |

| <            | 00100                      | F | T | F | F | Yes      |

| <=           | 00110                      | F | T | T | F | Yes      |

| ?            | 00001                      | F | F | F | T | No       |

| <>           | 01100                      | T | T | F | F | Yes      |

| <=>          | 01110                      | T | T | T | F | Yes      |

| ? >          | 01001                      | T | F | F | T | No       |

| ?>=          | 01011                      | T | F | T | T | No       |

| ? <          | 00101                      | F | T | F | T | No       |

| ? <=         | 00111                      | F | T | T | T | No       |

| ? =          | 00011                      | F | F | T | T | No       |

| NOT(>)       | 11000                      | F | T | T | T | Yes      |

| NOT(>=)      | 11010                      | F | T | F | T | Yes      |

| NOT(<)       | 10100                      | T | F | T | T | Yes      |

| NOT(<=)      | 10110                      | T | F | F | T | Yes      |

| NOT(?)       | 10001                      | T | T | T | F | No       |

| NOT(<>)      | 11100                      | F | F | T | T | Yes      |

| NOT(<=>)     | 11110                      | F | F | F | T | Yes      |

| NOT(?>)      | 11001                      | F | T | T | F | No       |

| $NOT(? \ge)$ | 11011                      | F | T | F | F | No       |

| NOT(? <)     | 10101                      | T | F | T | F | No       |

| NOT(? <=)    | 10111                      | T | F | F | F | No       |

| NOT(? =)     | 10011                      | T | Т | F | F | No       |

Table 2.2: IEEE test operation (comparison).

# 2.3 Rounding

#### 2.3.1 IEEE Rounding Definition

IEEE rounding is a mapping from the reals into an IEEE floating-point type. The IEEE standard defines rounding in four rounding modes: round toward 0 (RZ), round to nearest(even) (RNE), round toward  $+\infty$  (RI) and round toward  $-\infty$  (RMI). Let  $\mathcal{REP}^{\infty} = \mathcal{REP} \cup \{+\infty, -\infty\}$ . For the rounding mode  $mode \in \{RZ, RNE, RI, RMI\}$ , we present the rounding definition of the IEEE standard by the description of the rounding function  $r_{mode} : \mathbb{R} \longrightarrow \mathcal{REP}^{\infty}$ . For the three directed rounding modes  $mode \in \{RZ, RI, RMI\}$  the obvious meaning of IEEE rounding is given by:

$$r_{RI}(x) = \min\{y \in \mathcal{REP}^{\infty} \mid x \leq y\}$$

$$r_{RMI}(x) = \max\{y \in \mathcal{REP}^{\infty} \mid x \geq y\}$$

$$r_{RZ}(x) = \begin{cases} r_{RMI}(x) & \text{if } x \geq 0\\ r_{RI}(x) & \text{if } x < 0. \end{cases}$$

The definition of the rounding function  $r_{RNE}$  is a bit more complicated. Let  $x_{max}^* = 2^{e_{max}}(2-2^{-p})$  and let  $y \in \mathcal{REP}$  be the representable number nearest to x if this is unique, otherwise let  $y \in \mathcal{REP}$  be the even representable number, that is nearest to x. Then,

$$r_{RNE}(x) = \begin{cases} +\infty & \text{if } x \ge x_{max}^* \\ -\infty & \text{if } x \le -x_{max}^* \\ y & \text{otherwise.} \end{cases}$$

#### 2.3.2 Rounding Functions

In this section we define rounding for a particular precision  $\lambda$ , so that a real number x is mapped to an integral multiple of  $2^{-\lambda}$ . For a precision  $\lambda$ , we define four rounding functions, that we index by the names of the four IEEE rounding modes RZ, RNE, RI, and RMI. We will show in the next section how these rounding functions can be used to implement IEEE rounding. For the definition of the rounding functions, we chose the integer t, so that  $t \cdot 2^{-\lambda} \leq x < (t+1) \cdot 2^{-\lambda}$  and  $t^*$  is the even number of the set  $\{t, t+1\}$ .

$$rnd_{RI,\lambda}(x) = \begin{cases} t \cdot 2^{-\lambda} & \text{if } x = t \cdot 2^{-\lambda} \\ (t+1) \cdot 2^{-\lambda} & \text{otherwise} \end{cases}$$

(2.2)

$$rnd_{RMI,\lambda}(x) = t \cdot 2^{-\lambda}$$

(2.3)

$$rnd_{RZ,\lambda}(x) = \begin{cases} t \cdot 2^{-\lambda} & \text{if } x \ge 0 \text{ OR } x = t \cdot 2^{-\lambda} \\ (t+1) \cdot 2^{-\lambda} & \text{otherwise} \end{cases}$$

(2.4)

$$rnd_{RNE,\lambda}(x) = \begin{cases} t \cdot 2^{-\lambda} & \text{if } x < (t+0.5) \cdot 2^{\lambda} \\ t^* \cdot 2^{-\lambda} & \text{if } x = (t+0.5) \cdot 2^{\lambda} \\ (t+1) \cdot 2^{-\lambda} & \text{otherwise} \end{cases}$$

(2.5)

For the rounding of sign-magnitude representations with  $x = (-1)^s \cdot |x|$ , the four IEEE rounding modes for the rounding of x can be reduced to the three IEEE rounding modes  $\{RZ, RNE, RI\}$  for the rounding of |x| [33]. This is done by reducing the directed rounding modes RZ, RI and RMI to the rounding modes RZ and RI for the rounding on positive arguments based on the sign s of the number. Thus, leaving only the three rounding modes RZ, RNE, and RI that have only to operate on the positive argument |x|. In conjunction

| mode | $RND\_MODE[1:0]$ | $mode \star 0$ : | $sr_Mode[1:0]$ | $mode \star 1:$ | $sr_Mode[1:0]$ |

|------|------------------|------------------|----------------|-----------------|----------------|

| RZ   | 00               | RZ               | 00             | RZ              | 00             |

| RNE  | 01               | RNE              | 01             | RNE             | 01             |

| RI   | 10               | RI               | 10             | RZ              | 00             |

| RMI  | 11               | RZ               | 00             | RI              | 10             |

Table 2.3: rounding mode reduction for sign-magnitude arguments

with table 2.3 for the rounding mode reduction, we define the  $\star$ -operation:

$$\star: \quad \{RZ, RNE, RI, RMI\} \times \{0, 1\} \longrightarrow \{RZ, RNE, RI\}$$

$$(mode, s) \longmapsto mode \star s$$

that maps the rounding mode *mode* and the sign s to the corresponding reduced rounding mode  $mode \star s$ . Based on this definition, the rounding mode reduction can be written as:

$$rnd_{mode,\lambda}(x) = rnd_{mode,\lambda}((-1)^s \cdot |x|) = (-1)^s \cdot rnd_{mode\star s,\lambda}(|x|).$$

If we encode the four IEEE rounding modes by  $RND\_MODE[1:0]$  and the three reduced rounding modes by  $SR\_MODE[1:0]$  according to table 2.3, the  $\star$ -operation can be expressed by the equations:

$$sr\_mode[1] = rnd\_mode[1] \land (rnd\_mode[0]\overline{\otimes}s)$$

(2.6)

$$\operatorname{sr_MODE}[0] = \operatorname{\overline{RND_MODE}[1]} \land \operatorname{RND_MODE}[0]. \tag{2.7}$$

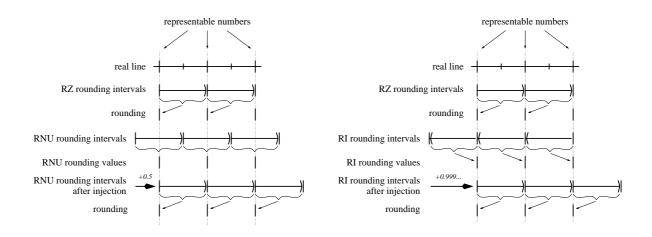

Furthermore, Quach et al. [33] suggested to implement RNE by round to nearest up (RNU). With an integer t, such that  $t \cdot 2^{-\lambda} \leq |x| < (t+1) \cdot 2^{-\lambda}$ , the rounding mode RNU is defined by:

$$rnd_{RNU,\lambda}(|x|) = \begin{cases} t \cdot 2^{-\lambda} & \text{if } |x| < (t+0.5) \cdot 2^{-\lambda} \\ (t+1) \cdot 2^{-\lambda} & \text{otherwise.} \end{cases}$$

(2.8)

The reason that RNE can be implemented by RNU is that  $rnd_{RNU,\lambda}(x) \neq rnd_{RNE,\lambda}(x)$ iff  $x = (t + 0.5) \cdot 2^{-\lambda}$  and the LSB of the binary encoding of  $(t + 1) \cdot 2^{-\lambda}$  is 1. Therefore, obtaining  $rnd_{RNE,\lambda}(x)$  from  $rnd_{RNU,\lambda}(x)$  can be accomplished by "pulling down" the LSB, when  $x = (t + 0.5) \cdot 2^{-\lambda}$ .

## 2.3.3 IEEE Rounding Functions

In this section a description of IEEE rounding is given, which is more practical than the definition by the IEEE standard. The following lemma shows how the rounding functions for a particular precision  $\lambda$  from the previous section are related to IEEE rounding. After that we will consider the IEEE rounding on factorings.

**Lemma 2.6** For  $2^{e'} \leq |x| < 2^{e'+1}$  and  $mode \in \{RZ, RNE, RI, RMI\}$ , let  $e'' = max\{e', e_{min}\}$  and  $xr = rnd_{mode, -e''+p-1}(x)$ . Then,

$$r_{mode}(x) = \begin{cases} \infty & \text{if } xr \ge 2^{e_{max}+1} \text{ and } mode \in \{RNE, RI\} \\ x_{max} & \text{if } xr \ge 2^{e_{max}+1} \text{ and } mode \in \{RZ, RMI\} \\ -x_{max} & \text{if } xr \le -2^{e_{max}+1} \text{ and } mode \in \{RZ, RI\} \\ -\infty & \text{if } xr \le -2^{e_{max}+1} \text{ and } mode \in \{RNE, RMI\} \\ xr & \text{otherwise} \end{cases}$$

**Proof:** In the definitions of IEEE rounding, in all cases the rounded result  $r_{mode}(x)$  is either the nearest number of the destination FP type that is larger than the operand x or the nearest number of the destination FP type that is smaller than or equal to the operand x. In the following, we distinguish between the cases: (a)  $|x| < x_{max}$  and (b)  $|x| \ge x_{max}$ .

(a) For  $|x| < x_{max}$ , we get  $|xr| \le x_{max} < 2^{e_{max}+1}$ , so that we have to show that the IEEE rounding definition from  $r_{mode}(x)$  is equivalent to  $rnd_{mode,-e''+p-1}(x)$  for all rounding modes. We will first show that the two possible rounding choices of the IEEE rounding definitions are identical to the two possible results from the definition of the function  $rnd_{mode,-e''+p-1}(x)$ .

(i) For  $|x| < 2^{e_{min}}$ , we are in the range of denormalized numbers, so that the gap between two consecutive FP numbers is  $2^{e_{min}-p+1}$  (see geometry of representable numbers in section 2.2.2) and there is an integer k, such that

$$f1 = k \cdot 2^{e_{\min} - p + 1} < x < (k + 1) \cdot 2^{e_{\min} - p + 1} = f2$$

and  $f1, f2 \in \mathcal{FP}_{n,p}$  are the nearest floating-point numbers in  $\mathcal{FP}_{n,p}$  larger than and smaller than or equal to x.

The definition of  $rnd_{mode, -e''+p-1}(x)$  uses the possible rounding results:  $f3 = l \cdot 2^{e''-p+1}$  and  $f4 = (l+1) \cdot 2^{e''-p+1}$  with  $f3 \leq x < f4$ . Since  $|x| < 2^{e_{min}}$ , we get  $e' < e_{min}$  and  $e'' = e_{min}$ . Thus, the possible rounding choices are the same like in the IEEE rounding definition:  $f1 = k \cdot 2^{e_{min}-p+1} = f3$  and  $f2 = (k+1) \cdot 2^{e_{min}-p+1} = f4$ .

(ii) For  $|x| \ge 2^{e_{min}}$ , we are in the range of normalized numbers, so that the gap between two consecutive FP numbers is  $2^{e'-p+1}$  (see geometry of representable numbers in section 2.2.2). In this case, there is an integer k, so that

$$f1 = k \cdot 2^{e'-p+1} \le x < (k+1) \cdot 2^{e'-p+1} = f2$$

and  $f1, f2 \in \mathcal{FP}_{n,p}$  are the nearest floating-point numbers in  $\mathcal{FP}_{n,p}$  larger than and smaller than or equal to x. Because for  $|x| \geq 2^{e_{min}}$ , we get  $e' \geq e_{min}$  and e'' = e', the numbers f1 and f2 agree with the two possible rounding results of the function  $rnd_{mode,-e'+p-1}(x) = rnd_{mode,-e'+p-1}(x)$  also in this case.

Based on the agreement of the two possible rounding choices, one can now easily check, that also the rounding decisions are the same for both the IEEE definition  $r_{mode}(x)$  and the rounding functions  $rnd_{mode,-e''+p-1}(x)$  for all four rounding modes. This completes the proof for case (a).