## **Control Flow Graphs for Real-Time System Analysis**

Reconstruction from Binary Executables and Usage in ILP-Based Path Analysis

#### Dissertation

Zur Erlangung des Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I der Universität des Saarlandes

> von Diplominformatiker **Henrik Theiling** aus Saarbrücken

Saarbrücken 2002

| Tag des Kolloquiums:          | 4. Februar 2003                                          |

|-------------------------------|----------------------------------------------------------|

| Dekan:                        | Prof. DrIng. Philipp Slusallek                           |

| Vorsitzender:                 | Prof. DrIng. Gerhard Weikum                              |

| Gutachter:                    | Prof. Dr. Reinhard Wilhelm                               |

| als Vertretung im Kolloquium: | Prof. Dr. Harald Ganzinger<br>Prof. Dr. Andreas Podelski |

| Beisitzer:                    | DrIng. Ralf Schenkel                                     |

#### Abstract

Real-time systems have to complete their actions w.r.t. given timing constraints. In order to validate that these constraints are met, static timing analysis is usually performed to compute an upper bound of the worst-case execution times (WCET) of all the involved tasks.

This thesis identifies the requirements of real-time system analysis on the *control flow graph* that the static analyses work on. A novel approach is presented that extracts a control flow graph from binary executables, which are typically used when performing WCET analysis of real-time systems.

Timing analysis can be split into two steps: a) the analysis of the behaviour of the hardware components, b) finding the worst-case path. A novel approach to path analysis is described in this thesis that introduces sophisticated interprocedural analysis techniques that were not available before.

### Zusammenfassung

Echtzeitsysteme müssen ihre Aufgaben innerhalb vorgegebener Zeitschranken abwickeln. Um die Einhaltung der Zeitschranken zu überprüfen, sind für gewöhnlich statische Analysen der schlimmsten Ausführzeiten der Teilprogramme des Echtzeitsystems nötig.

Diese Arbeit stellt die Anforderungen von Echtzeitsystem an den *Kontrollflußgraphen* vor, auf dem die statischen Analysen arbeiten. Ein neuartiger Ansatz zur Rückberechnung von Kontrollflußgraphen aus Maschinenprogrammen, die häufig die Grundlage der WCET-Analyse von Echtzeitsystemen bilden, wird vorgestellt.

WCET-Analysen können in zwei Teile zerlegt werden: a) die Analyse des Verhaltens der Hardwarebausteine, b) die Suche nach dem schlimmsten Ausführpfad. In dieser Arbeit wird ein neuartiger Ansatz der Pfadanalyse vorgestellt, der für ausgefeilte interprozedurale Analysemethoden ausgelegt ist, die vorher hier nicht verfügbar waren.

## **Extended Abstract**

Real-time systems are computer systems that have to perform their actions with fulfilment of timing constraints. Additional to performing the actions correctly, their correctness also depends on the fulfilments of these timing constraints.

The validation of timing aspects is called a *schedulability analysis*. A real-time system often consists of many tasks. Existing techniques for schedulability analysis require that the worst-case execution time (WCET) of each task is known.

Since the real WCET of a program is in general not computable, an upper bound to the real WCET has to be computed instead. For real-time systems, these WCET predictions must be *safe*, i. e., the real WCET must never be underestimated. On the other hand, to increase the probability of a successful schedulability analysis, the predictions should be as *precise* as possible.

Most static analyses, including approaches to WCET analysis, examine the control flow of the program. Because the behaviour of the program is typically not known in advance, an approximation to the control flow is used as the basis of the analysis. This approximation is called a *control flow graph*.

For good performance, modern real-time systems use modern hardware architectures. These use heuristic components, like caches and pipelines, to speed up the program in typical situations. Neglecting these speed up factors in a WCET analysis would lead to a dramatic overestimation of the real WCET of the program.

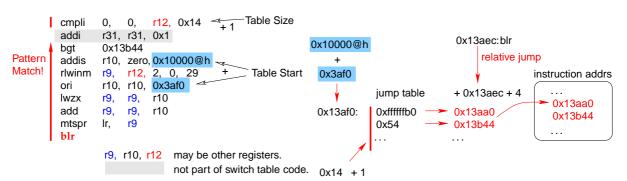

For taking into account hardware components, the program usually has to be analysed at the hardware level. Therefore, *binary executables* are the bases of analyses. Further, the timing behaviour of typical modern hardware depends on the data that is processed, and in particular on the addresses that are used to access memory. Again, full information about addresses is available from binary executables. The first part of this work presents a novel approach to extracting control flow graphs from binary executables. The general task is non-trivial, since often, the possible control flow is not obvious, e.g., when function pointers, switch tables or dynamic dispatch come into play. Further, it is often hard to predict what is the influence of a certain machine instruction on control flow, e.g., because its usage is ambiguous.

The reconstruction algorithms presented in this work are designed with real-time systems in mind. The requirements for a safe analysis also have to be considered during the extraction of control flow graphs from binaries, since analyses can only be safe if the underlying data structure is safe, too.

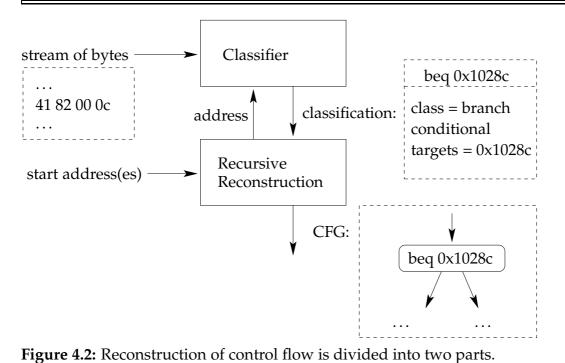

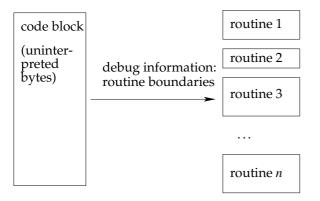

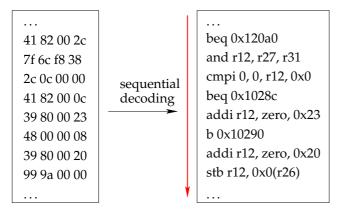

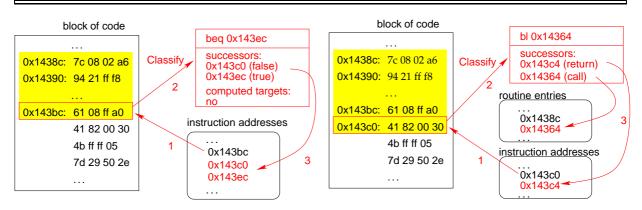

The reconstruction of control flow graphs from binary executables will be conceptually split into two separate tasks: a) given a stream of bytes from a binary executable and the address in the processor's code pointer, the precise classification of the instruction that will be executed by the machine, b) given a set of instruction classifications and possible program start nodes, the automatic composition of a safe and precise control flow graph.

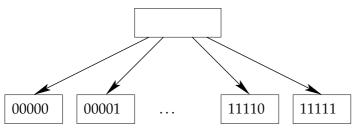

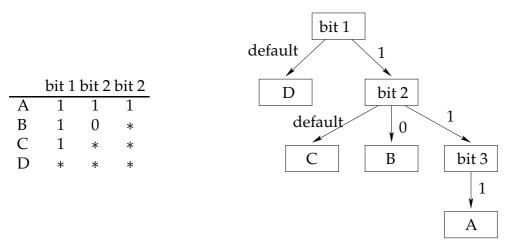

For solving the first task, we will use very efficient *decision trees* to convert raw bytes into instruction classifications. An algorithm will be presented that computes the decision trees automatically from very concise specifications that can trivially be derived from the vendor's architecture documentation. This is a novel approach that extricates the user from error-prone programming that had to be done in the past.

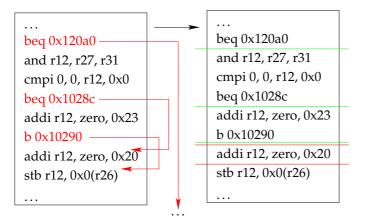

For the reconstruction of control flow from a set of instruction classifications, a *bottom-up approach* will be presented. This algorithm overcomes problems that top-down approaches usually have. Top-down approaches are fine for producing disassembly listings and for debugging purposes, but static analysis poses additional requirements on safety and precision that top-down algorithms cannot fulfil. Our bottom-up approach meets these requirements. Furthermore, it is implemented very efficiently.

The second part of this work deals with the analysis of real-time systems itself. Timing analysis that is close to hardware can be split into two parts: a) the analysis of the behaviour of the components at all blocks of the program and b) the computation of a global upper bound for the WCET based on the results of the analysis of each block. The latter analysis is called the *path analysis*.

An established technique of path analysis uses Integer Linear Programming (ILP). The idea is as follows: the program's control flow is described by a set of constraints, and the execution times of the program's blocks are combined in an objective function. The task of finding an upper bound of the WCET of the whole program is solved by maximising the objective function under consideration of the control flow constraints.

Because of the complex behaviour of modern hardware, sophisticated techniques for WCET analysis must typically be used. For instance, routine invocations in the program should not be analysed in isolation, since their timing behaviour may be very

different from invocation to invocation. This is because the state of the machine's hardware components is typically very different for each invocation and this state influences performance a lot.

For this reason, analyses usually perform better when they consider routine invocations in different execution *contexts*, where the contexts depend on the history of the program execution.

To make use of contexts, both parts of WCET analysis, the analysis of the hardware components and the path analysis must handle them. Up to now, it was not examined how path analysis can be done with arbitrary static assignment of execution contexts. This work will close this gap by presenting a new approach to ILP-based path analysis that can handle contexts, providing a high degree of flexibility to the user of the WCET analysis tool.

All algorithms presented in this thesis are implemented in tools that are now widely used in educational as well as industrial applications.

# Ausführliche Zusammenfassung

Echtzeitsysteme sind Computersysteme, die ihre Aufgaben innerhalb vorgegebener Zeitschranken erfüllen müssen. Zu ihre Korrektheit gehört zusätzlich zur funktionalen Korrektheit die Einhaltung dieser Zeitschranken.

Die Überprüfung des korrekten Zeitverhaltens nennt man *Planbarkeitsanalyse* (engl.: *schedulability analysis*). Ein Echtzeitsystem besteht häufig aus mehreren Teilprogrammen. In allen bekannten Ansätzen zur Planbarkeitsanalyse wird vorrausgesetzt, daß die schlimmste Ausführzeit (WCET, von engl. *worst-case execution time*) jedes einzelnen Teilprogramms bekannt ist.

Da die wirkliche Maximallaufzeit eines Programmes im allgemeinen nicht berechenbar ist, wird stattdessen eine obere Schranke berechnet. Bei Echtzeitsystemen müssen diese Vorhersagen *sicher* sein, d. h. die wirkliche Maximallaufzeit des Programmes darf niemals unterschätzt werden. Weiterhin sollten die Vorhersagen möglichst *genau* sein, um die Wahrscheinlichkeit einer erfolgreichen Planbarkeitsanalyse zu erhöhen.

Die meisten statischen Analysen, die WCET-Analyse eingeschlossen, untersuchen den Kontrollfluß eines Programmes. Da aber das Verhalten normalerweise vor Ablauf des Programms nicht bekannt ist, müssen Analysen mit einer Annäherung an den Kontrollfluß vorliebnehmen. Diese Annäherung nennt man *Kontrollflußgraph*.

Heutige Echtzeitsystem benutzen moderne Hardware, um deren Leistungsvorteile auszunutzen. Die Architekturen benutzen häufig heuristische Bausteine, wie Caches oder Pipelines, die die Ausführungsgeschwindigkeit des Programmes in häufig vorkommenden Situationen erhöhen sollen. Um starke Überschätzungen der Laufzeit zu vermeiden, muß eine WCET-Analyse typischerweise das Verhalten dieser Bausteine mitberücksichtigen.

Zur Vorhersage des Verhaltens von Hardwarebausteinen ist es normalerweise erforder-

lich, das Programm hardwarenah zu analysieren. Daher benutzt man für die Analyse das *Maschinenprogramm*. Die Ausführgeschwindigkeit hängt auch von den verarbeiteten Daten ab, vor allem von den Adressen, die zum Zugriff auf den Speicher benutzt werden. Auch aus diesem Grund verwendet man Maschinenprogramme, denn die nötigen Informationen sind dort vorhanden.

Im ersten Teil dieser Arbeit wird ein neuartiger Ansatz zur Rückberechnung von Kontrollflußgraphen aus Maschinenprogrammen vorgestellt. Die allgemeine Aufgabe ist schwierig, denn oft ist der mögliche Kontrollfluß nicht offensichtlich, z. B. bei der Verwendung von Funktionszeigern, switch-Tabellen oder dynamischen Methodenaufrufen. Desweiteren ist es häufig schwierig, vorherzusagen, welchen Einfluß bestimmte Befehlen auf den Kontrollfluß haben, da diese mitunter in verschiedenen Situationen auftauchen.

Der in dieser Arbeit vorgestellte Algorithmus zur Rückberechnung von Kontrollflußgraphen wurde unter besonderer Beachtung der speziellen Anforderungen von Echtzeitsystemanalyse entwickelt, denn ohne eine sichere Rückberechnung von Kontrollflußgraphen können darauf arbeitende Analysen ebenfalls nicht sicher sein.

Die Rückberechnung läßt sich in zwei Phasen zerlegen: a) die Erstellung einer Klassifizierung eines Maschinenbefehls bei Eingabe eines Byte-Stroms und der Adresse des Befehls, b) die automatische Rückberechnung eines sicheren und genauen Kontrollflußgraphen bei Eingabe einer Menge von Befehlsklassifikationen.

Um die erste Aufgabe zu lösen, werde ich einen sehr effizienten *Entscheidungsbaum* vorstellen, mit dessen Hilfe sich eine Folge roher Bytes in eine Befehlsklassifikation umwandeln läßt. Ein Algorithmus zur automatischen Berechnung eines solchen Entscheidungsbaums wird vorgestellt werden, der als Eingabe einzig eine Spezifikation erhält, die sich leicht aus der Architekturbeschreibung des Herstellers erstellen läßt. Dieser Ansatz befreit den Benutzer von fehlerträchtiger Programmierarbeit, die bisher nötig war.

Zur Rückberechnung eines Kontrollflußgraphen aus einer Menge von Befehlsklassifikationen wird ein *Bottom-Up-Ansatz* vorgestellt werden. Dieser überwindet Probleme von Top-Down-Ansätzen, die sich zwar gut zum Programmieren von Disassemblern oder Debuggern eignen, aber keineswegs den Anforderungen von Echtzeitsystemen gerecht werden. Unser Bottom-Up-Ansatz hingegen wird diesen gerecht und ist zudem sehr effizient implementiert.

Der zweite Teil dieser Arbeit behandelt die Analyse von Echtzeitsystemen selbst. Hardwarenahe WCET-Analyse kann man in zwei Teile aufspalten: a) die Analyse des Verhaltens der Hardwarebausteine für jeden Block des Programmes, b) die Berechnung einer oberen Schranke der WCET des Programms basierend auf den Ergebnissen der Analyse in a). b) nennt man *Pfadanalyse*.

Eine verbreitete Methode der Pfadanalyse benutzt Ganzzahlige Lineare Program-

mierung (ILP von engl. *Integer Linear Programming*). Die Idee dabei ist, daß man den Kontrollfluß des Programmes durch Nebenbedingungen beschreibt und die Laufzeiten der einzelnen Blöcke des Programmes in einer Zielfunktion zusammenfaßt. Das Maximierungsproblem der Zielfunktion unter Beachtung der Nebenbedingungen löst dann das Problem der Suche nach einer oberen Schranke für die Maximallaufzeit des Programmes.

Weil moderne Hardware sich komplex verhält, müssen normalerweise ausgefeilte Methoden zur WCET-Analyse verwendet werden. Beispielsweise sollten Routinenaufrufe nicht isoliert behandelt werden, da sich ihr Verhalten von Aufruf zu Aufruf stark unterscheiden kann. Das liegt daran, daß der Zustand der Hardwarebausteine die Ausführzeiten stark beeinflussen.

Aus diesem Grunde verbessert man die Vorhersagen für gewöhnlich, indem man Routinenaufrufe in verschiedenen *Kontexten* analysiert, wobei die Kontexte davon abhängen, was im Programm vorher schon ausgeführt wurde.

Um von Kontexten Gebrauch zu machen, müssen beide Teile der WCET-Analyse, die der Bausteine und die Pfadanalyse, sie verarbeiten können. Bisher war es nicht untersucht, wie man auf ILP beruhende Pfadanalysen mit beliebigen statisch berechneten Kontextzuweisungen durchführen kann. Diese Arbeit schließt diese Lücke und stellt einen Ansatz vor, der dem Benutzer des Analysewerkzeugs einen hohen Grad an Freiheit überläßt.

Alle in dieser Arbeit vorgestellten Algorithmen sind in Werkzeugen implementiert, die inzwischen in universitärem wie industriellem Gebrauch sind.

## Acknowledgements

First of all, I very much thank Reinhard Wilhelm for letting me have the opportunity to work and research at his chair and to write my thesis about this challenging and interesting topic. He was very helpful in discussions about this work and provided me with a lot of freedom for approaching my goals.

The research group provided a very pleasant working atmosphere. I would like to thank Michael Schmidt for our good team work with discussions about interfaces, implementation and algorithms. We implemented parts of the overall WCET framework together and Michael also contributed by writing some modules for exec2crl. Thanks are also due to Florian Martin and Christian Ferdinand for fruitfully discussing a lot of different topics with me. They often found peculiarities and had many hints and ideas. Thanks to Reinhold Heckmann for providing helpful thoughts and links to other peoples' research from most different areas of computer science. He was also a great help for me by proof-reading this thesis.

For excellent team work and discussions, I also thank Daniel Kästner, Marc Langenbach and Martin Sicks. Nico Fritz did a magnificent job implementing the ARM decoder module for exec2crl, despite his being a complete novice to its internal structure when he began.

During international conferences and other occasions, the whole real-time community constituted a nice atmosphere. Most notably, I had a lot of discussions with Sheayun Lee, Sungsoo Lim, Jan Gustafsson, Jakob Engblom and Andreas Ermedahl.

Thanks to Uta Hengst, Björn Huke, Daniel Kästner, Markus Löckelt and Nicola Wolpert for proof-reading parts of this work and giving valuable hints.

Last but not least, I would like to thank my family for their support during the time of my research and also Uta Hengst and Florian Martin for continuously reminding me to work hard.

# Contents

| Ι | Int  | roduc  | tion                            | 23 |

|---|------|--------|---------------------------------|----|

| 1 | Intr | on     | 25                              |    |

|   | 1.1  | Timin  | g Analysis of Real-Time Systems | 25 |

|   | 1.2  | Contro | ol Flow Graphs                  | 27 |

|   | 1.3  | Path A | Analysis                        | 28 |

|   | 1.4  | Scope  | of this Thesis                  | 30 |

|   |      |        |                                 |    |

| 2 | Basi | CS     |                                 | 33 |

|   | 2.1  | Select | ed Mathematical Notations       | 33 |

|   | 2.2  | Progra | am Structure                    | 34 |

|   |      | 2.2.1  | Programs and Instructions       | 34 |

|   |      | 2.2.2  | Basic Blocks                    | 35 |

|   |      | 2.2.3  | Routines                        | 35 |

|   |      | 2.2.4  | Control Flow Graph              | 36 |

|   |      | 2.2.5  | Call Graph                      | 36 |

|   |      | 2.2.6  | Example in C                    | 37 |

|   |      | 2.2.7  | Loops                           | 38 |

|   |      |        |                                 |    |

C

Г

|    | 2.3          | Intege   | r Linear Programming                         | 41 |

|----|--------------|----------|----------------------------------------------|----|

|    |              | 2.3.1    | Linear Programs                              | 41 |

|    |              | 2.3.2    | Simplex Algorithm                            | 43 |

|    |              | 2.3.3    | Integer Linear Programs                      | 44 |

|    |              | 2.3.4    | Branch and Bound Algorithm                   | 45 |

| 3  | Con          | trol Flo | ow Graphs                                    | 47 |

|    | 3.1          |          | ol Flow Graphs for Real-Time System Analysis | 47 |

|    |              | 3.1.1    | Safety                                       |    |

|    |              | 3.1.2    | Precision                                    |    |

|    | 3.2          | Detail   | ed Structure of CFG and CG                   | 48 |

|    |              | 3.2.1    | Alternative Control Flow and Edge Types      | 49 |

|    |              | 3.2.2    | Unrevealed Control Flow                      |    |

|    |              | 3.2.3    | Calls                                        | 50 |

|    |              | 3.2.4    | External Routines                            |    |

|    |              | 3.2.5    | Difficult Control Flow                       | 53 |

|    | 3.3          | Conte    | xts                                          | 54 |

|    |              | 3.3.1    | CallString(k)                                | 56 |

|    |              | 3.3.2    | Graphs with Context                          | 57 |

|    |              | 3.3.3    | Iteration Counts for Contexts                | 59 |

|    |              | 3.3.4    | Recursive Example                            | 59 |

|    |              | 3.3.5    | VIVU(n,k)                                    | 60 |

|    |              | 3.3.6    | Example                                      | 63 |

|    |              |          | -                                            |    |

| II | Co           | ontrol   | Flow Graphs and Binary Executables           | 65 |

| 4  | Intr         | oductio  | n                                            | 67 |

| I  | 4.1          |          | ems                                          |    |

|    | <b>T • T</b> | 1 10010  |                                              | 07 |

|   | 4.3  | Versat  | ility                                  | 71 |

|---|------|---------|----------------------------------------|----|

| 5 | Mac  | hine C  | ode Decoding                           | 73 |

|   | 5.1  | Introd  | uction                                 | 73 |

|   |      | 5.1.1   | Bit Patterns                           | 73 |

|   |      | 5.1.2   | Selected Design Goals                  | 74 |

|   |      | 5.1.3   | Chapter Overview                       | 76 |

|   | 5.2  | Data S  | Structure                              | 76 |

|   |      | 5.2.1   | Selection Algorithm                    | 77 |

|   |      | 5.2.2   | Restrictions on Pattern Sets           | 79 |

|   | 5.3  | Auton   | natic Tree Generation                  | 80 |

|   |      | 5.3.1   | Idea                                   | 80 |

|   |      | 5.3.2   | Algorithm                              | 81 |

|   |      | 5.3.3   | Default Nodes                          | 83 |

|   |      | 5.3.4   | Unresolved Bit Patterns                | 85 |

|   |      | 5.3.5   | Termination                            | 85 |

|   |      | 5.3.6   | Proof of Correctness                   | 85 |

|   | 5.4  | Efficie | nt Implementation                      | 87 |

|   |      | 5.4.1   | Complexity                             | 88 |

|   |      | 5.4.2   | Generalisation                         | 88 |

|   | 5.5  | Summ    | ary                                    | 88 |

| 6 | Reco | onstruc | tion of Control Flow                   | 89 |

|   | 6.1  | Introd  | uction                                 | 89 |

|   |      | 6.1.1   | Overview                               | 90 |

|   | 6.2  | Appro   | paches to Control Flow Reconstruction  | 90 |

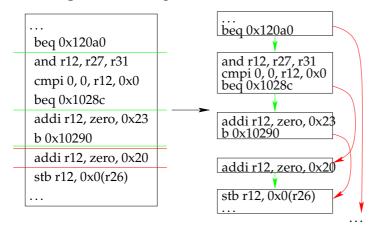

|   |      | 6.2.1   | Top-Down Approach                      | 91 |

|   |      | 6.2.2   | Problems Unsolved by Top-Down Approach | 92 |

|   |      | 6.2.3   | Intuition of Bottom-Up Approach        | 94 |

|   |      |         |                                        |    |

E

|     | 6.2.4 | Theory                      |

|-----|-------|-----------------------------|

| 6.3 | Modu  | lar Implementation          |

| 6.4 | The C | ore Algorithms              |

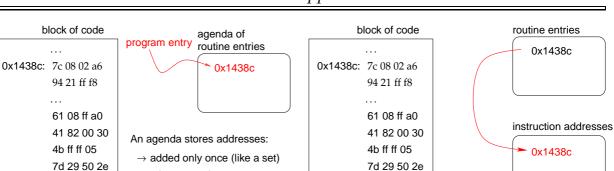

|     | 6.4.1 | Gathering Routines          |

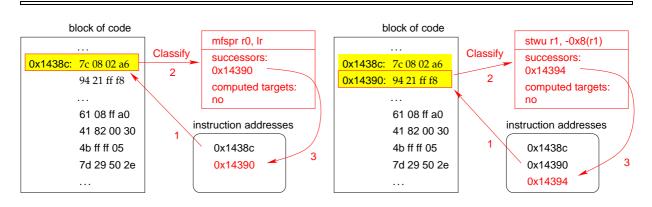

|     | 6.4.2 | Decoding a Routine          |

|     | 6.4.3 | Properties of the Algorithm |

| 6.5 | Imple | mentation                   |

|     | 6.5.1 | PowerPC                     |

|     | 6.5.2 | Infineon TriCore            |

|     | 6.5.3 | ARM                         |

107

119

## III Path Analysis

| 7 | Imp | licit Pa | th Enumeration (IPE)         | 109   |

|---|-----|----------|------------------------------|-------|

|   | 7.1 | Times    | and Execution Counts         | . 109 |

|   | 7.2 | Handl    | ling Special Control Flow    | . 110 |

|   |     | 7.2.1    | External Routine Invocations | . 110 |

|   |     | 7.2.2    | Unresolved Computed Branches | . 111 |

|   |     | 7.2.3    | Unresolved Computed Calls    | . 111 |

|   |     | 7.2.4    | No-return calls              | . 111 |

|   | 7.3 | ILP .    |                              | . 112 |

|   |     | 7.3.1    | Objective Function           | . 112 |

|   |     | 7.3.2    | Program Start Constraint     | . 113 |

|   |     | 7.3.3    | Structural Constraints       | . 113 |

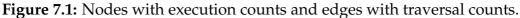

|   |     | 7.3.4    | Loop Constraints             | . 115 |

|   |     | 7.3.5    | Time Bounded Execution       | . 116 |

|   |     | 7.3.6    | User Added Constraints       | . 117 |

|   |     |          |                              |       |

#### 8 Interprocedural Path Analysis

| 8.1 | Basic  | Constraints                                   |

|-----|--------|-----------------------------------------------|

|     | 8.1.1  | Objective Function                            |

|     | 8.1.2  | Program Start Constraint                      |

|     | 8.1.3  | Structural Constraints                        |

| 8.2 | Loop   | Bound Constraints                             |

|     | 8.2.1  | Simple Loop Bound Constraints                 |

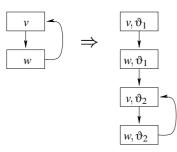

|     | 8.2.2  | Loop Bound Constraints for $VIVU(x,\infty)$   |

|     | 8.2.3  | Loop Bound Constraints for Arbitrary Mappings |

| 8.3 | User A | Added Constraints                             |

|     |        |                                               |

### IV Evaluation

E

135

| 9  | Expe | erimental Results                         | 137 |

|----|------|-------------------------------------------|-----|

|    | 9.1  | Implementation                            | 137 |

|    | 9.2  | Decision Trees                            | 137 |

|    | 9.3  | CFG Reconstruction                        | 139 |

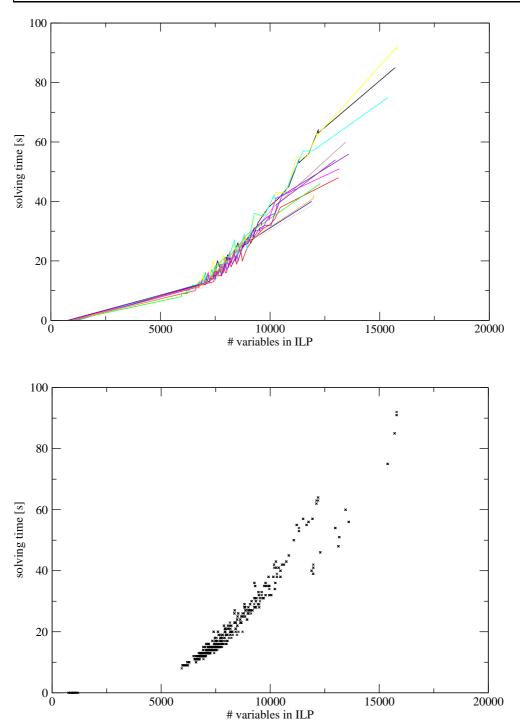

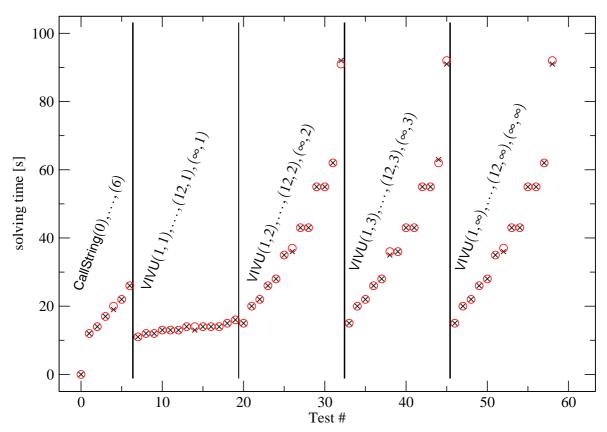

|    | 9.4  | Path Analysis                             | 141 |

| 10 | Rela | ted Work                                  | 147 |

|    | 10.1 | History of WCET Analysis                  | 147 |

|    |      | 10.1.1 Abstract Interpretation            | 147 |

|    |      | 10.1.2 Worst-Case Execution Time Analysis | 148 |

|    | 10.2 | Decision Trees                            | 150 |

|    | 10.3 | ICFG Reconstruction                       | 151 |

|    | 10.4 | Path Analysis                             | 152 |

| 11 | Con  | clusion                                   | 155 |

|    | 11.1 | Decision Trees                            | 155 |

|    | 11.2 | CFG Reconstruction                        | 156 |

E

| 11.3   | Path A                   | analysis                   | 57             |

|--------|--------------------------|----------------------------|----------------|

| 11.4   | Histor                   | y & Development            | 57             |

| 11.5   | Outloo                   | ok                         | 58             |

|        | 11.5.1                   | Cycles                     | 58             |

|        | 11.5.2                   | CFG Reconstruction         | 59             |

|        | 11.5.3                   | Architectures              | 59             |

|        |                          |                            |                |

|        |                          |                            |                |

| A Expe | eriment                  | ts in Tables and Figures 1 | 61             |

| -      |                          | ts in Tables and Figures 1 |                |

| -      | Path A                   | 0                          | 61             |

| -      | Path A<br>A.1.1          | analysis                   | 61<br>61       |

| -      | Path A<br>A.1.1<br>A.1.2 | Analysis                   | 61<br>61<br>64 |

# Part I

Introduction

# Chapter 1 Introduction

## 1.1 Timing Analysis of Real-Time Systems

The fundamental characteristic of real-time systems is that they are subject to timing constraints that determine when actions have to be taken. The fulfilment of these timing constraints, additional to the operational results, is part of the correctness of a real-time system.

In literature, real-time systems are usually divided into two types: hard and soft realtime systems, depending on whether their timing constraints are imperative or desirable. If not explicitly stated otherwise, the term *real-time system* will be used for a hard real-time system in this work. The imperative nature of the timing constraints makes static analysis particularly interesting for real-time system validation.

Real-time systems occur in many areas, e.g. in process control, nuclear power plants, avionics, air traffic control, medical devices, defence applications and controllers in automobiles.

A failure of a safety critical real-time system can lead to considerable damage or even a loss of lives. Therefore, the system must be validated. Among other properties, it has to be shown that it fulfils all its timing constraints. The validation of timing aspects is called a *schedulability analysis* (*see* [Liu and Layland., 1973; Stankovic, 1996]).

A real-time system is often composed of many tasks. All existing techniques for schedulability analysis require the worst-case execution time (WCET) of each task in the system to be known.

Since the exact WCET is in general not computable, estimations of the WCET have to be calculated. These estimations have to be *safe*, meaning they must never underestimate the actual WCET.

On the other hand, the WCET approximation should be *tight*, i.e., the overestimation should be as small as possible. This helps to reduce the costs for the hardware and increases the chances of a successful timing validation.

For simple hardware, i. e. for a processor with a fixed execution time for each instruction, estimation of the WCET is quite easy: if each instruction's execution time is known, the WCET can be computed by recursively combining execution times along the syntax tree of the program. This method was used in [Puschner and Koza, 1989] and in [Park and Shaw, 1991].

Modern hardware, however, becomes increasingly difficult to predict due to sophisticated heuristic components that increase execution speed of instructions for common special cases, which most likely make programs much faster on average, while single instructions may still be slow. This means that simple, conservative analysis techniques strongly overestimate the actual WCET.

The execution time of an instruction may depend on the internal state of the processor. This state gets more and more complex with the presence of the mentioned heuristic components. Therefore, predicting the relevant parts of the processor's internal state that influence the timing behaviour becomes more and more difficult. The following list shows some components of modern hardware that make predictions complicated.

**Pipelines.** Processing of a single instruction is usually split into several steps in a microprocessor: e.g., instruction fetch, instruction decode, compute, write-back, etc.. For one instruction, only one of these steps is used at the same time. Therefore, the idea is to use free components for other instructions in parallel.

This leads to *overlapping execution of instructions*, so-called *pipelining*. And because there might be dependencies between the instructions (e.g., a computed value is needed by a subsequent instruction), this means that interaction can occur between instructions that are executed after one another.

**Caches.** *Caches*, i. e. fast memory with limited size between the processor and the main memory of the computer, make execution times depend on execution history, because the access time of a cache depends on what was accessed before.

The degree of predictability of caches depends on various aspects, e.g. on the type of data stored in the cache (instructions or data, or even mixed) and on the cache design, in particular the cache replacement policy.

**Speculative execution.** To keep the pipeline filled at branches in the program, modern processors often implement a *branch prediction*, i.e. a heuristics to predict what is executed after a conditional branch when the condition is not yet known. These processors then speculatively fetch instructions from memory, which are discarded if the prediction is found to having been wrong. This mechanism often influences the cache behaviour in most complex ways.

The above list is not exhaustive.

Instructions not only interact with adjacent instructions w.r.t. their execution times, but also with very distant instructions in the program and even with themselves during subsequent executions. Additionally, the execution time depends on the input data for the instructions. Therefore, a simple method of recursively composing the run-time is usually not feasible for modern architectures.

## **1.2 Control Flow Graphs**

Most static analyses work along the control flow of a program. The abstract concept of control flow has to be approximated by a data structure for analysis. One common structure is a *control flow graph*. In the following, the more precise term *interprocedural control flow graph* (ICFG) will be used. (The difference will be formally introduced later.)

Usually, the actual control flow is not fully known in general due to complex control transfers (e.g. computed branches, function pointers, dynamic dispatch, etc.). The more precise the approximating ICFG is, the more precise the analysis will be. Most importantly for real-time systems, it is vital that the approximating ICFG is *safe* under all circumstances.

Work about static analysis usually comes with the assumption that an ICFG is available. Even if it is, we must guarantee that the approximation is safe.

In order to estimate the WCET of a program, the analysis has to take the timing semantics of all hardware components into account. For this, it is vital on modern architectures to take all parts of hardware into account. Therefore, an analysis must typically consider the *machine code level*.

Further, for predicting their precise behaviour, all aspects that lead to different timing behaviour in any involved hardware component must be known. Any higher level than machine code might lack vital information. E. g., assembly code lacks information about addresses. Similarly, even compiled object files containing machine code sections lack the information about absolute location in memory, making predictions of memory accesses impossible. For these reasons, our framework performs WCET analysis on *statically linked binary executables*.

Dealing with binary executables, the question arises whether an ICFG is really available and whether this ICFG is really safe. Compilers often generate debug code containing information about the ICFG of the program. Unfortunately, though, one usually cannot always assume that this information is correct. Due to code optimisations the compiler may have performed, the hints about the ICFG often only correspond vaguely with reality.

It is even more unfortunate that executables for real-time systems most likely have no debug information at all, at least not for all parts, since *hand-written assembly code* is often included. E.g., hand-written assembly code can certainly be found in the real-time operating system, which is part of the statically linked executable.

In this work, an approach to a safe and precise ICFG reconstruction for real-time system analysis will be presented. The reconstruction problem will be discussed in detail in Chapter 4.

## 1.3 Path Analysis

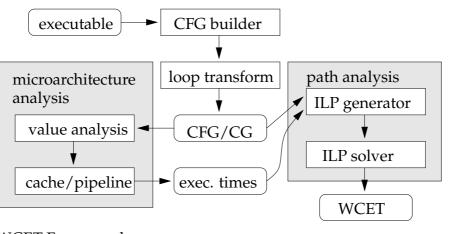

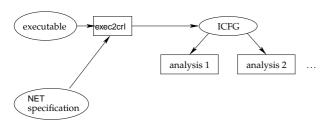

Our analysis framework for predicting the worst-case execution time (WCET) of binary executables for real-time systems is depicted in Figure 1.1. A WCET analysis can be split into two basic steps.

The first step is the *microarchitecture analysis*. The result of the first step is a worst-case execution time for each basic block of the program under examination.

The microarchitecture analysis consists of a chain of sub-analyses for different parts of the hardware, like value analysis (to find values of registers, in particular addresses for memory access), cache, pipeline and memory bus analyses. In our framework, all these

analyses are implemented with the PAG tool (*see* [Martin, 1995b; Martin, 1999b]), that uses Abstract Interpretation (AI) (*see* [Cousot and Cousot, 1977a; Nielson et al., 1999]) for analysis.

The second step of a WCET analysis is the worst-case path analysis. Based on the results of the microarchitecture analysis, it computes an upper bound of the actual WCET. We will call this the *predicted WCET* in the following.

Path analyses can be implemented in several ways. Because of good precision and speed, we use Implicit Path Enumeration (IPE) (*see* [Li et al., 1995a; Li et al., 1996]), which uses Integer Linear Programming (ILP) (*see* [Chvátal, 1983]) to find the WCET. In this approach, the ICFG of the program is represented by a set of linear constraints. Further, the objective function contains the execution time of each block of the program. Then, finding the predicted WCET is the problem of maximising the objective function. Chapter 7 will introduce this technique in detail.

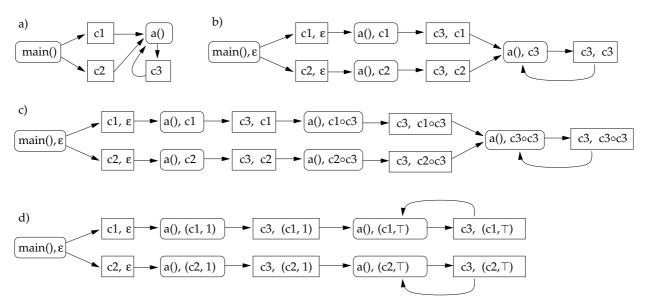

Due to important deviation in whether routines are executed in isolation or in contexts, routine invocations can be distinguished by their execution history, e.g., by their *call stacks* as distinctive features. These distinctions are called execution *contexts*. The precise methods of assigning contexts will be introduced in Chapter 3 and Chapter 8.

To make use of contexts, the original ICFG is transformed into one where nodes are split according to their distinctive contexts. The resulting graph, the *ICFG with contexts*, is then used for analysis instead of the original graph without contexts.

Our work group's PAG tool for writing analyses using Abstract Interpretation comes with interprocedural analysis methods, so ICFGs with contexts are can be used directly by the microarchitecture analysis chain.

Up to now, ILP-based path analysis was not well adapted to interprocedural analysis methods. It was shown in previous work (*see* [Theiling et al., 2000]) that it is possible in principle to combine microarchitecture analysis by Abstract Interpretation with path analysis by IPE. However, ways of using arbitrary methods of context computation were still unexamined. Chapter 8 proposes a general method of combining interprocedural analysis methods with ILP-based path analysis.

The task is non-trivial. ILP-based path analysis generates an *objective function* and some sets of constraints of the following types:

Entry constraints. These state that the program entry is executed once.

**Structural constraints.** These describe incoming and outgoing control flow at each basic block.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>A basic block is a sequence of instructions in which control flow enters only at the beginning and leaves at the end with no possibility of branching except at the end.

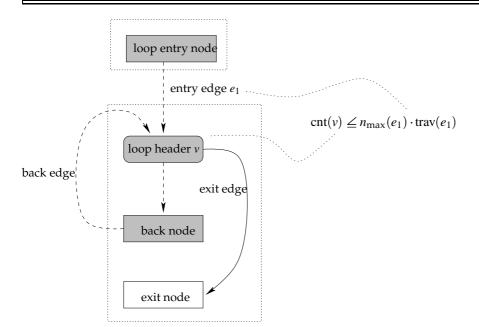

- **Loop bound constraints.** Each loop needs a maximal iteration count to make the ILP bounded. For good precision of analysis of loops, context distinction is desirable for different iterations. This is made possible by transforming loops into tail recursive functions, so that interprocedural analysis methods become applicable.

- **User defined additional constraints.** To improve precision by adding facts the user knows to the set of constraints.

Most of these constraints can be generated in a straight-forward way even for graphs with contexts. However, recursion poses a problem, since the presence of contexts restructures the analysis graphs w.r.t. the structure of cycles: entry and back edges of cycles in the original graph are not necessarily entry and back edges of cycles in the graph with context. Hence, a correspondence has to be found.

Chapter 8 will present how interprocedural analysis methods can be used for ILP-based path analysis, dealing with the trade-off between analysis precision and speed. On the one hand, high precision by using many contexts is desired, but one the other hand, a distinction by the whole execution history is usually too expensive. For best results, context computation should be as flexible as possible and should be limitable and adjustable for different programs under examination. Therefore, we will outline an algorithm for generating constraints, especially loop bound constraints, for ILP-based path analyses with arbitrary static context computations.

## 1.4 Scope of this Thesis

We needed ICFGs in a framework for WCET analysis for real-time systems.<sup>2</sup>

In this thesis, I focus on the problem of constructing ICFGs for that WCET analysis framework. I will identify the requirements for real-time systems and present safe, precise and also fast algorithms.

Further, I introduce a novel approach to interprocedural path analysis. Among other things, this will show that the reconstructed ICFGs are perfectly suited for WCET analysis for real-time systems.

Consequently, this document is split into two major parts:

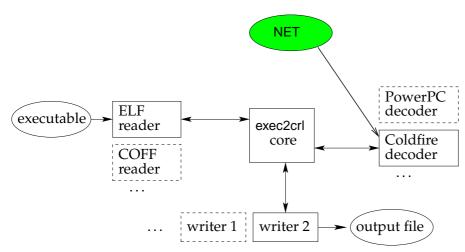

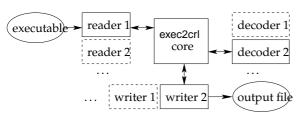

1. The design and implementation of novel algorithms for ICFG reconstruction will be presented in the first part. The modular and versatile tool exec2crl is the result.

<sup>&</sup>lt;sup>2</sup>Our work group was partially supported by the research project *Transferbereich* 14, *Runtime Guarantees for Modern Architectures by Abstract Interpretation*, 1999–2001, of Deutsche Forschungsgemeinschaft.

2. A new approach to interprocedural path analysis will be introduced in the second part. The approach is much more generic than previous work.

The following list is a detailed overview of the structure of this work.

Part 1 contains chapters that introduce basic notations, terms and methods.

Chapter 2 introduces basic symbols and terms used in the following chapters.

- **Chapter 3** describes control flow graphs with their special properties and requirements for real-time system analysis. Also, methods of interprocedural analysis are introduced here.

- **Part 2** contains chapters that describe different stages of ICFG reconstruction implemented in our reconstruction tool exec2crl.

- **Chapter 4** describes the steps that are performed during a safe and precise extraction of control flow from binary executables.

- **Chapter 5** outlines the algorithms that are used to automatically transform a vendor's machine description into a very efficient data structure that can be used for classifying single machine instructions.

- **Chapter 6** presents the core of exec2crl, i. e., the algorithms it uses to safely reconstruct the whole ICFG of a program from instruction classifications.

- **Part 3** contains chapters that present the interprocedural path analysis developed for our analysis framework.

- **Chapter 7** introduces the well-known technique of implicit path enumeration (IPE) that is widely used today for implementing path analyses.

- Chapter 8 presents our novel extension to IPE for interprocedural analysis.

- **Part 4** contains chapters that evaluate my work.

- Chapter 9 presents the experimental results.

- Chapter 10 concludes this work and discusses possible future work.

- Chapter 11 relates this work to that of other researchers.

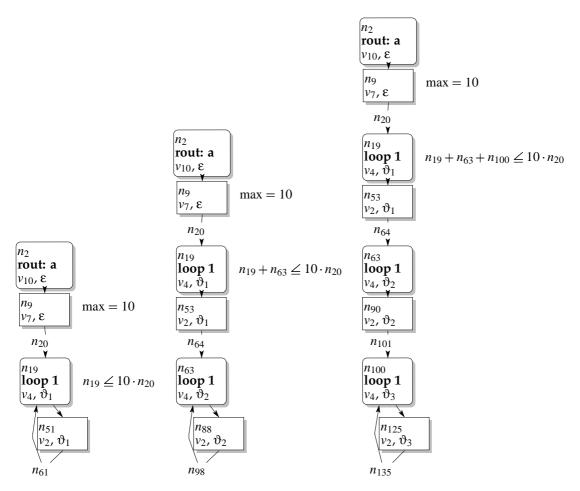

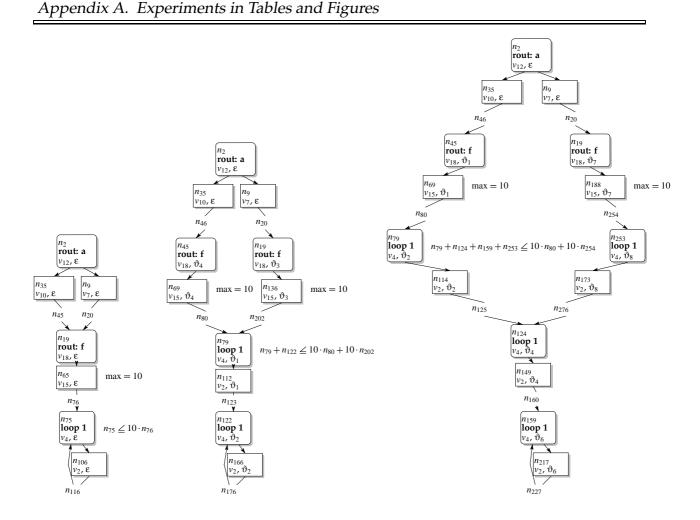

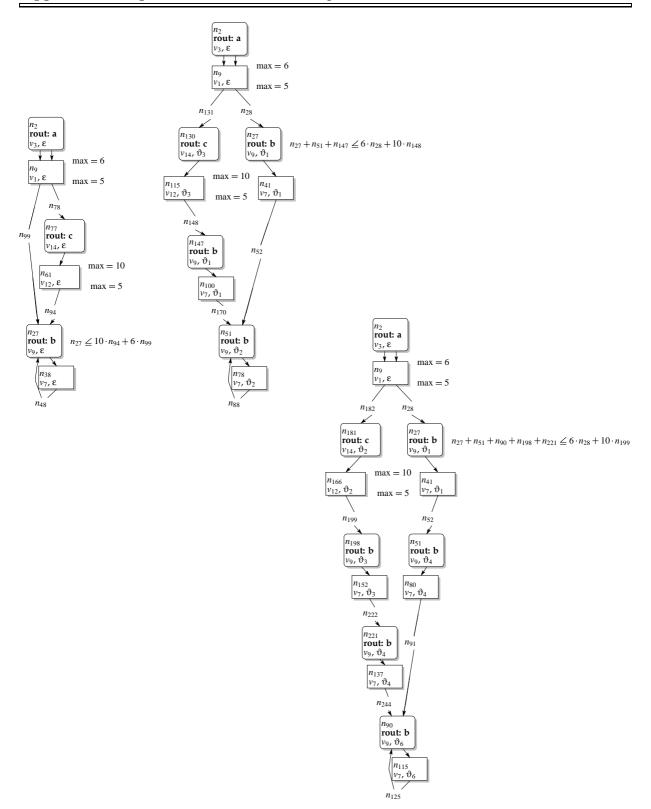

- **Appendix A** depicts many control flow graphs to show how loop constraints are generated in many different situations.

# Chapter 2 Basics

This chapter will introduce basic symbols and notations that will be used in the following chapters.

### 2.1 Selected Mathematical Notations

This section clarifies in brief words the usage of some mathematical symbols in this work. This section is not exhaustive, but only mentions some symbols that might be unclear. Mathematical notation is assumed to be known to the reader.

#### **Definition 2.1 (Tuples)**

For an arbitrary domain *D* and for elements  $d_1, d_2, ..., d_n \in D$ , the according *n*-tuple is written in two possible notations:

unrolled way:  $(d_1, d_2, \ldots, d_n)$

indexed way:  $(d_i)_{i \in \{1,...,n\}}$

The domain of tuples of length *n* is written  $D^{1,n}$ :

$$D^{1,n} := \{ (d_i)_{i \in \{1,\dots,n\}} \mid d_i \in D \}$$

(2.1)

The empty tuple will be written  $\varepsilon$ .

In contrast to this, the domain of vectors of length n is written  $D^n$ :

$$D^{n} := \left\{ \begin{pmatrix} d_{1} \\ \vdots \\ d_{n} \end{pmatrix} \mid d_{i} \in D \right\}$$

(2.2)

#### **Definition 2.2 (Kleene Closure)**

Given an arbitrary domain *D*, we define:

$$D^+ = \bigcup_{n \in \mathbb{N}} D^{1,n} \tag{2.3}$$

$$D^* = D^+ \cup \{\varepsilon\} \tag{2.4}$$

#### **Definition 2.3 (Powerset)**

For an arbitrary domain *D*, let  $\mathfrak{P}(D)$  be its power set, i. e., the set of all subsets of *D*.

$$\mathfrak{Y}(D) := \{ D' \mid D' \subseteq D \}$$

$$(2.5)$$

#### **Definition 2.4 (Image)**

Given a function  $f : M \to N$  and a set  $M' \subseteq M$ , the image of M' will be written f(M') and is defined as follows.

$$f(M') := \{ f(m) \mid m \in M' \}$$

(2.6)

The image of *f* is the special case f(M).

#### 2.2 Program Structure

This section introduces notations that are used to analyse programs. The structure of programs under examination will be clarified.

Let the program under examination be called  $\mathcal{P}$ .

#### 2.2.1 Programs and Instructions

Analyses work on programs, which are given as a sequence of instructions. Instructions are either machine instructions, as is often the case for real-time system analysis, or more generally minimal statements in the language the analysis works on.

Depending on control flow, the given sequence of instructions is split into basic blocks, which are the basics of analysis.

#### 2.2.2 Basic Blocks

The control flow of the program under examination is defined by jump instructions, which are intraprocedural branches, and call instructions, which are interprocedural branches. The branches divide the program into basic blocks, which control flow enters at the beginning and leaves at the end, without the possibility of branching except for the end of the basic block.

Let the set of basic blocks be *V*. This set must be finite:  $|V| < \infty$ .

The reconstruction of control flow includes finding the division into basic blocks. For raw machine code, this is not trivial. It is one topic of this work and will be described in detail in Chapter 6.

In the scope of this work, we will use the following terms. The following terms will be intuitively introduced now and clarified with

#### 2.2.3 Routines

Structuring a program into smaller pieces of code is done in order to re-use parts of the program (usually parameterised) and to get a nicer structure. These re-usable pieces of code will be called *routines*. The words 'function' and 'procedure' occur in literature as well, but this document keeps using 'routine' for the program substructures in order to avoid confusion with mathematical functions.

Let *R* be the set of routines of  $\mathcal{P}$  and let  $r_0$  be the routine to be invoked upon the start of  $\mathcal{P}$ , i. e.,  $r_0$  is the *main routine* of  $\mathcal{P}$ .

Every basic block belongs to exactly one routine. Let the function rout :  $V \rightarrow R$  associate each basic block with its routine.

Let  $V_f$  be the set of basic blocks of each routine:  $V_f = \{v \in V \mid rout(v) = f\}$ .

Every routine has exactly one basic block that is the first to be executed upon invocation. Let this basic block be called the routine's *start node*. The set Starts  $\subseteq$  *V* contains all start nodes of  $\mathcal{P}$ , one for each routine.

Let there be a function

start :

$$R \rightarrow$$

Starts (2.7)

that associates the start node with its routine.

Another set of interesting basic blocks is constituted by those that contain routines invocations. These basic blocks are called *call nodes*. Let the set  $Calls \subseteq V$  contain all call nodes of  $\mathcal{P}$ .

The following function associates call nodes with their invoked start nodes. Call nodes

may be associated with more than one start node, if there is more than one possible routine to be invoked. This happens for computed calls.

The function will be defined for all nodes for convenience and returns { } for non-call nodes.

target :

$$V \to \mathfrak{P}(\text{Starts})$$

$v \mapsto \{v' \in V \mid v \text{ invokes } v'\}$

(2.8)

#### 2.2.4 Control Flow Graph

Each routine has its own control flow graph, consisting of nodes that are basic blocks, and edges representing the control flow between the blocks.

Let  $CFG_f = (V_f, E_f), f \in R$  be the **control flow graph** of routine *f*.

As mentioned before, a control flow graph has exactly one start node start(f) via which all control flow enters routine f.

For a path in a graph *G*, e. g. in CFG<sub>*f*</sub>, from node  $v_1$  to  $v_2$ , we will write  $v_1 \rightarrow^*_G v_2$ .

#### Definition 2.5 (Branch, Jump, Call)

If control flow has several alternative possibilities to continue at run-time after a given basic block, i.e., if a node in a graph has several out-going edges, this situation will be called *a branch*.

Branches in control flow graphs will be called *jumps*.

Branches in call graphs will be called *calls* or *subroutine calls* or *subroutine invocations*. Call graphs will be defined now.

#### 2.2.5 Call Graph

An important structure is a call graph. It is the graph that connects call nodes and start nodes. It is defined by structures already defined: Calls and Starts constitute the nodes, and target restricted to Calls defines the intraprocedural edges. The linkage between start and call nodes is established by adding edges from start to call nodes for each routine. Formally, we define the following.

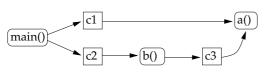

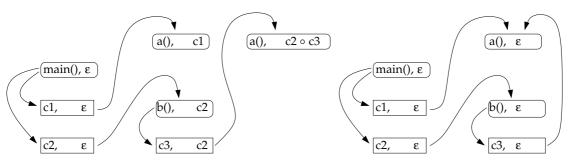

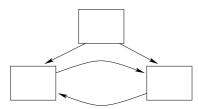

**Figure 2.1:** CG (without context) of Example 2.2.6. Start nodes are labelled with the name of the routine and a pair of parentheses, call nodes are labelled as shown in the comment in the C source code. Note that our CGs contain no return edges, only call edges.

#### **Definition 2.6 (Call Graph)**

Let  $CG = (\hat{V}, \hat{E}), \hat{V} = Calls \cup Starts, \hat{E} \subseteq \hat{V} \times \hat{V}$  be the **call graph** of  $\mathcal{P}$ , where  $\hat{E}$  is defined as follows.

$$\begin{split} \hat{E} &:= & \{(c,s) : c \in \mathsf{Calls}, s \in \mathsf{target}(c)\} \cup \\ & \bigcup_{f \in F} & \{(s,c) : s \in \mathsf{Starts}, c \in \mathsf{Calls} : \\ & \exists s \to^*_{\mathsf{CFG}_f} c\} \end{split}$$

It is required that call nodes have exactly one incoming edge in the CFG. This can be ensured by inserting additional empty nodes for the call nodes that contradict this requirement (the PAG framework does this). This way, together with the above definitions, each call node c also has exactly one outgoing edge in the CFG. In the CG, c also has exactly one incoming edge (from the start node) and possibly several outgoing edges (defined by target(c)).

## 2.2.6 Example in C

```

void a() {

... // basic block b1

}

void b() {

a(); // invocation c3

}

int main() {

a(); // invocation c1

b(); // invocation c2

}

```

Figure 2.1 shows the call graph of this short program.

**Note 1:** Definitions of call graphs in other literature often connect routines instead of start and call nodes. However, the call graphs that we are going to use have to distin-

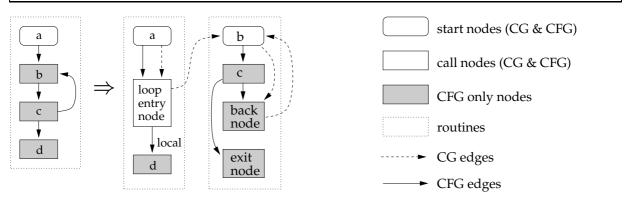

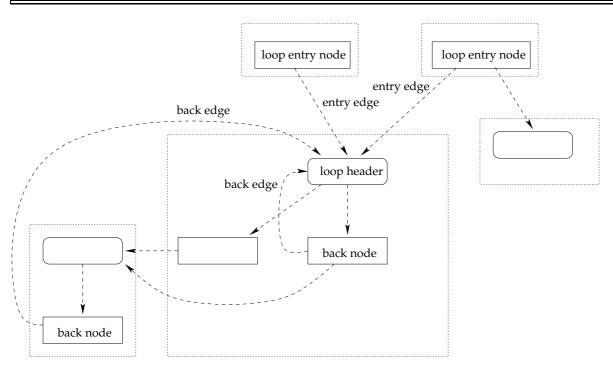

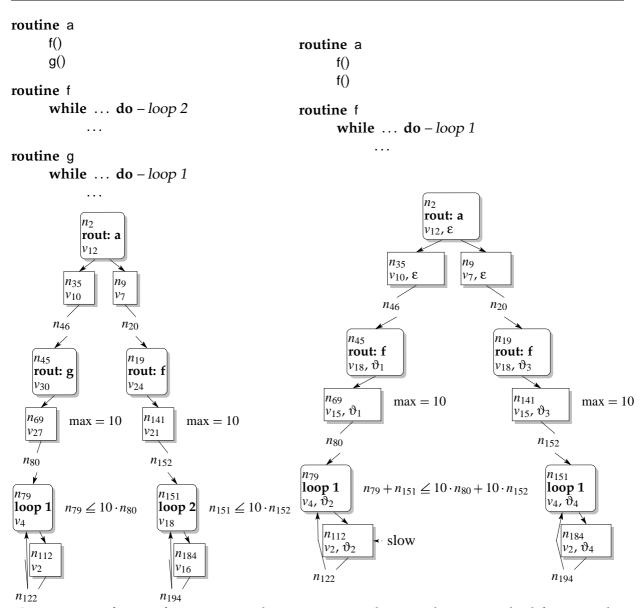

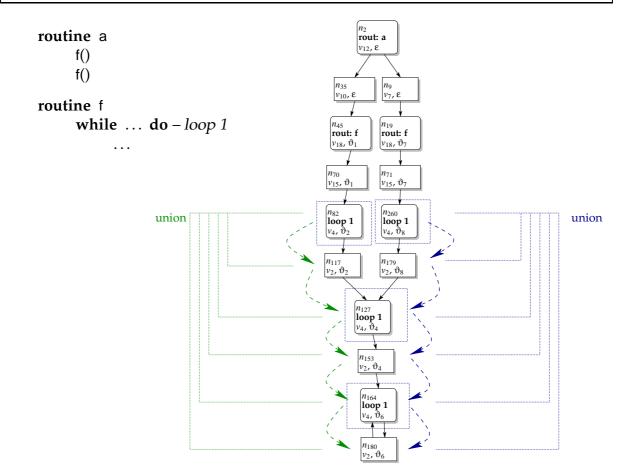

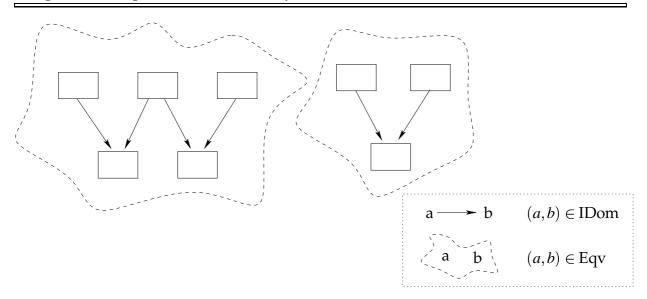

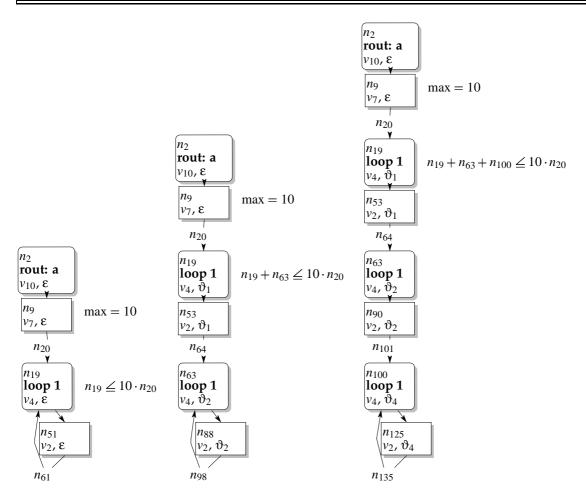

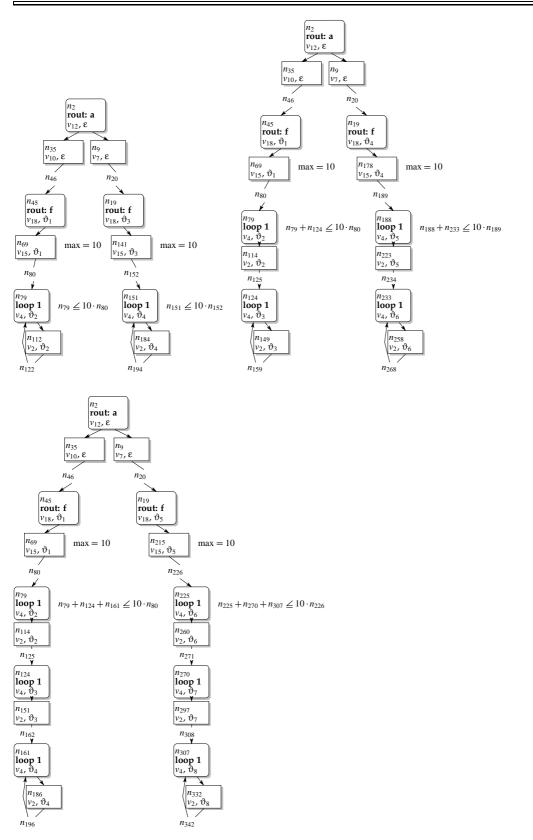

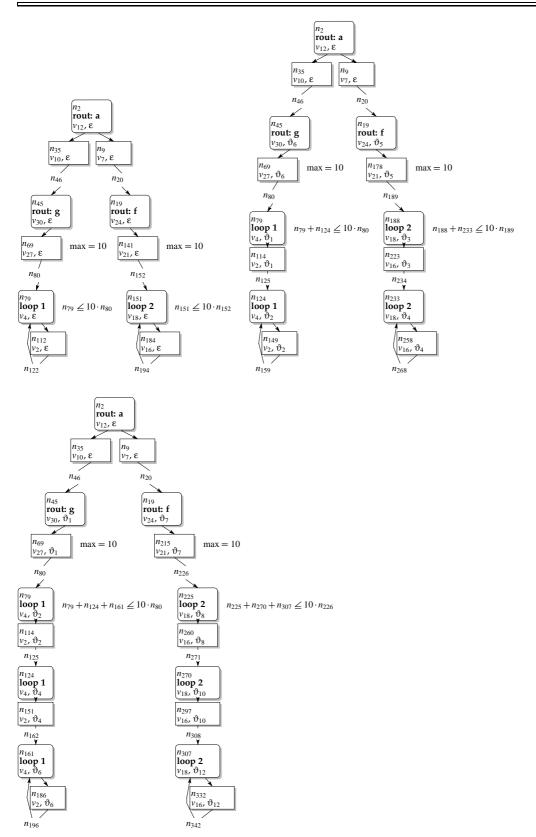

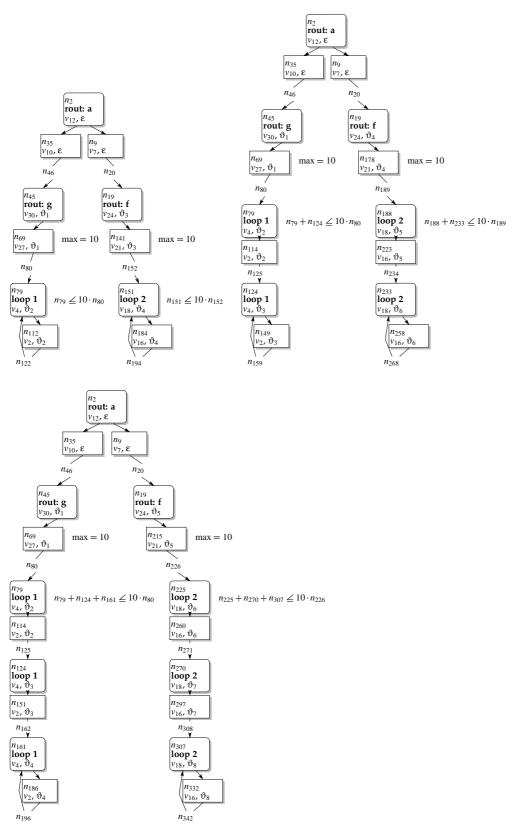

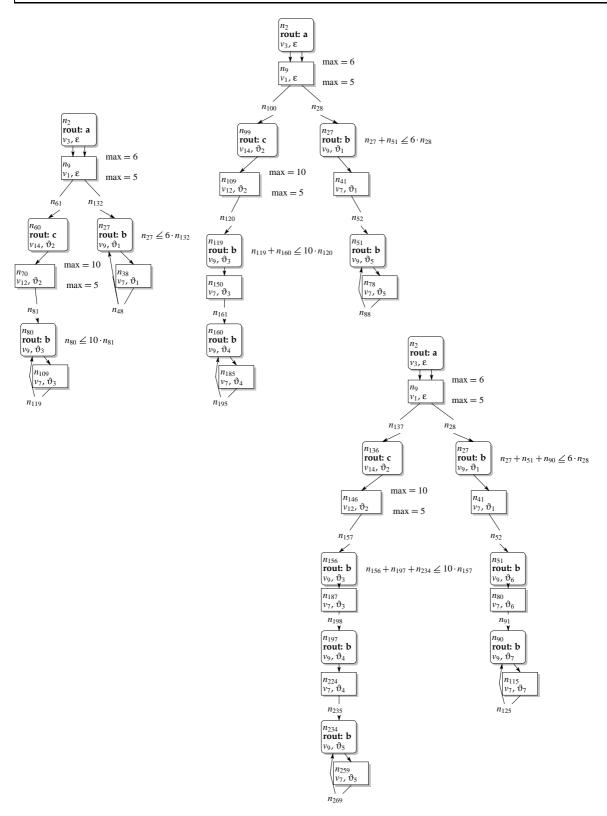

**Figure 2.2:** CFG modifications by loop transformation. The loop transformation introduces a new routine and new call nodes for each loop and transforms the loop into a recursive routine. Dashed lines represent edges in the call graph, which are introduced by this transformation.

guish call nodes, too. To get the call graphs used in other literature – those that connect routines – simply form super nodes from start and call nodes of the same routine. This way each node corresponds to a routine.

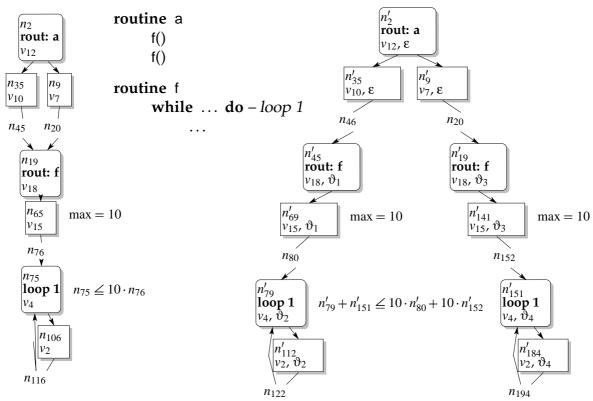

## 2.2.7 Loops

The term 'loop' will be used for a *natural loop* as defined in [Aho et al., 1986]. A natural loops has two basic properties:

- 1. A natural loop has exactly one start node which is executed every time the loop iterates. This node is called *header*.

- 2. A natural loop is repeatable, i.e., there is a path back to the header.

We handle loops and recursion uniformly in our approach. This is done by transforming all loops into recursive routines by making the loop body a routine on its own and inserting interprocedural edges accordingly. The loop transformation that is used to transform loops into routines uses an algorithm from [Lengauer and Tarjan, 1979] to find and extract loops.

Figure 2.2 depicts a loop transformation.

Apart from loops, there must be no other cycles in the control flow graphs. Although this is a restriction, compiled code and well-done hand written assembly code will not use other types of cyclic control flow. The reason for this restriction is the unbounded run-time of control flow cycles. When the path analysis searches the maximal run-time, loops must be bounded with maximal iteration counts in order to make the problem

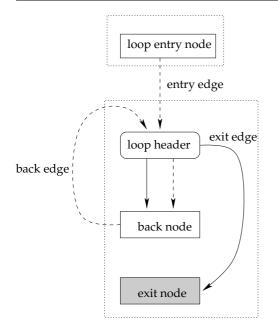

**Figure 2.3:** A simple loop with all the important edges. Dotted lines and white nodes are in the call graph, the other items are part of the control flow graph

solvable. Because only loop iteration counts are specifiable, only these types of cycles are currently allowed.

After loop transformation, there must be no cycles in the control flow graphs at all. All cycles must have been moved to the call graph and marked as loops.

Let *L* be the set of loops of program  $\mathcal{P}$ . Because loops are converted into recursive routines in our framework, it holds that  $L \subseteq R$ . Therefore, the header of a loop is simply the start node of the loop. Still, we define a function that assigns the header to a loop for clarity.

### **Definition 2.7 (Loop Header)**

The *header of a loop*  $\overline{l} \in L$  is defined as follows.

header :

$$L \rightarrow \text{Starts}$$

$l \mapsto \text{start}(l)$  (2.9)

Figure 2.3 shows a simple loop.

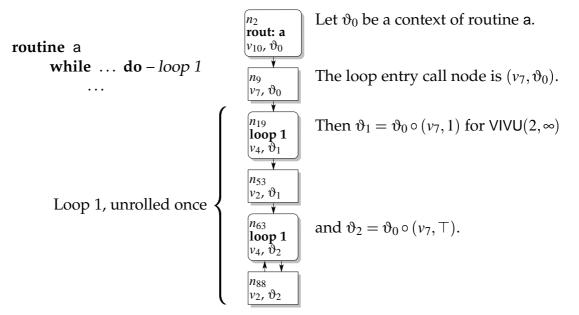

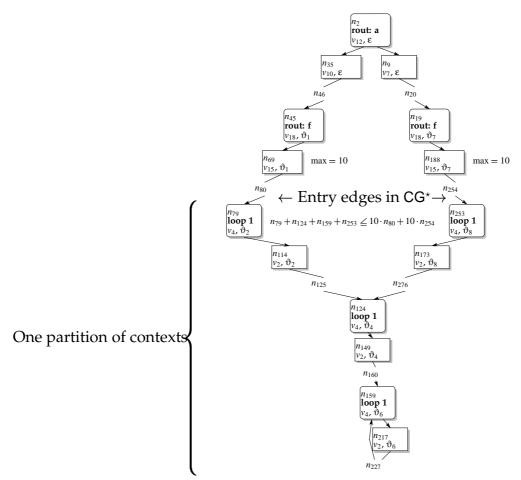

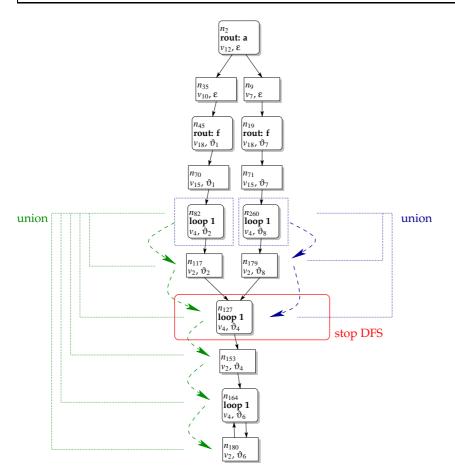

Because loops and recursion are the same in our framework, there may be more than one entry for a loop. This case occurs when a recursive routine is invoked from several different call sites. A more complex example of a loop is shown in Figure 2.4 on the next page.

#### Chapter 2. Basics

**Figure 2.4:** Complex recursion, CG only. The loop is entered from two call sites. One of the entry nodes also has an outgoing edge that calls a non-involved routine. There are two back edges, one of which recurses via another function call. Further, one of the back nodes has two outgoing edges, but only one is a back edge. To handle all this, much care has to be taken.

**Definition 2.8 (Entry Edges)**

Let there be a function

entries:

$$L \to \mathfrak{P}(\hat{E})$$

(2.10)

that assigns to a loop its entry edges.

Let there also be a function that returns the set of back edges of the loop, i. e. those edges that enter the loop from inside the loop. Note that usage of 'inside' here refers to nested re-invocations of the loop as well.

#### **Definition 2.9 (Back Edges)**

$$back: L \to \mathfrak{P}(\hat{E}) \tag{2.11}$$

The number of iterations of loops will be specified using two functions. One for the minimum iteration count and one for the maximum. The iteration bounds will be defined *for each entry* of the loop and, therefore, the two functions take and *loop entry node* as their argument.

Definition 2.10 (Minimum and Maximum Loop Iteration Count)

Let *l* be a loop and  $e \in \text{entries}(l)$  one of its entry edges.

The **minimum loop execution count** per entrance of *l* via *e* will be written  $n_{\min}(e)$ .

The **maximum loop execution count** per entrance of *l* via *e* will be written  $n_{\max}(e)$ .

## 2.3 Integer Linear Programming

This section introduces the basics of Integer Linear Programming (ILP) briefly. A precise description of the underlying theory can be found in many books (*see* [Chvátal, 1983; Schrijver, 1996; Nemhauser and Wolsey, 1988]).

## 2.3.1 Linear Programs

This section introduces the structure of Linear Programs. How they can be solved will be shown in the next section.

#### **Definition 2.11 (Comparison of Vectors)**

Let  $\Delta \in \{ \leq, =, \geq \}$  be a comparison operator and let  $a, b \in \mathbb{R}^n$ . Then we define

$$a\Delta b :\Leftrightarrow a_i \Delta b_i, \ \forall i = 1, \dots, n$$

#### **Definition 2.12 (Linear Combination)**

Let  $x \in \mathbb{R}^n$  be variable and let  $a \in \mathbb{R}^n$  be constant. Then  $a^T x$  is called the *linear combination* of x.

#### **Definition 2.13 (Linear Program)**

Let  $t \in \mathbb{R}^d$ ,  $b \in \mathbb{R}^m$ ,  $A \in \mathbb{R}^{m \times d}$  be known and constant. A *Linear Program* (LP) is the task to maximise  $t^T x$  in such a way that  $x \in \mathbb{R}^d_{\geq 0} \land Ax \leq b$ . In short, this is written:

$$\max: t^T x \mid A x \leq b, \ x \in \mathbb{R}^d_{\geq 0}.$$

#### **Definition 2.14**

In Definition 2.13 the function  $C : \mathbb{R}^d \to \mathbb{R}$  where  $C(x) = t^T x$  is called *objective function*.

The inequalities given by  $Ax \leq b$  are called *constraints*. *x* is said to be a *feasible* solution, if it satisfies  $Ax \leq b$ . Let  $P = \{x \in \mathbb{R}^d_{\geq 0} \mid Ax \leq b\}$  be the set of feasible solutions of *x*.  $x^*$  is said to be an *optimal* solution, if  $t^T x^* = \max\{t^T x \mid x \in P\}$ .

To reduce a problem of minimising to one of maximising, the objective function can be multiplied by -1.

Further, the constraints that are used in the definition of a Linear Program are of the form  $a_{k,1}x_1 + a_{k,2}x_2 + \cdots + a_{k,d}x_d \leq b_k$ . Other types of constraints like

$$a_{k,1}x_1 + \dots + a_{k,d}x_d \ \Delta \ a'_{k,1}x'_1 + \dots + a'_{k,e}x'_d \tag{2.12}$$

where  $\Delta \in \{ \leq, =, \geq \}$  can be reduced to the basic form by using the following transformations:

- 1. Instead of  $\sum_{1} \Delta \sum_{2}$  write  $\sum_{1} \sum_{2} \Delta 0$ .

- 2. Instead of  $\Sigma \ge 0$  write  $-\Sigma \le 0$ .

- 3. Instead of  $\Sigma = 0$  write  $\Sigma \leq 0$  and add the constraint  $-\Sigma \leq 0$ .

There are three cases that can occur when an LP is tried to be solved:

1.  $P = \{\}$ : The LP is *infeasible*. 2.  $P \neq \{\}$ , but  $\nexists \sup\{t^T x \mid x \in P\}$ . The LP is *unbounded*. 3.  $P \neq \{\}$ , and  $\exists \max\{t^T x \mid x \in P\}$ . The LP is *feasible* and has a finite solution.

To find the solution of a linear program, upper bounds of the objective function must be computed. The problem of finding the least upper bound is also an LP that is defined as follows.

#### Definition 2.15 (Primal and Dual Problem)

Let max :  $t^T x | Ax \leq b, x \in \mathbb{R}^d_{\geq 0}$  be a Linear Program. Let this program be called *primal problem*. The *dual problem* is the problem of finding the least upper bound of  $t^T x$ , which is defined as follows: min :  $y^T b | y^T A \geq t^T$ ,  $y \in \mathbb{R}^d_{\geq 0}$ .

The two following theorems hold (Duality Theorems of Linear Programming):

#### Theorem 2.16 (Weak Duality)

Let  $\bar{x}$  be a feasible solution of the primal problem max :  $t^T x | Ax \leq b, x \in \mathbb{R}^d_{\geq 0}$  and let  $\bar{y}$  be a feasible solution of its dual problem min :  $y^T b | y^T A \geq t^T, y \in \mathbb{R}^d_{\geq 0}$ . Then it holds that:

$$\bar{y}^T b \ge t^T \bar{x}$$

#### **Theorem 2.17 (Strong Duality)**

Let  $x^*$  be a feasible solution of the primal problem max :  $t^T x | Ax \leq b, x \in \mathbb{R}^d_{\geq 0}$  and be  $y^*$  be a feasible solution of its dual problem min :  $y^T b | y^T A \geq t^T, y \in \mathbb{R}^d_{\geq 0}$ . Then it holds that:

$$y^{*T}b = t^T x^* \iff x^*$$

and  $y^*$  are optimal.

#### Corollaries

- If the primal problem is unbounded, the dual problem is infeasible.

- If there are feasible solutions of the primal and the dual problems, then there is an optimal solution. The values of the objective function of the two problems are equal for the optimal solution.

The following *Simplex* algorithm exploits that for a feasible preliminary solution *x* of the primal problem, there is a solution *y* of the dual problem. If that solution is feasible in the dual problem, it is optimal (due to the second corollary). If it is not, the basic solution can be improved.

#### 2.3.2 Simplex Algorithm

This section introduces a non-formal description of the Simplex algorithm. There is a vast amount of literature about LP solving and the Simplex algorithm available for the interested reader, e. g. [Chvátal, 1983; Schrijver, 1996; Nemhauser and Wolsey, 1988].

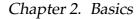

The constraints of a linear program isolate a convex area in  $\mathbb{R}^n_{\geq 0}$ . An optimal solution is found in one of the corners of this area. Starting with an arbitrary corner, a better

solution of the objective function is searched by following one of the outgoing edges of that corner. This is repeated until no adjacent corner has a better value, which means that the optimal solution has been found. Figure 2.5 on the next page illustrates this algorithm.

The simplex algorithm can be used to solve large problems, since for most applications, its runtime is O(m) for *m* constraints. However, constraints can be constructed so that the algorithm performs in only  $O(2^m)$  time (e.g. the Klee Minty cube (*see* [Chvátal, 1983])). There are better algorithms from the complexity point of view, e.g. the Ellipsoid method or the Projective Scaling Algorithm by Karmarker, which have polynomial run-time.

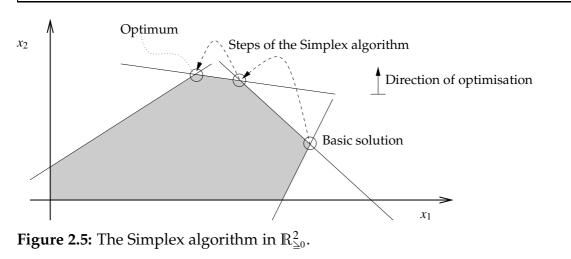

## 2.3.3 Integer Linear Programs

Many problems only allow integer solutions for the solutions of an LP, i. e., in Definition 2.13 on page 42 it must additionally hold that  $x \in \mathbb{Z}^d$ . And because we already made the restriction that  $x \ge 0$ , it must even hold that  $x \in \mathbb{N}_0^d$ .

This type of constraint will be needed for the algorithms in Chapter 7, where the variables of the LP are execution counts of basic block, which are naturally integers.

#### **Definition 2.18 (Integer Linear Program)**

Let  $t \in \mathbb{R}^d$ ,  $b \in \mathbb{R}^m$ ,  $A \in \mathbb{R}^{m \times d}$  be constant and known. An *integer linear program* (ILP) is the task to maximise  $t^T x$  in such a way that  $x \in \mathbb{N}_0^d \land Ax \leq b$ .

$$\max: t^T x \mid Ax \leq b, \ x \in \mathbb{N}_0^d.$$

To find a solution of an ILP, additional steps have to be taken, because the Simplex algorithm (and others for LP solving) cannot be used directly, since the additional restriction

**Figure 2.6:** Domain of feasibility of an ILPs (grid points) and corresponding domain of feasibility of the LP-relaxed problem (shaded area).

to integer variable cannot be handled by them. Actually, it is  $\mathcal{NP}$ -complete to solve ILPs. However, in practice, many large ILPs problems are solvable with a moderate amount of effort.

#### **Definition 2.19 (LP-Relaxed Problem)**

Let max :  $t^T x | Ax \leq b, x \in \mathbb{N}_0^d$  be an Integer Linear Program. Then max :  $t^T x | Ax \leq b, x \in \mathbb{R}_{\geq 0}^d$  is said to be the corresponding *LP-relaxed problem*. In the following, it will also be called *relaxed problem*.

The relaxed problem is used to solve ILPs. It does not contain demands for integer variables and all feasible solutions of the ILP are also feasible for the LP. I. e., starting from the LP the integer property of all variables is tried to be achieved. The following algorithm works like that.

## 2.3.4 Branch and Bound Algorithm

The basic idea of the Branch and Bound Algorithm is to solve the relaxed LP and then split the domain of feasibility into two sub-problems in order to satisfy the demand for integer variables. Each sub-problem is then solved until all variables are integers.

Let  $\Psi$  be an ILP and let  $\Psi'$  be the relaxed problem. If it is feasible, solving  $\Psi'$  yields a solution  $\hat{x} \in \mathbb{R}^{d}_{\geq 0}$ .

If  $\hat{x} \in \mathbb{Z}^d$ , so a solution is found for  $\Psi$ , too. If not a coordinate  $i \in \{1, ..., n\}$  is chosen such that  $\hat{x}_i \notin \mathbb{Z}$ . The two sub-problems  $\tilde{\Psi}_1$  and  $\tilde{\Psi}_2$  are created from  $\Psi'$  by adding one of the following inequalities:

$$x_i \leq \lfloor \hat{x}_i \rfloor \tag{2.13}$$

$$x_i \geq \lceil \hat{x}_i \rceil \tag{2.14}$$

45

These constraints exclude  $\hat{x}$  as a solution for  $\tilde{\Psi}_1$  and  $\tilde{\Psi}_2$ . This method is repeated until all variables are integers.

No word was said about major problems and methods used in this algorithm, such as how to choose a coordinate, or which order the sub-problems should be solved in. Again, interested readers should refer to standard literature like [Chvátal, 1983; Schrijver, 1996; Nemhauser and Wolsey, 1988].

There are freely available tools like lp\_solve<sup>1</sup> that implement very good algorithms for solving ILPs. lp\_solve was used for this thesis.

<sup>&</sup>lt;sup>1</sup>lp\_solve was written by Michel Berkelaar and is freely available at ftp://ftp.es.ele.tue.nl/pub/lp\_solve.

# Chapter 3 Control Flow Graphs

While the previous chapter has already introduced basics about programs, their control flow graphs and call graphs, this chapter will describe in detail the precise structure of the control flow graphs our framework uses. Requirements of CFGs and CGs for real-time system analysis will be discussed.

# 3.1 Control Flow Graphs for Real-Time System Analysis

To talk about control flow graphs and call graphs simultaneously, the term *interprocedural control flow graph (ICFG)* will be used to refer to all control flow graphs and to the call graph of a program.

Real-time system analysis requires *safe* and *precise* analysis methods. Safety has the highest priority since real-time systems are usually part of a large, safety-critical environment where errors can lead to fatal damage, as mentioned already in the introductory chapter.

## 3.1.1 Safety

For our WCET analysis framework, this means that all analyses must be based on a safe ICFG in the first place. If the ICFG is unsafe, the whole analysis chain will be unsafe.

To define safety for ICFGs, it must be thought about what unsafety means, since ICFGs seem to be something that either represents a program, or which does not, in which case it must be said to be incorrect. It is not that simple, however, since control flow is sometimes unclear or unpredictable for analyses. Of course, our first requirement is correctness. This is more than obvious:

#### A safe interprocedural control flow graph must be correct.

Secondly, if any uncertain control flow is encountered, it must be clearly marked for analyses to be able to react to uncertain control flow.

#### A safe interprocedural control flow graph must mark uncertainties clearly.

Subsequent chapters will reason about how to achieve these goals when reconstructing control flow. This chapter will focus on the precise structure of ICFGs and on how the required information can be made available to analyses.

## 3.1.2 Precision

For analyses to be precise, the underlying ICFGs must be precise, too. Whenever control flow can be represented precisely or imprecisely, this chapter will discuss that topic.

Precision in control flow is usually an issue for alternative flow, i. e., where the final taken alternative is decided at run-time. Examples are computed jumps (e. g. switch tables) or computed calls (e. g. function pointers or virtual function calls in object-oriented languages). The issue is usually a question of infeasibility: more precision means to be able to predict statically which alternative paths are really infeasible. The more this can be predicted, the more precise the ICFG will be.

## 3.2 Detailed Structure of CFG and CG

This section describes the precise structure of the ICFGs that are used in this thesis. It is a clarification of the data structures presented in Chapter 2.

The graphs that are used are based on those provided by the PAG framework. However, the graphs used here are computed from the PAG graphs to suite the needs of the presented algorithms best. This section will clarify how these graphs look like.

In order to prevent special cases, like conditional calls, etc., our CFGs and CGs contain additional *empty* basic blocks at specific locations, i. e., when routines are invoked and left. Because of loops being transformed to recursion, these empty blocks also help to avoid special cases here, e.g., there cannot be two loops starting before the same basic block. This can be programmed in Pascal with two nested repeat loops.

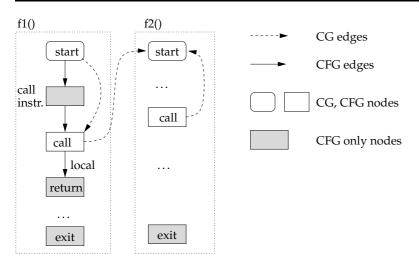

**Figure 3.1:** CFG and CG of a call of a recursive routine. The two graphs are shown in one figure. This figure clarifies the use of local edges and shows that there are no return edges (e.g. from a node in routine f2 back to the call node in f1).

Four types of empty nodes exist: at each routine invocation, two additional empty nodes are inserted: a *call* node and a *return* node. The actual call instruction is located in the block before the call node. Routines begin with an empty *start* node and returning control flow is gathered in a unique *exit* node.

Our CFGs contain a *local* edge after each call node, because the call graphs will not contain flow information about routine returns. This is the most convenient way of representation for the analyses that will be described later (*see* Section 7.3.3 on page 113).

A routine call with all important nodes is depicted in Figure 3.1.

## 3.2.1 Alternative Control Flow and Edge Types

Alternative control flow occurs at two levels: in the control flow graph, where if-thenelse statements are the most common example, followed by switch-statements, and in the call graph, where function pointers are the most common example. Virtual function calls are usually a special case of function pointers.

To handle alternative control flow in control flow graphs, there are different types of edges. Some analyses need this edge type in order to compute the correct behaviour. E.g. jumps often have different execution times for different types of edges.

We formally define the edge type as a function that assigns a type to each edge.

#### **Definition 3.1 (Edge type)**

Let type :  $E \rightarrow \{\text{normal}, \text{false}, \text{true}, \text{local}\}$

- **normal edge:** outgoing edge of basic blocks whose control flow exits without alternatives (i. e., without a branch)

- **false edge:** for a conditional jump, this marks the edge that is taken if the branch is not taken. This type of edge is also known as a *fall-through edge*. At each block, there is maximally one of these edges.

- true edge: for a jump, this marks possible branch targets of the jump.

- **local edge:** this edge was introduced in the previous section: it is the representation of control flow after a call.

For switch tables, there may be a number of true edges, one for each possible branch target.

Alternative control flow in the call graph is marked in the same way by using multiple outgoing edges from a call node to several start nodes.

## 3.2.2 Unrevealed Control Flow

If any control flow is unknown, it is *required* that the control flow graph contains information about this. This is vital for analyses, since they might analyse to the wrong thing.

Unrevealed control flow, i. e., edges that are known to exist but with an unknown target, can be marked at the basic block to have additional successors in the control flow graph or the call graph. We introduce two sets to account for this.

#### **Definition 3.2 (Unrevealed edges)**

Let Calls  $\subseteq$  Calls be the set of call nodes that contain instruction with unknown call targets. Because we cannot have edges with an unknown target, we use this set instead.

For a given routine f, let  $\tilde{V}_f \subseteq V_f$  be the set of basic block that contain instructions with unknown jump targets.

## 3.2.3 Calls

Modern architectures and run-time libraries have several interesting peculiarities that have to be thought about. Many of these peculiarities showed up when the control flow

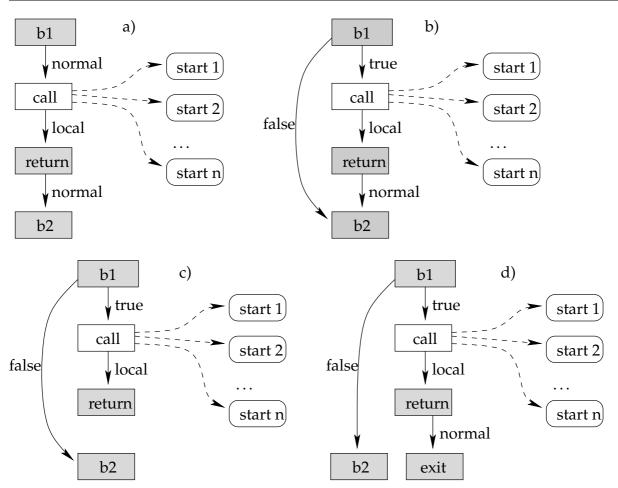

**Figure 3.2:** Different types of calls and their representation in the ICFG. a) normal call (with several alternative targets), b) conditional call, c) conditional no-return call, e) conditional immediate-return call

reconstruction algorithms (*see* Chapter 6) were implemented for different targets. Calls are more complex than normal jumps, since they involve the mechanism of returning to the caller, so the fall-through edge has a totally different meaning for calls than for jumps. Therefore, the generation of edges needs to be clarified for the interprocedural case as well as for the intraprocedural case.

In the course of the examination of different programs, libraries and architectures, we found the need to distinguish the following types of calls. The categories listed below are not mutually exclusive.

- **computed calls:** calls that use the value of a register as a branch target. These usually result in alternative control flow.

- unpredictable calls: calls that have unrevealed call targets.

- **conditional calls:** calls that may possibly not be taken.

- not-taken calls: calls that are never taken

- **no-return calls:** calls that never return, e.g., because they invoke a routine that implements an infinite loop, or calls to a system function that exits the program.

- **immediate-return calls:** calls that end the current function immediately when they return.

Handling of computed calls and unpredictable calls has been described already above.

Calls that are not taken are represented by having no call nodes at all.

Whether a call is conditional, not-taken, no-return or immediate-return is represented by edges in the control flow graph. One interesting fact is that calls might *not* return to the caller, but branch to somewhere else when they return. This is the case for no-return and immediate-return calls.

Figure 3.2 on the previous page shows the ICFGs associated with different types of calls.

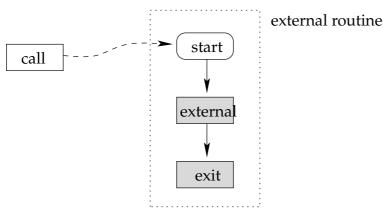

## 3.2.4 External Routines

External routine calls are frequent and should be handled by any WCET analysis framework. Our approach is to introduce a basic block of the type *external*, which represents the execution of the external routine. It is like a black box.

Analyses can decide how to handle these external basic block nodes. The WCET analysis will have to assume that the run-time of such blocks is known, so either a library of pre-analysed run-times is needed, or the user has to be queried.

**Figure 3.3:** External routine call: an *external* node is introduced that represents the external routine as a black box.

## 3.2.5 Difficult Control Flow

Programmers may use strange concepts of structure and produce something that is executable, but with weird control flow. This chapter deals with these cases.

Examples of weird, or better *difficult* control flow are the following.

- Jumps into loops past the loop header.

- Entering routines at different basic blocks.

Unfortunately, even so-called high-level programming languages sometimes support the generation of structures that are difficult. E. g. most imperative programming languages support a goto command that allows for jumping to any point in the current procedure. This way entering loops past the header is possible.

Some old imperative languages that are still in wide use, like C, even do not enforce a clear block-structure for their own structuring mechanisms. E. g., while and case statements need not be nested correctly, triggering the same problem of entering loops past the header. An infamous example is Duff's device, used to unroll a typical memory copy loop and interlace it with the initial aligning case. This is shown in Figure 3.4 on the next page.

Many cycles that are not natural loops could be transformed into a natural loop by unrolling them once. Duff's device is one example for this. Usually, it is not clear which block should be the loop header then, because with different entries it is unclear which block inside the loop is executed as many times as the loop is executed.

The second example, entering routines at several basic blocks can usually only be programmed when using the assembly or machine language directly. Although this is assumed to be very bad coding style, it can often be reconstructed to nice control flow by

Chapter 3. Control Flow Graphs

```

unsigned int n = (count + 7) / 8;

switch (count % 8) {

do {

case 0: *to++ = *from++;

case 7: *to++ = *from++;

case 6: *to++ = *from++;

case 5: *to++ = *from++;

case 4: *to++ = *from++;

case 3: *to++ = *from++;

case 1: *to++ = *from++;

case 1: *to++ = *from++;

} while (--n > 0);

}

```

**Figure 3.4:** Duff's device. The loop is entered at several points by interlacing switch statement and while loop in C.

introducing additional routines (e.g., when the same routine tail is used by two routines, this tail can be made a routine on its own if no jumps leave that new routine).

However, such a structure cannot *always* be reduced to nice control flow, so a full automation cannot be expected. Therefore, it seems unwise to start implementing without observing the important special cases that should be handled automatically. Our framework is very flexible to easily allow such extensions as soon as they are encountered.

## 3.3 Contexts