# Formal Verification of Pipelined Microprocessors

Dissertation zur Erlangung des Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I der Universität des Saarlandes

Daniel Kröning

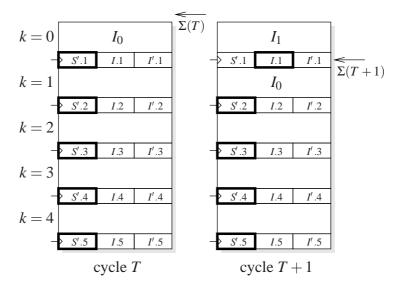

Saarbrücken, 2001

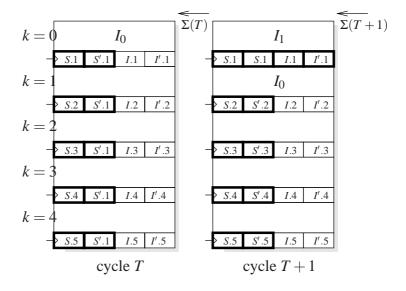

#### Abstract

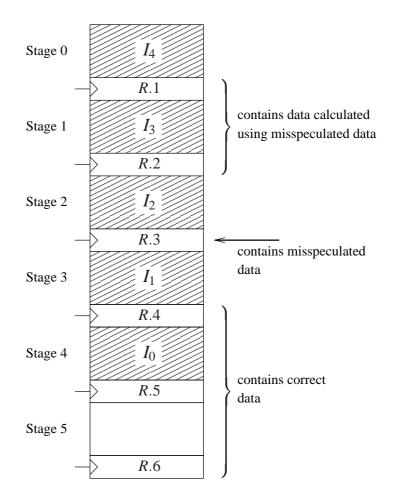

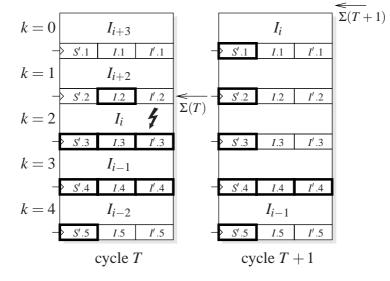

Subject of this thesis is the formal verification of pipelined microprocessors. This includes processors with state of the art schedulers, such as the Tomasulo scheduler and speculation. In contrast to most of the literature, we verify synthesizable design at gate level. Furthermore, we prove both data consistency and liveness. We verify the proofs using the theorem proving system PVS. We verify both in-order and out-of-order machines. For verifying in-order machines, we extend the stall engine concept presented in [MP00]. We describe and implement an algorithm that does the transformation into a pipelined machine. We describe a generic machine that supports speculating on arbitraty values. We formally verify proofs for the Tomasulo scheduling algorithm with reorder buffer.

#### Kurzzusammenfassung

Gegenstand dieser Dissertation ist die formale Verifikation von Mikroprozessoren mit Pipeline. Dies beinhaltet auch Prozessoren mit aktuellen Scheduling-Verfahren wie den Tomasulo Scheduler und spekulativer Ausführung. Im Gegensatz zu weiten Teilen der bestehenden Literatur führen wir die Verifikation auf Gatter-Ebene durch. Des weitern beweisen wir sowohl Datenkonsistenz als auch eine obere Schranke für die Ausführungszeit. Die Beweise werden mit dem Theorem Beweissystem PVS verifiziert. Es werden sowohl in-order Maschinen als auch out-of-order Maschinen verifiziert. Zur Verifikation der in-order Maschinen erweitern wir die Stall Engine aus [MP00]. Wir beschreiben und Implementieren ein Verfahren das die Transformation in die "pipelined machine" durchführt. Wir beschreiben eine generische Maschine die Spekulation auf beliebige Werte erlaubt. Wir verifizieren die Beweise für den Tomasulo Scheduler mit Reorder Buffer.

# **Extended Abstract**

Microprocessors are in use in many safety-critical environments, such as cars or planes. We therefore consider the correctness of such components as a matter of vital importance. Testing microprocessors is limited by the huge state space of modern microprocessors. We therefore think formal verification is the sole way to obtain a guarantee.

This formal verification should be done such that any third party is able to verify the correctness with low effort, i.e., we aim to provide a proof of correctness that can be checked mechanically. In particular, we think that all critical designs should be delivered in form of a four-tuple: 1) the design itself, 2) a specification, 3) a human-readable proof, and 4) a machine-verified proof.

In this thesis, we present proofs of correctness for complex microprocessors. Designing microprocessors is considered an error-prone process. A well known example for this is the Pentium FDIV bug [Coe95, Pra95].

In this thesis, we provide a rigorously formal approach to hardware verification. The designs presented in this thesis include state of the art schedulers, such as the Tomasulo scheduler [Tom67] and speculation. In contrast to most of the literature, the designs we provide are very close to gate level. In particular, we are synthesizing some of the designs for the XILINX FPGA series.

These designs are of high complexity, and so are the proofs. In contrast to [MP95, Lei99, MP00], the proofs are machine verified using the theorem proving system PVS [CRSS94]. We do not present the original PVS proof in this thesis but aim to provide comprehensible paper-and-pencil proofs.

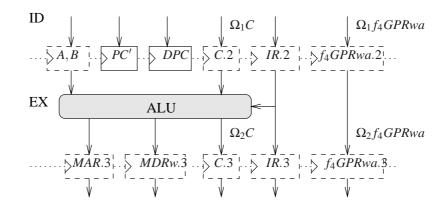

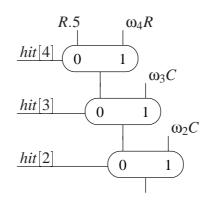

In order to verify sequential machines, we extend the data consistency invariant given in [MP00] by defining a "correct value" of an implementation register such as *IR*.2. Given the correctness of functional components such as the ALU, this allows for an almost fully automated proof of the data consistency of the prepared sequential machine using PVS. We argue that the correct functional components provide correct results if given correct inputs.

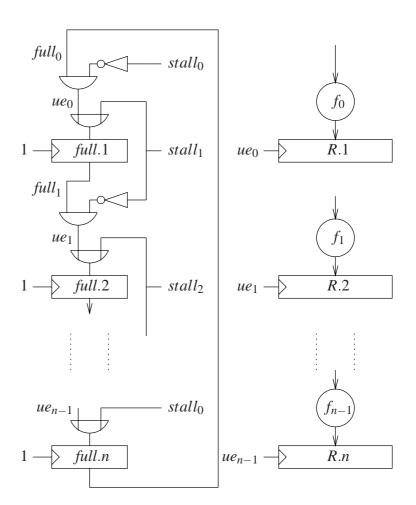

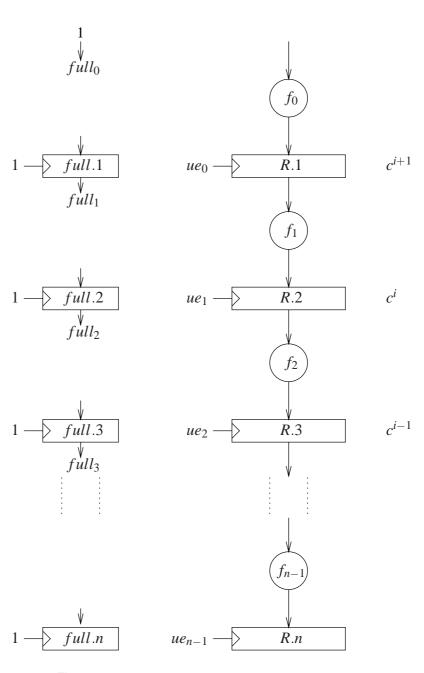

We extend the stall engine concept presented in [MP00] by providing

a fully generic stall engine design. In contrast to [MP00], our stall engine design supports an arbitrary number of stages and allows for stalling (and therefore clocking) all stages independently. Furthermore, it supports *pipeline bubble removal*, i.e., the stages are clocked whenether the in-order property permits this. This includes that bubbles are removed from the pipeline if necessary. We formally verify data consistency and liveness properties for this stall engine.

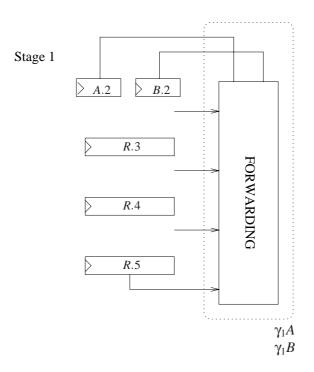

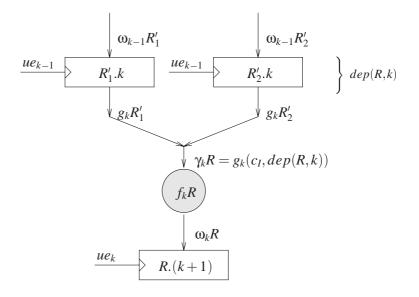

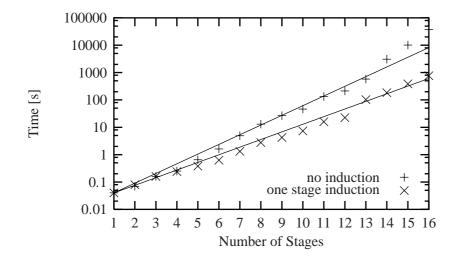

Using this extended stall engine, we improve the process of transforming the prepared sequential machine into the pipelined machine by providing a tool that does this transformation automatically. This includes the generation for forwarding and interlock hardware.

We then prove the data consistency of the pipelined machine. We do so by showing that the inputs of the pipeline stages are correct. Using this fact, we argue the correctness of the output values as we do for the prepared sequential machine, since the functional components of the machines are identical.

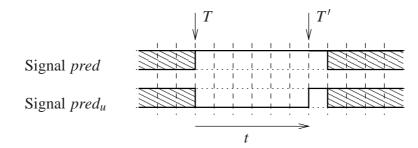

We present a generic approach to speculative execution and propose a data consistency criterion for such a machine. We then apply this method in order to implement and prove DLX pipelines with branch prediction and precise interrupts. It is a well-known fact that both techniques are implemented using speculation [SP88]. However, to the best of our knowl-edge, implementing both techniques as an instance of a generic speculation mechanism is done for the first time.

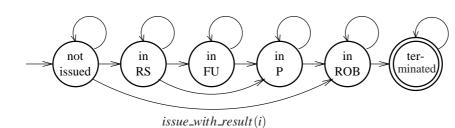

Besides the in-order pipelines, we verify the correctness of the Tomasulo scheduling algorithm with reorder buffer as described in [KMP99]. The reorder buffer realizes in-order termination, which allows implementing precise interrupts. The proof of correctness covers the arguments neccessary to show the uniqueness of the tags.

Furthermore, we rigorously prove the liveness of all machines we design, i.e., we prove that any given instruction sequence is executed within a finite amount of time. Although critical, liveness issues are often not covered in the open literature.

# Zusammenfassung

Mikroprozessoren werden in vielen sicherheitskritischen Bereichen eingesetzt, wie beispielsweise in Automobilen oder Flugzeugen. Wir erachten daher die Korrektheit solcher Komponenten als lebenswichtig. Der Test von Prozessoren ist durch den extrem großen Zustandsraum moderner Prozessoren nur eingeschränkt möglich. Wir sind daher der Meinung, daß formale Verifikation die einzige Möglichkeit darstellt, eine Garantie zu erhalten.

Diese formale Verifikation sollte so durchgeführt werden, daß Dritten die Möglichkeit offen steht, die Korrektheit mit geringen Aufwand nachzuvollziehen. Wir wollen daher einen Beweis zur Verfügung stellen, der automatisiert überprüft werden kann. Insbesondere sollten alle kritischen Designs in Form von vier-Tupeln ausgeliefert werden: 1) das Design selbst, 2) eine Spezifikation, 3) ein manuell nachvollziehbarer Beweis, und 4) ein maschinell verifizierbarer Beweis.

Gegenstand dieser Dissertation sind Korrektheitsbeweise für komplexe Mikroprozessoren. Die Erstellung von Mirkoprozessordesigns gilt als fehleranfällig. Ein bekanntes Beispiel ist der Pentium FDIV bug [Coe95, Pra95].

In dieser Dissertation wird das Problem der Korrektheit von Hardware streng formal behandelt. Die Designs beinhalten Prozessoren mit aktuellen Scheduling Verfahren, wie beispielsweise dem Tomasulo Scheduler aus [Tom67] und spekulativer Ausführung. Im Gegensatz zu weiten Teilen der bestehenden Literatur sind die Designs auf Gatter-Ebene spezifiziert. Insbesondere werden einige der Designs für die XILINX FPGA Serie synthetisiert.

Die Designs haben hohe Komplexität, was sich auf die Beweise auswirkt. Im Gegensatz zu [MP95, Lei99, MP00] sind die Beweise mit dem Theorem Beweissystem PVS verifiziert. Wir geben in dieser Dissertation nicht den originalen PVS Beweis an, sondern versuchen einen nachvollziehbaren Beweis in üblicher mathematischer Notation anzugeben.

Um sequentielle Maschinen zu verifizieren, erweitern wir die Datenkonsistenz-Invariante aus [MP00] indem wir einen "korrekten Wert" eines Implenentation Registers wie beispielsweise *IR*.2 definieren. Gegeben die Korrektheit der funktionalen Komponenten, wie beispielsweise der ALU, erlaubt uns dies den Beweis der Datenkonsistenz der präpariert sequentiellen Maschine in PVS fast völlig zu automatisieren. Wir argumentieren, daß die funktionellen Komponenten korrekte Ergebnisse liefern wenn sie korrekte Eingaben erhalten.

Wir erweitern das Konzept der "stall engine" aus [MP00] indem wir eine vollständig generische stall engine angeben. Im Gegensatz zu der stall engine aus [MP00], erlaubt unsere stall engine eine beliebige Anzahl von Stufen und ermöglicht es, alle Stufen unabhängig voneinander anzuhalten. Des weiteren unterstützt unsere stall engine das Entfernen von "pipeline bubbles". Das bedeutet, daß die Stufen immer dann in Betrieb sind, wenn dies die in-order Eigenschaft zuläßt. Das beinhaltet, daß "pipeline bubbles" wenn notwendig aus der Pipeline entfernt werden. Wir verifizieren die Datenkonsistenz dieser stall engine und geben Eigenschaften an, die es erlauben Laufzeitschanken zu beweisen.

Mit dieser erweiterten stall engine verbessern wir die Transformation der präpariert sequentiellen Maschine in die Maschine mit Pipeline indem wir ein Programm implementieren das diese Transformation automatisiert. Dies beinhaltet die Generierung von Forwarding und Interlock Schaltkreisen.

Anschließen beweisen wir die Datenkonsistenz der Maschine mit Pipeline. Dies wird dadurch erreicht, daß wir beweisen, daß die Eingaben der Pipeline Stufen korrekt sind. Damit können wir wie bei der präpariert sequentiellen Maschine argumentieren, daß die Ausgaben korrekt sind, da die funktionalen Einheiten identisch sind.

Wir geben einen generischen Ansatz zur Realisierung von spekulativer Ausführung an und stellen ein Datenkonsistenzkriterium dafür auf. Wir wenden diese Methode dann an um DLX Pipelines mit Branch Prediction und präzisen Interrupts zu implementieren und zu verifizieren. Es ist allgemein bekannt, daß beide Techniken mit spekulativer Ausführung zu implementieren sind [SP88]. Nach unserem Wissen ist dies jedoch das erste Mal, daß beide Techniken als Instanz eines generischen Mechanismus' für spekulative Ausführung implementiert werden.

Neben den in-order Pipelines verifizieren wir die Korrektheit des Tomasulo Scheduling Algorithmus' mit Reorder Buffer. Der Reorder Buffer bewirkt in-order Terminierung, was es erlaubt, präzise Interrupts zu implementieren. Der Korrektheitsbeweis beinhaltet die Argumente, die notwendig sind, um die Eindeutigkeit der Tags zu beweisen.

Des weiteren beweisen wir eine obere Schranke für die Ausführungszeit von Programmen auf allen Maschinen. Obwohl dies eine kritische Eigenschaft darstellt, wird dieses Thema in oder offenen Literatur oft übergangen.

# Contents

| 1 | Intr | oductio | n                                 | 1  |

|---|------|---------|-----------------------------------|----|

|   | 1.1  | Forma   | l Verification of Microprocessors | 1  |

|   | 1.2  | Relate  | d Work                            | 2  |

|   | 1.3  | Contri  | bution                            | 4  |

|   | 1.4  | Organi  | ization                           | 5  |

| 2 | Basi | c Conc  | epts                              | 7  |

|   | 2.1  | Specif  | ying Machines                     | 7  |

|   |      | 2.1.1   | Mathematical Machines             | 7  |

|   |      | 2.1.2   | Notation                          | 8  |

|   |      | 2.1.3   | Bits and Bit Vectors              | 9  |

|   |      | 2.1.4   | Gates                             | 11 |

|   |      | 2.1.5   | Interpretations of Bit Vectors    | 13 |

|   | 2.2  | Basic   | Circuits                          | 15 |

|   |      | 2.2.1   | Binary Trees                      | 15 |

|   |      | 2.2.2   | Zero Tester                       | 16 |

|   |      | 2.2.3   | Equality Tester                   | 16 |

|   |     | 2.2.4          | Parallel Prefix                                       | 16       |

|---|-----|----------------|-------------------------------------------------------|----------|

|   |     | 2.2.5          | Adders                                                | 19       |

|   |     | 2.2.6          | Verification of a Carry Lookahead Adder               | 21       |

|   | 2.3 | Verific        | ation of an ALU                                       | 22       |

|   |     | 2.3.1          | Specification                                         | 22       |

|   |     | 2.3.2          | Implementation                                        | 25       |

|   | 2.4 | Specif         | ying the Reference Machine                            | 27       |

|   |     | 2.4.1          | DLX Architecture                                      | 27       |

|   |     | 2.4.2          | Configuration of an Integer DLX with Delayed PC       | 27       |

|   |     | 2.4.3          | Initial Configuration                                 | 28       |

|   |     | 2.4.4          | Transition Function                                   | 29       |

|   | 2.5 | Literat        | ure                                                   | 33       |

| 2 |     | anonti         | I Implementation Mashing                              | 35       |

| 3 | 3.1 | -              | al Implementation Machine                             |          |

|   |     |                | repared Sequential Machine                            | 35       |

|   | 3.2 |                | A Simple Hordware Description Longuage                | 36       |

|   |     | 3.2.1<br>3.2.2 | A Simple Hardware Description Language                | 36       |

|   |     |                | The Register Set of the Implementation Machine .      | 37       |

|   |     | 3.2.3          | Scheduling of the Prepared Sequential Machine         | 38<br>41 |

|   |     | 3.2.4          | The Transition Function                               | 41<br>43 |

|   |     | 3.2.5<br>3.2.6 | Inputs                                                | 43<br>47 |

|   |     | 3.2.0<br>3.2.7 | Register Files and Memory     Multiment Band Accesses | 47<br>51 |

|   |     |                | Multiport Read Accesses                               |          |

|   | 2.2 | 3.2.8          | Notation                                              | 51       |

|   | 3.3 |                | nputed Control                                        | 52       |

|   | 3.4 | -              | nenting the Prepared Sequential DLX                   | 53       |

|   |     | 3.4.1          | Structure                                             | 53       |

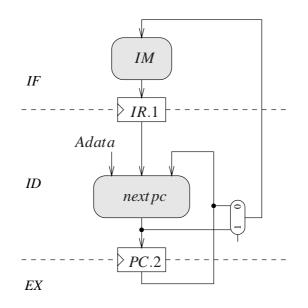

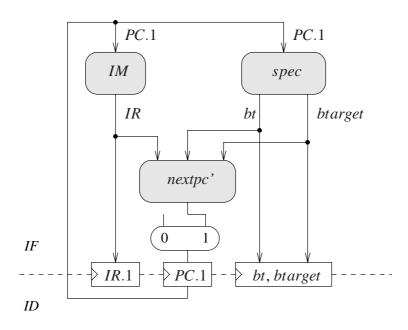

|   |     | 3.4.2          | The Instruction Fetch Stage                           | 55<br>55 |

|   |     | 3.4.3          | The Instruction Decode Stage                          | 55       |

|   |     | 3.4.4          | The Execute Stage                                     | 58       |

|   |     | 3.4.5          | The Memory Stage                                      | 59       |

|      | 3.4.6          | The Write Back Stage                           |

|------|----------------|------------------------------------------------|

| 3.5  | Data C         | Consistency Proof 61                           |

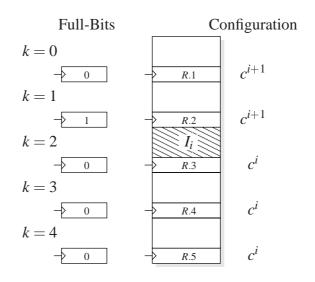

|      | 3.5.1          | Properties of the Full Bits 61                 |

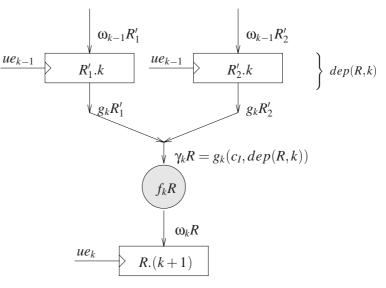

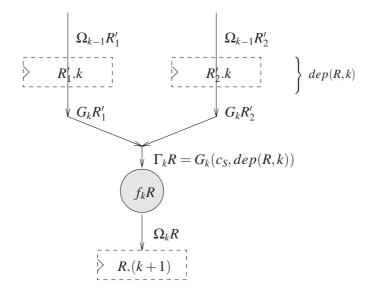

|      | 3.5.2          | Scheduling Functions                           |

|      | 3.5.3          | Properties of the Scheduling Function 65       |

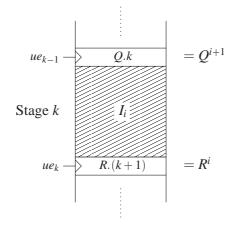

|      | 3.5.4          | Data Consistency Proof Strategy 71             |

|      | 3.5.5          | Correctness of the Transition Functions 78     |

| 3.6  | Livene         | ess                                            |

|      | 3.6.1          | Introduction                                   |

|      | 3.6.2          | Liveness Criterion                             |

|      | 3.6.3          | Liveness Properties of the Scheduling Logic 87 |

|      | 3.6.4          | Liveness Proof for the Sequential DLX 88       |

| 3.7  | Literat        | ture                                           |

| Dine | lined M        | Tachines 91                                    |

| 4.1  |                |                                                |

| 4.1  | 4.1.1          |                                                |

|      |                |                                                |

|      | 4.1.2<br>4.1.3 | 0                                              |

| 4.2  |                | e                                              |

| 4.2  |                | rding                                          |

|      | 4.2.1          | Introduction                                   |

|      | 4.2.2          | Forwarding from the Next Stage 101             |

| 4.0  | 4.2.3          | Result Forwarding                              |

| 4.3  |                | g                                              |

| 4.4  |                | menting the $DLX_{\pi}$                        |

| 4.5  |                | Consistency                                    |

| 4.6  |                | ess                                            |

|      | 4.6.1          | Introduction                                   |

|      | 4.6.2          | Extended Liveness Calculus                     |

|      | 4.6.3          | Liveness Proof                                 |

| 4.7  |                | mance                                          |

| 4.8  | Literat        | ture                                           |

| _ | G    |          |                                                    | 4.40 |

|---|------|----------|----------------------------------------------------|------|

| 5 | -    |          | Execution                                          | 149  |

|   | 5.1  | Introdu  | ction                                              | 149  |

|   | 5.2  | Stall Er | ngine with Speculation                             | 151  |

|   | 5.3  | Schedu   | le with Speculation                                | 153  |

|   | 5.4  | Schedu   | ling Invariants                                    | 157  |

|   | 5.5  | Specula  | ative Inputs                                       | 159  |

|   | 5.6  | Detecti  | ng Misspeculation                                  | 159  |

|   | 5.7  | Rollbac  | k                                                  | 161  |

|   | 5.8  | Extende  | ed Read Access Semantics                           | 163  |

|   |      | 5.8.1    | Specification Registers                            | 163  |

|   |      | 5.8.2    | External Signals                                   | 165  |

|   | 5.9  | Branch   | Prediction                                         | 166  |

|   |      | 5.9.1    | The DLX without Delayed PC $\ldots$                | 166  |

|   |      | 5.9.2    | The Sequential DLX without Delayed PC $\ldots$ .   | 167  |

|   |      | 5.9.3    | The Pipelined DLX without Delayed PC               | 168  |

|   | 5.10 | Data Co  | onsistency                                         | 173  |

|   |      | 5.10.1   | Data Consistency Criterion                         | 173  |

|   |      | 5.10.2   | Properties of the Pipeline                         | 180  |

|   |      | 5.10.3   | Data Consistency Invariants                        | 184  |

|   | 5.11 | Livenes  | 38                                                 | 191  |

|   |      | 5.11.1   | Liveness Proof Strategy                            | 191  |

|   |      | 5.11.2   | Properties of $M(T)$ $\hdots$                      | 192  |

|   |      | 5.11.3   | Rollback Properties                                | 195  |

|   |      | 5.11.4   | Liveness Proof                                     | 209  |

|   | 5.12 | Precise  | Interrupts                                         | 211  |

|   |      | 5.12.1   | Definition                                         | 211  |

|   |      | 5.12.2   | The DLX with Interrupts                            | 211  |

|   |      | 5.12.3   | Hardware for the DLX with Interrupts               | 218  |

|   |      | 5.12.4   | Configuration of the Pipelined DLX with Interrupts | 220  |

|   |      | 5.12.5   | Transition Functions of Stage 0                    | 220  |

|   |      | 5.12.6   | Transition Functions of Stage 1                    | 223  |

|   |      |          |                                                    |      |

xii

|   |      | 5.12.7  | Transition Functions of Stage 2      |  |

|---|------|---------|--------------------------------------|--|

|   |      | 5.12.8  | Transition Functions of Stage 3      |  |

|   |      | 5.12.9  | Transition Functions of Stage 4      |  |

|   |      | 5.12.10 | Data Consistency and Liveness        |  |

|   | 5.13 | Literat | ure                                  |  |

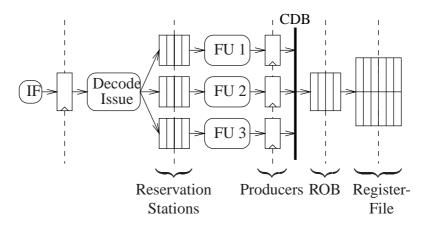

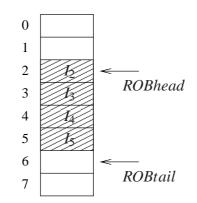

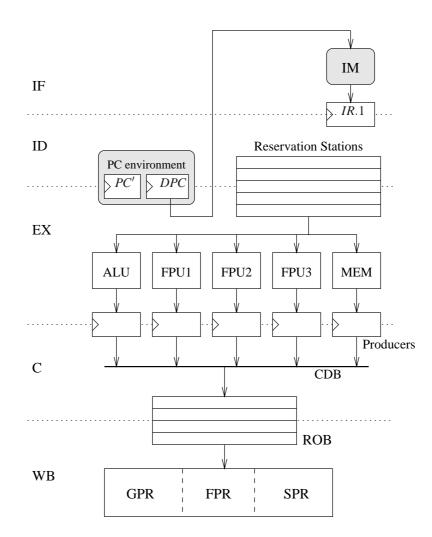

| 6 | Out  | of-Ord  | er Execution 241                     |  |

|   | 6.1  | Introdu | action                               |  |

|   | 6.2  | The To  | masulo Algorithm with Reorder Buffer |  |

|   | 6.3  | Tomas   | ulo Data Structures                  |  |

|   |      | 6.3.1   | Reorder Buffer                       |  |

|   |      | 6.3.2   | Register File Extentions             |  |

|   |      | 6.3.3   | Reservation Stations                 |  |

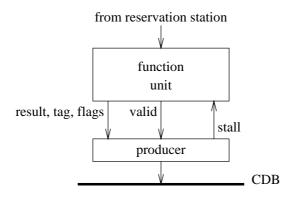

|   |      | 6.3.4   | Producers                            |  |

|   |      | 6.3.5   | Initial Configuration                |  |

|   | 6.4  | Tomas   | ulo Protocols                        |  |

|   |      | 6.4.1   | Formalization                        |  |

|   |      | 6.4.2   | Issue                                |  |

|   |      | 6.4.3   | CDB Snooping                         |  |

|   |      | 6.4.4   | Dispatch 250                         |  |

|   |      | 6.4.5   | Completion                           |  |

|   |      | 6.4.6   | Writeback                            |  |

|   | 6.5  | Data C  | Consistency                          |  |

|   |      | 6.5.1   | Scheduling Functions                 |  |

|   |      | 6.5.2   | Function Unit Axioms 259             |  |

|   |      | 6.5.3   | ROB Flags 261                        |  |

|   |      | 6.5.4   | ROB Properties                       |  |

|   |      | 6.5.5   | Instruction Phases                   |  |

|   |      | 6.5.6   | Tag Consistency                      |  |

|   |      | 6.5.7   | Data Consistency Criterion           |  |

|   |      | 6.5.8   | Forwarding Tags Consistency          |  |

|   |      |         |                                      |  |

xiii

|   |                                                        | 6.5.9 Tag Uniqueness                                     | 283                                                                                                                |

|---|--------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|   |                                                        | 6.5.10 Data Consistency Invariants                       | 287                                                                                                                |

|   | 6.6                                                    | Liveness                                                 | 296                                                                                                                |

|   | 6.7                                                    | Verifying the DLX Implementation                         | 303                                                                                                                |

|   |                                                        | 6.7.1 Implementation Differences                         | 303                                                                                                                |

|   |                                                        | 6.7.2 Verifying the Instruction Fetch                    | 305                                                                                                                |

|   |                                                        | 6.7.3 Verifying IEEEf                                    | 306                                                                                                                |

|   |                                                        | 6.7.4 Verifying Interrupts                               | 308                                                                                                                |

|   | 6.8                                                    | Literature                                               | 309                                                                                                                |

| 7 | Pers                                                   | spective                                                 | 311                                                                                                                |

|   | 7.1                                                    | Functional Units                                         | 311                                                                                                                |

|   | 7.2                                                    | In-Order Scheduling and Forwarding                       | 312                                                                                                                |

|   | 7.3                                                    | Speculation                                              | 313                                                                                                                |

|   | 7.4                                                    | Out-of-Order Execution                                   | 313                                                                                                                |

|   | 7.5                                                    | Synthesizing Hardware                                    | 313                                                                                                                |

| A | The                                                    | orem Index                                               | 315                                                                                                                |

|   | A.1                                                    | The PVS Proof Tree                                       | 315                                                                                                                |

|   |                                                        |                                                          | 210                                                                                                                |

|   | A.2                                                    | Basic Concepts                                           | 316                                                                                                                |

|   | A.2<br>A.3                                             | Basic Concepts       A Sequential Implementation Machine |                                                                                                                    |

|   |                                                        | *                                                        | 317                                                                                                                |

|   | A.3                                                    | A Sequential Implementation Machine                      | 317<br>318                                                                                                         |

|   | A.3<br>A.4                                             | A Sequential Implementation Machine                      | 317<br>318<br>319                                                                                                  |

| в | A.3<br>A.4<br>A.5<br>A.6                               | A Sequential Implementation Machine                      | 317<br>318<br>319                                                                                                  |

| _ | A.3<br>A.4<br>A.5<br>A.6<br>DLX                        | A Sequential Implementation Machine                      | 317<br>318<br>319<br>321                                                                                           |

| _ | A.3<br>A.4<br>A.5<br>A.6<br>DLX<br>Perf                | A Sequential Implementation Machine                      | <ul> <li>317</li> <li>318</li> <li>319</li> <li>321</li> <li>323</li> </ul>                                        |

| C | A.3<br>A.4<br>A.5<br>A.6<br>DLX<br>Perf                | A Sequential Implementation Machine                      | <ul> <li>317</li> <li>318</li> <li>319</li> <li>321</li> <li>323</li> <li>331</li> </ul>                           |

| C | A.3<br>A.4<br>A.5<br>A.6<br>DLX<br>Perf<br>Live<br>D.1 | A Sequential Implementation Machine                      | <ul> <li>317</li> <li>318</li> <li>319</li> <li>321</li> <li>323</li> <li>331</li> <li>335</li> <li>335</li> </ul> |

## Introduction

#### 1.1 Formal Verification of Microprocessors

$N^{\rm OWADAYS,\,microprocessors}$  are in use in many safety-critical environments, such as cars or planes. We therefore consider the correctness of such components as a matter of vital importance.

Verifying the correctness of microprocessors used to be done by extensive tests. However, the state space of modern microprocessors is huge and tests never attain full coverage, especially for 64-bit designs. We therefore think formal verification is the sole way to obtain a guarantee.

This formal verification should be done such that any third party is able to verify the correctness with low effort, i.e., we aim to provide a proof of correctness that can be checked mechanically. In particular, we think that all critical designs should be delivered in form of a four-tuple: 1) the design itself, 2) a specification, 3) a human-readable proof, and 4) a machine-verified proof. Moreover, we think that there will be a considerable market for such four-tuples.

Let us motivate why we distinguish human-readable proofs and machine-readable proofs and why we demand for both. This is not a common demand. In industrial environments, low-effort but automatized verification is preferred.

INTRODUCTION

However, proofs written for theorem proving systems tend to be hard to read. This becomes worse the higher the grade of automatization of the theorem proving system is. We think that this leads to two drawbacks: Without a human-readable proof, one completely depends on the soundness of the theorem proving system. This includes that one depends on the clarity and accuracy of the specification language of the theorem proving system.

The second drawback is that automatized design verification is of no aid in understanding the designs. In contrast to that, we have experienced that writing proofs, in particular the human-readable proofs, is producing generic theories and design approaches previously unknown. We therefore claim that providing human-readable proofs will aid automatizing the actual design process, since generic theories allow for the development of non-specialized tools with diversified use.

In this thesis, we present proofs of correctness for complex microprocessors. Designing microprocessors is considered an error-prone process. Due to the complexity of the designs, errors often remain undiscovered even in case extensive testing is done. A well known example for this is the Pentium FDIV bug [Coe95, Pra95].

#### 1.2 Related Work

There are many publications on the formal verification of sequential machines, e.g., Cohn verified the VIPER processor [Coh87], Joyce verified the Tamarack [Joy88a, Joy88b], Hunt verified the FM8501 [Hun94], and Windley verified the AVM-1 [Win95].

In [HP96, PH94], Hennessy and Patterson describe a 32-bit RISC architecture, the DLX, which serves as basis for many microprocessor verification projects. In [MP95], Mueller and Paul describe sequential DLX designs at gate level, including a machine with precise interrupts.

The formal verification of a pipelined processor is reported in [BS89]: Bickford and Srivas verify a three stage DLX-like RISC processor. In [LO96], Levitt and Olukotun verify a five-stage DLX pipeline by transforming it back into a sequential machine by removing stalling and rollback logic.

In [Hos00], Hosabettu verifies both in-order and out-of-order DLX im-

Section 1.2

**RELATED WORK**

plementations that are not synthesizeable. The pipelined implementation has a trivial stalling logic. The verification is done using the completion function approach and PVS.

Further literature on the verification of pipelined machines is [LO96], which covers automatic verification of pipelined microprocessors, [BM96] provides a manual proof of a DLX pipeline, Burch, Dill [BD94] verify a very simple pipeline. Henzinger et.al. [HQR98] use refinement mappings in order to model-check a RISC pipeline.

Besides PVS, there are more theorem proving systems that are applied for hardware verification, such as HOL [CGM86] or ACL2 [KM96]. There has been much success in verifying complete, complex systems using theorem provers [BS89, HGS99, SH99]. However, theorem proving systems always involve much manual work.

Recent papers show the correctness of complex designs or schedulers in theorem proving systems such as PVS. Hosabettu et al. [HGS99] prove both safety and liveness of Tomasulo's algorithm using PVS. Swada and Hunt [SH99] provide an ACL2 proof of a complete design implementing a Tomasulo scheduler with reorder buffer.

Henzinger et al. [HQR98] verify a simple pipelined processor using a model checker. McMillan [McM98] partly automates the proof by refinement of Tomasulo's algorithm presented in [DP97] with the help of compositional model checking. This technique is improved in [McM99b] by theorem proving methods to support an arbitrary register size and number of function units.

In the literature cited above, the complex designs are verified at very high levels of abstraction. In particular, there is even not much literature on details of actually implementing complex microprocessors. Gatelevel descriptions of microprocessors usually never go beyond simple machines, with the exception of [Lei99] and [MP00]: In [Lei99], Holger Leister presents out-of-order designs and evaluates the architectures regarding hardware cost and performance. The correctness is argued using paper-and-pencil proofs but not verified by means of machine.

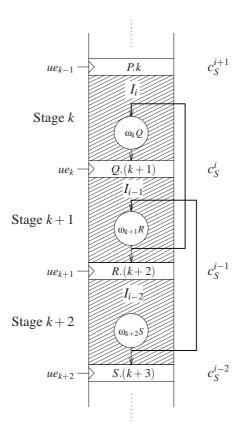

In [MP00], Silvia M. Mueller and Wolfgang J. Paul present gate-level designs of pipelined DLX implementations including a machine with full IEEE floating point arithmetic and interrupts. The correctness of the machines is argued as follows: The authors build a sequential machine but with the structure of a pipelined machine. This machine is called *prepared sequential machine*. The authors transform this prepared sequential machine

INTRODUCTION

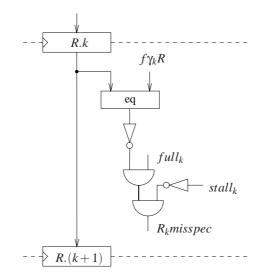

chine into a pipelined machine by adding interlock and forwarding hardware. This is supported by introducing the concept of a *stall engine*. The stall engine encapsulates the logic required for generating clock enable signals for the individual pipeline stages.

The correctness of the pipelined machine is argued as follows: given the correctness of the prepared sequential machine, the authors prove the pipeline to be correct by arguing that it simulates the prepared sequential machine. This is done using a *scheduling function*. This function maps a configuration of the physical machine to a configuration of the abstract reference machine.

#### 1.3 Contribution

In this thesis, we provide a rigorously formal approach to hardware verification. The designs presented in this thesis include state of the art schedulers, such as the Tomasulo scheduler [Tom67] and speculation. In contrast to most of the literature, the designs we provide are very close to gate level. In particular, we are synthesizing some of the designs for the XILINX FPGA series.

These designs are of high complexity, and so are the proofs. In contrast to [MP95, Lei99, MP00], the proofs are machine verified using the theorem proving system PVS [CRSS94]. However, we never present the original PVS proof in this thesis. We aim to provide proofs that come close to comprehensible paper-and-pencil proofs in the tradition of [KP95, MP95, MP00]. We aim to maintain the full formal reasoning of the PVS proofs, to the extent that the proofs are reviewable on a line-per-line basis. This resulted in several PVS proofs to be re-written due to better readability of the paper version of the proof.

In order to verify sequential machines, we extend the data consistency invariant given in [MP00] by defining a "correct value" of an implementation register such as *IR*.2. Given the correctness of functional components such as the ALU, this allows for an almost fully automated proof of the data consistency of the prepared sequential machine using PVS. We argue that the correct functional components provide correct results if given correct inputs.

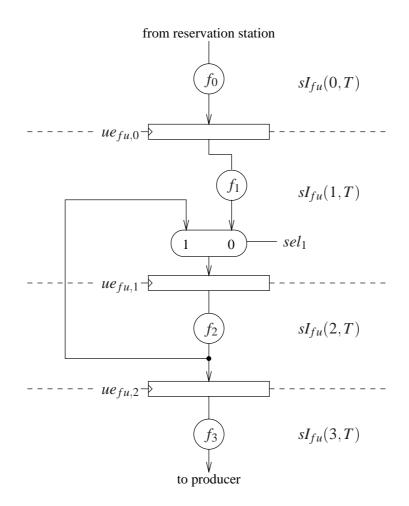

We extend the stall engine concept presented in [MP00] by providing a fully generic stall engine design. In contrast to [MP00], our stall en-

ORGANIZATION

gine design supports an arbitrary number of stages and allows for stalling (and therefore clocking) all stages independently. We formally verify data consistency and liveness properties for this stall engine.

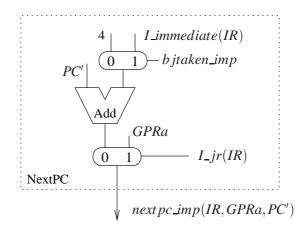

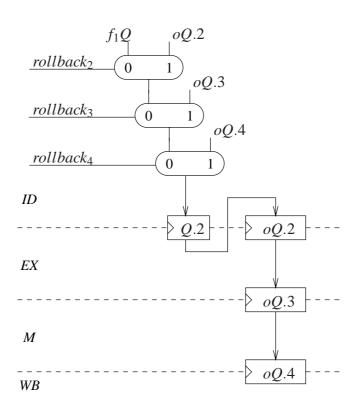

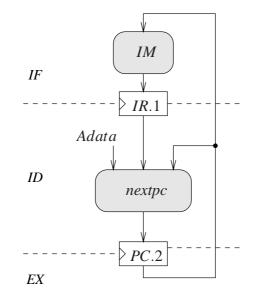

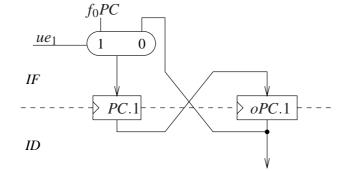

Using this extended stall engine, we can significantly improve the process of transforming the prepared sequential machine into the pipelined machine by providing a tool that does this transformation automatically. This includes the generation for forwarding and interlock hardware. In particular, the transformation of the PC environment of the DLX with Delayed PC, i.e., removing the *DPC* register, turns out to be a special case of adding forwarding.

We then prove the data consistency of the pipelined machine. We do so by showing that the inputs of the pipeline stages are correct. Using this fact, we argue the correctness of the output values as we do for the sequential prepared machine, since the functional components of the machines are identical.

We present a generic approach to speculative execution and propose a data consistency criterion for such a machine. We then apply this method in order to implement and prove DLX pipelines with branch prediction and precise interrupts. It is a well-known fact that both techniques are implemented using speculation [SP88]. However, to the best of our knowl-edge, implementing both techniques as an instance of a generic speculation mechanism is done for the first time.

Besides the in-order pipelines, we verify the correctness of the Tomasulo scheduling algorithm with reorder buffer as described in [KMP99]. The reorder buffer realizes in-order termination which allows implementing precise interrupts. The proof of correctness covers the arguments neccessary to show the uniqueness of the tags.

Furthermore, we rigorously prove the liveness of all machines we design, i.e., we prove that any given instruction sequence is executed within a finite amount of time. Although critical, liveness issues are often not covered in the open literature.

#### 1.4 Organization

Chapter 2 describes basic concepts. We introduce the mathematical hardware model, and describe the implementation and verification of basic cir-

INTRODUCTION

cuits, such as adders. We use these basic circuits in order to implement and verify an ALU. We then provide a formal specification of a DLX RISC microprocessor without interrupts and floating point instructions.

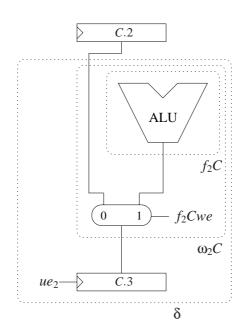

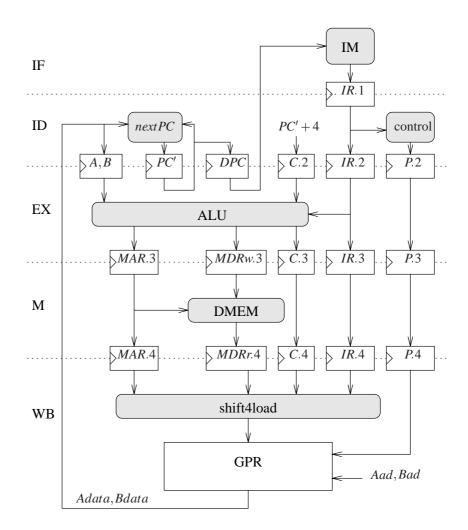

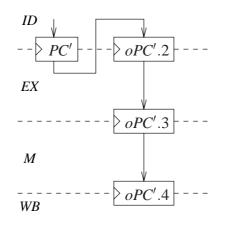

In chapter 3, we describe how we model the hardware of a microprocessor. We describe the extended stall engine for the prepared sequential machine. We introduce the functions used in order to model the registers, the circuits between the registers and the forwarding logic. We use this formalism in order to implement and verify a prepared sequential DLX. We also show the liveness of the prepared sequential machine.

In chapter 4, we describe how the stall engine is modified in order to get a pipelined machine. We describe how to add the forwarding and interlock hardware and prove the correctness of the pipelined machine. This comprises of both data consistency and liveness.

In chapter 5, we describe a generic approach to speculative execution. We prove its data consistency and liveness. We implement two machines as examples: the first machine guesses whether branches are taken or not. The second machine guesses whether we have an interrupt or not. We prove that this realizes precise interrupts according to the specification given in [MP00].

In chapter 6, we describe the results of verifying an out-of-order DLX with Tomasulo scheduler as presented in [Krö99].

# **Basic Concepts**

#### 2.1 Specifying Machines

#### 2.1.1 Mathematical Machines

$T^{\text{HE SUBJECT}}$  of this thesis is to present a provably correct microprocessor. A microprocessor is said to be correct if it interprets a given instruction set architecture (ISA). The instruction set architecture is usually given as an informal list of registers and instructions, and a specification of the impact of these instructions on the values of the registers. The implementation of this ISA, the microprocessor, is a piece of hardware.

In order to make a formal proof of the correctness of such a processor, it is necessary to formalize the specification, the implementation, and the correctness criterion.

Mathematical machines are a common method to model the behavior of arbitrary microprocessor systems. There are different definitions of mathematical machines. In this thesis, the mathematical machine is used to specify both the microprocessor hardware and the instruction set architecture. The correctness criterion and its proof then rely on arguments on these two mathematical machines.

The model used in this thesis is similar to the synchronous transition

```

BASIC CONCEPTS states (STS) model used in [KP96, DP97]. In contrast to [DP97], the math-

ematical machines here work fully deterministic to allow direct hardware

synthesis from the mathematical machine. A very similar approach is also

used in [Cyr93].

```

- **Definition 2.1** A mathematical machine, as used in this thesis, is a triple  $M = (C, c^0, \delta)$  that consists of the following components:

- *C* is the set of all possible configurations of *M*. An element *c* of *C* is called configuration or state of the machine.

- The initial configuration  $c^0$  is a configuration of M.

- The transition function  $\delta: C \to C$  maps one configuration  $c^T$  to its successor  $c^{T+1}$ .

The sequence  $c^0, c^1, \ldots$  of configurations is called computation of M. The configuration  $c^T$  is called configuration in cycle T. The configurations of M in cycles  $T \ge 1$  are defined recursively as follows:

$$c^T = \delta(c^{T-1})$$

In the literature, the transition function is often called next state function [Cyr93].

#### 2.1.2 Notation

**Registers** Both the specification and the implementation of a microprocessor use registers. A register is a place where a value can be stored and re-read in later cycles. In terms of mathematical machines, a value of a register is part of the configuration c.

Let  $\mathbb{R} = \{R_1, \dots, R_n\}$  be a finite set of registers. Each register R can have a value within a finite domain  $\mathbb{W}(R)$ , i.e.,  $R_i \in \mathbb{W}(R_i)$ .

In order to allow an easy identification of the value of a register in the configuration of a mathematical machine, all valid configurations in C are expected to be a tuple of the values of all registers:

$$C = W(R_1) \times W(R_2) \times \ldots \times W(R_n)$$

The value of a given register  $R_i$  can be extracted from a configuration c with a projection function  $\varphi_i$ . Let c be  $(a_1, a_2, \dots, a_n)$ .

$\varphi_{R_i}: C \to \mathbb{W} \ (R_i), \qquad \varphi_{R_i}(c) = a_i$

Let  $c = c^T$  be part of a computation of a mathematical machine. In this case, let  $R^T$  be a shorthand for  $\varphi_R(c^T)$ .

Let *c*.*R* be a shorthand for the value of the projection  $\varphi_R$  applied to *c*:

$$c.R := \varphi_R(c)$$

In analogy to that, let  $\delta R$  be a shorthand for the restriction of a state transition function to a register value:

$$\delta . R : C \to W (R), \qquad \delta . R = \varphi_R \circ \delta$$

#### **Signals**

A signal *s* is defined as a mapping from the set of configurations into an arbitrary domain W(s):

$$s: C \to W(s)$$

Signals are therefore a shorthand for a calculation on a given configuration.

#### 2.1.3 Bits and Bit Vectors

In order to model gates and wiring between gates in a formal way, the theorem proving system PVS [CRSS94] provides a bit vector library. Bits are defined as a boolean value and bit strings are defined as a vector of boolean values.

An *n*-dimensional vector on a domain *D* is a mapping from  $\{i \in \mathbb{N}_0 \mid i < n\}$  into *D*.

#### Section 2.1

Specifying Machines

BASIC CONCEPTS

Let  $a_n$  denote the component n of the vector a:

$$a_n := a(n)$$

**Definition 2.4** A bit is a value in the domain  $B = \{0, 1\}$ . The value 0 is called FALSE *Bits and Bit Vectors* and the value 1 is called TRUE. An *n*-bit bit vector is an *n*-dimensional vector on B. The number *n* is called length of the bit vector. If *a* is an *n*-bit bit vector, this is denoted by:

$$a \in bvec[n]$$

There is a projection function to get a subpart of an *n*-bit bit vector. Let x < n and  $y \le x$ . The function a[x : y] takes a bit vector *a* and returns the subvector from  $a_x$  downto  $a_y$ :

$$[x:y]: bvec[n] \longrightarrow bvec[x-y+1]$$

$$a[x:y](i) := a(i+y) \quad \forall 0 \le i \le (x-y)$$

**Dots Notation** Let  $\circ$  be a binary operator on a set *T*:

$$\circ: T \times T \to T$$

Let *n*, *a*, *b* be nonnegative integers with  $b \ge a$ . Let *X* be an *n*-dimensional vector on *T*. The following definition is used for the common "dots notation":

$$X_a \circ X_{a+1} \circ \ldots \circ X_b := r_{\circ,a,b}(b,X)$$

The function  $r_{\circ,a,b}$  is defined recursively as follows: Let v[n] denote the set of *n*-dimensional vectors on *T*.

$$r_{\circ,a,b}: \{a,\ldots,b\} \times v[b-a+1] \to T$$

$$r_{\circ,a,b}(i,X)$$

:=  $\begin{cases} X_a & : i = a \\ r_{\circ,a,b}(i-1,X) \circ X_i & : \text{ otherwise} \end{cases}$

In case *a* is omitted, zero is assumed:

|       | T = 0 | T = 1 | T = 2 | T = 3 | T = 4 |

|-------|-------|-------|-------|-------|-------|

| $A^T$ | 0     | 1     | 0     | 1     | 1     |

| $B^T$ | 0     | 0     | 1     | 1     | 1     |

Section 2.1

Specifying Machines

Table 2.1 The computation of the example machine

$$r_{\circ,b}: \{0,\ldots,b\} \times v[b+1] \to T$$

$$r_{\circ,b}(i,X)$$

:=  $\begin{cases} X_0 & : i = 0 \\ r_{\circ,b}(i-1,X) \circ X_i & : \text{ otherwise} \end{cases}$

#### 2.1.4 Gates

Using the definition of bits above, the basic gates such as AND and OR are defined in a obvious way: a gate like AND with two inputs and one output is a mapping on two bits:

$$AND: B \times B \longrightarrow B$$

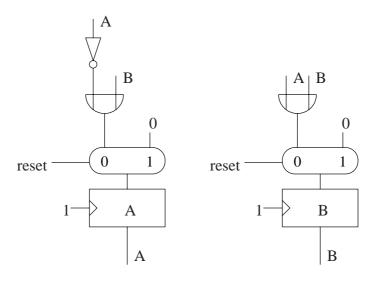

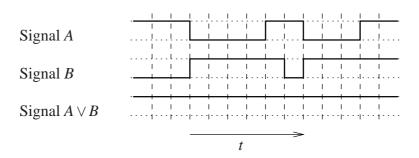

As an example, consider the following mathematical machine (a two bit saturating counter): It has two one bit registers  $\mathbb{R} = \{A, B\}$  with  $\mathbb{W}$  (A) =  $\mathbb{W}$  (B) =  $\mathbb{B}$ . The configuration set C therefore is  $\mathbb{B}^2$ . Let the transition function  $\delta$  be defined as follows:

$$\delta A(c) = \overline{c.A} \lor c.B$$

$$\delta B(c) = c.A \lor c.B$$

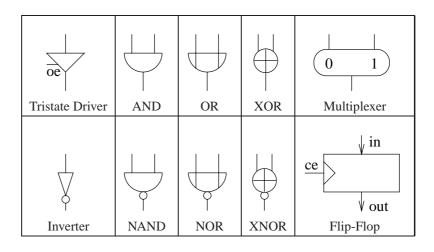

Let the initial configuration  $c_0$  be  $\{0,0\}$ . This mathematical machine models hardware: in order to illustrate the hardware modeled by mathematical machines, the symbols from figure 2.1 are used.

The transition function  $\delta$  models two OR-gates and one inverter. The configuration set models two one-bit registers. In hardware, registers usually do not have defined initial values. In order to get the initial configuration  $c_0$ , an external signal *reset* is assumed. This signal is active during

BASIC CONCEPTS

Figure 2.1 Symbols of the basic gates

Figure 2.2 A two bit saturating counter

cycle -1. Using multiplexers, this allows calculating the initial configuration.

The hardware modeled by the mathematical machine described above is illustrated by figure 2.2. Table 2.1 lists the values of the registers *A* and *B* in the configurations  $c^0$  to  $c^4$ .

#### 2.1.5 Interpretations of Bit Vectors

The interpretation of a bit vector *a* as a binary number is a mapping from the *n*-bit bit vectors into  $\{0, \ldots, 2^n - 1\}$ . The mapping is denoted by  $\langle a \rangle_n$ . If the length of the bit vector argument is obvious in the context, just  $\langle a \rangle$  is used.

$$\langle \rangle_n : bvec[n] \longrightarrow \{0, \dots, 2^n - 1\}$$

$\langle a \rangle_n := \sum_{i=0}^{n-1} a_i \cdot 2^i$

The PVS bit vector library provides the function bv2nat[n] for this purpose. The value of this function is defined by a recursive function that takes an n-bit bit vector and an index *i*: the function sums up the first *i* addends of the sum above:

$$\langle \rangle_n^i : \{0, \dots, n\} \times bvec[n] \longrightarrow \{0, \dots, 2^n - 1\}$$

$\langle a \rangle_n^i = \sum_{j=0}^{i-1} a_j \cdot 2^j$

In PVS, this is defined using a recursion:

$$\langle a \rangle_n^i := \begin{cases} 0 & : i = 0\\ 2^{i-1} \cdot a_{i-1} + \langle a \rangle_n^{i-1} & : \text{ otherwise} \end{cases}$$

It is easy to prove that both definitions are equivalent and that  $\langle a \rangle_n^n = \langle a \rangle_n$  holds.

The interpretation of a bit vector *a* as a two's complement number is a mapping from the *n*-bit bit vectors into  $\{-2^{n-1}, \ldots, 2^{n-1}-1\}$ :

$$[]_n: bvec[n] \longrightarrow \{0, \dots, 2^n - 1\}$$

#### Section 2.1

Specifying Machines

BASIC CONCEPTS

$$[a]_n := -a_{n-1} \cdot 2^{n-1} + \langle a[n-2:0] \rangle_{n-1}$$

The bit  $a_{n-1}$  is called *sign bit*.

This allows defining several operations on bit vectors such as addition and subtraction:

$$+, -: bvec[n] \times bvec[n] \longrightarrow bvec[n]$$

$$a + b := c \quad \text{such that} \quad \langle c \rangle_n = \langle a \rangle + \langle b \rangle \mod 2^n$$

$$a - b := c \quad \text{such that} \quad \langle c \rangle_n = \langle a \rangle - \langle b \rangle \mod 2^n$$

A similar definition is used for operations on a bit vector and an integer:

$+, -: bvec[n] \times \mathbb{Z} \longrightarrow bvec[n]$   $a + b := c \quad \text{such that} \quad \langle c \rangle_n = \langle a \rangle + b \mod 2^n$   $a - b := c \quad \text{such that} \quad \langle c \rangle_n = \langle a \rangle - b \mod 2^n$

An unary minus on bit vectors is defined as follows:

$$-: bvec[n] \longrightarrow bvec[n]$$

$$-a := c \quad \text{such that} \quad \langle c \rangle_n = -\langle a \rangle \mod 2^n$$

The function *zero\_extend*<sub>k</sub> extends a given *n*-bit bit vector to  $k \ge n$  bits by adding zeros:

$$zero\_extend_k : bvec[n] \longrightarrow bvec[k]$$

$$zero\_extend_k(a)_i = \begin{cases} a_i & i < n \\ 0 & : & otherwise \end{cases}$$

The function *sign\_extend*<sub>k</sub> extends a given *n*-bit bit vector to  $k \ge n$  bits by adding the sign bit:

$$sign\_extend_k : bvec[n] \longrightarrow bvec[k]$$

$$sign\_extend_k(a)_i = \begin{cases} a_i : i < n \\ a_{n-1} : otherwise \end{cases}$$

#### 2.2 Basic Circuits

Section 2.2

BASIC CIRCUITS

#### 2.2.1 Binary Trees

Let *n* be a power of two, i.e.,  $n = 2^k$ ,  $k \in \mathbb{N}_0$ . Let  $\circ : T \times T \longrightarrow T$  be a dyadic function that is associative. Let T denote a set and let v[n] denote *Binary Tree Circuit* the set of *n*-dimensional vectors on *T*.

The binary tree is implemented as follows:

$$btree_{\circ,k}: v[2^k] \longrightarrow T$$

$btree_{\circ,k}(X) = \begin{cases} X_0 & : k = 0\\ btree_{\circ,k-1}(X(0), \dots, X(2^{k-1}-1)) \circ & : \text{ otherwise}\\ btree_{\circ,k-1}(X(2^{k-1}), \dots, X(2^k-1)) \end{cases}$

The binary tree circuit  $btree_{\circ,k} : v[n] \longrightarrow T$  calculates the following func-  $\triangleleft$  Lemma 2.1 tion:

$$btree_{\circ,k}(X) = X_0 \circ X_1 \circ \ldots \circ X_{n-1}$$

This is shown by induction on k. For k = 0, the claim is obviously true. **PROOF** For k + 1, the claim is:

$$btree_{\circ,k+1} = X(0) \circ \ldots \circ X(2^{k+1}-1)$$

By definition of *btree*, this is equivalent to:

$$btree_{\circ,k}(X(0),\ldots,X(2^{k}-1)) \circ btree_{\circ,k}(X(2^{k}),\ldots,X(2^{k+1}-1)) =$$

$X(0) \circ \ldots \circ X(2^{k+1}-1)$

By the induction premise for both btree instances, this is equivalent to:

$$(X(0) \circ \ldots \circ X(2^{k} - 1)) \circ (X(2^{k}) \circ \ldots \circ X(2^{k+1} - 1))$$

=  $X(0) \circ \ldots \circ X(2^{k+1} - 1)$

This is shown by induction using that  $\circ$  is associative.

BASIC CONCEPTS

Let *n* be a power of two. The zero tester is implemented as follows:

*zerotester* : *bvec*[

$$n$$

]  $\rightarrow$  B

$$zerotester(a) = btree_{OR}(a)$$

Lemma 2.2 ► The zero tester calculates the following function:

2.2.2 Zero Tester

$zerotester(a) = (\forall i : \overline{a_i})$

This is shown by induction on n using lemma 2.1.

#### 2.2.3 Equality Tester

Using the zero tester, an equality tester is constructed as follows:

*equalitytester* :  $bvec[n] \times bvec[n] \longrightarrow B$

$equalitytester(a,b) = zerotester(a \oplus b)$

Lemma 2.3 ► The equality tester is correct:

equalitytester(a,b) = (a = b)

The correctness is shown easily with lemma 2.2.

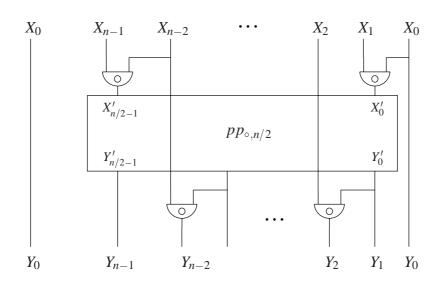

#### 2.2.4 Parallel Prefix

**Definition 2.6** Let T denote a set and let v[n] denote the set of *n*-dimensional vectors *Parallel Prefix* on T. Let  $\circ : T \times T \longrightarrow T$  be an associative dyadic function. The *n*-fold generic parallel prefix circuit  $PP_{\circ,n} : v[n] \longrightarrow v[n]$  calculates the following function:

$$PP_{\circ,n}(X)_i = X_0 \circ X_1 \circ \ldots \circ X_i \qquad i \in \{0, \ldots, n-1\}$$

BASIC CIRCUITS

n > 1

Figure 2.3 The recursive specification of an *n*-fold parallel prefix circuit

The parallel prefix circuit is implemented by means of a recursive definition (figure 2.3). Let *n* be a power of two, i.e.,  $n = 2^K$  with  $K \in \mathbb{N}$ , and let  $X \in v[2^K]$  be the inputs of the circuit.

The function  $ppX'_{\circ}$  calculates the inputs  $X'_0$  to  $X'_{n/2-1}$  for the next recursion step. The recursion depth is given by the first parameter *K*:

$$ppX'_{\circ} : \mathbb{N} \times v[2^{K}] \longrightarrow v[2^{K-1}]$$

$$ppX'_{\circ}(K,X)_{i} := X(2 \cdot i) \circ X(2 \cdot i + 1)$$

Given those inputs, the function  $ppY_{\circ}$  calculates the outputs  $Y_0$  to  $Y_{n-1}$ . As above, the recursion depth is given by the first parameter *K*:

$$ppY_{\circ}(K,X)_{i} = \begin{cases} X_{0} & i = 0\\ ppY_{\circ}(K-1, ppX_{\circ}'(K,X))_{\frac{i-1}{2}} & \text{odd } i\\ ppY_{\circ}(K-1, ppX_{\circ}'(K,X))_{\frac{i}{2}-1} \circ X_{i} & \text{even } i \end{cases}$$

The outputs of the parallel prefix circuit are the values  $Y_0$  to  $Y_{n-1}$ :

$$pp_{\circ}(X)_i := ppY_{\circ}(K,X)_i$$

The parallel prefix circuit is correct:

Theorem 2.4 \_\_\_\_\_

BASIC CONCEPTS

$$pp_{\circ}(X)_i = X_0 \circ X_1 \circ \ldots \circ X_i$$

In order to prove theorem 2.4, the definition pp1 is used. The first parameter defines the number of inputs, the second parameter is the index of the output, the third parameter is the input vector.

$$pp1: \mathbb{N} \times \{0, \dots, 2^{K} - 1\} \times \nu[2^{K}] \longrightarrow T$$

$$pp1(K, i, X) := \begin{cases} X_{0} & : i = 0\\ pp1(K, i - 1, X) \circ X_{i} & : \text{ otherwise} \end{cases}$$

Lemma 2.5  $\blacktriangleright$  This definition is equivalent to  $PP_{\circ,n}$ , which is an easy proof by induction:

$$pp1(K,i,X) = PP_{\circ,n}(X)_i$$

Lemma 2.6  $\blacktriangleright$  If *i* is odd, applying *pp1* to  $X'_0$  to  $X'_{(i-1)/2}$  is equivalent to applying *pp1* to  $X_0$  to  $X_i$ :

$$ppl(K-1,(i-1)/2,ppX'(K,X)) = ppl(K,i,X)$$

If *i* is even and not zero, appending  $X_i$  to the sequence above on the left hand side produces the desired result:

$$ppl(K-1,i/2-1,ppX'(K,X)) \circ X_i = ppl(K,i,X)$$

**PROOF** This is shown by induction on *i*. For i = 0, the claim is obvious. For odd i + 1, the claim is:

$$ppl(K-1, i/2, ppX'(K, X)) = ppl(K, i+1, X)$$

By definition of *pp1*, this is equal to:

$$pp1(K-1,i/2-1,ppX'(K,X)) \circ ppX'(K,X)(i/2) = pp1(K,i+1,X)$$

Unfolding  $ppX'_{\circ}$ , this results in:

$$pp1(K-1, i/2 - 1, ppX'(K, X)) \circ (X_i \circ X_{i+1}) = pp1(K, i+1, X)$$

Since  $\circ$  is associative, this is equal to:

$$(pp1(K-1,i/2-1,ppX'(K,X)) \circ X_i) \circ X_{i+1} = pp1(K,i+1,X)$$

#### Section 2.2

This is shown by unfolding the definition of pp1 on the right-hand side and by the induction hypothesis for even *i*.

For even i + 1, the claim is shown by the definition of pp1 and the induction premise for odd i.

The parallel prefix circuit computes *pp1*.

$$\forall 0 \le k \le K, X \in v[2^k], 0 \le i \le 2^k : ppY(k, i, X) = ppI(k, i, X)$$

.

This is shown by induction on k. For k = 0, the claim is obvious. For **PROOF** k + 1, and after definition unfolding, the claim is:

$$ppY(k+1,i,X) \stackrel{!}{=} ppI(k+1,i,X)$$

For i = 0, the claim is shown by definition unfolding. If *i* is odd, the claim is:

$$ppY(k, (i-1)/2, ppX'(k+1, X)) \stackrel{!}{=} ppI(k+1, i, X)$$

.

This is shown using the induction hypothesis and lemma 2.6.

If *i* is even, the claim is:

$$ppY(k, i/2 - 1, ppX'(k+1, X)) \circ X_i \stackrel{!}{=} ppI(k+1, i, X)$$

This is shown using the induction premise and lemma 2.6.

#### 2.2.5 Adders

The definitions used in this section are taken from the PVS bit vector library. In order to define adders, the two functions *cout* and *sum* are used. Using both functions, one gets a fulladder.

The functions take three input bits a, b, and cin. The function *cout* calculates the carry-out bit of the adder, the function *sum* calculates the sum bit.

*cout*, *sum* :

$$B \times B \times B \rightarrow B$$

19

BASIC CIRCUITS

Lemma 2.7

BASIC CONCEPTS

The functions are defined using XOR, AND, and OR gates as follows:

$$cout(a, b, cin) := (a \land b) \lor ((a \oplus b) \land cin)$$

$sum(a, b, cin) := a \oplus b \oplus cin$

Definition 2.7 Let x and y denote two *n*-bit bit vectors and *cin* a single bit. The carry bits c(0) to c(n-1) are defined as follows:

$c(i) := \begin{cases} cout(x_0, y_0, cin) & : i = 0\\ cout(x_i, y_i, c(i-1)) & : otherwise \end{cases}$

Definition 2.8 ►An *n*-bit adder implements the following function *add* on two *n*-bit bit<br/>vectors *x*, *y*: The function is defined using the addition on bit vectors as<br/>defined in section 2.1.5.

$$add: bvec[n] \times bvec[n] \longrightarrow bvec[n]$$

$add(x,y) = x + y$

Let c(i) denote the *i*-th carry bit as in definition 2.7. An *n*-bit adder with carry-in and carry-out implements the following function *addc* on two *n*-bit bit vectors *x*, *y* and the carry-in bit *cin*:

$addc: bvec[n] \times bvec[n] \times B \longrightarrow bvec[n] \times B$

addc(x, y, cin) := (result, cout)with result :=  $(x + y + \langle cin \rangle)$ , cout := c(n-1)

The carry chain adder is implemented as follows:

$cc: bvec[n] \times bvec[n] \times \mathbb{B} \longrightarrow bvec[n] \times \mathbb{B}$ cc(x, y, cin) := (result, cout) $i \in \{0, \dots, n-1\}: result(i) := \begin{cases} sum(x_0, y_0, cin) & : i = 0\\ sum(x_i, y_i, c(i-1)) & : otherwise\\ cout & := c(n-1) \end{cases}$

Lemma 2.8 ► The carry chain adder is correct according to definition 2.8.

The proof for this lemma is already in the PVS bit vector library.

#### 2.2.6 Verification of a Carry Lookahead Adder

Section 2.2

BASIC CIRCUITS

The *carry lookahead adder* provides both low hardware cost and low depth [KP95].

Let c(0) to c(n-1) denote the carry bits as defined in definition 2.7 for the addition of two *n*-bit bit vectors *a* and *b* and the carry-in bit *cin*. The idea is to use a parallel prefix calculation (definition 2.6) in order to calculate the carry bits c(i). Using these bits, the carry lookahead adder is realized as follows:

$$cla(a, b, cin) = (result, cout)$$

with  $result(i) = a(i) \oplus b(i) \oplus \begin{cases} cin & : i = 0 \\ c(i-1) & : otherwise \end{cases}$

and  $cout = c(n-1)$

The inputs  $(g_i, p_i)$  and the associative function  $\circ$  used for the parallel prefix circuit are taken from [MP00]:

$$p_i := a(i) \oplus b(i)$$

$$g_i := \begin{cases} ((a(i) \oplus b(i)) \land cin) \lor (a(0) \land b(0)) & : i = 0 \\ a(i) \land b(i) & : otherwise$$

$$(g_1, p_1) \circ (g_2, p_2) := (g_2 \lor g_1 \land p_2, p_1 \land p_2)$$

The proof that  $\circ$  is associative is trivial in PVS.

Let G(i) and P(i) denote the outputs of the parallel prefix circuit, i.e., according to theorem 2.4 (correctness of the parallel prefix circuit) this is:

$$G(i) = ((g_0, p_0) \circ \dots \circ (g_i, p_i)).g$$

$$P(i) = ((g_0, p_0) \circ \dots \circ (g_i, p_i)).p$$

We will now show that we get the carry bits by calculating G(i) as above.

The carry bits c are G.

c = G

Lemma 2.9

BASIC CONCEPTS

The proof for this claim is already given in [MP00]. We verify it using PVS.

**PROOF** The proof proceeds by induction on *i*. For i = 0, the claim follows by definition unfolding.

For i + 1, the claim after applying theorem 2.4 (correctness of the parallel prefix circuit) is:

$c(i+1) = ((g_0, p_0) \circ \dots \circ (g_{i+1}, p_{i+1})).g$

By definition of  $\circ$ , this is equivalent to:

$c(i+1) = g_{i+1} \lor ((g_0, p_0) \circ \dots \circ (g_i, p_i)) g \land p_{i+1}$

By the induction hypothesis, this is equivalent to:

$c(i+1) = g_{i+1} \lor c(i) \land p_{i+1}$

By definition of the carry bits, this is equivalent to:

$$a(i+1) \wedge b(i+1) \vee ((a(i+1) \oplus b(i+1)) \wedge c(i))$$

=  $g_{i+1} \vee c(i) \wedge p_{i+1}$

**QED** This is shown by definition of  $g_{i+1}$  and  $p_{i+1}$ .

#### 2.3 Verification of an ALU

#### 2.3.1 Specification

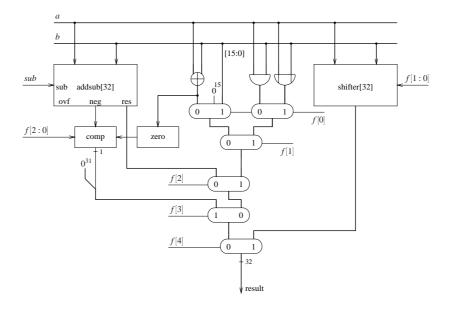

An ALU (arithmetic logical unit) performs operations such as addition, subtraction, comparisons, and bitwise operations such as AND, OR, and XOR.

The ALU takes two 32-bit bit vector operands a and b and additional five bits f. These bits f control the operation performed by the ALU. The ALU returns the result bit vector and an additional bit *ovf* that is set iff an overflow occurred during an addition or subtraction.

# Section 2.3

VERIFICATION OF AN ALU

| f[4] | f[3] | f[2] | f[1] | f[0] | Function                  |

|------|------|------|------|------|---------------------------|

| 0    | *    | *    | 0    | *    | $a \ll b[4:0]$            |

| 0    | *    | *    | 1    | 0    | $a \gg b[4:0]$            |

| 0    | *    | *    | 1    | 1    | $a \gg_a b[4:0]$          |

| 1    | 0    | 0    | 0    | 0    | a+b with overflow test    |

| 1    | 0    | 0    | 0    | 1    | a+b without overflow test |

| 1    | 0    | 0    | 1    | 0    | a-b with overflow test    |

| 1    | 0    | 0    | 1    | 1    | a-b without overflow test |

| 1    | 0    | 1    | 0    | 0    | $a \wedge b$              |

| 1    | 0    | 1    | 0    | 1    | $a \lor b$                |

| 1    | 0    | 1    | 1    | 0    | $a \oplus b$              |

| 1    | 0    | 1    | 1    | 1    | $b[0:15]0^{16}$           |

| 1    | 1    | 0    | 0    | 0    | return zero               |

| 1    | 1    | 0    | 0    | 1    | [a] > [b] ? 1:0           |

| 1    | 1    | 0    | 1    | 0    | a = b ? 1 : 0             |

| 1    | 1    | 0    | 1    | 1    | $[a] \ge [b] ? 1 : 0$     |

| 1    | 1    | 1    | 0    | 0    | a < b ? 1 : 0             |

| 1    | 1    | 1    | 0    | 1    | $a \neq b$ ? 1 : 0        |

| 1    | 1    | 1    | 1    | 0    | $[a] \le [b] ? 1 : 0$     |

| 1    | 1    | 1    | 1    | 1    | return one                |

Table 2.2 ALU functions

**BASIC CONCEPTS**

Figure 2.4 The ALU implementation

Table 2.2 lists the operations performed by the ALU. It is taken from [MP95] with small modifications. The notation  $a \ll b$  is used to denote a left shift of *a* with shift distance *b*,  $a \gg b$  denotes a logic right shift of *a* with shift distance *b*,  $a \gg_a b$  denotes an arithmetic right shift of *a* with shift distance *b*.

**Overflow** Let  $\circ$  be an addition or subtraction, i.e.,  $\circ \in \{+, -\}$ . An overflow indicates that the result of  $[a] \circ [b]$  is not in the range of the 32-bit two's complement numbers. Let  $a \in T_n$  denote that a is in the range of the *n*-bit two's complement numbers.

Table 2.2 does not provide overflow test and comparisons for unsigned binary numbers in contrast to most microprocessors processors such as the MIPS CPUs or the Intel Pentiums [KH92, Int95b]. We do so in order to maintain the instruction set used in [MP00].

#### 2.3.2 Implementation

Figure 2.4 [MP95] gives an overview of the ALU implementation. Depending on the signals f, the result from the appropriate unit is taken.

The addsub unit takes the operands a and b and one extra input bit *sub*, which indicates whether to do an addition or a subtraction. If *sub* is set, the unit performs a subtraction. The *sub* bit is calculated as follows:

$$sub := \overline{f_4 \wedge \overline{f_3} \wedge \overline{f_2} \wedge \overline{f_1}}$$

The unit returns the result bit vector, and the flag bits *ovf* and *neg*. The *ovf* bit is supposed to indicate the overflow condition described in the section above. The *neg* bit is used for the comparison operations and indicates that  $[a] \circ [b]$  is below zero.

The addsub unit is realized as follows: Let op1 and op2 denote the operands. The second operand is inverted in case of a subtraction.

$$op1 := a$$

$op2 := b \oplus (sub^{32})$

This is justified by the following lemma:

For all bitvectors a, inverting and incrementing a implements the unary  $\triangleleft$  Lemma 2.10 minus on bitvectors.

$$(a\oplus(1,\ldots,1))+1=-a$$

This is shown in the PVS bit vector library.

Using the operands and the sub bit the result is calculated by an adder. In the following, the carry lookahead adder (section 2.2.6) is used. However, there is also an implementation and proof of a compound adder, as described in [MP00], in the PVS tree in order to allow cycle time vs. hardware cost tradeoffs. The implementation and the proof are omitted here.

The *sub* bit is passed as carry-in bit to the adder. This realizes the incrementation in case of a subtraction.

$$addsub(a, b, sub) := (result, ovf, neg)$$

### Section 2.3

VERIFICATION OF AN ALU

BASIC CONCEPTS

with result = cla(op1, op2, sub). result

The bits *ovf* and *neg* are calculated as follows:

$$neg = cla(op1, op2, sub).cout \oplus op1[31] \oplus op2[31]$$

$$ovf = neg \oplus cla(op1, op2, sub).result[31]$$

Lemma 2.11

The calculation of *result* in the addsub unit is correct.

$addsub(a, b, sub).result = a \circ b$

This is shown using lemma 2.10 and 2.9.

Lemma 2.12 ► The calculation of the *ovf* signal in the addsub unit is correct.

$addsub(a, b, sub).ovf = ([a] \circ [b]) \notin T_n$

Lemma 2.13 ► The calculation of the *neg* signal in the addsub unit is correct.

$addsub(a, b, sub).neg = ([a] \circ [b]) < 0$

A proof for the lemmas 2.12 and 2.13 can be found in [MP00]. The full proof is also in the PVS tree.

An equality tester is realized by testing if  $a \oplus b$  is zero. Using the output signal *eq* of the zero tester and the signals *ovf* and *neg* from the addsub unit, the comp unit makes the comparisons as follows:

$comp: bvec[5] \times B \times B \longrightarrow B$  $comp(f, neg, eq) = (f_2 \wedge neg) \vee (f_1 \wedge eq) \vee (\overline{eq} \wedge \overline{neg} \wedge f_0)$

Using the lemmas 2.2, 2.3, 2.12, and 2.13, the correctness of the comp unit is shown.

Lemma 2.14 ► The ALU is correct.

This is shown by a case-split on the operation code f using the lemmas above. The correctness of the shifter is assumed.

# 2.4 Specifying the Reference Machine

### 2.4.1 DLX Architecture

The reference machine used for all designs in this thesis is the DLX [HP96, SK96]. However, the DLX architecture serves as an example only. The algorithms and proof method presented here does not depend on any properties of the DLX architecture.

The DLX architecture is a load/store architecture with support for integer and floating point arithmetic. The DLX instruction set (appendix B) is a RISC instruction set and is similar to the MIPS instruction set.

The DLX architecture provides three register files:

- The general purpose register file (GPR) consists of 32 integer registers ( $R_0,...,R_{31}$ ), each of which is 32 bits wide. The register  $R_0$  is defined to be always zero. The general purpose registers are used for all integer operations and memory addressing purposes.

- The **floating point register file** (FPR) consists of 32 single precision floating point registers ( $FGR_0,...,FGR_{31}$ ), each of which is 32 bits wide. These registers can also be accessed as 16 double precision floating point registers ( $FPR_0, FPR_2,...,FPR_{30}$ ), each of which is 64 bits wide. The register  $FPR_0$  is mapped onto the single precision registers  $FGR_0$  and  $FGR_1$ , and so on:

$$FPR_{0}(i) = \begin{cases} FGR_{0}(i) & : i < 32 \\ FGR_{1}(i-32) & : i \ge 32 \end{cases}$$

The floating point registers are used by FPU (floating point unit) instructions only.

• The **special purpose register file** (SPR) consists of several registers needed for special purposes such as flags and masks. An example is the IEEE floating point flags register.

#### 2.4.2 Configuration of an Integer DLX with Delayed PC

The configuration set of the DLX specification machine consists of the visible registers (register files RF), the program counter (PC) registers, and

#### Section 2.4

SPECIFYING THE REFERENCE MACHINE

BASIC CONCEPTS

the main memory (MEM) of the machine:

$$C_{DLX} = \mathbb{W} (RF) \times \mathbb{W} (RPC) \times \mathbb{W} (MEM)$$

The DLX implementation presented in chapter 3 implements integer operations only and no interrupts. The floating point and special purpose registers are not needed therefore. The machine is called DLX<sub> $\sigma$ </sub>.

$$RF = \{GPR[0], \dots, GPR[31]\}$$

$$W \ (GPR[i]) = B^{32}$$

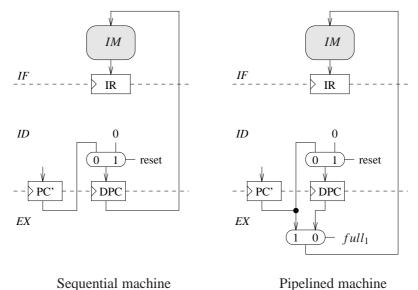

In order to implement pipelining at a high performance level without the need for a branch prediction mechanism, the DLX implemented in this thesis uses the concept of *delayed PCs* [MPK00, MP00]: all modifications to the PC register are delayed by one instruction, not just taken branches. This is realized by buffering the PC register in a register called DPC ("delayed PC"). The Delayed PC technique is provably equivalent to the delayed branch semantics. The delayed branch semantics is, for example, used in the MIPS [KH92], the SPARC [SPA92] and the PA-RISC [Hew94] instruction set.

In order to implement the Delayed PC technique, two PC registers are required: *DPC*, the delayed PC, and *PC'*:

$$RPC = \{DPC, PC'\}$$

$$W (DPC) = W (PC') = B^{32}$$

The main memory of the DLX specification machine consists of  $2^{30}$  memory cells, each of which is 32 bits wide. That accounts for a total of four gigabytes RAM:

$$MEM = \{MEM[0], \dots, MEM[2^{30} - 1]\}$$

W  $(MEM[i]) = B^{32}$

# 2.4.3 Initial Configuration

The GPR registers and the main memory of the  $DLX_{\sigma}$  machine are initialized with arbitrary but fixed values. The PC registers *DPC* and *PC'* are

initialized as follows [MPK00]:

$$c_0.DPC = 0$$

$$c_0.PC' = 4$$

Section 2.4

SPECIFYING THE REFERENCE MACHINE

# 2.4.4 Transition Function

The DLX<sub> $\sigma$ </sub> machine provides control instructions (conditional branch and jump), ALU instructions such as add and compare, and the memory instructions load and store. The instruction that is to be executed is encoded in a 32-bit instruction word. This instruction word is fetched from the instruction memory *IM*, which is assumed to be constant in this thesis. The instruction memory is not part of the configuration therefore.

Let the signal *I* denote the instruction word fetched. The address used to fetch *I* is taken from the register DPC, as required by the Delayed PC technique [MPK00]:

$$I(c) = IM(c.DPC)$$

Figure 2.5 Integer instruction formats of the DLX

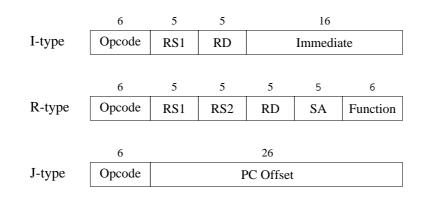

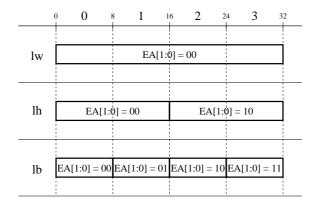

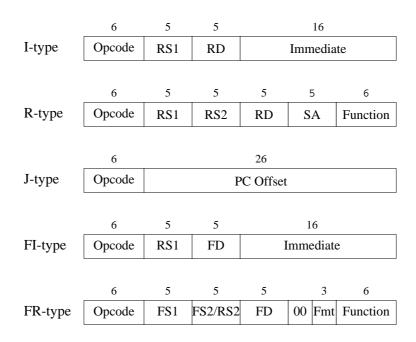

The DLX architecture provides three instruction formats for integer instructions (figure 2.5): the I-type format provides a 16-bit immediate constant and two register addresses, the R-type format provides three register addresses, a 5-bit immediate constant and an additional 6-bit function code. The J-type format provides a 26-bit immediate constant, which is used as PC offset.

BASIC CONCEPTS

The coding of the instructions is given in appendix B. In order to decode the instruction word *I*, the following functions are used: The functions *I\_rtype*, *I\_jtype*, *I\_itype* indicate an R-type, J-type, and I-type instruction, respectively:

$$I\_rtype(I) = (/I_{31} \land /I_{30} \land /I_{29} \land /I_{28} \land /I_{27} \land /I_{26}) \lor (/I_{31} \land I_{30} \land /I_{29} \land /I_{28} \land /I_{27} \land I_{26})$$

$$I\_jtype(I) = (/I_{31} \land /I_{30} \land /I_{29} \land /I_{28} \land I_{27}) \lor (I_{31} \land I_{30} \land I_{29} \land I_{28} \land I_{27})$$

$$I\_itype(I) = \overline{I\_jtype(I)} \land \overline{I\_rtype(I)}$$

The function *I\_JD* extracts the index of the destination register from the instruction word:

$$I\_RD(I) = \begin{cases} I[20:16] : I\_itype(I) \\ I[15:11] : I\_rtype(I) \\ 0^5 : otherwise \end{cases}$$

The functions *I\_RS*1 and *I\_RS*2 extract the index of the first and second operand from the instruction word, respectively:

$$I\_RS1(I) = I[25,21]$$

$I\_RS2(I) = I[20,16]$

The function *L\_immediate* extracts the immediate constant from the instruction word:

$I\_immediate(I) = \begin{cases} sign\_extend_{32}(I[15,0]) &: I\_itype(I) \\ zero\_extend_{32}(I[10,6]) &: I\_rtype(I) \\ sign\_extend_{32}(I[25,0]) &: I\_jtype(I) \\ 0 &: otherwise \end{cases}$

This allows defining the values of the source operands: the integer DLX instructions can have up to two source operands. Let *op1* and *op2* denote the values of these operands. If the address of the operand is zero, the value of the operand is zero by convention:

$$op1(c) = \begin{cases} 0 & : I\_RS1(I) = 0\\ c.GPR[I\_RS1(I)] & : \text{ otherwise} \end{cases}$$

(2.1)

$$op2(c) = \begin{cases} 0 & : I\_RS2(I) = 0\\ c.GPR[I\_RS2(I)] & : \text{ otherwise} \end{cases}$$

(2.2)

**Branch Mechanism** The DLX architecture provides two instructions to modify the PC' register: the branch instructions test a given register for a condition and add the offset given as immediate constant if the condition holds; the jump instructions always set the PC' register to the given value.

Section 2.4

SPECIFYING THE REFERENCE MACHINE

In order to determine the instruction coded by an instruction word I, a boolean function is defined for each instruction. The equations for these functions are generated from the instruction set in appendix B and are in the PVS tree. A list of the functions is also in appendix B.

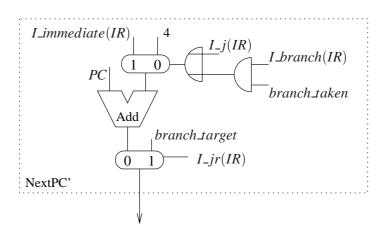

The functions  $I_{-j}(I)$  and  $I_{-jr}(I)$  return true iff the instruction is a jump instruction. In case of  $I_{-j}(I)$ , the immediate constant is used as offset to the PC, in case of  $I_{-jr}(I)$  the jump target is the value of the first operand. The function  $I_{branch}(I)$  is used to detect a branch. If the instruction is a branch,  $I_{branch}_{-eq}(I)$  indicates that the branch is to be taken if the operand is zero. If  $I_{branch}_{-eq}(I)$  does not hold, the branch is to be taken if the operand is not zero.

Let *GPRa* be the value of the operand. The function b *jtaken*(I, *GPRa*) is true iff the given instruction I is a taken branch or jump:

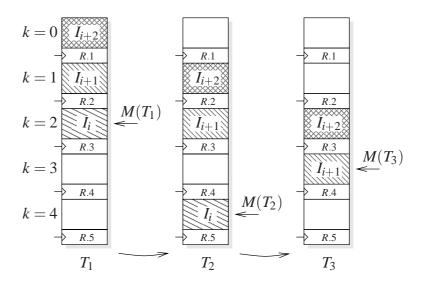

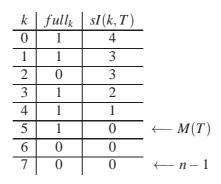

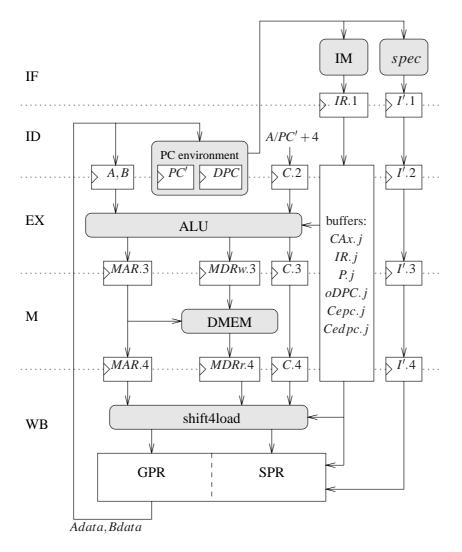

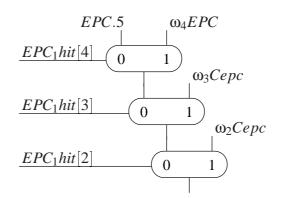

$$b \ jtaken : bvec[32] \times bvec[32] \longrightarrow \mathbb{B}$$