# Formal Verification of a Fully IEEE Compliant Floating Point Unit

### Dissertation

zur Erlangung des Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I der Universität des Saarlandes

### Christian Jacobi

cj@cs.uni-sb.de

Saarbücken, April 2002

ii

Dekan: Prof. Dr. Philipp Slusallek Erstgutachter: Prof. Dr. Wolfgang J. Paul Zweitgutachter: Prof. Dr. Harald Ganzinger Tag des Kolloquiums: 25. Oktober 2002

Hiermit erkläre ich, dass ich die vorliegende Arbeit ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

Saarbrücken, im April 2002

iv

Mathematical proofs, like diamonds, are hard as well as clear, and will be touched with nothing but strict reasoning. — John Locke

> There's always one more bug. — Murphy

### Danke

An dieser Stelle möchte ich allen danken, die zum Gelingen der vorliegenden Arbeit beigetragen haben.

Mein Dank gilt zunächst meinen Eltern, die mich während der gesamten Zeit meiner Ausbildung gefördert haben.

Herrn Prof. Paul danke ich für die Unterstützung während meines Studiums und meiner Promotion.

Danken möchte ich meinen Freunden

- Christoph Berg und Jochen Preiß für viele hilfreiche Diskussionen, das Korrekturlesen der Arbeit und die vielen Skat-Abende;

- Christoph Berg, Sven Beyer, Daniel Kröning, Dirk Leinenbach und Carsten Meyer für die hervorragende Zusammenarbeit im VAMP Projekt;

- allen Mitarbeitern des Lehrstuhls Paul für das gute Arbeits-Klima;

- Jan Pessenlehner für den Gas-Herd.

vi

#### Abstract

In this thesis we describe the formal verification of a fully IEEE compliant floating point unit (FPU). The hardware is verified on the gate-level against a formalization of the IEEE standard. The verification is performed using the theorem proving system PVS. The FPU supports both single and double precision floating point numbers, normal and denormal numbers, all four IEEE rounding modes, and exceptions as required by the standard.

Beside the verification of the combinatorial correctness of the FPUs we pipeline the FPUs to allow the integration into an out-of-order processor. We formally define the correctness criterion the pipelines must obey in order to work properly within the processor. We then describe a new methodology based on combining model checking and theorem proving for the verification of the pipelines.

#### Kurzzusammenfassung

Die vorliegende Arbeit behandelt die formale Verifikation einer vollständig IEEEkonformen Floating Point Unit (FPU). Die Hardware wird auf Gatter-Ebene gegen eine Formalisierung des IEEE Standards verifiziert. Zur Verifikation wird das Beweis-System PVS benutzt. Die FPU unterstützt Fließkommazahlen mit einfacher und doppelter Genauigkeit, normale und denormale Zahlen, alle vier Rundungsmodi und alle Exception-Signale.

Neben der Verifikation der kombinatorischen Schaltkreise werden die FPUs gepipelined, um sie in einen Out-of-order Prozessor zu integrieren. Die Korrektheits-Kriterien, die die gepipelineten FPUs befolgen müssen, um im Prozessor korrekt zu arbeiten, werden formal definiert. Es wird eine neue Methode zur Verifikation solcher Pipelines beschrieben. Die Methode beruht auf der Kombination von Model-Checking und Theorem-Proving.

#### **Extended Abstract**

In this thesis we report on the verification of a fully IEEE compliant floating point unit (FPU). The verification is performed on the gate level against a formalization of the IEEE standard by means of the theorem proving system PVS [OSR92]. The design of the FPU and the formalization of the IEEE standard are based on the textbook on computer architecture by Müller and Paul [MP00]. We extend their work by formally verifying the designs and the formalization of the standard. We have found several errors in the designs as well as in the theory.

The verification is divided into three parts. We first describe the formalization of the IEEE standard. This includes a formalization of normal and denormal numbers and the normalization algorithm. We then define the rounding function. All four rounding modes from the IEEE standard are captured. We prove that the rounding function conforms to the standard. Next, we define the five exceptions from the standard and exponent wrapping. We then describe the concept of  $\alpha$ equivalence from [EP97, MP00].  $\alpha$ -equivalence partitions the real numbers into equivalence classes such that equivalent numbers are rounded the same and yield the same IEEE exceptions, which is also formally proved. We then describe the encoding of floating point numbers in bitvectors and formally define the correctness of the supported floating point operations.

The second part of this thesis covers the verification of the actual floating point hardware against the formalization presented before. We verify three separate FPUs, one for addition and subtraction, one for multiplication and division, and one for comparisons, format conversions, and various miscellaneous operations.

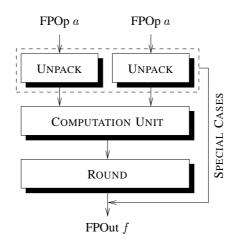

Each FPU is divided into three parts which are verified separately and then are combined to the complete FPU. The first part is an unpacker which converts the operands into some more convenient internal format. It follows the computation unit which performs the actual operation, e.g., an addition or division. The computation units do not need to compute an exact result, but an  $\alpha$ -equivalent approximation. The approximations are fed into the rounding unit which computes the correctly rounded result and the exception flags. By the properties of  $\alpha$ -equivalence it follows that the approximation is rounded to the same result as the exact result would have been.

The decomposition of the FPUs into unpacker, computation unit, and rounding unit eases the verification, since each part can be verified separately. Using the precise, mathematical specifications of each part, the parts can then be composed in a rigorous way.

The verified FPUs are used in an out-of-order processor. In order to exploit the capabilities of this processor, the FPUs are pipelined. The pipelines may process multiple instructions simultaneously, may have variable latency, and may reorder instructions internally. For the iterative division algorithm, the pipeline has a cycle in the pipeline structure. We formally describe the correctness criterion the pipelined FPUs shall obey in order to work properly inside the processor. We have

developed a new methodology based on combining model checking and theorem proving for the verification of the pipelines.

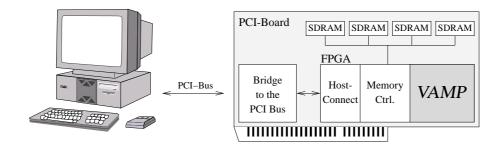

This thesis is part of a larger project at Saarland University which aims at the formal verification of a complete microprocessor including caches and the floating point units from this thesis. Our group has developed a tool which automatically translates hardware specifications from the theorem prover PVS to the hardware description language Verilog. Using this tool, we have implemented and tested the FPU and the complete processor on a Xilinx FPGA. We give a detailed project description and status at the end of this thesis.

#### Zusammenfassung

Die vorliegende Arbeit behandelt die formale Verifikation einer vollständig IEEEkonformen Floating Point Unit (FPU). Die Hardware wird auf Gatter-Ebene gegen eine Formalisierung des IEEE Standards verifiziert. Zur Verifikation wird das Beweis-System PVS [OSR92] benutzt. Das FPU-Design und die Formalisierung des IEEE Standards basieren auf dem Lehrbuch über Computer-Architektur von Müller und Paul [MP00]. Wir erweitern die Arbeit von Müller und Paul, indem wir die Designs und die Formalisierung des Standards formal verifizieren. Wir haben mehrere Fehler in den Designs und in der Theorie gefunden.

Die Verifikation ist in drei Teile aufgeteilt: zunächst beschreiben wir die Formalisierung des IEEE Standards. Diese beinhaltet eine Formalisierung von normalen und denormalen Zahlen und des Normalisierungsalgorithmus'. Danach definieren wir die Rundungsfunktionen. Alle vier Rundungsmodi aus dem Standard werden behandelt. Wir beweisen, dass die Rundungsfunktionen dem Standard entsprechen. Anschließend definieren wir alle fünf Exceptions aus dem Standard und Exponent Wrapping. Wir beschreiben dann das Konzept der  $\alpha$ -Äquivalenz aus [EP97, MP00].  $\alpha$ -Äquivalenz partitioniert die reellen Zahlen in Äquivalenz-Klassen, so dass äquivalente Zahlen gleich gerundet werden und die selben Exceptions auslösen. Dies wird ebenfalls formal bewiesen. Danach beschreiben wir die Einbettung von Fließkommazahlen in Bitvektoren und definieren formal die Korrektheit der unterstützten Operationen.

Der zweite Teil der Arbeit behandelt die Verifikation der eigentlichen Fließkomma-Hardware bezüglich der vorher beschriebenen Spezifikation. Wir verifizieren drei getrennte FPUs: eine für Addition/Subtraktion, eine für Multiplikation/Division, und eine für Vergleich/Konvertierung und einige weitere Operationen.

Jede FPU ist in drei Teile zerlegt, die separat verifiziert werden und später zur kompletten FPU zusammengesetzt werden. Der erste Teil ist der Unpacker, der die Operanden in ein geeigneteres internes Format umwandelt. Es folgt die Berechnungs-Einheit, die die eigentliche Operation ausführt. Die Berechnungs-Einheit braucht nicht das exakte Ergebnis zu berechnen, sondern nur eine  $\alpha$ -äquivalente Approximation. Diese Approximation wird dann an den Runder übergeben, der das korrekt gerundete Ergebnis und die Exceptions berechnet. Die Eigenschaften der  $\alpha$ -Äquivalenz garantieren, dass die Approximation genauso gerundet wird und die selben Exceptions auslöst, wie es dass exakte Ergebnis würde.

Die Zerlegung der FPUs in Unpacker, Berechnungs-Einheit und Runder erleichtert die Verifikation, da jeder Teil einzeln verifiziert werden kann. Die Teile werden dann mit Hilfe ihrer präzisen mathematischen Spezifikation zusammengesetzt.

Die verifizierten FPUs werden in einen Out-of-order Prozessor eingebettet. Um die Möglichkeiten dieses Prozessors auszunutzen, werden die FPUs gepipelined. Die Pipelines können mehrere Instruktionen gleichzeitig ausführen, haben variable Latenz, und können die Instruktionen intern umordnen. Die Pipelines haben Zyklen

in ihrer Struktur, um den iterative Divisions-Algorithmus zu implementieren. Wir definieren formal die Korrektheits-Kriterien, die die gepipelineten FPUs erfüllen müssen, um innerhalb des Prozessors korrekt zu funktionieren. Wir beschreiben eine neue Methode zur Verifikation solcher Pipelines. Die Methode beruht auf der Kombination von Model-Checking und Theorem-Proving.

Die vorliegende Arbeit ist Teil eines größeren Projekts an der Universität des Saarlandes, welches die formale Verifikation eines kompletten Prozessors zum Ziel hat. Der Prozessor beinhaltet Caches und die FPUs aus dieser Arbeit. Unsere Gruppe hat ein Programm entwickelt, welches Hardware-Spezifikationen in PVS automatisch in die Hardware-Beschreibungssprache Verilog übersetzt. Mit Hilfe dieses Programms haben wir die FPU und den gesamten Prozessor auf einem Xilinx FPGA implementiert. Wir beschreiben das Projekt ausführlich am Ende dieser Arbeit. xii

# Contents

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

| 2 | The  | Prototype Verification System              | 3  |

|   | 2.1  | Bits and Bitvectors                        | 3  |

|   | 2.2  | Designing Combinatorial Hardware in PVS    | 5  |

|   | 2.3  | Modeling Clocked Circuits                  | 7  |

|   | 2.4  | Related Work                               | 7  |

| 3 | The  | ory of IEEE Rounding                       | 9  |

|   | 3.1  | Factorings                                 | 10 |

|   |      | 3.1.1 Basic Definitions                    | 10 |

|   |      | 3.1.2 Normalization                        | 11 |

|   |      | 3.1.3 Representable Factorings             | 13 |

|   | 3.2  | Rounding                                   | 13 |

|   |      | 3.2.1 Definition                           | 14 |

|   |      | 3.2.2 Decomposition Theorem                | 14 |

|   |      | 3.2.3 Correctness of the Rounding Function | 16 |

|   | 3.3  | Exceptions and Wrapped Exponents           | 17 |

|   |      | 3.3.1 Overflow                             | 18 |

|   |      | 3.3.2 Underflow                            | 19 |

|   |      | 3.3.3 Wrapped Exponent                     | 20 |

|   |      | 3.3.4 Inexact                              | 21 |

|   | 3.4  | $\alpha$ -Equivalence                      | 21 |

|   | 3.5  | Rounding Representatives                   | 24 |

|   | 3.6  | IEEE Number Format                         | 28 |

|   | 3.7  | Floating Point Operations                  | 30 |

|   |      | 3.7.1 Basic Operations                     | 30 |

|   |      | 3.7.2 Comparison                           | 32 |

|   |      | 3.7.3 Conversion                           | 33 |

|   | 3.8  | Related Work                               | 36 |

| 4 | Veri                | fication of the Floating Point Hardware                                                   |  |  |  |  |

|---|---------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

|   | 4.1                 | Unpacker                                                                                  |  |  |  |  |

|   |                     | 4.1.1 Floating Point Unpacker                                                             |  |  |  |  |

|   |                     | 4.1.2 Fixed Point Unpacker                                                                |  |  |  |  |

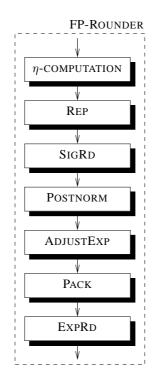

|   | 4.2                 | Rounder                                                                                   |  |  |  |  |

|   |                     | 4.2.1 $\eta$ -Computation Stage                                                           |  |  |  |  |

|   |                     | 4.2.2 Rep, SigRd and Postnorm Stages                                                      |  |  |  |  |

|   |                     | 4.2.3 AdjustExp, Pack and ExpRd Stages                                                    |  |  |  |  |

|   | 4.3                 | Multiplicative Floating Point Unit                                                        |  |  |  |  |

|   |                     | 4.3.1 Multiplication/Division Algorithm                                                   |  |  |  |  |

|   |                     | 4.3.2 Hardware Implementation                                                             |  |  |  |  |

|   |                     | 4.3.3 Special Cases                                                                       |  |  |  |  |

|   |                     | 4.3.4 Putting It All Together                                                             |  |  |  |  |

|   | 4.4                 | Additive Floating Point Unit                                                              |  |  |  |  |

|   |                     | 4.4.1 Additive FPU Core                                                                   |  |  |  |  |

|   |                     | 4.4.2 Special Cases                                                                       |  |  |  |  |

|   |                     | 4.4.3 The Sign of Addition/Subtraction                                                    |  |  |  |  |

|   |                     | 4.4.4 Putting It All Together                                                             |  |  |  |  |

|   | 4.5                 | Comparison, Conversion and Miscellaneous Operations                                       |  |  |  |  |

|   | 7.5                 | 4.5.1 Comparisons                                                                         |  |  |  |  |

|   |                     | 4.5.1       Conversion to Floating-Point Formats                                          |  |  |  |  |

|   |                     | 4.5.2       Conversion to Integer Format         4.5.3       Conversion to Integer Format |  |  |  |  |

|   | 4.6                 | Discrepancies to the IEEE Standard                                                        |  |  |  |  |

|   | 4.7                 | Related Work                                                                              |  |  |  |  |

|   | 4.7                 |                                                                                           |  |  |  |  |

| 5 | Pipelining the FPUs |                                                                                           |  |  |  |  |

|   | 5.1                 | Pipeline Correctness Criterion                                                            |  |  |  |  |

|   |                     | 5.1.1 Formalization of the EU Interface                                                   |  |  |  |  |

|   |                     | 5.1.2 Correctness Criterion                                                               |  |  |  |  |

|   | 5.2                 | Example Pipeline                                                                          |  |  |  |  |

|   | 5.3                 | Pipeline Verification by Theorem Proving                                                  |  |  |  |  |

|   | 5.4                 | Pipeline Verification by Model Checking                                                   |  |  |  |  |

|   | 5.5                 | Translating FairCTL to $\forall t$ form                                                   |  |  |  |  |

|   |                     | 5.5.1 Fixpoints                                                                           |  |  |  |  |

|   |                     | 5.5.2 The FairCTL Operators                                                               |  |  |  |  |

|   |                     | 5.5.3 Proof of $\mu$ -Calculus $\equiv \forall t$ -Form                                   |  |  |  |  |

|   |                     | 5.5.4 Non-Determinism versus Input Sequences                                              |  |  |  |  |

|   | 5.6                 | Pipeline Verification using Model Checking and Theorem Proving                            |  |  |  |  |

|   |                     | 5.6.1 Separating Pipeline Control and Datapaths                                           |  |  |  |  |

|   |                     | 5.6.2 Verification of the Pipeline                                                        |  |  |  |  |

|   |                     | 5.6.3 Some Practical Considerations                                                       |  |  |  |  |

|   | 5.7                 | Putting It All Together                                                                   |  |  |  |  |

|   | 5.8                 | Related Work                                                                              |  |  |  |  |

|   | 2.0                 |                                                                                           |  |  |  |  |

| 6 | The                                    | VAMP Project                                        | 103 |

|---|----------------------------------------|-----------------------------------------------------|-----|

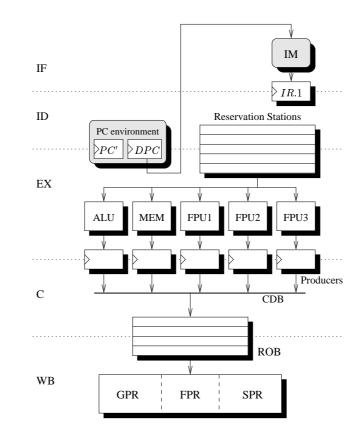

|   | 6.1                                    | The VAMP Processor Core                             | 104 |

|   | 6.2                                    | The Memory Unit                                     | 105 |

|   | 6.3                                    | Verification Effort                                 |     |

|   | 6.4                                    | Translating PVS to Verilog                          | 108 |

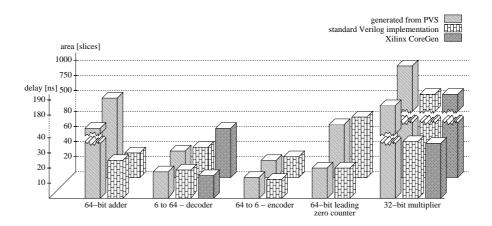

|   | 6.5                                    | Experimental Results                                | 108 |

|   |                                        | 6.5.1 Implementation of General-Purpose Circuits    | 109 |

|   |                                        | 6.5.2 Implementation of the Floating Point Units    | 110 |

|   |                                        | 6.5.3 Implementation of the Complete VAMP Processor | 111 |

|   | 6.6                                    | Related Work                                        | 113 |

| 7 | Sum                                    | mary, Discussion and Future Work                    | 115 |

|   | 7.1                                    | Summary                                             | 115 |

|   | 7.2                                    | Discussion                                          | 116 |

|   | 7.3                                    | Future Work                                         | 118 |

| A | Floa                                   | ting Point Instruction Set                          | 121 |

| B | Proc                                   | of of Carry-Chain adder                             | 123 |

| С | C Circuits, Theorems and Lemmas in PVS |                                                     |     |

| D | Mul                                    | tiplicative Pipeline Control in SMV                 | 133 |

# **List of Figures**

| 2.1  | Construction and correctness statement of a full adder                       | 5   |

|------|------------------------------------------------------------------------------|-----|

| 2.2  | Construction and correctness statement of a carry-chain adder                | 6   |

| 2.3  | Modeling clocked circuits                                                    | 7   |

| 3.1  | $\alpha$ -equivalence                                                        | 22  |

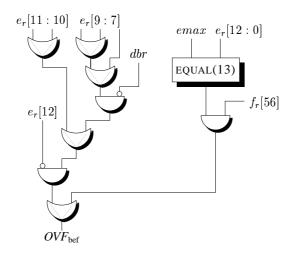

| 3.2  | Computing representatives by sticky-computation                              | 24  |

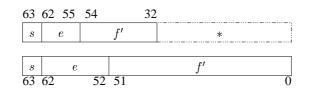

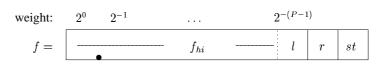

| 3.3  | Embedding of $(s, e, f')$ in one bitvector $\ldots \ldots \ldots \ldots$     | 28  |

| 4.1  | Top-level view of the floating point units.                                  | 39  |

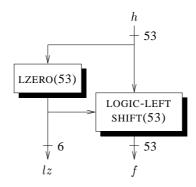

| 4.2  | Normalization shift in the unpacker                                          | 41  |

| 4.3  | Design of the fixed point unpacker                                           | 43  |

| 4.4  | Top-level view of the rounder.                                               | 45  |

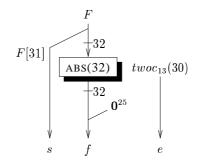

| 4.5  | Computation of $OVF_{bef}$                                                   | 48  |

| 4.6  | Decomposition of the significand into $f_{hi}$ , least-, round-, and sticky- |     |

|      | bit                                                                          | 49  |

| 4.7  | Computation of $[q]_{-(P+1)}$                                                | 57  |

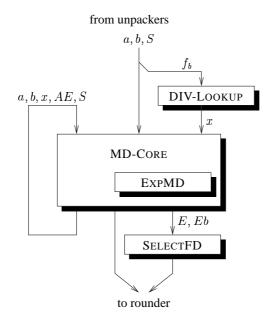

| 4.8  | Top-level schematics of the multiplicative funtional unit                    | 58  |

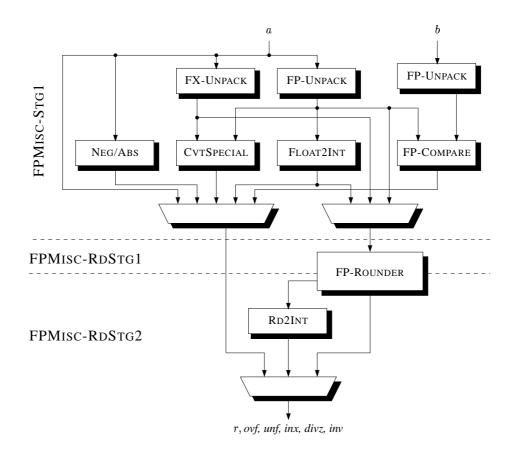

| 4.9  | Top-level schematics of the Misc-FPU.                                        | 71  |

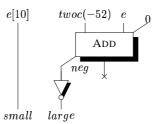

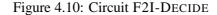

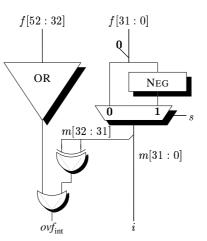

| 4.10 | Circuit F2I-DECIDE                                                           | 75  |

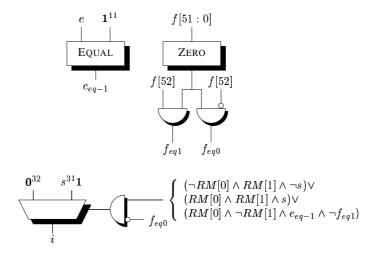

| 4.11 | Circuit F2I-SMALL                                                            | 75  |

| 4.12 | Circuit RD2INT                                                               | 76  |

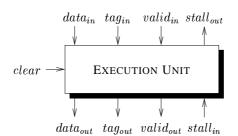

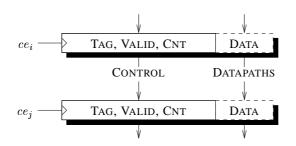

| 5.1  | Execution unit interface                                                     | 83  |

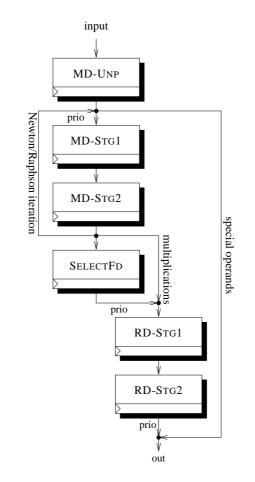

| 5.2  | FPU pipeline                                                                 | 87  |

| 5.3  | Separating Control and Datapaths                                             | 96  |

| 6.1  | Overview of the VAMP microprocessor                                          | 105 |

| 6.2  | Comparison of the cost of translated designs and optimized macros            | 109 |

| 6.3  | Overview of the VAMP processor implementation                                | 112 |

|      |                                                                              |     |

### **Chapter 1**

### Introduction

Over the last decades, microprocessors have become commonly used within many applications. In particular, microprocessors are being used in life-critical environments such as automobiles, air planes, power plants and medical instrumentations. Hence, the correctness of microprocessors is of vital importance.

Simultaneously to the upcoming of microprocessors in everyday's life, the complexity of the processors grew so large that the traditional way of asserting correctness by testing and simulation is now unsatisfactory, at least for safety-critical applications. Furthermore, the cost of errors in microprocessors is gigantic. Probably the most popular example is the Pentium bug [Pra95], which cost Intel nearly half a billion dollar in 1995. One may expect that a similar bug today would cost the tenfold.

Formal verification offers a means to rigorously check the correctness of processors. Our group at Saarland University is currently working on the formal verification of a microprocessor called VAMP (for Verified Architecture MicroProcessor). The VAMP has many complex features also found in contemporary commercial micropocessors: it features pipelined out-of-order execution, precise interrupts, a cache hierarchy, and a floating point unit.

In this thesis, we consider the verification of the VAMP floating point unit (FPU). The FPU is developed in the textbook on computer architecture by Müller and Paul [MP00]. Along with the complete designs come paper-and-pencil proofs for the correctness of the circuits. These proofs served as guidelines for the formal verification in the theorem proving system PVS [OSR92]. The FPU is verified on the gate-level against a formalization of the IEEE standard 754 for binary floating point arithmetic [IEEE]. The formalization of the IEEE standard is based on [Min95, EP97, MP00].

The FPU is fully IEEE compliant. It features both single and double precision operations. All four rounding modes specified in the IEEE standard are implemented. Denormal numbers are handled completely in hardware, and floating point exceptions are computed as required by the standard. The operations supported by the FPU are addition, subtraction, multiplication, division, comparison, conversions, and various others.

In order to implement the FPU with reasonable cycle time, the FPUs are pipelined. The pipelined FPUs may process multiple operations simultaneously, and the operations have variable latency. Furthermore, the operations may be reordered internally, i.e., they need not leave the pipeline in the order they enter it. We have developed a new methodology combining model checking and theorem proving to verify the correctness of the pipelines.

The presented FPU is the first formally verified, fully IEEE compliant floating point unit which is publicly available. The PVS files can be found at our web site<sup>1</sup>.

#### Outline

Chapter 2 briefly describes the theorem prover PVS. We present a summary of PVS's bitvector library, and describe how combinatorial and clocked hardware is designed and specified in PVS. As an example, we present the construction of a simple carry-chain adder.

The main work of this thesis is presented in chapters 3–5. Chapter 3 presents the formalization of the IEEE standard against which the floating point hardware is verified. Furthermore, theorems and notations facilitating the hardware verification are presented. Chapter 4 presents the verification of the combinatorial floating point hardware. In chapter 5, we describe the verification of the pipelining of the combinatorial FPUs.

We present an overview of the VAMP project in chapter 6. Chapter 7 summarizes the thesis and discusses benefits and drawbacks of our approach to the verification and implementation of complex hardware. Finally, we give a brief outlook to future work.

Related work is discussed at the end of each chapter.

<sup>&</sup>lt;sup>1</sup>http://www-wjp.cs.uni-sb.de/~cj/PhD/, see also the VAMP homepage http://www-wjp.cs.uni-sb.de/projects/verification/

### Chapter 2

# The Prototype Verification System

The Prototype Verification System (PVS) [OSR92] is a general-purpose interactive theorem prover developed at SRI International. The PVS system is based on typed higher-order logic within a Genzen-like sequent calculus [Gen35]. PVS features an expressive specification language, powerful decision procedures, e.g., for linear arithmetic, and a  $\mu$ -calculus model-checker [RSS95]. We will not describe PVS in detail here; we refer the reader to various tutorials and manuals on PVS [COR<sup>+</sup>95, OSRSC99a, OSRSC99b, SORSC99].

In the following, we will give a brief overview of PVS's bitvector library which we use throughout this thesis. We then describe how combinatorial and sequential hardware is modeled in PVS. Exemplarily, we describe the construction of a carrychain adder. This is not intended to provide a deep understanding of PVS, but only to give an idea of the way we design and verify hardware.

Except for the construction of the carry-chain adder in section 2.2 we use standard mathematical notation instead of the PVS syntax throughout this thesis. The proofs in this thesis are proofs in mathematical textbook fashion which are extracted from the actual PVS proofs. Using standard mathematical notation eases readability of the definitions and proofs. For reference, we list the PVS names of all lemmas and theorems from this thesis in Appendix C.

#### 2.1 Bits and Bitvectors

In this section, we give a short summary of PVS's bitvector library [BMS<sup>+</sup>96]. The type of bits is defined as  $\mathbb{B} := \{0, 1\}$ . The set of bitvectors of length  $n \in \mathbb{N}^+$  is denoted by  $\mathbb{B}^n$ . PVS distinguishes bitvectors of length 1 from single bits; for the sake of readability we ignore this distinction in this thesis.

Let bv, bv' be bitvectors. The  $i^{\text{th}}$  bit of bitvector bv is denoted by bv[i]. The sub-bitvector  $bv[j] \dots bv[i]$  is denoted by bv[j:i]. The concatenation of bv and

bv' is denoted by  $bv \circ bv'$ . A bitvector of length n consisting solely of b's ( $b \in \mathbb{B}$ ) is denoted by  $b^n$ . The bit-wise connectives  $\land, \lor, \oplus$ , and  $\neg$  on bitvectors of equal length are defined in the usual way.

**Number Representations.** The natural number represented by  $bv \in \mathbb{B}^n$  is defined as

$$\langle bv \rangle := \sum_{i=0}^{n-1} 2^i \cdot bv[i].$$

(2.1)

The two's complement value of bv is

$$[bv] := \begin{cases} \langle bv \rangle & \text{if } \langle bv \rangle < 2^{n-1}, \\ \langle bv \rangle - 2^n & \text{otherwise.} \end{cases}$$

(2.2)

The range of the n-bit two's complement numbers is

$$T_n := \{-2^{n-1}, \dots, 2^{n-1} - 1\}.$$

(2.3)

The proof that  $T_n$  indeed is the range of the *n*-bit two's complement numbers can be found in the bitvector library.

The PVS bitvector library provides a large number of lemmas on bitvectors and the numbers represented by them. For instance, one of the most-often used lemmas states for bitvectors  $bv \in \mathbb{B}^n$ ,  $bv' \in \mathbb{B}^m$ :

$$\langle bv \circ bv' \rangle = \langle bv \rangle \cdot 2^m + \langle bv' \rangle.$$

(2.4)

In the following, we will often use the lemmas from the bitvector library without explicitly quoting them.

The rest of this section is not part the PVS bitvector library. For the definition of IEEE floating point numbers in section 3.6 we need one further integer number format, namely *biased integer* format. For *n*-bit numbers, let  $bias_n := 2^{n-1} - 1$ . The biased integer value of  $bv \in \mathbb{B}^n$  is defined as

$$[bv]_{\text{bias}} := \langle bv \rangle - bias_n. \tag{2.5}$$

Furthermore, we need a notion of binary fractions. Let  $bv \in \mathbb{B}^n$ . When bv shall be interpreted as a number with k digits behind the binary point, its value is  $\langle bv \rangle \cdot 2^{-k}$ . In order to use the large number of bitvector lemmas, we do not introduce a new type for binary fractions, but reuse the standard definition (2.1) and scale by  $2^{-k}$ .

We often write  $bv \in \mathbb{B}^{m+k}$  to denote bitvectors which are interpreted as binary fractions with m bits before and k bits behind the binary point. The formal meaning of  $\mathbb{B}^{m+k}$  is exactly the same as  $\mathbb{B}^n$  for n = m + k;  $\mathbb{B}^{m+k}$  is only a notational hint that bv should be interpreted as a binary fraction.

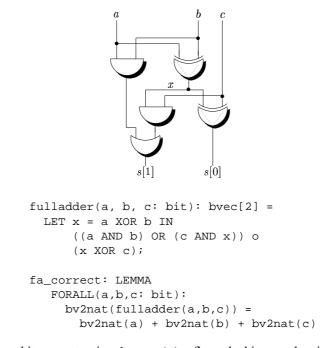

Figure 2.1: Construction and correctness statement of a full adder

**Notation.** For reasons of readability, we often intermix bitvectors and the numbers represented by them in the text. For example, f may denote both the significand's value or the significand's bitvector representation of a floating point number. If the precise distinction of numbers and their bitvector representation is beneficial for the understanding, we use narrow letters f for numbers, and bold letters f for bitvectors.

#### 2.2 Designing Combinatorial Hardware in PVS

In this section, we briefly describe how combinatorial hardware is designed in PVS. As an example we use a simple carry-chain adder.

The PVS language supports the (recursive) definition of functions which call other functions similar to a functional programming language. We use functions to model combinatorial hardware modules. For example, a full adder can be seen as a function which maps three inputs  $a, b, c \in \mathbb{B}$  to a 2-bit output  $s \in \mathbb{B}^2$ . Figure 2.1 compares the construction of such a full adder using schematics and using the PVS language. The correctness of the full adder is asserted in the lemma fa\_correct also shown in figure 2.1.

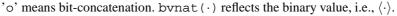

Analogously, an *n*-bit carry-chain adder can be seen as a function which maps the input bitvectors  $a, b \in \mathbb{B}^n$  and the carry-in  $c_{in} \in \mathbb{B}$  to a sum-bitvector  $s \in \mathbb{B}^{n+1}$ . Figure 2.2 shows schematic and PVS constructions of a carry-chain adder.

Figure 2.2: Construction and correctness statement of a carry-chain adder

Note that the function  $carry_chain$  has an additional parameter n used to parameterize the size of the adder. The lemma  $cc_adder_correct$  asserts the correctness of the adder for all widths n. The transcript of the PVS proof of this lemma can be found in Appendix B.

The correctness statements of the full adder and the carry-chain adder relate the hardware implementations to mathematical specifications of the form  $\langle sum \rangle = \langle a \rangle + \langle b \rangle + \langle c_{in} \rangle$ . Having precise specifications of the modules enables the composition of components to more and more complex hardware, and the rigorous mathematical reasoning about these compositions.

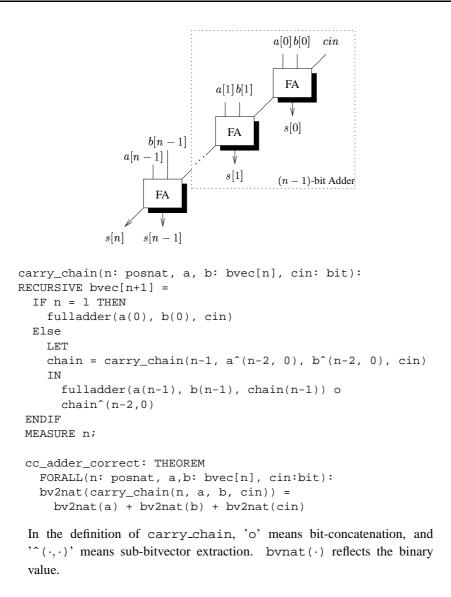

Figure 2.3: Modeling clocked circuits

#### 2.3 Modeling Clocked Circuits

The subset of PVS which we use to model combinatorial hardware is similar to a functional programming language, thus offering no direct support for state-holding variables, as opposed to conventional programming or hardware description languages. Therefore, the concept of registers needs some extra consideration in PVS.

We may regard a clocked circuit as a circuit with only one state-holding register R (which may consist of many bits), and a *combinatorial* circuit ns (cf. Fig. 2.3a). The circuit ns takes as inputs the current state of register R and some external inputs, and computes some outputs and the next state of register R. The combinatorial circuit ns can be represented as a PVS function as described in the previous section:

> $ns: State \times Input \rightarrow State \times Output$ (current\_state, inp)  $\mapsto$  (next\_state, out)

The *State*, *Input*, and *Output* types may be arbitrarily nested records of bitvectors.

Multiple clocked circuits can be combined to one larger clocked circuit by interconnecting inputs and outputs, and using the cartesian product of the state types as new state type (cf. figure 2.3b). In this way, e.g., we embed the FPU into the processor. The result is one single combinatorial next-state function operating on the state of the processor and the state of the FPU.

#### 2.4 Related Work

Formalizing combinatorial and clocked circuits in a functional programming language style, and verification of the hardware using a theorem prover is by no means new. For example, [HD85,KSK93,Mel93,SRC97] design, specify and verify hardware in PVS or other theorem provers in a very similar way.

### Chapter 3

### **Theory of IEEE Rounding**

This chapter presents the theory of rounding which has been used in the verification of the floating point hardware. The theory consists of a formalization of the IEEE standard 754 [IEEE] (mostly simply called "the standard" in this thesis), and notations and theorems facilitating the verification of the actual floating point hardware.

The theory presented in this chapter is primarily based on the work of Even and Paul [EP97] and Müller and Paul [MP00, Chap. 7]. The paper-and-pencil proofs in [MP00] served as guidelines for the formal proofs. Here, their work is extended in that we formally verify the theory in PVS. The definition of the rounding function in this chapter is based on Miner's formalization of the IEEE standard in PVS [Min95].

In section 3.1, we define the notion of *factorings*. Factorings are a numerical abstraction of bitvector-represented floating point numbers. The abstraction eases the verification, since one may argue about numbers instead of single bits and bitvectors. We proceed in section 3.2 with the definition of the rounding function and the proof of the *decomposition theorem of rounding*, which allows to split the rounding process into three steps. This enables a decomposition of the actual rounding hardware in a similar fashion, which in turn simplifies the design and the verification of the rounding hardware (see chapter 4). In section 3.3 we define the floating point exceptions and exponent wrapping.

The concept of  $\alpha$ -equivalence is defined in section 3.4.  $\alpha$ -equivalence is a concise way to talk about sticky-bit computations. The real numbers are partitioned into equivalence classes by means of  $\alpha$ -equivalence. The salient property of this partitioning is that for appropriate  $\alpha$ ,  $\alpha$ -equivalent numbers are rounded to the same floating point number, which is proved in section 3.5.  $\alpha$ -equivalence enables a decomposition of the FPU into computation units (e.g., adder, divider) and a rounding unit. The computation unit delivers a result to the rounder which needs not be exact but only  $\alpha$ -equivalent to the exact result. The rounder therefrom computes the correct floating point result and the exception signals. The decomposition simplifies the design and the verification of the FPU, since one can handle

the units separately and then compose them using the theorems on  $\alpha$ -equivalence and rounding.

In section 3.6 we describe the encoding of floating point numbers in the bitvector representation defined in the standard. We also introduce the special values *infinity* and *Not-a-Number* (NaN). The supported floating point operations are described in section 3.7. We give a correctness predicate for the basic operations  $(+, -, \times, \div)$  on non-special operands. We then define the result of comparisons between floating point numbers, and of conversions between different floating point formats and between floating point numbers and integers. Section 3.8 discusses related work.

Sections 3.1–3.5 of this chapter are a revised version of [Jac01], which has been presented as a poster at TPHOLs 2001.

#### 3.1 Factorings

#### 3.1.1 Basic Definitions

We abstract IEEE numbers as defined in the standard to *factorings*. A factoring is a triple (s, e, f) with sign bit  $s \in \{0, 1\}$ , exponent  $e \in \mathbb{Z}$ , and significand  $f \in \mathbb{R}_{\geq 0}$ . Note that exponent range and significand precision are unbounded. The value of a factoring is

$$[s, e, f] := (-1)^s \cdot 2^e \cdot f.$$

The standard introduces an exponent width N, from which constants  $e_{\min} := -2^{N-1} + 2$  and  $e_{\max} := 2^{N-1} - 1$  are derived. These constants are used to bound the exponent range.

We call a factoring (s, e, f) normal if  $e \ge e_{\min}$  and  $1 \le f < 2$ . A factoring is called *denormal* if  $e = e_{\min}$  and  $0 \le f < 1$ . We call a factoring an *IEEE factoring* if it is either normal or denormal.

The following lemmas list some basic facts about factorings. We omit the proofs since they are fairly simple.

**Lemma 3.1** A factoring (s, e, f) has zero value, iff f = 0.

**Lemma 3.2** Let (s, e, f) and (s', e', f') be factorings with  $1 \le f, f' < 2$ . It holds

$$e > e' \implies |\llbracket s, e, f \rrbracket| > |\llbracket s', e', f' \rrbracket|$$

The property also holds for IEEE factorings.

**Lemma 3.3** Let (s, e, f) and (s', e', f') be IEEE factorings. It holds

$$|\llbracket s, e, f \rrbracket| > |\llbracket s', e', f' \rrbracket| \iff (e > e' \lor (e = e' \land f > f')).$$

The next lemma states that nonzero IEEE factorings are unique:

**Lemma 3.4** Let (s, e, f) and (s', e', f') be IEEE factorings with nonzero value. It holds

$$\llbracket s,e,f \rrbracket = \llbracket s',e',f' \rrbracket \iff (s,e,f) = (s',e',f').$$

Zero has two IEEE factorings  $(0, e_{\min}, 0)$  and  $(1, e_{\min}, 0)$ , called +0 and -0, respectively.

#### 3.1.2 Normalization

Next, we define the normalization algorithm. We start by defining a function  $\widehat{norm}$  which maps nonzero factorings to factorings with significand between 1 and 2:

$\widehat{\mathit{norm}}(s,e,f) := (s,e + \lfloor \log_2 f \rfloor, f \cdot 2^{-\lfloor \log_2 f \rfloor}).$

We proceed with the definition of the function *norm*, which maps any (possibly zero) factoring to an IEEE factoring. Let  $(\hat{s}, \hat{e}, \hat{f}) := \widehat{norm}(s, e, f)$ :

$$norm(s, e, f) := \begin{cases} (\hat{s}, \hat{e}, \hat{f}) & \text{if } f \neq 0 \text{ and } \hat{e} \ge e_{\min}, \\ (\hat{s}, e_{\min}, \hat{f} \cdot 2^{\hat{e}-e_{\min}}) & \text{if } f \neq 0 \text{ and } \hat{e} < e_{\min}, \\ (s, e_{\min}, 0) & \text{if } f = 0. \end{cases}$$

The following lemma summarizes the most important properties of the normalization functions:

**Lemma 3.5** Let (s, e, f) be an arbitrary factoring. It holds:<sup>1</sup>

- (i)  $\|\widehat{norm}(s, e, f)\| = \|s, e, f\|$  if  $f \neq 0$ ,

- (ii)  $1 \le \widehat{norm}_f(s, e, f) < 2$  if  $f \neq 0$ ,

- (*iii*) [norm(s, e, f)] = [s, e, f],

- (iv) norm(s, e, f) is an IEEE factoring.

Having defined the normalization algorithm, we define conversion functions  $\eta$  and  $\hat{\eta}$ , which assign factorings to reals x:

$$\begin{aligned} \hat{\eta}(x) &:= \widehat{norm}(sign(x), 0, |x|) & \text{for } x \neq 0, \\ \eta(x) &:= norm(sign(x), 0, |x|) & \text{for arbitrary } x, \end{aligned}$$

where sign(x) = 0 if  $x \ge 0$ , and sign(x) = 1 otherwise.<sup>2</sup>

**Lemma 3.6** Let  $x \in \mathbb{R}$ . It holds:

(i)  $x = [\hat{\eta}(x)]$  if  $x \neq 0$ ,

$<sup>\</sup>widehat{norm}_f(s, e, f)$  denotes the *f*-component of the triple  $\widehat{norm}(s, e, f)$ ; analogous for other functions and components.

<sup>&</sup>lt;sup>2</sup>We distinguish +0 and -0 in our theory of factorings, but for the conversion from reals to factorings we convert  $0 \in \mathbb{R}$  to +0.

(*ii*)  $x = [\![\eta(x)]\!]$

**Lemma 3.7** Let  $x \in \mathbb{R}$  with  $x \neq 0$  in the context of  $\hat{\eta}$ . It holds:

(i)  $\hat{\eta}_e(x) = \lfloor \log_2 |x| \rfloor$ (ii)  $\hat{\eta}_f(x) = |x| \cdot 2^{-\hat{\eta}_e(x)}$ (iii)  $\eta_e(x) = \begin{cases} \lfloor \log_2 |x| \rfloor & \text{if } x \neq 0 \text{ and } \lfloor \log_2 |x| \rfloor \ge e_{\min}, \\ e_{\min} & \text{otherwise.} \end{cases}$ (iv)  $\eta_f(x) = |x| \cdot 2^{-\eta_e(x)}$

The above lemmas all follow easily by expanding definitions and applying some basic arithmetic.

**Lemma 3.8** Let (s, e, f) be an arbitrary factoring with value  $x := [\![s, e, f]\!], x \neq 0$ . It holds

- (i)  $|x| \ge 2^{e_{\min}} \Longrightarrow \eta(x) = \hat{\eta}(x)$ , i.e.,  $\eta$  and  $\hat{\eta}$  coincide for normal numbers.

- (ii) If  $1 \le f < 2$ , it holds  $(s, e, f) = \hat{\eta}([\![s, e, f]\!])$ .

- (iii) If (s, e, f) is an IEEE factoring, it holds  $(s, e, f) = \eta(\llbracket s, e, f \rrbracket)$ .

- (iv)  $\hat{\eta}_e(x) \leq \eta_e(x)$

*Proof:* Statements (*i*),(*ii*) and (*iv*) are simple consequences of lemma 3.7. Statement (*iii*) is proved by using lemma 3.4 with  $(s', e', f') = \eta([\![s, e, f]\!])$ .

**Lemma 3.9** Let  $x \in \mathbb{R}$  and  $(s, e, f) = \eta(x)$ . It holds:

- (i) (s, e, f) is normal, iff  $|x| \ge 2^{e_{\min}}$ ,

- (ii) (s, e, f) is denormal, iff  $|x| < 2^{e_{\min}}$ .

*Proof:* It suffices to prove the first part, the second then follows directly, since  $\eta(x)$  is either normal or denormal by definition of IEEE factorings. If x = 0, the claim holds trivially. If (s, e, f) is normal, it holds  $e \ge e_{\min}$  and  $f \ge 1$ , hence  $2^e \cdot f \ge 2^{e_{\min}}$ . From lemma 3.6(*ii*) and the definition of  $\llbracket \cdot \rrbracket$  we conclude  $|x| \ge 2^{e_{\min}}$ . Assume otherwise that  $|x| \ge 2^{e_{\min}}$ . From lemma 3.8(*i*) we know  $(s, e, f) = \hat{\eta}(x)$ . The claim now follows from lemmas 3.5(*ii*) and 3.7(*i*).

#### 3.1.3 Representable Factorings

Let P be the significand precision as defined in the standard. A significand f is called *representable*, if f has at most P - 1 digits behind the binary point, i.e., if  $2^{P-1} \cdot f \in \mathbb{N}_0$ . We call an IEEE factoring (s, e, f) semi-representable, if f is representable. We call an IEEE factoring *representable*, if it is semi-representable, and furthermore  $e \leq e_{\text{max}}$  holds. We call a real x (semi-)representable, if  $\eta(x)$  is (semi-)representable.

Representable numbers exactly correspond to the representable numbers as defined in the standard (cf. lemmas 3.36 and 3.37). Common values for (N, P) are (8, 24) and (11, 53), called single and double precision, respectively. However, the theory described here is not limited to these values of N and P. We only assume N > 2 and P > 1. The standard defines an encoding of single and double precision IEEE factorings into bitvectors of length 32 and 64, respectively (cf. section 3.6). The idea behind factorings is to leave the bitvector level and argue about the more abstract factorings in order to ease the verification of hardware.

The following lemma bounds (semi-)representable numbers.

**Lemma 3.10** Let (s, e, f) be a semi-representable factoring, and i > e be an integer. It holds

- (i)  $f \le 2 2^{1-P}$ ,

- (*ii*)  $|[s, e, f]| \le 2^i 2^{i-P}$ ,

- (iii)  $X_{\text{max}} := 2^{e_{\text{max}}} \cdot (2 2^{1-P})$  is the largest representable number.

The following lemma characterizes the minimum distance between distinct semirepresentable factorings:

**Lemma 3.11** Let (s, e, f) and (s', e', f') be semi-representable factorings with values  $x := [\![s, e, f]\!]$  and  $x' := [\![s', e', f']\!]$ , let  $x \neq x'$ , and i be an integer. It holds

$$e \ge i \text{ and } e' \ge i \Longrightarrow |x - x'| \ge 2^{i - (P-1)}$$

The following lemma states that semi-representability is not disturbed by multiplication with powers of 2:

**Lemma 3.12** Let (s, e, f) be a semi-representable factoring, and  $n \in \mathbb{N}_0$ . Then  $\eta(2^n \cdot [\![s, e, f]\!])$  is a semi-representable factoring.

#### 3.2 Rounding

Since (semi-)representable numbers are not closed under arithmetic operations (e.g., addition, division), the IEEE standard defines four rounding modes: round to nearest, round up, round down, and round to zero. In this section, we define the rounding function, which maps arbitrary reals to semi-representable numbers according to the standard. The definition is similar to Miner's definition [Min95]; it only differs in cases of overflow and underflow (Sect. 3.3).

#### 3.2.1 Definition

We start with the definition of a function  $r_{int}(\cdot, \mathcal{M})$  for each rounding mode  $\mathcal{M} \in \{near, up, down, zero\}$ , which rounds reals x to integers:

$$\begin{aligned} r_{\text{int}}(x, up) &:= [x] \\ r_{\text{int}}(x, down) &:= [x] \\ r_{\text{int}}(x, zero) &:= (-1)^{sign(x)} \cdot \lfloor |x| \rfloor \\ r_{\text{int}}(x, near) &:= \begin{cases} \lfloor x \rfloor & \text{if } x - \lfloor x \rfloor < \lceil x \rceil - x, \\ \lceil x \rceil & \text{if } x - \lfloor x \rfloor > \lceil x \rceil - x, \\ x & \text{if } \lfloor x \rfloor = \lceil x \rceil, \\ 2 \lfloor \lceil x \rceil / 2 \rfloor & \text{otherwise.} \end{cases} \end{aligned}$$

Note that  $x - \lfloor x \rfloor$  and  $\lceil x \rceil - x$  are simply the fraction of x and its complement, respectively.

By scaling by  $2^{P-1}$ , reals are rounded to rationals with P-1 fractional digits:

$$r_{\operatorname{rat}}(x, \mathcal{M}) := 2^{-(P-1)} \cdot r_{\operatorname{int}}(x \cdot 2^{P-1}, \mathcal{M}).$$

Further scaling with  $2^e$ ,  $e := \eta_e(x)$ , yields the IEEE rounding function:

$$rd(x, \mathcal{M}) := 2^e \cdot r_{rat}(x \cdot 2^{-e}, \mathcal{M}).$$

It is not obvious that this definition conforms with the IEEE standard. In section 3.2.3 we prove a theorem to convince the reader of the conformance.

#### **3.2.2 Decomposition Theorem**

The decomposition theorem we prove in this section decomposes the computation of the rounding function into three steps:  $\eta$ -computation (sometimes called prenormalization in the literature), significand rounding, and a post-normalization. The benefit of having the decomposition theorem is that it simplifies the design and verification of rounder implementations. Furthermore, it is a powerful tool in other proofs, e.g., in theorem 3.28.

The  $\eta$ -computation step computes the IEEE factoring  $X = \eta(x)$ , where x is the number to be rounded. The significand round step then rounds the significand computed in the  $\eta$ -computation to P - 1 digits behind the binary point. This is formalized in the function *sigrd*:

$$sigrd(X, \mathcal{M}) := \left| r_{rat} \left( (-1)^s \cdot f, \mathcal{M} \right) \right|,$$

where X = (s, e, f) is an IEEE factoring, and  $\mathcal{M}$  is a rounding mode. The following lemma states some properties of the *sigrd* function:

#### Lemma 3.13

(i)  $sigrd(X, \mathcal{M}) = |rd(\llbracket X \rrbracket, \mathcal{M})| \cdot 2^{-e}$ ,

- (ii)  $0 \leq sigrd(X, \mathcal{M}) \leq 2$ ,

- (iii)  $1 \leq f \Longrightarrow 1 \leq sigrd(X, \mathcal{M}),$

- (iv)  $1 > f \implies 1 \ge sigrd(X, \mathcal{M}),$

- (v)  $sigrd(X, \mathcal{M}) \cdot 2^{P-1}$  is an integer.

*Proof:* Part (*i*) follows by expanding the definitions of *sigrd* and *rd*. For parts (*ii*)–(*iv*) one expands the definition down to  $r_{int}$  and applies basic properties of the floor and ceiling functions. Part (*v*) is a direct consequence of the definition of  $r_{rat}$ .

In the case that the significand rounding returns 0 or 2, the factoring has to be post-normalized. If the significand round returns 0, the sign bit is forced to 0 in order to yield  $\eta(0)$ . In case the significand round returns 2, the exponent is incremented, and the significand is forced to 1:

$$postnrom(X, \mathcal{M}) = \begin{cases} (s, e, sigrd(X, \mathcal{M})) & \text{if } 0 < sigrd(X, \mathcal{M}) < 2, \\ (s, e+1, 1) & \text{if } sigrd(X, \mathcal{M}) = 2, \\ (0, e_{\min}, 0) & \text{if } sigrd(X, \mathcal{M}) = 0. \end{cases}$$

**Lemma 3.14** The result postnrom(X, M) of the post-normalization is a semirepresentable IEEE factoring.

*Proof:* The case  $sigrd(X, \mathcal{M}) \in \{0, 2\}$  is trivial. Assume  $0 < sigrd(X, \mathcal{M}) < 1$ . By lemma 3.13(*iii*) we know f < 1, and hence  $e = e_{\min}$  since X is an IEEE factoring. Therefore  $postnrom(X, \mathcal{M})$  is an IEEE factoring, and with lemma 3.13(v) it is a semi-representable factoring.

Now assume  $1 \leq sigrd(X, \mathcal{M}) < 2$ . Since the input X is an IEEE factoring, we know  $e \geq e_{\min}$ , and hence  $(s, e, sigrd(X, \mathcal{M})) = postnrom(X, \mathcal{M})$  is an IEEE factoring; semi-representability now follows from lemma 3.13(v).

**Lemma 3.15**  $[postnrom(X, \mathcal{M})] = rd([X], \mathcal{M}).$

*Proof:* Apply lemma 3.13(*i*) and expand definitions.

**Theorem 3.16 (Decomposition Theorem)** For any real x, and rounding mode  $\mathcal{M} \in \{near, up, down, zero\}$ , it holds

$$postnrom(\eta(x), \mathcal{M}) = \eta(rd(x, \mathcal{M})).$$

*Proof:* For nonzero rounding results, the claim follows from lemmas 3.8(iii) and 3.15. Otherwise, the claim follows by expanding the definitions of *norm*,  $\eta$ , and *postnrom*.

The IEEE factoring of the rounding result can therefore be computed by first computing the IEEE factoring  $\eta(x)$  of x, then rounding the significand, and finally

post-normalizing the result. This decomposition of the rounding function is well known [Gol96], but has been (paper-and-pencil) proved explicitly for the first time in [MP00]. We extend this work by formally verifying the decomposition theorem.

The following lemma is our first application of the decomposition theorem as a proof utility:

**Lemma 3.17** Let  $x \in \mathbb{R}$  and  $(s, e, f) = \eta(x)$ . It holds:

(s, e, f) is denormal  $\implies \eta_e(rd(x, \mathcal{M})) = e_{\min}.$

*Proof:* Since (s, e, f) is denormal, it holds  $e = e_{\min}, f < 1$ . By lemma 3.13(*iv*) and the definition of post-normalization, it follows  $postnrom_e(\eta(x), \mathcal{M}) = e_{\min}$ . The claim now follows by application of the decomposition theorem 3.16.

#### **3.2.3** Correctness of the Rounding Function

We now demonstrate that the definition of the IEEE rounding function rd conforms with the IEEE standard. The specification of the round to nearest mode in the standard is as follows:

(...) In this mode the representable value nearest to the infinitely precise result [of any floating point operation] shall be delivered; if the two nearest representable values are equally near, the one with its least significant bit [digit] zero shall be delivered. (...)

Since our formal definition of the function rd does not obviously coincide with this informal definition, the following theorem is proved. This theorem hopefully convinces the reader of the conformance of our rounding definition.

**Theorem 3.18** Let  $x, x' \in \mathbb{R}$  and x' be a semi-representable number.

- (i) For any rounding mode  $\mathcal{M}$ ,  $rd(x, \mathcal{M})$  is semi-representable.

- (ii) rd(x, near) is a nearest semi-representable number:  $|x - x'| \ge |x - rd(x, near)|.$

- (iii) If there are two nearest numbers, then the one with least significant digit zero is chosen:  $x' \neq rd(x, near)$  and |x x'| = |x rd(x, near)| implies  $\eta_f(rd(x, near)) \cdot 2^{P-1}$  is even.

*Proof:* Part (*i*) is a trivial consequence of lemma 3.14 and theorem 3.16. Part (*ii*) and (*iii*) rely on the following fact proved by Miner in PVS [Min95]:

$$|x - r_{int}(x, near)| \leq \frac{1}{2}$$

and

$|x - r_{int}(x, near)| = \frac{1}{2} \Longrightarrow r_{int}(x, near)$  is even.

Let  $(s, e, f) = \eta(x)$  and  $(s', e', f') = \eta(x')$ . It is easy to adopt the above fact to the *rd*-function:

$$|x - rd(x, near)| \leq 2^{e-P} \text{ and}$$

$$|x - rd(x, near)| = 2^{e-P} \Longrightarrow \left(rd(x, near) \cdot 2^{-(1+e-P)}\right) \text{ is even.}$$

(3.1)

We now prove part (*ii*). We may assume that  $x' \neq rd(x, near)$ , since otherwise the claim is trivial. From the decomposition theorem and the definition of the postnormalization we know that  $\eta_e(rd(x, near)) \geq e$ . Now assume  $e' \geq e$ . Using lemma 3.11 (where we set  $(s, e, f) = \eta(rd(x, near))$ ,  $(s', e', f') = \eta(x')$ , and i = e) results in

$$|rd(x, near) - x'| \ge 2^{e-(P-1)} = 2 \cdot 2^{e-P}.$$

(3.2)

Using the triangle inequality, (3.1) and (3.2) together yield

$$|x - x'| \ge 2^{e - P}. {(3.3)}$$

Equations (3.1) and (3.3) yield part (*ii*). Assume otherwise that e' < e. Since  $e_{\min} \le e'$  we have  $e_{\min} < e$ , and therefore  $f \ge 1$ , since (s, e, f) and (s', e', f') are IEEE factorings. Hence  $|x| \ge 2^e$ . Lemma 3.10(*ii*) with i = e gives  $|x'| \le 2^e - 2^{e-P}$ . Together this implies

$$|x' - x| \ge 2^{e-P}. {(3.4)}$$

Again, (3.1) and (3.4) yield part (*ii*). The proof of part (*iii*) is similar.  $\Box$

Similar informal specifications exist in the standard for the three remaining rounding modes, and conformance theorems for these have been proved in PVS.

The following theorem states that the semi-representable numbers are exactly the fixpoints of the rounding function:

**Theorem 3.19** For any real x and rounding mode  $\mathcal{M}$ , x is semi-representable iff  $rd(x, \mathcal{M}) = x$ .

*Proof:* If  $rd(x, \mathcal{M}) = x$ , x is semi-representable by theorem 3.18(*i*). Conversely, if x is semi-representable and  $\mathcal{M} = near$ , then the round result must equal x by theorem 3.18(*ii*) with x' = x. The claim for the remaining rounding modes follows analogously from their respective conformance theorems.

#### **3.3** Exceptions and Wrapped Exponents

The IEEE standard defines five exceptions: invalid operation (*INV*), division by zero (*DIVZ*), overflow (*OVF*), underflow (*UNF*), and inexact result (*INX*). In this section, we define the *OVF*, *UNF*, and *INX* exceptions. The *INV* and *DIVZ* exceptions will be defined later.

The standard requires that each occurrence of an exception shall set a status flag and call a trap handler. The trap handler can be disabled on user request. We do not describe the actual handling of the status flags and the trap handling, since this is part of the CPU instead of the FPU. However, since the detection of exceptions as well as the final result of floating point operations depend on whether the trap handlers are enabled or disabled, we need the enable flags for the overflow and underflow exceptions *OVFen* and *UNFen*, respectively. They are provided by the CPU.

#### 3.3.1 Overflow

The standard defines the overflow exception as follows:

The overflow exception shall be signaled whenever the destination format's largest finite number is exceeded in magnitude by what would have been the rounded floating-point result were the exponent range unbounded. (...)

In lemma 3.10 we proved that  $X_{\text{max}} = 2^{e_{\text{max}}} \cdot (2 - 2^{1-P})$  is the format's largest representable value. Since our rounding function by definition rounds as if the exponent range were unbounded above, we can define the *OVF* exception as follows:

$$OVF(x, \mathcal{M}) := (|rd(x, \mathcal{M})| > X_{\max}).$$

Here, x is the exact result of a floating point operation. The OVF exception depends on the rounding mode, since different rounding modes round numbers slightly outside the representable range ( $|x| = X_{max} + \varepsilon$ ) differently to either  $X_{max}$ , or to the next value outside the format's range.

Lemma 3.20 It holds

$$OVF(x, \mathcal{M}) \iff \eta_e(rd(x, \mathcal{M})) > e_{\max}.$$

*Proof:* The  $\Rightarrow$  direction follows from lemma 3.10 and theorem 3.18(*i*), the  $\Leftarrow$  direction from lemma 3.2.

For the implementation of the *OVF* test in the actual hardware, it is beneficial to differentiate between overflows which are apparent before rounding, and overflows which just arise during rounding:

$$OVF_{bef}(x) := \eta_e(x) > e_{max},$$

$$OVF_{aft}(x, \mathcal{M}) := \eta_e(x) = e_{max} \wedge sigrd(\eta(x), \mathcal{M}) = 2$$

In the first case we say the overflow occurs *before rounding*, in the latter case we say *after rounding*.

Lemma 3.21 An overflow occurs, iff it occurs before or after rounding:

$OVF(x, \mathcal{M}) \iff OVF_{bef}(x) \lor OVF_{aft}(x, \mathcal{M})$

*Proof:* By lemma 3.20 we have  $OVF(x, \mathcal{M}) \iff \eta_e(rd(x, \mathcal{M})) > e_{\text{max}}$ . The claim now follows from the decomposition theorem 3.16 and the definition of *postnrom*.

### 3.3.2 Underflow

The standard defines the underflow exception as follows:

Two correlated events contribute to underflow. One is the creation of a tiny nonzero result between  $\pm 2^{e_{\min}}$  (...) The other is extraordinary loss of accuracy (...) When an underflow trap (...) is not enabled (...), underflow shall be signaled when both tininess and loss of accuracy have been detected. When an underflow trap (...) is enabled, underflow shall be signaled when tininess is detected regardless of loss of accuracy. (...)

For each of the contributing events, the standard leaves the choice between two different implementations. We use *tininess before rounding* (instead of after rounding) and *inexact result* as loss of accuracy (instead if denormalization loss). Tininess before rounding occurs

(...) when a nonzero result computed as though both exponent range and the precision were unbounded would lie strictly between  $\pm 2^{e_{\min}}$ .

This is formalized as

$$TINY(x) := (x \neq 0 \land |x| < 2^{e_{\min}}).$$

Here again, x is the exact result of a floating point operation, and therefore is "computed as though both exponent range and the precision were unbounded." An inexact result occurs

(...) when the delivered result differs from what would have been computed were both exponent range and precision unbounded.

We formalize this as

$$LOSS(x, \mathcal{M}) := (rd(x, \mathcal{M}) \neq x).$$

Loss of accuracy only syntactically depends on the rounding mode, since this is a required parameter to the *rd*-function. From theorem 3.19 it easily follows  $LOSS(x, M_1) = LOSS(x, M_2)$  for distinct rounding modes  $M_i$ .

**Lemma 3.22** Let  $x \in \mathbb{R}$  and  $(s, e, f) = \eta(x)$ . It holds

$$LOSS(x, \mathcal{M}) \iff (sigrd((s, e, f), \mathcal{M}) \neq f).$$

*Proof:* By definition of *LOSS* and lemma 3.4 we have

$$LOSS(x, \mathcal{M}) \iff (\eta(rd(x, \mathcal{M}) \neq eta(x))).$$

The claim now follows from the decomposition theorem 3.16 and the definition of *postnrom*.  $\Box$

Having defined tininess and loss of accuracy, we can define the underflow exception:

$$UNF(x, \mathcal{M}, UNFen) := TINY(x) \land (LOSS(x, \mathcal{M}) \lor UNFen)$$

.

As mentioned above, the standard leaves other choices for the definition of *TINY* and *LOSS*. We refer the reader to [Har99, MP00] for lemmas about the relations between the different definitions.

### 3.3.3 Wrapped Exponent

In case of an overflow or underflow with corresponding trap enabled, the standard requests to deliver a biased result to the trap handler:

Trapped overflows (...) shall deliver to the trap handler the result obtained by dividing the infinitely precise result by  $2^A$  and then rounding. The bias adjust A is 192 in the single, 1536 in the double format. (...)

Note that  $A = 3 \cdot 2^{N-2}$  with exponent width N = 8 and N = 11, respectively. Analogously to overflows, trapped underflows shall deliver the result obtained by multiplying the exact result with  $2^A$  and then rounding. This is captured in the following definition. Again, x is the exact result of a floating point operation:

$$wrapped(x, \mathcal{M}, OVFen, UNFen) :=$$

$\begin{cases} x \cdot 2^{-A} & \text{if } OVF(x, \mathcal{M}) \text{ and } OVFen, \\ x \cdot 2^{A} & \text{if } UNF(x, \mathcal{M}, UNFen) \text{ and } UNFen, \\ x & \text{otherwise.} \end{cases}$

Now we are ready to define the floating point result of operations with exact result *x*:

$result(x, \mathcal{M}, OVFen, UNFen) := rd(wrapped(x, \mathcal{M}, OVFen, UNFen), \mathcal{M})$

For the sake of conciseness, we sometimes omit the *OVFen* and *UNFen* parameters in applications of the *wrapped* and *result* function.

The idea behind exponent wrapping is that multiplying the result with  $2^{\pm A}$  before rounding scales the result into the representable range. The FPU returns the wrapped and rounded result to the trap handler, which can use the result in subsequent operations.

If an overflow is detected with disabled trap, the *result* definition above returns a result exceeding  $X_{\text{max}}$ . The standard however requests a final result of either  $\pm X_{\text{max}}$  or  $\pm \infty$ , depending on the sign and the rounding mode. This will be specified as a case-split in section 3.7.1.

### 3.3.4 Inexact

The standard defines the inexact exception as follows:

If the rounded result of an operation is not exact or if it overflows without an overflow trap, then the inexact exception shall be signaled.  $(\ldots)$

It is not clear if the "rounded result" is meant to be  $rd(x, \mathcal{M})$  without being wrapped, or  $result(x, \mathcal{M})$ , which potentially has been wrapped. In Harrison's formalization of the IEEE standard [Har99] exponent wrapping is not considered, and thus the inexact exception is defined as

$INX(x, \mathcal{M}, OVFen) := LOSS(x, \mathcal{M}) \lor (OVF(x, \mathcal{M}) \land \overline{OVFen}).$

In contrast, a test<sup>3</sup> on Intel's Pentium II with the operation  $x := X_{\min}/2$  with enabled underflow trap and  $\mathcal{M} = up$  did not yield an *INX* signal (where  $X_{\min}$  is the smallest representable value). If x is not being wrapped before rounding, then rounding up x yields  $X_{\min}$ . Hence, if the *INX* signal was computed as  $rd(x, \mathcal{M}) \neq x$ , the rounded result would differ from x and so the *INX* signal should be set. Otherwise,  $x \cdot 2^A$  is a representable number, and hence rounding does not change  $x \cdot 2^A$ . Consequently, if the "rounded result" in the IEEE standard is meant to be the wrapped and rounded result, then no *INX* signal should be set.

In contrast to Harrison [Har99], we define the inexact exception as

$$INX(x, \mathcal{M}, OVFen, UNFen) := LOSS(wrapped(x, \mathcal{M}, OVFen, UNFen), \mathcal{M}) \\ \vee (OVF(x, \mathcal{M}) \land \overline{OVFen}).$$

This is the definition also used in IBM's S/390 [IBM00, Pg. 19-22] and in [MP00], e.g. It has the advantage that programs can distinguish exact (except for exponent wrapping) from inexact computations in case of trapped overflows and underflows. For example, the above computation  $x := X_{\min}/2$  can be represented exactly after having been multiplied with  $2^A$ .

We believe that the IEEE standard is ambiguous in this point.

### **3.4** $\alpha$ -Equivalence

We now formalize the concept of  $\alpha$ -equivalence<sup>4</sup> and  $\alpha$ -representatives from [EP97, MP00]. This concept is a very concise way to speak about sticky-bit computations.

Let  $\alpha$  be an integer. Two reals x and y are said to be  $\alpha$ -equivalent ( $x \equiv_{\alpha} y$ ), if x = y or if there exists some  $q \in \mathbb{Z}$  with  $q \cdot 2^{\alpha} < x, y < (q+1) \cdot 2^{\alpha}$ , i.e., if both x

<sup>&</sup>lt;sup>3</sup>The test-program is available at our website:

http://www-wjp.cs.uni-sb.de/~cj/PhD/

<sup>&</sup>lt;sup>4</sup>The term  $\alpha$ -equivalence is not related to the term as used in  $\lambda$ -calculus (see e.g. [Bar90]).

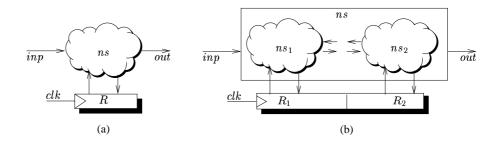

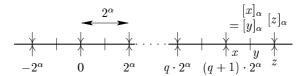

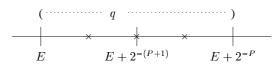

Figure 3.1:  $\alpha$ -equivalence

and y lie in the same open interval between two consecutive integral multiples of  $2^{\alpha}$  (cf. figure 3.1). Clearly, if such a q exists, it must be  $q_{\alpha}(x) := \lfloor x \cdot 2^{-\alpha} \rfloor$ . The  $\alpha$ -representative of x is defined as

$$[x]_{\alpha} := \begin{cases} x & \text{if } x = q_{\alpha}(x) \cdot 2^{\alpha}, \\ \left(q_{\alpha}(x) + \frac{1}{2}\right) \cdot 2^{\alpha} & \text{otherwise.} \end{cases}$$

If x is an integral multiple of  $2^{\alpha}$ , the representative of x is x itself, and the midpoint of the interval between the surrounding multiples of  $2^{\alpha}$  otherwise. The following lemma summarizes some important facts:

**Lemma 3.23** Let x, y be reals, and  $\alpha, k$  be integers.

. .

. .

| (i) $\equiv_{\alpha}$ is an equivalence relation,                                               |                                                    |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------|

| (ii) $x \equiv_{\alpha} [x]_{\alpha}$ ,                                                         |                                                    |

| (iii) $x \equiv_{\alpha} y \iff [x]_{\alpha} = [y]_{\alpha}$ ,                                  | (representative equivalence)                       |

| (iv) $x \equiv_{\alpha} y \iff -x \equiv_{\alpha} -y$ , and $[-x]_{\alpha} = -[x]$              | $_{\alpha}$ , (negative value)                     |

| (v) $x \equiv_{\alpha} y \iff 2^k \cdot x \equiv_{\alpha+k} 2^k \cdot y$ , and $[2^k \cdot x]$  | $_{\alpha+k} = 2^k \cdot [x]_{\alpha},  (scaling)$ |

| (vi) $x \equiv_{\alpha} y \iff x + k \cdot 2^{\alpha} \equiv_{\alpha} y + k \cdot 2^{\alpha}$ , | (translation)                                      |

| (vii) $x \equiv_{\alpha} y \implies x \equiv_{\alpha+k} y \text{ if } k \ge 0$ ,                | (coarsening)                                       |

| $(\textit{viii}) \ x = 0 \iff x \equiv_{\alpha} 0 \iff [x]_{\alpha} = 0,$                       | (zero value)                                       |

*Proof:* Parts (*i*)-(*iv*),(*viii*) are simple consequences of the definition, parts (*v*)-(*vii*) are proved by induction on k.

Lemma 3.23(*iii*) is used in the following to conclude the validity of statements on  $\alpha$ -equivalent numbers x, y from the validity of the same statement on x and its representative  $[x]_{\alpha}$ . For example, we will prove in theorem 3.28 that x and  $[x]_{\alpha}$ round to the same value for appropriate  $\alpha$ . From this, one can conclude using lemma 3.23(*iii*) that  $\alpha$ -equivalent x, y also round to the same number: it holds  $[x]_{\alpha} = [y]_{\alpha}$  and hence  $rd(x, \mathcal{M}) = rd([x]_{\alpha}, \mathcal{M}) = rd([y]_{\alpha}, \mathcal{M}) = rd(y, \mathcal{M})$ . We will not explicitly reference any further usage of this proof idea.

....

.

**Lemma 3.24** Let  $x, y \in \mathbb{R}$ ,  $\alpha, k \in \mathbb{Z}$  such that  $x \equiv_{\alpha} y$  and  $k \geq \alpha$ . It holds

$$x < 2^k \iff y < 2^k$$

*Proof:* The claim is trivial if x = y. We therefore may assume that it exists a  $q \in \mathbb{Z}$  such that

$$q \cdot 2^{\alpha} < x, y < (q+1) \cdot 2^{\alpha}.$$

(3.5)

It cannot hold  $q < 2^{k-\alpha} < q+1$  since this would enclose the integer  $2^{k-\alpha}$  in between the two consecutive integers q and q+1. This implies that either  $q \ge 2^{k-\alpha}$  or  $2^{k-\alpha} \ge q+1$ . First assume  $q \ge 2^{k-\alpha}$ , hence  $q \cdot 2^{\alpha} \ge 2^{k}$ . Equation (3.5) now implies  $x > 2^{k}$  and  $y > 2^{k}$ . Assume otherwise  $2^{k-\alpha} \ge q+1$ , i.e.,  $2^{k} \ge (q+1) \cdot 2^{\alpha}$ . Now (3.5) implies  $2^{k} < x$  and  $2^{k} < y$ .

The following theorem describes equivalence on factorings:

**Lemma 3.25** Let  $x, x' \in \mathbb{R}$  nonzero,  $e := \eta_e(x), e' := \eta_e(x'), \hat{e} := \hat{\eta}_e(x), \hat{e}' := \hat{\eta}_e(x')$ , and  $\alpha$  be an integer. It holds

- (i)  $x \equiv_{\alpha} y \Longrightarrow sign(x) = sign(x'),$

- (ii)  $\alpha \leq \hat{e} \text{ and } x \equiv_{\alpha} x' \Longrightarrow \hat{e} = \hat{e}',$

- (iii)  $\alpha \leq e \text{ and } x \equiv_{\alpha} x' \Longrightarrow e = e',$

- (iv)  $|x| \ge 2^{e_{\min}}$  and  $\alpha \le e \Longrightarrow \hat{e} = \hat{\eta}_e([x]_{\alpha}),$

- (v)  $|x| < 2^{e_{\min}} \text{ and } \alpha \leq e \Longrightarrow \hat{\eta}_e([x]_{\alpha}) < e_{\min}.$

*Proof:* We only prove part (*ii*). Part (*i*) is easy, parts (*iii*)–(*v*) are similar to (*ii*).

With lemma 3.23(*vii*) it suffices to proof the claim for  $\alpha = \hat{e}$ . By part (*i*) and lemma 3.23(*iv*) we may assume  $x, x' \ge 0$ .

Since the claim is trivial for x = x', we further assume that  $q_{\hat{e}}(x) \cdot 2^{\hat{e}} < x, x' < (q_{\hat{e}}(x) + 1) \cdot 2^{\hat{e}}$  by definition of  $\alpha$ -equivalence. From lemma 3.5(*ii*), we know  $1 \le x \cdot 2^{-\hat{e}} < 2$ , and therefore  $q_{\hat{e}}(x) = \lfloor x \cdot 2^{-\hat{e}} \rfloor = 1$ . We then have  $2^{\hat{e}} < x, x' < 2^{\hat{e}+1}$ , and therefore  $\hat{e} = \lfloor \log x \rfloor = \lfloor \log x' \rfloor$ . Lemma 3.7 proves the claim.

We now are ready to prove an important theorem, which allows the easy computation of IEEE factorings corresponding to representatives:

**Theorem 3.26** Let  $x \in \mathbb{R}$ , let  $(s, e, f) := \eta(x)$  be the corresponding IEEE factoring, and let  $p \ge 0$  be an integer. The IEEE factoring of  $[x]_{e-p}$  can be computed by computing the representative  $[f]_{-p}$  of f:

$$\eta([x]_{e-p}) = (s, e, [f]_{-p}).$$

$$f = f_k f_{k-1} \dots f_1 f_0 \cdot f_{-1} f_{-2} \dots f_{-p} f_{-p-1} \dots f_{-l}$$

$$[f]_{-p} = f_k f_{k-1} \dots f_1 f_0 \cdot f_{-1} f_{-2} \dots f_{-p} sticky$$

Figure 3.2: Computing representatives by sticky-computation

*Proof:* From lemma 3.25(*i*) and 3.25(*iii*) we have  $\eta_s([x]_{e-p}) = s$  and  $\eta_e([x]_{e-p}) = e$ . From lemma 3.7 we know  $\eta_f([x]_{e-p}) = |[x]_{e-p}| \cdot 2^{-e}$ . With lemma 3.23(*iv*) and 3.23(*v*), we have  $|[x]_{e-p}| \cdot 2^{-e} = [|x| \cdot 2^{-e}]_{-p}$ . Lemma 3.7 gives  $|x| \cdot 2^{-e} = f$ , and hence  $\eta_f([x]_{e-p}) = [f]_{-p}$ .

Next, we show that the representative of f can be computed by a *sticky-bit* computation. Let  $f \ge 0$  be a real in binary format  $f_k, \ldots, f_0, f_{-1} \ldots, f_{-l} \in \{0, 1\}^{(k+1)+l}$  such that  $f = \sum_{i=-l}^k f_i \cdot 2^i$ . Let p be an integer,  $k \ge -p > -l$ . The (-p)-sticky-bit of f is the logical OR of all bits  $f_{-p-1}, \ldots, f_{-l}$  (cf. figure 3.2):

$$sticky_{-p}(f) := f_{-p-1} \lor \ldots \lor f_{-l}$$

**Theorem 3.27** With the above definitions, the representative  $[f]_{-p}$  of f can be computed by replacing the less significant bits by the sticky bit:

$$[f]_{-p} = \sum_{i=-p}^{k} f_i \cdot 2^i + 2^{-p-1} \cdot sticky_{-p}(f)$$

*Proof:* By definition,  $q_{-p}(f) = \lfloor f \cdot 2^p \rfloor$ , and therefore  $q_{-p}(f) = \sum_{i=-p}^k f_i \cdot 2^{i+p}$ . Furthermore,  $f = q_{-p}(f) \cdot 2^{-p}$ , iff  $sticky_{-p}(f) = 0$ . Applying this in the definition of  $\lfloor \cdot \rfloor_{-p}$  proves the claim.

Theorems 3.26 and 3.27 together allow an easy computation of representatives (respectively their IEEE factorings) by or-ing the less significant bits in an OR tree, and replacing them by the sticky bit. This technique is well known [Gol96], but the formalism with  $\alpha$ -representatives allows for a very concise argumentation about these sticky computations. The verification of the adder circuitry in [BJ01, Ber01], e.g., relies heavily on the concept of  $\alpha$ -equivalence.

# 3.5 Rounding Representatives

The most important property of  $\alpha$ -representatives is that rounding and exceptioncomputation yield the same result on  $\alpha$ -equivalent x, x' for appropriate  $\alpha$ . This will be proved in this section. The proofs in this section are completely different from the proofs in [EP97, MP00]. There, the proofs are by geometrical arguments which are not suitable for formal verification.

**Theorem 3.28** Let  $x \in \mathbb{R}$ ,  $(s, e, f) := \eta(x)$ , and  $\mathcal{M}$  be a rounding mode. It holds

$$rd(x, \mathcal{M}) = rd([x]_{e-P}, \mathcal{M}).$$

*Proof:* It is technically very tedious to prove this theorem in PVS. We only give a sketch of the PVS proof. By theorems 3.16 and 3.26 it suffices to show

$$sigrd((s, e, f), \mathcal{M}) = sigrd((s, e, [f]_{-P}), \mathcal{M})$$

By unfolding the definitions of *sigrd* and  $r_{rat}$ , this is equivalent to

$$r_{\rm int}((-1)^s \cdot f \cdot 2^{P-1}, \mathcal{M}) = r_{\rm int}((-1)^s \cdot [f]_{-P} \cdot 2^{P-1}, \mathcal{M}).$$

(3.6)

Since the claim is trivial if  $[f]_{-P} = f$ , we can assume by the definition of  $\alpha$ -equivalence that  $f \cdot 2^P \notin \mathbb{Z}$ , and  $[f]_{-P} = (q + 0.5) \cdot 2^{-P}$  with  $q := q_{-P}(f) = \lfloor f \cdot 2^P \rfloor$ . Hence  $[f]_{-P} = (\lfloor f \cdot 2^P \rfloor + 0.5) \cdot 2^{-P}$  holds. Substituting this in (3.6) yields

$$r_{\text{int}}((-1)^{s} \cdot f \cdot 2^{P-1}, \mathcal{M}) = r_{\text{int}}((-1)^{s} \cdot \left(\left(\lfloor f \cdot 2^{P} \rfloor + 0.5\right) \cdot 2^{-1}\right), \mathcal{M}) \\ = r_{\text{int}}((-1)^{s} \cdot \left(\frac{1}{4} + \frac{1}{2} \lfloor f \cdot 2^{P} \rfloor\right), \mathcal{M}).$$

(3.7)

The theorem now follows from the next two lemmas. Lemma 3.29 proves that the claim is correct if  $\mathcal{M} \neq near$ . Lemma 3.30 proves that the same cases apply in the definition of  $r_{int}(\cdot, near)$  on both sides of equation (3.7). Then the claim again follows by lemma 3.29.

**Lemma 3.29** For all  $z \in (\mathbb{R}^+ \setminus \mathbb{N})$  and  $s \in \{0, 1\}$ , it holds

$$\lfloor (-1)^s \cdot z \rfloor = \lfloor (-1)^s \cdot \left(\frac{1}{4} + \frac{1}{2} \lfloor 2z \rfloor\right) \rfloor,$$

$$\lceil (-1)^s \cdot z \rceil = \lceil (-1)^s \cdot \left(\frac{1}{4} + \frac{1}{2} \lfloor 2z \rfloor\right) \rceil.$$

**Lemma 3.30** For all  $z \in \mathbb{R}^+$ ,  $2z \notin \mathbb{Z}$  and  $s \in \{0, 1\}$ , set  $z' := (-1)^s \cdot z$ . It holds