# Pure

**Bond University**

**DOCTORAL THESIS**

Generating Effective Test Suites for Reactive Systems using Specification Mining

Bokil, Prasad Ramesh

Award date: 2014

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Generating Effective Test Suites for Reactive Systems using Specification Mining

Presented By

### Prasad Ramesh Bokil

Submitted in total fulfilment of the requirements of the degree of

Masters By Research

Faculty of Business Bond University The Australia January 6, 2014

### Abstract

Failures in reactive embedded systems are often unacceptable. Effective testing of embedded systems to detect such unacceptable failures is a difficult task.

We present an automated black box test suite generation technique for embedded systems. The technique is based on dynamic mining of specifications, in the form of a finite state machine (FSM), from initial runs. The set of test cases thus produced may contain several redundant test cases. Many of the redundant test cases are then eliminated by an aggressive greedy test suite reduction algorithm to yield the final test suite. The tests generated by our technique were evaluated for their effectiveness on five case studies from the embedded domain. The evaluation of the results indicate that a test suite generated by our technique is promising in terms of effectiveness and scales easily. Further, the test suite reduction algorithm may sometimes remove non-redundant test cases too. Therefore, in our experimentation, we have also evaluated the change in the effectiveness of test suites due to this reduction.

In this thesis, we describe the test suite generation and reduction technique in detail and present the results of the case studies. This thesis is submitted to Bond University in fulfilment of the requirements of the degree of Masters by Research. This thesis represents my own original work towards this research degree and contains no material which has been previously submitted for a degree or diploma at this University or any other institution, except where due acknowledgement is made.

> Prasad Ramesh Bokil Faculty of Business Bond University Robina 4229 Australia

### Acknowledgment

I would like to express my gratitude to my supervisors Prof. Padmanabhan Krishnan, Prof. Marcus Randall and Mr. R. Venkatesh for the useful comments, remarks and engagement through the learning process of this master thesis. I would also like to thank my loved ones, who have supported me throughout entire process, both by keeping me harmonious and helping me putting pieces together. I will be grateful forever for your love.

## Table of Contents

| List of Figures |                   |                                                   | 6  |

|-----------------|-------------------|---------------------------------------------------|----|

| Li              | st of '           | Tables                                            | 7  |

| 1               | Intro             | oduction                                          | 8  |

|                 | 1.1               | Analysis for error detection                      | 8  |

|                 | 1.2               | Testing for error detection                       | 11 |

|                 | 1.3               | The problem statement                             | 16 |

| 2               | Literature Review |                                                   | 18 |

|                 | 2.1               | Test generation                                   | 19 |

|                 | 2.2               | Test Suite Reduction                              | 30 |

|                 | 2.3               | Evaluation of test suite effectiveness            | 33 |

| 3               | Preliminaries     |                                                   | 38 |

|                 | 3.1               | Reactive embedded software                        | 38 |

|                 | 3.2               | Test vector, test case and test suite             | 40 |

|                 | 3.3               | Inputs and outputs of an embedded software system | 42 |

|                 | 3.4               | Modified Condition Decision Coverage              | 42 |

|                 | 3.5               | Finite State Machine (FSM)                        | 45 |

| 4  | Test   | Generation Technique 4                      | 47 |

|----|--------|---------------------------------------------|----|

|    | 4.1    | Test Generation Technique - High Level    4 | 47 |

|    | 4.2    | Test Generation Technique - Low level       | 49 |

|    |        | 4.2.1 Inputs to test generation 4           | 49 |

|    |        | 4.2.2 Test Generation Method 5              | 50 |

|    | 4.3    | Demonstration on an example program         | 70 |

|    |        | 4.3.1 Example program 7                     | 70 |

|    |        | 4.3.2 Execution on Example Program          | 72 |

| 5  | Expe   | imental Evaluation 8                        | 80 |

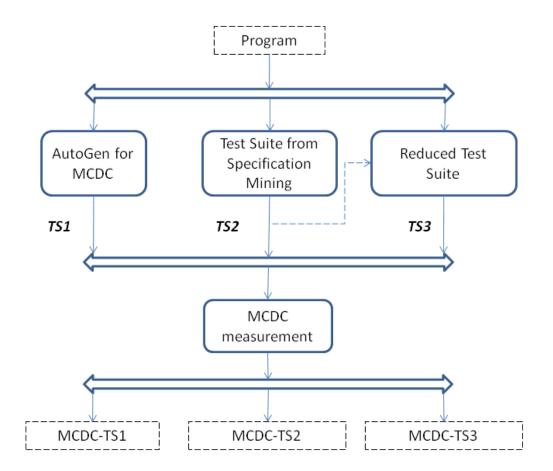

|    | 5.1    | Evaluation of test suite effectiveness    8 | 80 |

|    | 5.2    | Case Studies 8                              | 33 |

|    | 5.3    | Resources used in experimentation           | 35 |

|    | 5.4    | Experimentation                             | 35 |

|    | 5.5    | Observation of the Results 9                | 90 |

|    | 5.6    | Lessons Learnt 9                            | 91 |

|    | 5.7    | Threat to Validity 9                        | 93 |

| 6  | Cone   | usion and Future Work 9                     | 96 |

| Bi | bliogr | phy 9                                       | 99 |

### 5

# List of Figures

| 2.1 | FSM example 1 explaining program state     | 26 |

|-----|--------------------------------------------|----|

| 2.2 | FSM example 2 explaining program state     | 28 |

| 2.3 | Mutation Testing                           | 34 |

| 3.1 | Reactive System                            | 40 |

| 3.2 | An Example FSM                             | 46 |

| 4.1 | Test Generation Technique                  | 48 |

| 4.2 | Program Trace Format                       | 56 |

| 4.3 | FSM of sample program trace                | 57 |

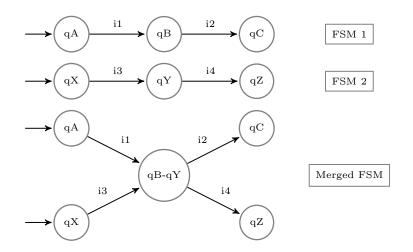

| 4.4 | State merging process                      | 61 |

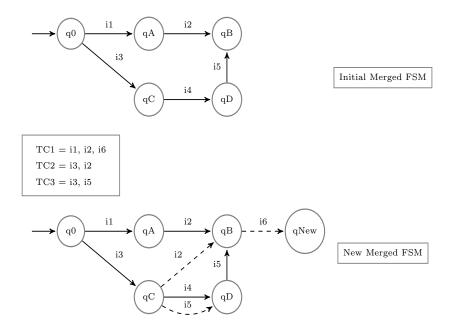

| 4.5 | Test suite reduction                       | 67 |

| 4.6 | Example Program: Trace Format              | 74 |

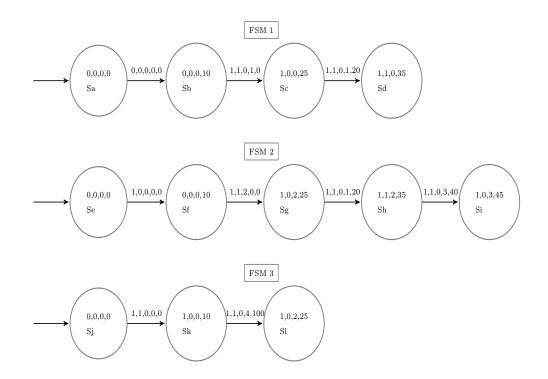

| 4.7 | Example program: Three FSMs of program run | 75 |

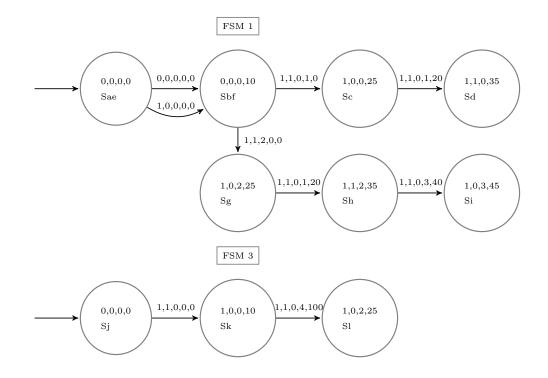

| 4.8 | Example program: Semi-merged FSM           | 76 |

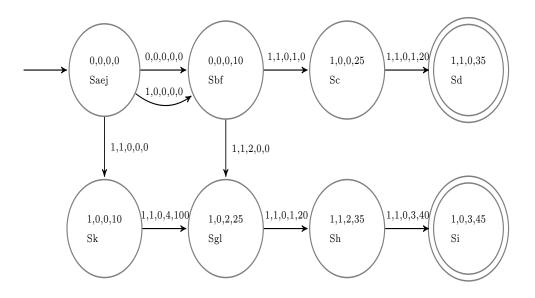

| 4.9 | Example program: Merged FSM specification  | 77 |

| 5.1 | Test Suite Evaluation                      | 82 |

## List of Tables

| 4.1 | Example program: Initial Test Suite | 72 |

|-----|-------------------------------------|----|

| 4.2 | Example program: New Test Suite     | 78 |

| 5.1 | Details of Case Study               | 83 |

| 5.2 | Results of Experimentation          | 89 |

### 1. Introduction

Certain software in embedded systems, like avionic and automotive systems, is *safety-critical*. Examples of such software are flight navigation, autopilot in avionics and braking system and airbags deployment in automotive systems. Failures in these systems risk loss of life and property. No *safety-critical* software should have critical errors, else they may manifest into unacceptable failures. Preventable losses have been observed due to software failures [59], [37], [20]. However, preventing or detecting critical errors in embedded systems is a difficult task [14].

Attempts have been made to detect errors in software, both by software analysis and by software testing. We discuss some of these attempts in detail in the following sections.

### **1.1** Analysis for error detection

Errors may get detected at various stages of a software development life cycle - requirement specification, design and implementation. We list the predominant analysis methods and mention their limitations for industrial embedded systems.

Requirement analysis includes the task to detect errors and inconsisten-

cies in the requirements. This prevents percolation of errors into the design phase and beyond. Requirement analysis may include validating the requirements against expected behaviour and detecting ambiguous requirements. There exist tools capable of detecting errors in requirements like QUARCC [9], QUARS [24] and KaOS [83]. However, these tools are not adequate for industrial software [48]. In most projects, requirements are present in nonexecutable informal notations [48]. So requirement analysis is manual, which makes the error detection task time-consuming and error-prone. Also, the requirements keep changing, which adds to the complexity of the analysis [21].

Design analysis involves detecting errors in the design artifacts such as state-charts and UML models. Example of errors include infeasible designs, performance issues deviation from specifications, deadlocks and unreachable states in state-charts. Though advantageous, the basic limitation of design analysis is availability of a low level design that represents the implementation. Many a times, for legacy as well as other software, the designs are absent. Thus design analysis requires an effort to develop designs, which is not always put in [36]. With no designs, design analysis cannot be done. Even when designs are present, there are many cases where the design does not depict the actual implementation [62]. Last minute changes to the software is the primary cause of this, where changes are made to an implementation without updating the design artifiacts due to time constraints. In such cases, it is hard to perform any design analysis.

Program analysis aims at automatic analysis of program behaviour. The two main approaches in program analysis are: static analysis and dynamic analysis. Static analysis techniques inspect the code for errors without execution of the code [23]. They can help uncover a number of errors in the code, like zero division, deadlocks and array index out of bounds. Tools and techniques implementing static analysis include PolySpace [61], ASTREE [13] and TECA [54]. These tools do scale up for large codes, but are imprecise [74]. The tools display a number of warnings which can be potential errors in the code. These warnings need to be manually verified for actual errors, which takes a lot of time and effort and the process is error prone. The problem of manual verification of warnings is compounded with increase in complexity of the software, as the number of warnings is directly proportional to size of code. As a result, static analysis has its limitation for use on industrial embedded software.

Dynamic analysis, on the other hand, relies on program execution to study the code behaviour, often using instrumentation. The effectiveness of such an analysis depends greatly on the sufficiency of test inputs, *i.e.*, it must be ensured that an adequate slice of program's set of possible execution behaviours have been observed. A practicable measure of this comes from software testing techniques such as *code coverage*. Dynamic analysis has the additional ability to find security issues caused by the code's interaction with other system components like SQL databases, application servers or Web services. Among its advantages over static analysis, the following are noteworthy:

- identification of vulnerabilities in a runtime environment.

- ability to analyse applications in which one does not have access to the actual code.

- identification of vulnerabilities that might have been false negatives in the static code analysis.

However, such an analysis is often too complex to work with. For instance,

it's quite difficult to trace a vulnerability back to the exact location in the code. Besides, one cannot guarantee the full coverage of the source code in dynamic analysis, as it is performed based on user interactions or automatic tests. Thus, no analysis at any level is sufficient for industrial embedded software.

### **1.2** Testing for error detection

There exists basic testing methods which are used to detect software errors that could lead to failures [63]. We mention the predominant testing techniques and their limitations for industrial embedded systems.

One of the best testing methods is exhaustive testing, which tests the software for all combination of inputs. This ensures tests which can detect all errors from the system. However, even for trivial programs, exhaustive testing is infeasible since it is time and effort intensive. Also, in most cases, it is not possible to generate an exhaustive test suite, like programs with unbounded loops. Thus other forms of testing are used. Requirement based testing is one of the primary forms of testing, where a test suite is prepared for checking the system based on the requirements of the system. Model based testing [5] is used when a model of the system is available. This model drives generation of test suite. Other types of test suite generation techniques include those that try to achieve metrics such as structural coverage [88] [31] [77], mutation killing [19], and so on.

We argue that none of the above techniques of testing are sufficient for embedded systems [55]. Requirement based tests may not exercise the complete code [53], because of which bugs may remain undiscovered. Model based testing has problems similar to design analysis. The models of software are either absent or do not faithfully represent the implementation. Thus, model based testing may not give useful tests. Test suite generation techniques to achieve structural coverage suffer either from accuracy or scalability issues when run on large systems [57]. It is also noteworthy that coverage may sometimes be unsuitable to generate test suites [43], but this is often domain specific.

With none of these sufficing, there is a need for an effective testing technique for industrial embedded systems. We aim at developing one such technique that will help testing of these systems. For this, we choose to detect errors from program implementations. The rest of this paragraph justifies this choice of ours. Many a times, software programs are the only executable artifacts available with the team. Automated testing using nonexecutable artifacts is difficult. Non-executable artifacts will have to be made executable, which may require time and effort and the process is error-prone. Most requirements and design documents are either non-executable or they do not match with the implementation for reasons mentioned earlier. Software programs, on the other hand, are executable and thus their testing can be easily automated. Also, there are cases where the requirement and design is free from critical errors, but the implementation may contain errors. These errors may be introduced while converting design into implementation. Example of such errors are null pointer dereferencing and array index out of bounds. These errors are usually introduced by a programmer while coding. Thus, to improve the usability of the technique, we focus on error detection from software programs.

Static and dynamic program analysis are often used to automatically detect errors from embedded programs. Error conditions are encoded as properties and the analysis tools try to determine whether these properties

### CHAPTER 1. INTRODUCTION

hold in the system. A different use of these analysis tools is to automatically generate test suites for the program which in turn would detect errors. In practice, these tools are useful on small programs. However, it is well known that for most industrial applications, due to the size and complexity of programs, static analysis tools are imprecise and dynamic analysis tools are un-scalable [57].

Software testing methods are traditionally divided into **white-** and **blackbox** testing. The difference is in the point of view that a tester takes while designing the test cases. White-box testing focuses on testing the internal structures or workings of a program, as opposed to the functionality exposed to the end-user. The tester chooses inputs to exercise paths through the code and determine the appropriate outputs. Black-box testing, in contrast, treats the software as a "black box", examining functionality without any knowledge of internal implementation. The tester is only aware of what the software is supposed to do, not how it does it.

While white-box testing can be applied at different levels of the software testing process, it is usually done at the *unit* level. Though this method of test design can uncover many errors and problems, it might not detect unimplemented parts of the specification or missing requirements. Blackbox testing, on the other hand, can be applied to most levels of software testing: *unit, integration, system* and *acceptance*.

A notable limitation of black box testing comes from the possibility that coincidental aggregation of several errors may produce the correct response for a test case, preventing error detection. This makes it challenging to generate effective test cases. Moreover, the black-box testing method makes it difficult to design test cases (with just functional specifications) and may lead to redundant test cases. However, we prefer black-box testing for this work because of the following advantages of it (Tanja E. Vos, et al.[84] discuss the relevance of such testing approaches in similar settings):

- The test is unbiased because the designer and the tester are independent of each other.

- The tester does not need access to the code; knowledge of any specific programming languages isn't required.

- The test is done from the point of view of the user, not the designer.

- Test cases can be designed as soon as the specifications are complete.

- It averts the need for program analysis which is often costly. As a result, the techniques scale better.

There are existing techniques for error detection of programs using black box analysis. Random testing is a simple black box test generation technique, which may be effective in some cases [38]. We aim to refine random testing using information about the behaviours of the program. We identify the set of input and output variables used by the program and then capture the functional (input-output) behaviour of programs. Hence our approach is predominantly black box that relies on the identification of these variables. Our technique is based on specification mining [89]. We extract partial specification of the system by observing behaviour of the system over a test suite. The specification is in the form of a Finite State Machine (FSM). This specification guides further test generation. The advantages of our technique are that it is precise and scalable in principle and requires no program analysis. On the downside, owing to the use of a black box approach, our technique may generate a larger test suite as compared to white-box techniques. Error detection becomes increasingly difficult with the increasing size of test suites (the response for each test case needs to be computed and tested against an oracle). As a result, we need to reduce the test suite. While reducing the test suite, we need to ensure that the size of the test suite reduces without compromising on the error detection effectiveness of the test suite. There have been several efforts on minimization of test suites [40], [80]. Measures, such as test case similarity [35], have been introduced to identify relevant tests and to understand test suites better. To address the issue of test suite reduction, we also present a straightforward test suite reduction algorithm. This algorithm reduces the size of the test suite in the black box paradigm while trying to maintain test suite effectiveness. As explained by Mary Jean Harrold, et al. [75], automated test suite reduction does help in reducing number of tests, but suffers from loss in error detection of test suite. Our technique exhibits similar characteristics. Thus, there is a trade-off between the number of tests against which error detection from program is to be measured and the loss of effectiveness.

In evaluating the effectiveness of our approach, we use Modified Condition Decision Coverage (MC/DC) [53] as a measure of test suite effectiveness. While coverage directed test generation isn't the most effective, especially for avionics systems [78], the reader must note that we only use coverage as an effectiveness measure and not to guide the test suite generation. For embedded systems, MC/DC is a commonly used coverage criterion, especially for safety critical applications. Importance of MC/DC over other practical coverage criteria has been established by Kalpesh Kapoor, et al. [52]. Standards like DO-178B [2] for avionics and ISO-26262 [3] for automotive, mandate MC/DC for all its systems.

### 1.3 The problem statement

Specification mining by observing system behaviour isn't unexplored, though not for embedded systems. But the key question we wish to answer is the following:

## Can black box techniques be as *effective* as white box techniques?

We look for an answer in the context of industrial systems in the embedded domain and use MC/DC as an effectiveness measure for the technique. To find the answer, we evaluated the effectiveness of the algorithm sketched below on a program P viewed as a black box with just an input-output relation.

- 1. Generate an initial test suite TS.

- 2. Extend TS to  $TS_1$  using specification mining techniques leading to a sink-free FSM.

- 3. Reduce  $TS_1$  to  $TS_2$  by eliminating test cases that are not necessary for state coverage but that satisfy a *connectedness* criterion (*i.e.*, FSM is a connected graph but not a multigraph).

The main contribution of our work is a black box test suite generation technique for reactive embedded systems, which generates a *satisfactory* test suite. By *satisfactory*, we mean a test suite which is comparable in effectiveness with respect to a white box test suite and is acceptable for practitioners. We show the effectiveness and scalability of the technique via case studies. While improvements to the algorithms need to be investigated, initial results are promising.

In theory, our black box test suite generation technique can be applied to any reactive program. The only prerequisite is that inputs, outputs that form the state and program executable are available. However, for simplicity of experimentation and evaluation, we have our analysis to reactive programs written in C. So for explanation purposes, we demonstrate our technique on a sample C program. Inputs, process and outputs at each stage of the technique are detailed.

Rest of the thesis is organised as follows. Chapter 2 presents the literature review. Chapter 3 introduces terms used in the thesis. Chapter 4 explains our technique of test suite generation using specification mining and test suite reduction technique in the black box domain. Chapter 5 reports the test suite evaluation process, experimentation process and results of experimentation. Chapter 6 concludes with summary and future work.

### 2. Literature Review

Effective testing of embedded software in a black box environment is a difficult task [6]. There is a need for tests that verify the software. However, manually preparing such tests is time consuming and error prone. As discussed later, current testing methods may not be sufficient for effective detection of bugs from these systems. Thus, there is a need for an automatic test generation method. Such a technique may generate effective, but a lot of tests. This highlights the need for test reduction as well.

Our literature review is divided into three parts. The first part presents work related to test generation. We give motivation as to why test generation is important and list the usual types of test generation techniques. Explanation regarding limitations of these test generation techniques with respect to our domain is provided. We discuss specification mining in detail, which is our approach of test generation. The second part gives insight on the test suite minimization techniques and argues about our choice of test suite minimization technique.

The aim of generating tests is to find errors in software. The generated tests must, therefore, be effective on the software. A metric to measure the test suite effectiveness needs to be decided. In the third part of this chapter, we look at several test suite effectiveness measurement techniques and explain the motivation behind choosing code coverage as a measure for the current work.

In the next couple of sections, we focus on black box techniques for generation and minimization of test suites. Evaluation of test suite effectiveness is independent of the technique used for generation of test suite. Hence, we do not restrict ourselves to black box for measuring test suite effectiveness.

### 2.1 Test generation

In this section, we focus on test generation methods on software. Some of the methods are as follows:

Exhaustive test generation [30] is one of the most simplest test generation techniques, which, in the ideal case, guarantees generation of data to detect all possible errors of the software. This is possible for programs with finite number of all possible inputs. However, in practice, it is extremely hard to generate exhaustive test data for the system. Number of inputs to the program, datatype of the inputs, unbounded loops and reactive behaviour of the program make use of exhaustive inputs infeasible. Also, there exists the oracle problem, where there needs to be a check of the output of the program over a test case, with the desired output of the system. Being too effort and time intensive, very few projects have an automated way of checking this. Thus, all checkings are done manually. It is extremely time consuming and error prone to manually check the output of a program with its desired output. Thus, for almost all programs, exhaustive test generation is not useful.

**Requirement based test generation** helps produce test data based on requirements of the program. This type of inputs test the program for

their functionality. Robert M. Poston [70] gives a detailed explanation of an automated test generation depending on requirements of the system and its usefulness. However, requirement based tests may not exercise complete code [53], because of which critical errors in the program may not be discovered. Thus, just requirement based testing is insufficient.

Model based test generation [5] is used when the model of the software is available. This model drives generation of test suite. But, many a times, for legacy as well as other codes, the models are absent. Thus model based testing requires an effort to develop models, which is not always put into [36]. In the absence of models, model based testing cannot be done. Even when models are present, there are many cases where the model does not depict the actual implementation [62]. This is mostly because of last minute changes required in the software, when changes are made directly on implementation without updating the model because of time constraints. In such cases, model based testing may not give useful tests.

At code level, there are various white box test generation techniques, which are summarized by Jon Edvardsson [22]. Program analysis is one of the techniques used to generate a test suite [28]. A test suite generated to improve code coverage [31] [77] is often used in the industry. Test suites are also prepared to detect memory related errors [92], concurrency errors [56] like read-write race and deadlocks. Richard A. DeMillo, et al. [19] explain a technique for test generation for mutations of the program. Performance of most white box test generation techniques on small examples is appreciable, but may be unsatisfactory for large systems as they run into accuracy and scalability issues [57] [7] [8].

There are a few **black box test generation techniques** as well. A. A. Omar, et al.[67] give a survey on the black box test generation techniques.

We provide, below, a brief overview of some of the techniques listed there.

Random test generation is a trivial black box technique to generate a test suite. Dick Hamlet [38] discusses situations where random testing would be sufficient and would be an alternative to systematic testing. However, random testing is mostly unsystematic and there is no guarantee that it would catch the errors [32].

In equivalence partitioning (EP) [67], the input domain of a program is partitioned into a finite number of equivalence classes. Assumption is that, for all classes, a test of a representative value of a class is equivalent to a test of any other value of that class. Boundary value analysis (BVA) is similar to EP, with the constraint that values are picked at the boundaries of the classes. This helps testing at boundaries, where errors may be present. Stuart C. Reid [72] explains how BVA is better than EP and random testing on an avionic code.

However, EP and BVA require (mostly manual) identification of equivalence classes and generating tests within that classes. The determining factor of success of EP and BV is the quality of creation of equivalence classes. With manual effort involved, cost of test generation increases and this process becomes error prone, reducing the effectiveness of error detection.

*Cause effect graphing* [63] is a systematic technique for representing test cases as a combination of inputs. The test cases can point out ambiguities and incompleteness in the specification. Yet, the process can be difficult to apply in practice, because the complexity of applying the technique increases for large number of causes (distinct input or equivalence class of input) [68].

The condition table method [30] is a method in which a condition table is prepared by looking at program specification. Tests are prepared from combination of conditions relevant to the correct operation of the program.

Another such method is *the category partition method* [68], where tests are prepared by systematically decomposing the program specifications. Both these methods depend heavily on availability of the specification, which may not always be available. Also, manual effort is involved making the process costly and error prone.

Except for random testing, the above black box testing methods are not suitable for reactive programs. In reactive programs, inputs may appear at varying intervals and response of the system is determined by the previous state of the program. Thus, sequences of inputs are needed to increase the effectiveness of the test suites, which is not exhibited by any of the above techniques. Also, most black box techniques are specification based or require manual intervention, which limit the applicability of the techniques.

In a paper by Michael D. Ernst, et al.[39], a technique to improve test suite using operational abstractions has been mentioned, where a better test suite is derived from an existing test suite by checking the behaviour of each test case. This technique requires domain knowledge of the system, which may not always be available.

Test generation using specification mining is a relatively newer area related to test generation. We explain in detail the literature review regarding specification mining.

### **Specification Mining**

Recently, there has been research in generating specifications by observing program behaviour, which has been loosely summarized by Andreas Zeller [89]. Techniques have been developed for specification mining on Object Oriented (OO) systems. Andreas Zeller, et al. [16] explain the *ADABU*  technique for capturing object behaviour models from JAVA code. SPY [27] is a technique to recover specification of a software component from the observation of its run-time behaviour. Similarly, Mayur Naik, et al. [64] demonstrate use of static and dynamic analysis for preparing specifications from JAVA programs.

The technique of specification mining has also been applied to test generation. TAUTOKO [15] is a tool to generate specifications from dynamic analysis of programs and then generate test data from the specifications. Michael D. Ernst, et al. [90] explain a combination of static and dynamic analysis has been used for automated test generation and authors claim it to be superior than TAUTOKO. All these approaches of specification mining are strictly for OO systems, while most of embedded systems do not have OO programs, but are rather coded in C language [73].

Similarly, for determining Application Program Interface (API) behaviour, specifications can be mined either from the program source code using static program analysis [17] [76] or from execution traces [79]. However, these techniques cannot be directly applied to embedded systems because of the difference of nature of the programs. To mine API behaviour, a 'set of valid APIs' is considered as a 'program state'. Most specification mining algorithms for API programs are based on this 'state' concept. Clearly, this concept of state (and thus even the algorithms) cannot be used for embedded programs.

There are techniques where knowledge of the program internals or domain is used for specification mining. In a paper by Fides Aarts, et al. [4], regular inference has been used to build a Finite State Machine (FSM) from program behaviour. Antti Kervinen, et al. [47] discuss a technique to generate test models from test cases using domain specific language to prepare the models. Gerard J. Holzmann, et al. [44] discuss a technique and a tool Modex,

to extract specifications from code, where code is annotated with specific statements to help in specification extraction. These techniques require the user to have a certain degree of knowledge about the system and also to make changes to the program/technique. This may not be possible at all times due to the time constraints in the project.

A number of authors suggest ways to prepare formal specification from programs. Patrice Godefroid, et al. [29] explain the automatic preparation of symbolic equations for testing x86 processor instructions. Using an exhaustive test suite, the authors are able to determine the behaviour of Arithmetic and Logic Unit (ALU) type instructions, by considering the instruction as a black box. Claire Le Goues, et al. [58] explain a process to generate specifications from code using code quality as its guide. Although it reduces the false positives in the specifications, it extracts specific patterns in code and not the entire specification. Also, as shown by Mark Gabel, et al. [25], techniques that match a specific pattern of the specification to all possible program component combinations, are NP-complete in its general form.

Thus, our literature review suggests that specification mining technique has not been applied for test generation of embedded reactive programs. In the following section, we look at options for :

- representation of extracted specifications and our choice as FSM,

- representation of *state* of FSM and our choice of output variable values as state, and

- test generation techniques using specification mining and our choice of technique.

#### Choice of representation of extracted specifications

Specification mining techniques use different representations for the specification, like equations, models and FSMs. Patrice Godefroid, et al. [29] represent the extracted specification using equations while Antti Kervinen, et al. [47] use models to denote the extracted specifications. However, a majority of the representation of extracted specification is a FSM [15], [90], [64], [17], [76]. Clearly, FSM is the preferred form of specification representation. The primary reason for choosing FSM is that the representation closely depicts the implementation. Also, FSMs can be executable, which help in automating processes over the FSMs. The FSMs can be expanded or contracted, which depict refinement and abstraction of the specification. Our target programs are reactive programs, which are usually represented as state-charts. Since state-charts are built on top of FSMs, reactive programs can be naturally represented as FSMs. Thus, like majority of the specification mining techniques, we also choose FSMs as our choice of specification representation.

### Choice of state of FSM

The choice of *state* is an important consideration for specifications represented as FSM. Most specification mining techniques are for object oriented type of systems for which, *state* in the specification is the list of all available methods in the class. We explain with example, two *state* capture concepts present in the literature. Illustration is provided by an example from paper by Carlo Ghezzi, et al. [27], as in Listing 2.1.

1. State based on availability of methods

```

public class Stack {

public Stack() { .. }

public void push(String element) { .. }

public void pop() throws Error { .. }

public String top() throws Error { .. }

public boolean isEmpty() { .. }

public int size() { .. }

}

```

Listing 2.1: Example code to explain program state

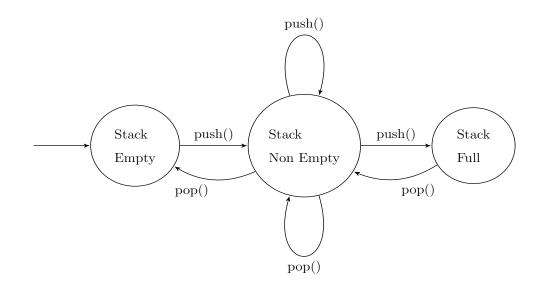

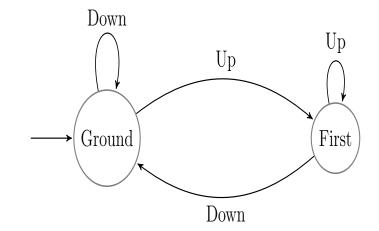

Figure 2.1: FSM example 1 explaining program state

The example code in Listing 2.1 implements a *stack* data structure. It has methods like push and pop. A sample FSM of the stack is represented in Figure 2.1. It shows four states depending on the working of the program. The main point to be noted is that each state represents the set of available methods present in that state. Thus, just assuming push and pop methods,

- the *Initial State* has the initialize method

- the *stack empty* state has just push () method available

- the stack full state has just pop () method available, while

- the *stack non empty* state has both pop() and push () methods available.

This type of *state* concept is predominantly used in object oriented systems. However, inferences from the example suggest that this concept of *state* is not possible for non-object oriented systems.

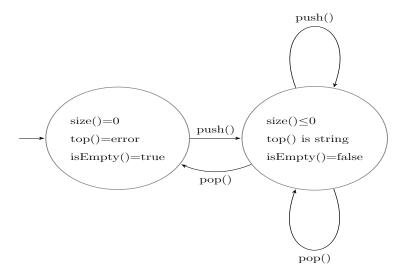

2. State based on values of method return

For the same example code, Listing 2.1, an alternate representation of *state* is as in Figure 2.2. This representation is used by Andreas Zeller, et al. [16]. In this representation, the return values of methods are used to form the state of the program. Again, this representation is not possible for non-object oriented systems, since class and methods do not exist. Thus, this representation cannot be applied directly for our technique. For our technique, we use a modified form of 'state based on values of method return'. We elaborate on our choice of *state* representation.

Figure 2.2: FSM example 2 explaining program state

In 'state based on values of method return' technique for OO systems, the methods are just an interface to retrieve values of members of the class. Thus, the values of members of the class determine the state of the program. These members are chosen to represent the state since the aggregation of values of members depict the information required to form the program state. Also, values of members are persistent, which means that they retain values over multiple method executions over the class.

For our imperative programs, we can use a similar concept of state. All variables in the program of imperative system are similar to members of the class of OO systems. Before execution of the program and class, variables and members will all be initialized to their default state respectively. During execution of the program, variables can indicate the current state of the program, similar to members of the class. With this correlation, we can modify the technique of 'state based on values of method return' with values of variables as state for our technique.

The state of the program will be represented by variables which help to maintain the persistence of the program. For imperative systems like C, these can be the global and static variables of the program. Static variables can be converted to global using temporary variables. However, if global variables in the program never change their values (act like constants), then they may not represent the program state. These would be similar to members of a class whose values never change and thus do not contribute to state representation. As a result, we consider a subset of global variables, which are variables whose values change during execution of the program. As explained in 3.3, we call this subset of global variables as output variables of the program. Along with output variables, return value of program iteration is required to represent the state. This is the value returned by each iteration of the reactive loop in the program. This is explained in detail in 3.1 and 3.3. For simplicity, we call the return value of each iteration as a output variable as well. Thus, we use a representation in which the FSM state is represented by values of output variables of the system.

### Choice of test generation technique

Studies suggest that, till now, TAUTOKO [15] is the most successful black box technique for test generation which uses specification mining techniques. Thus, we develop our technique in a similar way.

We discuss about TAUTOKO in detail. TAUTOKO [15] is a tool for OO programs to generate specifications from dynamic analysis of programs. The specifications are in the form of an automata and are used to generate test data to detect exceptions in the program. In this technique, the list of all available methods is considered as state of the specification. TAUTOKO prepares a specification from a seed test suite, and enhances the specification by execution of all possible methods from every state of the program, thus generating a complete specification. In this process, it generates an effective test suite which detects exceptions in the object oriented programs. So, for a class in object oriented system, one can test for all sequence of methods in that class. A test case of this test suite consists of a sequential list of methods of the class, along with values.

Since TAUTOKO uses an exhaustive approach, the technique may not scale up for large programs. Also, we cannot borrow the concept of state of TAUTOKO for non object oriented embedded programs. The concept of *program state* is the list of all available methods at a particular execution state in the program. For TAUTOKO, some inputs cannot appear at certain times (like, a *pop* method cannot appear when the program state is *stackEmpty*). But, for reactive embedded systems, all inputs are equally likely to appear at all times. Our technique of test generation is derived from TAUTOKO, but is scalable in principle.

### 2.2 Test Suite Reduction

Developing a quick and efficient test suite reduction technique is hard. The optimal test suite reduction problem is an instance of set-cover problem which is NP-Complete [26].

Ideally, we want to generate a test suite which is minimal in size and is effective to detect all errors in the program. The test suite size should be small to tackle the oracle problem. At the same time, we do not want to loose any test suite effectiveness (*i.e.*, test coverage) due to test suite minimization. As explained by W. Eric Wong, et al. [87], optimally minimizing test suite with respect to a criterion may lead to major reduction with negligible losses in test suite effectiveness. However, these results were contradicted by some studies [42] [51], who claimed that optimally reducing test suite for a criterion does decrease their effectiveness. However, on a space application, Eric Wong, et al. [86] demonstrated that significant test suite reduction can be achieved with little or no loss in test suite effectiveness. Thus, it is generally assumed in the research community that test suite minimization does not cause much loss in test suite effectiveness [49].

Work has been done on test suite reduction for regression testing [33], [46]. The test suite reduction for regression testing decreases the time required to re-test the software after changes are made to the software. When certain features of a software are modified, the entire test suite is executed over the software. This is to check if the output of the modified software is same as per the requirement. However, one can execute only a subset of the test suite and not execute those test cases which do not execute any modified part of code. This saves time and effort in executing the tests. Regression testing of high-assurance software is particularly expensive, such as software that is produced for airborne systems. One reason for this expense is the extensive verification required for the software. As quoted by Mary Jean Harrold, et al. [51], one of the company reports that for one of its products of about 20,000 lines of code, the MC/DC-adequate test suite requires seven weeks to run. Test suite reduction for regression can help solve this problem.

However, reduction methods for regression test suite cannot be used for our technique. This is because, these reduction methods reduce the effort of execution of unnecessary tests as opposed to discarding tests having no value. These techniques help choose test cases to temporarily ignore for execution while we want techniques to completely delete the unwanted test case.

Most test suite reduction techniques are performed over some properties. Such properties include code coverage (like [45], [51]) and mutation analysis (like [66]). Test suite reduction for code coverage discards test cases which add no value to code coverage. Similarly, test suite reduction for mutation analysis discards test cases which do not increase mutation kill ratio. However, all these techniques are useful when program code is available. In the black box domain, code coverage based or mutation based test suite reduction algorithms cannot be used, program code is unavailable to perform any such analysis.

For black box, there are few test suite reduction techniques. A random technique is unusable as one can always delete the important test cases [34]. So random test suite reduction is rarely used. Most times, test reduction is based depending on some criteria. The HGS algorithm [41] is a test suite reduction technique, which reduces a test suite based on requirements. The HGS algorithm uses a greedy technique which selects the next test case which matches the most requirements. Mary Jean Harrold, et al. [41] showed that this technique reduces test suites without major loss of test suite effectiveness and the claim was supported [34]. Mats P. E. Heimdahl, et al. [42] explain another greedy technique to reduce test suites using models. This uses model checking techniques to reduce the test suites. Michael D. Ernst, et al. [39] propose a new technique for generating, augmenting, and minimizing test suites called the *operational difference technique*. This technique analyses program properties rather than program code. Jiang Zheng [91] explains a black box technique for selecting test cases for regression, based on documentation.

Of these techniques, we select a slightly customized version of the HGS

algorithm. The reason for selecting HGS algorithm is that it is easy to implement and has been proven to be effective. Most other techniques of test suite reduction require different prerequisites whereas our technique need the specifications, which have been generated by us.

### 2.3 Evaluation of test suite effectiveness

The effectiveness of a test suite is dictated by the number of errors detected by it. In order to get an absolute measure, one may look at the ratio of errors detected by a test suite to the total number of errors in a program. However, this ratio is not easy to arrive at, as the total number of possible errors in a program is rarely known. As a result, test suite effectiveness is measured in relative terms. If a test suite TS1 finds more errors than another test suite TS2, then TS1 is said to be more effective than TS2.

We would like to measure the effectiveness of the test suite generated by our technique. This would be measured on a relative basis with test suite generated using other techniques. For checking effectiveness, we need two versions of the program, one with errors and other with the errors fixed. Executing the test suites on the programs would show their effectiveness. However, coming up with this setup is hard because of the actual availability of such versions of a program. So we decide to use the other established methods to measure test suite effectiveness.

Jeff Offutt, et al. [60] explain a few alternate methods of test suite measurement. As per the paper, mutation testing and code coverage are effective forms of test suite effectiveness measurement. We discuss both methods of test suite effectiveness measurement and conclude on a metric.

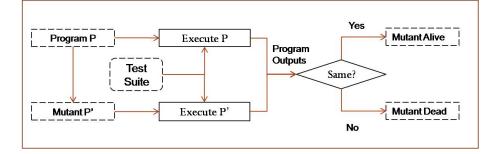

Figure 2.3: Mutation Testing

### **Mutation Testing**

Mutation testing [65] can be used to measure quality of test suite for the given program. The flow diagram in Figure 2.3 attempts to illustrate the technique. In mutation testing, the source code of a program P is mutated (or modified) to create a program P'. The test suite of the program is executed over both versions of the program and their respective output is compared. If any test case in the test suite produces a different outputs for program P and P', the mutant is said to be killed (or detected). This means that the current test suite is good enough to catch a bug in the program where P' is the buggy version of the program. Similarly, mutant programs P1', P2', ... Pn' are automatically created based on some properties. Thus, Mutation Kill Ratio (MKR) is computed for a test suite which is the ratio of number of mutants killed by a test suite to the total number of mutants against which the test suite was run. A test suite TS1 is considered to be more effective than TS2 if MKR of TS1 is greater than that of TS2.

We could have used MKR as a measure in evaluation of test suite effectiveness. With a C program and an input test suite, there are tools available for computing MKR, like Proteum [18] and MILU [50]. However, our experience with the tools indicates that these tools are inadequate when run for industrial software. We tried to execute Proteum on our case studies, but the tool would throw an exception for industry code. Building an automated mutation analysis tool was beyond the scope of the thesis, since it was time and effort intensive. As a result, we could not use mutation testing for effectiveness evaluation of our test suites.

#### Code Coverage

A large number of coverage criteria have been defined for a variety of testing applications. Hong Zhu, et al. [93] illustrate some fundamental notions underlying these while presenting a comprehensive survey of various types of test adequacy criteria. For the sake of completeness, we introduce some of the most basic ones here: (For the ease of illustration of some of these criteria, we implicitly switch between the two equivalent notions - a program and its control-flow graph.)

- Function coverage Has each function in the program been called?

- **Statement coverage** Has each statement in the program been executed?

- Decision coverage Has every edge in the program been executed, *i.e.*, have the requirements of each branch of each control structure been met as well as not met?

- **Condition coverage** (or *predicate* coverage) Has each boolean subexpression evaluated both to true and false? This does not necessarily imply decision coverage.

- **Condition/decision coverage** Have the decision and condition coverage been satisfied?

For safety-critical applications, we often look at a stricter criteria called **modified condition/decision coverage** (MC/DC). This criterion extends condition/decision criteria with the requirements that each condition should affect the decision outcome independently. For example, consider the expression 2.3.1 in a code:

if (a or b) and c then

$$\dots$$

(2.3.1)

The following tests satisfy the condition/decision criteria for the above statement: (a=true, b=true, c=true) and (a=false, b=false, c=false). However, the above tests set will not satisfy modified condition/decision coverage, since in the first test, the value of b and in the second test the value of c would not influence the output. Therefore, the tests needed to satisfy MC/DC are (a=false, b=false, c=true), (a=true, b=false, c=true), (a=false, b=true, c=true) and (a=true, b=true, c=false).

For embedded systems, MC/DC is a commonly used coverage criterion. Importance of MC/DC over other practical coverage criteria has been proven by Kalpesh Kapoor, et al. [52]. Safety critical standards like DO-178B [2] for avionics and ISO-26262 [3] for automotive mandate MC/DC for all its systems. Therefore, we use MC/DC as our code coverage criterion for checking effectiveness of test suites.

Similar to most structural coverage criteria, MC/DC of a test suite is measured as follows:

$$MC/DC = \frac{\left(\begin{array}{c} \text{Total number of conditions which} \\ \text{have showed independent effect} \end{array}\right)}{\left(\begin{array}{c} \text{Total number of conditions} \\ \text{present in the code} \end{array}\right)} * 100 \qquad (2.3.2)$$

We assume that, if test suite TS1 attains more MC/DC than test suite TS2, then TS1 is said to be more effective than TS2. The intuition behind the assumption is that more the MC/DC, more is the coverage of the code of the program.

In the next chapter, we introduce some of the basic terms and notions that will frequently appear in the rest of this thesis. We start with an informal definition of an embedded reactive system and introduce a few commonly used terms in software testing. Later, we get into the details of MCDC, a code coverage criteria that we employ to test the effectiveness of our technique, and briefly explain finite state machines.

# 3. Preliminaries

This section introduces some terms and notions which are used in this thesis.

# 3.1 Reactive embedded software

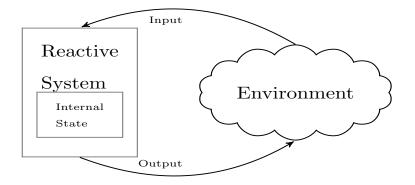

Most software in embedded systems is reactive in nature. The software accepts a set of inputs, processes them and produces a set of outputs before processing the next set of inputs. Figure 3.1 shows the interaction between a reactive system and its environment. The environment can be any entity which provides continuous inputs to the system. A practical approach to model-based testing of reactive embedded systems is to allow modeling of the environment to enable test automation [6]. Examples of environment are humans, sensor values and other similar systems. The environment provides input to the reactive system. The reactive system processes these inputs and generates outputs, which are sent back to the environment. The system will mostly maintain an internal state. This internal state will facilitate the system to decide on the output values. This state may note the number of times a particular input has occurred, last instance of an input, last instance of an output and the internal timer values. Once the outputs are presented to the environment, the reactive system will read the next set of inputs and

the process continues.

A typical example of a reactive embedded software is a wiper control of a car. The system is supplied with inputs to operate the wiper. This input can be provided either by a human (by adjusting wiper setting), sensor values (rain sensor) or the car itself (if ignition is on). An example input can be to operate the wiper at medium speed. The wiper control system processes the inputs and performs calculations depending on its internal state. For example, the input state may be that the wipers are off. In this case, it needs to start the wiper operation and increase its speed. It may also happen that the wiper is already running at high speed, where in the wiper speed needs to be reduced. Thus, the wiper control module computes the wiper operation and produces an output. As soon as the output is produced, the wiper control system waits for the next set of inputs to work on.

There are two assumptions about reactive systems. Firstly, it is assumed that a reactive system operates instantaneously, that is without any time delay. In practice, any reactive system takes a non-zero time for its operation, which is acceptable in practice. Secondly, it is assumed that reactive systems will run for a relatively long time, depending on its deployment. For example, it is expected that the automatic door operation system of a car is in operation for entire lifetime of the car. This makes it important to test reactive systems for long sequences of input, so that some defects can be detected. A peculiar feature of reactive embedded systems is that any of the available inputs can occur at anytime. As an example, wiper on or off, speed of the wiper, rain sensor and other sensors are inputs that can occur at anytime while the system is functioning. This is in contrast to other systems like banking software, where a series of different inputs in a well defined sequence is needed for proper functioning of the software.

Figure 3.1: Reactive System

Another feature of most embedded systems is that the inputs are predominantly boolean or enumeration types. For example, whether the wiper is on or off, wiper speeds and so on are all types of such inputs. The above information regarding embedded systems can be used for test generation of these systems.

A sample outline of a sequential program which depicts a reactive system is shown in Listing 3.1. In the program, the driver function contains a loop which executes forever. This loop is called the reactive loop. Each iteration of this loop is called as an iteration of the reactive loop or program iteration. This loop reads inputs, executes the system and produces outputs, all in a continuous manner.

# **3.2** Test vector, test case and test suite

Almost all software systems need to be tested for error detection. We define terms used during this testing and explain it with the help of the wiper control example.

A test vector for a system is a single assignment of values to inputs of that

CHAPTER 3. PRELIMINARIES

```

driverFunction( ) {

repeat the loop forever {

read inputs from environment for the reactive system

execute the reactive system

report outputs of reactive system to the environment

}

}

```

Listing 3.1: Sequential program depicting a reactive system

system. A single test vector is input at each iteration of reactive loop of the program. A *test case* (or *test data*) for a system is a sequence of one or more test vectors. The sequence of test vectors in a test case should be constant. The output of a test case may change if the order of test vector execution is altered. Ideally, a test case should contain expected values of the system for each test vector. Our test cases need not have expected values since we ignore all expected values for the purpose of test generation. A *test suite* is a set of test cases. The order of test cases in the test suite can be altered without changing the output of the system.

For the wiper control system of the car, assume that we would like to test if the wiper works for medium wiper speed for 10 seconds followed by high wiper speed for 5 seconds. Thus, a *test vector* would be the value of medium speed of the wiper (say tv1). Another *test vector* would be the value of high speed of the wiper (say tv2). These test vectors would be input at different iterations of the system. A *test case* would contain the test vector tv1 to be executed for 10 seconds followed by test vector tv2 for 5 seconds. Note that changing the ordering of test vectors may change the output of the system for the test case. Many such individual test cases form the *test suite* for the wiper software.

# 3.3 Inputs and outputs of an embedded software system

Inputs to an embedded software system are values which are provided by the environment to the reactive program. At a program level, we define input variables as variables which are read in the program. Similarly, outputs are values generated by the reactive system for the environment. We define output variables of a program as global variables to which values are assigned in the program and the return value of program iteration. We assume the set of input and output variables to be disjoint.

### **3.4** Modified Condition Decision Coverage

Modified Condition Decision Coverage (MC/DC) is one of the most widely used code coverage criterion for embedded systems. MC/DC shows an independent effect of each of its conditions on the decision. To show an independent effect of a condition (called condition under consideration or CUC) on a decision, two sets of test values are needed. In both sets, the values of all conditions, except CUC, are masked so that they do not play any role in the decision making process. Thus, toggling the value of the condition under consideration, the decision should toggle and this becomes a test case which satisfies MC/DC for that condition.

Consider that a particular decision in the code is *cond1 AND (cond2 OR cond3)*. Such code types are common in embedded systems. A usual error in such systems is the logical operator error (AND replaced by OR and vice versa).

For the above case, let us consider cond2 to be CUC. The two test cases

for MC/DC of cond2 are (cond1=T, cond2=T and cond3=F) and (cond1=T, cond2=F and cond3=F). The two test cases toggle the value of just CUC and the decision toggles. Now assume that first AND operator in the decision should have been an OR operator as per the specification. In this case, the output of the decision in one of the test cases would be computed differently than in the specification. This would help uncover the logical operator error.

There are three types of MC/DC: Unique-Cause MC/DC, Unique-Cause + Masking MC/DC, and Masking MC/DC [11]. We explain in brief the three types of MC/DC and explain our choice of Masking MC/DC in the experiments.

Unique-Cause MC/DC requires a unique cause for all possible (uncoupled) conditions. Unique cause means that toggling a single condition should change the expression result, with all other conditions constant. In the case of strongly coupled conditions, no coverage set is possible. For example, consider the following expression.

if (a or b) and (a or c) then

$$\dots$$

$(3.4.1)$

For the above expression, conditions a are strongly coupled in the expression. Unique-cause MC/DC cannot be achieved for this expression, since changing the value of one condition changes the other condition too. For such cases, no guidance is provided by DO-178B standards on how to cover these conditions. Fortunately, expressions with strongly coupled conditions are quite rare in airborne software (one study puts it at 72 conditions of 20,256 expressions).

Unique-Cause + Masking MC/DC requires a unique cause for all possible (uncoupled) conditions. For strongly coupled conditions, masking will be allowed for that condition only (i.e., all other (uncoupled) conditions will remain fixed). For expression 3.4.1, unique-cause + masking MC/DC is allowed to have values for tuple (a,b,c) as (0,0,1)and (1,0,1) to show independent effect of first instance of the condition a.

3. Masking MC/DC, as its name implies, allows masking in all cases. This is an extension beyond 2 that masking be allowed for strongly coupled conditions only. For expression 3.4.1, masking MC/DC can have values for tuple (a,b,c) as (0,0,1) and (1,0,0) to show independent effect of first instance of the condition a.

Out of the above three types of MC/DC, masking MC/DC is the preferred choice of MC/DC to satisfy maximum MC/DC of a system. There are multiple reasons for choosing masking MC/DC [11]:

- 1. Masking MC/DC requires a number of tests equivalent or lesser than that of the other forms of MC/DC,

- 2. The performance of masking MC/DC is nearly identical from the probability of error detection viewpoint,

- 3. More independence pairs at all levels can be prepared for masking MC/DC than for either of the unique-cause forms. It is assumed that the larger the number of independence pairs, the easier the coverage would be to attain.

MC/DC is the only practically useful code coverage criteria, which guarantees that detection of logical errors. Other code coverage criteria either give no guarantees (like decision coverage) or require too many test cases (like multiple condition coverage). As a result, we use masking MC/DC in the evaluation of test suite effectiveness.

# 3.5 Finite State Machine (FSM)

A finite state machine is a mathematical model of computation consisting of a set of states, a start state, an input alphabet and a transition function to go from one state to another depending on the input symbol. It can be conceived as an abstract machine that can be in one of a finite number of states. At any given time, the machine can be in only one of its states (the current state).

The behaviour of state machines can be observed in a number of systems performing a predetermined sequence of actions depending on a sequence of events with which they are presented. Some common examples include vending machines which dispense products when the proper combination of coins are deposited, elevators, spell-checkers, traffic lights switching between red, yellow and green, and combination locks which require the input of combination numbers in the proper order.

Finite-state machines have been used to model a large number of problems, among which are electronic design automation, communication protocol design, language parsing and other engineering applications. In biology and artificial intelligence research, state machines or hierarchies of state machines have been used to describe neurological systems and in linguistics to describe the grammars of natural languages.

The example in Figure 3.2 encodes as an FSM, the design of an overly simplified elevator controller (figure and explanation referred from 'FSM tutorial' [82]). The elevator can be at one of the two floors (states): Ground or First.

Figure 3.2: An Example FSM

This is controlled through a switch which can take two values (inputs): Up and Down. The circles represent the states and the arrows represent transitions between them. The arrow labels indicate the input value corresponding to the transition. For instance, when the elevator is in the Ground state and the input value is Up, the state of the elevator changes to First.

We will now start looking at the test generation technique, in the chapter to come. To start with, we will spend some time to get a high level overview of the procedure. As a next step, we would zoom in to illustrate all the important steps of the process. The implementation details and the pseudocode of each of them would also form a part of this illustration. We would be ending the chapter with a demonstration of our technique on a sample program.

# 4. Test Generation Technique

This chapter describes our test generation technique. We split this chapter into four sections. Initially, we give a high level explanation of our technique. Next, we provide a detailed explanation of the test generation process. This includes inputs to our technique and the algorithms underlying test suite generation and test suite reduction. The third section contains the implementation level details of the technique. The final section demonstrates our test generation technique on an example program. We explain each part of the technique, with their inputs and outputs, when the example program is input to test generation.

# 4.1 Test Generation Technique - High Level

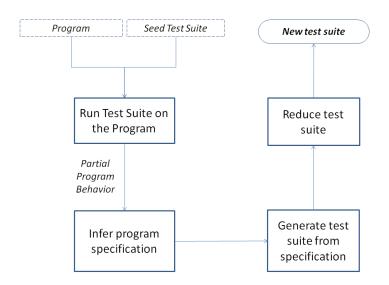

A high level test generation technique is as explained in Figure 4.1.

Our aim is to generate a test suite from the program. This is done by exploiting the dynamic behaviour of the program. The test generation comprises of the following steps.

- 1. Inputting a reactive program and an initial test suite.

- 2. Running the test suite on the reactive program

Figure 4.1: Test Generation Technique

The initial test suite, obtained as an input, is executed over the input program to produce execution sequences.

3. Inferring program specifications

Execution sequences are converted to a specification, depicting the behaviour of the program for the initial test suite.

4. Generating test suite from specification

Properties of specification are used to generate additional tests, which would explore new behaviours of the program.

5. Reducing the generated test suite

Test cases not contributing to test suite effectiveness are removed.

Outputting the test suite thus generated

It is the initial test suite with the additional tests appended to it.

The next section details this process of test generation.

## 4.2 Test Generation Technique - Low level

Before explaining the test suite generation process, we explain the inputs to the test generation process.

### 4.2.1 Inputs to test generation

The inputs to test generation process are: a reactive program, the input and output variables of the program, an initial test suite and a timeout value. The characteristics of these are explained below.

#### **Reactive program**

Our technique of test generation through specification mining is directed toward reactive embedded systems. Programs showing the characteristics of reactive embedded systems (see Section 3.1) are selected. Thus, we assume our programs accept a set of inputs, process them and produce a set of outputs before processing the next set of inputs.

#### Input and output variables

Inputs and outputs of embedded programs are explained in Section 3.3. For our technique of test generation, we assume that input and output variables of the program have been provided. In Section 5.4, we show how these variables can be extracted automatically from the program.

#### Initial test suite

As explained in Section 3.2, a test suite consists of test cases. We call a test suite an initial test suite if the test suite is already available to us. We require this initial test suite for our test generation.

We assume the availability of such an initial test suite (TS), to guide the specification mining process. In case such a test suite is not available, Section 5.4 explains possible steps to prepare an initial test suite.

#### Timeout value

For some programs, our technique of test generation may take time that is not acceptable in practice. This is true for reactive programs, which are designed to run for long durations and thus will have long tests. Preparing such tests may take time. For these programs, we need some external control to stop the test suite generation process if it exceeds a pre-specified time limit. If such an external control is not available, the test suite generation process may take a very long time before stopping. Hence, we accept a timeout value for our test generation technique. When the time taken by the test generation algorithm exceeds the timeout value, the test suite generation process is halted. The value of timeout can be configured to be within the time constraints. This enables us to experiment with large systems with predecided time bounds on the test generation process.

### 4.2.2 Test Generation Method

For each stage of test generation and reduction, we classify the stage into three components. The first component informally explains the process of that stage. The next component gives input and output formats of each stage. The final component gives implementation level details of that stage with algorithms and data structures used in implementation.

We have implemented our test generation technique in the *PERL* pro-

gramming language. The main function of the *PERL* script has steps as in Algorithm 1. Throughout this thesis, we refer to this algorithm as the *main algorithm*.

Inputs to the algorithm are: a C file (F), name of the selected function under test (funcName), the list of input variables  $(I_{list})$ , the list of output variables  $(O_{list})$ , the initial test suite (TS) and the timeout value  $(TM_{val})$ . For simplicity of explanation, the algorithm shown here accepts only a single C file. This, however, is not a limitation of the procedure. The algorithm can trivially be modified to accept multiple files as input. The algorithm first prepares a wrapper function to test the selected function. Next, an executable file is prepared to execute the test suite over the selected function. A loop executes the set of statements of recording program behaviours (recProgBehaviour), preparing FSMs from program traces (prepareFSMsfromTraces), merging the FSMs to generate a single specification FSM (mergeFSMs) and generating test data from the specification FSM (genTestDataFromSpec). The loop terminates when no new test data can be generated from the specification with our technique (errorFlag) or when timeout has occurred  $(lTimeVar >= TM_{val})$ . Once the loop has executed, we have TS with initial and new test cases. The test suite (TS) is optimized using a reduction criteria (reduceTestSuite) to generate a reduced test suite  $TS_{reduced}$ . The algorithm outputs the test suite  $TS_{reduced}$ .

In practice, prepareFSMsfromTraces and mergeFSMs are part of a single stage. For simplicity, they are explained as separate stages.

Each of these are explained below in detail.

#### 1. Prepare program environment

Preparing a program environment includes preparing a driver function and using the driver function to prepare a program executable.

```

Algorithm 1 PseudoPERL script for test generation

Input: F, I<sub>list</sub>, O<sub>list</sub>, TS, TM<sub>val</sub>

driverFunc = prepareProgramDriver (F, funcName, I_{list}, O_{list})

execFile = prepareExecutable (driverFunc, F)

testGenFlag, lTimeVar, FSMspec = (TRUE, START, ())

TS_{new} = TS

while testGenFlag = TRUE do

traceFiles = recProgBehaviour ( execFile, TS_{new} )

FSMs = prepareFSMs from Traces (traceFiles)

FSMspec = mergeFSMs (FSMs, FSMspec)

newTestData, errorFlag = genTestDataFromSpec (FSMspec)

if errorFlag = FALSE then

TS = appendNewTestData(TS, newTestData)

TS_{new} = newTestData

if lTimeVar >= TM_{val} then

testGenFlag = FALSE

end if

else

testGenFlag = FALSE

end if

end while

TS_{reduced} = reduceTestSuite (TS)

Output: TS<sub>reduced</sub>

```

Initially, we prepare a driver for the program. This driver simulates an environment to the actual program function. The driver is similar to the program shown in Listing 3.1. Driver contains a reactive loop where input values are accepted, the program function is called and the output is displayed. The driver can be generated with the availability of input and output variables.

Once the driver function is generated, we prepare an executable file with the program and driver function.

#### Implementation detail

To generate the driver for the program, we need

- input and output variables with their datatypes, and

- signature of the program function.

With this information, the driver can be prepared as shown in Figure 4.1. Function *prepareProgramDriver* from *main algorithm* produces this driver function. The driver function is written to a separate file. The driver in the figure is for programs in pseudo C language. A similar driver can be prepared for most such languages.

In the initial part of the driver, file pointers and temporary variables are declared. This declaration is with respect to the datatypes. Next, a *driverFunction* is written which simulates the actual reactive environment. The *driverFunction* opens the input test file for reading and executes the reactive loop till all tests in a test file are read. It also calls functions which read inputs and print outputs in a desirable format.

Once the driver is generated, an executable file is prepared. We use the GCC compiler to generate the executable file. The function prepare-

*Executable* calls the GCC compiler with the C files and driver function as input and outputs an executable file.

#### 2. Run initial test suite on the program

The initial test suite TS is executed on the program to produce a set of program runs.

The driver in step 1 is prepared such that each test case is input to the program. The function is executed for that test case. Result, namely the values of output variables, are printed to a file. This process of reading test vector, executing the function and capturing outputs is sequentially performed for each test vector in the test case. This process is repeated for each test case in the test suite.

Each test case produces a program trace or a program run, which contains information regarding the program's run for a set of inputs, executed in sequence. We prepare this trace as shown in Figure 4.2

The program run has information of the values of input variables and program states in the sequence of execution. First, the initial values of output variables are recorded. This is followed by the values of input variables. Next, the values of output variables after execution of inputs on the function are noted. This pair of related input-output values is recorded for all test vectors in a test case. Execution of all test cases in the test suite result in a set of such program runs.

#### Implementation detail