| Cronfa - Swansea University Open Access Repository                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This is an author produced version of a paper published in:  IEEE Journal of the Electron Devices Society                                                                                                                                                       |

| Cronfa URL for this paper: http://cronfa.swan.ac.uk/Record/cronfa49903                                                                                                                                                                                          |

| Paper: Russell, S., Perez-Tomas, A., McConville, C., Fisher, C., Hamilton, D., Mawby, P. & Jennings, M. (2017). Heteroepitaxial Beta-Ga2O3 on 4H-SiC for an FET With Reduced Self Heating. <i>IEEE Journal of the Electron Devices Society, 5</i> (4), 256-261. |

| http://dx.doi.org/10.1109/JEDS.2017.2706321                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                 |

This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence. Copies of full text items may be used or reproduced in any format or medium, without prior permission for personal research or study, educational or non-commercial purposes only. The copyright for any work remains with the original author unless otherwise specified. The full-text must not be sold in any format or medium without the formal permission of the copyright holder.

Permission for multiple reproductions should be obtained from the original author.

Authors are personally responsible for adhering to copyright and publisher restrictions when uploading content to the repository.

http://www.swansea.ac.uk/library/researchsupport/ris-support/

Received 8 December 2016; revised 14 February 2017, 22 March 2017, and 1 May 2017; accepted 16 May 2017. Date of publication 19 May 2017; date of current version 21 June 2017. The review of this paper was arranged by Editor S. Ikeda.

Digital Object Identifier 10.1109/JEDS.2017.2706321

# Heteroepitaxial Beta-Ga<sub>2</sub>O<sub>3</sub> on 4H-SiC for an FET With Reduced Self Heating

# STEPHEN A. O. RUSSELL<sup>1</sup>, AMADOR PÉREZ-TOMÁS<sup>2</sup>, CHRISTOPHER F. McCONVILLE<sup>3</sup>, CRAIG A. FISHER<sup>1</sup>, DEAN P. HAMILTON<sup>1</sup>, PHILIP A. MAWBY<sup>1</sup> (Senior Member, IEEE), AND MICHAEL R. JENNINGS<sup>1</sup> (Member, IEEE)

1 School of Engineering, University of Warwick, Coventry CV4 7AL, U.K.

2 Catalan Institute of Nanoscience and Nanotechnology, CSIC and the Barcelona Institute of Science and Technology, 08193 Barcelona, Spain 3 College of Science, Engineering and Health, RMIT University, Melbourne, VIC 3001, Australia

CORRESPONDING AUTHOR: S. A. O. RUSSELL (e-mail: s.russell@warwick.ac.uk)

This work was supported by the Advanced Propulsion Centre and the 'Preparing for the Grand Challenge' Scheme under Project PGC007.

**ABSTRACT** A method to improve thermal management of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs is demonstrated here via simulation of epitaxial growth on a 4H-SiC substrate. Using a recently published device as a model, the reduction achieved in self-heating allows the device to be driven at higher gate voltages and increases the overall performance. For the same operating parameters an 18% increase in peak drain current and 15% reduction in lattice temperature are observed. Device dimensions may be substantially reduced without detriment to performance and normally off operation may be achieved.

**INDEX TERMS** FET, gallium oxide, molecular beam epitaxy, normally-off, self-heating, silicon carbide, threshold voltage.

# I. INTRODUCTION

Wide band-gap semiconductor materials commonly thought of for use in power electronic devices include silicon carbide (SiC) [1], [2], gallium nitride (GaN) [3] and diamond. SiC has shown the greatest potential to date in replacing silicon for DC power applications, indeed 4H-SiC diodes and MOSFETs are today commercially available. Diamond has been touted as the ideal material for high power electronics due to its large thermal conductivity, high breakdown field and high bulk carrier mobility. It has the potential to compete with both SiC for high voltage DC applications and GaN for RF power applications [4]–[6]. However despite recent advances, doping and substrate cost remains an issue [7], [8].

In contrast, beta-Gallium Oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) could offer an alternative to 4H-SiC for power applications. Its key intrinsic material properties are competitive with diamond, e.g., a band-gap of 4.8 eV and high breakdown field 8 MVcm<sup>-1</sup> [9], [10]. Large scale growth is also far less challenging and possible at a fraction of the cost [11].

Despite the material structure being first investigated in the 1960s [12] it is only much more recently this material has

been suggested for application in power electronic devices. Indeed, Ga<sub>2</sub>O<sub>3</sub> thin-films have been successfully employed for a variety of applications including a window layer for solar cells and a transparent conductive oxide [13]–[15]. This holds promise for a larger degree of integration compared with traditional wide band-gap semiconductors, e.g., into display screens or transparent electronics [16].

In recent years basic FET devices have been demonstrated [17]–[20], although p-type doping (which is notoriously difficult in wide band-gap semiconductors) is still a practical challenge. The best oxide solution is yet to be settled upon with work to date mainly focusing on Al<sub>2</sub>O<sub>3</sub>, although in theory SiO<sub>2</sub> provides a greater band off-set and hence reduced gate leakage [21], [22].

In this paper a SILVACO Atlas non-isothermal model for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> demonstrated in a recent paper is employed to recreate a device demonstrated by Higashiwaki *et al.* [18], [23]. The low thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> ( $\sim$ 0.2 Wcm<sup>-1</sup>K<sup>-1</sup>) [10] can be regarded as perhaps the most severe drawback for very high voltage applications. We demonstrate via simulation the advantages

of engineering a thin film of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> onto a good thermal conductor such as SiC ( $\sim$ 5 Wcm<sup>-1</sup>K<sup>-1</sup>) to increase the thermal performance of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.

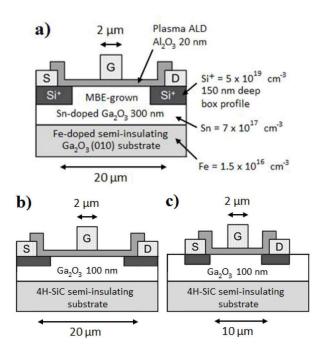

**FIGURE 1.** Schematic showing the structure and doping of a) original MOSFET device based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [18] and b) & c) adaptations made in this paper.

### **II. SIMULATION**

Fig. 1 shows a cross-section of the FET modelled here. The semi-insulating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate material is detailed in the original paper as having a doping of  $1.5 \times 10^{16} \text{ cm}^{-3}$ , while the dopant in the Molecular Beam Epitaxy (MBE) layer is  $7 \times 10^{17} \text{ cm}^{-3}$  with half considered activated. The Si ohmic dopant is 5 x  $10^{19}$  cm<sup>-3</sup> with 3 x  $10^{19}$  cm<sup>-3</sup> activated. A 20 nm Al<sub>2</sub>O<sub>3</sub> Atomic Layer Deposited (ALD) oxide layer covers the device with a source-drain spacing of 20  $\mu$ m and gate length 2  $\mu$ m. This device (Fig. 1a) suffers from self-heating effects due to the relatively poor thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> which reduces the saturated drain current value. One way to mitigate this is to use a substrate with a high thermal conductivity such as 4H-SiC. A recent study has shown the positive impact this can have even on Si based devices [24]. The lattice match of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> to 4H-SiC is close at 3.04Å compared to 3.07Å respectively, allowing for low defect density materials to be grown and interfaces to be formed between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and 4H-SiC by growth methods such as MBE used in this instance.

A simple constant thermal conductivity and low-field mobility model was used for this study with main parameters summarised in Table 1.

As many  $\beta$ -Ga2O3 parameters are not fully established yet care is needed to not pick unrealistic values. Electron effective mass is taken to be 0.28 m<sub>o</sub> giving a calculated local conduction band density of states  $N_c = 3.72 \times 10^{18}$  cm<sup>-3</sup>,

**TABLE 1. Simulation parameters.**

| Material | Parameter                                | Value                                                    |

|----------|------------------------------------------|----------------------------------------------------------|

| β-Ga2O3  | Bandgap Energy                           | 4.8 eV                                                   |

|          | Thermal Conductivity                     | 0.13 Wcm <sup>-1</sup> K <sup>-1</sup>                   |

|          | Effective Mass                           | $0.28 \text{ m}_0$                                       |

|          | Local Conduction Band Density of States  | $3.72 \times 10^{18} \text{ cm}^{-3}$                    |

|          | Epitaxial Layer Mobility                 | 118 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>      |

|          | Epitaxial Layer Dopant                   | $7 \times 10^{17} \text{ cm}^{-3}$                       |

|          | Concentration                            | $(3.5 \times 10^{17} \text{ cm}^{-3} \text{ activated})$ |

|          | Substrate Mobility                       | 20 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>       |

|          | Substrate Dopant Concentration           | $1.5 \times 10^{16}  \text{cm}^{-3}$                     |

| 4H-SiC   | Bandgap Energy                           | 3.23 eV                                                  |

|          | Thermal Conductivity                     | 3.7 Wcm <sup>-1</sup> K <sup>-1</sup>                    |

|          | Effective Mass                           | $0.41  \mathrm{m}_{\mathrm{0}}$                          |

|          | Local Conduction Band Density of Stateas | 5 x 10 <sup>18</sup> cm <sup>-3</sup>                    |

|          | Substrate Mobility                       | 460 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>      |

|          | Substrate Dopant Concentration           | $1.5 \times 10^{16}  \text{cm}^{-3}$                     |

$\beta$ -Ga2O3 parameters taken from [12 & 25] whereas standard SILVACO parameters are used in the case of the 4H-SiC substrate

mobility of the channel layer and mobility of the semi-insulating substrate are set to be 118 and 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> respectively [25].

A parameter (LAT.TEMP) was added to the model to account for poor heat flow in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material. The lattice temperature coefficient for the temperature dependence of electron mobility TMUN=2.0 was used as seen in Equation (1).

$$\mu_{n0} = MUN \left(\frac{T_L}{300}\right)^{-TMUN} \tag{1}$$

where  $\mu_{n0}$  represents electron mobility adjusted for lattice temperature, MUN the originally input mobility value,  $T_L$  lattice temperature and TMUN the temperature dependence coefficient.

The material parameters of 4H-SiC are much better established and standard SILVACO parameters were used for this material.

### **III. RESULTS & DISCUSSION**

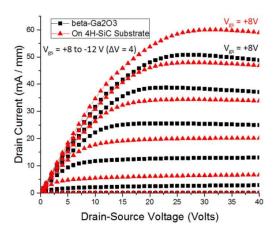

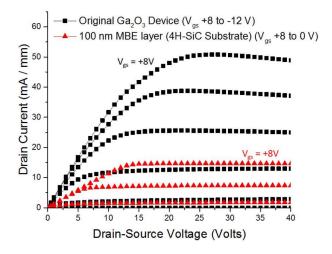

Fig. 2 demonstrates the immediate benefit of switching to a 4H-SiC substrate for this technology, output characteristics are displayed for the original device as well as the modelled version on a 4H-SiC substrate simulated to have the same doping level (1.5 x 1016 cm<sup>-3</sup>) as the original  $\beta$ -Ga2O3 substrate. Peak drain current increases for all gate bias points, an increase of 19% is seen for  $V_{gs} = +8V$  with peak lattice temperature reducing by 15% at this bias point, far extending the realm of operation of the original device.

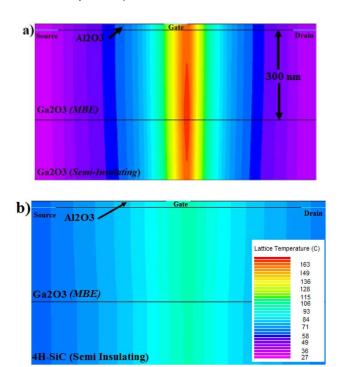

A visual comparison is shown in the form of a heat contour map for the original device and the 4H-SiC substrate version in Fig. 3. For the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device at a V<sub>gs</sub> of +8V and V<sub>ds</sub> of +40V the lattice temperature reaches a peak of 166° C,

VOLUME 5, NO. 4, JULY 2017 257

FIGURE 2. Comparison of the output characteristics from a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and the same on a 4H-SiC substrate, both are simulated to have a 300 nm thick epitaxial layer.

FIGURE 3. Lattice temperature at  $V_{gs} = 8V$  for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (a) and 4H-SiC (b) substrate.

for the same bias on a 4H-SiC substrate the peak lattice temperature reaches only 98° C.

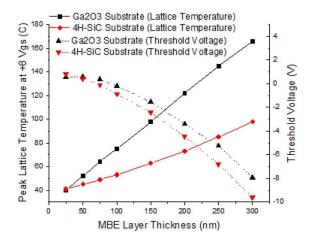

The 4H-SiC version remains normally-on although this can be shifted in both cases by a reduction in thickness of the epilayer. Fig. 4. Shows the shift in threshold voltage (V<sub>T</sub>) for modelled devices as the simulated epitaxial layer thickness is reduced, there is also an associated reduction in temperature.

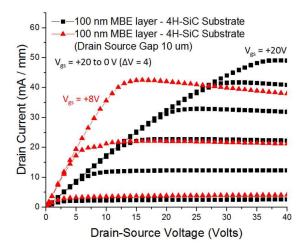

Fig. 5 shows the output characteristic of a 100 nm epitaxial layer FET on 4H-SiC device compared to the original  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET. Self-heating is virtually eliminated at this gate voltage  $(V_{gs})$  of +8 V (lattice temperature = 53° C). Peak drain current is understandably reduced due to the more

FIGURE 4. Comparison of transfer characteristics for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and the same on a 4H-SiC substrate.

restricted and hence resistive route but the nature of this design and its improved thermal conductivity allows a much higher V<sub>gs</sub> to be used.

FIGURE 5. Output characteristic for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with 100 nm layer thickness.

Fig. 6 shows how this device may be driven easily to  $V_{gs} = 20 \text{ V}$ . A similar peak drain current to the original device is achieved although on-resistance of the device is increased. If however the source-drain gap is reduced to 10  $\mu$ m a similar output characteristic to the original device may be seen with a substantially reduced V<sub>T</sub> and a lower lattice temperature (91° C at  $V_{GS} = +8 \text{ V}$ ).

Analyzing current density for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET at voltages close to V<sub>T</sub> the current path is partially forced through the semi-insulating substrate, albeit at a much reduced level due to the lower mobility of this layer. Reducing the MBE layer thickness ensures this occurs at a more positive V<sub>gs</sub> and impacts upon the threshold voltage. On the 4H-SiC substrate the heterojunction present means negligible charge will migrate in to this layer giving rise to the marginal difference in V<sub>T</sub> between substrates. This is visualized in Fig. 7.

VOLUME 5, NO. 4, JULY 2017 258

FIGURE 6. Output characteristic for 4H-SiC substrate with 100 nm layer thickness, Vgs up to +20 (lattice temp max 71° C).

FIGURE 7. Current route at  $V_{gs} = -8V$  for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (a) and 4H-SiC (b) substrate.

Below a thickness of 100 nm the device becomes normally-off (below 75 nm for the 4H-SiC substrate). As the MBE layer thickness approaches 100 nm the shift in  $V_T$  plateaus and reducing beyond this point has little benefit and begins to severely limit current performance. With this reduced layer thickness less drain current is possible for the same gate voltage as the restricted route increases the resistance of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MBE layer.

A source-drain distance of 20 microns is relatively large even for a power FET and utilising the 4H-SiC substrate allows further device scaling to increase current performance. Halving this to 10 microns and biasing at +8  $V_{gs}$  a similar current level to the original device is obtained, still

with a lower peak lattice temperature of 91° C. This scaling will of course put further stress on the dielectric layer. Simulation shows a maximum electric field of 1.22 MVcm $^{-1}$  even at +20 Vgs on the gate dielectric for the 100 nm on 4H-SiC device with reduced source-drain dimension. This is well within the remit of either Al<sub>2</sub>O<sub>3</sub> or SiO<sub>2</sub> as a gate dielectric

This demonstration allows many further routes to be taken in terms of scaling, the suitable lattice match of these two materials make it the perfect complement. Improvements in processing of this technology will undoubtedly yield more improvements from this promising material. It is accepted that 4H-SiC substrates are expensive however recent technological innovations such as those offered by Siltectra GmbH mean substrates may be split and recycled many times over [26]. The ability to grow high quality large area substrates of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> also raises the possibility of wafer bonding to high thermal conductivity substrates.

## **IV. CONCLUSION**

The replacement of the semi-insulating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with a 4H-SiC alternative in this device yields two improvements. Firstly the reduction in self-heating due to the order of magnitude thermal conductivity of 4H-SiC compared to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Secondly due to this it is possible to scale the device in reducing the MBE layer thickness and reducing the source-drain gap, giving overall the same current performance with a drastically reduced  $V_T$ .

Future work should focus on the best gate oxide for this technology. Characterization of interface traps will shed some light on this matter and the best route to practically scaling these FETs. Attention also needs to be payed to ohmic metallization stacks as even in 4H-SiC devices stability of these at elevated temperature can still be an issue [27].

### **REFERENCES**

- [1] J. Rabkowski, D. Peftitsis, and H.-P. Nee, "Silicon carbide power transistors: A new era in power electronics is initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17–26, Jun. 2012, doi: 10.1109/MIE.2012.2193291.

- [2] U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, "GaN-based RF power devices and amplifiers," *Proc. IEEE*, vol. 96, no. 2, pp. 287–305, Feb. 2008, doi: 10.1109/JPROC.2007.911060.

- [3] A. Fontserè et al., "Temperature dependence of Al/Ti-based ohmic contact to GaN devices: HEMT and MOSFET," Microelectron. Eng., vol. 88, no. 10, pp. 3140–3144, Oct. 2011, doi: 10.1016/j.mee.2011.06.015.

- [4] K. Hirama *et al.*, "High-performance p-channel diamond MOSFETs with alumina gate insulator," in *IEDM Tech. Dig.*, 2007, pp. 873–876, doi: 10.1109/IEDM.2007.4419088.

- [5] D. A. J. Moran, S. A. O. Russell, S. Sharabi, and A. Tallaire, "High frequency hydrogen-terminated diamond field effect transistor technology," in *Proc. 12th IEEE Conf. Nanotechnol.*, Birmingham, U.K., 2012, pp. 1–5, doi: 10.1109/NANO.2012.6321925.

- [6] S. Russell, S. Sharabi, A. Tallaire, and D. A. J. Moran, "RF operation of hydrogen-terminated diamond field effect transistors: A comparative study," *IEEE Trans. Electron Devices*, vol. 62, no. 3, pp. 751–756, Mar. 2015, doi: 10.1109/TED.2015.2392798.

VOLUME 5, NO. 4, JULY 2017 259

- [7] F. Cappelluti et al., "Investigating the properties of interfacial layers in planar Schottky contacts on hydrogen-terminated diamond through direct current/small-signal characterization and radial line small-signal modelling," Appl. Phys. Lett., vol. 106, no. 10, Sep. 2015, Art. no. 103504, doi: 10.1063/1.4915297.

- [8] S. A. O. Russell *et al.*, "Surface transfer doping of diamond by MoO<sub>3</sub>: A combined spectroscopic and hall measurement study," *Appl. Phys. Lett*, vol. 103, no. 20, Nov. 2013, Art. no. 202112, doi: 10.1063/1.4832455.

- [9] H. H. Tippins, "Optical absorption and photoconductivity in the band edge of β-Ga<sub>2</sub>O<sub>3</sub>," *Phys. Rev.*, vol. 140, no. 1A, pp. A316–A319, Oct. 1965, doi: 10.1103/PhysRev.140.A316.

- [10] M. D. Santia, N. Tandon, and J. D. Albrecht, "Lattice thermal conductivity in β-Ga<sub>2</sub>O<sub>3</sub> from first principles," *Appl. Phys. Lett.*, vol. 107, no. 4, Jul. 2015, Art. no. 041907, doi: 10.1063/1.4927742.

- [11] Z. Galazka *et al.*, "Czochralski growth and characterization of β-Ga<sub>2</sub>O<sub>3</sub> single crystals," *Cryst. Res. Technol.*, vol. 45, no. 12, pp. 1229–1236, Dec. 2010, doi: 10.1002/crat.201000341.

- [12] S. Geller, "Crystal structure of β-Ga<sub>2</sub>O<sub>3</sub>," J. Chem. Phys., vol. 33, no. 3, pp. 676–684, Sep. 1960, doi: 10.1063/1.1731237.

- [13] Y. S. Lee et al., "Atomic layer deposited gallium oxide buffer layer enables 1.2 V open-circuit voltage in cuprous oxide solar cells," Adv. Mater., vol. 26, no. 27, pp. 4704–4710, Jul. 2104, doi: 10.1002/adma.201401054.

- [14] T. Minami, Y. Nishi, and T. Miyata, "Heterojunction solar cell with 6% efficiency based on an n-type aluminium-gallium-oxide thin film and p-type sodium-doped Cu<sub>2</sub>O sheet," *Appl. Phys. Exp.*, vol. 8, no. 2, Jan. 2015, Art. no. 022301, doi: 10.7567/APEX.8.022301.

- [15] M. Orita, H. Ohta, M. Hirano, and H. Hosono, "Deep-ultraviolet transparent conductive β-Ga<sub>2</sub>O<sub>3</sub> thin films," *Appl. Phys. Lett.*, vol. 77, no. 25, pp. 4166–4168, Dec. 2000, doi: 10.1063/1.1330559.

- [16] X. Yu, T. J. Marks, and A. Facchetti, "Metal oxides for optoelectronic applications," *Nat. Mater.*, vol. 15, no. 4, pp. 383–396, Mar. 2016, doi: 10.1038/nmat4599.

- [17] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates," *Appl. Phys. Lett.*, vol. 100, no. 1, Jan. 2012, Art. no. 013504, doi: 10.1063/1.3674287.

- [18] M. Higashiwaki et al., "Depletion-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs," in Proc. 71st Device Res. Conf., Notre Dame, IN, USA, 2013, pp. 1–2, doi: 10.1109/DRC.2013.6633890.

- [19] M. Higashiwaki *et al.*, "Depletion-mode Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors on β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates and temperature dependence of their device characteristics," *Appl. Phys. Lett.*, vol. 103, no. 12, Sep. 2013, Art. no. 123511, doi: 10.1063/1.4821858.

- [20] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 212–215, Feb. 2016, doi: 10.1109/LED.2015.2512279.

- [21] T. Kamimura et al., "Band alignment and electrical properties of Al<sub>2</sub>O<sub>3</sub>/β-Ga<sub>2</sub>O<sub>3</sub> heterojunctions," Appl. Phys. Lett., vol. 104, no. 19, May 2014, Art. no. 192104, doi: 10.1063/1.4876920.

- [22] K. Konishi et al., "Large conduction band offset at SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub> heterojunction determined by X-ray photoelectron spectroscopy," *Phys. Status Solidi B*, vol. 253, no. 4, pp. 623–625, Feb. 2016, doi: 10.1002/pssb.201552519.

- [23] ATLAS SILVACO, "Atlas simulation of a wide bandgap Ga<sub>2</sub>O<sub>3</sub> MOSFET," *Simul. Stand.*, vol. 23, no. 4, pp. 7–9, Oct./Dec. 2013.

- [24] C. Chan, P. A. Mawby, and P. M. Gammon, "Analysis of linear-doped Si/SiC power LDMOSFETs based on device simulation," *IEEE Trans. Electron Devices*, vol. 63, no. 6, pp. 2442–2448, Jun. 2016, doi: 10.1109/TED.2016.2550865.

- [25] K. Irmscher, Z. Galazka, M. Pietsch, R. Uecher, and R. Fornari, "Electrical properties of β-Ga<sub>2</sub>O<sub>3</sub> single crystals grown by the Czochralski method," J. Appl. Phys. vol. 110, no. 6, Sep. 2011, Art. no. 063720, doi: 10.1063/1.3642962.

- [26] [Online]. Available: http://www.siltectra.com/

- [27] D. P. Hamilton *et al.*, "High-temperature electrical and thermal aging performance and application considerations for SiC power DMOSFETs," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7967–7979, Oct. 2017, doi: 10.1109/TPEL.2016.2636743.

**STEPHEN A. O. RUSSELL** was born in Kent, U.K., in 1984. He received the M.Sc. (Hons.) degree in physics from the University of Birmingham, Birmingham, U.K., in 2007, the M.Sc. degree in nanotechnology from University College London, London, U.K., in 2009, and the Ph.D. degree in electronic engineering from the University of Glasgow, Glasgow, U.K., in 2013.

From 2013 to 2014, he was a Post-Doctoral Research Assistant with the University of Glasgow reasearching diamond electronics with a focus on

field-effect transistors for high-performance applications and has authored several papers on this topic. In 2014, he was a Research Fellow with the University of Warwick, where he was involved in high-voltage blocking (10 kV) silicon carbide MOSFETS.

Dr. Russell has recently been appointed as a Senior Research Fellow with the University of Warwick to continue work on this and other power semiconductor devices. More recently he has taken an interest in Gallium Oxide as a new material for power electronics. In 2017, he was awarded a feasibility study from the Advanced Propulsion Centre, U.K., to investigate on the above area.

**AMADOR PÉREZ-TOMÁS** received the Ph.D. degree in physics from the Autonomous University of Barcelona, Barcelona, Spain, in 2005.

From 1999 to 2001, he was with Hewlett-Packard. From 2006 to 2008, he was a Research Fellow with the University of Warwick, Coventry, U.K. From 2008 to 2014, he was with the Consejo Superior de Investigaciones Científicas Ramon y Cajal. In 2014, he joined the Institut Català de Nanociència i Nanotecnologia. He has authored or co-authored over 150 journal papers and con-

ferences. He is the Founder of SME Wismok SL (Orbital 40, SME Seal of Excellence). His current research interests include engineering wide bandgap semiconductors and perovskite materials for novel electronic and optoelectronic devices.

CHRISTOPHER F. McCONVILLE is the Deputy Pro Vice-Chancellor for Research and Innovation with the College of Science, Engineering and Health, RMIT University, Melbourne, Australia. He was a Professor of Experimental Physics with the University of Warwick, U.K., where he is currently an Honorary Professor. From 2010 to 2016 he was the Head of the Nanoscience Research Cluster, where he was formerly the Director of the Science City Research Alliance between the University of Warwick and the University of

Birmingham, where he holds the Honorary Chair in Physics.

His research interests include surfaces, interfaces, epitaxial growth of semiconducting materials, conventional, and novel oxide electronic materials. His research cluster uses MBE, PLD, and CVD growth facilities and also uses a range of surface and bulk sensitive techniques (including XRD, TEM, XPS, STM, and AFM) to extract physical and electronic structure information. He has pioneered surface studies of III–V's, III-nitrides, and several semiconducting oxide materials.

Mr. McConville was the recipient of an Erskine Fellowship in 2010, the Institute of Physics and British Vacuum Council's Senior Prize, and the John Yarwood Memorial Medal in 2007. He has raised over £11M in grant income; delivered over 120 invited lectures and seminars at national and international conferences, workshops, and research institutions world-wide; published over 250 papers in refereed journals along with three book chapters. He is the Co-Editor of the first book on III-nitride materials entitled *Indium Nitride and Related Alloys* (2009).

260 VOLUME 5, NO. 4, JULY 2017

**CRAIG A. FISHER** was born in Warwickshire, U.K., in 1984. He received the M.Sc. degree in advanced electronics engineering and the Ph.D. degree in silicon carbide power electronics with a focus on three principle areas: novel edge termination solutions for high voltage power devices, carrier lifetime enhancement using high temperature processes, and the formation of robust ohmic contacts to p-type 4H-SiC, from the University of Warwick, Coventry, U.K., in 2010 and 2014, respectively.

He then spent 12 months as a Research Fellow with the School of Engineering, University of Warwick, where his research interests included the design, fabrication, and characterization of 4H-SiC MOSFETs and diodes for high voltage (>3.3 kV) applications. Since 2015, he has been involved in the power electronics industry, developing silicon carbide power devices and systems. He has authored (or co-authored) over 40 journal/international conference papers, and has acted as a Reviewer for the IEEE TRANSACTIONS ON ELECTRON DEVICES and the IET.

PHILIP A. MAWBY (S'85–M'86–SM'01) received the B.Sc. and Ph.D. degrees from the University of Leeds, U.K., in 1986. His Ph.D. degree focused on the development of GaAs/AlGaAs heterojunction bipolar transistors for high power radio frequency applications, in conjunction with co-workers with the GEC Hirst Research Centre, Wembley, U.K. Following this, he joined the University of Wales, Swansea, U.K., where he established the Power Electronics Design Centre, which carried work out in a

whole range of areas relating to power electronics. The center focused on interaction with SMEs in Wales as well as larger international companies. While he was in Swansea, he also held the Royal Academy of Engineering Chair for Power Electronics.

After 19 years with the University of Wales, he joined the University of Warwick, Coventry, U.K., where he founded the Power Electronics, Applications and Technology in Energy Research group. His main research interests include materials for new power devices, the modeling of power devices and circuits, and power integrated circuits. He has also worked extensively on the development of device simulation algorithms, as well as optoelectronic and quantum-based device structures.

Dr. Mawby is on many international conference committees including ISPSD, EPE, BCTM, and ESSDERC. He is a Chartered Engineer, a fellow of the IET and of the Institute of Physics. He has published over 70 journal papers and 100 conference papers, and is a Distinguished Lecturer for the IEEE Electron Devices Society.

**DEAN P. HAMILTON** received the first degree and M.Eng. degree in electronic systems engineering from the University of York, U.K., in 1996 and 1997, respectively, and the Ph.D. degree from the University of Warwick, Coventry, U.K. He joined the Systems Design team with Marconi Communications and then Ericsson where he focused on large high speed data switching systems, led the development of an ADSL system, and was a member of the next-generation system developments team.

He was a Research Fellow with the School of Engineering Power Electronics Research Group. He has been part of a team to develop and validate a fast inverter simulator for Toyota, Japan, to model the continuous power cycling of IGBTs and on a low carbon vehicle project to evaluate SiC MOSFETs and packaging.

Dr. Hamilton's current project and research interests are on the high temperature reliability and performance of SiC power devices and packaging materials for future high temperature capable power modules and converters. He is a member of the Materials Research Society and a frequent reviewer of IEEE journal publications.

MICHAEL R. JENNINGS was born in Neath, Wales, in 1980. He received the B.Eng. degree in electronics with communications from the University of Wales, Swansea, U.K., in 2003, the B.Eng. from Union College, Schenectady, NY, USA, and the Ph.D. degree in power semiconductors from the University of Warwick, Coventry, U.K.

His current research interests include high voltage bipolar devices (PiN diodes and Thyristors) in SiC, novel gate oxidation processes for FETs,

and 3C-SiC (cubic) growth above direct wafer bonded Si/SiC structures.

Dr. Jennings is a Lecturer on the first year general engineering electronics course. He was a recipient of the Science City Research Alliance Fellowship, sponsored by the European Regional Development Fund and Advantage West Midlands, in 2009. He has won travel scholarships from the IEE (Hudswell Bequest Fellowship) and Welsh Livery Guild for electrical engineering research purposes. The scholarships obtained allowed him to visit Rensselaer Polytechnic Institute, Troy, NY, USA, in 2005. The focus of his research within this remit was the development of Silicon carbide devices.

VOLUME 5, NO. 4, JULY 2017 261