Technische Universität Ilmenau Fakultät für Maschinenbau Pontificia Universidad Católica del Perú Escuela de Posgrado

## **Master Thesis**

Implementation of a High Performance Embedded MPC on FPGA using High-Level Synthesis

> To achieve the Degree of: Master of Science (M. Sc.) In Mechatronics

Submitted by: Antonio Araujo Barrientos

Supervisor (TU Ilmenau): Dr. rer. nat. Abebe Geletu Supervisor (PUCP): Dr. Elizabeth Villota Cerna

Date and Place: 13/04/2017, Ilmenau, Germany

## Implementation of a High Performance Embedded MPC on FPGA using High-Level Synthesis

Master Thesis in Mechatronics

submitted by

#### Antonio Araujo Barrientos

born on 02 April 1992 in Lima

in the

### Simulation and Optimal Processes Group

Department of Computer Science and Automation Technische Universität Ilmenau

> Advisors: Dr. rer. nat. Abebe Geletu Dr. Elizabeth Villota Cerna (PUCP)

Submission Date: 13 April 2017

### Declaration

I declare that the work is entirely my own and was produced with no assistance from third parties.

I certify that the work has not been submitted in the same or any similar form for assessment to any other examining body and all references, direct and indirect, are indicated as such and have been cited accordingly.

## Abstract

Model predictive control (MPC) has been, since its introduction in the late 70's, a well accepted control technique, especially for industrial processes, which are typically slow and allow for on-line calculation of the control inputs. Its greatest advantage is its ability to consider constraints, on both inputs and states, directly and naturally. More recently, the improvements in processor speed have allowed its use in a wider range of problems, many involving faster dynamics. Nevertheless, implementation of MPC algorithms on embedded systems with resources, size, power consumption and cost constraints remains a challenge.

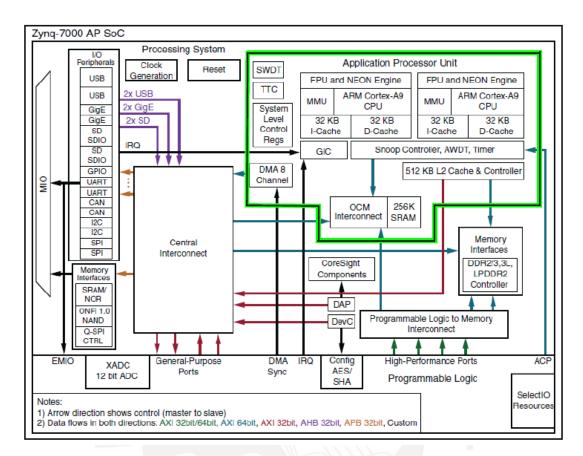

In this thesis, High-Level Synthesis (HLS) is used to implement implicit MPC algorithms for linear (LMPC) and nonlinear (NMPC) plant models, considering constraints on both control inputs and states of the system. The algorithms are implemented in the Zynq<sup>®</sup> -7000 All Programmable System-on-a-Chip (AP SoC) ZC706 Evaluation Kit, targeting Xilinx's Zynq<sup>®</sup>-7000 AP SoC which contains a general purpose Field Programmable Gate Array (FPGA). In order to solve the optimization problem at each sampling instant, an Interior-Point Method (IPM) is used. The main computation cost of this method is the solution of a system of linear equations. A minimum residual (MINRES) algorithm is used for the solution of this system of equations taking into consideration its special structure in order to make it computationally efficient. A library was created for the linear algebra operations required for the IPM and MINRES algorithms.

The implementation is tested on trajectory tracking case studies. Results for the linear case show good performance and implementation metrics, as well as computation times within the considered sampling periods. For the nonlinear case, although a high computation time was needed, the algorithm performed well on the case study presented. Because of resources constraints, implementation of the nonlinear algorithm on higher order systems was precluded.

Master Thesis Antonio Araujo Barrientos

## Kurzfassung

Modellprädiktive Regelung (engl: Model Predictive Control (MPC) ist, seit der Einführung in den späten 70er Jahren, eine gut angenommene Regelungstechnik, insbesondere für industrielle Prozesse, die typischerweise langsam sind und die online Steuergröße Berechnung ermöglichen. Ihr größter Vorteil ist die Fähigkeit, Beschränkungen bezüglich der Steuergrößen und der Regelgrößen zu berücksichtigen. In letzter Zeit hat die Verbesserung der Geschwindigkeit der Prozessoren den Einsatz in einer breitere Problemreichweite mit einer schnelleren Dynamik ermöglicht. Allerdings bleibt die MPC Algorithmus-Implementierung in eingebetteten Systeme mit beschränkte Ressourcen, Größe, Energieverbrauch und Kosten eine Herausforderung.

In dieser Arbeit wird die High-Level Synthesis (HLS) benutzt, um implizit MPC Algorithmen für lineare (LMPC) und nichtlineare (NMPC) Regelstrecken zu implementieren, wobei Steuergröße- und Regelgrößenbeschränkungen berücksichtigt werden. Die Algorithmen sind im Zynq<sup>®</sup>-7000 AP SoC ZC706 Auswertungskit implementiert, wobei auf der Xilinxs Zynq<sup>®</sup>-7000 AP SoC, der ein allgemeiner Zweck FPGA enthält, abgezielt wird. Ein innere-Punkte Verfahren (engl: Interior-Point Method (IPM)) wird für die Lösung des Optimierungsproblems in jedem Sampling benutzt. Die größte Berechnungskomplexität bei dem IPM ist die Lösung eines linearen Gleichungssystems. Ein minimaler Residuum-Algorithmus (MINRES) wird für die Lösung dieses Gleichungssystem benutzt, wobei die spezielle Struktur berücksichtigt wird, um das Verfahren recheneffizient zu machen. Es wurde eine Bibliothek mit Funktionen für die benötigten linearen Algebra

Die Implementierung wird in Trajektorieverfolgung Fallstudien getestet. Die Ergebnisse für den linearen Fall zeigen gute Leistungen und Metriken, sowie Rechenzeiten innerhalb des berücksichtigten Taktzeiten. Für den nichtlinearen Fall wurde eine hohe Rechenzeit benötigt. Trotzdem hat der Algorithmus für die vorgestellte Fallstudie gut funktioniert. Infolge der Ressourcenbeschränkungen war die Implementierung des nichtlinearen Algorithmus für Systeme höherer Ordnung verhindert.

Master Thesis Antonio Araujo Barrientos

# Acknowledgments

Special acknowledgment to my supervisor Dr. Abebe Geletu for the valuable guide throughout the development of my thesis. I also thank professor Pu Li for the interest shown and the support. My thankfulness also to Dr. Elizabeth Villota for the comments on my work. Finally, I would like to thank my family and all my friends with whom I spent this year in Ilmenau for the support provided.

Master Thesis Antonio Araujo Barrientos

# Contents

| 1 | Intr | oduction                                  | 1  |

|---|------|-------------------------------------------|----|

|   | 1.1  | Motivation                                | 1  |

|   | 1.2  | Problem Statement                         | 2  |

|   | 1.3  | Objectives                                | 3  |

|   | 1.4  | Thesis Organization                       | 3  |

|   |      |                                           |    |

| 2 | Higl | h-Level Synthesis                         | 5  |

|   | 2.1  | Embedded Systems Processors               | 5  |

|   | 2.2  | Field Programmable Gate Array (FPGA)      | 6  |

|   | 2.3  | Traditional FPGA Programming Languages    | 8  |

|   | 2.4  | High-Level Synthesis (HLS)                | 9  |

|   | 2.5  | Summary                                   | 11 |

| 3 | Мос  | del Predictive Control (MPC)              | 13 |

|   | 3.1  | Principle of MPC                          | 13 |

|   | 3.2  | Linear Model Predictive Control (LMPC)    | 14 |

|   |      | 3.2.1 LMPC Formulation                    | 14 |

|   |      | 3.2.2 Explicit LMPC                       | 16 |

|   |      | 3.2.3 Implicit LMPC                       | 16 |

|   |      | 3.2.3.1 Dense Approach                    | 17 |

|   |      | 3.2.3.2 Sparse Approach                   | 17 |

|   | 3.3  | Nonlinear Model Predictive Control (NMPC) | 20 |

|   |      | 3.3.1 NMPC Formulation                    | 21 |

|   | 3.4  | Summary                                   | 22 |

| 4 | Inte | rior-Point Method (IPM)                   | 23 |

|   | 4.1  | Primal-Dual IPM for QP                    | 24 |

|   | 4.2  | Primal-Dual IPM for NLP                   | 28 |

|   | 4.3  | Summary                                   | 30 |

#### Contents

| Imp | lementation of Embedded MPC Algorithms on FPGA Using HLS                                                                                                                | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Related Work                                                                                                                                                            | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.2 | Compressed Storage Formats                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3 | Hardware and Software                                                                                                                                                   | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.4 | LMPC Algorithm Implementation                                                                                                                                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.4.1 Block Structure and Sparsity                                                                                                                                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.4.2 LMPC Formulation                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.4.3 Primal-dual IPM implementation                                                                                                                                    | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.4.4 MINRES Algorithm Implementation for QP                                                                                                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.5 | NMPC Algorithm Implementation                                                                                                                                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.5.1 Block Structure and Sparsity                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.5.2 NMPC Formulation                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.5.3 Primal-dual IPM implementation for NLP                                                                                                                            | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 5.5.4 MINRES Algorithm Implementation for NLP                                                                                                                           | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.6 | Optimization Directives                                                                                                                                                 | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.7 | Integration in Vivado IDE                                                                                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.8 | Summary                                                                                                                                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Cas | e Studies                                                                                                                                                               | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1 | Case Studies for LMPC                                                                                                                                                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                                                                                         | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

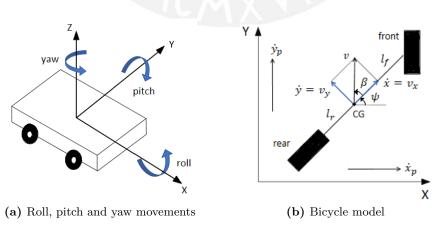

|     | 6.1.2 Three-state Bicycle Model                                                                                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 6.1.3 Five-state Bicycle Model                                                                                                                                          | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 6.1.4 Satellite Model                                                                                                                                                   | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 6.1.5 Comparison Between FPGA and Pure Software Implementation                                                                                                          | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2 | Case Studies for NMPC                                                                                                                                                   | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

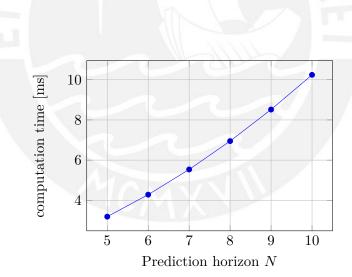

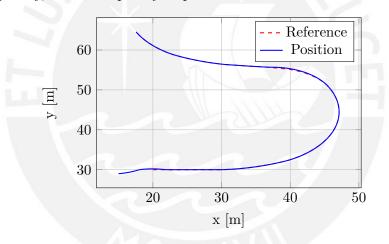

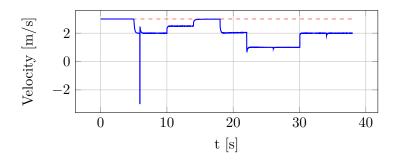

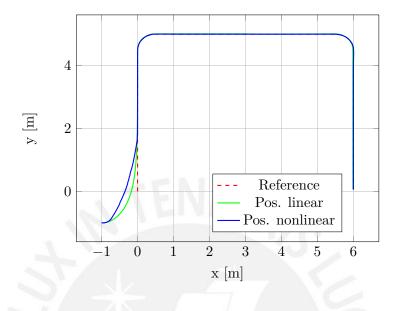

|     | 6.2.1 Three-state Bicycle Model                                                                                                                                         | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.3 | Summary                                                                                                                                                                 | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Con | clusions and Future Work                                                                                                                                                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | 5.2       Compressed Storage Formats         5.3       Hardware and Software         5.4       LMPC Algorithm Implementation         5.4.1       Block Structure and Sparsity         5.4.2       LMPC Formulation         5.4.3       Primal-dual IPM implementation for QP         5.4.4       MINRES Algorithm Implementation for QP         5.5       NMPC Algorithm Implementation         5.5.1       Block Structure and Sparsity         5.5.2       NMPC Formulation         5.5.3       Primal-dual IPM implementation for NLP         5.5.4       MINRES Algorithm Implementation for NLP         5.5.3       Primal-dual IPM implementation for NLP         5.5.4       MINRES Algorithm Implementation for NLP         5.5.4       MINRES Algorithm Implementation for NLP         5.5.4       MINRES Algorithm Implementation for NLP         5.6       Optimization Directives         5.7       Integration in Vivado IDE         5.8       Summary         6.1       Case Studies for LMPC         6.1.1       Linearization Along Trajectories         6.1.2       Three-state Bicycle Model         6.1.3       Five-state Bicycle Model         6.1.4       Satellite Model         6.1.5 |

### Chapter 1

## Introduction

### 1.1 Motivation

Embedded control is necessary to adequately fulfill the functionality of an embedded system. This control strategy has to be implemented on the chosen processor, satisfying any resources constraints and performance requirements, like for example area constraints, computation time, which is vital for real time applications, and power consumption requirements. Embedded control is ubiquitous, for example in the automotive and aircraft industries for applications like autonomous driving, in robotics or even in more simple systems like household appliances.

Typical processors for embedded applications include CPUs, Graphics Processor Units (GPUs) and Digital Signal Processors (DSPs). These processors execute instructions in a sequential way. Multi core processors can be used to achieve parallelism, as is, in fact, the case for GPUs which contain a large number of programmable cores; however, despite the improvements in performance, these processors continue to possess a fixed hardware architecture. On the other hand, hardware-customizable integrated circuits, namely Field Programmable Gate Arrays (FPGAs), are much more flexible and a wide level of parallelism can be achieved, allowing to trade off resource usage for higher throughput and lower latency in order to meet resource constraints, while achieving a higher power efficiency [14], which is an important issue since most fast autonomous systems are battery driven. In this context, the use of hardware implementations on FPGAs is of great interest and the main topic of this thesis.

Hardware programming is traditionally performed based on Hardware Description Languages (HDLs) like VHDL or Verilog, targeting Application-Specific Integrated Circuits (ASICs) or FPGAs. The latter require less design time, effort and costs, and offer the capability of being reprogrammed at the expense of a lower achievable

#### 1 Introduction

performance. The design and verification of embedded systems with this approach demands a lot of time compared with pure software implementations. In order to increase productivity, lot of effort has been put into the development of High-Level Synthesis (HLS) tools, which allow the user to specify the behavior of the algorithm at a higher level of abstraction, commonly using C/C++ language. Implementing the algorithms at this higher level of abstraction permits more complex algorithms to be accelerated in hardware without any knowledge of HDLs being required. This reduces significantly the design time, at the expense of a lower control over the final synthesized design.

Real systems may have constraints on both control inputs and states. For example, in the injection system of a car, the valves have a maximum opening gap and due to consumption matters, the flow through the valves may be restricted to be between certain values; this would represent respectively constraints on a control input and a state for this particular system. Classical control techniques, namely PID control, fail to take these constraints into consideration and therefore operate the plant far from the constraints in order to allow for disturbances to take place, making the operation inefficient [45]. Model Predictive Control (MPC) is one of the few advanced control techniques that has had an important and widespread impact on industrial process engineering, precisely because of its ability to naturally take the constraints of the system into consideration, as well as being easily applied to MIMO systems.

Implicit MPC requires the control input to be calculated at every sampling instant, which initially confined its implementation to systems with slow dynamics, especially in the chemical industry. With the growing improvements in processor speed and growing transistor count, MPC is in recent years being applied to systems with faster dynamics. This poses the challenge of calculating the control input to be applied to the system within a shorter period of time.

MPC involves the solution at every sampling period of an optimization problem. This problem resulting from the control formulation possesses a well defined structure, which can be used to tailor the algorithms for the solution in order to improve the efficiency and speed, while reducing memory requirements.

### 1.2 Problem Statement

The on-line computation of the MPC problem solution demands a high computational effort and must be obtained within the sampling period of the system under consideration. For fast dynamic systems, this is usually in the order of milliseconds. For the case of embedded control, this solution must be also computed in an efficient way so that

timing, resource, and power consumption requirements are met. An FPGA is chosen to accelerate the most computationally demanding tasks of the MPC problem solution.

### 1.3 Objectives

This thesis aims to design a high performance embedded MPC implementation accomplishing the following objectives:

- To study FPGAs hardware architecture for efficient implementations.

- To study the use of HLS tools on modern FPGA hardware.

- To design a high-level performance implementation of an MPC scheme for the embedded control of fast autonomous systems.

- To validate the viability of the implementation through case studies and real-time MPC control of systems with fast dynamics.

### 1.4 Thesis Organization

The content of this thesis is organized as follows:

- Chapter 2 starts with a brief overview of the different processor types available for embedded control. It gives then an introduction to FPGAs and the ways they can be programmed, namely using HDLs or HLS, expatiating on the use of the latter as an important topic of this work.

- Chapter 3 presents the principle of MPC and the formulations for Linear Model Predictive Control (LMPC) and Nonlinear Model Predictive Control (NMPC) considered in this thesis. Special care is taken in describing the structure of the corresponding Quadratic Programming (QP) and Nonlinear Programming (NLP) problems that result from the approach chosen for the formulation.

- Chapter 4 describes the primal-dual Interior-Point Method (IPM) for the solution of QP and NLP problems, and the special structure arising from the control approach, which is exploited to improve computation time and memory requirements.

- Chapter 5 describes in detail the implementation of the IPM solvers. The chapter starts with an overview of the related work done regarding hardware MPC implementations. Then, a description of the compressed storage formats used for memory utilization reduction is given, the employed hardware and software tools

#### 1 Introduction

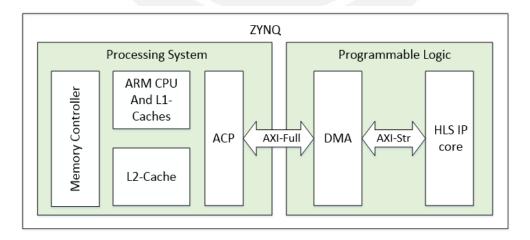

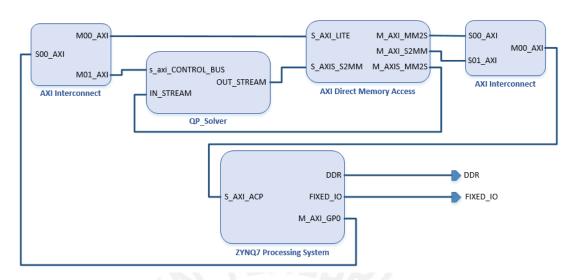

are then introduced. Next, LMPC and NMPC algorithm implementations are described step by step. An explanation of the optimization directives used for exploiting parallelization in the FPGA is then given. This chapter ends with a description of how the solvers implemented using HLS are integrated on a design targeting a Zynq<sup>®</sup> All Programmable System-on-a-Chip (AP SoC).

- Chapter 6 presents a description of the models considered for the case studies. Trajectory tracking problems were solved and the results obtained are shown and described, together with performance and utilization metrics.

- Chapter 7 concludes this thesis with a summary of the work done and the obtained results, as well as possible future research directions.

### Chapter 2

## **High-Level Synthesis**

ASICs and FPGAs are the most popular hardware programming technologies. They are traditionally programmed with Hardware Description Languages (HDLs) like VHDL or Verilog, which make the design process long and require expertise. Another approach is the use of HLS tools. This chapter introduces the use of HLS for FPGA programming.

### 2.1 Embedded Systems Processors

This section provides a brief overview of the processor choice for embedded systems, based on the description by Vahid and Givargis presented in [64].

An embedded system is any computer system different from a PC with constrained features like size, cost, performance and power consumption designed to perform a single task. Its most important part is the processor, which performs the required computations and manages the entire operation. Depending on the architecture used for the desired functionality it can be one of the following:

- General-purpose processor, suits a wide range of applications, which reduces design time and related costs at the expense of achievable performance. Reduced instruction set computing (RISC) processors, like those with the ARM architecture widely used in embedded applications, are an example of this category.

- Single-purpose processor, is customized for a single specific functionality. Is also called accelerator and will be considered in this thesis for the hardware implementation. This type of processor allows for fast performance and small size and power consumption, at the expense of higher development costs and lower flexibility.

• Application-specific processor, developed for a particular type of applications that have similar characteristics. Properties of this processor type can be placed inbetween the previous two types. An important example of an application-specific processor are DSPs, which allow math intensive operations to be executed on digital signals, like video and audio.

Beside the processor technology previously described, the Integrated Circuit (IC) technology also plays an important role in determining how the digital gate-level implementation is mapped to the IC. Bottom layers on an IC form transistor-based logic gates and top layers connect these gates through wires. Three different technologies are to be considered:

- In full-custom IC technology, all layers are optimized for a particular implementation. Excellent performance can be achieved while retaining a small size and power consumption at the expense of elevated development costs and design time. Only economically viable for large production volumes, like commercially available microprocessors.

- Semi-custom, for this case lower layers are fully or partially built, remaining the upper layers for the developer to finish. Present good performance and size, with smaller costs as full-custom ICs. ASICs are an example of this technology.

- In programmable logic devices all layers already exist, circuits are programmed by creating or destroying connections between gate-connecting wires. FPGAs are the most popular devices of this type. As an important topic of this thesis, they will be treated separately in section 2.2.

Any type of processor technology can be implemented on any type of IC technology, for this thesis, a hardware accelerator was implemented on an FPGA.

### 2.2 Field Programmable Gate Array (FPGA)

An FPGA is a semiconductor device, namely an IC, that can be programmed after fabrication and can be dynamically reconfigured for different tasks. This distinguishes them from ASICs, which are more application-specific [72]. The fabrication cost of an ASIC for a given application is still very high, making it economically viable only for applications demanding a lot of units, sometimes in the range of millions.

On normal processors, instructions are executed in a sequential manner. Initial attempts to improve execution runtime for a given application relied on the increase

in the processor clock frequency so that instructions would execute faster. Afterwards, attempts considering specialized processors like DSPs or GPUs became popular. The problem with these approaches is that regardless of a growing processor speed the memory accesses are limited by a fixed unified memory space. This led to the introduction of multi core processors and parallel execution which are preferred today. Unlike processors, FPGAs don't execute programs as a sequence of instructions, they allow for parallel implementation of an algorithm without the restriction of cache and a fixed memory space, FPGAs are therefore ideal for implementing hardware accelerators to improve algorithm performance [74].

FPGAs give the designer the opportunity to obtain the power consumption savings and the performance of a custom implementation without the cost and complexity of developing an ASIC. In addition, reprogrammability and the increasing logic density, consisting up to two million logic cells on modern devices allows for the implementation of complex algorithms while exploiting the inherently parallel nature of a custom circuit [74]. All these properties make FPGAs a good choice for numerous applications in different markets like aerospace, military and defense, audio and video processing, automotive, medical, communications and industrial applications [18, 72].

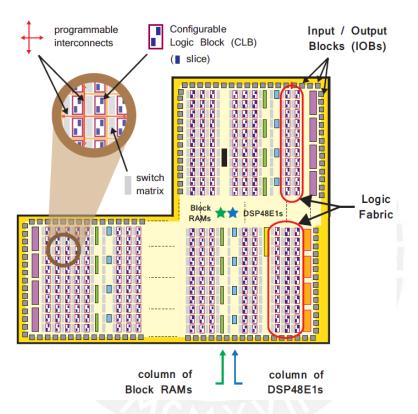

In this thesis, a Xilinx<sup>®</sup> device is utilized for the implementation of an MPC algorithm. Using Xilinx<sup>®</sup>-specific terms, general purpose FPGA logic fabric is composed basically of slices, Configurable Logic Blocks (CLBs) and Input/Output Blocks (IOBs) as well as special resources like DSP48E1 and Block RAMs (BRAMs). Figure 2.1 shows the basic architecture of the Programmable Logic (PL) part for the Zynq<sup>®</sup> device used for this work. Next, a brief explanation extracted from [21] is given:

- Lookup Table (LUT): Resource capable of implementing simple logic functions, small ROM, small RAM or a shift register. LUTs can be combined to form larger units.

- Slice: Unit that contains resources for implementing combinatorial and sequential logic circuits. Composed basically by LUTs and Flip-Flops (FFs).

- CLB: Each CLB contains two logic slices and is positioned next to a switch matrix, which makes possible the connection between elements within a CLB and from one CLB to other resources.

- IOB: Are the interface between the FPGA resources and the physical pads of the device. Each IOB can handle a 1-bit input or output signal.

- BRAM: This special purpose component is thought for dense memory requirements. Can implement RAM, ROM, and FIFO buffers. Using BRAMs allows a large

amount of data (up to 36Kb for Zynq<sup>®</sup> devices) to be stored in a small physical space on the device. The alternative, implemented only with LUTs is called distributed memory.

• DSP48E1 Are dedicated silicon resources for implementing high-speed arithmetic on signals with medium to long arithmetic word lengths. Comprise a pre-adder/subtractor, a multiplier, and a post-adder/subtractor with a logic unit.

Figure 2.1 – Logic fabric on the Zynq 7000 AP SoC[21]

### 2.3 Traditional FPGA Programming Languages

VHDL and Verilog are the most widely used HDLs, both are IEEE standards and are supported by synthesis tools for ASICs and FPGAs [17]. VHDL was developed in the 70's and 80's by the U.S. Department of Defense and was proposed as an IEEE standard in 1986, being adopted one year later [55]. Verilog was adopted as a standard in 1995 [65].

Hardware description involves two major aspects: behavior and structure. Behavioral description requires a language which allows the behavior or functionality to be declared

independent of structural or design aspects. The description of structure requires the language to express this hardware structure irrespective of the behavioral models that might be applied to it [48]. HDLs allow the design to be portable and independent of technology, allowing the engineer to focus on functionality. After an HDL design is completed it allows for simulation, synthesis, place and route procedures and finally it can be simulated again to verify results as well as timing and design constraints fulfillment [55].

### 2.4 High-Level Synthesis (HLS)

A great disadvantage of FPGA programming using the languages described in section 2.3 is the long design and implementation times when compared to alternative fixed architectures like GPUs or DSPs which are programmed only in software using languages with a higher level of abstraction. The continuously increasing complexity of functionalities and applications implemented, and the additional complexity as the result of intending to meet design constraints make necessary the use of tools that increase design productivity [20]. In this context, HLS tools have been developed to ease and accelerate the hardware design process and have started gaining acceptance since the 2000's. A detailed study on HLS history and the reasons why early attempts failed to gain acceptance is presented in [46], a review of its benefits is presented in [20]. A detailed overview of the HLS tools available up to 2011 can be found in [47]. For the work presented in this thesis, Xilinx<sup>®</sup> hardware was used, consequently, Vivado<sup>®</sup> HLS software was employed for generating a Register Transfer Level (RTL) model which was later programmed in the FPGA. For a detailed description of the tool used for this work refer to [76]. Following, a brief introduction to HLS extracted from [76] is presented.

Vivado<sup>®</sup> HLS transforms a description specified in C, C++ or System C into an RTL implementation. This higher level of abstraction programming allows both software and hardware programmers to benefit from both domains easing the design process and increasing productivity.

The HLS process consists basically of scheduling and binding operations. During scheduling, it is defined in which clock cycle each operation will be performed and during binding hardware resources to implement the scheduled operations are assigned. This process is done taking into consideration the target device, timing constraints and any optimization directive specified. Optimization directives give the programmer the possibility to influence the final RTL implementation in the desired way to improve the results. Unlike in HDLs where the interface of the design has to be explicitly specified by the programmer, in designs specified with HLS it is inferred from the arguments and return variables of the function to be synthesized, also called top function, so care must be taken in the programming style.

Vivado<sup>®</sup> HLS uses three metrics to measure the performance of a design:

- Area: Quantifies the resources (BRAMs, DSP48Es, FFs and LUTs) required for the implementation considering the target device.

- Latency: Number of clock cycles required for the function to compute all output values.

- Initiation Interval (II): Number of clock cycles before new data can be input to the function.

When designing with Vivado<sup>®</sup> HLS special care must be taken as not all C/C++ constructs are supported for synthesis; for example, no memory allocation is permitted, so all memory requirements must be known at compile time.

After developing the code with the desired functionality, it can be simulated to verify correctness. The first step is to perform a C simulation. For this purpose, an appropriate test bench written also in a high-level language is required, which should provide inputs to the top function and compare the outputs with known solutions to verify the operations are correctly performed. Once the functionality has been verified the C synthesis is performed. In this step, all user-defined optimization directives are considered and different solutions can be created to facilitate the comparison process. C synthesis outputs an RTL design which can again be verified during C/RTL cosimulation. A great advantage of HLS is that the same test bench used for C simulation is used in this step, which reduces significantly the verification time [47]. Finally, the design can be exported as an Intellectual Property (IP) block for its integration in a more complex design using Xilinx<sup>®</sup>'s IP Integrator.

Apart from the metrics used by Vivado HLS presented previously in this section, there are also three important concepts to take into consideration [74]:

- Clock Frequency: Is defined as the longest time it takes a signal to travel from a source register to a sink register.

- Throughput: Expresses the rate at which data can be passed through the system.

- Pipelining: Is the process of inserting registers between computation blocks in order to get smaller segments and allow for concurrent operation execution. Can increase latency in absolute number of clock cycles but increases performance by allowing a higher clock frequency and improving throughput. The latency caused by pipelining is a trade-off to consider during FPGA design.

### 2.5 Summary

This chapter presented a brief description of the processor choice on embedded applications focusing on the architecture and the IC technology. A description of FPGA technology and why it is a good choice for parallel computing was given. HDLs were briefly described, giving more emphasis on HLS as a productivity oriented alternative for hardware programming.

### Chapter 3

## Model Predictive Control (MPC)

MPC is a model-based control technique which determines the optimal control inputs, based on the current measurement (or estimation) of the states, such that a desired reference is reached or followed. This is accomplished by predicting the system's future response and minimizing a cost function, while having the constraints on the states and control inputs under consideration.

MPC was originally developed in the petrochemical industry. The first description of MPC applications was presented in 1976 by Richalet et al. at a conference and then summarized in 1978 in an *Automatica* paper [60]. The software proposed was called IDCOM, an acronym for Identification and Command. Later, at the 1979 National AIChE meeting, engineers of Shell Oil presented their MPC technology named dynamic matrix control (DMC) [57]. In recent years the scope of applications has increased drastically, covering areas including chemicals, food processing, automotive and aerospace applications; a detailed overview of MPC and industrial applications can be found in [56, 57].

### 3.1 Principle of MPC

MPC has had a widespread impact on industrial process control and is recently being adopted for a much wider range of applications, made possible by the constant increase in computing speed and power [45]. Its main advantage over other control techniques is the ability to naturally handle the constraints on states and control inputs of the system, allowing for a more efficient operation. It is also easily extended to multivariable systems.

The principle of MPC consists in finding, at each sampling instant, the optimal control inputs along a predefined time horizon, often called prediction horizon, in order to follow the desired reference. This is achieved by predicting the future outputs based on an explicit model while minimizing a cost function and having constraints on the system under consideration. Once the optimal control inputs for the current prediction horizon have been computed, only the inputs corresponding to the first interval of the prediction horizon are applied to the system. The process is repeated on every sampling instant shifting the prediction horizon accordingly, an approach known as *receding horizon* strategy [45]. At every sampling instant, the new measurement available, or estimation if not all states are measured, is used as input for the optimization problem.

### 3.2 Linear Model Predictive Control (LMPC)

In case the system to be controlled is linear—or a linearization around an operating point is considered—, the cost function is quadratic, and both the states and control inputs constraints are linear, then the MPC problem is an LMPC problem. The last two conditions are normally easily satisfied since the cost function is chosen to be quadratic and the constraints on the system typically appear as box constraints (simple bounds). The advantage of this formulation is that the optimization problem can be formulated as a QP problem, which is convex and therefore assures a global minimum can be found [52].

#### 3.2.1 LMPC Formulation

Consider the following linear time-varying discrete system:

$$\begin{aligned} x_{k+1} &= A_k x_k + B_k u_k \,, \\ y_k &= C x_k \,, \end{aligned} \tag{3.1}$$

where  $x_k \in \mathbb{R}^n$ ,  $u_k \in \mathbb{R}^m$  and  $y_k \in \mathbb{R}^p$  represent the states, inputs, and outputs of the system, respectively. Throughout this thesis, the notation  $x_k = x(k) = x(t = kT_s)$ , for k = 0, 1, 2, ... and  $T_s$  representing the sampling period will be considered.

The LMPC algorithm will compute the optimal control inputs  $u^*$  over a predefined control horizon  $(N_u)$ , required to follow the desired reference, and use the model in (3.1) to predict the future states over the prediction horizon  $(N_p)$ . Applied inputs to the system are considered to be piecewise constant over the sampling period.  $N_u$  is normally chosen to be less than or equal to  $N_p$ , in the following, they will be considered to be equal and will be denoted with the letter N. In order to find the optimal solution, the following cost function is to be minimized at each sampling instant k:

$$J(k) = \frac{1}{2} \left( \sum_{i=1}^{N} \|x(k+i|k) - x_r(k+i|k)\|_{Q_i}^2 + \sum_{i=0}^{N-1} \|u(k+i|k) - u_r(k+i|k)\|_{R_i}^2 \right)$$

(3.2)

where  $x_r$  and  $u_r$  denote the reference vectors for the states and control inputs respectively. The expression  $||x||_Q^2$  represents the quadratic form  $x^TQx$  and x(k+i|k) denotes the values predicted for the states at the instant k + i using the measurement or estimation available at instant k, the same applies for inputs u. It may be preferable to consider the change in the control input  $\Delta u$  instead of the control input itself; in that case, the cost function (3.2) can be easily modified. Considering the dynamics of the system and the constraints the following optimization problem is solved every time a new measurement is available:

$$\underset{u,x}{\text{minimize }} J(k) = \frac{1}{2} \sum_{i=1}^{N} \|x(k+i|k) - x_r(k+i|k)\|_{Q_i}^2 + \frac{1}{2} \sum_{i=0}^{N-1} \|u(k+i|k) - u_r(k+i|k)\|_{R_i}^2,$$

$$(3.3a)$$

subject to:

$$x(k|k) = x_0, \qquad (3.3b)$$

$$x(k+i+1|k) = A_i x(k+i|k) + B_i u(k+i|k), \qquad i = 0, 1, .., N-1, \qquad (3.3c)$$

$$D_i x(k+i|k) \le d_i, \qquad i = 1, 2, ...N,$$

(3.3d)

$$F_i u(k+i|k) \leq f_i, \qquad i = 0, 1, \dots N - 1.$$

(3.3e)

Equation (3.3c) considers the general case of a linear time-varying system, where the subindex in the matrices A and B indicates their value at instant i in the prediction horizon, starting from the actual sampling period k. Equations (3.3d) and (3.3e) impose constraints on the states and control inputs respectively, they appear usually as box constraints ( $min \leq var \leq max$ ) and can be formulated with the matrices and vectors shown in equation (3.4). In case a given state or input is not constrained then the corresponding terms in the matrices and vectors in (3.4) are simply set to zero without altering the problem structure.

$$D_i = \begin{bmatrix} I \\ -I \end{bmatrix} , \quad d_i = \begin{bmatrix} x_{max} \\ -x_{min} \end{bmatrix}, \quad (3.4a)$$

$$F_i = \begin{bmatrix} I \\ -I \end{bmatrix}$$

,  $f_i = \begin{bmatrix} u_{max} \\ -u_{min} \end{bmatrix}$ . (3.4b)

For the case of LMPC the optimization problem to solve at each sampling interval can be formulated as a QP problem of the form:

$$\underset{\xi}{\text{minimize } J(k)} = \frac{1}{2}\xi^T Q\xi + q^T \xi , \qquad (3.5a)$$

subject to:

$$A\xi = b \,, \tag{3.5b}$$

$$C\xi \leqslant d$$

. (3.5c)

Where the vector  $\xi$  represents the optimization variables and its structure depends on the solution approach. For the problem to be convex, matrix Q must be positive semidefinite [52].

#### 3.2.2 Explicit LMPC

From the LMPC formulation (3.3) is clear that when considering a time-invariant system and assuming constraints and references remain constant, only the initial state will change at every sampling instant. In explicit LMPC the optimization problem (3.3) is solved off-line for a number of initial states of interest in order to obtain an explicit dependence between the control action u and the states x of the system [8]. This approach alleviates the on-line computational cost of MPC allowing for faster systems to be considered; nevertheless, the memory requirements increase with the size of the problem. It is, therefore, more appropriate for small problems.

#### 3.2.3 Implicit LMPC

Implicit LMPC requires the solution of (3.3) to be computed on-line on every sampling instant, which demands a significant computational effort. For many years, this led MPC to be applied only to slow processes which allowed this computation to be performed within the sampling period [28]. In recent years, the application range of MPC has widened as the computational capacity of controllers improved. Two approaches for the formulation of (3.5) will be considered next.

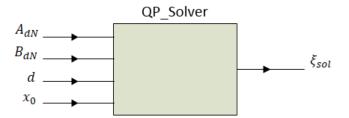

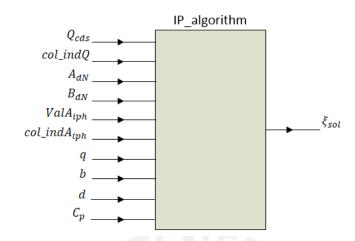

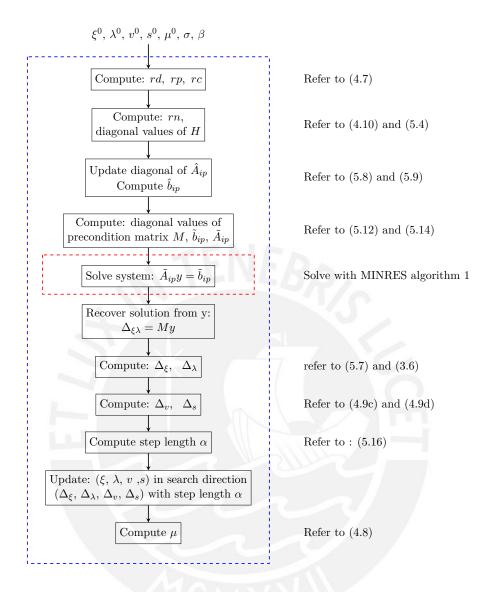

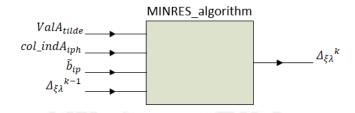

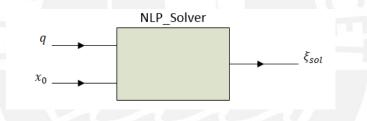

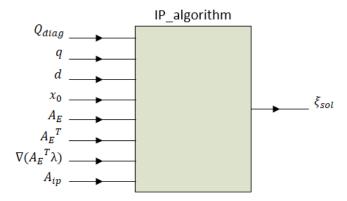

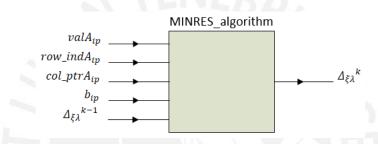

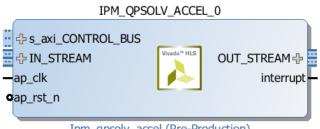

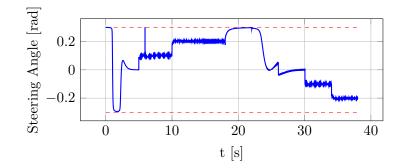

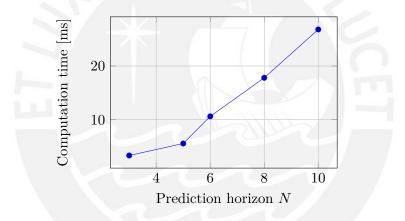

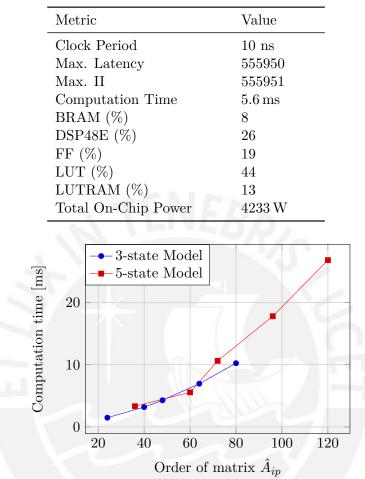

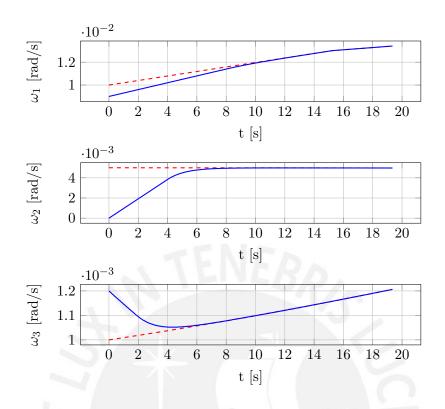

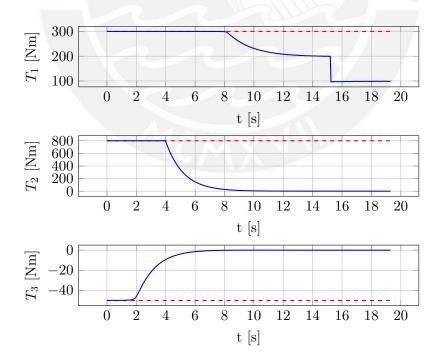

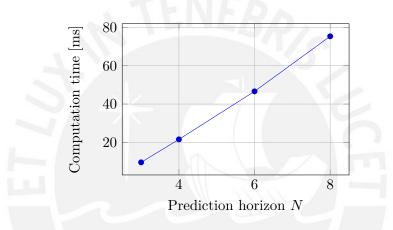

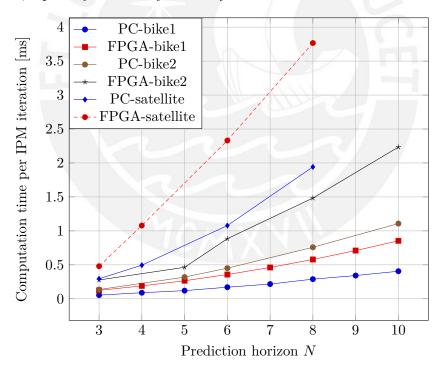

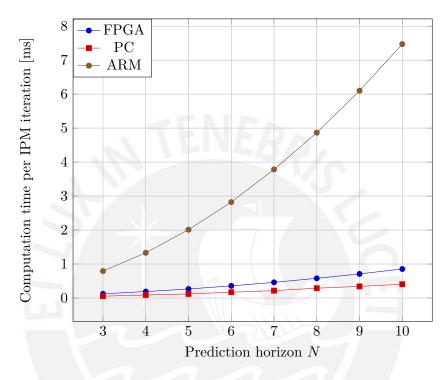

#### 3.2.3.1 Dense Approach