# Implementation of an AMIDAR-based Java Processor

#### Implementierung eines AMIDAR-basierten Java Prozessors

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von Dipl.-Inform. Changgong Li aus Heilongjiang, China Tag der Einreichung: 02.10.2018, Tag der Prüfung: 08.04.2019 Darmstadt – D 17

- 1. Gutachter: Prof. Dr.-Ing. Christian Hochberger

- 2. Gutachter: Prof. Dr. Wolfgang Karl

Fachgebiet Rechnersysteme Fachbereich Elektrotechnik und Informationstechnik Implementation of an AMIDAR-based Java Processor Implementierung eines AMIDAR-basierten Java Prozessors

Genehmigte Dissertation von Dipl.-Inform. Changgong Li aus Heilongjiang, China

1. Gutachter: Prof. Dr.-Ing. Christian Hochberger

2. Gutachter: Prof. Dr. Wolfgang Karl

Tag der Einreichung: 02.10.2018 Tag der Prüfung: 08.04.2019

Darmstadt – D 17

Li, Changgong: Implementation of an AMIDAR-based Java Processor Darmstadt, Technische Universität Darmstadt, Jahr der Veröffentlichung der Dissertation auf TUprints: 2019 Tag der mündlichen Prüfung: 08.04.2019

Verfügbar unter lediglich die vom Gesetz vorgesehenen Nutzungsrechte gemäß UrhG

# **Erklärung laut Promotionsordung**

## §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

## § 8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

## § 9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

## § 9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

Darmstadt, den 02.10.2018

(Dipl.-Inform. Changgong Li)

#### Kurzfassung

In dieser Arbeit wird ein Java Prozessor vorgestellt, welcher auf der Adaptive Microinstruction Driven Architecture (AMIDAR) basiert. Dieser Prozessor wird bereits als Forschungsplattform zur Untersuchung und Entwicklung adaptiver Prozessor-Architekturen verwendet. Mittels eines konfigurierbaren Beschleunigers ist er in der Lage, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren und somit deren Ausführungs-Performance dynamisch zu erhöhen.

Gegenüber klassischen RISC-Prozessoren besteht ein AMIDAR-basierter Prozessor aus vier unterschiedlichen Arten von Komponenten: einer Token-Machine, verschiedenen funktionalen Einheiten (FUs), einem Token-Verteilungsnetzwerk sowie einer FU-Kommunikationsstruktur. Die Token-Machine ist eine spezielle FU, welche die Ausführungen der anderen FUs steuert. Dazu übersetzt sie die Instruktionen in einen Satz von Mikroinstruktionen, den sogenannten Tokens, und sendet diese über das Token-Verteilungsnetzwerk an die entsprechenden FUs. Die Tokens teilen einzelnen FUs mit, welche Operationen auf den Eingangsdaten ausgeführt werden und an welche FUs die Ergebnisse anschließend geschickt werden sollen. Nachdem eine Operation ausgeführt wurde, wird deren Ergebnis an die FU-Kommunikationsstruktur übergeben, damit es an die vorgegebene Ziel-FU weitergeleitet werden kann.

Für den Instruktionssatz, welcher durch den Java-Bytecode definiert ist, sind insgesamt sechs FUs mit bestimmten Funktionalitäten für den Java Prozessor entwickelt worden. Diese umfassen einen Frame Stack, einen Heap Manager, einen Thread Scheduler, einen Debugger, eine Integer-ALU und eine Floating-Point Unit. Mit diesen FUs kann der Prozessor bereits die SPEC JVM98 Benchmarks fehler-frei durchführen. Dies deutet darauf hin, dass er sich über eingebettete Software hinaus für ein breites Spektrum von Anwendungen einsetzen lässt.

Neben der Bytecode-Ausführung beinhaltet dieser Prozessor auch einige erweiterte Funktionen, welche seine Leistung und Nutzbarkeit deutlich verbessert haben. Zum Ersten enthält er einen Objekt-Cache basierend auf einer neuartigen Methode zur Generierung der Cache-Indizes, welche eine bessere durchschnittliche Trefferrate bietet, als die klassische XOR-basierte Methode. Zum Zweiten ist ein hardwarebasierter Garbage Collector in den Heap Manager integriert, welcher den durch den Garbage Collection Prozess verursachten Overhead erheblich reduzieren kann. Zum Dritten ist die Thread-Verwaltung ebenfalls komplett in Hardware umgesetzt und kann deshalb parallel mit der laufenden Anwendung durchgeführt werden. Außerdem ist ein Debugging Framework für den Prozessor entwickelt worden, welches mehrere mächtige Debugging-Funktionalitäten auf Hardware- und Software-Ebene bereitstellt.

#### Abstract

This thesis presents a Java processor based on the *Adaptive Microinstruction Driven Architecture* (AMI-DAR). This processor is intended as a research platform for investigating adaptive processor architectures. Combined with a configurable accelerator, it is able to detect and speed up hot spots of arbitrary applications dynamically.

In contrast to classical RISC processors, an AMIDAR-based processor consists of four main types of components: a token machine, functional units (FUs), a token distribution network and an FU interconnect structure. The token machine is a specialized functional unit and controls the other FUs by means of tokens. These tokens are delivered to the FUs over the token distribution network. The tokens inform the FUs about what to do with input data and where to send the results. Data is exchanged among the FUs over the FU interconnect structure.

Based on the virtual machine architecture defined by the Java bytecode, a total of six FUs have been developed for the Java processor, namely a frame stack, a heap manager, a thread scheduler, a debugger, an integer ALU and a floating-point unit. Using these FUs, the processor can already execute the SPEC JVM98 benchmark suite properly. This indicates that it can be employed to run a broad variety of applications rather than embedded software only.

Besides bytecode execution, several enhanced features have also been implemented in the processor to improve its performance and usability. First, the processor includes an object cache using a novel cache index generation scheme that provides a better average hit rate than the classical XOR-based scheme. Second, a hardware garbage collector has been integrated into the heap manager, which greatly reduces the overhead caused by the garbage collection process. Third, thread scheduling has been realized in hardware as well, which allows it to be performed concurrently with the running application. Furthermore, a complete debugging framework has been developed for the processor, which provides powerful debugging functionalities at both software and hardware levels.

# Contents

| 1 | Intr       | oduction                            | 1         |

|---|------------|-------------------------------------|-----------|

|   | 1.1        | Motivation                          | 1         |

|   | 1.2        | Research Goals                      | 1         |

|   | 1.3        | Thesis Outline                      | 3         |

| _ |            |                                     |           |

| 2 |            | nical Background                    | 4         |

|   | 2.1        | AMIDAR                              | 4         |

|   |            | 2.1.1 Overview                      | 4         |

|   | 0.0        | 2.1.2 ADLA                          | 5         |

|   | 2.2        |                                     | 7         |

|   |            | 2.2.1 Java in Embedded Systems      | 7         |

|   |            | 2.2.2 Concurrency                   | 8         |

|   | 2.3        | 5                                   | 12        |

|   |            | 5                                   | 12        |

|   |            | 5                                   | 13        |

|   |            | 0                                   | 15        |

|   |            | 0                                   | 20        |

|   |            |                                     | 24        |

|   | 2.4        | Priority Queue Architectures        | 28        |

| 3 | Dola       | ted Work                            | 33        |

| 3 | 3.1        |                                     | <b>33</b> |

|   | 3.2        |                                     | 35<br>35  |

|   | 3.2<br>3.3 | 5                                   | 33<br>37  |

|   | 3.3<br>3.4 | 8                                   | 37<br>40  |

|   | 3.4<br>3.5 |                                     | 40<br>44  |

|   | 5.5        |                                     | 44        |

| 4 | Imp        | ementation                          | 47        |

|   | 4.1        | Overview                            | 47        |

|   |            | 4.1.1 Processor Microarchitecture   | 47        |

|   |            | 4.1.2 Support for 64-Bit Operations | 49        |

|   |            | 4.1.3 Infrastructure                | 50        |

|   |            |                                     | 51        |

|   |            | 4.1.5 Executable Generation         | 52        |

|   |            | 4.1.6 System Boot                   | 53        |

|   | 4.2        | AMIDAR Executable Format            | 53        |

|   |            | 4.2.1 Layout                        | 53        |

|   |            | 4.2.2 Header                        | 54        |

|   |            | 4.2.3 Table Section                 | 55        |

|   |            | 4.2.4 Info Section                  | 60        |

|   |            | 4.2.5 Data Section                  | 61        |

|   |            |                                     | 63        |

|   |            |                                     | 67        |

|   | 4.3        |                                     | 68        |

|   |            |                                     | 69        |

|   |            | 0 1                                 | 72        |

|   |            | 1                                   | 72        |

|   |            |                                     | 74        |

|   |            |                                     | / T       |

|     |       | 4.3.5 FU Interfaces                               | 77        |

|-----|-------|---------------------------------------------------|-----------|

|     | 4.4   | Frame Stack                                       | 78        |

|     |       | 4.4.1 Datapath Components                         | 79        |

|     |       | 4.4.2 Execution of Tokens                         | 81        |

|     |       | 4.4.3 Generation of Root Set                      | 83        |

|     |       | 4.4.4 Overflow Handling                           |           |

|     | 4.5   | Heap Manager                                      | 84        |

|     |       | 4.5.1 Memory Layout                               |           |

|     |       | 4.5.2 Components of the Heap Manager              |           |

|     |       |                                                   | 93        |

|     |       | 4.5.4 Object Allocation                           |           |

|     |       | 4.5.5 Garbage Collection                          |           |

|     |       | 4.5.6 Wishbone Object Access                      |           |

|     | 4.6   | Thread Scheduler                                  |           |

|     |       | 4.6.1 Datapath Components                         |           |

|     |       | 4.6.2 Hardware-Software Interface                 |           |

|     |       | 4.6.3 Implementation of Thread Management         |           |

|     |       | 4.6.4 Implementation of Java Monitor Construct    |           |

|     |       | 4.6.5 Interrupt Handling                          |           |

|     | 4.7   | AMIDAR Debugging Framework                        |           |

|     |       | 4.7.1 Concept and Implementation                  |           |

|     |       | 4.7.2 Use Cases                                   |           |

|     |       | 4.7.3 Performance and Resource Usage              |           |

|     |       |                                                   |           |

| 5   | Eva   | luation                                           | 165       |

|     | 5.1   | Benchmarks                                        | 165       |

|     | 5.2   | Performance                                       | 165       |

|     | 5.3   | Object Cache                                      |           |

|     | 5.4   | Garbage Collector                                 |           |

|     |       | 5.4.1 Functional Verification                     | 168       |

|     |       | 5.4.2 Overhead Analysis                           |           |

|     | 5.5   | Thread Scheduler                                  |           |

|     |       | 5.5.1 Functional Verification                     | 170       |

|     |       | 5.5.2 Overhead Analysis                           |           |

|     | 5.6   | Resource Usage                                    | 175       |

| _   | -     |                                                   |           |

| 6   |       |                                                   | 176       |

|     | 6.1   | 5                                                 | 176       |

|     | 6.2   | Future Work                                       | 177       |

| Di  | hlioa | raphy                                             | 179       |

| DII | bilog | гарпу                                             | 1/9       |

| Α   | Add   | itional Measurement Results                       | XIV       |

| P   | E11 / | Devetions                                         |           |

| В   |       |                                                   |           |

|     | B.1   |                                                   | XIV       |

|     | B.2   | Frame Stack Operations    Heap Manager Operations |           |

|     | B.3   |                                                   | X X I I I |

# List of Figures

| 2.1  | General model                                                 | 4   |

|------|---------------------------------------------------------------|-----|

| 2.2  | Meta-table and token-matrix                                   | 7   |

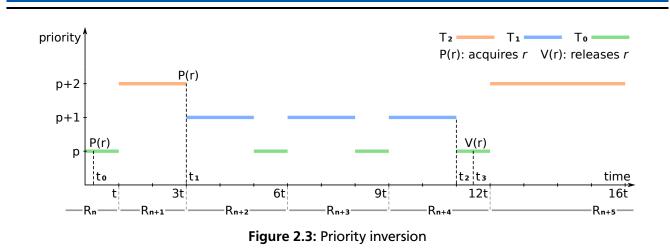

| 2.3  | Priority inversion                                            | 23  |

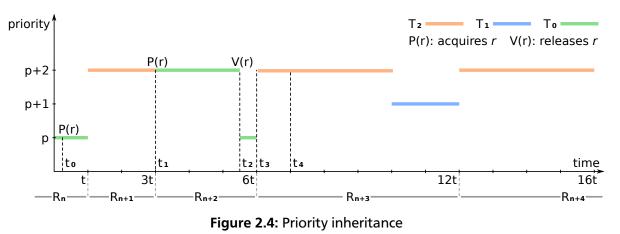

| 2.4  | Priority inheritance                                          | 24  |

| 2.5  | Binary tree of comparators priority queue                     | 29  |

| 2.6  | Shift register priority queue                                 | 29  |

| 2.7  | Shift register block                                          | 30  |

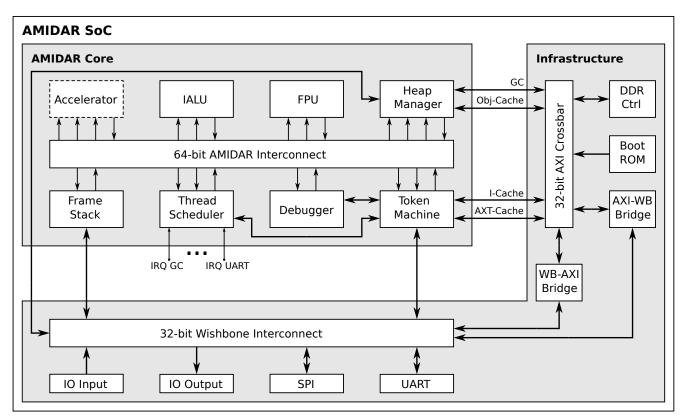

| 2.8  | Systolic array priority queue                                 | 31  |

| 2.9  | Systolic array block                                          | 31  |

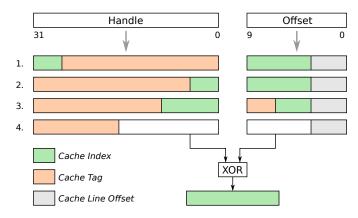

| 3.1  | Object cache index generation schemes                         | 36  |

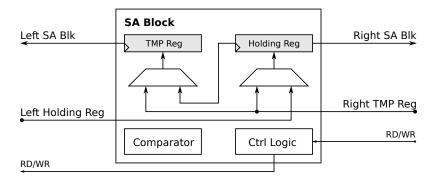

| 4.1  | AMIDAR SoC                                                    | 47  |

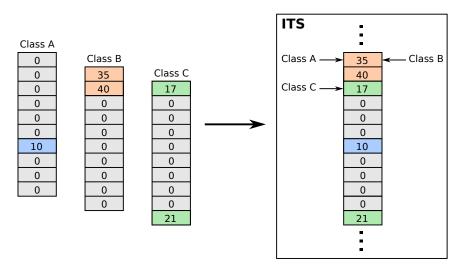

| 4.2  | Merging multiple interface tables                             |     |

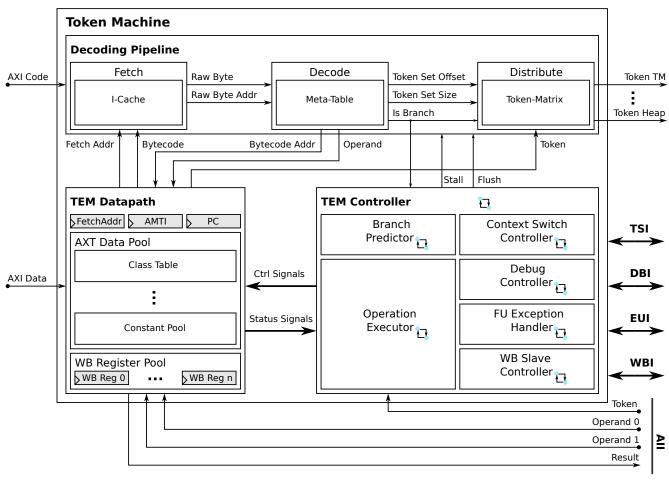

| 4.3  | Token machine overview                                        | 68  |

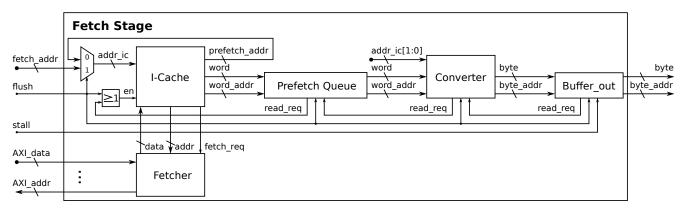

| 4.4  | Fetch stage                                                   | 69  |

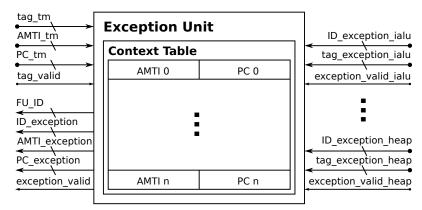

| 4.5  | Exception unit                                                | 76  |

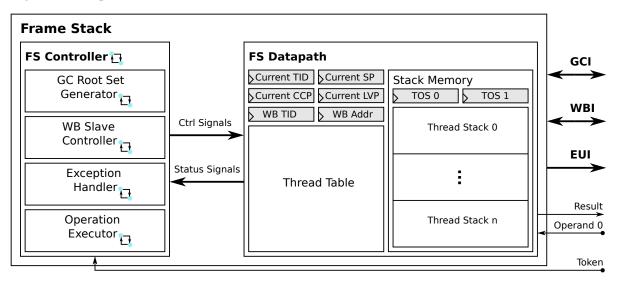

| 4.6  | Frame stack overview                                          | 79  |

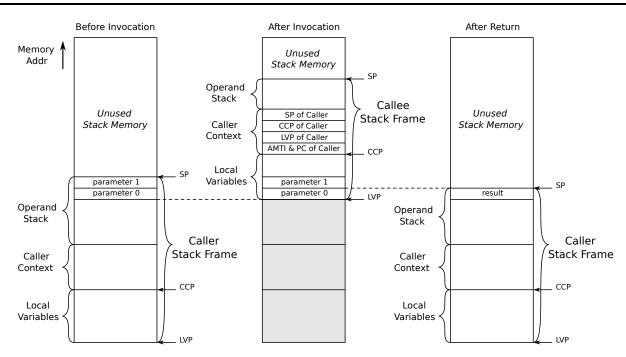

| 4.7  | Stack frame creation and elimination                          | 83  |

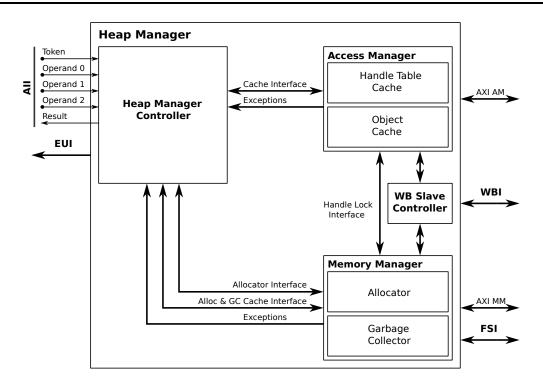

| 4.8  | Heap manager overview                                         | 85  |

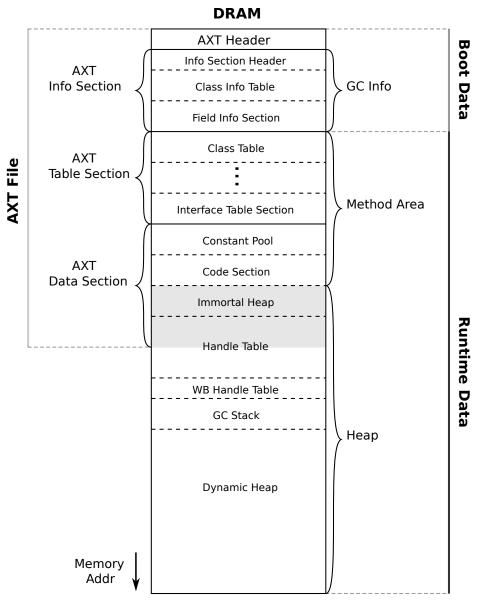

| 4.9  | Memory layout                                                 | 86  |

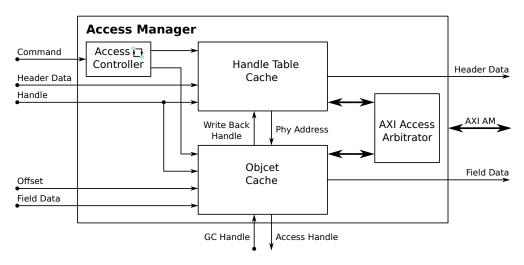

| 4.10 | Access manager overview                                       | 89  |

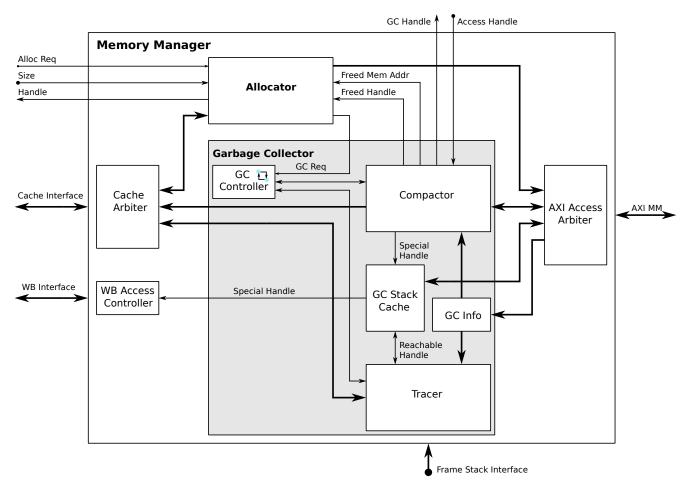

| 4.11 | Memory manager overview                                       | 91  |

| 4.12 | Set index generation using fixed scheme                       | 94  |

| 4.13 | Set index generation using dynamic scheme                     | 95  |

|      | Miss rates for all applications with all cache configurations |     |

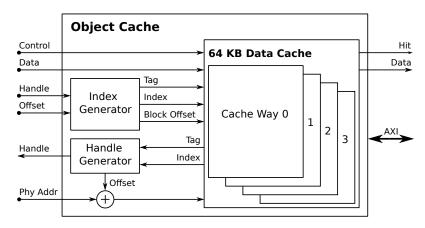

| 4.15 | Object cache                                                  | 100 |

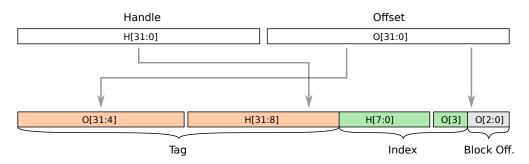

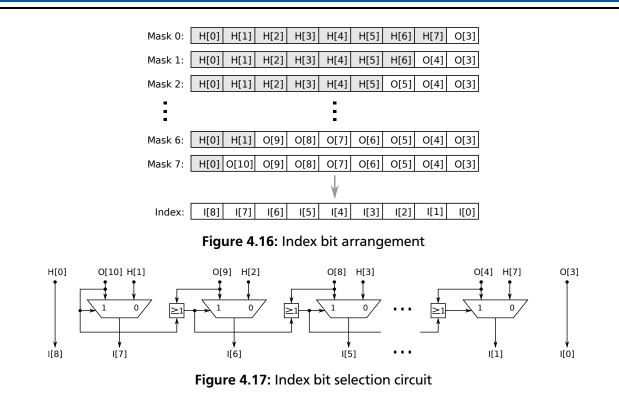

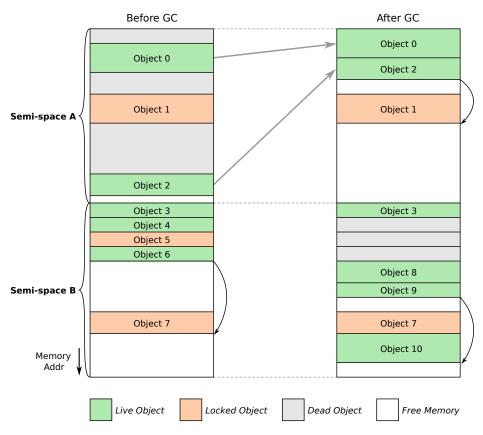

| 4.16 | Index bit arrangement                                         | 101 |

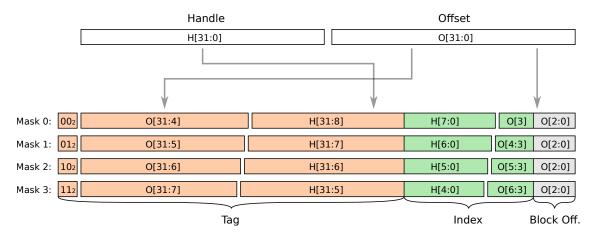

| 4.17 | Index bit selection circuit                                   | 101 |

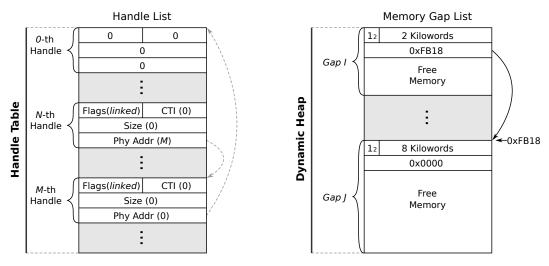

| 4.18 | Handle and memory gap lists                                   | 101 |

| 4.19 | Internal object representation                                | 103 |

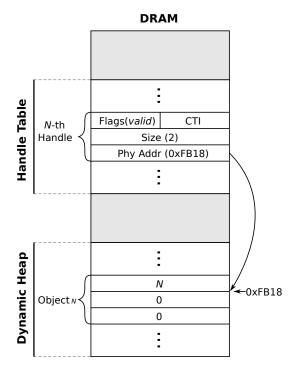

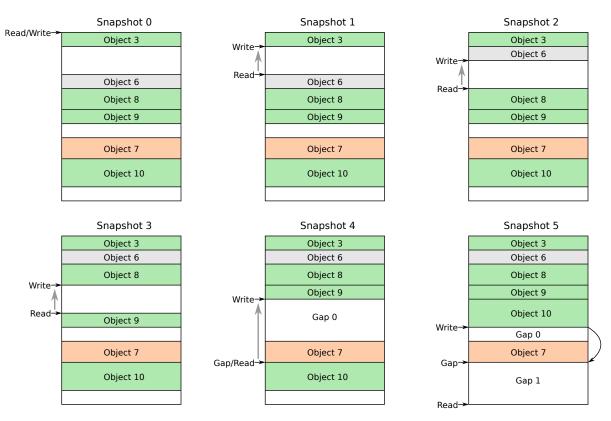

| 4.20 | Snapshots of the dynamic heap                                 | 105 |

| 4.21 | Snapshots of the compaction space                             | 115 |

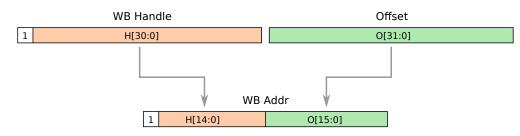

| 4.22 | Generation of WB address                                      | 117 |

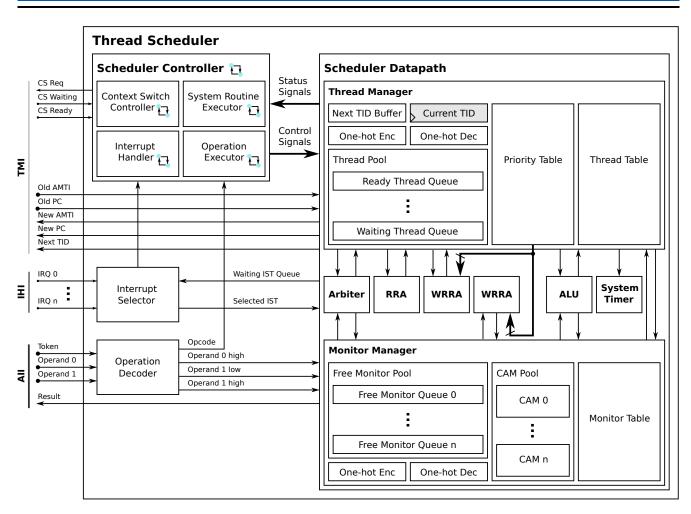

| 4.23 | Thread scheduler overview                                     | 118 |

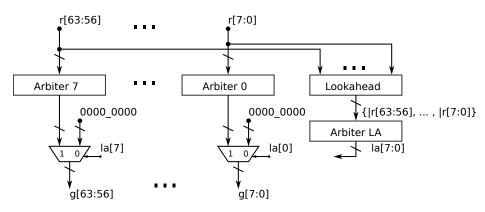

| 4.24 | Basic arbiter architecture                                    | 119 |

| 4.25 | Extended arbiter architecture                                 | 119 |

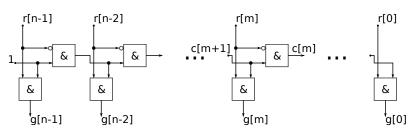

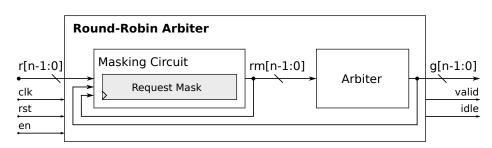

| 4.26 | Round-robin arbiter                                           | 121 |

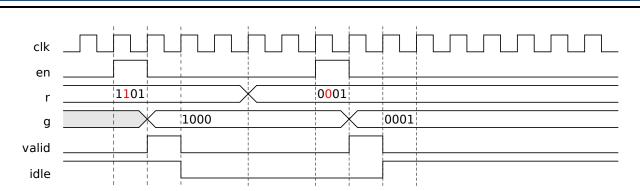

| 4.27 | Timing diagram for the second RRA sample round                | 122 |

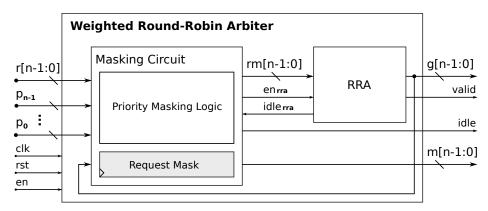

| 4.28 | Weighted round-robin arbiter                                  | 122 |

| 4.29 | Priority masking logic of the WRRA circuit                    | 123 |

| 4.30 | Timing diagram for the second WRRA sample round               | 125 |

| 4.31 | Thread queue                                                  | 126 |

| 4.32 | Priority table                                                | 127 |

|      | WRRA-PQ                                                       |     |

| 4.34 | Circuit for sharing a WRRA-PQ among monitors                  | 129 |

| 4.35 | Creation and termination of a thread                          | 135 |

|      | Thread state transitions                                      |     |

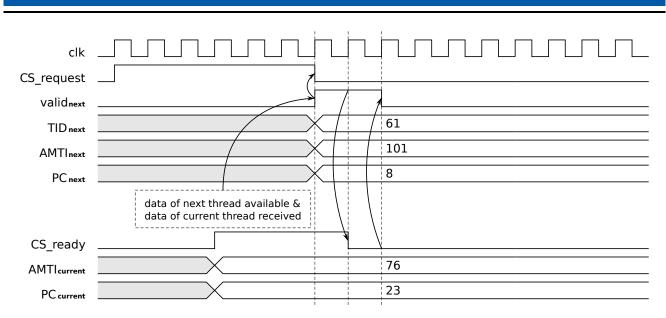

| 4.37 | Handshaking protocol between the scheduler and token machine  | 145 |

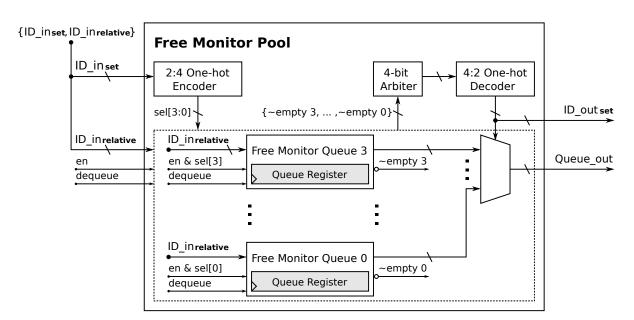

|      | Free monitor pool                                             |     |

|      |                                                               |     |

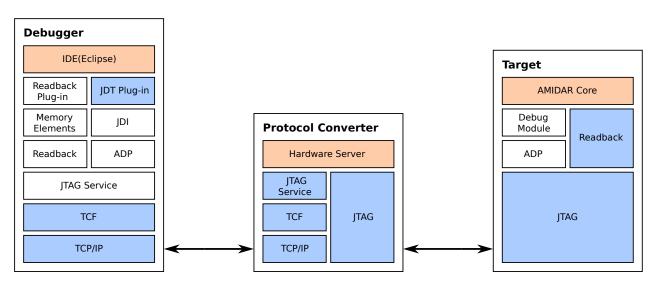

| 4.39 | Concept of the AMIDAR debugging framework | 157 |

|------|-------------------------------------------|-----|

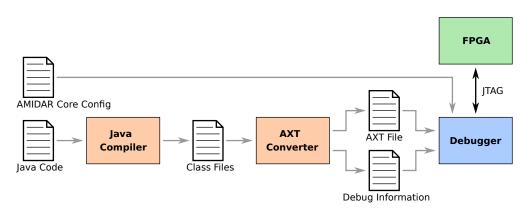

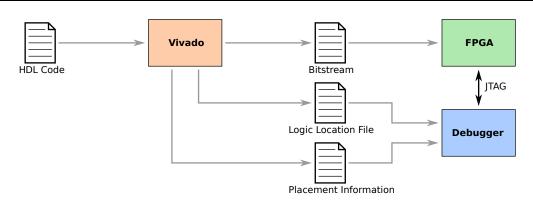

|      | Tool flow for Java debugging              |     |

|      | Tool flow for hardware debugging          |     |

| 4.42 | Debugging the software in Eclipse         | 162 |

| 4.43 | Activating exception breakpoints          | 162 |

| 4.44 | Inspecting hardware memory elements       | 163 |

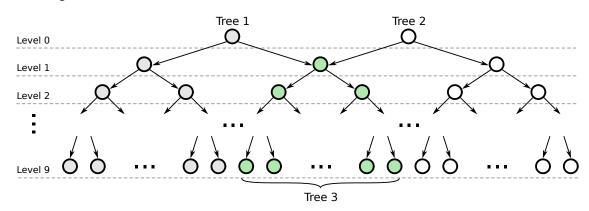

| 5.1  | Object trees sharing a common subtree     | 169 |

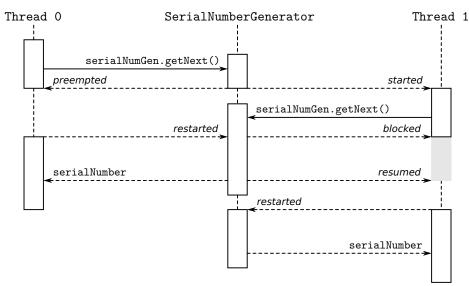

| 5.2  | Synchronizing two threads                 | 172 |

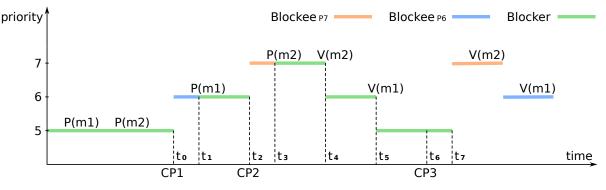

| 5.3  | Priority changes of the blocker thread    | 173 |

# List of Tables

| 2.1  | Peak number of active locks                                                    | 28  |

|------|--------------------------------------------------------------------------------|-----|

| 3.1  | Overview of selected Java processors                                           |     |

| 4.1  | Header of an AXT file                                                          |     |

| 4.2  | Attributes of a class                                                          | 56  |

| 4.3  | Attributes of an array type                                                    | 56  |

| 4.4  | Attributes of a method                                                         | 58  |

| 4.5  | Attributes of an exception handler                                             | 58  |

| 4.6  | Header field of an object                                                      | 63  |

| 4.7  | Quick bytecodes of ldc, ldc_w and ldc2_w                                       | 64  |

| 4.8  | Quick bytecodes of getstatic and putstatic                                     | 64  |

| 4.9  | Quick bytecodes of getfield and putfield                                       | 65  |

| 4.10 | Quick bytecodes of invoke-bytecodes                                            | 66  |

|      | Quick bytecodes of object-related bytecodes                                    | 66  |

| 4.12 | Quick bytecodes of array-related bytecodes                                     | 67  |

|      | Measurement results for analyzing the AXT limitations                          | 67  |

| 4.14 | Compactness comparison among different formats                                 | 68  |

| 4.15 | Entry types of the stack memory                                                | 80  |

| 4.16 | Pointer registers of the current frame                                         | 80  |

| 4.17 | Bit probabilities of the individual index bits                                 | 96  |

| 4.18 | Average miss rates for all cache configurations                                | 98  |

| 4.19 | Percentages of heap accesses to objects/arrays with size less than eight words | 100 |

| 4.20 | Header flags for memory management                                             | 107 |

|      | Comparison of 64-bit arbiters with and without lookahead                       |     |

| 4.22 | Two sample arbitration rounds of a 4-bit RRA                                   | 121 |

| 4.23 | Two sample arbitration rounds of a 4-bit WRRA                                  | 124 |

| 4.24 | Operations of the ALU in the thread scheduler                                  | 130 |

| 4.25 | Operations supporting thread-specific methods                                  | 133 |

| 4.26 | Operations supporting synchronization-specific methods                         | 133 |

| 4.27 | Operations supporting interacting with the thread scheduler                    | 134 |

| 4.28 | Thread attributes                                                              | 138 |

| 4.29 | Monitor attributes                                                             | 147 |

| 4.30 | Runtime of the debugging framework for certain actions                         | 164 |

| 5.1  | Evaluation benchmarks                                                          | 165 |

| 5.2  | Standard AMIDAR system configuration                                           | 166 |

| 5.3  | Execution time and comparison                                                  | 166 |

| 5.4  | Percentages of execution time used for copying arrays                          | 167 |

| 5.5  | Miss rate comparison                                                           | 168 |

| 5.6  | Measurement results of db                                                      | 170 |

| 5.7  | Average overheads caused by garbage collection                                 | 170 |

| 5.8  | Processor times assigned to threads with different priorities                  | 171 |

| 5.9  | Overheads caused by context switching                                          | 174 |

| 5.10 | Resource usage of AMIDAR core                                                  | 175 |

| 5.11 | Resource distribution among FUs inside AMIDAR core                             | 175 |

| A.1  | Measurement results for each benchmark                                         | XIV |

|      |                                                                                |     |

# List of Abbreviations

| ADLA   | Abstract Description Language for AMIDAR Processors |

|--------|-----------------------------------------------------|

| ADP    | AMIDAR Debug Protocol                               |

| AMAT   | Average Memory Access Time                          |

| AMIDAR | Adaptive Microinstruction Driven Architecture       |

| AMP    | Active Memory Processor                             |

| AMTI   | Absolute Method Table Index                         |

| API    | Application Programming Interface                   |

| AST    | Abstract Syntax Tree                                |

| AXI    | Advanced eXtensible Interface                       |

| AXT    | AMIDAR Executable                                   |

| BNF    | Backus-Naur Form                                    |

| BRAM   | Block Random-Access Memory                          |

| BTC    | Binary Tree of Comparators                          |

| CAM    | Content-Addressable Memory                          |

| CBT    | Complete Binary Tree                                |

| ССР    | Caller Context Pointer                              |

| CDC    | Connected Device Configuration                      |

| CGMT   | Coarse Grained Multithreading                       |

| CGRA   | Coarse Grained Reconfigurable Array                 |

| CLDC   | Connected Limited Device Configuration              |

| СТ     | Class Table                                         |

| CTI    | Class Table Index                                   |

| DEX    | Dalvik Executable                                   |

| DMA    | Direct Memory Access                                |

| DMS    | Dynamic Mask Selection                              |

| DRAM   | Dynamic Random-Access Memory                        |

| EDF    | Earliest Deadline First                             |

| ETS    | Exception Table Section                             |

| EUI    | Exception Unit Interface                            |

| FIFO   | First In, First Out                                 |

| FLC    | Flat-Lock                                           |

| FPGA   | Field Programmable Gate Array                       |

| FSM    | Finite State Machine                                |

| FU     | Functional Unit                                     |

| FU-NI  | Functional Unit Native Interface                    |

| GC     | Garbage Collection                                  |

| GCMM   | Garbage-Collected Memory Module                     |

| GCU    | Garbage Collector Unit                              |

| GP     | Guaranteed Percentage                               |

| HDL    | Hardware Description Language                       |

| ICE    | In-Circuit Emulation                                |

| IDE    | Integrated Development Environment                  |

| IIS    | Implemented Interfaces Section                      |

| IMT    | Interleaved Multithreading                          |

| IP     | Intellectual Property                               |

| IRQ    | Interrupt Request                                   |

| -      |                                                     |

| ISA    | Instruction Set Architecture        |

|--------|-------------------------------------|

| IST    | Interrupt Service Thread            |

| ITS    | Interface Table Section             |

| J2ME   | Java 2 Micro Edition                |

| J2SE   | Java 2 Standard Edition             |

| Jamuth | Java Multithreaded Processor        |

| JDI    | Java Debug Interface                |

| JDT    | Java Development Tools              |

| JOP    | Java Optimized Processor            |

| JRE    | Java Runtime Environment            |

| JTAG   | Joint Test Action Group             |

| JVM    | Java Virtual Machine                |

| LIFO   | Last In, First Out                  |

| LILT   | Logically-Indexed, Logically-Tagged |

| LSB    | Least Significant Bit               |

| LSTF   | Least Slack Time First              |

| LUT    | Lookup Table                        |

| LVP    | Local Variables Pointer             |

| MDM    | MicroBlaze Debug Module             |

| MIG    | Memory Interface Generator          |

| MLFQ   | Multilevel Feedback Queue           |

| MLQ    | Multilevel Queue                    |

| MMU    | Memory Management Unit              |

| MSB    | Most Significant Bit                |

| OLAT   | Ordered List of Array Types         |

| OLI    | Ordered List of Interfaces          |

| OSM    | Object Space Manager                |

| PQ     | Priority Queue                      |

| RANSAC | Random Sample Consensus             |

| RM     | Rate Monotonic                      |

| RMTI   | Relative Method Table Index         |

| RR     | Round-Robin                         |

| RRA    | Round-Robin Arbiter                 |

| RTM    | Real-Time Task Manager              |

| RTOS   | Real-Time Operating System          |

| RTU    | Real-Time Unit                      |

| SA     | Systolic Array                      |

| SHAP   | Secure Hardware Agent Platform      |

| SMT    | Simultaneous Multithreading         |

| SoC    | System-on-Chip                      |

| SP     | Stack Pointer                       |

| SR     | Shift Register                      |

| TCF    | Target Control Framework            |

| TEM    | Token Execution Module              |

| TLB    | Translation Lookaside Buffer        |

| TMT    | Temporal Multithreading             |

| WB     | Wishbone                            |

| WCET   | Worst Case Execution Time           |

| WRRA   | Weighted Round-Robin Arbiter        |

|        |                                     |

#### 1 Introduction

#### 1.1 Motivation

With the continuous advancement of the semiconductor manufacturing technology, more and more transistors can be integrated into a single chip on the one hand. On the other hand, however, exponentially increased mask costs make it impossible to produce a small quantity of chips for an application-specific design. Consequently, merely general-purpose processors that are capable of running various applications are allowed to be mass-produced. Most of the time, such a processor can only achieve a suboptimal performance when running an application in comparison with a dedicated integrated circuit designed for that application. Aimed at addressing this issue, reconfigurable computing in different granularities has been proposed [114]. *Field programmable gate arrays* (FPGAs) and *coarse grained reconfigurable arrays* (CGRAs) are the major technologies that are currently adopted for this purpose.

One of the primary advantages of FPGAs is that logic resources can be reconfigured at the gate level. This fine-grained reconfigurability enables individual circuits to be realized, which accomplish required behaviors of different applications. However, this high flexibility comes with the disadvantage of the large amount of configuration information. For this reason, reconfiguring FPGAs takes a lot of time. In contrast to FPGAs, CGRAs provide the reconfigurability solely at the word level, which reduces the amount of configuration information dramatically and therefore results in a significant increase in reconfiguration efficiency.

Both of these technologies have one drawback in common. They require a major restructuring and/or rewriting of the application code. For FPGAs, this means that time-consuming code parts have to be realized using a *hardware description language* (HDL) like Verilog, while for CGRAs, some code structures have to be redesigned to fit into the structure of the underlying hardware. Often only a complete new development will reach the full potential of the adopted implementation technology. This causes not just a huge development overhead but also requires the expert-level knowledge about the corresponding technology.

The aim of our ongoing research is to provide a new processor paradigm, namely the AMIDAR class of processors [38]. AMIDAR is a general-purpose processor model that can be applied to various instruction sets and microarchitectures. This model allows a processor based on it to autonomously adapt to requirements of different applications, achieving a truly dynamic adaptivity. So far, our research has been conducted using the simulator of an AMIDAR-based Java processor. The research results show that the dynamic adaptivity can be best achieved by combining the processor with a CGRA which serves as a configurable accelerator [32]. This approach requires an adaption program to be executed in parallel with a running application, which generates configuration information for the CGRA at runtime. The significant performance increases observed when running real-world programs on the simulated processor indicate the great potential of the AMIDAR concept and have become the driving force that leads the research into the next phase: hardware implementation.

#### 1.2 Research Goals

The key goal of this thesis is to develop an AMIDAR-based Java processor in the form of a soft *intellectual property core* (IP-core) for FPGAs. In the following, this processor and its simulated counterpart are

referred to as simply the AMIDAR processor and the AMIDAR simulator. The AMIDAR processor targets the embedded domain just like all preexisting Java processors. However, its main focus is generalpurpose computation rather than the improvement of real-time capability, which most preexisting Java processors attempt to address. The reason for this design decision is that the AMIDAR processor must be able to execute the adaption program that performs sophisticated analysis and scheduling algorithms on the hot spots of a running application. This program has been implemented and validated on the top of the AMIDAR simulator without concern for any constraints that could occur in a hardware processor. As a result, it is much more complex than a typical embedded software. The current version of the program consists of about hundred Java classes. Depending on the complexity of the running application, it could cause a large runtime memory footprint. Therefore, to support a broad variety of applications and adaption algorithms, the AMIDAR processor should satisfy the following functional requirements:

- It can store Java classes efficiently.

- It can execute multiple threads correctly.

- It can perform garbage collection effectively.

To determine if and how well the requirements above are met, the resulting hardware implementation needs to be tested and evaluated using a standard *Java virtual machine* (JVM) benchmark suite. Besides fulfilling the fundamental requirements, this thesis also aims to implement several enhanced features that increase the performance and usability of the AMIDAR processor, including:

• An efficient object cache

Java is an object-oriented language. Thus, almost all operations need to be performed on objects. Since a huge number of objects can be created by running a Java application, objects typically reside in the external memory. Exploiting an object cache will avoid the high access latency introduced by the external memory and also benefit from the object-based memory access model of Java, increasing the performance of the entire system.

• Hardware-based system services

In a classical JVM, system services such as garbage collection and thread scheduling must share the processor with the running application, which causes performance overhead and additional memory usage. Employing dedicated hardware modules, these services can be performed concurrently with the execution of the application. This kind of parallelism is one of the key benefits that FPGAs provide and thus should be utilized.

• Built-in debugging support

Debugging is a major challenge in developing a hardware system. Hence, one of the main goals of the AMIDAR processor is to enable and simplify debugging. Many modern FPGAs allow on-chip data to be read out at runtime, which can be exploited to realize a fine-grained hardware debugger.

# 1.3 Thesis Outline

The remaining chapters of this thesis are organized as follows. Chapter 2 provides the background information on the AMIDAR concept, the Java programming language, the Java runtime system and hardware architectures proposed for scheduling threads. Chapter 3 presents the related work, including different Java processors, object caches, hardware-based garbage collectors and thread schedulers as well as several hardware debuggers. In Chapter 4, the implementation of the AMIDAR processor is described in detail. This chapter is centered around the executable format designed for the AMIDAR processor, the bytecode execution and the realization of the enhanced features mentioned above. Then, with regard to performance and size, the AMIDAR processor is evaluated in Chapter 5. Finally, Chapter 6 presents conclusions and an outlook onto future work.

#### 2 Technical Background

## 2.1 AMIDAR

## 2.1.1 Overview

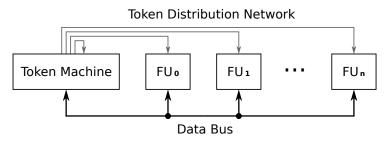

AMIDAR [38] is a general-purpose processor model for tackling today's and tomorrow's problems in the field of embedded systems. It has already been the host of some interesting research, including object oriented microarchitecture, *synthilation* [43] and CGRA-based *online synthesis* [32]. This model contains four key parts: a *token machine*, a *token distribution network*, a *data bus* and several specific functional units (FUs) such as integer ALU or heap manager. Each FU has at most one output port and an arbitrary number of input ports. Data is passed between the FUs over the data bus, as shown in Figure 2.1.

Figure 2.1: General model

The centerpiece of the AMIDAR model is the token machine that must be included in every AMIDAR implementation. It fetches instructions and decodes them into tokens for the FUs. A token can be considered as a microinstruction that needs to be executed by some specific FU. It is assigned an identifier called tag that helps determine if all operands required by the token have arrived at the data input ports of the FU. Tokens are sent over the token distribution network to different FUs. An FU will start executing an incoming token as soon as all necessary operands with the same tag as that of the token have been delivered to it over the data bus. Tokens that do not require input data can be executed immediately. After the operation has been completed, its result is transferred to a waiting FU and used as an operand for the current token of this FU. To ensure a correct operand match, the result must be assigned the identical tag as that of the token of the waiting FU.

A token can be formally defined as a 5-tuple:  $T = \{UID, OP, TAG, DP, INC\}$ . *UID* identifies which FU should execute this token. *OP* specifics the concrete operation. *TAG* serves as the identifier of the token and enables a precise operand match as mentioned above. *DP* describes the destination address of the result of the token. It contains the *UID* and a port number of the destination FU. *INC* is a flag and controls the generation of the tag of the result. If it is asserted, the result is tagged using *TAG* + 1; otherwise, *TAG*.

One of the major advantages of the AMIDAR model is that it supports simultaneous execution of instructions automatically, because their tokens can be executed on various FUs in parallel. These tokens can be clearly separated from each other by simply assigning them different tags. Also, this model allows integration of new FUs and instructions using these FUs into an existing AMIDAR processor. To meet this goal, only a small part of the token machine of the processor needs to be reconfigurable to

support inserting the token sets of the new instructions and attaching the new FUs to the token machine. Furthermore, the AMIDAR model decouples different FUs of a processor by exploiting a central bus. Each FU can be optimized separately or be customized to the end user's usage patterns, without having to consider how the other FUs are implemented. Because of this, different FUs might even be driven by various clock signals. This provides maximum design flexibility to a developer.

### 2.1.2 ADLA

As mentioned above, AMIDAR is a general-purpose processor model that can be applied to various *instruction set architectures* (ISAs). Since designing a token set for each instruction of a target ISA is time-consuming and error-prone, the *abstract description language for AMIDAR processors* (ADLA) and the associated compiler were developed to assist with the design process. This language abstracts away unnecessary low-level details and allows a designer to focus on the syntax and semantics of every instruction. Its compiler converts the ADLA description of an instruction set to a binary representation. Below, ADLA is briefly described based on a simple example.

#### ADLA Description of Java Bytecode iadd

This bytecode adds two 32-bit integers on the top of the operand stack and then pushes the result back onto the stack (for more details about the Java memory model, see Section 2.3.1). As Listing 1 illustrates, the ADLA description of an instruction begins with the mnemonic of the instruction (line 0). The operations that need to be performed by different FUs upon occurrence of the instruction are defined in the following curly braces by means of tokens (line 2-5).

#### Listing 1: Token set of iadd

```

0: iadd

1: {

2: T(framestack, POP32, ialu.1),

3: T(framestack, POP32, ialu.0),

4: T(ialu, IADD, framestack.0)++;

5: T(framestack, PUSH32)

6: }

```

The syntax of token definition in ADLA can be formally described by using *Backus-Naur form* (BNF) as follows:

token ::=  $T (FU_{exe}, operation[, FU_{dest}.port])[++]$

Identifier *T* indicates the beginning of a token definition.  $FU_{exe}$  and *operation* are necessary parts of the definition, which determine the FU executing the token and the concrete operation.  $FU_{dest}$  and *port* are optional and required only if *operation* has a result.  $FU_{dest}$  corresponds to the FU that the result is sent to and *port* defines the data input port of  $FU_{dest}$  that receives the result. If the tag of the result needs to be incremented, the token ends with ++ in addition.

In the example above, the first two tokens are executed by an FU called frame stack that manages the operand stack of each Java thread. Both of them perform the same operation, namely popping the 32-bit top value from the operand stack of the current thread and sending it to the integer-ALU. The only difference between them is the port of the integer-ALU adopted to receive their results. Since *POP*32 does not require any operand, these two tokens may have the same tag without causing any operand mismatch. Their results and the third token are also assigned this tag so that the integer-ALU can determine whether both operands of IADD have arrived. The result of IADD is returned to the frame stack and then used as the operand of the last token. To indicate that this operand belongs to the last token rather than the first two that are also executed by the frame stack, a different tag needs to be assigned to it. This is achieved by inserting ++ at the end of the third token. Accordingly, the tag used by the last token also needs to be incremented to guarantee a correct operand match. For this purpose, the last token is separated from the third one by using a semicolon. In contrast, tokens with the same tag are separated by commas, like the former three ones in this example.

### **Compilation of ADLA Description**

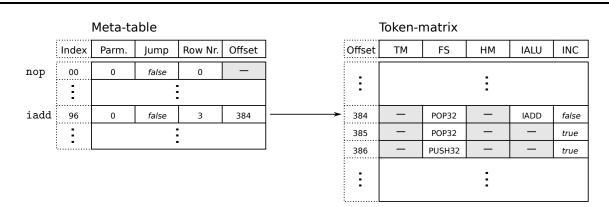

After all instructions of a target architecture have been described by using ADLA, an equivalent inmemory representation is generated by the ADLA compiler automatically. This representation consists of two parts: a *meta-table* and a *token-matrix*. The former keeps the fundamental information about the instructions and the latter saves their token sets.

The meta-table contains a single entry for each instruction, which is indexed by the opcode of the instruction. For example, in the context of Java, the meta-information of **iadd** is stored in the 96th entry because the opcode of **iadd** is equal to 96. The meta-information of an instruction includes:

- The number of its parameters.

- A flag indicating if the instruction performs a jump operation.

- The number of rows used to save its tokens in the token matrix.

- The offset of its token set inside the token matrix.

Each column of the token-matrix corresponds to an FU and each row contains the tokens of a token set, which can be delivered to different FUs with the same tag. This implies that multiple tokens which are defined sequentially in a token set can be sent to the corresponding FUs concurrently. However, a single row does not always include a token for every FU. Therefore, each cell of the matrix has a flag indicating whether it holds a valid token entry or not. Also, there is an additional flag for every row. If this flag is asserted, the tag of the tokens held in the next row needs to be incremented; otherwise, the tag remains unchanged.

Assume that some customized version of the AMIDAR processor is solely composed of a token machine (TM), a frame stack (FS), a heap manager (HM) as well as an integer-ALU (IALU). Figure 2.2 illustrates a snapshot of the meta-table and token-matrix generated for this processor. To simplify the representation, this snapshot only shows the tokens defined for **iadd**. As can be seen in the meta-table, this bytecode neither has any parameter nor executes a jump operation. Its tokens are stored in a total of three rows in the token-matrix (row 384-386).

Row 384 of the token-matrix contains two tokens of **iadd** because they have the same tag and are distributed to various FUs. Although the second token executed by the frame stack, which is stored in

Figure 2.2: Meta-table and token-matrix

row 385 also has this tag, it cannot be sent with the first one together, since the token machine can only deliver one token to each FU at a time. The tag of the fourth token in row 386 is incremented by asserting the INC-flag of row 385 to ensure a correct operand match as described above. Note that the INC-flag of the last row of a token set is always asserted to clearly separate the current token set from the next one in the token-matrix.

# 2.2 Java

# 2.2.1 Java in Embedded Systems

Java is one of the most popular programming languages in the world. Its usage spans a broad range of areas, from the development of server-side software to the creation of Android applications. Even in the field of embedded systems, where C is traditionally considered as the dominant language, Java is becoming increasingly attractive for the following reasons:

- Java is a simple object-oriented language. Peripherals and sensors can be represented in a straightforward manner by means of objects.

- Java programs are highly portable. Classes can be shared among different devices without the need to recompile them.

- Java is equipped with a rich set of libraries. Exploiting the *application programming interfaces* (APIs) provided by these libraries, development productivity can be greatly increased.

- Java supports multi-threading at the language level. Parallel activities of various peripherals can be easily modeled with threads.

- Java is safer and more reliable than C. Safety from the beginning has been one of the key goals of Java. To meet this goal, Java provides multiple mechanisms. First, it performs strong type checking at both compile time and runtime. Second, objects are accessed through references instead of error-prone pointers. Third, memory management in Java is fully automatic, including object allocation, initialization and reclamation. Also, the built-in exception handling reports errors explicitly, which simplifies debugging significantly.

• There is a worldwide population of Java developers that have trained in different domains. Their programming skills and experience can be utilized in the field of embedded systems directly.

To satisfy requirements from different application areas, various *Java runtime environments* (JREs) are available. For example, *Java Platform, Standard Edition* (Java SE) targets desktop and server class computers, while *Java Platform, Micro Edition* (Java ME) is aimed at headless embedded systems on devices with one megabyte or less of memory. From Java version 1.2 to 1.4, these JREs are named as *Java 2 Standard Edition* (J2SE) and *Java 2 Micro Edition* (J2ME) respectively. J2ME includes two further configurations defined to classify embedded systems at a fine-grained level, namely *Connected Device Configuration* (CDC) and *Connected Limited Device Configuration* (CLDC). Such configurations are actually the specifications for the Java runtime systems that a J2ME device must support. CLDC was designed for devices with 160 KB to 512 KB total memory and has been chosen as the specification for the vast majority of preexisting Java processors.

### 2.2.2 Concurrency

Java is an explicitly multi-threaded language. This section introduces the thread and synchronization models of Java briefly. In addition, several relevant Java methods used to develop multi-threaded programs are also described below.

#### **Thread Model**

Java supports multi-threading at the language level directly. For creating threads and synchronizing their executions, Java provides multiple API methods. Using these methods, programmers can generate a new thread instance, set its attributes (e.g. its priority) and define the task run by it. Once a thread is started, the Java runtime system takes over responsibility for scheduling the execution of the thread regarding its attributes.

The scheduling model of Java is preemptive, which means that the runtime system assigns each thread a time-slice to execute its task, interrupts the execution after the expiration of the time-slice and context switches to another thread. This process is repeated periodically until all threads have finished their tasks. In this way, different tasks can be performed simultaneously (more precisely, pseudo-simultaneously), which provides two major advantages for program design and development.

The first advantage is speeding up the execution of multiple tasks on a single processor system. This may sound a little counterintuitive at first, especially when considering the overhead caused by context switches. However, a key point is that an I/O operation often takes much more time than a context switch. Without using multiple threads, the program blocks during the entire I/O process. In contrast, it can execute further, if other threads are available, which perform nonblocking tasks.

Another advantage as a direct consequence of the first one is the improvement of the responsiveness of a program. As mentioned, the AMIDAR processor is intended to be used in the field of embedded systems. Such a system typically includes a set of peripherals that operate at different speeds for various purposes. If the system needs to check the status of each of its peripherals in a round-robin fashion and then executes some specific operation on the corresponding peripheral according to the check result, it cannot respond to a request from any of other peripherals before the current operation is complete. In general, the request of an external device is sent to a processor in the form of an interrupt. Using a dedicated *interrupt service thread* (IST) for each peripheral, the system can handle requests from external devices as desired, achieving the maximum responsiveness. To meet this goal, the interrupt handling model of the AMIDAR processor has been integrated into the thread model of Java completely.

## Synchronization Model

Since multiple threads may share common data or resources, Java employs a synchronization mechanism known as *monitor* for the purpose of thread-safety. Every object is associated with a single monitor that ensures the mutually exclusive access to the object to prevent collisions over common resources. Java provides built-in support for monitor in terms of the **synchronized** keyword that can be used on both methods and instruction sequences called critical sections. At the source code level, there is no difference between a synchronized method and a critical section from the aspect of semantics. For example, the codes shown in Listing 2 and 3 perform exactly the same operation. However, the Java compiler treats them differently, which is illustrated in Listing 4 and 5.

#### Listing 2: Synchronized method

```

private int cnt = 0;

public synchronized void inc() {

cnt++;

}

```

#### Listing 4: Bytecodes of synchronized method

| //                         | 0:                         | aload_0              |      |  |

|----------------------------|----------------------------|----------------------|------|--|

| //                         | 1:                         | dup                  |      |  |

| //                         | 2:                         | astore_1             |      |  |

| //                         | 3:                         | monitore             | nter |  |

| 0:<br>1:<br>2:<br>5:<br>6: | al<br>du<br>ge<br>ic<br>ia | tfield<br>onst_1     | #12  |  |

| 7.                         | pu                         | LITEIU               | #12  |  |

|                            |                            | aload_1<br>monitore: | xit  |  |

#### Listing 3: Critical section

```

private int cnt = 0;

public void inc() {

synchronized(this) {cnt++;}

}

```

#### Listing 5: Bytecodes of critical section

| 0:  | aload_0      |     |  |

|-----|--------------|-----|--|

| 1:  | dup          |     |  |

| 2:  | astore_1     |     |  |

| 3:  | monitorenter |     |  |

|     |              |     |  |

| /*  | cnt++; */    |     |  |

| 4:  | aload_0      |     |  |

| 5:  | dup          |     |  |

| 6:  | getfield     | #12 |  |

| 9:  | iconst_1     |     |  |

| 10: | iadd         |     |  |

| 11: | putfield     | #12 |  |

|     |              |     |  |

| 14: | aload_1      |     |  |

| 15: | monitorexit  |     |  |

As can be seen in Listing 5, the Java compiler explicitly inserts two synchronization-specific bytecodes, namely **monitorenter** and **monitorexit** that enclose the critical section as well as several bytecodes (e.g. line 0-3) that compute the operands for them. Since a synchronized method lacks **monitorenter** and **monitorexit** in its bytecode stream, the Java runtime system has to check its access flag additionally to determine how to execute it properly.

If a thread needs to execute a synchronized method or a critical section on an object, it must acquire (or enter if the monitor is considered as a door to the object) the monitor of the object at first. Otherwise, it must block until the monitor is released. Once the monitor of an object has been owned by some thread, its owner may reenter it recursively. The runtime system needs to track how many times the monitor has been entered, using a counter. Each time the owner leaves the monitor on return from a synchronized method or leaving the scope of a critical section, the internal counter of the monitor is decremented by one. Only if the counter of the monitor reaches zero, the monitor may be released and allows to be entered by another thread. If only one thread is blocked by the released monitor, it may acquire the monitor directly. However, if multiple threads are blocked, one of them needs to be selected and assigned the monitor by the runtime system. The selection algorithm is not explicitly defined in the Java specification and therefore is implementation-dependent.

## **Thread-specific Methods**

As mentioned above, a number of methods are available for writing multi-threaded programs. They can be categorized into two groups: thread-specific and synchronization-specific methods. The former group contains all methods declared in class **java.lang.Thread**, some of which are native methods and others are implemented based on the native ones. The latter group includes several native methods declared in class **java.lang.Object**. This subsection provides an overview on the thread-specific methods, while the synchronization-specific methods are presented in the following subsection.

**constructor:** A new thread instance can be created by using the constructor of class **Thread**. The task that needs to be executed by the thread can be optionally passed in as an argument of the constructor. In this case, the task object must be an instance of some class that implements interface **Runnable**. This object is then assigned to a field of the thread instance, which is called **target**.

**run:** This method defines the code sequence that performs the actual task. If the **target** field is not null, it just invokes the **run**-method on **target** as follows:

Listing 6: Thread.run()

```

public void run() {

if (target != null) {

target.run();

}

}

```

An alternative approach to defining a task is to override the **run**-method in a subclass of **Thread** and create new thread instances from the subclass instead of **Thread**.

**start:** A newly created thread instance is not taken into account by the runtime system for scheduling until its **start**-method has been invoked. Through the invocation of this method, the thread is attached to some internal data structure of the runtime system (e.g. a priority queue), which holds all ready threads. During the next scheduling process, the runtime system will select one of these ready threads to replace the currently running thread, using an implementation-specific algorithm. **setPriority:** Using this method, a thread may be given an explicit priority; if not, it simply inherits the priority from the thread creating it, i.e. its parent thread. Java defines a total of 10 priority levels from 1 to 10, where 1 represents the minimum priority and 10 the maximum. Threads with higher priority are executed in preference to threads with lower priority.

**yield:** This method gives the runtime system a hint that the thread calling it is willing to give up the processor in order to allow another ready thread to be executed. Nonetheless, the runtime system may choose to ignore the hint and let the current thread run further. This means that the result of the execution of this method is implementation-specific and therefore unpredictable.

**sleep:** The invocation of this method causes the calling thread to sleep for a given time. During this time, the execution of the thread may not be resumed. A very important thing to note is that the monitors owned by the calling thread are not released and thus can not be entered by other threads.

**join:** If a running thread calls this method on another thread, T, it cannot proceed before T has terminated. Optionally, a timeout value may be given to limit the joining duration. If the timeout value expires before T has terminated, the calling thread becomes ready again. Like the **sleep**-method, this method does not release the monitors owned by the calling thread.

### Synchronization-specific Methods

All synchronization-specific methods are based on the monitor construct of Java. Class **Object** provides three native methods that utilize the monitor construct to support more sophisticated synchronization mechanisms among threads. Invoking these methods on an object has one common constraint that the calling thread must already own the monitor of the object, otherwise an exception will be thrown by the runtime system.

wait: The invocation of the wait-method on an object causes the calling thread to give up the monitor of the object and start waiting on the object (i.e. the thread is suspended). A waiting thread is not considered by the runtime system during the scheduling process. The released monitor is assigned to one of the blocked threads requiring this monitor, based on an implementation-specific selection algorithm. Optionally, a timeout value may be given as an argument to limit the waiting duration. After the expiration of the timeout value, the waiting thread becomes ready automatically, i.e. it is allowed to be scheduled to run again. If no timeout value is given, the thread waits until either of the following methods is invoked.

**notify:** This method notifies the runtime system that the monitor of the object on which the method has been invoked is about to be released. The runtime system wakes up one of the threads waiting for the object's monitor according to some implementation-dependent algorithm. However, the awakened thread must enter the monitor first before it can run further.

Java Specification [49]: The awakened thread will compete in the usual manner with any other threads that might be actively competing to synchronize on this object; for example, the awakened thread enjoys no reliable privilege or disadvantage in being the next thread to lock this object.

Note that the internal counter of the monitor needs to be reset to the status before calling the **wait**-method once the awakened thread reenters the monitor.

**notifyAll:** Calling this method on an object wakes up all threads waiting for the monitor of the object instead of a single one, which is the only difference between the **notify**- and **notifyAll**-methods. All awakened threads have to compete with any other threads that are also trying to enter the monitor. Three important things to note about both of the **notify**- and **notifyAll**-methods are that:

- 1. If there is no waiting thread, nothing will happen through executing these methods.

- 2. The monitor is actually not released after calling either of these methods until the thread returns from the synchronized-method or leaves the critical section, or executes the **wait**-method on the corresponding object.

- 3. Unlike calling the **wait**-method, the thread that calls either of these methods proceeds until the next thread context switch, otherwise it would not be able to release the monitor indeed.

For the latter two reasons above, the **notify**- and **notifyAll**-methods should always be invoked at the end of a synchronized method or a critical section, or just before calling the **wait**-method so that the awakened thread or threads may really acquire the monitor.

### 2.3 Java Runtime System

### 2.3.1 Memory Model

The ISA defined by the Java bytecode partitions memory into three runtime data areas: *method area*, *heap* and *Java stack*. In the following, each of these data areas is described briefly.

#### **Method Area**

The method area can be considered as the code memory of a Java runtime system and is shared among all threads of an application. It holds the meta-information about the loaded classes, the bytecode streams of the methods defined in these classes as well as a set of constant values. All these information and data are generated by the Java compiler and saved statically in individual class files, using a platformindependent format. At runtime, they need to be extracted from the class files and loaded into the method area so that they can be accessed by the runtime system. Their representation inside the method area is implementation-specific and should be designed to facilitate efficient execution of the application.

#### Неар

Like the method area, the heap is also shared among all threads. It manages class instances and arrays created at runtime. Since Java does not allow an object to be deallocated explicitly, the runtime system needs to provide a garbage collector that reclaims the memory of unreachable objects. The manner in which the garbage collector cleans up the heap is not explicitly defined and therefore can be designed based on the specific characteristics of the runtime system.

## Java Stack

In contrast to both data areas above, every thread is assigned a dedicated Java stack as it is created. Each time a thread invokes a method, a new frame is pushed onto the thread's Java stack. The method uses this frame to store its parameters, local variables, intermediate computation results and other context-related data. Once the method invocation is complete, the frame is discarded.

The method that is currently being executed by a thread is referred to as the thread's *current method*, and its frame is known as the *current frame*. The runtime system executes bytecodes solely on the current frame. A frame is no longer current if its method invokes another method or its method completes. In the former case, the frame of the invoked method becomes the current frame. In the latter case, the current frame is removed from the Java stack and the previous frame becomes the current one.

The stack frame of a method consists of three parts, namely a local variable array, an operand stack and a frame data section, as explained below.

**Local Variable Array:** All local variables of the method are saved in an array of words. The length of this array is determined at compile time and is loaded together with the bytecode stream of the method into the method area at runtime. An element of this array can be addressed by its index directly. A value of type **long** or **double** occupies two successive entries in the array, while a value of any other type only one. This implies that values of type **byte**, **char** and **short** need to be cast to integers before they are stored into the local variable array. Besides holding the local variables, this array is also employed to pass the parameters of the method. Any parameters of the method must be placed into the successive local variables starting from local variable 0, in their declaration order.

**Operand Stack:** The operand stack is a 32-bit *last-in-first-out* (LIFO) stack that serves as the primary work space of the Java runtime system. Java supplies a number of load and store bytecodes that are solely used to transfer values between the operand stack and other data areas, including the method area, the heap and the local variable array. The vast majority of the remaining bytecodes take values from the operand stack, perform corresponding operations on them, and then push the results back onto the operand stack. For this reason, the depth of the operand stack varies continuously as bytecodes are executed. Pushing a value of type **long** or **double** onto the operand stack increases its depth by two, while pushing a value of any other type increases its depth by one. Also, the operand stack is used to prepare parameters for a method and receive the method's result. The parameters must be pushed onto the operand stack in the order in which they are declared.

**Frame Data Section:** The frame data section is intended to assist the runtime system with constant pool resolution, method return and exception dispatch. However, its actual layout, size and functions are implementation-dependent and therefore can be quite different from one runtime system to another. For example, in a classical JVM, it might store a reference to the constant pool of the class that defines the method, the value of the *program counter* (PC) of the calling method (i.e. the caller) as well as a reference to the exception handler table of the method. In contrast, it solely saves the context data of the caller in the AMIDAR processor.

#### 2.3.2 Object Access

#### **Object Addressing**

As described in Section 2.3.1, the heap is the runtime data area from which objects and arrays are allocated. While developing a heap management system, a key design decision that needs to be made is the way how objects are addressed. Two important schemes include *direct addressing* and *logical addressing* (or *indirect addressing*).

In the former scheme, an object is referenced by its base physical address or its base virtual address if a virtual memory system is used. This allows the physical or virtual address of a field of the object to be calculated by simply summing the object's base address and the field's offset. However, this scheme unduly complicates object relocation which is necessary for heap compaction. The reason is that all references to an object must be updated across the whole memory system from the frame stack to the heap at a time after the object has been reallocated.

In contrast, an object is referenced by a location-independent identifier in the latter scheme, which is referred to as *handle* in this thesis. A handle is actually an index into a table called *handle table* below. The handle table holds meta-information about every object, like its base physical address. This scheme greatly simplifies object reallocation because an object's memory address only needs to be updated in the handle table once. The primary drawback of this scheme is the indirection overhead when accessing a field of an object, since the object's memory address is not directly available and must be retrieved from the handle table. This issue can be overcome by using an object cache, because the handle table look up is only necessary if a cache miss occurs.

#### **Object Caching**

A Java program can create a large number of objects throughout its lifetime. Therefore, the heap is usually resident in external memory to provide sufficient storage space. To avoid the high access latency introduced by the external memory, an object cache is typically employed, whose architecture is determined by the object addressing scheme used, as discussed below.

In the case of the direct addressing scheme, a physically addressed cache is the only choice, if no virtual memory system exists. Otherwise, either a physically or a virtually addressed cache can be used, depending on where the *translation lookaside buffer* (TLB) is placed, before or after the cache. Both of these caches treat data blocks of the external memory as their first-class entities. Thus, every word held in a cache line is accessible, providing the full cache capacity to the runtime system. Also, this allows for prefetching an adjacent object on the occurrence of a cache eviction.

Upon an access to a field of some object, both of these caches take the sum of the object's base address and the field's offset, namely the address of the field, as input. Each of the tag value, the cache line index and the cache line offset is just a subset of the field's address bits. In this way, successive fields of the object can be distributed through the entire cache, reducing conflicts. The major difference between a physically and virtually addressed cache is that the latter one needs to handle the issue of address aliasing, while the former one does not.

For the logical addressing scheme, a physically addressed cache could be used. In this case, the handle table would serve as the TLB. However, this would incur a delay of at least one clock cycle due to the handle table lookup. A classical way to solve this issue is to employ a logically addressed cache whose cache lines are tagged directly with handle-offset pairs. Although the basic idea of a logically addressed cache is quite similar to that of a virtually addressed one, they differ from each other in several aspects.

Unlike a virtual address, the handle of an object is the object's unique identifier. Therefore, a logically addressed cache does not need to deal with address aliasing and can be implemented as a *logically-indexed*, *logically-tagged* cache (LILT). In such a cache, the first-class entities are objects rather than memory blocks. This means that each cache line can only be associated with a single object. As

a result, some words at the end of a cache line will not be used, if the size of the cached object is not an integral multiple of the cache line size. This phenomenon is referred to as *external fragmentation* below. The direct consequence caused by the external fragmentation is the reduction of the effective cache capacity. Another negative effect is the increased complexity of the write-back logic, because only the valid part of a cache line may be written back to the heap. The external fragmentation can be considered as the price paid for the major benefit brought by the indirect addressing scheme, namely the easy implementation of heap compaction.

A logically addressed cache does not support prefetching an adjacent object upon a cache miss. However, the vast majority of objects are short-lived [14, 127] and will die in the cache [123], which means that prefetching would be actually only important for long-lived objects that need to be cached repeatedly. According to previous research, there is little spatial locality between long-lived objects [13]. Consequently, the lack of object prefetching should not result in a notable performance loss.

Another key difference between a logically and virtually addressed cache is the way how cache index is generated. Upon an access to a field of an object, a logically addressed cache typically generates the cache index with several handle bits and several offset bits in the hope of reducing intra- and inter-object conflicts at the same time. If the index solely consisted of handle bits, the fields of a large object would be stored in a single cache set, leading to increased intra-object conflicts. If the index was only made up of offset bits, small objects would be restricted to the cache sets at the beginning of the cache, increasing inter-object conflicts. Which and how many bits should be selected from each of the handle and the offset for the purpose of index generation are implementation dependent issues. In Section 3.2 below, several index generation schemes are discussed in detail. Since only a part of the offset bits are used to calculate the cache index, the maximum cache space that may be occupied by an object is limited. In contrast, a virtually addressed cache does not have such a limitation and therefore can even be filled with one single object.

## 2.3.3 Garbage Collection

As mentioned in Section 2.3.1, when running a Java program, objects allocated from the heap cannot be explicitly deallocated by the program. To avoid running out of memory, a runtime system must provide a mechanism to automatically clean up the heap, which is known as garbage collection [69]. The part of the runtime system that is employed to perform garbage collection is typically referred to as garbage collector. A garbage collector has two major tasks: detection of garbage objects and reclaiming the memory occupied by such objects. An object is considered garbage, if it is no longer referenced by the program, otherwise it is said to be live. In the following, the implementation of a garbage collector is discussed from different points of view briefly.

#### **Garbage Detection**

There are two well-known approaches to distinguishing between live and garbage objects, namely *reference counting* [27] and *tracing* [69]. A reference counting garbage collector keeps track of the number of references to every object. Once the reference number of an object becomes zero, the object can be garbage collected. This approach allows any unreferenced object to be detected and removed on the fly, which makes it suitable for real-time systems in particular. Its main disadvantage is that it cannot

recognize reference cycles. Also, maintaining a reference count for each object on the heap increases both performance overhead and memory usage. Due to these drawbacks, the vast majority of modern garbage collectors are based on the latter approach, namely tracing. Therefore, the discussion below is centered around tracing garbage collection.

A tracing garbage collector determines which objects are still referenced by the program, i.e. it detects live objects rather than garbage objects. For this purpose, it traces out the graph of references starting from a set of root objects and marks every reachable object as live. Accordingly, objects that are not reachable from the root set will remain unmarked and become eligible for garbage collection.

An object is considered a root object if it is directly accessible to the program. Thus, although its definition is implementation-dependent, the root set should always include any object references stored on any Java stack and in the static fields of any class. An object referenced by a root object is reachable and therefore is a live object. An object referenced by a live object is reachable as well, which means that object reachability is a transitive closure. All reachable objects can be potentially accessed by the program and thus may not be removed.

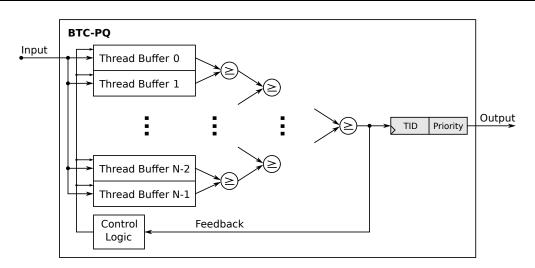

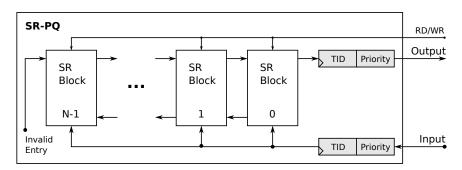

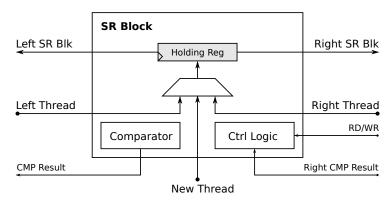

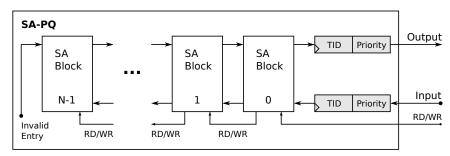

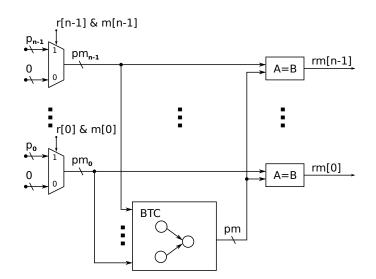

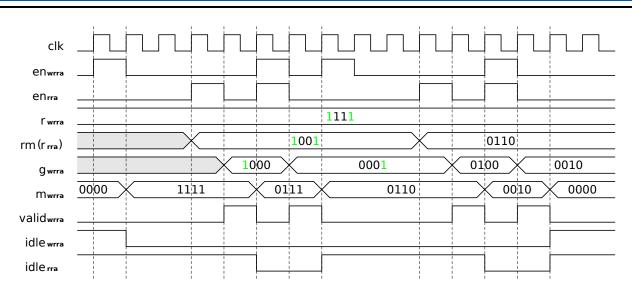

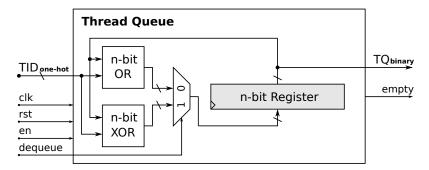

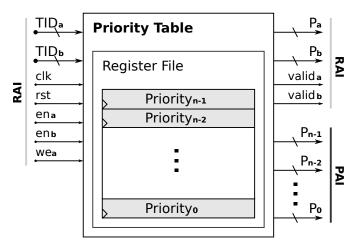

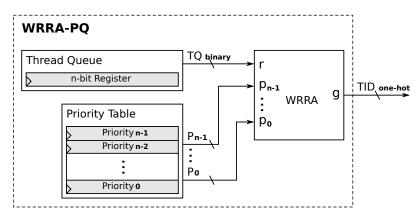

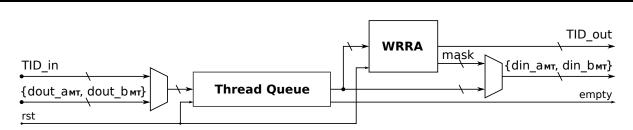

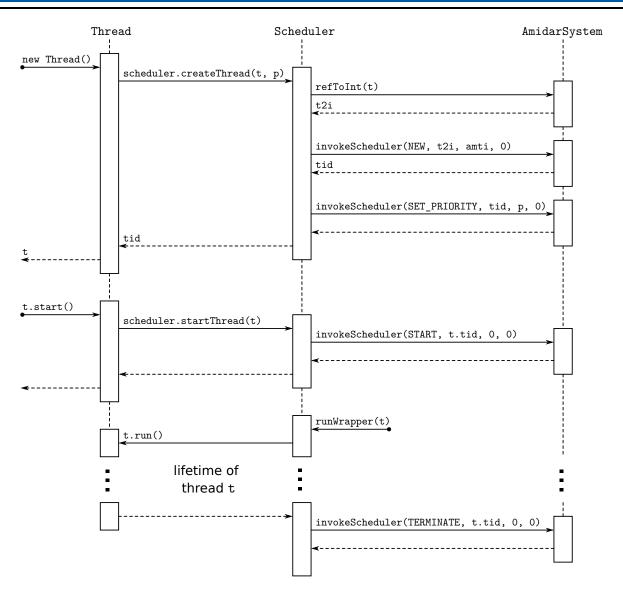

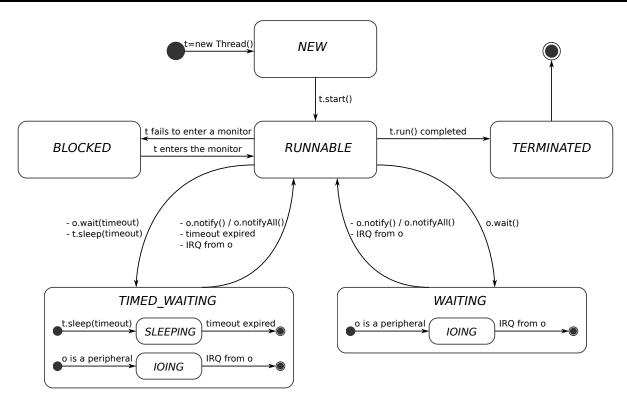

Inside a runtime system, especially on the Java stack and the heap, an object reference is represented in the same way as a 32-bit primitive value [50]. If a garbage collector can tell apart a reference from a primitive value so that the references to live objects can be precisely identified during the tracing process, it is called a *precise* collector, otherwise a *conservative* collector. A conservative collector cannot recognize a garbage object, if that object happens to be pointed to by some primitive value which appears to be a valid reference. As a result, garbage collection has to be performed more frequently. Implementing a precise collector requires assistance from both of the runtime system and the compiler. The runtime system must be able to extract the references stored on any Java stack to construct the root set. The compiler needs to generate type information about every field of a class to allow each reference contained in an object of the class to be exactly traced.