# DESIGN OF A DEDICATED IFT MICROCONTROLLER

by

#### **GRAYSON HIMUNZOWA**

Student number: 214025179

Submitted in fulfilment of the requirements for the degree of

## **DOCTOR OF PHILOSOPHY IN ENGINEERING (MECHATRONICS)**

in the

## FACULTY OF ENGINEERING

at the

#### NELSON MANDELA UNIVERSITY

Supervisor: Professor Farouk Smith

2017

## DECLARATION

NAME<sup>\*</sup>

# GRAYSON HIMUNZOWA

STUDENT NUMBER: 214025179

QUALIFICATION: Doctor of Philosophy in Engineering (Mechatronics)

In accordance with rule G5.6.3, I hereby declare that the above-mentioned thesis is my own work and that it has not previously been submitted for assessment to another university or for another qualification.

i

att.

SIGNATURE

GRAYSON HIMUNZOWA

11/04/18

DATE:

#### SUMMARY

The design of a Dedicated IFT Microcontroller originated from the successful implementation of the Iterative Feedback Tuning (IFT) technique into the Digital Signal Processor microcontroller (DSP56F807C) at the University of Cape Town in 2006. However, implementation of the IFT technique on a general-purpose microcontroller is neither optimal, nor a cost-effective exercise, as most of the microcontroller peripherals remain unused, and drain energy for doing nothing. In addition, microcontrollers and DSPs are software-driven devices whose nature is sequential in executing algorithms, and hence have a significant effect on the bandwidth of the closed-loop control. To mitigate the said problem, the design of a Dedicated IFT Microcontroller is proposed in this thesis. To accomplish this goal, the preliminary task was to explore the IFT theory and its applications, followed by a review of the literature on FPGA design methodology for industrial control systems, Microcontroller design automation (EDA) tools and other application software was also conducted.

After the literature review, the IFT was investigated exhaustively by applying it to three types of plants, namely: a DC motor, an oscillatory plant, and an unstable plant. Each of these plants were tested using three types of initial controllers, namely heavily-damped, critically damped and under-damped initial controllers. The plants were also tested by varying the amplitude of the reference signal, followed by using a single-step signal of constant amplitude of one volt. The intention of exploring all of these possibilities was meant to firmly expose the IFT boundaries of applicability, so that the final product would not be vulnerable to unnecessary post-production discoveries.

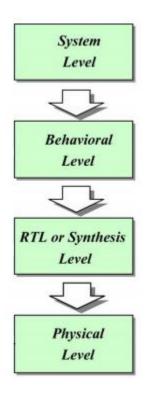

The design methodology adopted in this research was a popular hierarchical and modular top-down procedure, which is an array of abstraction levels that are detailed as: system level, behavioural level, Register-Transfer Level (RTL) and Gate level. At system level, the Dedicated IFT Microcontroller was defined. Thereafter, at behavioural level, the design was simulated using VHDL, created by porting the LabView IFT code to the Xilinx EDA tool. At the RTL, the synthesisable VHDL code utilising fixed-point number representation was written. The compiled bit file was downloaded onto National Instruments (NI) Digital Electronics FPGA Board featuring

ii

the Spartan 3 series FPGA. This was tested, using a method known as simulation in the hardware.

The key contribution of this thesis is the experimental validation of the IFT technique on FPGA hardware as it has never been published before, the work described in chapter four and five. The other contribution is the analysis of 1DOF IFT technique in terms of limitations of applicability for correct implementation, which is the main work of chapter three.

This work could be used to explore other computational methods, like the use of floating-point number representation for high resolution and accuracy in numerical computations. Another avenue that could be exploited is Xilinx's recent Vivado methodology, which has the capacity for traditional programming languages like C or C++, as these have in-built floating-point number capability.

Finally, out of this work, two papers have already been published by Springer and IEEE Xplore Publishers, and a journal paper has also been written for publication in the *Control Systems Technology* journal.

## ACKNOWLEDGEMENTS

- I dedicate this thesis to the almighty God for giving me life, energy and zeal throughout my period of study.

- Thank you to my supervisor (Professor Farouk Smith) for guidance and also financial support in the procurement of research equipment and reviewing the thesis.

- Thank you to Professor EI-Hossein Khaled for welcoming me to NMMU.

- Thank you to Professor Martin Braae, formerly from the University of Cape Town, for assistance with the technical issues of the project.

- Thank you to Professor Mundia Muya and Doctor Ackim Zulu (both from the University of Zambia) for supporting this study programme at home.

# LIST OF FIGURES

# Page

| Figure 1:     | Block diagram of closed loop system of two-degree-of-freedom controller |

|---------------|-------------------------------------------------------------------------|

| Figure 2:     | Closed-loop system for 1DOF controller                                  |

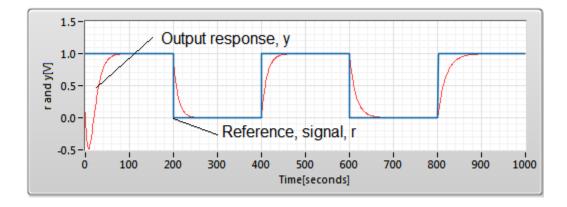

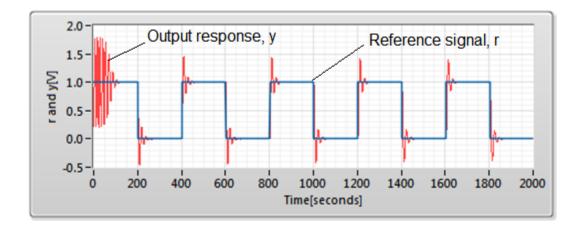

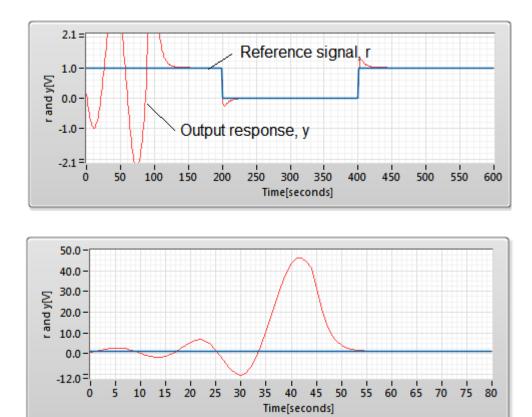

| Figure 3(a):  | Reference signal and DC motor output signal                             |

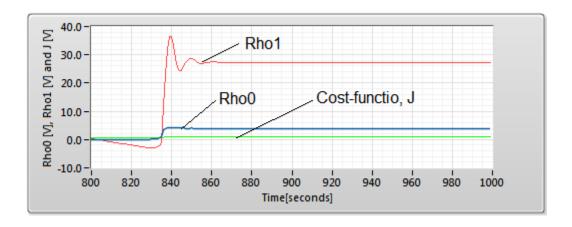

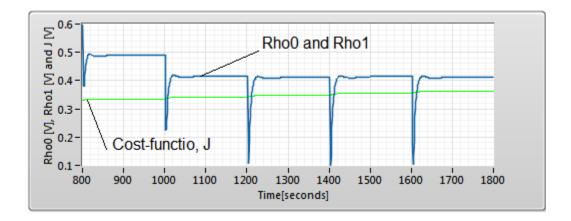

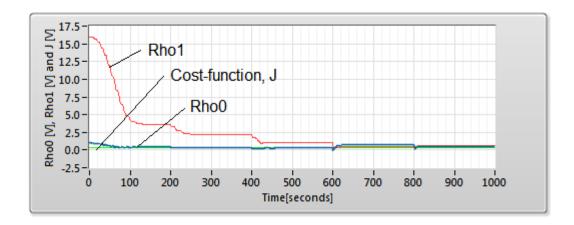

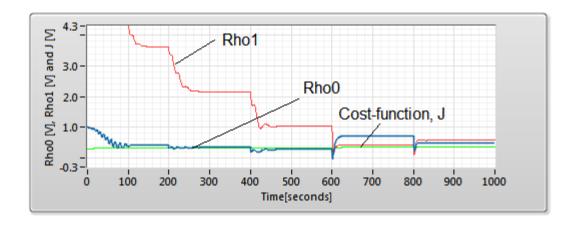

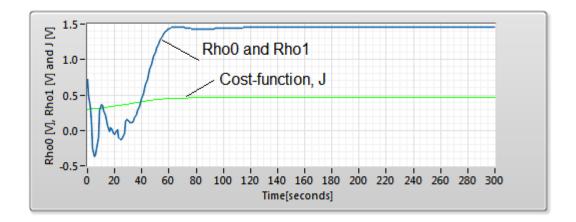

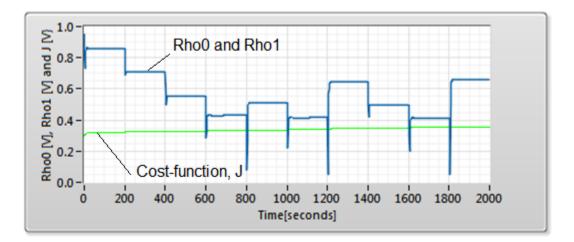

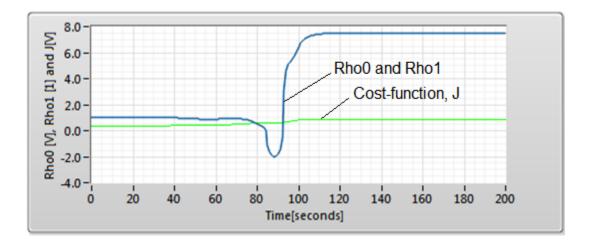

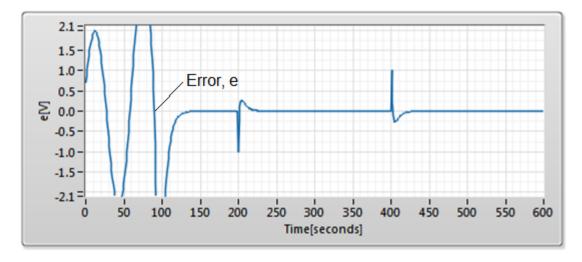

| Figure 3(b):  | Rho0, Rh01 and cost function, J signals                                 |

| Figure 3(c):  | Rho0, Rh01 and cost function, J signals                                 |

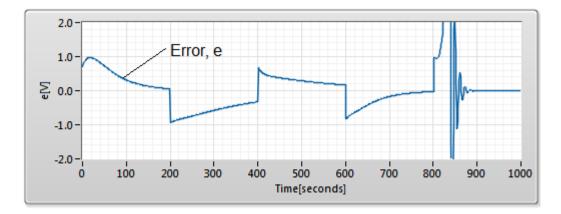

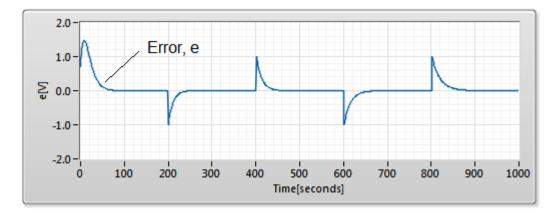

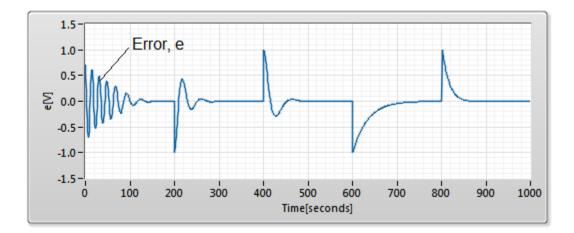

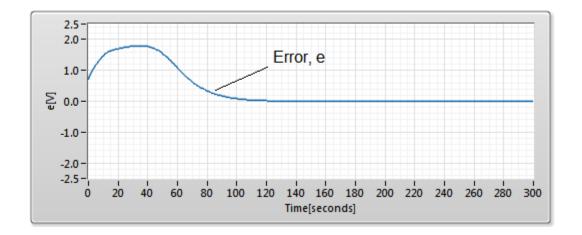

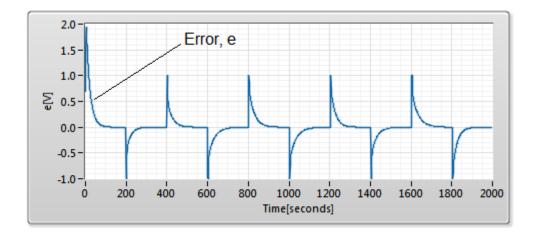

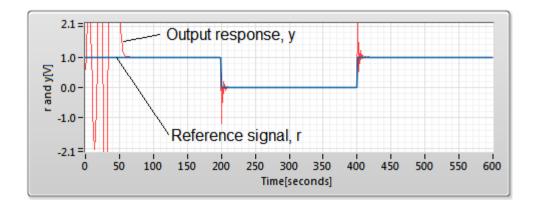

| Figure 3(d)   | Error signal                                                            |

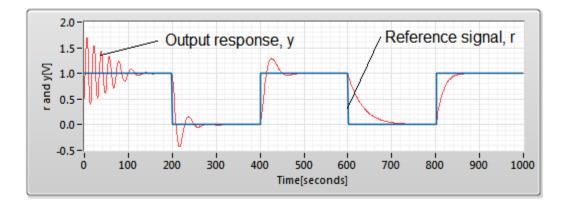

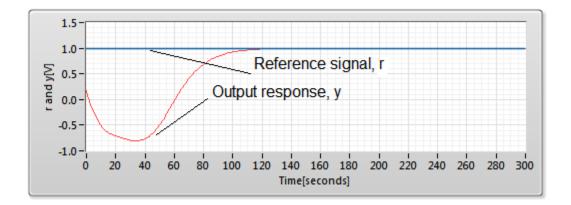

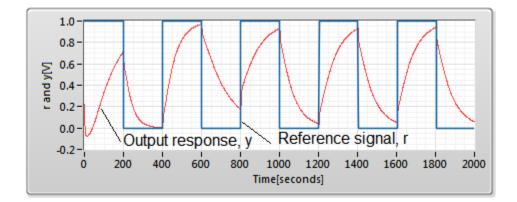

| Figure 4(a):  | Reference signal and DC motor output signal                             |

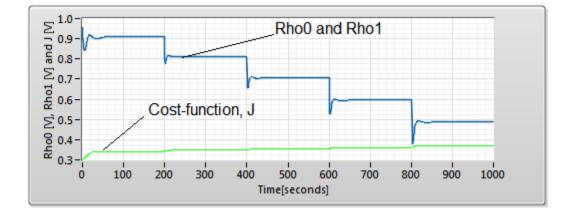

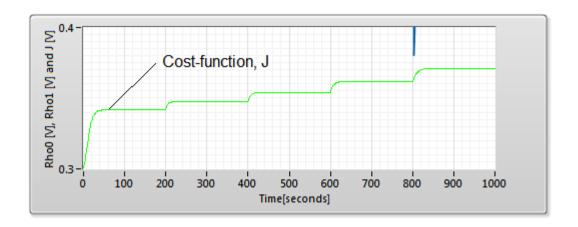

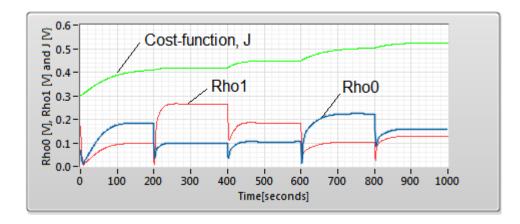

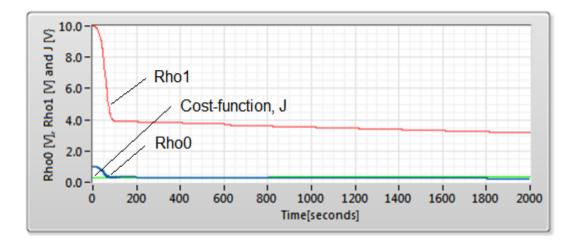

| Figure 4(b):  | PI controller parameter signals and cost function signal                |

| Figure 4(c) : | Magnified PI controller parameter signals                               |

| Figure 4(d):  | Magnified cost function signal                                          |

| Figure 4(e) : | Error signal                                                            |

| Figure 5(a):  | Reference signal and DC motor output signal                             |

| Figure 5(b):  | PI controller parameter signals and cost function signal                |

| Figure 5(c):  | PI controller parameter signals and cost function signal                |

| Figure 5(d):  | Error signal                                                            |

| Figure 6(a):  | Reference signal and DC motor output signal43                           |

| Figure 6(b):  | PI controller parameter signals and cost function signal                |

| Figure 6(c):  | Error signal                                                            |

| Figure 7(a):  | IFT response for oscillatory plant                        |

|---------------|-----------------------------------------------------------|

| Figure 7(b):  | Parameter trajectory and cost function48                  |

| Figure 7(c):  | Error signal 48                                           |

| Figure 7(d):  | IFT response for oscillatory plant51                      |

| Figure 7(e):  | Parameter trajectory and cost function51                  |

| Figure 8(a):  | IFT response for oscillatory plant 52                     |

| Figure 8(b):  | Parameter trajectory and cost function52                  |

| Figure 8(c):  | Error signal                                              |

| Figure 9(a):  | IFT response for oscillatory plant 55                     |

| Figure 9(b):  | Parameter trajectory and cost function55                  |

| Figure 9(c):  | Error signal                                              |

| Figure 10(a): | IFT response for unstable plant                           |

| Figure 10(b): | Parameter trajectory for unstable plant and cost function |

| Figure 10(c): | Error behaviour                                           |

| Figure 11(a): | IFT response for unstable plant61                         |

| Figure 11(b): | Parameter trajectory for unstable plant                   |

| Figure 11(c): | Error behaviour                                           |

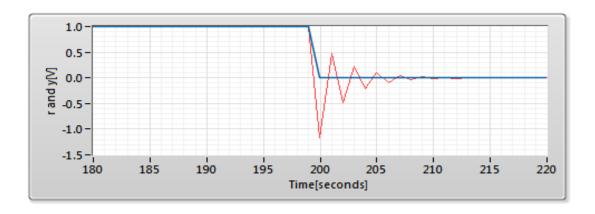

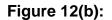

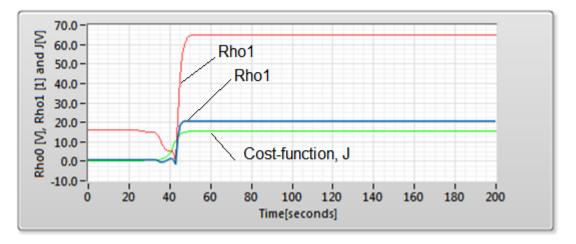

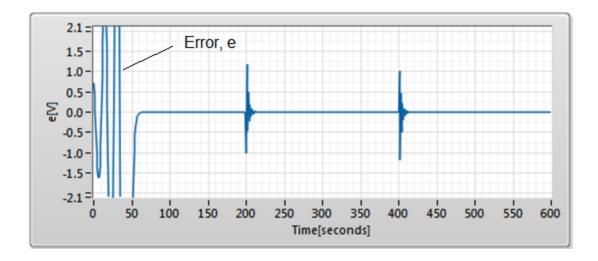

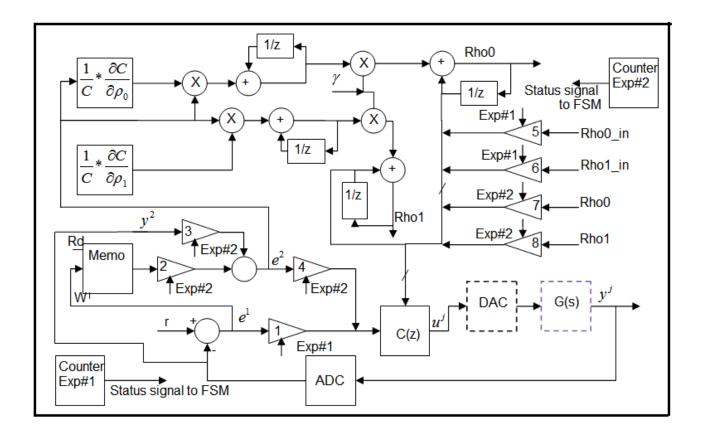

| Figure 12(a): | IFT response for unstable plant64                         |

| Figure 12(b): | Magnified IFT response for unstable plant                 |

| Figure 12(c): | Parameter trajectory for unstable plant and cost function |

| Figure 12(d): | Error behaviour                                           |

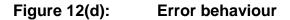

| Figure 13:                | Generic FPGA architecture                                                           | 70 |

|---------------------------|-------------------------------------------------------------------------------------|----|

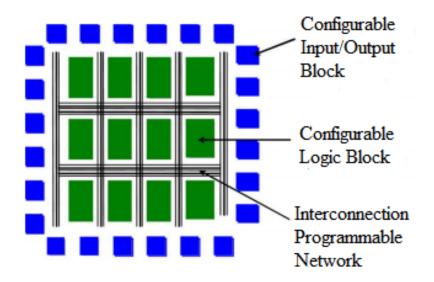

| Figure 14:                | Logic cell structure [11]                                                           | 71 |

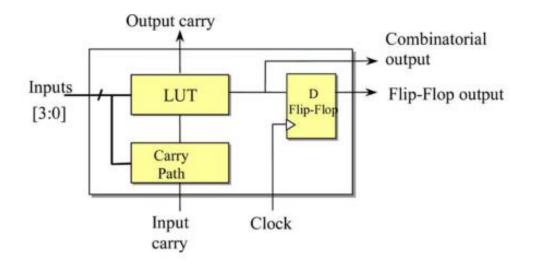

| Figure 15:                | IFT technique architecture                                                          | 74 |

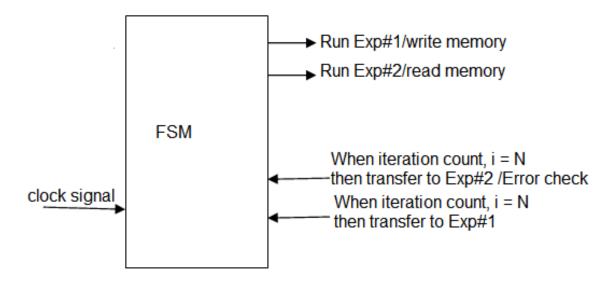

| Figure 16:                | IFT technique finite-state machine block diagram                                    | 76 |

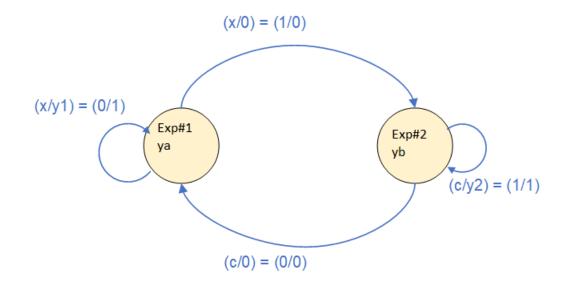

| Figure 17:                | IFT technique FSM state diagram                                                     | 77 |

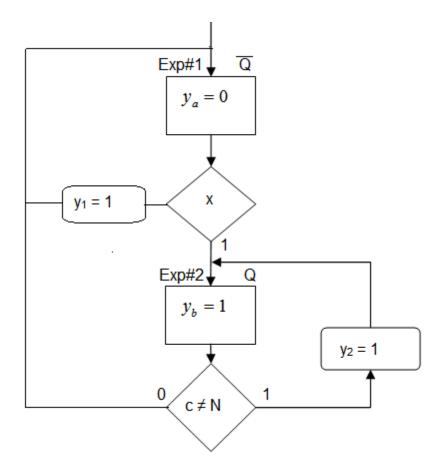

| Figure 18:                | IFT technique ASM chart                                                             | 77 |

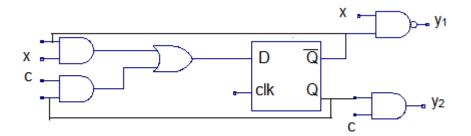

| Figure 19:                | IFT technique FSM                                                                   | 78 |

| Figure 20:                | Simulation results for the IFT VHDL code                                            | 84 |

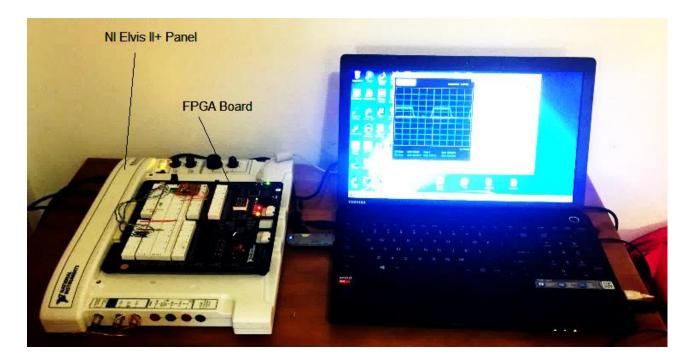

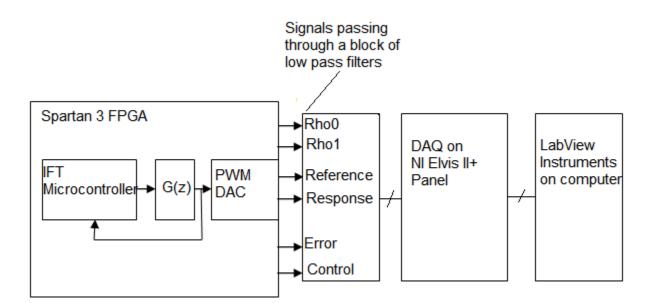

| Figure 21:                | Experimental setup for testing of IFT microcontroller                               | 87 |

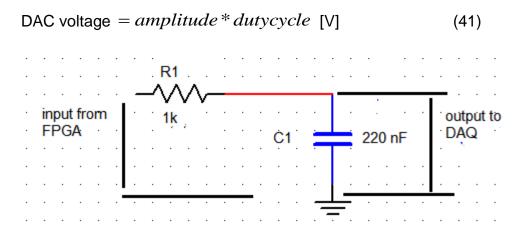

| Figure 22:                | Block diagram of experimental setup for testing a dedicated IFT microcontroller     | 88 |

| Figure 22:                | Low pass filter                                                                     | 88 |

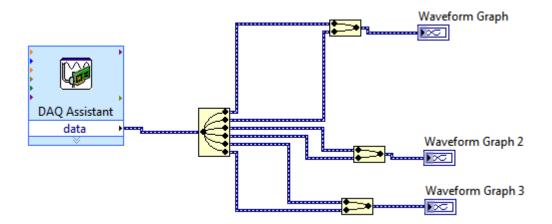

| Figure 23:                | LabView code for displaying signals on graphs                                       | 90 |

|                           | Experimental setup for testing of IFT microcontroller showing the ini he controller |    |

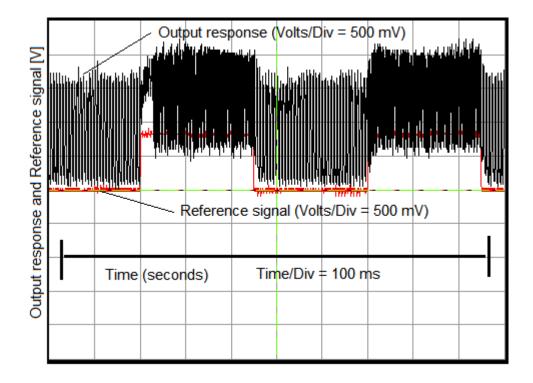

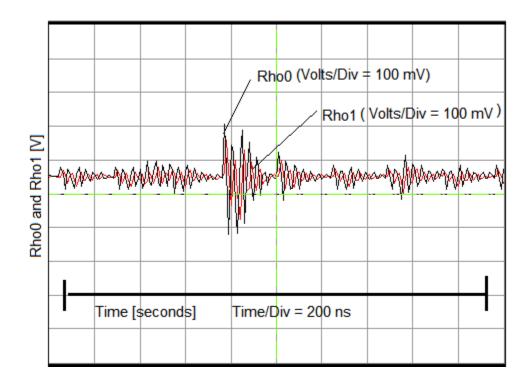

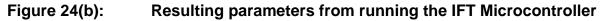

| Figure 24(b):             | Resulting parameters from running the IFT microcontroller                           | 93 |

| Figure 24(a):             | Experimental setup for testing of IFT microcontroller                               | 94 |

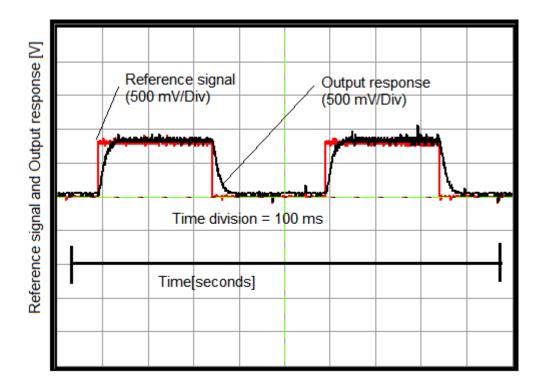

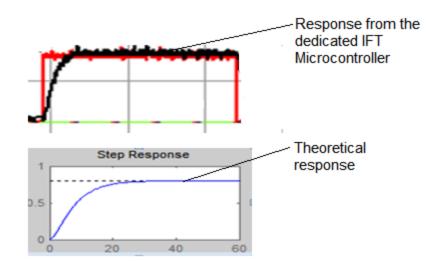

| Figure 25(a):             | Experimental setup for testing of IFT microcontroller                               | 95 |

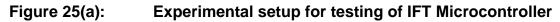

| Figure 25(b):<br>response | Comparison of response from the hardware with the theoreti                          |    |

| Figure 25(c)              | : Experimental setup for testing of IFT microcontroller                             | 96 |

| Figure 25(b):             | Experimental setup for testing of IFT microcontroller                               | 96 |

# LIST OF TABLES

# Page

| Table 1:  | IFT signals for experiment#1, experiment#2 and experiment#313         |

|-----------|-----------------------------------------------------------------------|

| Table 2:  | Roots of the DC Motor closed-loop control system                      |

| Table 3:  | Routh-Hurwitz for the characteristic equation in (32)                 |

| Table 4:  | Roots of the DC Motor closed-loop control system                      |

| Table 5:  | Roots of the DC Motor closed-loop control system                      |

| Table 6:  | Roots of the oscillatory closed-loop control system                   |

| Table 7:  | Effect of varying amplitude reference signal – a slow-damped case 39  |

| Table 8:  | Effect of varying amplitude reference signal – a fast-damped case 40  |

| Table 9:  | Effect of varying amplitude reference signal – an oscillatory case 41 |

| Table 10: | Roots of the oscillatory plant closed-loop control system             |

| Table 11: | Roots of the fast-damped plant for closed-loop control system         |

| Table 12: | Roots of the oscillatory plant for closed-loop control system         |

| Table 13: | Roots of the oscillatory plant for closed-loop control system         |

| Table 14: | Roots of the fast-damped plant for closed-loop control system         |

| Table 15: | Roots of the oscillatory plant for closed loop control system         |

| Table 16: | VHDL code 81                                                          |

| Table 17: | VHDL code structure for IFT technique 82                              |

| Table 18: | Device utilisation summary                                            |

| Table 19: | Parameter pairs in the region of stability91                          |

# LIST OF ACRONYMS

| 1-DOF, 2-DOF | One Degree of Freedom, Two Degrees of Freedom             |

|--------------|-----------------------------------------------------------|

| BFGS         | Broyden - Fletcher - Goldfarb - Shanno                    |

| DSP          | Digital Signal Processor                                  |

| PID, PI      | Proportional Integral Differential, Proportional Integral |

| DC, ISE      | Direct Current, Integrated System Environment             |

| VLSI         | Very Large Scale Integration                              |

| EDA          | Electronic Design Automation                              |

| IC, NI       | Integrated Circuit, National Instruments                  |

| FSM, ASM     | Finite State Machine, Algorithmic State Machine           |

| VHDL         | Very High Speed IC Hardware Description Languages         |

| HLS          | High Level Synthesis                                      |

| ADC          | Analogue-to-Digital Converter                             |

| DAC          | Digital-to-Analogue Converter                             |

| ZOH          | Holding Circuit                                           |

| FPGA         | Field-Programmable Gate Array                             |

| RTL          | Register Transfer Level                                   |

| IFT          | Iterative Feedback Tuning                                 |

| PWM          | Pulse Width Modulation                                    |

# TABLE OF CONTENTS

# Page

| DECLARATION      | I    |

|------------------|------|

| SUMMARY          | II   |

| ACKNOWLEDGEMENT  | IV   |

| LIST OF FIGURES  | V    |

| LIST OF TABLES   | VIII |

| LIST OF ACRONYMS | IX   |

# **CHAPTER 1**

# **RESEARCH PROPOSAL**

| 1.1 |                            | 1 |

|-----|----------------------------|---|

| 1.2 | MOTIVATION OF THE RESEARCH | 1 |

| 1.3 | PROBLEM STATEMENT          | 2 |

| 1.4 | HYPOTHESIS                 | 2 |

| 1.5 | OBJECTIVES                 | 3 |

| 1.6 | RESEARCH METHODOLOGY       | 3 |

| 1.7 | PLAN OF DEVELOPMENT        | 4 |

## CHAPTER 2

# LITERATURE REVIEW

| 2.1 | SEARCH OBJECTIVE                         | 5 |

|-----|------------------------------------------|---|

| 2.2 | IFT TECHNIQUE APPLICATIONS SURVEY        | 5 |

| 2.3 | FPGA-BASED CONTROLLERS LITERATURE REVIEW | 7 |

| 2.4 | SUMMARY                                  | 9 |

## CHAPTER THREE

# STUDY AND VALIDATION OF IFT TECHNIQUE

| 3.1   | INTRODUCTION                                                             | 10 |

|-------|--------------------------------------------------------------------------|----|

| 3.2   | ITERATIVE FEEDBACK TUNING TECHNIQUE OVERVIEW                             | 10 |

| 3.2.1 | Generation of the gradients for modelling error and controller signal    | 16 |

| 3.2.2 | IFT technique of first-degree-of-freedom (1DOF) controller               | 17 |

| 3.2.3 | Criterion function specification                                         | 19 |

| 3.2.4 | Algorithm formulation for 1DOF                                           | 20 |

| 3.3   | SIMULATION OF IFT TECHNIQUE USING LABVIEW PLATFORM                       | 24 |

| 3.3.1 | Simulation of IFT applied to the DC Motor                                | 29 |

| 3.3.2 | The effect of varying the reference signal amplitude on IFT optimisation | 39 |

| 3.3.3 | The effect of single-step reference signal on IFT optimisation           | 43 |

| 3.3.4 | Simulation of IFT using oscillatory plant                                | 45 |

| 3.3.5 | Simulation of the IFT using unstable plant                               | 57 |

| 3.3.6 | Summary                                                                  | 66 |

# **CHAPTER 4**

| 4.1   |                                                         | . 68 |

|-------|---------------------------------------------------------|------|

| 4.2   | OVERVIEW OF AN FPGA TECHNOLOGY                          | . 68 |

| 4.3   | DESIGN METHODOLOGY                                      | . 73 |

| 4.3.1 | System Level Abstraction                                | .73  |

| 4.3.2 | Behavioural Level Abstraction                           | .78  |

| 4.3.3 | RTL Abstraction                                         | . 82 |

|       | 4.3.3.1 Simulation of VHDL Code for IFT Microcontroller | . 83 |

| 4.3.4 | Gate Level Abstraction                                  | . 85 |

| 4.4   | SUMMARY                                                 | . 85 |

# CHAPTER 5

# **TESTING OF A DEDICATED IFT MICROCONTROLLER**

| 5.1   | INTRODUCTION                | 86 |

|-------|-----------------------------|----|

| 5.2   | EXPERIMENTAL SETUP          | 86 |

| 5.2.1 | Procedure of the experiment | 90 |

| 5.3   | SUMMARY                     | 97 |

# **CHAPTER 6**

# CONTRIBUTION AND FUTURE RESEARCH

| 6.1  |                   |     |

|------|-------------------|-----|

| 6.2  | NEW CONTRIBUTIONS |     |

|      | FUTURE RESEARCH   |     |

| 6.4  | PUBLICATIONS      |     |

| REFE | RENCE             | 100 |

| APPE | NDIX I            |     |

| APPE | NDIX II           |     |

| APPE | NDIX III          | 110 |

| APPE | NDIX IV           | 118 |

| APPE | NDIX V            |     |

#### CHAPTER ONE

#### **RESEARCH PROPOSAL**

#### 1.1 INTRODUCTION

The design of a Dedicated IFT Microcontroller was conceived as the result of the successful implementation of the Iterative Feedback Tuning (IFT) technique into the Digital Signal Processor microcontroller (DSP56F807C) at the University of Cape Town in 2006. However, the implementation of the IFT technique on a general-purpose microcontroller is not optimal, nor a cost-effective exercise, as most of the microcontroller peripherals remain unused, meaning that such extra hardware is a cost in energy. Microcontrollers and DSPs are software-driven devices whose nature is sequential in executing algorithms, and hence have a significant effect on the bandwidth of the closed loop control. These problems can be mitigated by developing a dedicated or hard-wired IFT Microcontroller that contains only necessary peripherals, and having the hardware IFT execute in parallel. To realise this, the IFT Microcontroller was developed on a Field Programmable Gate Array (FPGA). This concept would not only resolve the above mentioned problems, but also improve performance (in terms of power consumption and execution speed).

## 1.2 MOTIVATION OF THE RESEARCH

A vast number of IFT applications currently existing or described in [1] and other literatures, is one of the motivating factors that triggered this research. For example: tuning of PID controller parameters [2, 3, 4, 7], application to Zang sugar cane process plant [5], application to non-linear systems [6], application to model-free design with guaranteed stability [8], application to DC-servo with backlash [9], application in design of robust controllers [9], to mention a few. The IFT technique is one of the most recent methods that can mitigate the above-mentioned problems efficiently, but no stand-alone hardware or commercial product exists that can implement IFT technique.

Finally, due to rapid progress in very large-scale integration (VLSI) technology and electronic design automation (EDA) techniques in recent years, an opportunity for the development of complex and high-performance controllers for industrial electronic systems has been created. Nowadays, the design engineer is using modern EDA tools to design, simulate, and verify a design before committing to hardware [12].

The development of a Dedicated IFT Microcontroller at the level of an integrated circuit (IC) is important, as this can lead to commercialisation of the IFT technique or development of industrial product with compactness, and excellent control performance at reduced cost.

## 1.3 PROBLEM STATEMENT

Problems resulting from modelled and external uncertainty always deteriorate the control performance of proportional-integral-differential (PID) controllers that are widely used in industrial control. In the absence of self-tuning, the fixed PID parameters can hardly adapt to uncertainty or time-varying systems [13]. In addition to this, there is a particular case of industrial interest in which tuning of a proportional-integral (PI) or PID controller needs to be adaptive since classical approaches contain a number of fundamental problems [1], such as:

- the amount of offline tuning required;

- the assumption on the plant structure;

- the issue of system stability; and

- the difficulties in dealing with nonlinear, large time-delayed and time-variant plants.

Hence, the main objective of this thesis is to design a Dedicated IFT Microcontroller with compactness and improved performance to resolve the above problems existing in industrial control.

## 1.4 HYPOTHESIS

Our hypothesis statement is given as follows:

We believe that a dedicated IFT Microcontroller with improved performance can be developed into an FPGA device.

## 1.5 OBJECTIVES

The main objective of this research is to design a Dedicated IFT Microcontroller with improved controller performance using FPGA hardware, and is achieved through the following specific objectives:

- Study and validate the IFT technique with a view to developing a novel hardware (Dedicated IFT Microcontroller) for tuning proportional-integral (PI) controller parameters. Both IFT technique of one degree of freedom (1DOF) and two degrees of freedom (2DOF) will be studied but only 1DOF will be validated in order to simplify the dedicated IFT Microcontroller hardware.

- Design the architecture (data path) and finite-state machine (FSM) for a Dedicated IFT Microcontroller and develop VHDL code for it. The general purpose architecture is avoided for reasons of high speed and power consumption as compared with dedicated architecture.

- Testing of a Dedicated IFT Microcontroller with a simulated DC motor. A physical DC motor is avoided due to want of keeping the research narrow but detailed.

# 1.6 RESEARCH METHODOLOGY

Our research method progressed as follows:

- Research proposal development through intensive review of literature in the areas of adaptive control algorithms (with main emphasis on IFT algorithm theory and applications), controllers based on FPGA hardware and FPGA Design Methodology for Industrial Control System.

- A study of IFT technique and FPGA architecture was carried out. Since FPGA was a platform on which controller hardware was developed, a thorough survey across a wide family of FPGAs was conducted in order to select a suitable FPGA that can accommodate a highly complex adaptive control technique (IFT).

- design of a Dedicated IFT Microcontroller and development of VHDL code; simulation and experimentation; analysis and discussion of results.

- optimisation of a Dedicated IFT Microcontroller architecture; simulation and experimentation; analysis and discussion of results.

- testing of the Dedicated IFT Microcontroller to a novel process.

- analysis and discussion of results.

- thesis report write-up.

## 1.7 PLAN OF DEVELOPMENT

Chapter two discusses the literature review on IFT technique theory and applications, FPGA-based controllers, and FPGA Design Methodologies for the Industrial Control System. Chapter three reports the study and validation of the IFT technique, with a view to creating a Dedicated IFT Microcontroller. Chapter four describes the design of a Dedicated IFT Microcontroller. Chapter five describes the testing of a Dedicated IFT Microcontroller. New contributions, recommendations and Chapter Summarys are provided in Chapter six.

## CHAPTER TWO

### LITERATURE REVIEW

## 2.1 SEARCH OBJECTIVE

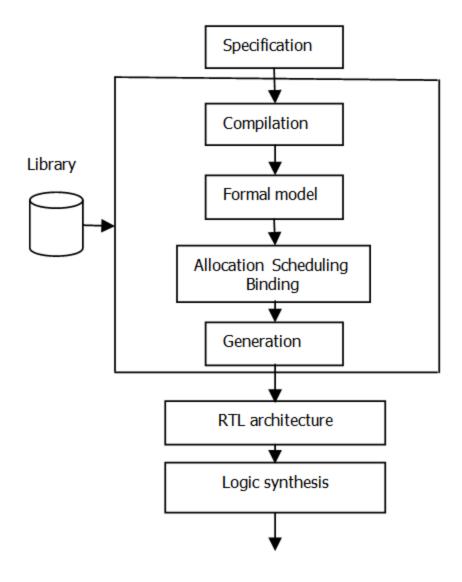

Since the main objective of the thesis was to design a Dedicated IFT Microcontroller, the preliminary task was to explore the IFT theory and its applications, mainly its recent advances: the improved algorithm, its extension, and the combination with other algorithms. In addition, a great deal of literature on FPGA design methodology for industrial control systems, Microcontroller design principles, and FPGA theory and trends were reviewed and this formed the major part of the project. Furthermore, a survey of electronic design tools and other application software was done. These included Quartus II Web Edition, ModelSim-Altera Web Edition, Xilinx ISE and Vivado HLS.

## 2.2 IFT TECHNIQUE APPLICATIONS SURVEY

A vast number of IFT applications currently existing or described in literature are a motivating factor in the pursuance of the thesis entitled "Design of a Dedicated IFT Microcontroller". Some of these applications surveyed are outlined below:

- In [2], IFT was applied to optimise the Electronic Throttle Control (ETC) system of an engine. The application showed that the IFT provides very good performance for controller tuning. The system was implemented on a Pentium processor and was carried out experimentally. This has clearly shown the need to develop a dedicated hardware for its implementation, in order to reduce the cost and improve its performance in the long run.

- In [3], IFT was applied to tune PID parameters in applications where the objective is to achieve a fast response, to set point changes, and the performance of IFTtuned PID controllers was compared to the performance of the classical tuned PIDcontrollers. It revealed better results (faster settling time) than the later. The work was carried out through simulation examples. Thus, a simple and efficient PIDtuning scheme was developed in this particular work though non-experimental work, however, no experimental verification was conducted.

- In [4], a relay auto-tuning of PID controllers using IFT was applied to a process control problem in which the PID controller was auto-tuned to give specific bandwidth and phase margin. The algorithm was tested in the laboratory on a coupled tank, and the theoretical results were demonstrated to be observed in practice, confirming the viability of the IFT technique.

- In [15], the extension of IFT as a tuning algorithm was presented. informative data was used to improve the convergence properties of the method, and reduce the total number of required plant experiments, especially when tuning for disturbance rejection. This was achieved through application of an external probing signal in the tuning algorithm. The technique was further used to guarantee nominal stability and to improve the parameter update using a line search algorithm for determining iteration step size, through the use of Levenberg-Marquardt optimisation. The proposed algorithm was compared to classical formulation in the simulation study of the disturbance rejection problem. It was found that perturbed IFT is an advantage when tuning for disturbance rejection.

- In [16], tuning of robot joint controllers using IFT was considered, different IFT schemes were validated in simulation, and real experiments on an industrial robot manipulator were conducted. From a practical point of view, the scheme therefore offers several advantages: it is straightforward to apply the direct optimal tuning algorithm, particularly to basic control loops in the process industry, which are typically PID loops. In addition, IFT has high potential for tuning of controllers applied to non-linear systems, which is currently a challenge in industrial control. With favourable results having been obtained, the need has arisen to develop a chip that implements the technique.

- In [17], IFT was applied to tune a second-degree-of-freedom (2DOF) PID-controller to minimise the given quadratic cost function of a system output error and control effort. The tuning effort was divided into two parts. First, the classical 1DOF PID controller was iteratively tuned and the remaining parameters of 2DOF PID were then tuned, independently in the next iterative procedure; and second, the Broyden-Fletcher-Glodfard-Shanno (BFGS) method as a quasi-Newton method was employed. From the numerical simulations and the experiments, the

effectiveness of the proposed method was shown. For experimental purposes, the controller was implemented into the PC, a clear indication that IFT could be feasible to be implemented into a custom device such as a Microcontroller or an FPGA.

In addition to the above surveyed IFT applications, FPGA-based controllers were also surveyed and a sample of them are listed in the next subsection. The purpose of this survey was to ascertain the feasibility and benefits of using an FPGA as a platform for developing the Dedicated IFT Microcontroller.

## 2.3 FPGA-BASED CONTROLLERS LITERATURE REVIEW

The surveyed literature on FPGA-based controllers and FPGA Design Methodology for Industrial Control Systems is summarised as follows:

- In [12], the state of the art of FPGA based controller design was reviewed. The design methodologies utilised three main design rules given as algorithm refinement, modularity, and systematic search for the best compromise between control performance and architectural constraints. Two complete case studies on the benefits of FPGA implementation, when using the proposed system modelling and design methodology were presented. A control algorithm, when implemented in an FPGA, can have a short execution time due to the high degree of parallelism of its architecture. Another perspective on FPGA design is to use FPGAs with analogue to digital converter (ADC) and digital to analogue converter (DAC) imbedded in them. Only Microsemi have fused an ADC into their FPGA to date.

- In [13], a motion control system, using a radial basis function neural network (RBF NN) self-tuning PID controller for X-Y table was realised in an FPGA, to create a motion control-integrated circuit (IC). This was done by hardware/software co-design (a necessary concept nowadays), and as a result the final product was made more compact, robust, flexible, and costeffective. The work was experimental and revealed favourable results. An IC that implements self-tuning PID was developed into the FPGA device.

- In [14], a novel technique for implementation of an efficient FPGA-based PIDcontroller for motion control of a permanent magnet DC motor is presented. This implementation technique circumnavigates the problem of interfacing an analogue-to-digital converter in real time. The implementation was done on the Xilinx Spartan 3 FPGA Board from National Instruments. The design showed significant improvement over the present way of implementing digital controllers into microcontrollers.

- In [18], a digital controller for a switching power converter was implemented in an FPGA device. The digital hardware using Very Large Scale Integrated Circuit Hardware Description Language (VHDL) with floating-point arithmetic were both verified by simulation and experiments. The results showed that the designed system meets its specification, and the simulations match the experimental results closely.

- In [19], a modular design of embedded feedback controllers was studied by utilising simulations into the FPGA hardware. To this end, a novel distributedarithmetic (DA)-based PID-controller algorithm was proposed and integrated into a digital feedback control system. The DA-based PID-controller demonstrated 80% savings in hardware utilisation and 40% savings in power consumption, which is desirable in embedded control applications. Simulations and experiments were tested using the system; it demonstrated good closed-loop stability and performance.

- In [20], a methodology was presented based on the control system L1 or I1 norms for computing the appropriate number of bits to represent each quantity when using fixed-point number representation. The methodology was shown to be effective for designing hardware for both shift-form and delta-form representations of the compensator, and was applied to a magnetic bearing control system. In this example, the delta-form realisation required less hardware than shift-form realisation.

- In [21], a simple auto-tuning technique for digitally controlled dc-dc for synchronous buck converters was proposed; this was an approach based on a relay feedback method. By the use of the iterative procedure, the tuning of PID parameters as a

result was obtained directly by including the controller in the relay feedback. Experimental investigations were conducted using the FPGA platform.

2.4 Chapter Summary

Considering the surveyed literature within the subject of the IFT technique applications based on FPGA technology, only [21] is directly related to the IFT technique, but its application is specific to Buck converters. The authors does not investigate, nor specify, whether the technique could be used for other plants.

## CHAPTER THREE

## STUDY AND VALIDATION OF IFT TECHNIQUE

## 3.1 INTRODUCTION

In this chapter, the IFT technique is studied and validated. This is accomplished by carrying out an overview of the technique's basic theory, followed by simulation on NI LabView software, mainly for the purpose of testing and validating it before committing it to hardware. The reason for the choice of LabView software as the platform for simulation, is that programs running on the LabView platform can easily be ported to VHDL with minimal modifications. To ensure an exhaustive investigation, the IFT is tested and validated by applying it to three types of plants, namely: a DC motor, an oscillatory plant, and an unstable plant. It is also tested by varying the amplitude of the reference signal, and also by using the single-step signal. The intention of exploring all of these possibilities is meant to firmly expose the IFT boundaries of applicability so that the final product is not vulnerable to unnecessary post-production discoveries such as operational errors.

## 3.2 ITERATIVE FEEDBACK TUNING TECHNIQUE OVERVIEW

Since the Dedicated IFT Microcontroller is based on the IFT technique, we consider a comprehensive overview of IFT basic theory in this section.

The IFT technique is purely a data-driven and gradient-based approach for optimising controller parameters, without full knowledge of the plant [9, 25]. It yields an unbiased estimate of the model (meaning that the IFT finds the correct controller for the plant in operation) [25]. Its concept derives from the given controller structure (given in advance), and the specification of a criterion or objective function of a Linear Quadratic Gaussian (LQG). The LQG is formed by data that is collected from closed-loop experiments, in which the number of experiments depend on the degree of freedom of the controller in question. For example, a second-degree-of-freedom (2DOF) controller would require three experiments to be performed at each stage of the iterative design, while a first-

degree-of-freedom (1DOF) controller would require only two batch experiments expected to be run at each stage of the iterative design. Thereafter, either of the gradient-based local minimisation techniques, such as steepest descent, the Hessian, Gauss-Newton, or Quasi-Newton [22], can search a minimum of the criterion LQG.

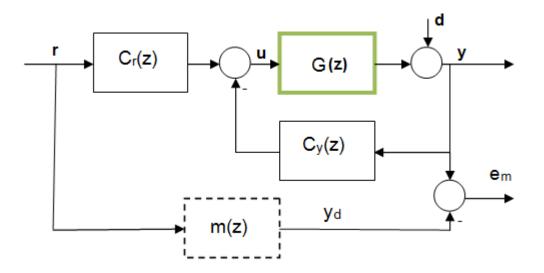

In this section we describe the IFT technique of a second-degree-of-freedom controller  $(C = \{C_r, C_y\})$ , so that investigations of implementation issues relevant to the design of the Dedicated IFT Microcontroller are simplified. The IFT technique is implemented on the discrete linear time invariant system *G*, as shown in figure 1.

# Figure 1: Block diagram of a closed loop system of a two-degree-of-freedom controller

- {r(t)} is the reference signal; the argument t is added to denote the sampling period,

- u(t) and y(t) are control and output signals respectively.

- $C_r(z,\rho)$  and  $C_y(z,\rho)$  are linear time-invariant transfer functions;

- $\rho$  is a vector of the PI controller parameters;

- *m*(*z*) and *e<sub>m</sub>* are the desired model for the controlled system, and the modelling error respectively.

The internal closed loop signals can be described via sensitivity function S and transfer function  $T_r$ , as follows:

$$u(t) = C_r * S * r(t) - C_y * S * d(t)$$

(1)

$$y(t) = T_r * r(t) + S * d(t)$$

(2)

Where  $S = \frac{1}{1 + G * C_y}$  and  $T_r = \frac{G * C_r}{1 + G * C_y}$

The output of the desired model is formulated from figure 1, and given in equation (3).

$$y_d = T_d * r(t) \tag{3}$$

Where  $T_d = m(z)$

Finally, the modelling error is computed from equation (4).

$$e_m(t) = y(t) - y_d \tag{4}$$

Figure1 can be simplified into an IFT of a 1DOF controller if  $C_r \cong C_y = C$ . The 1DOF controller runs only two experiments, and we will use it to formulate the hardware architecture for the design of a Dedicated IFT Microcontroller later, due to its simplicity compared to the 2DOF controller. The signals in equations (1), (2), (3), and (4) are measured in experiment#1, however, signals like the closed-loop error (e(t) = r(t) - y(t)), and the modelling error  $e_m(t)$ , are stored, since they are used to generate a reference signal and the criterion function in experiment#2. The reference signal r(t) in experiment#1 is also used as a reference signal in experiment#3 for the 2DOF controller.

The IFT procedure for the 2DOF controller experiments is as follows: At iteration i of the controller tuning algorithm, the controller  $C(z, \rho_i) = \{C_r(z, \rho_i), C_y(z, \rho_i)\}$  operates on the actual plant. Thereafter, three experiments are run, with each experiment storing a sequence of N-length data, as depicted in table 1.

Experiment#1 and experiment#3 consist only of gathering data under normal operating conditions, with the closed loop using the same reference signal for the said experiments [9]. Experiment#2 collects data from the closed-loop system with a reference signal( $r - y(\rho)$ ) derived from experiment#1. From now on we denote the N-length reference signal and the corresponding output signals by  $\{r_i^j\}$  and  $\{y_i^j(\rho_i)\}$  respectively. Where i = 0,1,2,...,N, a sample number or iteration number, and j = 1,2,3 is an experiment number.

| Experiment# | Input signal                            | Measured signals                                                                               | Stored                                                  |

|-------------|-----------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| j           |                                         |                                                                                                | signals                                                 |

|             |                                         |                                                                                                |                                                         |

| 1.          | $r_i^{j} = r$                           | $y^{j}(\rho_{i}) = T(\rho_{i}) * r_{i}^{j} + S(\rho_{i}) * d_{i}^{j}$                          | $e^{j}, e_{m}$ and $y^{j}$                              |

|             |                                         |                                                                                                |                                                         |

|             |                                         | $u^{j}(\rho_{i}) = S(\rho_{i}) * C_{r}(\rho) * r_{i}^{j} - C_{y}(\rho_{i})d_{i}^{j}$           |                                                         |

|             |                                         | $e_m = y^j - y_d$                                                                              |                                                         |

|             |                                         | $e^{j} = r_{i}^{j} - y^{j}$                                                                    |                                                         |

| 2.          | $r_i^{\ j} = e^{\ j} - y^{\ j}(\rho_i)$ | $y^{j}(\rho_{i}) = T(\rho_{i})(r_{i}^{j} - y^{j}(\rho_{i})) + S(\rho_{i})^{*}d_{i}^{j}$        | $rac{\partial e_{_{m}}}{\partial  ho}( ho_{_{i}})$ and |

|             |                                         | $u^{j}(\rho_{i}) = S(\rho_{i}) * C_{r}(\rho) * (r_{i}^{j} - y^{j}) - C_{v}(\rho_{i})d_{i}^{j}$ |                                                         |

|             |                                         | $e^{j} = r_{i}^{j} - y^{j}(\rho_{i})$                                                          | $\frac{\partial u^{j}}{\partial \rho}(\rho_{i})$        |

|             |                                         | $c = r_i  y  (p_i)$                                                                            | $\partial \rho $ (1)                                    |

| 3.          | $r_i^{j} = r_i^{j}$                     | $y^{j}(\rho_{i}) = T(\rho_{i}) * r_{i}^{j} + S(\rho_{i}) * d_{i}^{j}$                          | Same as in                                              |

|             |                                         | $u^{j}(\rho_{i}) = S(\rho_{i}) * C_{r}(\rho) * r_{i}^{j} - C_{y}(\rho_{i})d_{i}^{j}$           | experiment#1                                            |

|             |                                         | $e^{j} = r_{i}^{j} - y^{j}(\rho_{i})$                                                          |                                                         |

Table 1: IFT signals for experiment#1, experiment#2 and experiment#3

All the signals from figure 1 are tabulated in table 1 as  $r_i^1, e_i^1, u_i^1, y_i^1, d_i^1$ , denoting the reference, error, control, plant output, and disturbance signals in experiment#1

respectively; for experiment#2, these signals are denoted by  $r_i^2$ ,  $e_i^2$ ,  $u_i^2$ ,  $y_i^2$ ,  $d_i^2$ , and by  $r_i^3$ ,  $e_i^3$ ,  $u_i^3$ ,  $y_i^3$ ,  $d_i^3$  in experiment#3.

After the experiments, the processing stage commences with the gradient calculation, followed by the selection of a positive definite matrix R, and finally, the updating of the controller parameters. We illustrate the sequence, beginning with the formulation of the criterion function.

The modelling error and the controller output signals that are measured from the experiments, are assembled together with filters and constants to form a criterion function, as given in equation (5).

$$J(\rho_i) = \frac{1}{2N} E\{\sum_{i=0}^{N} [(L_e * e_m(\rho_i))^2 + \lambda * (L_u * u^1(\rho_i))^2]\}$$

(5)

Where  $L_e$  and  $L_u$  are frequency-dependent weights or filters that penalise the modelling error  $e_m$  and control input  $u^1$ , according to the designer's needs. E{...} is the expectation taken with respect to stochastic disturbances that enter the process and thus affect the closed loop.

Each version of the criterion function defines a specific type of IFT. Some types of IFT criterion functions are, for example, where the cost function is obtained from the modelling error  $e_m$ , as in equation (5), from the traditional error e, or from the traditional error without the control signal u included in the cost function.

Many specific IFT criterion functions can be formulated as in equation (5), by varying the type of desired model. The IFT criterion function, driven by the traditional error, depends heavily on the model of the plant, since different plants would produce different traditional errors. The use of the traditional error to formulate the cost function is achieved by making the desired model, m(z) = 1.

The objective of the IFT is to find an optimal set of parameters  $\rho$ , which minimises the criterion function *J*, as given in equation (6). This is the minimisation of the cost function, also given in equation (7) later, in another form [11].

$$\rho_{i+1} = \arg\min J(\rho_i) \tag{6}$$

The major stumbling block for the solution of this optimal control problem is the computation of the gradient of the criterion function with respect to controller parameters [9]. The gradient of the criterion function is thus given by equation (7), with the frequency weighting filters set to one (thus  $L_e = L_u = 1$ ) for simplicity, but they are important, since they give extra flexibility in optimisation of the criterion function.

$$\frac{\partial J}{\partial \rho}(\rho_i) = \frac{1}{N} * \sum_{i=0}^{N} [e_m(\rho_i) * \frac{\partial e_m}{\partial \rho} (\rho_i) + \lambda * \sum_{i=0}^{N} u^1(\rho_i) * \frac{\partial u^1}{\partial \rho}(\rho_i)$$

(7)

The necessary condition for optimality of the parameters is  $\frac{\partial J}{\partial \rho}(\rho) = 0$ . Hence, to be able to compute such an equation for  $\rho$ , the model of the plant, in totality, is required. In this respect, the plant model is generally not known in most industrial applications, and therefore, the required analytical form cannot be obtained. The main contribution of the IFT was to circumvent the said problem, by offering a procedure to calculate the gradient  $\frac{\partial J}{\partial \rho}(\rho)$  directly from closed-loop data. Hence, the IFT is entirely a data-based paradigm, implying that it can easily be implemented into a DSP microcontroller (best for algorithms [12]), as opposed to an FPGA device that has parallel attributes.

If the gradient  $\frac{\partial J}{\partial \rho}(\rho)$  could be computed, then the solution of equation (7) would be obtained by stochastic approximation of Robins and Monro of 1951 [15], given as

$$\rho_{i+1} = \rho_i - \gamma_i * R_i^{-1} \frac{\partial J}{\partial \rho}(\rho_i)$$

(8)

In equation (8),  $\gamma$  (gamma) is a positive real scalar that determines the step size. It can be fixed or established by a line search. The matrix *R* is some appropriate positive definite matrix that determines the amplitude of the steps (or the step sizes), in the direction of each parameter provided by either the steepest descent, the Gauss Newton method, or the Quasi Newton method. The choice of *R* as an identity matrix renders a steepest descent gradient that is normally negative and also slow to converge, but would be beneficial for power consumption, because it does not require much resource of the FPGA device. The choice of *R* as a Hessian matrix is not feasible – even in the literature, the approximation of the Hessian is preferred over the Hessian matrix directly [3, 4, 5, 6, 8]. This can be generated by the Gauss Newton method (as shown in equation (9)), or the Quasi Newton method [25, 26], however, hardware implementation into an FPGA would be complicated and would demand high power consumption since huge FPGA resource shall be required.

$$R_{i} = \frac{1}{N} * \sum_{i=1}^{N} \left( E\left[\frac{\partial e_{m}}{\partial \rho}(\rho_{i})\right] E\left[\frac{\partial e_{m}}{\partial \rho}(\rho_{i})\right]^{T} + \lambda * E\left[\frac{\partial u^{1}}{\partial \rho}(\rho_{i})\right] E\left[\frac{\partial u^{1}}{\partial \rho}(\rho_{i})\right]^{T}$$

(9)

The Quasi Newton choice of *R* is covered widely in [11, 17].

#### 3.2.1 Generation of the gradients for modelling error and controller signal

The main difficulty with IFT is the problem with calculation of the gradient of the criterion function J, with respect to controller parameters, since the model of the plant is not known. This problem is resolved through filtering the modelling error and the controller output signals. The output of these filters are the gradients of the respective signals, which are measured and stored to compute the gradient of the criterion function, as shown in equation (7).

Noting that

$\frac{\partial e_m}{\partial \rho}(\rho_i) = \frac{\partial y}{\partial \rho}(\rho_i)$ , since it is the plant that causes variation in the modelling error  $e_m$ , we state the expressions in equations (10) and (11). These are standard IFT equations,

derived in [9, 26].

$$\frac{\partial e_m}{\partial \rho}(\rho_i) = \frac{\partial}{\partial \rho}(y^1) = \frac{\partial}{\partial \rho}(T(\rho_i) * r + S(\rho_i) * d_i)$$

$$=\frac{1}{C_r(\rho)}*\left[\left(\frac{\partial C_r}{\partial \rho}(\rho_i)-\frac{\partial C_y}{\partial \rho}(\rho_i)\right)y^3+\frac{\partial C_y}{\partial \rho}(\rho_i)y^2\right]$$

(10)

$$\frac{\partial u^{1}}{\partial \rho}(\rho_{i}) = \frac{\partial}{\partial \rho}(u^{1}) = \frac{1}{C_{r}(\rho)} * \left[ \left( \frac{\partial C_{r}}{\partial \rho}(\rho_{i}) - \frac{\partial C_{y}}{\partial \rho}(\rho_{i}) \right) u^{3} + \frac{\partial C_{y}}{\partial \rho}(\rho_{i}) u^{2} \right]$$

(11)

The first term in equation (10) is a filter, taking the output signal from the plant  $y^3$  as input, and the second term in equation (10), also a filter taking  $y^2$  as input. The output of the two filters are passed via two input adders to produce the gradient of the modelling error. Similarly, the first term of equation (11) is a filter, taking signals from the controller  $u^3$  as input, and the second term also a filter taking an input signal  $u^2$  from the controller. The output of the two filters are also passed via two input adders to produce the gradient of the controller output. It is shown here that gradients of a criterion function are signals measured from the closed loop system, and applied in equation (7) to compute the gradient of *J* with respect to controller parameters.

#### 3.2.2 IFT technique of a 1DOF controller

Having described the IFT technique for a 2DOF controller, we present here the IFT technique for the 1DOF controller. This is aimed at implementation on the FPGA hardware, because its algorithm is simpler than the IFT technique of the 2DOF controller. As mentioned previously in section 3.2, it runs two experiments compared to three of IFT technique for the 2DOF controller. The choice of degree of freedom depends mainly on

application needs. For example, the IFT of the 2DOF controller is good for disturbance rejection, and the IFT for the 1DOF controller is good for reference signal tracking and regulation [26].

In this section, we develop a deterministic version of Iterative Feedback Tuning for the case of a simple PI controller, so that the design of the Dedicated IFT Microcontroller is simplified. The PI controller is chosen because it is a very common control law, and hence a reasonable starting point. It is also important to industrial applications [22].

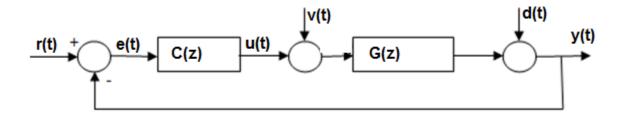

We investigate a single input, single output control system of 1DOF control law, as shown in figure 2.

Figure 2: Closed Loop System for 1DOF controller

The reference, error, input disturbance, controller output, output disturbance, and plant output signals are represented by r(t), e(t), v(t), u(t) d(t) and y(t) respectively. The plant G(z) is a step invariant transformation of the DC motor  $(\frac{1.01}{2s+1})$  used in [1]. This was chosen to validate the IFT technique, by comparing its performance on the FPGA, with that of [1]. C(z) is the PI controller, which is a step transformation of the s-domain PI controller ( $\rho_0 + \frac{\rho_1}{s}$ ). The internal closed loop signals can be described with sensitivity and transfer functions (considering d(t) = 0), as follows:

$$u(t) = C * S * r(t) - C * S * d(t)$$

(12)

$$y(t) = T_r * r(t) + S * d(t)$$

(13)

Where  $S = \frac{1}{1+G^*C}$  and  $T_r = \frac{G^*C}{1+G^*C}$

We consider d(t) as zero mean weakly stationary random noise.

Experiment#1 of the 1DOF controller measures and stores signals  $e^{1}(\rho)$ ,  $u^{1}(\rho)$ , and  $y^{1}(\rho)$  for N length of time. Rho is a constant for each set of two experiments (#1 to #2). However, it is changed after every experiment#2, thus rho is used as an argument. Experiment#2 is known as the gradient experiment, where the gradient of the modelling error and control input signals are measured and stored. Thereafter, the criterion function J is specified by utilising the measured signals in experiment#2, and exiperiment#1. After summing over N-length samples, the gradient ( $\frac{\partial J}{\partial \rho}$ ) of the criterion function, needed to optimise or update the PI-controller parameters, is obtained.

#### 3.2.3 Criterion function specification

Controller optimisation requires that a criterion function is defined, usually by expressing it in terms of J, as given in equation (5). We rewrite the criterion function expression, since it utilises the traditional error  $e^2$ , and not the modelling error  $e_m$  used in equation (5). The desired model is set to unity (desired model, m(z) = 1), implying that the cost function, that optimises the controller parameters, is as a result of the summation of the traditional error, and the controller output signals which was obtained from experiment#2, and given in equation (14) below.

$$J = \frac{1}{2N} \sum_{i=0}^{N} \left[ (L_e * e^2(\rho))^2 + \lambda * (L_u * u^2(\rho))^2 \right]$$

(14)

$e^2$  denotes the traditional error from experiment#2, and  $u^2$  the control signal. The first term is the closed loop tracking error, and the second term the penalty on the control

effort from experiment#2.  $L_e$  and  $L_u$  in the first and second terms are frequency weighting filters that were initialised to one  $(L_e = L_u = 1)$  to simplify the hardware to be implemented on the FPGA, though it does give extra flexibility in the control action. The advantage of this criterion function is that it presents a good balance between overshoot and settling time [24], and it simplifies the hardware design since the desired model is reduced to unity, It also makes the assumption for a plant structure become insignificant, since the desired model is reduced to a scalar. However, the main drawback of this criterion function, as compared to other minimisation criterion functions, is the difficulty of obtaining an analytical solution to the controller design [24].

After formulating the criterion function J, we minimise it by generating its gradient through summation, as given by equation (15).

$$\frac{\partial J}{\partial \rho}(\rho_i) = \frac{1}{N} \sum_{i=0}^{N} \left[ e^2(\rho_i) \frac{\partial e^2}{\partial \rho}(\rho_i) + \lambda * u^2(\rho_i) \frac{\partial u^2}{\partial \rho}(\rho_i) \right]$$

(15)

$e^2$  denotes a traditional error, and  $u^2$  denotes a control signal. Once the gradient  $\frac{\partial J}{\partial \rho}$  is computed, the solution of equation (15) is found in the same way it is done in the IFT of the 2DOF controller.

#### 3.2.4 Algorithm formulation for 1DOF

The algorithm is formulated in two segments, namely experiment#1 and experiment#2.

Experiment#1 comprises equations (16), (17), (18) and (19). Equation (16) compares the reference signal and plant output signal, to produce the traditional error, as shown in figure 2.

$$e^{1}(t) = r_{i}^{1}(t) - y^{1}(t)$$

(16)

The PI-controller, without a holding circuit (ZOH), is required for the formulation of a filter  $(\frac{1}{C} * \frac{\partial C}{\partial \rho})$  (in z-domain), for generating gradients needed for computation of the gradient of the cost function, as shown in equation (15). The reason for this is because the IFT loop from the traditional error to parameter update is purely a digital process, hence does not require usage of a DAC or ADC. The PI controller on the other hand, with a holding circuit (ZOH), is required because its output drives a DAC for actuating the plant. For this reason, the transformation of the PI controller transfer function into a digital equation, without a ZOH circuit, and with a ZOH circuit, is given in appendix V, yielding difference equations, as given in equations (17) and (18).

$$u_{t} = u_{t-1} + (\rho_{0} + \rho_{1}) * e_{t} - \rho_{0} * e_{t-1}$$

[V] (17)

$$u_{t} = u_{t-1} + \rho_{0} * e_{t} + (\rho_{1} * T - \rho_{0}) * e_{t-1}$$

[V] (18)

We also transform the plant into a digital equation with a ZOH circuit, since the output of a plant is connected to an ADC.

Transformation to the Z-domain begins by first setting the sampling time for the plant according to the governing principles of the Nyquist sampling theorem. This theorem states that the "sampling frequency  $f_s$  for a given source signal should be at least double the signal frequency". In our simulation, the sampling frequency adopted is 2.5 times the signal frequency. This is to ensure that the digital system mimics the continuous system. Thus

$$f_s = 2.5 * \frac{1}{T}$$

T is the time constant for the DC motor model or plant. In this case, the sampling frequency = 5 Hz, yielding a sampling time of 200 ms.With this sampling time in place, the plant digital equation is derived as shown in equation (19). Derivation details for the plant digital equation is presented in Appendix V.

$$y(t) = 0.904837 * y(t-1) + 0.09516 * u(t)$$

<sup>(19)</sup>

The equations of (20), (21), (22), (23), (24), (25), (26), (27), and (28), as shown below, describe the algorithm of experiment two.

The plant output signal  $y^2(t)$ , is compared with the reference signal  $e^1(t)$  (from experiment#1), as achieved by equation (20).

$$e^{2}(t) = e^{1}(t) - y^{2}(t)$$

(20)

The PI-controller is reproduced in experiment#2, to generate a control signal,  $u^2(t)$ , and is given equation (21).

$$u_t^{2} = u_{t-1}^{2} + \rho_0 * e_t^{2} + (\rho_1 * T - \rho_0) * e_{t-1}^{2}$$

<sup>(21)</sup>

The plant output signal,  $y^2(t)$  in experiment#2, is given in equation (22).

$$y^{2}(t) = 0.904837 * y^{2}(t-1) + 0.048057 * u^{2}(t)$$

(22)

The difference equations for generating the gradient of the error signal,  $\frac{\partial e^2}{\partial \rho}$ , with respect to controller parameters directly, were developed by Hjarmarsson in 1994 [5], and were an important advance in the development of adaptive controllers. This was achieved by passing the error signal through a filter  $\frac{1}{C} * \frac{\partial C}{\partial \rho}$  and measuring the output, which yielded the gradient of the error signal required for specification of the cost function. This was developed in order to circumvent the difficulty in computation of the gradient of the cost function, as some quantities involved are unknown or only partially known [5].

The difference equations for the gradient signals are derived as follows:

The PI-controller, given in equation (17), is used to derive the gradient difference equations, as shown below:

$$\frac{1}{C} * \frac{\partial C}{\partial \rho} = \frac{1}{C} * \begin{bmatrix} \frac{\partial C}{\partial \rho_0} \\ \\ \frac{\partial C}{\partial \rho_1} \end{bmatrix} = \frac{z-1}{(\rho_0 + \rho_1) * z - \rho_0} * \begin{bmatrix} 1 \\ \\ \frac{z}{z-1} \end{bmatrix} = \begin{bmatrix} \frac{z-1}{(\rho_0 + \rho_1) * z - \rho_0} \\ \\ \frac{z}{(\rho_0 + \rho_1) * z - \rho_0} \end{bmatrix} = \begin{bmatrix} \frac{de^2}{d\rho_0} / e^2 \\ \\ \frac{de^2}{d\rho_1} / e^2 \end{bmatrix}$$

Additionally, the difference equations are given in equations (23) and (24).

$$\frac{de^2}{d\rho_0}(t) = \frac{\rho_0}{\rho_0 + \rho_1} * \frac{de^2}{d\rho_0}(t-1) + \frac{1}{\rho_0 + \rho_1} * (e^2(t) - e^2(t-1))$$

(23)

$$\frac{de^2}{d\rho_1}(t) = \frac{\rho_0}{\rho_0 + \rho_1} * \frac{de^2}{d\rho_0}(t-1) + \frac{1}{\rho_0 + \rho_1} * (e^2(t))$$

(24)

The gradient of the criterion function, which is a summation of measured signals,  $e^{2}(t)$ ,

$$u^{2}(t), \frac{de^{2}}{d\rho}$$

, and  $\frac{du^{2}}{d\rho}$ , are given in equations (25) and (26).

$$\frac{dJ}{d\rho_0}(t) = \frac{dJ}{d\rho_0}(t-1) + e^2(t) * \frac{de^2}{d\rho_0}(t)$$

(25)

$$\frac{dJ}{d\rho_1}(t) = \frac{dJ}{d\rho_1}(t-1) + e^2 * \frac{de^2}{d\rho_1}(t)$$

(26)

The parameter update expressions are given in equations (27) and (28).

$$\rho_0(t) = \rho_0(t-1) - \gamma_i * \frac{dJ}{d\rho_0}$$

(t) (27)

$$\rho_1(t) = \rho_1(t-1) - \gamma_i * \frac{dJ}{d\rho_1}(t)$$

(28)

The equations from (16) to (28) outline the flow of the IFT technique applied to a controller of 1DOF, and can be mapped onto the Matlab or LabView platforms, for simulation purposes.

In section 3.3, this is done, with LabView, mainly to take advantage of LabView's FPGA add-on software, which can be compiled for downloading into an FPGA device.

### 3.3 SIMULATION OF IFT TECHNIQUE USING THE LABVIEW PLATFORM

This section is devoted to validating and testing the IFT "to destruction", so that the boundaries of its applicability can be obtained. This is done to avoid unnecessary post-production discoveries in the final product that may seriously impact on its commercial viability. In order to carry out a wide investigation, three different plants were used in the simulation, namely: the DC Motor that was used in [1], and is reproduced here (in equation (29) for ease of reference), the oscillatory plant given in equation (30), and the unstable plant given in equation (31).

$$g(s) = \frac{1.01}{2s+1}$$

(29)

$$g(s) = \frac{10}{s^2 + 3s + 10} \tag{30}$$

$$g(s) = \frac{1}{2s - 1} \tag{31}$$

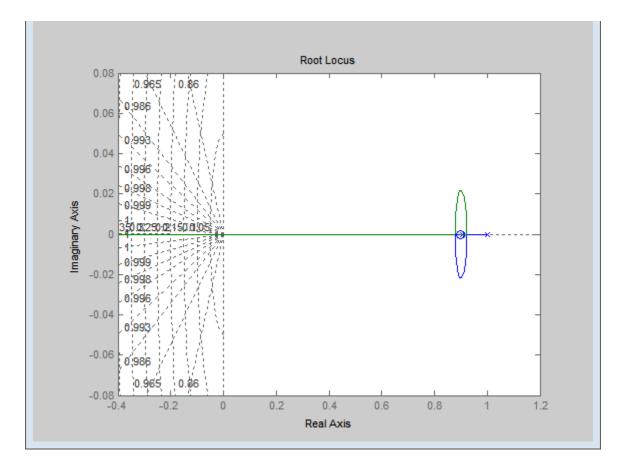

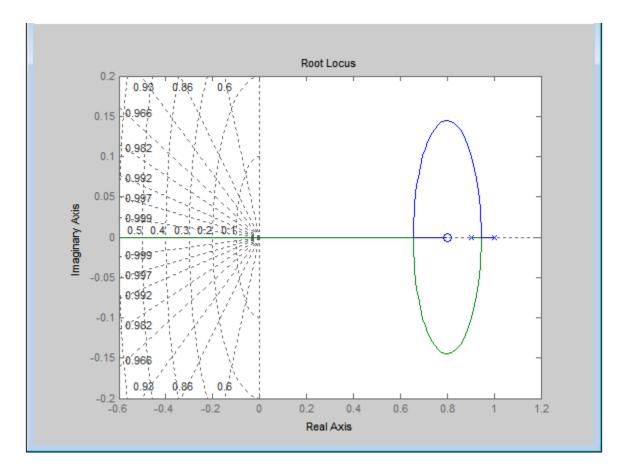

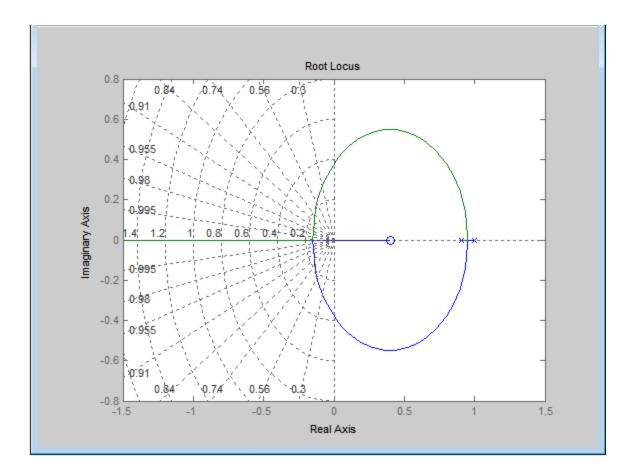

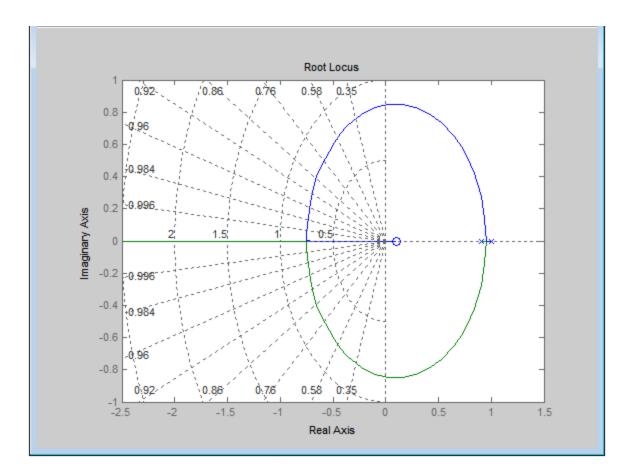

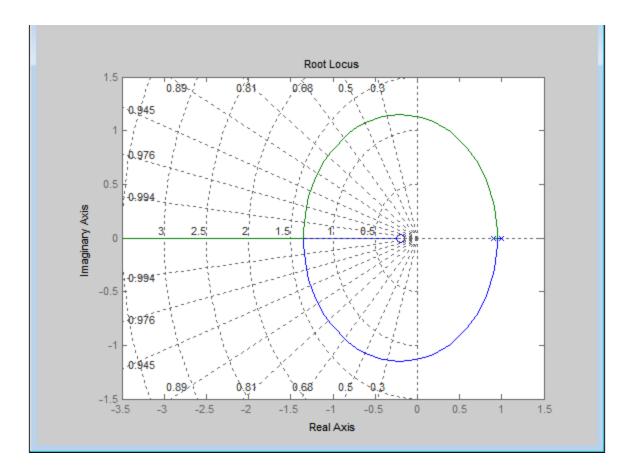

Though IFT assumes that knowledge of the plant is not available or only partially known, the initial focus will be on the DC motor (a known plant), controlled by the PI-controller, for validation and testing purposes. The region of controller parameters are determined, which yields a stable closed-loop system in the z-plane by use of the root locus method, to provide preliminary information (especially the initial controller parameters for running the IFT) for the test and validation of the IFT technique, before simulation (on the LabView platform) is commenced. The PI controller and the DC motor in the z-domain with the holding circuits are derived in appendix V, and is stated here for easy of reference: the PI controller represented in the z-domain with a holding circuit is given as:

$$u(z) = \frac{\rho_0 * z + (\rho_1 * T - \rho_0)}{z - 1}$$

Similarly, the DC motor model is also given as  $\frac{0.09516}{z - 0.9048057}$ .

The open-loop PI controller applied to the DC motor is given as

$$k(z) * gh(z) = \frac{\rho_0 * z + (\rho_1 * T - \rho_0)}{z - 1} * \frac{0.09516}{z - 0.9048057}$$

, yielding open-loop poles at  $z = 1$  and

z = 0.9048057, with one moving zero ( $z = 1 - \frac{\rho_1}{\rho_0}T$ ) since it is dependent on the controller

parameters which are varying due to the controller tuning, and the sampling time that is chosen by the designer in relation to the sampling time of the plant. That is, the sampling time for the controller should be faster than that of the plant. We determine the  $\frac{\rho_1}{\rho_0}$  ratio,

since the zero must lie in the region -1 < z < 0.9048057 to force the locus of the closed-loop poles inside the unit circle, in order to help to pull the poles outside, into the unit circle. To expose the stability region for the closed-loop system, the closed-loop system is derived for the PI controller applied to the DC motor. The derivation is given in appendix V for equation (32).

$$\frac{y(z)}{r(z)} = \frac{0.09516*\rho_0*(z+(\frac{\rho_1}{\rho_0}*T-1))}{z^2+(0.095*\rho_0-1.90)*z+(0.90+0.095*\rho_1*T-0.095*\rho_0)} [V/V]$$

(32)

This equation is a closed-loop PI controller applied to the DC motor. It is expressed in such a way that the root locus can easily be applied to tracing the poles of the system. However, to perform the procedure, the controller parameters must first be chosen, because the zero of the open-loop system must lie within the range -1 < z < 0.9048057 on the left-hand side of the two open-loop poles in the z-plane. For each chosen zero, the parameters are computed, followed by running the root locus and verifying the region of stability. To determine the parameters, the zero location is chosen, and to simplify the design, the open-loop system zero should lie on real axis from z = -0.9 to z = 0.9.

From this point on, rho0 and rho1 will be used in the text to denote  $\rho_0$  and  $\rho_1$  respectively. For each zero location chosen, controller parameters are computed using

the expression  $1 - \frac{\rho_1}{\rho_0} * T$  (the moving zero). rho0 is then chosen with the knowledge that, as it varies from 0 to infinite gain, the closed-loop poles move towards open-loop and infinite zeros. Hence, if the rho0 value is chosen for oscillatory, under-damped, fastdamped, critically damped, slow-damped or over-damped responses, the parameters, for examplea zero at z = 0.0, are computed as follows:

$$1 - \frac{\rho_{1}}{\rho_{0}} * T = 0.0$$

$$\frac{\rho_{1}}{\rho_{0}} = \frac{1}{T}$$

$$\rho_{1} = 10 * \rho_{0} = 10$$

T = 0.1 seconds (chosen for a PI controller model) is two times faster than the sampling time for the plant. As an example, rho0 is set equal to 1.0, and the value of rho1 calculated depending on the zero location. The ratio of rho1 to rho0 determines how far apart the parameters are to each other as they become optimised by the IFT.

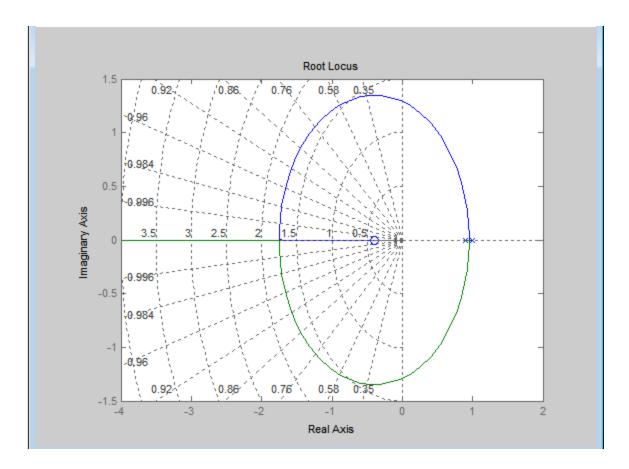

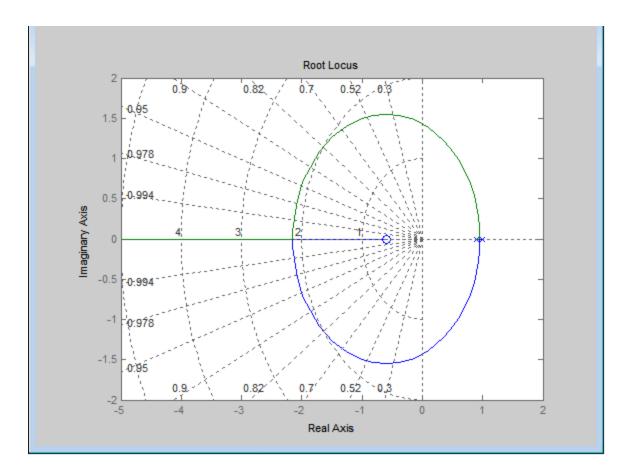

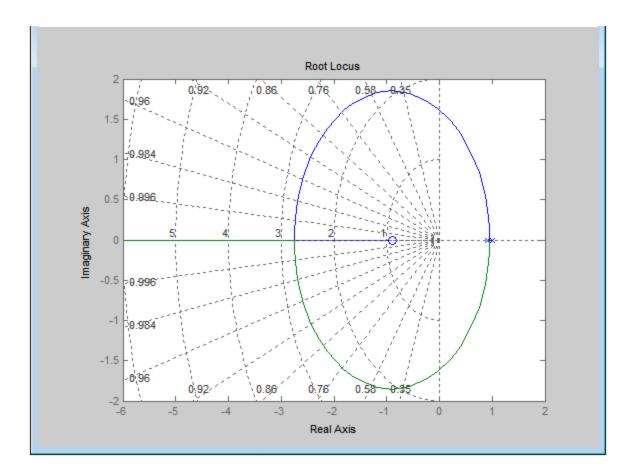

Table 2 shows the roots of the characteristic equation for the closed-loop system as per zero location on the z-plane. The root locus for the PI controller applied to the DC motor for different zero locations, shown in table 2, are illustrated in appendix III. According to the captured root locus results for the PI controller applied to the DC motor, the closed-loop poles for the system with zeros from z = -0.2 to z = 0.9 are stable. However, for the system with zeros from z = -0.4, it has part of its loci in an unstable region. Hence, it is prudent to use the system with zeros from z = -0.2 to z = 0.9 to z = 0.9 that have the loci inside the unit circle. Amongst the zero locations stipulated in table 2, location 0.4 is selected for investigation. It does not mean the choice 'zero location' is niche, but only chosen as an example. This zero is in the region of stability, as can be shown by a plot of root locus, in appendix III, figure AP.3. The rho-space is selected, from which results are obtained and mapped. Thereafter, the rho-space where the closed loop system is stable, is determined.

| Zero location on the | Rho0 | Rho1  | Roots        |

|----------------------|------|-------|--------------|

| z-plane              |      |       |              |

| 2.00                 | 0.10 | 0.20  | 0.98         |

|                      |      |       | 0.91         |

| 0.90                 | 1.00 | 1.00  | 0.90 + 0.01i |

|                      |      |       | 0.90 + 0.01i |

| 0.40                 | 1.00 | 6.00  | 0.90 + 0.22i |

|                      |      |       | 0.90 + 0.22i |

| -0.20                | 1.00 | 12.00 | 0.90 + 0.32i |

|                      |      |       | 0.90 + 0.32i |

| -0.60                | 1.00 | 16.00 | 0.90 + 0.38i |

|                      |      |       | 0.90 + 0.38i |

| -4.2                 | 1.00 | 52.00 | 0.90 + 0.70i |

|                      |      |       | 0.90 + 0.70i |

|                      |      |       |              |

|  | Table 2: | Roots of the DC motor closed-loop cor | ntrol system |

|--|----------|---------------------------------------|--------------|

|--|----------|---------------------------------------|--------------|

Having conducted root-locus analysis for the closed-loop system at different zero locations, the PI controller applied to the DC motor is verified for stability by use of a Routh-Hurwitz criterion. This procedure is accomplished by transforming the system's characteristic equation from equation (32), into the s-plane by means of bilinear transformation as follows: the characteristic equation is given as

$$z^{2} + (0.09516*\rho_{0} - 1.904837)*z + (0.904837 + 0.09516*\rho_{1}*T - 0.09516*\rho_{0} = 0$$

(33)

In the above given characteristic equation, z is substituted with  $\frac{w+1}{w-1}$  to yield the w-plane equation.

$$\left(\frac{w+1}{w-1}\right)^2 + (0.09516*\rho_0 - 1.904837)*\left(\frac{w+1}{w-1}\right) + (0.904837 + 0.09516*\rho_1*T - 0.09516*\rho_0 = 0$$

$$0.095*\rho_1*T*w^2 + (0.1904 - 0.19*\rho_1*T + 0.19*\rho_0)*w + 0.095*\rho_1*T - 0.095*\rho_0 + 1.9048 = 0$$

Hence, the Routh-Hurwitz array is formed, as given in table 3.

## Table 3: Routh-Hurwitz for the characteristic equation

| $w^2$ | $0.095*\rho_1*T$ $0.095*\rho_1*T-0.095*\rho_0+1.9048$ |

|-------|-------------------------------------------------------|

| W     | $(0.1904 - 0.19*\rho_1*T + 0.19*\rho_0) \qquad 0$     |

| $w^0$ | $0.095*\rho_1*T - 0.095*\rho_0 + 1.9048$              |

To find a range of controller parameters where the closed-loop system is stable, we arrange rho1 in terms of rho0 as follows: for zero location at 0.8 and sampling time at 0.1 seconds, the relationship is computed as:

$$1 - \frac{\rho_1}{\rho_0} * T = 0.8$$

$$\frac{\rho_1}{\rho_0} = \frac{0.2}{T}$$

$$\rho_1 = 2 * \rho_0$$

Hence, rho1 in table 3 is substituted with 2\*rho0, in order to find the range of controller parameters for which the closed-loop system is stable. The range for  $w^2$  is computed as follows:

$0.095 * T * 2 * \rho_0 = 0$  $\rho_0 = 0$

Giving a range of  $\rho_0 > 0$ .

Similarly, the range for w is computed as follows:

$(0.1904 - 0.19 * \rho_1 * T + 0.19 * \rho_0) = 0$  $\rho_0 = \frac{0.1904}{-0.1520} = -1.2526$

Giving a range of  $\rho_0 > -1.2526$ .

Finally, the range for  $w^0$  is zero, indicated by the relation:

$0.095 * \rho_1 * T - 0.095 * \rho_0 + 1.9048 = 0$  $(0.095 - 0.019)\rho_0 = 1.9048$  $\rho_0 = 25.0632$

Giving a range of  $\rho_0 < 25.0632$ .

Therefore, the overall range for closed-loop system stability for the PI controller applied to the DC motor (for rho0) is given as  $-1.2526 < \rho_0 < 25.0632$ . Similarly, the range for rho1 is  $-2.5052 < \rho_1 < 50.1264$ . Hence, parameter values outside the obtained range for rho0 and rho1 would render the closed-loop system unstable. This information can help to test the tuning action of the IFT technique, by selecting parameters outside the range and verifying if IFT is capable of forcing the parameters within the given range.

#### 3.3.1 Simulation of the IFT applied to the DC motor

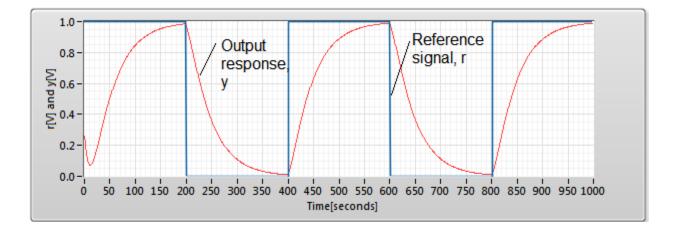

Using the rho-space mapped in table 2, we run the PI controller (without the IFT) driving the DC motor, and map the results of output responses in appendix IV. The PI controller (with the IFT) is implemented next, driving the DC motor once again and recording the results of the output responses in figure 3, figure 4 and figure 5. Thereafter, the results are compared to ascertain the validity of the IFT technique as an optimising technique. From this, we can safely select initial parameters which are slow-damped, fast-damped, and oscillatory closed-loop systems. The IFT is implemented 1 000 times, optimising one sample at a time while observing the trend of optimisation in 1000 spaces (N = 1000) or more, where a great amount of tuning information is required. A single IFT cycle composing of {experiment#1...}, {experiment#2...}, and {update parameters} phases

takes 40s and is synchronised with the step changes in the reference signal. The DC motor output signal y, reference signal r, controller parameters  $\rho_0$  and  $\rho_1$ , error e and cost function J, are the focus of our investigations.

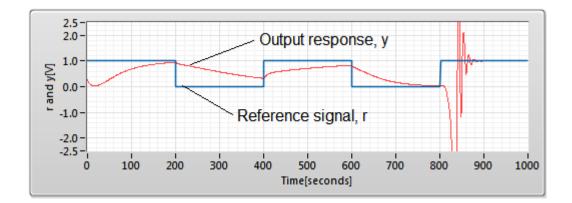

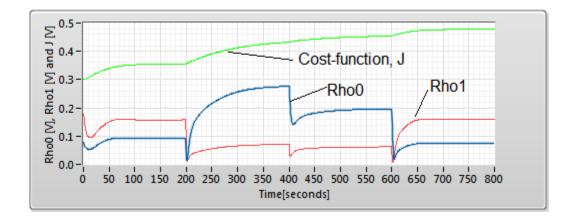

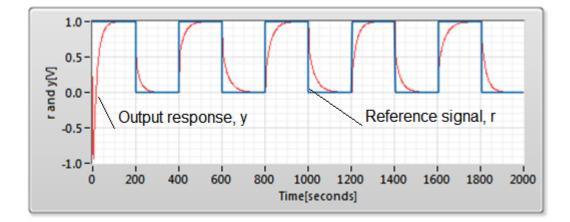

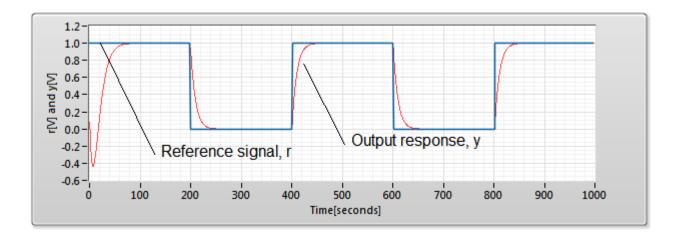

## (I) Slow-damped case

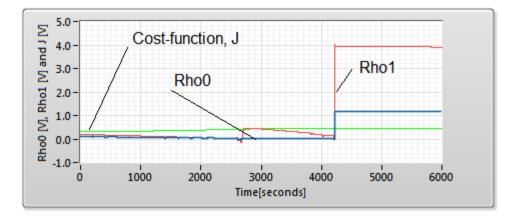

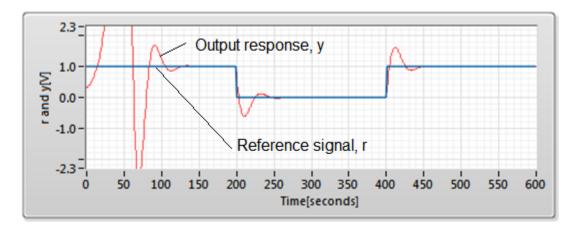

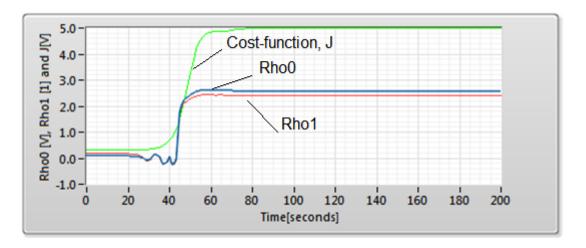

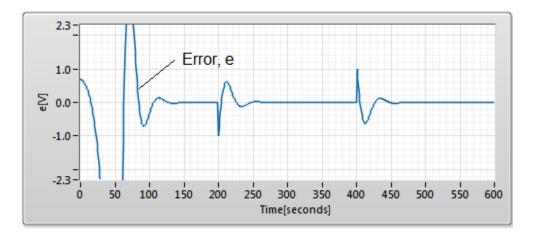

The results for the initial slow-damped closed-loop system is illustrated in figure 3. As depicted, the controller is started with initial parameters of rho0 = 0.1 and rho1 = 0.2 which results in a slow or heavily damped closed-loop system. This is indicated in figure AP.IV.1 in appendix IV. The response of the DC motor and the reference signals are illustrated in figure 3a, followed by the results for the controller parameters and the cost function in figure 3b. Figure 3c illustrates the results for the controller parameters in a magnified format. Finally, figure 3d shows results for the error signal.

Figure 3(a): Reference signal and DC motor output signal

Figure 3(b): Rho0, Rh01 and cost function, J signals

Figure 3(c): Rho0, Rh01 and cost function, J signals

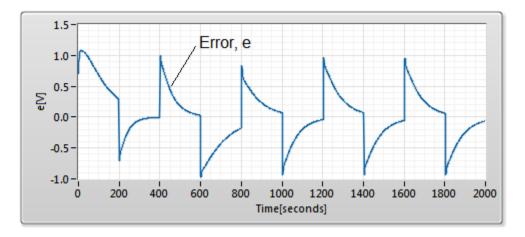

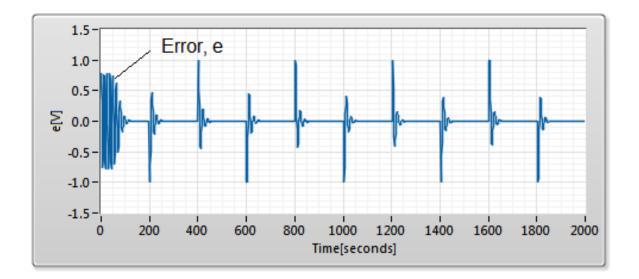

Figure 3(d): Error signal

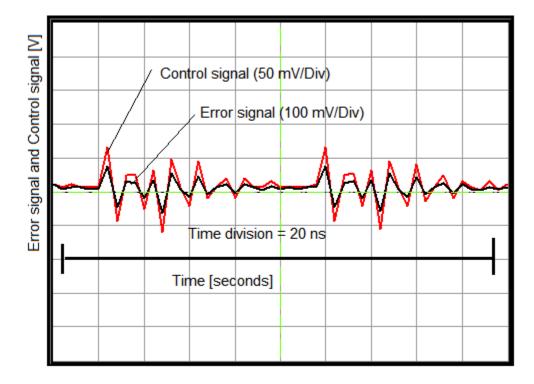

The DC motor output response is heavily damped from sample number zero to sample number 800, and thereafter it becomes unstable up to sample number 860 where controller parameters converge to rho0 = 4.2 and rho1 = 28.0, as illustrated in figure 3c. This behaviour is readily explained by roots of the characteristic equation for the closed-loop system for the given sample numbers in table 4. At sample number 15 the roots indicate slow stability, which later turns out to be an integrator, and finally converges to an oscillatory stable response. The sample numbers selected are mapped in table 4 with their respective parameter values and roots. This optimisation has multi-minima at samples number 15, 200, 405, and 605, as shown in figure 3b. Optimisation occurs up to sample number 1 to sample number 840. This is due to the presence of a huge error in the region, as shown in figure 3d. Clearly, the simulation for the initial slow-damped closed-loop system has validated the optimising capability of the IFT in optimising controller parameters, in that the heavily-damped DC motor response turns into an oscillatory stable response (see figure 3a).

| Sample No. | Rho0 | Rho1  | Roots        |

|------------|------|-------|--------------|

| 15         | 0.06 | 0.10  | 0.99         |

|            |      |       | 0.90         |

| 200        | 0.02 | 0.02  | 1.00         |

|            |      |       | 0.90         |

| 405        | 0.14 | 0.03  | 1.00         |

|            |      |       | 0.89         |

| 605        | 0.02 | 0.01  | 1.00         |

|            |      |       | 0.90         |

| 840        | 4.2  | 36.00 | 0.75 + 0.53i |

|            |      |       | 0.75 - 0.53i |

Table 4: Roots of the DC motor closed-loop control system

| 900 | 4.2 | 28.00 | 0.75 + 0.45i |

|-----|-----|-------|--------------|

|     |     |       | 0.75 - 0.45i |

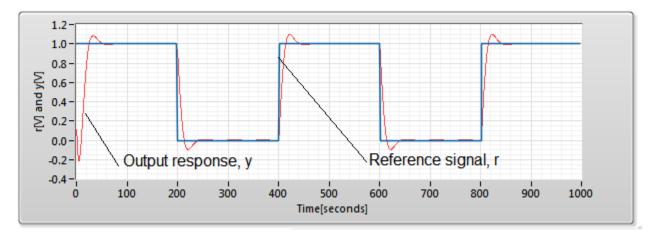

(II) Fast-damped case

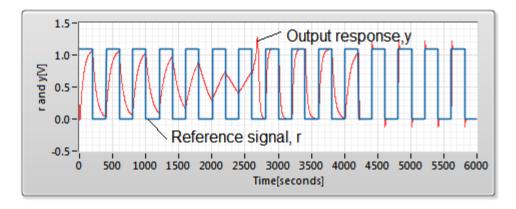

The results for the initial fast-damped closed-loop system are illustrated in figure 4.

Figure 4(a): Reference and DC motor output signal

Figure 4(b): PI controller parameter and cost function signals

Figure 4(c): Magnified PI controller parameter signals

Figure 4(d): Magnified cost function signal

Figure 4(e): Error signal

The IFT is implemented with initial parameters of rho0 = 1.0 and rho1 = 1.0, which represents a fast-damped or critical-damped closed-loop system, as indicated in figure AP.IV.2 of appendix IV. The response of the DC motor and the reference signals are illustrated in figure 4a, followed by the results for controller parameters and the cost function segmented into figures 4b, 4c, and 4d, in order to magnify significant sections of the graphs. The results for the error signal is shown in figure 4e. The response demonstrates similarity to the response of the PI controller (without the IFT) applied to the DC motor, as demonstrated from sample number 200 to sample number 1000 (see figure 4a and figure AP.IV.2).

From sample number zero to sample number 200, the response is in its transient state, as shown by the roots of the characteristic equation in table 5. The details are obtained by studying figures 4b, 4c, and 4d, which displays a variation of the controller parameters as a result of the controller tuning.

The tuning in this case is of varying multi-minims from sample number zero to sample number 1000, and then converges to a single-minima at sample 1200, occurring at every 200 samples, with parameters converged to rho0 = 0.4 and rho1 = 0.4. The cause of these minimum spikes is as a result of increase in the cost function after every 200 samples (see figure 4d: The increments of the cost function). The minimums are tabulated in table 5.

The cost function builds up after every 200 samples, from sample number zero to sample number 1000, due to the remnant error that is not minimised (see figure 4e).

| Sample No. | Rho0 | Rho1 | Roots                        |

|------------|------|------|------------------------------|

| 5          | 0.85 | 0.85 | 0.91 + 0.01i<br>0.91 - 0.01i |

| 200        | 0.78 | 0.78 | 0.93<br>0.90                 |

| 400  | 0.65 | 0.65 | 0.94 |

|------|------|------|------|

|      |      |      | 0.90 |

| 600  | 0.53 | 0.53 | 0.95 |

|      |      |      | 0.90 |

| 800  | 0.38 | 0.38 | 0.96 |

|      |      |      | 0.90 |

| 1000 | 0.23 | 0.23 | 0.98 |

|      |      |      | 0.90 |

| 1200 | 0.13 | 0.13 | 0.99 |

|      |      |      | 0.90 |

| 1400 | 0.13 | 0.13 | 0.99 |

|      |      |      | 0.90 |

| 1600 | 0.13 | 0.13 | 0.99 |

|      |      |      | 0.90 |

| 1800 | 0.13 | 0.13 | 0.99 |

|      |      |      | 0.90 |

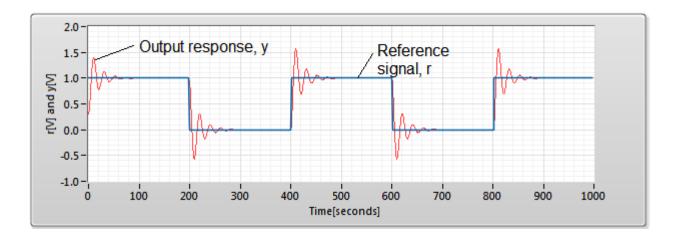

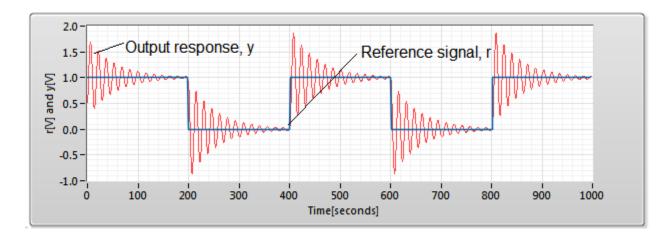

(III) Oscillatory case

The results for the initial oscillatory controller parameters are illustrated in figure 5.