# Interdigitated Back Contacts Solar Cell Based on Thin Crystalline Silicon Substrates

Thesis submitted in partial fulfillment of the requirement for the PhD Degree issued by the Universitat Politecnica de Catalunya (UPC), in its Electronic Engineering Program

# **Chen Jin**

Supervisor: Dr. Isidro Martín García

Co-supervisor: Dr. Moisés Garín Escrivá

September 2018

**Electronic Engineering Department**

### Acknowledgement

The first and foremost gratitude goes to my supervisor Dr. Isidro Martín Garcia. From the first day of entering the PhD program he has been instantly helping and supporting me. His knowledge and patience always guide and encourage me. No matter when, I always can get help from him to solve the problems I encountered during the study. He has done everything a supervisor can do for his student. It is my great pleasure to work with him.

I would like to give my great appreciation to Prof. Ramón Alcubilla and my co-supervisor Dr. Moisés Garín. Ramón is always ready to hear my progress on study and inspire me with many ideas, and it is his trust makes it possible that I won the scholarship. Without the guidance and ideas from Moisés, the first obtained experimental results of my PhD study cannot come out, which gives me a lot of confidence.

I also would like to thank Dr. Pablo Ortega for giving me valuable suggestions on laboratory work. Deepest thanks to Dr. Gema López, who taught me the most on laboratory work. The experience she shared with me makes me a skilled experimenter from a green hand. To Trifon Trifonov and Arnau for the professional skill on taking SEM images and teaching. Special thank goes to lab technicians Miguel and Xavi, who help me a lot on daily work. Thank you Miguel for the concern and great help for me. I will never forget the moments we pass together in the laboratory with Gema, Eric, Gerard, Guillermo, David Cardador, Rasha, etc. I am also thankful to Luis Enrique from ICFO for the assistance on RIE and ALD. Thanks to other professors from the group, Sandra, Cristobal and Kim, for your help and support.

Next, I would like to thank all friends from the PhD office, David Cavalheiro, Mohamed Saad, Martín, Teresa, Lukasz, Chenna, Sergi, Bremnen, Santi, etc., for the precious café/beer time and talks we had together. Thank all the friends that I got to know in UPC, especially H. Yang, B. Ye, M. Zhang, and J, Lei, for years of support and friendship.

I would like to say thank you to my parents, it is your understanding and unconditional love that keep me optimistic and growing up. I cannot make it today without your support and encouragement. Finally, I would express my sincere thankfulness to my wife, Wenfei, for your support and love all these years, from the moment that we listened the song together.

#### Abstract

This thesis contributes to the fabrication technology of c-Si solar cells on thin substrates based on Interdigitated Back-Contacted (IBC) structures. The potential of this structure to obtain high efficiencies is well-known. However, important challenges should be addressed to adapt it to thin c-Si substrates, such as the manufacturing of the thin c-Si substrate itself, light absorption enhancement, device structure design, surface passivation, etc. Focused on these challenges, experiments and simulations have been carried out, including innovative thin c-Si substrate fabrication method *Millefeuille* process, novel IBC solar cell structures combining laser doping and silicon heterojunction technologies and thin IBC solar cell performance prediction through simulation. Finally, a 30 µm thick c-Si solar cell is fabricated by thinning down a finished device applying a silicon etching technique that combines dry and wet etching.

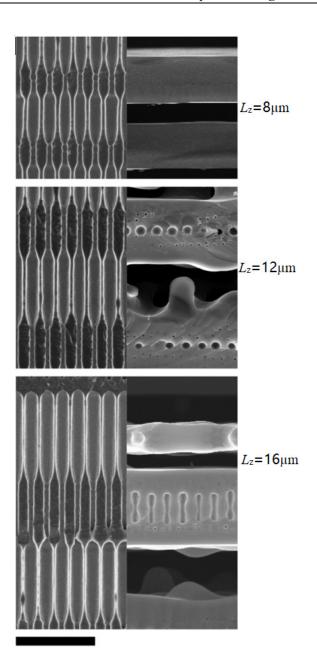

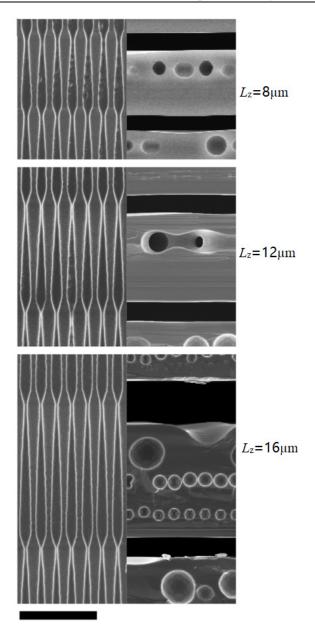

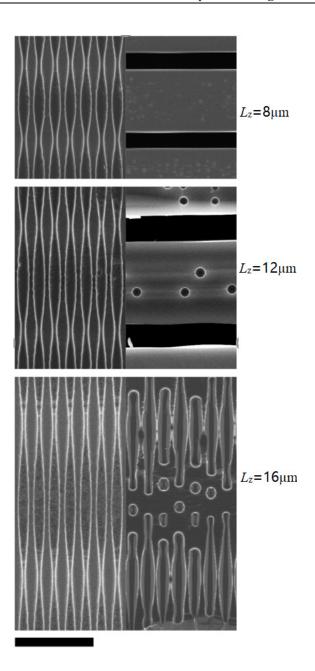

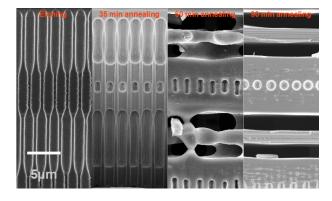

Considering the *Millefeuille* process, based on the technological know-how the impact of both modulated profile and periodicity of silicon pores on the generated thin layer quality is explored and the results are visualized by SEM images. Furthermore, the solid-void transformation evolution during the high temperature annealing reveals the pore status at 35, 60 and 90 minutes, allowing a deeper understanding of the practical silicon atomic surface diffusion and the shape evolution.

In order to find a viable and promising device structure that can be used in case of thin silicon substrates, a hybrid p-type solar cell structure is reported. In this case, emitter is based on silicon heterojunction technology while the base contacts are created by laser processing Al<sub>2</sub>O<sub>3</sub>/SiC<sub>x</sub> films. Special attention of the compatibility of both technologies has been paid in the proposed fabrication process including emitter region re-passivation and contact metallization. This work provides a new approach for achieving low-temperature high efficiency c-Si solar cells, as well as a novel pathway compatible to the fabrication of IBC devices based on thin c-Si substrate.

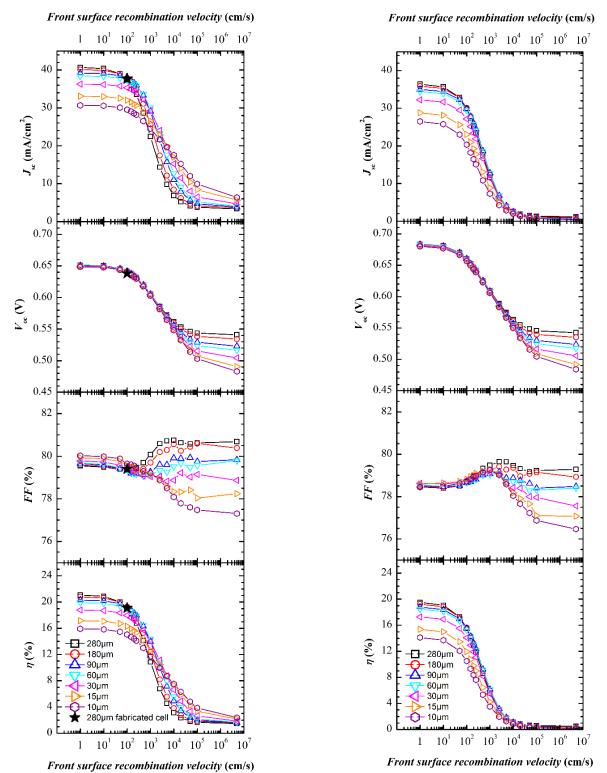

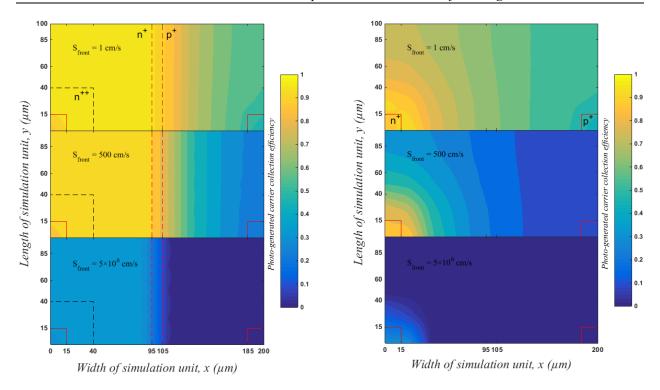

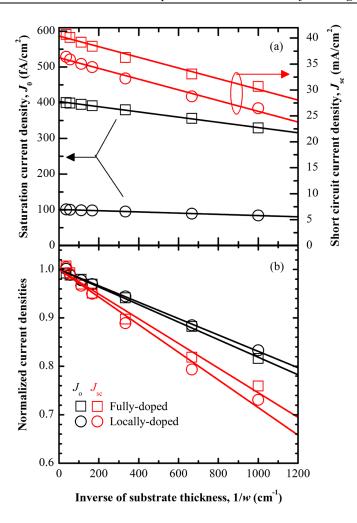

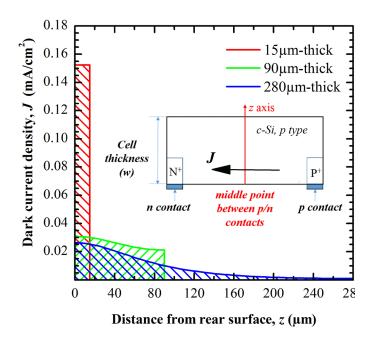

In parallel with experimental progress, the simulation on thin c-Si IBC solar cell is carried out for performance study and prediction involving two typical rear surface doping structures: fully- and locally-doped. Simulation results of fully-doped structure reveal an efficiency potential of 16-17 % for thin c-Si IBC solar cell based on substrates of 10-15 µm without changing the

technology developed for thick ones. Regarding the locally-doped structure, its performance is less tolerant to the degradation of front surface passivation. Additionally, a strong reduction of short-circuit current related to stronger requirements in the effective diffusion length is also deduced. Finally, a reduction of saturation current density, probably related to a change in the distribution of current that flow parallel to the rear surface, is also observed when the device is slimmed down. Next, a thin IBC c-Si solar cell efficiency potential is explored through rear contacts pitch study and the highest conversion efficiency is expected when contact pitches are minimum in the range of study.

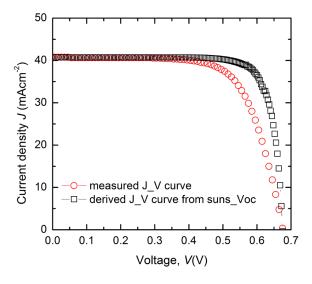

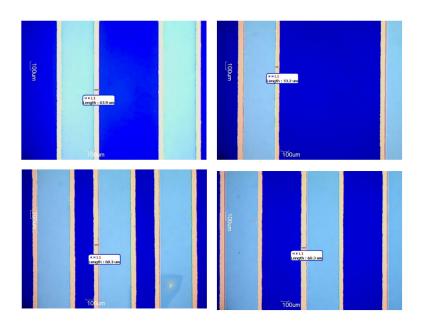

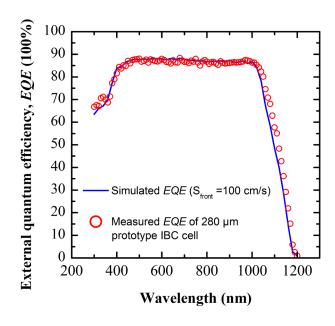

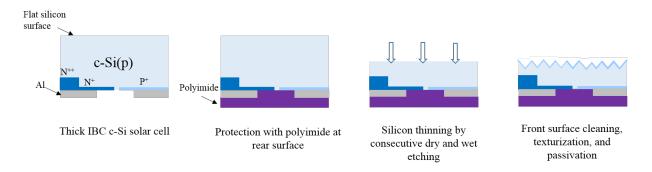

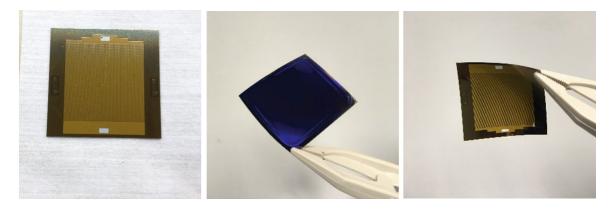

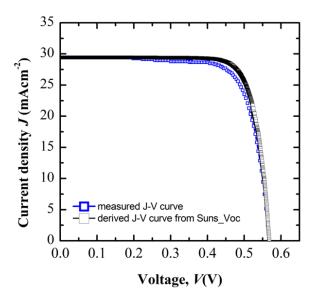

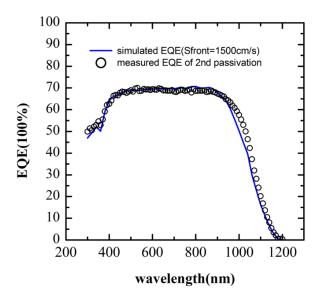

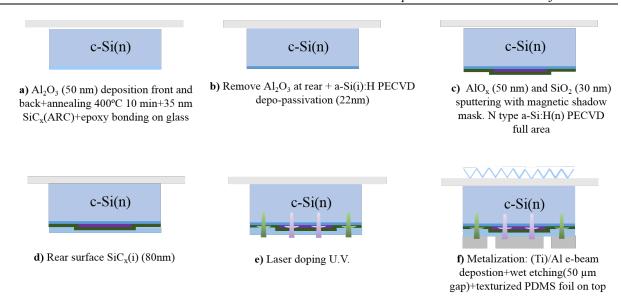

Finally, efforts are paid to get a thin c-Si solar cell through thinning down an already finished device of thick substrate. A silicon etching process based on RIE and wet chemical etching is proposed. Different experiments demonstrate that the front surface can be successfully repassivated after etching process. Additionally, random pyramids are created on that surface and the optical response of thin c-Si substrates is measured revealing a potential photogenerated current in the range of 40 mA/cm2 for 30 µm-thick substrates. Applying all these techniques to a final device, a 12.1 % efficiency is achieved and the front surface recombination velocity is deduced to be 1500 cm/s by comparing EQE with simulation results.

# **Contents**

| Acknowledgment                                                                                                    | I     |

|-------------------------------------------------------------------------------------------------------------------|-------|

| Abstract                                                                                                          | III   |

| Chapter I                                                                                                         | 1     |

| Introduction                                                                                                      | 1     |

| I. 1 Current status of photovoltaics solar energy and thesis motivation                                           | 2     |

| I. 2 Challenges for thin c-Si solar cell based on IBC structures                                                  | 5     |

| I. 3 Thesis outline                                                                                               | 8     |

| Chapter II                                                                                                        | 12    |

| Fundamental Background                                                                                            | 12    |

| II. 1 State of the art                                                                                            | 13    |

| II. 2 Theoretical and technical background                                                                        | 22    |

| II. 3 Solar cell characterization equipment                                                                       | 30    |

| Chapter III                                                                                                       | 36    |

| Progress in the Millefeuille process: towards high-quality ultrathin c-Si substrates for photovoltaic application |       |

| III. 1 Introduction                                                                                               | 37    |

| III. 2 Theoretical background                                                                                     | 40    |

| III. 3 Experimental method:                                                                                       | 46    |

| III. 4 Experimental design and results                                                                            | 52    |

| III. 5 Conclusions                                                                                                | 61    |

| Chapter IV                                                                                                        | 65    |

| IV. 1 Introduction                                                                                                | 66    |

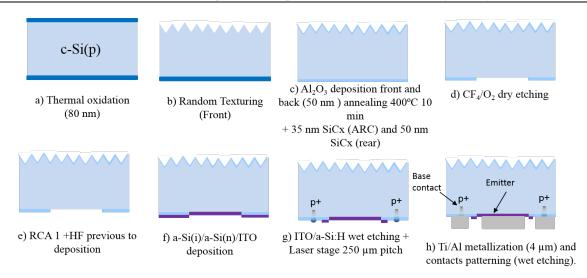

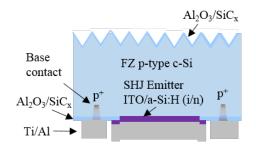

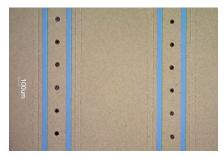

| IV. 2 Device fabrication                                                                                          | 67    |

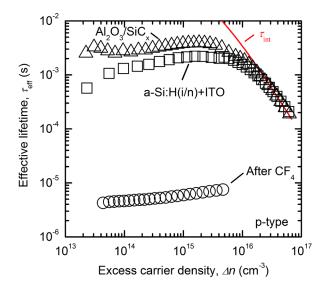

| IV. 3 Results and discussion                                                                                      | 70    |

| IV. 4 Improvement of SHJ emitter                                                                                  | 76    |

| IV. 5 Conclusions                                                                                                 | 78    |

| Chapter V                                                                                                         | 82    |

| 3D Simulations of Interdigitated Back-Contacted Crystalline Silicon Solar Cells on Thin Substrate                 | es 82 |

| V. 1 Fully-doped vs. locally-doped structure                                                                      | 83    |

| V 2 Simulation on rear contact pitch variation                                                                    | 100   |

| Chapter VI                                                      | 108 |

|-----------------------------------------------------------------|-----|

| Thin IBC c-Si solar cell fabrication based on silicon etching   | 108 |

| VI. 1 Introduction                                              | 109 |

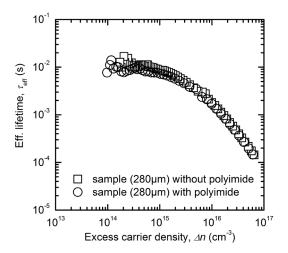

| VI. 2 Polyimide coating                                         | 109 |

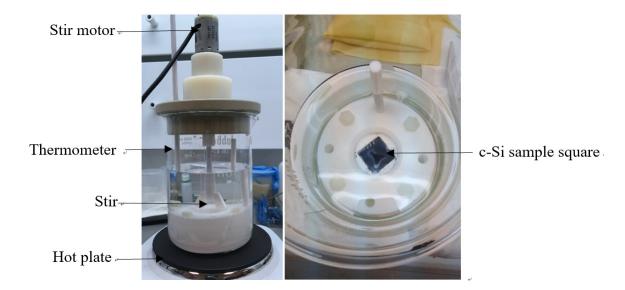

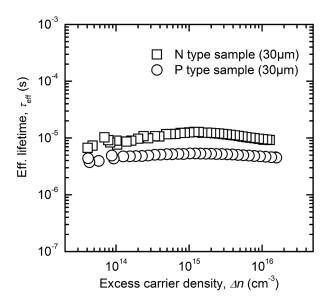

| VI. 3 Thinning down of c-Si substrates                          | 112 |

| VI. 4 Textured thin c-Si substrates                             | 116 |

| VI. 5 Thin IBC c-Si solar cell fabrication and characterization | 122 |

| VI. 6 Conclusions                                               | 125 |

| Chapter VII                                                     | 128 |

| Conclusions and future work                                     | 128 |

| VII. 1 Conclusions                                              | 129 |

| VII. 2 Future works                                             | 131 |

| Publication list                                                | 136 |

# **Chapter I**

# Introduction

In this chapter, an introduction of the thesis is given including several aspects: the current status of photovoltaics solar energy especially for devices based on crystalline silicon material; the challenges for thin crystalline silicon solar cell fabrication and the Interdigitated Back Contacts structure design; a brief review of the state of the art of these devices and the related theoretical and technical background. Based on the provided information in this chapter, the main line of study as well as the objectives of the thesis are clarified and targeted.

# I. 1 Current status of photovoltaics solar energy and thesis motivation

Electricity as a form of energy is essential for all sectors of the modern society. A clean, cheap and renewable electricity generation process has been identified as a one of the main conundrums of the last decades.

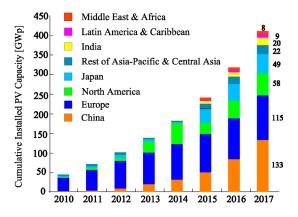

Photovoltaic (PV) solar energy is considered as one of the promising, sustainable and environment-friendly energy resource that could help in this way. Since the first effective solar cell was fabricated in Bell's Laboratory in 1954 [1, 2], a great effort has been devoted to develop more efficient and cost-competitive devices. As a result, PV solar energy for terrestrial application has exponentially grown playing a more and more significant role. The PV installation status by the end of 2017 is shown in the Fig. I. 1. The accumulative installation of PV modules are more than 400 GW around the world and the photovoltaics is a fast growing market as it is demonstrated by the Compound Annual Growth Rate (CAGR) of PV installations that was 40% between 2010 to 2016 [3].

Fig. I. 1 Global cumulative PV installation until 2017 [3]

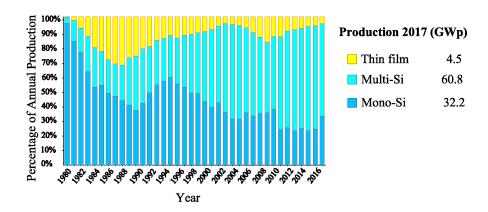

Among all kinds of technology or material utilized for PV device production, crystalline silicon has been the dominant one in photovoltaic market in the last decades when the PV market has followed an explosive growth, competing against other PV technologies as Thin Film and multi-junction solar cell based concentrated photovoltaics. As it is shown in Fig. I. 2, Si-wafer based PV technology accounted for about 94% of the total production in 2016. The share of multi-

crystalline technology is now about 70% of total production, leading to the market share of all thin film technologies amounted to about 6% of the total annual production in 2016 [3].

Fig. I. 2 Evolution of market share of different technologies for PV production [3]

Regarding the energy conversion efficiency, the record lab cell efficiency is 26.7% for monocrystalline [4] and 22.3% for multi-crystalline [5] silicon wafer-based technology. The former is very close to the theoretical limit of 29.4 % [6] assuming perfect optics and surface properties and only intrinsic recombination properties in the c-Si bulk. Consequently, the dominant position of c-Si technology could not be based on further increase in conversion efficiency but on a constant cost-reduction strategy applied throughout all the value chain. One of the trends is the reduction of the substrate thickness, since c-Si wafer accounts for 40% of today's cell cost [7] and most of the incident photons are absorbed in the first microns beneath the surface. Substrate thickness has been systematically reduced in the last years to the current 150-160 µm and it is foreseen that wafer thickness could be reduced even further to 120 µm and the module technology in the future will be able to use wafers as thin as 100 µm [7]. These data demonstrate that c-Si solar cell manufacturers are paying big efforts in reducing device thickness applying expected improvements of current technology. However, novel approaches could lead to further thickness reduction leading to a further cost-saving. Currently, many research groups are focused on envisaging the fabrication technology and solar cell structure needed for devices well below 100 µm while keeping high efficiency (a detailed state of the art review of thin c-Si solar cell is reported in chapter II).

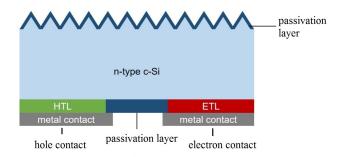

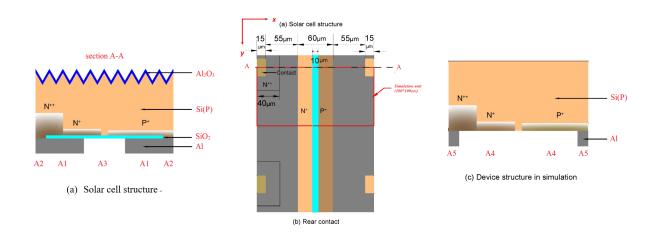

This thesis aims at contributing to the technology needed to fabricate c-Si solar cells on thin substrates based on Interdigitated Back-Contacted (IBC) structure. A sketch of this type of structure is shown in the next Fig. I. 3. As it can be seen, all the contacts are located at the rear side of the cell keeping the front surface without any shadowing from the metal grid. The potential of this structure to obtain high efficiencies is demonstrated by the fact that it is the one used in the last world record efficiency solar cells [4, 8-9]. However, important challenges should be addressed to adapt it to thin c-Si substrates as described in the next subsection.

Fig. I. 3 A sketch of Interdigitated Back-Contacted (IBC) structure

Before going into the details, the word "thin" applied to c-Si substrates should be defined as it is a key word of this work and will frequently appear through the thesis. Typically, Si wafers below 150 µm are labeled as "thin". Recently, due to the interest by the industry in reducing substrate thickness and the introduction of new promising techniques to produce thinner kerfless wafers, there is an increasing tendency to term substrates with thickness in the range 1-20µm as "ultrathin", however it is usually used in a certain context to differentiate them from the traditional thin wafers. Since there is still no standard for thickness categories of c-Si wafer and each fabricated "thin" c-Si solar cell could have a different thickness, the thickness of the c-Si substrates will be specified besides the term "thin". In this work, generally a thickness in the range of 10 to 50 µm is referred as thin through the whole text, except for the literature review presented in next chapter in which the term "ultrathin" is used for consistence with the authors.

# I. 2 Challenges for thin c-Si solar cell based on IBC structures

A first challenge is the manufacturing of the thin c-Si substrate itself. In order to keep the cost-reduction strategy, a cost-competitive technique to obtain the c-Si substrate should be found. Nowadays, several techniques have been proposed and a review of them will be included in chapter II. As a first approach, massive Si etching from c-Si thick substrates to get thin wafers has little attraction from industrial solar cell production due to its cost. The most promising solutions involve standalone thin c-Si substrates extracted from thick c-Si, for example through substrate cleavage. However, there is not a well-established technology that could be considered as a standard solution to this challenge yet.

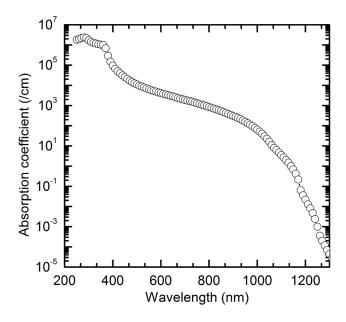

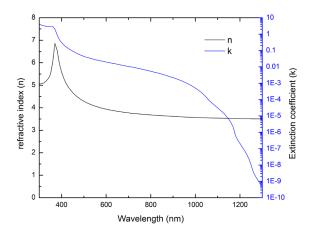

Regarding solar cell processing based on thin Si substrate, the maintenance of relatively high efficiency is required in order to realize the cost-saving strategy. For fulfilling this objective, the very first consideration is the optical performance of the cell. Light absorption plays a major role on device efficiency due to the weakening of the long wavelength sun light absorption when the c-Si substrate absorber is thinner. The light absorption coefficients of intrinsic silicon [10], are shown in Fig. I. 4.

Fig. I. 4 Absorption coefficient of Silicon [10]

As it can be seen, absorption coefficient is reduced for increasing wavelengths. Following Beer-Lambert law, light absorption shows an exponential decay with a characteristic length equals to the inverse of the absorption coefficient, i.e. absorption length. Then, at the absorption length the substrate has absorbed a factor of 1-e<sup>-1</sup>≈64 % of the incident light. For example, the data point at the 1000 nm shows an absorption coefficient of 64 cm<sup>-1</sup>, hence the absorption depth is 155 μm meaning that the 155 μm-thick intrinsic silicon material would show an optical loss of 36 % when only one pass of the light through it is considered. Notice that 155 μm is a thickness which is currently used in commercial devices meaning that optical losses due to low absorption of IR photons occur. Fortunately, very low sun irradiance is located beyond 1000 nm when the standard spectrum for terrestrial application is considered (AM1.5g spectrum). These optical losses would dramatically increase when thin substrates are involved. Not only the optical loss would start for shorter wavelengths, but the sun irradiance is much intense for wavelengths closer to the visible range resulting in a critical loss. As a consequence, a strategy for light trapping, i.e. increase the optical path of the light inside the substrate, must be considered for thin devices.

Conventionally, c-Si surface roughness for light anti-reflection is realized by pyramids texturing and it has been broadly used for laboratory and commercial PV cells due to its effective light absorption enhancement. This kind of surface morphological deformation is achieved at the expense of the c-Si material etching, while the etched Si thickness could be as deep as about 20 µm. This approach is appropriate for c-Si solar cells that are based on conventional Si wafer as the etched thickness is not significant for the wafer mechanical properties and the subsequent processing steps. However, in case of thin c-Si material, it does not seem a feasible solution. As a consequence, an experimentally viable pathway should be determined for effectively improving the thin c-Si light absorptance. It should be mentioned that along this work, despite some efforts have been paid to improve optical properties of thin c-Si solar cells (see reference [11]), this challenge has not been addressed in depth due to time limitations.

Besides the light absorption management task for thin c-Si solar cell, device structure design is essential for approaching high efficiency. Historically, double side contacted c-Si solar cells have been considered as reference structure [12]. In such devices, the electron contact is on one surface while the hole contact is located on the opposite one. As it was mentioned before, the rear

contacts structure has the advantage that no metal grid is on the front side avoiding the shadow loss; secondly, the electron and hole contacts are all arranged at the rear surface hence the contacts area can be tailored approaching the optimum design without worrying about the trade-off between the contacts series resistance and the front metal finger reflectance. Furthermore, this structure facilitates the cell stringing and wafer interconnection for module fabrication.

For thin c-Si substrates, the IBC structure shows further advantages. Since all contacts are at the rear side, the front surface requirements are relaxed to just a good surface passivation allowing a more flexible application of light trapping techniques. Additionally, IBC structure will potentially facilitate cell processing and assembling, in particular for very thin fragile c-Si substrates. This type of substrates can be transferred to a transparent panel (e.g. glass or silicone, also used for cell encapsulation) leaving the rear surface accessible for contact definition. Some devices using this structure on thin c-Si substrates have been reported in the literature leading to efficiencies of 18.9 % and 13.7 % on 45 and 10 µm-thick solar cells, respectively [13, 14]. Although an optimum device structure for thin devices has not been established, IBC structure is considered as a promising candidate for high efficiency thin c-Si solar cell.

Classically speaking, base and emitter formation is one of the critical step of the c-Si solar cell processing, during which, the definition of p-n junction region is realized. The emitter formation based on dopant thermal diffusion has dominated the solar cell fabrication for a long time in both laboratory and industrial areas. The technology is quite established and the relevant parameters such as the dopant concentration profile as a function of time and temperature can be accessed by mature numerical simulation. However, the high temperature thermal diffusion is a power and time consuming procedure and, more importantly, its application to thin c-Si substrates is not straightforward due to their different mechanical and thermal properties. Thus this step must be adapted to be feasible for thin substrates or even replaced by other more convenient low temperature approaches.

As in case of thick Si wafer, a good surface passivation is an essential quality indicator to assure the final PV device performance. Due to mono-crystalline silicon material properties, recombination at the surfaces dominates recombination mechanisms which is even more

significant for thin c-Si substrates. Special attention must be paid to this task adapting the conventional technologies, typically consisting of dielectric deposition, to the requirements of thin substrates.

As a conclusion, back contacted structure is a viable and promising design for high efficiency thin c-Si solar cells that would potentially facilitate the solar cell optical and electrical processing

#### I. 3 Thesis outline

This thesis addresses part of the challenges described above. In particular, chapter III reports on the improvements applied to a technology called "millefeuille" which lead to multiple thin c-Si substrates from a single wafer. This technology, based on the application of macroporous silicon with modulated width, has been developed in our research group. The chapter deals with the impact of porous periodicity and profile to the quality of the c-Si layers. In chapter IV, a fabrication process combining laser doping and heterojunction technology is explained. These devices have homojunction base contacts while emitter contacts are based on silicon heterojunction resulting in hybrid devices. Both technologies are low temperature and potentially compatible to thin c-Si substrates. A fabrication process combining both technologies is proposed and its potential is demonstrated by applying it on conventional c-Si substrates. Chapter V is focused on the effect of substrate thickness and front surface recombination velocity on c-Si IBC solar cells. This work is done through 3D simulations where a rear surface configuration mimicking high efficiency devices is defined as a reference. Then, substrate thickness is reduced from 280 to 10 µm with interesting effects on carrier collection and cell efficiency. In chapter VI, a 30 µm-thick solar cell is fabricated with relevant efficiency. In order to minimize handling problems, we start from a thick c-Si substrate where the rear surface is processed using conventional technologies. Then, the substrate is mechanically and chemically thinned down to be finally textured and repassivated. The obtained results are validated through 3D simulations. Finally, chapter VII shows the conclusions and future work related to this thesis.

Before going into all these results, next chapter describes the background on which the work is based. It includes a theoretical and technical background as well as a detailed state of the art of thin c-Si solar cells.

#### References I

- [1] April 25, 1954: Bell Labs Demonstrates the First Practical Silicon Solar Cell. APS News. American Physical Society, 18 (4), April 2009.

- [2] D. M. Chapin, C. S. Fuller and G. L. Pearson. A new silicon p-n junction photocell for converting solar radiation into electrical power. *Journal of Applied Physics*. 25 (5): 676–677, May 1954.

- [3]https://www.ise.fraunhofer.de/content/dam/ise/de/documents/publications/studies/Photovoltaics-Report.pdf

- [4] Yoshikawa K, Kawasaki H, Yoshida W, Irie T, Konishi K, Nakano K, Uto T, Adachi D, Kanematsu M, Uzu H, Yamamoto K. Silicon heterojunction solar cell with interdigitated back contacts for a photoconversion efficiency over 26%. *Nature Energy*, 2(5): 17032, 2017.

- [5] Benick J, Richter A, Müller R, et al. High-efficiency n-type HP mc silicon solar cells. *IEEE J Photovoltaics*, 7(5):1171 1175, 2017.

- [6] Richter, A., Hermle, M., Glunz, S.W. Reassessment of the limiting efficiency for crystalline silicon solar cells. *IEEE J Photovoltaics*, vol. 3, 1184–119, Oct. 2013.

- [7] International Technology Roadmap for Photovoltaics (ITRPV), Results 2017, Ninth Edition, March 2018. <a href="http://www.itrpv.net/Reports/Downloads/">http://www.itrpv.net/Reports/Downloads/</a>

- [8] Panasonic Press Release, 10 April 2014. Panasonic HIT® Solar Cell Achieves World's Highest Energy Conversion Efficiency of 25.6% at Research Level (http://panasonic.co.jp/corp/news/official.data/data.dir/2014/04/en140410-4/en140410-4.html

- [9] http://www.kaneka.co.jp/kaneka-e/images/topics/1473811995/1473811995\_101.pdf

- [10] M. A. Green. Self-consistent optical parameters of intrinsic silicon at 300 K including temperature coefficients. *Solar Energy Materials and Solar Cells*, vol. 92, pp. 1305–1310, 2008.

- [11] Arnau Rosell Canet. Optical Enhancement of Solar Cells Using Textured PDMS Films. *Bachelor thesis*, 2018.

- [12] Jianhua Zhao, Aihua Wang and Martin A. Green. 24.5% Efficiency silicon PERT cells on MCZ substrates and 24.7% efficiency PERL cells on FZ substrates, *Prog. Photovolt: Res. Appl.*, 7, 471-474, 1999.

- [13] F. Haase, S. Kajari-Schröder, R. Brendel. High efficiency back-contact back-junction thinfilm monocrystalline silicon solar cells from the porous silicon process. *Journal of Applied Physics*, vol. 114, no. 19, p. 194505, 2013.

[14] S. Jeong, M. D. McGehee, Y. Cui. All-back-contact ultra-thin silicon nanocone solar cells with 13.7% power conversion efficiency. *Nature Communications*, vol. 4, Dic. 2013.

# **Chapter II**

# **Fundamental Background**

In the first part of this chapter, the state of the art of thin c-Si solar cell fabrication and development is presented. This part covers several challenges for achieving efficient thin c-Si solar cell, namely, thin c-Si substrate fabrication method, passivation strategy, device structure design and light absorption enhancement. Representative reports from literature relating to these topics are selected and introduced briefly.

In the second part of the chapter, a brief introduction of solar cell basic theory and a description of technical background are presented, giving a general understanding of c-Si solar cell fundamentals and the experimental equipment used.

#### II. 1 State of the art

The research on silicon photovoltaics has a long history and fruitful results. However, the thickness of silicon substrates is normally in the range of 150 and 300 µm which is limited by the silicon wafer sawing technique. The study on thin silicon substrate based solar cells is attracting attention due to the cost-saving expectation and the emerging silicon wafer thinning technologies, and it involves various study fields, including the thin silicon wafer fabrication method, the improvement of light absorption on thinned absorber, the feasibility of different surface passivation strategies and recombination mechanisms, etc. In fact, a complete revision of all crystalline solar cell related components is required.

A recent published silicon solar cell efficiency table [1] is presented in Table II. 1. It can be seen that competitive efficiency has been obtained although a substantial reduction of substrate thickness. An efficiency higher than 20 % is reported for a silicon substrate as thin as 35  $\mu$ m [2]. Moreover, a more than significant 10 % of efficiency is obtained with only 2  $\mu$ m thick substrate [3].

**Table II. 1** Efficiency records of silicon solar cell, cited from Green 2018

| Classification              | Efficiency (%) | Area (cm²) | V <sub>oc</sub> (V) | $J_{\rm sc}$ (mA/cm <sup>2</sup> ) | Fill Factor (%) | Description               |

|-----------------------------|----------------|------------|---------------------|------------------------------------|-----------------|---------------------------|

| Silicon                     |                |            |                     |                                    |                 |                           |

| Si (crystalline cell)       | $26.7 \pm 0.5$ | 79.0       | 0.738               | 42.65                              | 84.9            | Kaneka,n-type rear IBC    |

| Si(multicrystalline cell)   | $22.3 \pm 0.4$ | 3.923      | 0.6742              | 41.08                              | 80.5            | FhG-ISE,n-type            |

| Si(thin transfer submodule) | $21.2\pm0.4$   | 239.7      | 0.687               | 38.50                              | 80.3            | Solexel (35 µm thick)     |

| Si (thin film minimodule)   | $10.5\pm0.3$   | 94.0       | 0.492               | 29.7                               | 72.1            | CSG solar(<2 µm on glass) |

Research on this topic has two main challenges: on one hand, a fabrication technique for thin high quality c-Si substrate at low cost is not established; and on the other hand, the device processing as a whole is more difficult considering the fragile and even flexible features of thinned c-Si substrates. Thus, an adapted fabrication procedures should be considered combining thin substrate fabrication and device processing. In order to have a general understanding of the present progress about thin crystalline Si film based solar cells, a review based on a series of representative articles are presented, the review presented below is divided into several topics: the thin c-Si

obtaining method, passivation strategy, structure design of solar cell and light absorption enhancement.

#### II. 1. 1 Thin c-Si substrate fabrication method

In the next part, several thin c-Si substrate fabrication methods are introduced, namely, silicon etching on Si and SOI (Silicon on insulator) wafer, porous silicon (PSI) layer transfer, c-Si films exfoliation, liquid phase silicon crystallization, and silicon *Millefeuille* process

#### (a) Bulk silicon thinning from thick wafer

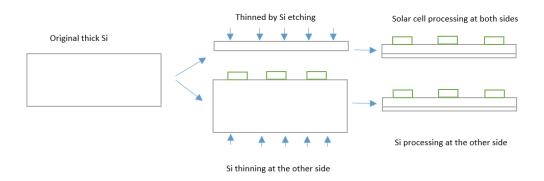

As a first approach, the fabrication of the thin film by thinning the original thick silicon wafer based on chemical wet etching is reported [4-6]. Typically, a 300-400 µm thickness float-zone (FZ) wafer is etched by chemical etching to the desired thickness. The thickness of the etched thin films are characterized by the transmittance of a white light source from backside as well as by SEM. A 50 µm thin wafer fabricated by mechanical grinding and wet chemical etching is also reported in [6]. This wafer thinning strategy is shown in the Fig. II. 1 schematically. As can be seen, the fabrication of solar cell device is either arranged before substrate thinning or after that.

Fig. II. 1 schematic diagram of thin c-Si solar cell fabrication based on normal Si wafer

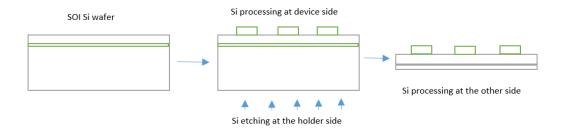

S. Jeong *et al.* [7] employed a SOI (Silicon on insulator) silicon wafer for obtaining the thin Si layer. After processing the exposed surface with thermal oxidation, n<sup>+</sup>/p<sup>+</sup> regions patterning and diffusion, the back side of the SOI wafer is patterned and etched by reactive ion etching (RIE) method. Then the buried oxide layer is exposed and removed by wet chemical etching for

following treatment. Hence, a 10  $\mu m$  Si substrate is obtained from SOI wafer. The schematic diagram can be seen in the Fig. II. 2.

Fig. II. 2 Schematic diagram of thin c-Si solar cell fabrication based on SOI wafer

#### (b) Porous silicon thin layer transfer

A more efficient and promising method for fabricating thin crystalline silicon wafer-sized film is porous silicon (PSI) layer transfer, referencing several reported layer transferring methods [8-11]. Several researchers have chosen this method rather than etching normal Si wafer, since massive Si etching to get thin wafer has little attraction towards industrial solar cell production due to its costs. Rather than the chemical Si etching, PSI layer transfer method can generate thin Si film by separating the epitaxial-grown Si layer along the preformed porous layer based on a recyclable Si substrate. This technology is regarded having a future because except the front surface treatment, all the solar cell processing like back surface passivation, back contacts and back surface field (BSF) formation, etc., can be realized before layer transferring simply by following existed conventional processing sequences. It has a great interest in laboratory study and industrial area for the compatibility with the equipment which are prepared for normal silicon wafers based solar cell fabrication. For example, F. Haase et al. [12] employ Porous Silicon layer transfer method to fabricate back junction, back contact thin c-Si solar cell before detach it from the parent substrate. Another possibility to process thin substrates is to attach them to a steel layer. This layer is utilized for supporting the transferred epitaxial Si layer from a porous silicon donor substrate while the steel works as back contact [13, 14].

#### (c) Crystalline silicon films exfoliation

The idea is to exfoliate thin c-Si films from a thick substrate by weakening a crystalline plane at a certain depth inside the substrate. Then, the c-Si between the front surface and the corresponding depth is exfoliated. One possibility is to use proton ion implantation to make the crystal more fragile [15].

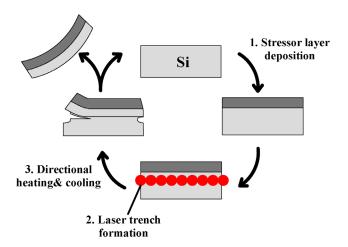

The energy of the ion implantation determines the penetration depth of the protons and therefore the thickness of the silicon film. It is also possible to exfoliate the sheet without having weakened any crystalline plane previously. This type of technique is based on the separation of the film by thermal stress. It is realized by exfoliating a material that is contacted on the silicon surface and its coefficient of thermal expansion is very different from that of silicon (different materials have been tested such as metals [16, 17] or polymers [18, 19]). Then the temperature is abruptly modified, giving rise to a thermal stress that breaks off the silicon film. Recently, this type of technique has been combined with the two methods previously presented for marking the exfoliation plane: the porous silicon [20] and the proton implantation [21]. In addition, the deposit of a thick layer of aluminum has been reported as a material to facilitate exfoliation and which in turn can be used as a back contact in the solar cell [22]. In this case the fragilized plane is marked by the formation of a notch with a laser beam. In the Fig. II. 3 a diagram of this technique can be seen.

Fig. II. 3 Diagram of crystalline silicon films exfoliation [22]

#### (d) Liquid phase crystallized silicon layers:

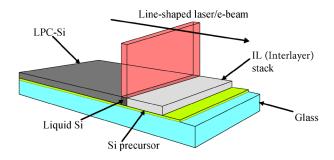

In this case the thin silicon substrate is achieved by evaporation of silicon on a glass and its subsequent recrystallization. A schematic figure of this technique is presented in Fig. II. 4 [23]. To reduce the costs of the deposit, it is done by evaporating silicon at a very high rate, giving rise to an amorphous layer of low quality. The recrystallization can be carried out by means of an electron beam [24] or a laser beam in the infrared [25]. To cover a large area, the recrystallization is done in several passes of the adjacent beam giving rise to a polycrystalline silicon, i.e., with different orientations in the same substrate. Thus, the quality of the obtained material is much lower than for the other technologies discussed. However, diffusion lengths of minority carriers longer than the usual thicknesses of 10-20 µm have been achieved, making their use for solar cells as demonstrated by [26].

Fig. II. 4 Schematic figure of liquid-phase silicon films crystallization [23]

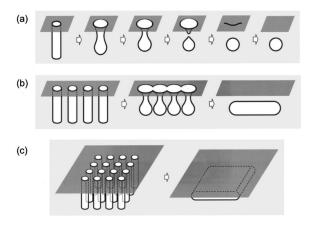

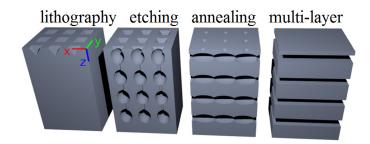

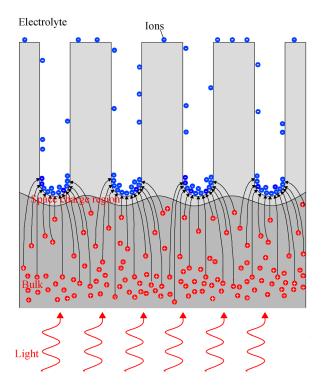

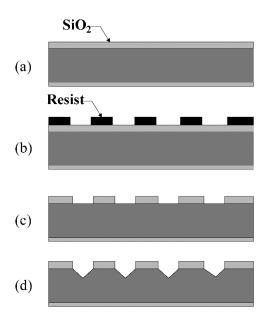

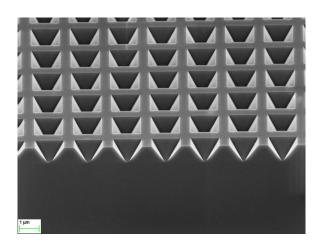

#### (e) Millefeuille process

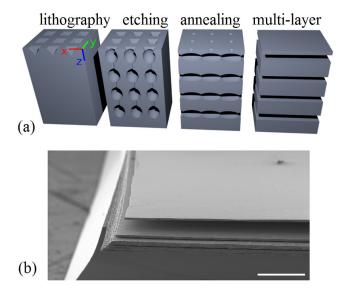

Millefeuille process is another kind of thin layer transfer method allowing multiple silicon thin layers fabrication by single step from a single crystalline n-type silicon wafer. This method was invented by the researchers from Micro and Nano Technology group (MNT) of UPC [27]. The schematic fabrication procedure is revealed in the Fig. II. 5 and the main steps are silicon porosification and high temperature annealing, leading to the multilayer generation. As can be seen from the SEM image, silicon thin layers with smooth surfaces are completely separated. Based on the technological know-how of the Millefeuille process, a further study of silicon pores on generated thin layer quality is carried out and reported in detail in next chapter. This process

provides a viable path for economic fabrication on thin free-standing silicon substrate for photovoltaics applications.

**Fig. II. 5** Silicon "*millefeuille*" fabrication process: (a) Schematic view of the four stages of c-Si multiple layers formation: lithography, electrochemical etching, annealing, and thin layer formation. (b) SEM image of a final "*millefeuille*" structure standing on the silicon wafer. Scale bar is 100 μm [27]

#### II. 1. 2 Passivation strategy

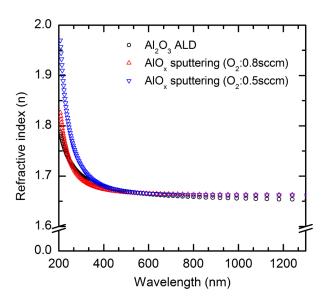

Currently, the passivation with regard to the thin c-Si solar cell generally follows the conventional thick c-Si solar cell mechanism which is typically based on dielectric layers. For example, PECVD deposition of Silicon oxynitride (SiON) and silicon nitride (SiN<sub>x</sub>) are also widely used for Si surface passivation [13, 14]. These two kinds of passivation layers also serve as antireflection layer for entering more incident light from the front side of ultra-thin c-Si solar cell. Aluminum oxide (AlO<sub>x</sub>) is another promising passivation candidate material, which is used as front surface passivation after the PSI layer is detached from the donor thick wafer [12].

Interestingly, the requirements for c-Si material quality are relaxed due to the increase if surface-to-volume ratio when c-Si substrates are thinned down. For example, in the work of S. Jeong *et al.* [7], passivation is based on thermal oxidation. However, a deep analysis is conducted revealing the correlation among the thickness of solar cell, the efficiency of solar cell and the

surface recombination velocity. It is reported that if the surface recombination velocity is 20 cm/s, the  $10 \mu m$  thick device showed efficiency maintained at around 20% although the lifetime decreased significantly, from 10 ms to  $10 \mu s$ . In contrast, the efficiency of the  $200 \mu m$  thick device with a similar decrease in effective lifetime would be changed significantly, from 21.8% to 6.5%. The conclusion is that a well passivated ultra-thin c-Si solar cell can keep efficiency even when the quality of the material is low.

#### II. 1. 3 Solar cell structure design

Generally, the c-Si solar cell structure varies from each other due to the different arrangement of the electrical contacts. Electron and hole contacts can either be arranged at both side of the cell, or gathered at only one side, while the contacts can either be full-area coverage or line- or point-like being determined by the emitter and base region of the cell. Hence, the c-Si solar cell structure design can be considered as the arrangement of the locations where electron and hole extraction occur, while an optimum structure promotes the free carrier generation and extraction before recombination.

Typically, substrates based on a chemical-etched Si layer from a normal thick Si wafer are preferred for double-side contacted structures [4-5]. However, PSI transferred thin Si can also be used in this type of design [13, 14]. It should be noticed that the emitter region in case of PSI transferred layer is at the rear surface as a consequence of the Si epitaxial growth.

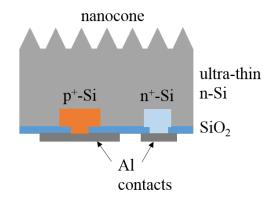

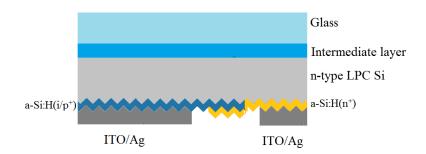

Taking advantage of SOI wafer, an interdigitated back contact (IBC) solar cell [7] is presented in Fig. II. 6. This kind of structure can eliminate the front surface contacts shadow loss, more importantly, it facilitates contact formation on the exposed surface while the other surface is not accessible. IBC structure can be also found in LPC substrates with relevant efficiencies [26]. In this case, electron and hole contacts are based on silicon heterojunction technology, as shown in Fig. II. 7.

Fig. II. 6 Schematic solar cell structure IBC nanocone [7].

Fig. II. 7 IBC structure in LPC substrates with heterojunction technology [26]

#### II. 1. 4 Light absorption enhancement

Light absorption enhancement is considered as an indispensable part involved in ultra-thin c-Si processing for high energy conversion efficiency, which has been reported by many researchers in this area. More effective and advanced absorption enhancement mechanism is primarily required in terms of ultra-thin c-Si solar cell, as the thinner the bulk material is, the more photons being transmitted through the c-Si before generating electron-hole pair due to the relatively low Si absorption coefficient. Besides, the conventional light trapping pattern, like texturing, may not be incorporated easily to ultra-thin Si film.

In order to improve optical absorption in thin c-Si substrates, two problems must be addressed. On the one hand, front reflectance should be reduced as much as possible, similarly than for conventional thick solar cells. This objective could be fulfilled by defining patterns on the front

surface bigger than the involved light wavelength, i.e. in the range of some microns, in order to increase the opportunities for a photon to be transmitted into the c-Si substrate. For example, shallow c-Si texturization is reported in [12-14]. Another possibility is to create a soft refractive index transition between the air and the absorber like in the case of black silicon [28]. In this case, c-Si front surface is nanotextured resulting in a porous material that could perfectly adapt the transition between both media.

On the other hand, optical path of photons that reach rear surface should be enlarged. This effect needs a good rear internal reflection together with a randomization of the angle of reflection. By this strategy, photons impinge front surface at an angle out of the scape cone resulting in light confinement. It has been demonstrated that optical path can be increased up to  $4n^2$  times [29], where n is the refractive index of the absorber. This light scattering can be done by patterning front, rear or both surfaces.

With these objectives in mind, many different approaches have been proposed in the literature. Among them, one can find nanopyramids [30], nanocones [31], plasmonic scatterers [32] and MIE resonators [33] with good results. For example, reference [34] reports that a 10 µm thick c-Si slice absorbs as much as a conventional 300 µm thick wafer when nano inverted pyramids are introduced. All these alternatives show surface structures in the range of 1 µm or lower. In order to correctly simulate them, the finite difference time domain (FDTD) method should be used [31].

#### II. 1. 5 Information summary table

In order to have a straightforward vision of the state of the art, several solar cell related parameters are summarized in the Table II. 2 below.

Table II. 2 Summary of the technical parameters of selected thin c-Si solar cells from literature

| References                           | [4]                                           | [5]                | [7]                      | [13]                                                                                           | [14]                                                                         | [12]                                                                                    | [26]                                                                                                            |

|--------------------------------------|-----------------------------------------------|--------------------|--------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Efficiency                           | 21.50%                                        | [3]<br>6%-7%       | 13.70%                   | 16.80%                                                                                         | 15.10%                                                                       | 18.90%                                                                                  | 14.2%                                                                                                           |

| Thickness                            | 21.30%<br>47μm                                | 10 to sub-<br>2μm  | 13.70%<br>10μm           | 18 μm                                                                                          | 13.10%<br>20 μm                                                              | 45 μm                                                                                   | 14.2%<br>13 μm                                                                                                  |

| Substrate<br>obtaining<br>method     | chemical etching                              | KOH wet etching    | RIE<br>etching of<br>SOI | PSI                                                                                            | PSI                                                                          | PSI                                                                                     | LPC                                                                                                             |

| Structure                            | PERL                                          | both side contacts | nanocone-<br>IBC         | PERL                                                                                           | PERL                                                                         | BC BJ cell                                                                              | IBC-SHJ                                                                                                         |

| Passivation<br>strategy              | oxide silicon<br>layer                        | aluminum<br>oxide  | Silicon<br>oxide         | silicon oxide<br>at the back<br>surface. 75nm<br>SiON at front<br>surface                      | SiO <sub>2</sub> at back<br>surface; SiN <sub>x</sub><br>at front<br>surface | SiO <sub>2</sub> at<br>lower<br>surface and<br>AlO <sub>x</sub> at the<br>front surface | SiO <sub>x</sub> N <sub>y</sub> (ON(ON))<br>interlayer at front<br>and a-Si:H at rear<br>with BSF at<br>emitter |

| Contacts                             | metal                                         | Cr and<br>Ag       | Al                       | Al+Steel at<br>rear<br>selective<br>n+laser doping<br>followed<br>by Ni/Cu<br>plating at front | Al+Steel at rear selective n+laser doping followed by Ni/Cu plating at front | Al                                                                                      | ITO/Ag                                                                                                          |

| Light<br>trappingat<br>front surface | inverted<br>pyramids                          | nanocone           | nanocone                 | shallow<br>texturing                                                                           | shallow<br>texturing                                                         | KOH<br>texturing                                                                        | Anti-reflection foil                                                                                            |

| Rear surface configuration           | electro-statically<br>induced n-type<br>layer | nanocone           | IBC<br>(metal Al)        | point Al<br>contact                                                                            | point Al<br>contact                                                          | IBC<br>(metal Al)                                                                       | Rear surface texturing                                                                                          |

# II. 2 Theoretical and technical background

#### II. 2. 1 Brief fundamental physics of c-Si solar cells

Generally, solar cell can be regarded as a sunlight-electricity converter that consists of three essential parts, namely, the light absorber, electron collector and hole collector no matter what kind of material it is based on. When the solar cell is placed under the sun, photons reach into the absorber and the electron and hole carriers are generated. Then these carriers gather at their collector regions respectively simultaneously creating a current in the circuit outside the device

and a potential difference between both contacts. Once the device is contacted and circuited with any electronic load, the light can be exploited in form of electricity.

Silicon is a material candidate for the application of light-electricity conversion due to its sunlight-wavelength-suited bandgap, which is 1.12 eV, i.e., photons with energy superior 1.12 eV can give their energy to generate electron-hole pairs. However, neither all the photon with energy higher than the absorber's bandgap can have the opportunity to excite an electron, nor all the generated carriers can be extracted from the solar cell. These facts are two main challenges limiting the energy conversion efficiency of solar cell. More precisely, the former is the light absorption and the latter is the recombination. The thermodynamic energy conversion limit was calculated by Shockley and Quisser [35] to be 29.4% under AM1.5G spectrum condition involving only the intrinsic recombination of silicon.

In the framework of this thesis, crystalline silicon bulk material is the light absorber. Thanks to the relatively longer carrier diffusion length of single-crystalline silicon than multi-crystalline and amorphous material, the light generated electrons and holes can be transported within the bulk material with negligible recombination. How to effectively attract and restrain these carriers to their own collector is actually the core challenge for realizing the function of light-electricity conversion. Doping of n and p type dopant material on different regions of silicon material, as a conventional fabrication method, is a viable path for achieving the separation of carriers. As a byproduct, p/n junction is formed. Due to the thermodynamic energy level difference of electron-rich n region and hole-rich p region, the privilege for either electron or hole transport presents. Alternatively, carrier selective layer deposition is employed to achieve the similar function as the p/n doping, for which, the layers that are formed by material favoring the conduction of electron and hole are respectively deposited at each region on the surface of silicon, i.e., electron transport layer (ETL) and hole transport layer (HTL).

# (a) Electrical performance under illumination: the IV curve and PV parameters

The question of how much energy can be converted from sunlight to electricity through solar cell is significant. To measure it, a device is characterized by sweeping a range of applied voltage under an illumination that could be sunlight or, more conveniently, the solar simulator in

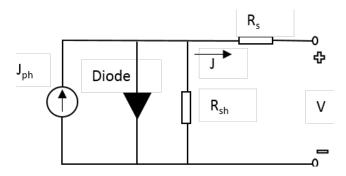

laboratory. Solar cell is made from a semiconductor material and the electrical performance under dark condition of a solar cell is an analogue to a conventional diode. When a solar cell is illuminated, a photogenerated current ( $J_{ph}$ ) is added to the equivalent diode circuit. The equivalent circuit is schematized in the Fig. II. 8.

Fig. II. 8 Equivalent circuit of photovoltaic device

The electrical mode presented above includes the series and shunt resistance influences that can alter the solar cell device performance. Along with the increase of series resistance  $R_s$ , that could be induced by contact resistance, emitter and base resistance, metal contact ohmic losses, etc., the converted current by solar cell photogeneration is suffered more dissipation and the terminal voltage drops, leading to a lower efficiency. Shunt resistance is set to describe the bypassed current instead of being extracted and used. A very resistive shunt is preferable and a low shunt can degrade the solar cell performance by declining the current at terminal.

In order to describe the electrical performance of a solar cell quantitatively, a mathematical expression is given (II. 1)

$$J(V) = J_{ph} - J_0 \left[ exp\left(\frac{e(V - J \cdot r_s)}{nkT}\right) - 1 \right] - \frac{V - J \cdot r_s}{r_{sh}}$$

(II. 1)

in which, J and V are terminal current density and voltage,  $J_{ph}$  is solar cell photocurrent density,  $r_s$  and  $r_{sh}$  is the normalized series and shunt resistances, e is electron charge, n is the ideality factor that express the relation between current and recombination mechanism (for example, n=1 when recombination takes place at the quasi-neutral regions while  $n\approx 2$  when it occurs at space charge regions, thus n is normally between 1 and 2), k and T are Boltzmann constant and temperature in Kelvin respectively.  $J_0$  is a kind of coefficient describing the recombination

current density usually named as reverse saturation current density. A higher  $J_0$  implies a stronger recombination that occurs either in space charge region or quasi neutral regions. Based on the expression equation, a  $J_0$  increase leads to a reduction of  $V_{oc}$  which should be prevented.

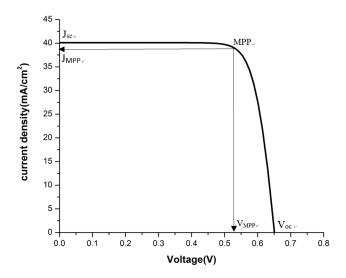

By sweeping the voltage from zero to beyond  $V_{oc}$ , a series of current-voltage data pair is obtained. A typical J-V curve of a solar cell is shown in Fig. II. 9.

Fig. II. 9 Typical current-voltage curve of solar cell under illumination

As presented in the Fig. II. 9, the efficiency of the solar cell is derived from the ratio between the maximal producible power and the incident solar energy (0.1 W/cm<sup>2</sup> under standard 1 sun condition). The current density and voltage where locates the maximal power point (MPP) are  $J_{\text{MPP}}$  and  $V_{\text{MPP}}$ , and the maximal power is the product of both values. Fill factor (*FF*) is a parameter defined as the ratio of maximal power and the product of  $V_{\text{oc}}$  and  $J_{\text{sc}}$ . Thus the efficiency can be expressed as (II. 2):

$$\eta = \frac{P_{MPP}}{P_{in}} = \frac{J_{sc} \cdot V_{oc} \cdot FF}{P_{in}}$$

(II. 2)

#### (b) Internal and external quantum efficiency

The current voltage curve is an essential expression of the energy conversion capacity of the device as a whole. However, the performance response of the device on distinct incident light

spectral condition is hard to know with merely  $J_{sc}$ ,  $V_{oc}$  and FF values and the in-field measurement is not always feasible. The measurement on quantum efficiency, or spectral response especially for solar cells, allows estimating the device current output under different spectrum.

Neither all the sunlight can be absorbed by the solar cell absorber, nor all the photogenerated carrier can be extracted and exploited. To each wavelength of light, the ratio between extracted carriers and the incident photons is defined as the external quantum efficiency (*EQE*) for this wavelength of light. This parameter accounts for the optical loss and the photogenerated carriers' recombination before extraction. The optical loss involves any photon that is not absorbed by the absorber material, while the carrier recombination occurs after the photon absorption and carrier separation. Excluding the optical loss, the quantum efficiency is concreted as internal quantum efficiency (*IQE*).

Once the external quantum efficiency is available, the current output under a certain spectrum of light is accessible by integrating *EQE* multiplied by the corresponding incident spectrum for the wavelength range of interest. Similarly, Spectral response is a parameter for a direct calculation from irradiance to the spectrally-resolved current which is also widely used.

#### (c) Carrier lifetime and surface recombination velocity

As mentioned previously, the internal quantum efficiency describes the capacity of carrier extraction after photogeneration and thus a high *IQE* implies a low recombination. The *IQE* largely depends on carrier lifetime, in other words, the carrier which has a longer lifetime has more probability to be extracted leading to a higher internal quantum efficiency. The pursuing for a high carrier lifetime is one of the most important task during the device design and fabrication, thus the recombination mechanism of carriers should be clarified at first.

Generally, recombination processes can be divided in two types, which are radiative and non-radiative respectively. In case of radiative process, the transition of electron between valence and conduction bands involves the emission of energy in form of photon. On the contrary, there is no emitted photon involved in case of non-radiative process and the energy can be transferred to a third electron or hole carrier, such as Auger recombination, or to the crystal lattice. The latter needs

the presence of a foreign atom or crystal defect that leads to an energy level within the band gap which carriers may occupy. Through this energy trap, recombination of carriers can occur, and it is referred as Shockley-Read-Hall (SRH) generation-recombination.

Therefore, the generation-recombination mechanism of carriers is categorized into radiative, Auger and Shockley-Read-Hall generation-recombination. Therefore, the bulk lifetime is calculated by equation (II. 3):

$$U = \frac{\Delta n}{\tau_{rad}} + \frac{\Delta n}{\tau_{Aug}} + \frac{\Delta n}{\tau_{SRH}} = \frac{\Delta n}{\tau_{bulk}}$$

(II. 3)

Where  $\Delta n$  is the excess carrier density generated by the light. Since this carrier density is composed by electron-hole pairs  $\Delta n = \Delta p$ . Assuming a constant  $\Delta n$  along the bulk, the total carrier lifetime is attributed to these three aspects, and the calculation is expressed in equation (II. 4).

$$\frac{1}{\tau_{bulk}} = \frac{1}{\tau_{rad}} + \frac{1}{\tau_{Aug}} + \frac{1}{\tau_{SRH}}$$

(II. 4)

Regarding c-Si surface, its recombination rate could be significant since the continuity of the crystal lattices vanishes, and dangling bonds, i.e. defects states, appear due to the partially bonded silicon atoms. Actually, recombination at surfaces follows the SRH mechanism as explained previously, and the net recombination rate is given by adding a parameter called recombination velocity (S).

$$U_{surface} = S \cdot \Delta n_{surface} \tag{II.5}$$

However, the  $\Delta n$  at surfaces can be found much different to the  $\Delta n$  of the bulk, thus an effective surface recombination velocity is appreciated.

$$U_{surface} = S_{eff} \cdot \Delta n \tag{II.6}$$

Obviously, the containment of SRH recombination at silicon surfaces is viable either by reducing the density of defects states or unbalancing carrier concentrations at the surface high recombining areas.

Finally, the total carrier lifetime can be regarded including surfaces lifetime and bulk lifetime. The total carrier lifetime can be measured experimentally leading to the effective minority carrier lifetime ( $\tau_{\text{eff}}$ ), and the expression is given (II. 7)

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{bulk}} + \frac{S_{eff,front}}{W} + \frac{S_{eff,rear}}{W}$$

(II. 7)

in which, W is the thickness of the sample.

#### II. 2. 2 Fabrication and characterization techniques

In this section, a brief description of the most relevant equipment for fabrication and characterization of the solar cells is reported. Apart from them, there are some other basic laboratory equipment, such as thermal and e-beam evaporator for metallization, RF sputtering, mask aligner and chemical bench, etc., that were frequently used but not described in detail in this document.

#### (a) Thermal Atomic Layer Deposition, ALD:

The atomic layer deposition (ALD) system in laboratory is the Savannah from Cambridge Nanotech Company. The ALD reaction is actually two sequential non-overlapping precursor-surface reactions that are realized by exposing the sample surface to each type of precursor, then the high quality thin film material is grown by a number of cycles. This deposition technique was exclusively used for aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) deposition onto c-Si surface. To deposit this layer, the precursors are trimethylaluminum ([Al(CH<sub>3</sub>)<sub>3</sub>], TMA) and H<sub>2</sub>O respectively.

The sample is firstly cleaned by a standard RCA process Then the first reaction of an ALD cycle begin with TMA exposure to the sample surface and the gas-solid reaction is self-limited once all the reactive sites on the sample surface is consumed. Next, a gas purge step of nitrogen is carried out to remove the non-reacted TMA and the reaction product CH<sub>4</sub>, and at this moment the sample surface is terminated by Al-(CH<sub>3</sub>)<sub>2</sub>. Then a pulse of another precursor H<sub>2</sub>O is followed reacting with the dangling methyl groups creating the Al-O-H, and a purge of N<sub>2</sub> is provided for

chamber evacuation, thus a full ALD cycle is finished. By repeating 480 ALD cycles, a 50 nm-thick of aluminum oxide layer is deposited. The deposition condition is shown in the Table II. 3.

Table II. 3 Precursors parameters and deposition conditions for ALD

|                                | Temperature in chamber | Precursors (pulse time)      | N <sub>2</sub> purge flow (duration) | Growth per cycle (GPC, Ångström) |

|--------------------------------|------------------------|------------------------------|--------------------------------------|----------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | 200 °C                 | TMA (0.05 sec)               | 20 (5)                               | 1 1 Å                            |

|                                |                        | H <sub>2</sub> O (0.015 sec) | 20 sccm (5 sec)                      | 1.1 Å                            |

#### (b) Plasma enhanced chemical vapor deposition (PECVD):

Plasma enhanced chemical vapor deposition belongs to chemical vapor deposition techniques, which are focused on thin films deposition from vapor phase to solid state on substrate. Process gas is decomposed aided/enhanced by a plasma created by radio-frequency (13.56 MHz) discharge between two flat and parallel electrodes.

In this work, RF PECVD from *Elettrorava* was used to deposit diverse types of thin films, such as amorphous silicon (a-Si:H), phosphorous doped amorphous silicon and silicon carbide  $(SiC_x)$ . The precursor gases parameters and the deposition conditions are summarized in the Table II. 4 below:

**Table II. 4** Precursors parameters and deposition conditions for PECVD

|                     | Temperature(display) | Pressure(mbar) | Potential power (W) | Precursors (sccm)                          |

|---------------------|----------------------|----------------|---------------------|--------------------------------------------|

| a-Si:H layer        | 300 °C (500°C)       | 0.5            | 6                   | SiH <sub>4</sub> (36)CH <sub>4</sub> (12)  |

| N type a-Si:H layer | 300 °C (500°C)       | 0.5            | 6                   | $SiH_4(36)PH_3(4)$                         |

| $SiC_x$             | 300 °C (500°C)       | 1              | 18                  | SiH <sub>4</sub> (1.2)CH <sub>4</sub> (60) |

This equipment mainly consists of two chambers, which are load-lock chamber and reaction chamber. After moving the sample into the reaction chamber, precursors gases mixture are introduced though Mass Flow Controller and pumped out continuously for maintaining a constant pressure. Once the plasma is ignited by a RF generator between the upper and lower electrodes, the gas mixture is decomposed in species reacting between them and on the sample surface depositing the film.

## II. 3 Solar cell characterization equipment

#### II. 3. 1 Carrier lifetime measurement

The lifetime performance study of photogenerated minority carriers is valuable for device quality control, i.e., a high carrier lifetime output represents a low recombination within the sample volume (including bulk and surfaces) and it is critical for approaching high efficient solar cell.

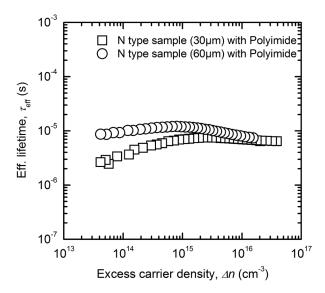

The instrument used for photogenerated carrier lifetime measurement is Sinton WCT-120 which is commercialized by Sinton Consulting [36]. Two main parameters that are captured during the measurement which are the photoconductance  $\Delta \sigma$  and the light intensity. The photoconductance  $\Delta \sigma$  is measured contactlessly by inductive coupling for determining the excess carrier density  $\Delta n$ ; while the light intensity is measured by a calibrated solar cell which is located near the sample under test, and the photogeneration rate G(t) can be estimated considering the reflection losses of the sample. Then the effective lifetime is calculated (II. 8):

$$\tau_{eff} = \frac{\Delta n}{\left(G(t) - \frac{d\Delta n}{dt}\right)} \tag{II.8}$$

The operation modes of this method can be either quasi-steady-state photoconductance (QSSPC) or photoconductance decay (PCD). In former mode, the light intensity of the illumination varies monotonically with a decay time of about 2.3 milliseconds allowing the balance of both photogeneration and recombination at each moment of time sweeping a range of  $\Delta n$  level (or injection level), while the latter presents a pulse of abrupt illumination (it lasts only about 15 microseconds) and after which the measurement takes place. The QSSPC mode is compatible with a wide range of carrier lifetime performance and the PCD mode is more suitable for relatively long lifetime carrier case.

As mentioned in section, effective lifetime could be related to bulk and surface recombination parameters. In this thesis, high quality Float Zone c-Si material is used as substrates. Then, we can consider only intrinsic mechanisms, i.e. Auger and radiative recombination rates, within the bulk.

Unless otherwise indicated, we use an intrinsic lifetime ( $\tau_{int}$ ) modeled as reported in reference [37] as bulk lifetime. Then, for samples symmetrically covered with passivating layers, we can get their corresponding effective surface recombination velocity ( $S_{eff}$ ) using the following equation (II. 9):

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{int}} + 2\frac{S_{eff}}{W} \tag{II.9}$$

#### II. 3. 2 External quantum efficiency

The measurement for external quantum efficiency is realized by using QEX10 Model from PVmeasurement. It consists of xenon lamp source, monochromator, filter and optics systems, providing a stable and monochromatic light. The wavelength for measurement ranges from 300 nm to 1200 nm and the intervals are selected to be 10 nm. The light is modulated at 66 Hz by a mechanical chopper.

Firstly the system is calibrated with a reference photodiode to make the sample measurement accurate. Once the sample under test is well positioned and connected, monochromatic light is applied onto the sample surface with about  $1 \times 1$  cm<sup>2</sup> area sweeping all the wavelength range. Then the external quantum efficiency at each wavelength is calculated as a ratio between the extracted carrier which is derived from the current density and the incident photons. A bias light generated by a halogen lamp in the range of 0.1-0.2 suns is used to reproduce carrier injection conditions inside the device during EQE measurement. The short circuit current under AM1.5G standard solar irradiance is calculated by EQE, (II. 10):

$$Jsc = e \times \int_{300}^{1200} EQE(\lambda) \times AM1.5G(\lambda) \times d\lambda$$

(II. 10)

## II. 3. 3 J-V and Suns-Voc measurement

With the calculated  $J_{sc}$  value by EQE under standard condition, the J-V curve under STC can be estimated by adjusting the solar simulator to reach an identical  $J_{sc}$  output. Then, J-V curve is

measured using Keithley 2601B SYSTEM SourceMeter. Based on the J-V curve, the V<sub>oc</sub> and FF value is extracted and thus the device electrical performance is estimated.

On the contrary to J-V measurement, the Suns- $V_{oc}$  measurement can give the solar cell performance without series resistance influence. In this setup, light is generated by a flash lamp and only the open-circuit voltage ( $V_{oc}$ ) of the device is measured while the illumination intensity is monitored by a calibrated cell during each light flash. According to the assumption of linear relationship between light intensity and  $J_{sc}$ , measured intensity in suns is converted to current density and the data pair of current density and voltage without ohmic losses impact is obtained (notice that the device is kept always under open-circuit conditions). The Suns- $V_{oc}$  curve has a great value on the qualification of device diode which provides the hint of series resistance impact on solar cell performance, especially on the FF.

## **References II**

- [1] Green, M.A., Hishikawa, Y., Baillie, A.W.Y.H., Dunlop, E.D., Levi, D.H. Solar cell efficiency tables (version 51). *Prog. Photovolt: Res. Appl.*, 26: 3-12, 2018.

- [2] Moslehi MM, Kapur P, Kramer J, Rana V, Seutter S, Deshpande A, Stalcup T, Kommera S, Ashjaee J, Calcaterra A, Grupp D, Dutton D, Brown R. World-record 20.6% efficiency 156mm× 156mm full-square solar cells using low-cost kerfless ultrathin epitaxial silicon & porous silicon lift-off technology for industry-leading high-performance smart PV modules. *PV Asia Pacific Conference (APVIA/PVAP)*, 24 October, 2012.

- [3] Keevers M. J. et al. 10% efficient CSG minimodules. 22nd European Photovoltaic Solar Energy Conference, Milan, September 2007.

- [4] Wang, A., Zhao, J., Wenham, S. R. and Green, M. A. 21.5% efficient thin silicon solar cell. *Prog. Photovolt: Res. Appl.*, 4: 55–58, 1996.

- [5] S. Wang, B. D. Weil, Y. Li, K. X. Wang, E. Garnett, S. Fan, Y. Cui. Large-area free-standing ultrathin single-crystal silicon as processable materials. *Nano Letters*, vol. 13, pp. 4393-4398, Sep. 2013.

- [6] G. P. Willeke. Thin crystalline silicon solar cells. *Solar energy materials and solar cells*, vol. 72, pp. 191–200, 2002.

- [7] S. Jeong, M. D. McGehee, Y. Cui. All-back-contact ultra-thin silicon nanocone solar cells with 13.7% power conversion efficiency. *Nature Communications*, vol. 4, Dic. 2013.

- [8] A. J. Baca, K. J. Yu, J. Xiao, S. Wang, J. Yoon, J. H. Ryu, D. Stevenson, R. G. Nuzzo, A. A. Rockett, Y. Huang, J. A. Rogers. Compact monocrystalline silicon solar modules with high voltage outputs and mechanically flexible designs. *Energy & Environmental Science*, vol. 3, p. 208, 2010.

- [9] C. H. Lee, J.-H. Kim, C. Zou, I. S. Cho, J. M. Weisse, W. Nemeth, Q. Wang, A. C. T. van Duin, T.-S. Kim, X. Zheng. Peel-and-stick: mechanism study for efficient fabrication of flexible/transparent thin-film electronics. *Scientific Reports*, vol. 3, Oct. 2013.

- [10] M. A. Meitl, Z.-T. Zhu, V. Kumar, K. J. Lee, X. Feng, Y. Y. Huang, I. Adesida, R. G. Nuzzo, J. A. Rogers. Transfer printing by kinetic control of adhesion to an elastomeric stamp. *Nature Materials*, vol. 5, pp. 33-38, 2006.

- [11] A. Carlson, A. M. Bowen, Y. Huang, R. G. Nuzzo, J. A. Rogers. Transfer printing techniques for materials assembly and micro/nanodevice fabrication. *Advanced Materials*, vol. 24, pp. 5284-5318, Oct. 2012.

- [12] F. Haase, S. Kajari-Schröder, R. Brendel. High efficiency back-contact back-junction thinfilm monocrystalline silicon solar cells from the porous silicon process. *Journal of Applied Physics*, vol. 114, p. 194505, 2013.

- [13] L. Wang, J. Han, A. Lochtefeld, A. Gerger, M. Carroll, D. Stryker, S. Bengtson, M. Curtin, H. Li, Y. Yao, and others. 16.8% efficient ultra-thin silicon solar cells on steel. *28th European Photovoltaic Solar Energy Conference and Exhibition*, pages 2641 2644, 2013.

- [14] A. Lochtefeld, L. Wang, M. Carroll, J. Han, D. Stryker, S. Bengtson, Y. Yao, D. Lin, J. Ji, C. Leitz, and others. 15%, 20 micron thin, silicon solar cells on steel. *39th Photovoltaic Specialists Conference (PVSC)*, Tampa, FL, USA, 2013.

- [15] F. Henley, A. Lamm, S. Kang, Z. Liu, L. Tian. Direct film transfer (DFT) technology for kerf-free silicon wafering, *23rd European Photovoltaic Solar Energy Conference and Exhibition*, pages 1090-1093, 2008.

- [16] M. Tanielian, S. Blackstone and R. Lajos. A new technique of forming thin free standing single-crystal films. *J. Electrochem.* pages, 507-509, 1985.

- [17] S.W. Bedell et al. Kerf-less removal of Si, Ge, and III-V layers by controlled spalling to enable low-cost PV technologies, *IEEE J. Photovoltaics*, vol. 2, 141-147, 2012.

- [18] R. Martini et al. Thin silicon foils produced by epoxy-induced spalling of silicon for high efficiency solar cells. *Applied Physics Letters*, 105, 173906, 2014.

- [19] P. Bellanger et al. New stress activation method for kerfless silicon wafering using Ag/Al and epoxy stress-inducing layers. *IEEE J. Photovoltaics*, vol. 4, pages 1228-1234, 2014.

- [20] V. Steckenreiter et al. Thermomechanical spalling of epitaxially grown silicon from porosified substrates. *Energy Procedia*, vol. 92, pages 873-879, 2016.

- [21] T. Pingault et al. A novel kerf-free wafering process combining stress-induced spalling and low energy hydrogen implantation. *Physica Status Solidi C*, vol. 13, pages 802–806, 2016.

- [22] R. Niepelt et al. Kerfless exfoliated thin crystalline Si wafers with Al metallization layers for solar cells. *Journal of Materials Research*, vol. 30, 213227-40, 2015.

- [23] Gabriel, O., Frijnts, T., Preissler, N., Amkreutz, D., Calnan, S., Ring, S., Stannowski, B., Rech, B., and Schlatmann, R. Crystalline silicon on glass-interface passivation and absorber material quality. *Prog. Photovolt: Res. Appl.*, 24: 1499-1512, 2016.

- [24] D. Amkreutz et al. Conversion efficiency and process stability improvement of electron beam crystallized thin film silicon solar cells on glass. *Solar Energy Materials and Solar Cells* vol. 123, pages 13-16, 2014.

- [25] S. Kühnapfel et al. Preferential {100} grain orientation in 10 micrometer-thick laser crystallized multicrystalline silicon on glass. *Thin Solid Films*, 576, pages 68-74, 2015.

- [26] C. Thi Trinh, N. Preissler, P. Sonntag, M. Muske, K. Jäger, M. Trahms, R. Schlatmann, B. Rech, and D. Amkreutz. Potential of interdigitated back-contact silicon heterojunction solar cells for liquid phase crystallized silicon on glass with efficiency above 14%. *Solar Energy Materials and Solar Cells*, vol. 174, pages 187-195, 2017.

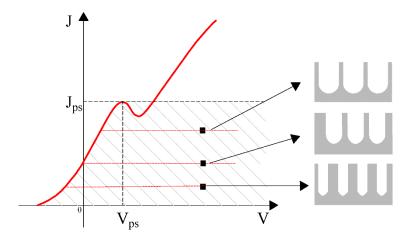

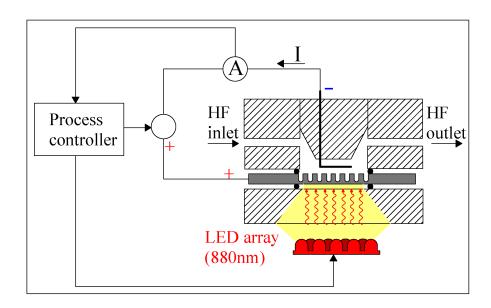

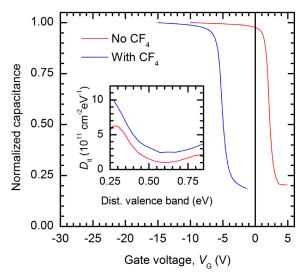

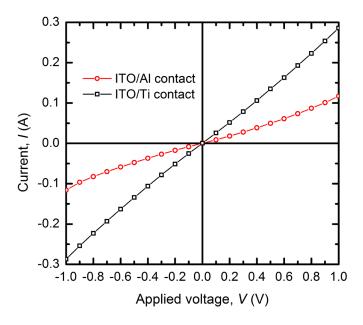

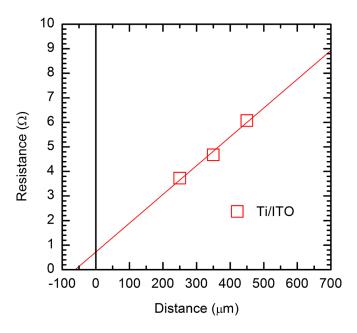

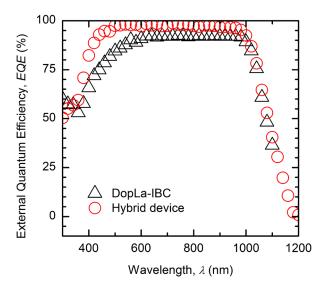

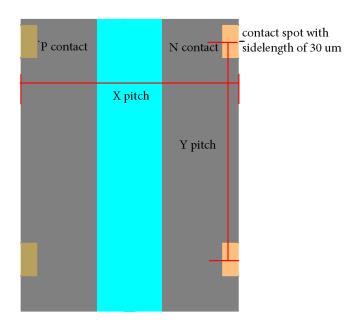

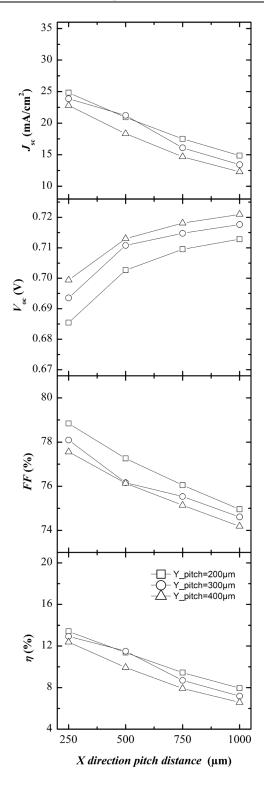

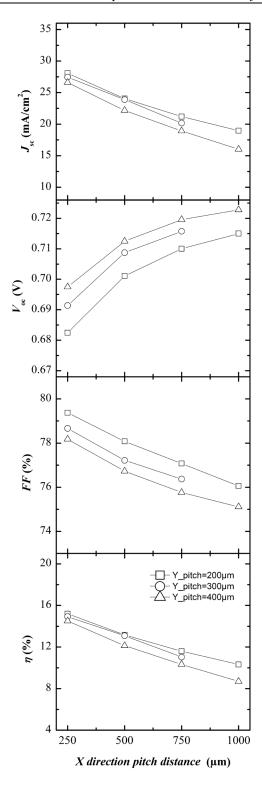

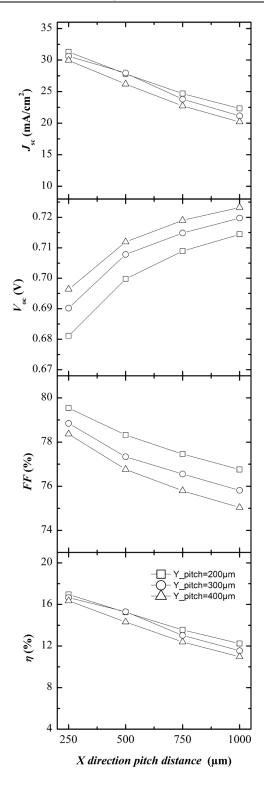

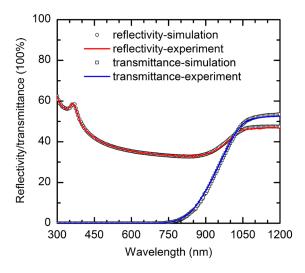

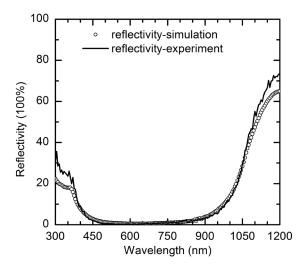

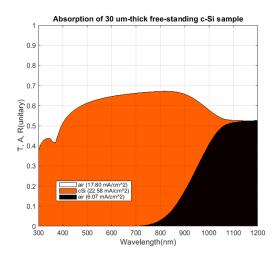

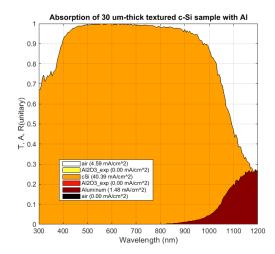

- [27] Hernández, D., Trifonov, T., Garín, M. & Alcubilla, R. 'Silicon millefeuille': From a silicon wafer to multiple thin crystalline films in a single step. *Applied Physics Letters*, 102, 172102, 2013.