| _     |              | •  |            |      | _        |          |        |

|-------|--------------|----|------------|------|----------|----------|--------|

| וםכנו | nartmont     | Λt | Flactrical | and  | Computer | -hαinα   | aarıng |

|       | yai tiiiciit | O. | Liccuitai  | allu | Compater | LIISIIII | CCIIII |

# Design, Optimization and Implementation of a High Frequency Link Multilevel Cascaded Inverter

Md. Mubashwar Hasan

This thesis is presented for the Degree of Doctor of Philosophy of Curtin University

# Declaration

To the best of my knowledge and belief this thesis contains no material previously published by any other person except where due acknowledgment has been made.

This thesis contains no material which has been accepted for the award of any other degree in any university.

|  | Hm | asan |

|--|----|------|

|--|----|------|

Signature: .....

Date: 07/03/2018

#### Abstract

Currently, multilevel inverter (MLI) is being used as a medium voltage power converter in several industrial applications such as liquefied natural gas (LNG), chemical, fuel and water plants, marine and electric vehicles, mining, power generation and power-quality improvement devices. Three MLI topologies, diode clamped or neutral point clamped (NPC), flying capacitor (FC) and cascaded H-bridge (CHB) MLI are considered as conventional MLI topologies for commercial applications. Among these topologies cascaded MLI is preferred for high power and voltage applications. The most attractive features of cascaded H-bridge inverter over the other conventional MLIs are modularity that facilitates simple and similar control to all H-bridge modules and utilizes cheap low-voltage switching devices in the CHB MLI to generate high voltage output. A number of new cascaded MLI (CMLI) topologies has been proposed in the the last few years aiming at reducing device counts while optimizing the number of levels in the inverter output voltage. Device reduction not only reduces the implementation cost, but also reduces the physical size and weight of the cascaded MLI.

This thesis presents a new concept of cascaded MLI device reduction by utilizing low frequency (50Hz) and high frequency (20kHz) transformer link. The transformer link not only overcomes the predominant CMLI problem of the need for multiple dc-power supplies, but also provides a galvanic isolation between the input and output sides of the inverter, which is essential for grid-connected applications. Two CMLI topologies, symmetric and asymmetric are proposed in this thesis. The asymmetric cascaded inverter is formed through the combination of any existing cascaded topology and a conventional three-phase, two-level inverter while a toroidal core is employed for the high frequency magnetic link to warrant compact size and high power density. On the other hand, the proposed symmetric cascaded MLI topology consists of series-connected half-bridge modules and a simple H-bridge module.

Compared with counterpart CMLI topologies available in the literatures, the proposed two inverter topologies in this thesis have the advantage of utilizing the least number of power electronic components without compromising the overall performance particularly when a high number of levels is required in the output voltage waveform. The feasibility and effectiveness of the proposed inverter topologies are confirmed through extensive simulation and experimental studies using a scaled down low-voltage laboratory prototype.

# Acknowledgments

First and foremost, I would like to take an opportunity to express immense gratitude to my supervisor, Associate Professor Dr. Ahmed Abu-Siada, who supported by all means in my research. It would not be easy to achieve my research goal without his active guidance, advice and encouragement. I am also grateful to my co-supervisor, Professor Syed Islam for his efforts. Moreover, I am thankful to Dr. S.M. Muyeen (Curtin University) and Dr. Mohamed S. A. Dahidah (Newcastle University, U.K) for their effective research collaboration.

Besides, I am thankful to the Department of electrical technical staffs, Mark Fowler, Russell Wilkinson, Zibby Cielma and Nicholas King for their friendly and helpful attitude while conducting different experiments.

Moreover, I would like to acknowledge the contribution of an Australian Government Research Training Program Scholarship in supporting this research.

Finally, I would like to express immense gratitude to my parents, siblings, wife, children and other family members for their encouragement and help.

#### **List of Publications**

It is acknowledged that most of the results from this work has been published in the following journal articles and conferences.

#### **Journal articles**

- Md Mubashwar Hasan, Ahmed Abu-Siada, Syed M. Islam, and S. M. Muyeen. "A Novel Concept for Three-Phase Cascaded Multilevel Inverter Topologies." *Energies*, 11(2), 268 (January 2018).

- 2. Md Mubashwar Hasan, Ahmed Abu-Siada, and Mohamed SA Dahidah. "A Three-Phase Symmetrical DC-Link Multilevel Inverter with Reduced Number of DC Sources." *IEEE Transactions on Power Electronics* (2018, In press)

- 3. Md Mubashwar Hasan, Ahmed Abu-Siada, and Md. Rabiul Islam. "Design and implementation of a novel three-phase cascaded half-bridge inverter." *IET Power Electronics*, Volume 9, Issue 8, June 2016, p. 1741 1752

- 4. Md Mubashwar Hasan, Ahmed Abu-Siada, Syed M. Islam, and Mohamed SA Dahidah. "A New Cascaded Multilevel Inverter Topology with Galvanic Isolation." IEEE Transactions on Industrial Applications (2018, In press)

#### **Conference Papers**

- Md Mubashwar Hasan, and A. Abu-Siada. "A high frequency linked modular cascaded multilevel inverter." In 2016 IEEE Industrial Electronics and Applications Conference (IEACon), pp. 47-51., 2016.

- 2. Md Mubashwar Hasan, and A. Abu-Siada. "A novel three phase cascaded multilevel inverter topology." In 2016 IEEE *Industrial Electronics and Applications Conference (IEACon)*, pp. 31-35.

- 3. Md Mubashwar Hasan, Ahmed Abu-Siada, and Md Rabiul Islam. "Investigation of low switching frequency control of a three phase cascaded H-bridge multilevel inverter." In 2016 IEEE *Electrical, Computer & Telecommunication Engineering (ICECTE), International Conference on*, pp. 1-5.

- 4. Md Mubashwar Hasan, A. Abu-Siada, Syed M. Islam, and S. M. Muyeen. "A Novel Generalized Concept for Three Phase Cascaded Multilevel Inverter Topologies." In *2017 IEEE Ninth Annual Green Technologies Conference (GreenTech)*, pp. 110-117.

Md Mubashwar Hasan, A. Abu-Siada, Syed M. Islam, and S. M. Muyeen. "A three-phase halfbridge cascaded inverter with reduced number of input DC supply." 2017 Australasian Universities Power Engineering Conference (AUPEC)

# **Book chapters**

Islam, Syed M., Chem V. Nayar, Ahmed Abu-Siada, and Md Mubashwar Hasan. "Power Electronics for Renewable Energy Sources." In *Power Electronics Handbook (Fourth Edition)*, pp. 783-827. 2018.

# **Table of Contents**

| Declarationii                                                                  |

|--------------------------------------------------------------------------------|

| Abstractiii                                                                    |

| Acknowledgmentsiv                                                              |

| List of Publicationsv                                                          |

| List of Figuresix                                                              |

| List of Tablesxii                                                              |

| List of Abbreviationsxiii                                                      |

| Chapter One: Introduction1                                                     |

| 1.1. Motivation and background of the study1                                   |

| 1.2 Problem statement of the research                                          |

| 1.3 Research objectives2                                                       |

| 1.4 Methodology2                                                               |

| 1.5 Significance of the work3                                                  |

| 1.6 Thesis outline3                                                            |

| Chapter Two: Comprehensive literature review for Cascaded Multilevel Inverter5 |

| 2.1 Introduction5                                                              |

| 2.2 Cascaded Multilevel inverter5                                              |

| 2.2.1 Basic concept of Multilevel inverter6                                    |

| 2.2.2 Conventional MLI topologies6                                             |

| 2.2.3 Benefits of Multilevel inverter7                                         |

| 2.2.4 Shortcomings of MLI8                                                     |

| 2.3 Basic MLI topologies8                                                      |

| 2.3.1 Diode clamp or Neutral point clamp (NPC) MLI8                            |

| 2.3.3 Cascaded H-bridge (CHB) Multilevel inverter11                            |

| 2.4 Cascaded MLI topologies with reduced device counts                         |

| 2.4.1 Cascaded MLI topologies with an extra full-bridge14                      |

| 2.4    | 4.2 Cascaded MLI topologies without extra full-bridge                              | 17      |

|--------|------------------------------------------------------------------------------------|---------|

| 2.5    | Summary                                                                            | 22      |

| Chapte | r Three: A Three-Phase Symmetrical DC-Link Multilevel Inverter with Reduced Nu     | mber of |

| DC Sou | rces                                                                               | 23      |

|        |                                                                                    |         |

| 3.1    | Introduction                                                                       |         |

| 3.2    | The proposed multilevel inverter and its modulation strategy                       |         |

| 3.3    | Semiconductor losses and converter efficiency                                      | 26      |

| 3.4    | Simulation and experimental results                                                | 28      |

| 3.4    | 4.1 Case study 1: The impact of load power factor                                  | 30      |

| 3.4    | 4.2 Case study 2: The performance of inverter under load dynamics                  | 33      |

| 3.4    | 4.3. Case study 3: Impact of changing the carrier frequency on the inverter perfor |         |

|        |                                                                                    | 34      |

| 3.4    | 4.4 Case study 4: Impact of Modulation index                                       | 35      |

| 3.4    | 4.5 Case study 5: photovoltaic application                                         | 36      |

| 3.5    | Comparison with other MLI topologies                                               | 37      |

| 3.5    | 5.1 Comparison with conventional topologies                                        | 37      |

| 3.5    | 5.1 Comparison with conventional topologies                                        | 38      |

| 3.6    | Summary                                                                            | 39      |

| Chapte | r Four: Design and implementation of a novel three-phase cascaded half-bridge in   | nverter |

|        |                                                                                    | 41      |

|        |                                                                                    |         |

| 4.1    | Introduction                                                                       | 41      |

| 4.2    | Proposed multilevel Inverter                                                       | 41      |

| 4.3    | Simulation method and experimental setup                                           | 48      |

| 4.4    | Results and discussions                                                            | 55      |

| 4.5    | Comparison with other MLI topologies                                               | 58      |

| 4.6    | Summary                                                                            | 60      |

| Chapte | r Five: A New Cascaded Multilevel Inverter Topology with Galvanic Isolation        | 61      |

| 5.1    | Introduction                                                                       | 61      |

| 5.2    | Proposed Cascaded Multilevel Inverter                                              | 61      |

| 5.3    | HF-Magnetic link Design                                                            | 65      |

| 5.4    | Performance of the proposed inverter                                               |         |

|        |                                                                                    |         |

| 5.5       | Applications of the proposed inverter                                                                                                                                          | . 75 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.6 Cc    | mparison with other three phase CMLI Topologies                                                                                                                                | . 75 |

| 5.7       | Summary                                                                                                                                                                        | . 78 |

| Chapter   | Six: Conclusions and Future work                                                                                                                                               | . 79 |

| 6.1       | Conclusions                                                                                                                                                                    | . 79 |

| 6.2 Fu    | ture work                                                                                                                                                                      | .81  |

| Referen   | ces                                                                                                                                                                            | .82  |

|           | List of Figures                                                                                                                                                                |      |

|           |                                                                                                                                                                                |      |

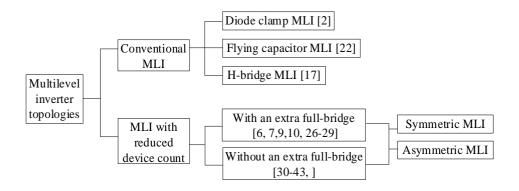

| _         | . 1 Generalized classification of MLI                                                                                                                                          |      |

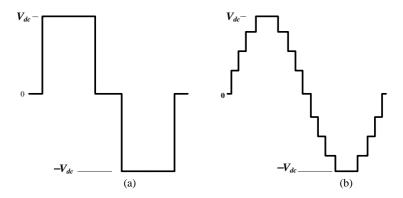

| _         | . 2 voltage waveform (a) three level line voltage, (b) nine level line voltage                                                                                                 |      |

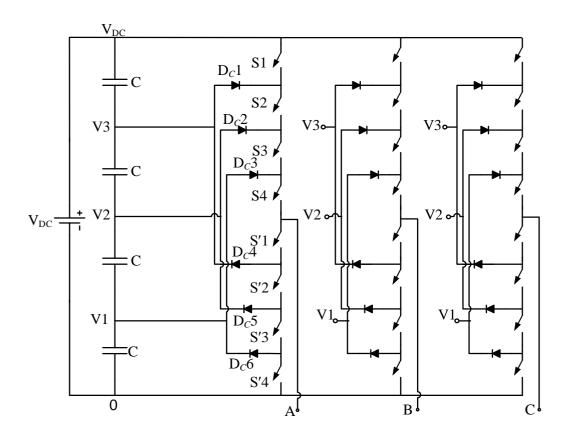

| _         | . 3 A five level diode clam MLI [2]                                                                                                                                            |      |

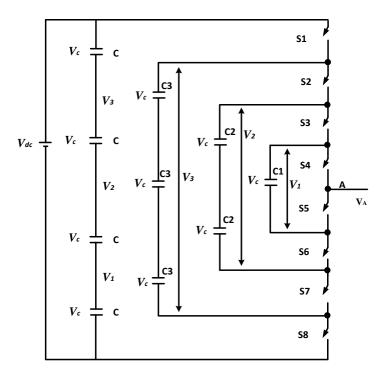

|           | .5 CHBMLI: (a) basic cell; (b) CHBMLI with two cascaded H-bridge cell [17]                                                                                                     |      |

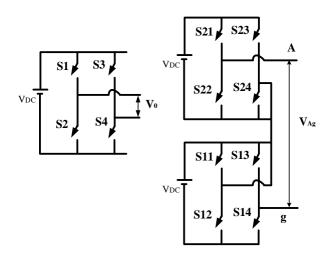

| _         | . 6 Basic operation of level and polarity generator based CMLI: (a) cascaded half-bride                                                                                        |      |

| _         | γ, (b) level generator output voltage, (c) polarity generator output voltage [7, 9, 10]                                                                                        |      |

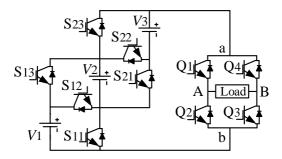

| Figure 2  | . 7 Half-bridge CMLI with non-isolated DC supply                                                                                                                               | . 15 |

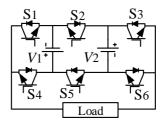

| Figure 2  | . 8 Topology proposed in [6, 27] (a) single phase structure, (b) three phase structure                                                                                         | . 16 |

| Figure 2  | . 9 CMLI topology with Switched Series/Parallel DC Voltage Sources [28]                                                                                                        | . 16 |

| •         | . 10 T-type MLI [29]                                                                                                                                                           |      |

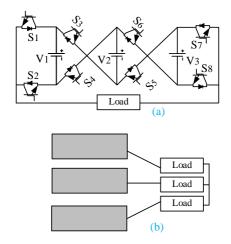

| Figure 2  | . 11 crossed switched CMLI: (a) single phase structure, (b) three phase structure [30-3                                                                                        | 34]  |

|           |                                                                                                                                                                                |      |

|           | . 12 Basic unit of developed H-bridge unit [35, 36]                                                                                                                            |      |

|           | . 13 A three level U-cell MLI [37-41]                                                                                                                                          |      |

| Figure 2  | . 14 A nine level E-type MLI topology [42, 43]                                                                                                                                 | . 20 |

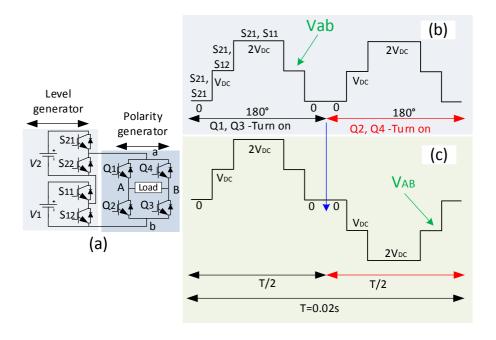

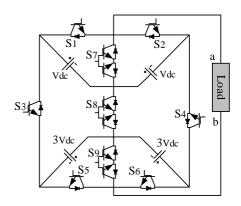

| Figure 3  | . 1 The proposed three-phase CMLI with two half-bridge cells per phase leg                                                                                                     | . 23 |

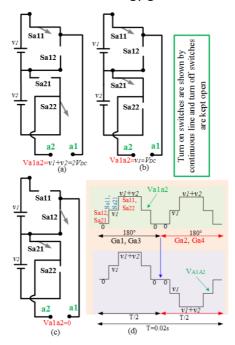

| Figure 3  | . 2 Switching logics for generating different levels in the level generator output voltag                                                                                      | es:  |

| (a) logic | for generating $2V_{DC}$ , (b) logic for generating $V_{DC}$ , (c) logic for generating 0, (d) desired                                                                         |      |

| output i  | n the level generator and polarity generator output voltage                                                                                                                    | . 25 |

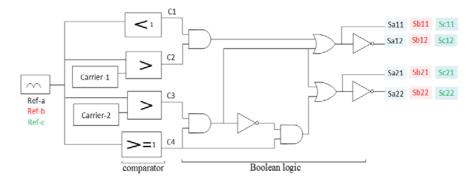

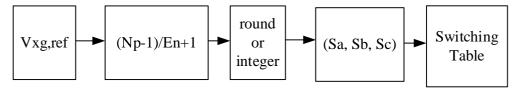

| _         | . 3 Block diagram of the modulation technique                                                                                                                                  |      |

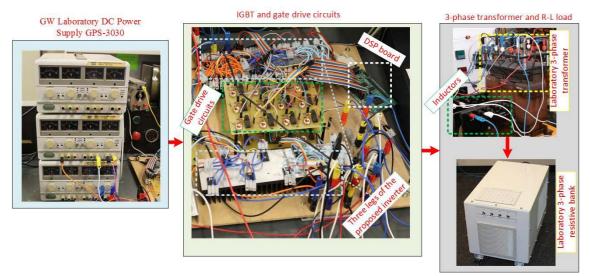

| _         | . 4 Experimental test-rig setup                                                                                                                                                | . 28 |

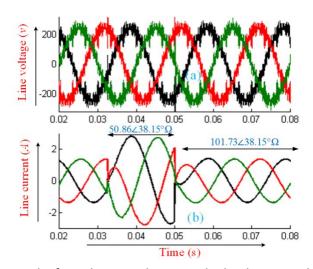

| _         | . 5 Simulation results of the output line voltages and line currents for (a) load of 0.79                                                                                      | _    |

|           | power factor and (b) load of nearly unity power factor                                                                                                                         | . 29 |

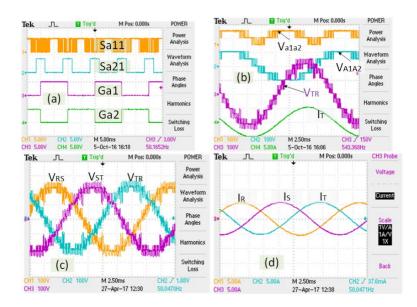

|           | . 6 Different experimental results for phase leg-A with a load of 0.79 lagging power a) gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polari | ty   |

| generator output voltages along with the line voltage and line current for phase leg-A, (c) three                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| phase line voltages and (d) three phase line currents30                                                                                          |

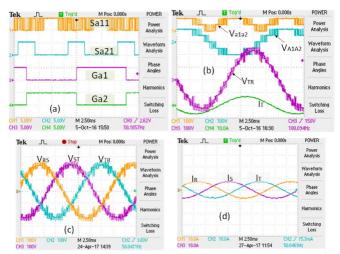

| Figure 3. 7 Different experimental results for phase leg-A with a load of 0.99 power factor: (a)                                                 |

| gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polarity generator                                               |

| output voltages along with the line voltage and line current for phase leg-A, (c) three phase line                                               |

| voltages and (d) three phase line currents30                                                                                                     |

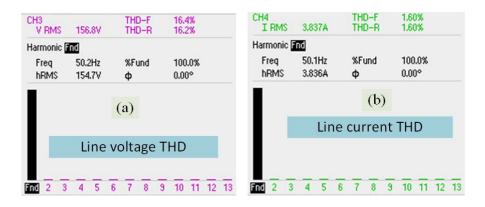

| Figure 3. 8 THD results for 0.79 (lagging) PF load: (a) THD for line voltage waveform, (b) THD for                                               |

| line current waveform31                                                                                                                          |

| Figure 3. 9 THD results for nearly unity PF load: (a) THD for line voltage waveform, (b) THD for                                                 |

| line current waveform31                                                                                                                          |

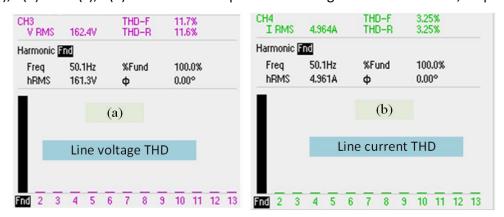

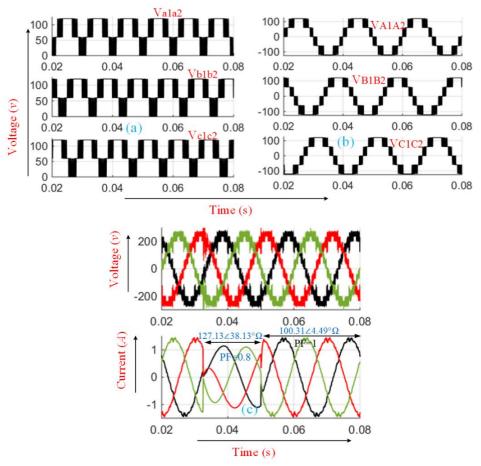

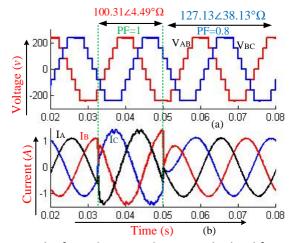

| Figure 3. 10 Simulation results for a dynamic change in the load from 0.99 PF (100.31∠4.49°Ω)                                                    |

| to 0.79 (lagging) PF (127.13∠38.13°Ω): (a) level generator output voltage, (b) polarity generator                                                |

| output voltage (phase voltage) and (c) line voltage and line current32                                                                           |

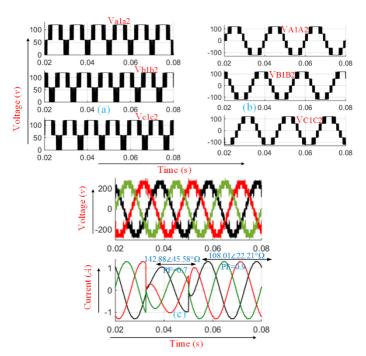

| Figure 3. 11 Simulation results for a dynamic change in the load from nearly 0.9 lagging PF                                                      |

| $(108.01 \angle 22.21^{\circ}\Omega)$ to 0.7 lagging PF (142.88 $\angle 45.58^{\circ}\Omega$ ): (a) level generator output voltage, (b)          |

| polarity generator output voltage (phase voltage) and (c) line voltage and line current                                                          |

| Figure 3. 12 Simulation results for a dynamic change in the load magnitude with the same PF:                                                     |

| (a) Line voltage, (b) Line current                                                                                                               |

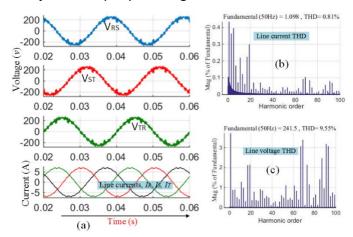

| Figure 3. 13 Simulation results for carrier frequency of 8 kHz: (a) line voltages and currents, (b)                                              |

| line current THD, (c) line voltage THD                                                                                                           |

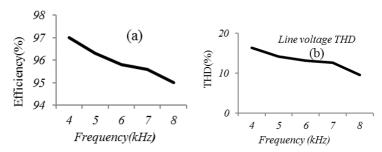

| Figure 3. 14 Effect of carrier frequency on (a) Semiconductor efficiency, (b) Line voltage THD 34                                                |

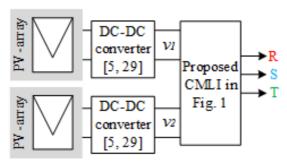

| Figure 3. 15 Simplified block diagram for PV-application of the proposed CMLI35                                                                  |

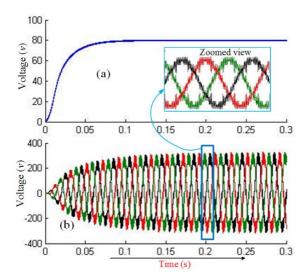

| Figure 3. 16 PV application: (a) PV module output voltage, (b) proposed inverter output line                                                     |

| voltage                                                                                                                                          |

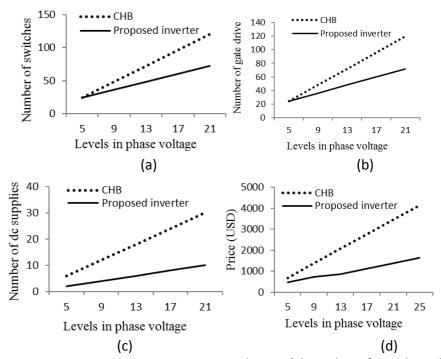

| Figure 3. 17 Device counts and cost comparison with CHB: (a) number of switching devices, (b)                                                    |

| number of gate drivers, (c) number of DC power supplies, (d) cost comparison per phase voltage                                                   |

| level                                                                                                                                            |

| iever                                                                                                                                            |

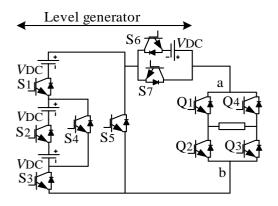

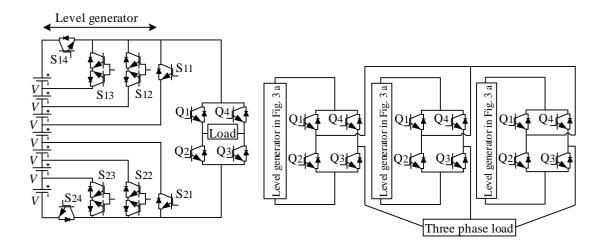

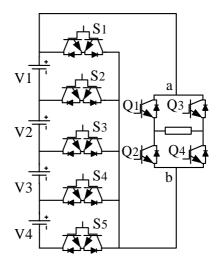

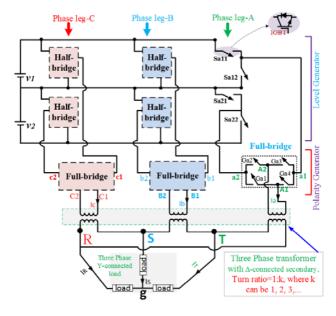

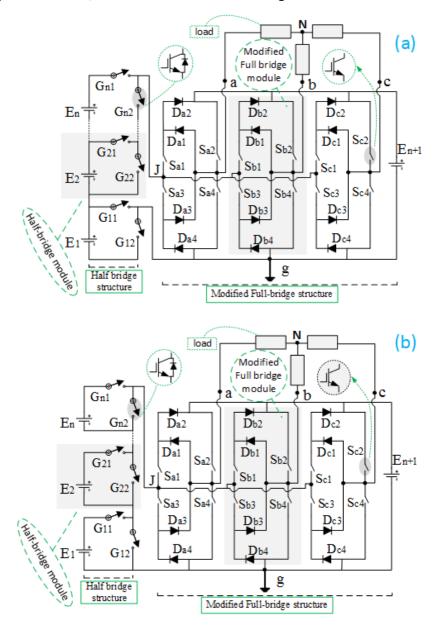

| Figure 4. 1 Proposed generalized three phase half-bridge topology: (a) Non-isolated input dc-                                                    |

| power supply-based half-bridge topology, (b) Isolated input dc-power supply-based half-bridge                                                    |

| topology                                                                                                                                         |

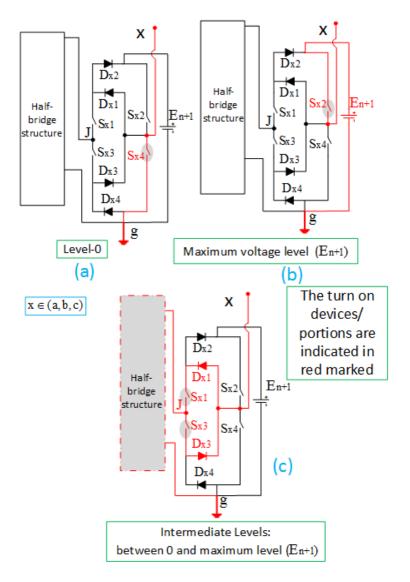

| Figure 4. 2 Generalized overview of the output voltage level generation for: (a) Zero voltage                                                    |

| level, (b)                                                                                                                                       |

| Figure 4. 3 Generalized modulation technique for switching sequence generation48                                                                 |

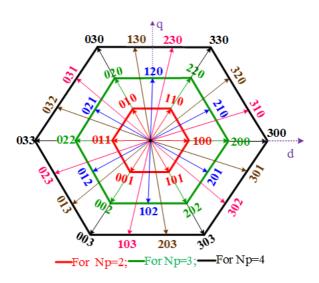

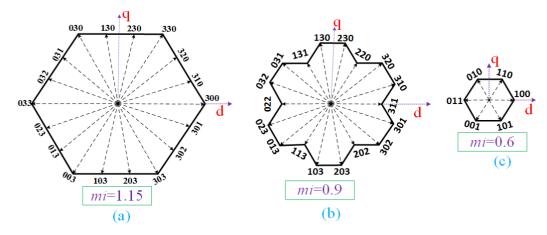

| Figure 4. 4. The presentation of switching states in the space vector diagram                                                                    |

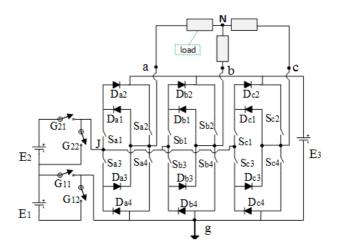

| Figure 4. 5 Schematic of the implemented topology                                                                                                |

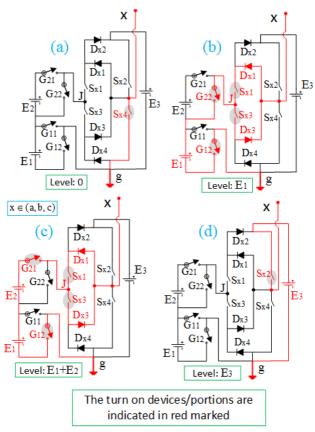

| Figure 4. 6 Different switching mode to generate all the possible levels in the pole voltage: (a)                                                |

|                                                                                                                                                  |

| Voltage level: zero; (b) Voltage level: E <sub>1</sub> ; (c) Voltage level: (E <sub>1</sub> +E <sub>2</sub> ); (d) Voltage level: E <sub>3</sub> |

| Figure 4. 7. Generalized switching states presentation by hexagon in d-q complex plane                                                           |

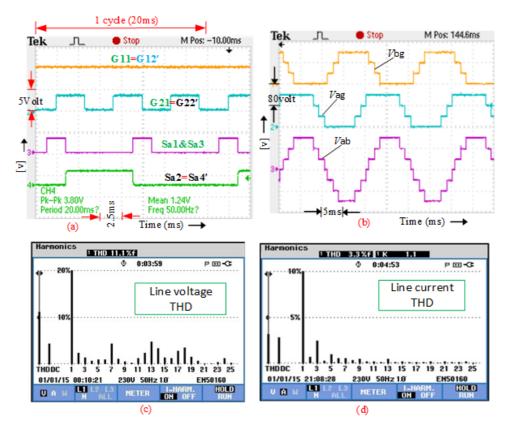

| Figure 4. 8 The switching signals for a complete cycle of the switches $(G_{11}, G_{22}, S_{a1}, S_{a2}, S_{a3})$ 53                             |

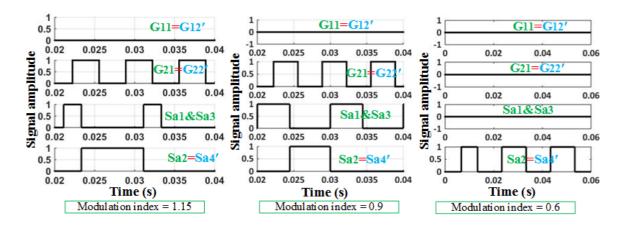

| Figure 4. 9 The functional block diagram of the experimental setup                                                                               |

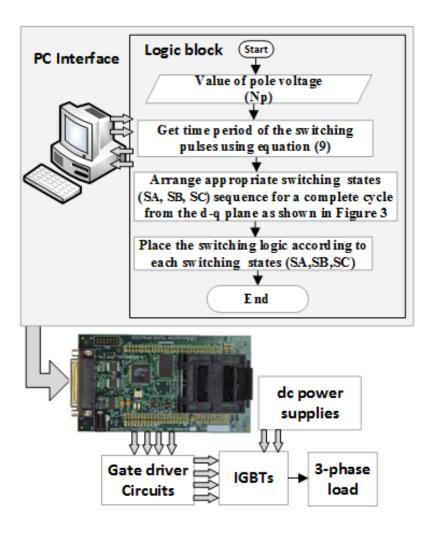

| Figure 4. 10 Simulation results:(a) Intermediate voltage, V <sub>Jg</sub> and pole voltage, V <sub>ag</sub> , (b)                                |

| Intermediate voltage, $V_{Jg}$ and pole voltage, $V_{Bg}$ , (c) Line voltage, $V_{AB}$ , which is generated by                                   |

| tilizing, $V_{ag}$ and $V_{bg}$ , (d) Phase voltage, $V_{aN}$ , (e) The line current, $I_{a1}$ and $I_{a2}$ for (R=40 $\Omega$ and L=1:<br>nH in each phase) and (R=120 $\Omega$ and L=90 mH in each phase), respectively, (f) THD of the line<br>oltage, (g) THD of the line current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

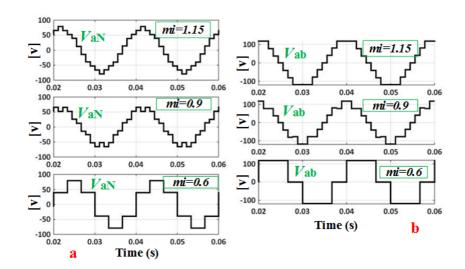

| igure 4. 11 Simulation results: (a) Phase voltage ( $V_{ag}$ ) for different modulation index, (b) Line oltage ( $V_{ab}$ ) for different modulation index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| igure 4. 12 Experimental results: (a) Gate signals of DSP output, (b) Pole voltage, V <sub>ag</sub> and V <sub>bg</sub> [and V <sub>bg</sub> ] (div, 5 ms/div], (c) THD of line voltage, (d) THD of line v | ne  |

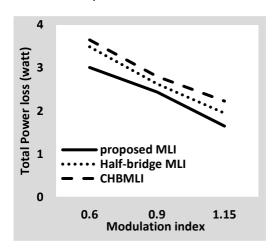

| igure 4. 13 Total loss for different modulation index [57, 71]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58  |

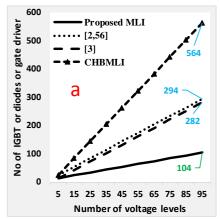

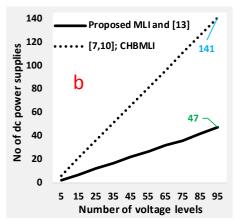

| igure 4. 14 Comparison study for the symmetric method in the half-bridge stage: (a) Number emiconductor devices (IGBT or diode or gate drive circuit) versus number of levels in the line oltage (V <sub>level</sub> ), (b) Number of dc-power supplies versus number of levels in the line voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | of  |

| V <sub>level</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59  |

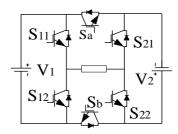

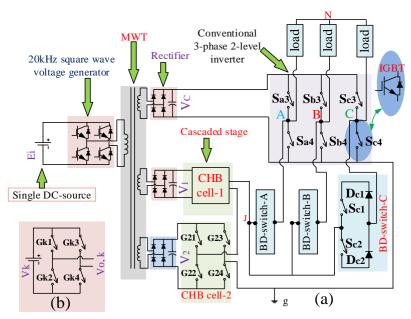

| igure 5. 1 Proposed cascaded multilevel inverter, (a) Proposed inverter when H-bridges are onsidered as cascaded cells, (b) A basic H-bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61  |

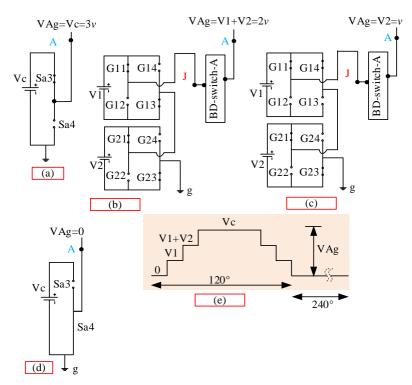

| igure 5. 2 Switching logics for generating four levels in the pole voltages: (a) level 3v; (b) Leve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| $\nu$ ; (c) Level $\nu$ ; (d) Level 0; (e) Complete cycle of the pole voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |

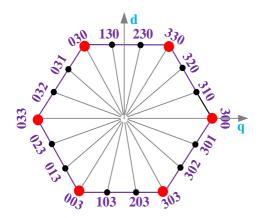

| igure 5. 3 Switching vectors in d-q complex plane of 18 switching states for generating four evels, $N_p$ =4 in the pole voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64  |

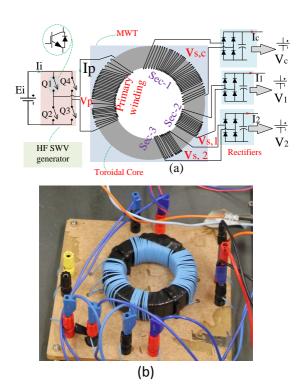

| igure 5. 4 High frequency magnetic link: (a) multiple isolated dc supplies management from a ingle dc source, (b) Prototype of the laboratory MWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | а   |

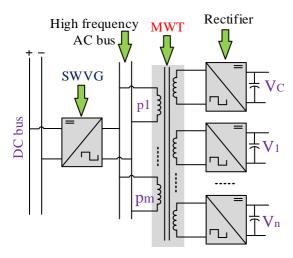

| igure 5. 5 Basic structure of MWT with multiple primary windings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66  |

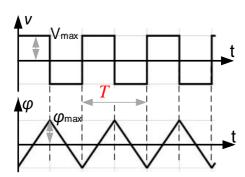

| igure 5. 6 Square wave voltage and flux in a toroidal transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67  |

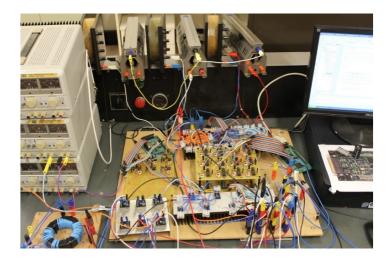

| igure 5. 7 Experimental prototype of the HF magnetic linked CMLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68  |

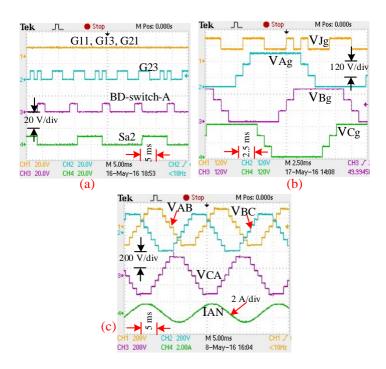

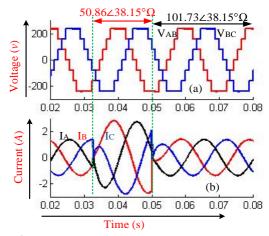

| igure 5. 8 Experimental waveforms of the proposed MLI with constant impedance load. (a) ate pulses for different switches in the H-bridge cells, BD-switch-A and a switch in convention overter within phase leg-A, (b) $V_{Jg}$ , $V_{Ag}$ , $V_{Bg}$ , $V_{Cg}$ , (c) line voltages ( $V_{AB}$ , $V_{BC}$ , $V_{CA}$ ) and line current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

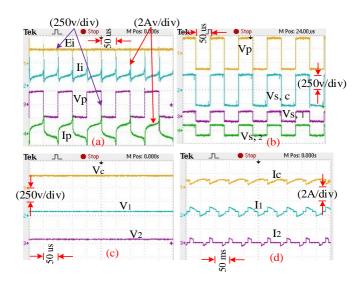

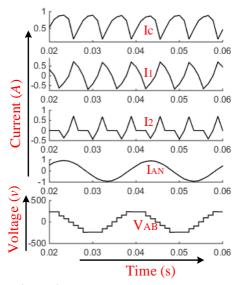

| igure 5. 9 Experimental performance with constant impedance load (a) input/output oltage/current ( $E_i$ , $I_i$ , $V_p$ , $I_p$ ) of the high frequency voltage generator, (b) primary, $V_p$ and econdary voltages, ( $V_{sc}$ ; $V_{s1}$ ; $V_{s2}$ ) of the toroidal transformer, (c) rectifier output voltages ( $V_C$ , $V_{s1}$ , $V_{s2}$ ) and (d) restifier output surrent ( $V_c$ , $V_c$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V1, |

| $I_2$ ) and (d) rectifier output current ( $I_C$ , $I_1$ , $I_2$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ne  |

| igure 5. 11 Simulation results for a dynamic change in the load from nearly unity PF<br>100.31∠4.49°Ω) to 0.8 lagging PF (127.13∠38.13°Ω): (a) line voltage waveforms, (b) line curre<br>vaveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nt  |

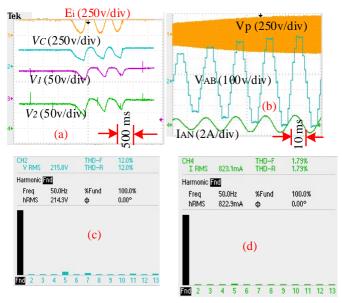

| igure 5. 12 Simulation results for a dynamic change in the load magnitude with the same PF: (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (a) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Figure 5. 13 Simulation results of rectifier output currents: $I_c$ , $I_1$ , $I_2$ and the MLI output voltage | зe |

|----------------------------------------------------------------------------------------------------------------|----|

| and current, $V_{AB}$ and $I_{AN}$ for asymmetric CHB input voltages                                           | 73 |

| Figure 5. 14 Simulation results of rectifier output currents: $I_c$ , $I_1$ , $I_2$ and the MLI output voltage | ge |

| and current, $V_{AB}$ and $I_{AN}$ for unbalanced CHB input voltages                                           | _  |

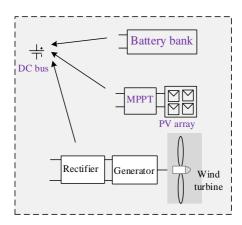

| Figure 5. 15 Common DC-bus with hybrid renewable energy sources                                                |    |

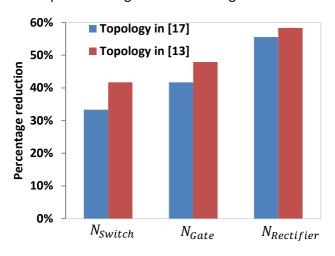

| Figure 5. 16 Percentage reduction in device count with respect to CMLI topologies proposed                     |    |

| [18] and [54]                                                                                                  |    |

|                                                                                                                |    |

|                                                                                                                |    |

| List of Tables                                                                                                 |    |

|                                                                                                                |    |

| Table 2. 1 Switching logic to generate 5-level output voltage                                                  | 9  |

| Table 2.2 Switching logic to generate 5-level output voltage                                                   | 11 |

| Table 2. 3 Switching logic of basic H-bridge cell                                                              | 12 |

| Table 2. 4 Switching logic to generate 5-level output voltage                                                  | 12 |

| Table 2. 5 Comparison among the three conventional MLI                                                         | 13 |

| Table 2. 6 Switching operation                                                                                 | 15 |

| Table 2. 7 Switching operation                                                                                 | 15 |

| Table 2. 8 Switching operation                                                                                 | 16 |

| Table 2. 9 Switching operation                                                                                 | 17 |

| Table 2. 10 Switching operation                                                                                | 18 |

| Table 2. 11 Switching operation                                                                                | 19 |

| Table 2. 12 Table Switching operation of U-cell                                                                | 19 |

| Table 2. 13 switching logic of E-type MLI                                                                      | 20 |

| Table 2. 14 Pros and cons of different reduced device count topologies                                         | 21 |

| Table 3. 1 Properties System specifications of the proposed inverter                                           | 27 |

| Table 3. 2 Inverter performance at different modulation index (based on simulation results)                    |    |

| Table 3. 3 Comparison between the proposed topology and conventional MLI                                       |    |

| Table 3. 4 Comparison of the proposed three-phase symmetric half-bridge topology with of                       |    |

| half-bridge topologies proposed in the literatures                                                             | 39 |

| Table 4. 1 Generalized switching states of the non-isolated dc-power supply-based proposed                     | Ч  |

| half-bridge MLI                                                                                                |    |

| Table 4. 2 Generalized switching states of the isolated dc-power supply-based proposed hal                     |    |

| bridge MLI                                                                                                     |    |

| Table 4. 3 Different dc-power supply choosing methods and related parameters for non-isol                      |    |

| half-bridge based MLIhalf-bridge based MLI                                                                     |    |

| Table 4. 4 Different dc-power supply choosing methods and related parameters for isolated                      |    |

| Half-bridge based MLI                                                                                          |    |

|                                                                                                                |    |

| 51 |

|----|

| 59 |

| 59 |

|    |

| 76 |

| d  |

| 77 |

|    |

# **List of Abbreviations**

| AC   | Alternating Current                |

|------|------------------------------------|

| BD   | Bi-directional                     |

| СНВ  | Cascaded H-bridge                  |

| CMLI | Cascaded Multilevel inverter       |

| DC   | Direct current                     |

| DSP  | digital signal processor           |

| FC   | flying capacitor                   |

| GEEP | Green Electric Energy Park         |

| HFML | High Frequency-Magnetic link       |

| IGBT | Insulated Gate Bipolar Transistors |

| LNG  | liquefied natural gas              |

| MWT  | multi-winding transformer          |

| MLI  | Multilevel inverter                |

| NPC  | Neutral point clamp                |

| PV   | photo-voltaic                      |

| SPWM | Pulse-Width Modulation             |

| SWV  | square wave voltage                |

| THD  | total harmonic distortion          |

# **Chapter One: Introduction**

# 1.1. Motivation and background of the study

The consumption and demand of energy is gradually increasing due to the worldwide rapid industrial development. Owing to the significant consumption of conventional petroleum-based fuel, the world healthy environment is under vulnerable threat. The concept of alternative source of electrical energy or renewable energy sources has come to the attention of the global countries in the last two decades. These new sources are usually interfaced with the electricity grid through power electronic converters. The performance of renewable energy sources such as photo-voltaic and wind turbine is impacted by several environmental conditions including sun radiation, temperature and wind speed. In many cases, the renewable energy source is accomplished with a battery storage system connected to a DC-AC converter [1]. Multilevel inverter (MLI) is gaining its popularity as a DC-AC converter in renewable energy systems, industrial applications [2, 3], liquefied natural gas (LNG), chemical, fuel and water plants, marine and electric vehicles, mining [3, 4], power generation and power-quality improvement devices [1]. There is a significant worldwide research activity aiming at maximizing MLI efficiency while minimizing its cost. Power electronic device count reduction is considered as one of the cost minimizing techniques of voltage source inverters. Also, the control of the inverter switching pulses is a very important section in designing a MLI with reduced device counts. The simplicity in control algorithm is always expected. Moreover, galvanic isolation between the inverter input DC voltage side and output voltage side is essential for grid connected inverters.

#### 1.2 Problem statement of the research

Three MLI topologies, diode clamped or neutral point clamped (NPC), flying capacitor (FC) and cascaded H-bridge (CHB) MLI are considered as conventional MLI topology for commercial applications [2, 3]. While all these conventional MLI topologies are utilized in in various industrial applications, cascaded MLI is preferred for high power and voltage applications (6.6-13.8kV, 500 MVA) [3, 4]. The most attractive features of cascaded H-bridge inverter over the other conventional MLIs are modularity, simple and similar control to all H-bridge modules and requirement for cheap-low voltage switching devices to generate high voltage output [5]. In spite of having a wide range of applications of conventional MLIs, a number of attractive new cascaded

MLI (CMLI) topologies are proposed in the recent few years. New multilevel inverter topologies are mainly developed to reduce device counts as it is directly related with cost and physical size of the converter. Three-phase CMLI has been widely used in large-scale renewable energy applications to comply with the high power conversion requirement. Although several topologies have been proposed in the literatures with reduced device count, majority of these topologies have not been extended to three phase structures yet. It is a common trend that the number of components of single phase topologies to be tripled when they are extended to three phase structures [6-10]. This thesis is aimed at resolving this issue as per the objectives listed below.

#### 1.3 Research objectives

The key objectives of this research proposal are summarised below:

- 1. Developing a cascaded MLI topology with reduced device count.

- 2. Developing a high frequency multi-winding transformer to facilitate the connection of the proposed MLI to a single DC bus system.

- 3. Developing an appropriate control algorithm for the proposed MLI in order to enhance the system efficiency and to improve the power quality of the generated waveforms.

- 4. Investigating the performance of the proposed topology under different loading and operating conditions.

- 5. Building a scaled down laboratory prototype for the proposed MLI topology.

### 1.4 Methodology

The research goals were achieved in three stages as descripted bellow: