# EFFICIENT HARDWARE AND SOFTWARE ASSIST FOR MANY-CORE PERFORMANCE

A Thesis Presented to The Academic Faculty

by

Jungju Oh

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Computer Science

School of Computer Science Georgia Institute of Technology December 2013

Copyright  $\bigodot$  2013 by Jungju Oh

# EFFICIENT HARDWARE AND SOFTWARE ASSIST FOR MANY-CORE PERFORMANCE

Approved by:

Professor Milos Prvulovic, Advisor School of Computer Science Georgia Institute of Technology

Professor Alenka Zajic, Co-advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Tom Conte School of Computer Science Georgia Institute of Technology Professor Hyesoon Kim School of Computer Science Georgia Institute of Technology

Professor Moinuddin K. Qureshi School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: 22 July 2013

To my beloved wife and our first son to be born from whom I have received endless support, and to my parents and brother whom I aspire to live and love like

# PREFACE

This thesis is about how we can do better in the many-core era. It begins with how we can run applications faster with many-core processors, even with the heterogeneous ones. It continues with how we can synchronize faster with more cores. It ends with how we can communicate faster between cores drifting apart in many-core processors. Essentially, this thesis provides vision for the upcoming obstacles with the ever increasing number of cores.

# ACKNOWLEDGEMENTS

I would like to express the deepest appreciation to my advisors, Dr. Milos Prvulovic and Dr. Alenka Zajic. They patiently provided the vision, encouragement and advise necessary for me to see the light at the end of the tunnel. And I also thank my kind committee members, Dr. Tom Conte, Dr. Hyesoon Kim, and Dr. Moinuddin Qureshi for their support and guidance. I extend my gratitude to my internship mentor at Intel, Dr. Christopher J. Hughes for his support, guidance and helpful suggestions.

My friends were sources of laughter and joy. They also gave me emotional support to never give up on this long, winding path. I thank to my lab mates, Guru, Ioannis, Anshuman, Kyle, and Sunjae. I am particularly grateful for the assistance given by my lunch mates, Minsung, Moonkyung, Sangmin, and Hyojoon.

I wish to thank my parents, Seungche Oh and Keumrye Lee. Their love was my driving force. I owe them everything and wish I could show how much I love them.

Last but not the least, I owe my deepest gratitude to my beloved wife who cheered me up and supported me everyday, for which reason I am forever indebted and do not know how to pay back.

# TABLE OF CONTENTS

| DE            | DIC     | ATIOI  | <b>N</b>                                              | iii          |  |

|---------------|---------|--------|-------------------------------------------------------|--------------|--|

| $\mathbf{PR}$ | PREFACE |        |                                                       |              |  |

| AC            | KNO     | OWLE   | DGEMENTS                                              | $\mathbf{v}$ |  |

| LIS           | T O     | F TAE  | BLES                                                  | x            |  |

| LIS           | T O     | F FIG  | URES                                                  | xii          |  |

| SU            | MM.     | ARY .  |                                                       | xv           |  |

| I             | INT     | RODI   | UCTION                                                | 1            |  |

|               | 1.1     |        | core Era and Parallel Applications                    | 1            |  |

|               | 1.2     | Scalab | vility Limiters                                       | 2            |  |

|               |         | 1.2.1  | Load Imbalance and Debugging Framework                | 2            |  |

|               |         | 1.2.2  | Barrier Latency and TL-based Hardware Barriers        | 3            |  |

|               |         | 1.2.3  | Increasing On-chip Latency and Hybrid TL Interconnect | 6            |  |

|               | 1.3     | Thesis | Statement                                             | 7            |  |

|               | 1.4     | Thesis | Overview                                              | 8            |  |

| II            | BA      | CKGR   | OUND AND RELATED WORK                                 | 9            |  |

|               | 2.1     | Load 1 | Imbalance Debugging                                   | 9            |  |

|               | 2.2     | Hardw  | vare Support for Barriers                             | 11           |  |

|               |         | 2.2.1  | Transmission Lines                                    | 12           |  |

|               | 2.3     | On-ch  | ip Network: Topologies and Latencies                  | 13           |  |

|               |         | 2.3.1  | On-chip Transmission Lines                            | 14           |  |

|               |         | 2.3.2  | Hybrid Interconnect and Steering                      | 15           |  |

| III           | A F     | RAM    | EWORK FOR DEBUGGING LOAD IMBALANCE .                  | 18           |  |

|               | 3.1     | Overv  | iew of LIME                                           | 18           |  |

|               | 3.2     | LIME   | Analysis Framework                                    | 23           |  |

|               |         | 3.2.1  | Causality Analysis for Hardware Events                | 23           |  |

|    |     | 3.2.2  | Hierarchical Clustering                     | 24 |

|----|-----|--------|---------------------------------------------|----|

|    |     | 3.2.3  | Classification of Clusters                  | 25 |

|    |     | 3.2.4  | Finding Cluster Leaders                     | 25 |

|    |     | 3.2.5  | Multiple Regression                         | 27 |

|    |     | 3.2.6  | Reporting to the Programmer                 | 29 |

|    | 3.3 | Impler | mentation                                   | 30 |

|    | 3.4 | Exper  | iments and Results                          | 31 |

|    |     | 3.4.1  | Experimental Setup                          | 31 |

|    |     | 3.4.2  | Simulator-Based Profiling                   | 32 |

|    |     | 3.4.3  | Pin-Based Profiling                         | 33 |

|    |     | 3.4.4  | Verifying Reported Cache Misses             | 34 |

|    |     | 3.4.5  | Verifying Reported Control Flow Causes      | 36 |

|    |     | 3.4.6  | Input Sensitivity of LIME                   | 40 |

|    |     | 3.4.7  | Scalability of LIME                         | 43 |

| IV | LIM | IE EX  | TENSION FOR HETEROGENEOUS CORES             | 46 |

|    | 4.1 | Load 1 | Imbalance Debugging for Heterogeneous Cores | 46 |

|    | 4.2 | LIME   | Analysis Extension                          | 51 |

|    |     | 4.2.1  | Scaling Thread Execution Time               | 52 |

|    | 4.3 | Exper  | iments and Results                          | 56 |

|    |     | 4.3.1  | Implementation and Experimental Setup       | 57 |

|    |     | 4.3.2  | Heterogeneity and Load Imbalance            | 58 |

|    |     | 4.3.3  | Scaling Results                             | 59 |

|    |     | 4.3.4  | Heterogeneous LIME Results                  | 62 |

| V  |     |        | FING MULTIPLE FAST BARRIERS USING ON-CHIP   | 64 |

|    | 5.1 | Design | n of TLSync                                 | 64 |

|    | 5.2 | Impler | mentation Details                           | 70 |

|    |     | 5.2.1  | Using TLs to Connect Many Cores             | 70 |

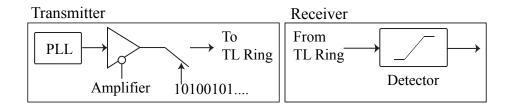

|    |     | 5.2.2  | Transmitter and Receiver Design             | 72 |

|    |     |        |                                             |    |

|    |               | 5.2.3   | Transmission Line Design                                                           | 74  |

|----|---------------|---------|------------------------------------------------------------------------------------|-----|

|    | 5.3           | Experi  | imental Evaluation                                                                 | 77  |

|    |               | 5.3.1   | Barrier Latency                                                                    | 78  |

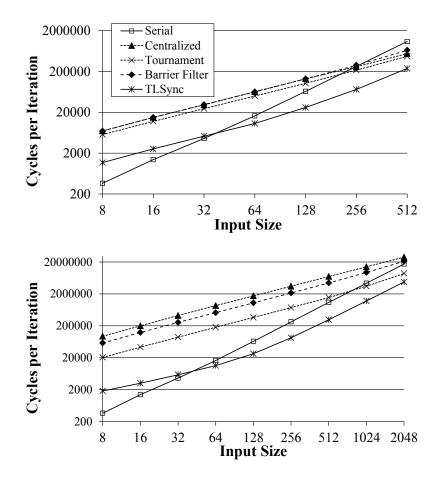

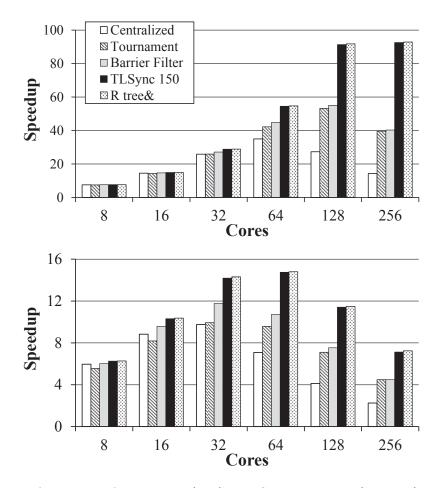

|    |               | 5.3.2   | Livermore Kernels                                                                  | 79  |

|    |               | 5.3.3   | Streamcluster and Dithering                                                        | 83  |

|    |               | 5.3.4   | Implementation Cost                                                                | 85  |

| VI | $\mathbf{TL}$ | RING    | INTERCONNECT: LOW-LATENCY UNSWITCHED<br>AND A HIGH-THROUGHPUT SWITCHED INTER-<br>T |     |

|    | 6.1           | Motiva  | ation                                                                              | 88  |

|    | 6.2           | Transr  | nission Line Ring                                                                  | 89  |

|    |               | 6.2.1   | Unidirectional Transmission Line Ring                                              | 90  |

|    |               | 6.2.2   | Disconnect-Based Arbitration Mechanism                                             | 96  |

|    |               | 6.2.3   | Broadcasts on the TL Ring                                                          | 96  |

|    | 6.3           | Traffic | Steering                                                                           | 97  |

|    |               | 6.3.1   | Benefit Estimation and Packet Scoring                                              | 97  |

|    |               | 6.3.2   | Threshold-Based Throughput Control                                                 | 100 |

|    |               | 6.3.3   | Emergency Re-steering                                                              | 101 |

|    | 6.4           | Impler  | nentation Cost                                                                     | 102 |

|    | 6.5           | Perfor  | mance Evaluation                                                                   | 104 |

|    |               | 6.5.1   | Characteristics of the Benchmark Applications                                      | 104 |

|    |               | 6.5.2   | Impact of Latency Reduction with TL                                                | 108 |

|    |               | 6.5.3   | Latency Estimation and Re-Steering                                                 | 109 |

|    |               | 6.5.4   | Effect of Ring Bandwidth and Steering                                              | 110 |

|    |               | 6.5.5   | Effect of Advanced Switched Networks                                               | 112 |

|    |               | 6.5.6   | Sensitivity to TL Ring Bandwidth                                                   | 113 |

|    |               | 6.5.7   | Non-Latency-Critical Applications                                                  | 114 |

|    |               | 6.5.8   | Power Benefit                                                                      | 114 |

| VII CONCLUSIONS AND FUTURE WORK |                             |     |  |  |

|---------------------------------|-----------------------------|-----|--|--|

| 7.1                             | Thesis Summary              | 115 |  |  |

| 7.2                             | Limitations and Future Work | 116 |  |  |

| 7.3                             | Concluding Remarks          | 118 |  |  |

| REFERENCES                      |                             |     |  |  |

# LIST OF TABLES

| 1  | Description of applications and parallel sections used in the experi-<br>ments. Parallel section denotes the location of the <i>pthread_barrier_wait</i><br>or <i>pthread_join</i> call that delimits the parallel section.                                          | 31 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Load imbalance occurred in benchmark applications for varying num-<br>ber of threads. Coefficient of Variation and Average/Max Ratio are<br>weighted averages of per instance values                                                                                 | 32 |

| 3  | Results of LIME analysis. The Rpt columns show the number of re-<br>ported events with score greater than 0.1. The number of all reported<br>events is listed in parentheses. The Score columns give the reported<br>score for the highest-scored event of each type | 33 |

| 4  | Results with Pin-based profiling                                                                                                                                                                                                                                     | 34 |

| 5  | Description of small, medium and large inputs for benchmark applica-<br>tions                                                                                                                                                                                        | 40 |

| 6  | Load imbalance of benchmark applications for varying input size and thread counts                                                                                                                                                                                    | 41 |

| 7  | Results of LIME analysis for 64 core configuration on varying input sizes (Small, Medium and Large)                                                                                                                                                                  | 42 |

| 8  | Scores reported by LIME analysis for homogeneous cores (Section 3.4.2) and for heterogeneous cores. For heterogeneous cores, unmodified LIME failed to locate the cause of imbalance in many applications.                                                           | 48 |

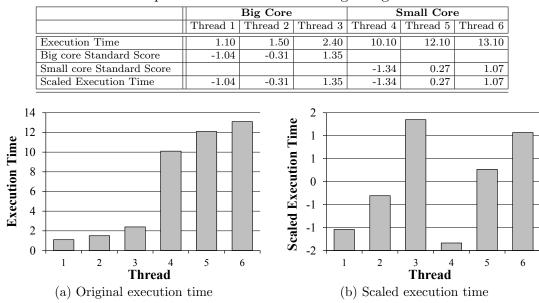

| 9  | Example of execution time scaling using standard scores                                                                                                                                                                                                              | 53 |

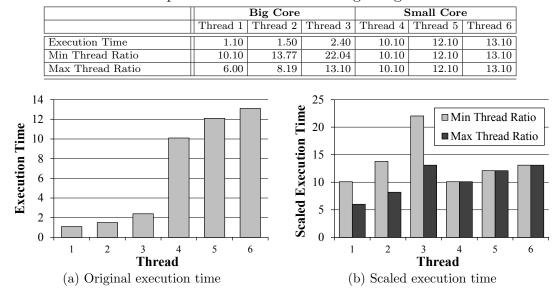

| 10 | Example of execution time scaling using standard scores                                                                                                                                                                                                              | 54 |

| 11 | Configuration of 32-core heterogeneous processor with 8 big cores and 24 small, throughput cores                                                                                                                                                                     | 57 |

| 12 | Scaling ratio with various scaling method. The ratio denotes how slow the small cores are than the big cores                                                                                                                                                         | 59 |

| 13 | Event costs calculated using average thread cost                                                                                                                                                                                                                     | 61 |

| 14 | Scores reported by LIME analysis for homogeneous cores (Section 3.4.2) and for heterogeneous cores. For heterogeneous case, big cores' thread execution times are scaled using average thread cost.                                                                  | 62 |

| 15 | Simulation Setup                                                                                                                                                                                                                                                     | 77 |

| 16 | The cost of main active components used in TLSync for a 16-core processor in 45nm technology                                                                                                                                                                         | 85 |

| 17 | The cost of main active components used in TL ring for 64-core pro- |     |

|----|---------------------------------------------------------------------|-----|

|    | cessor in 22 nm technology.                                         | 103 |

# LIST OF FIGURES

| 1  | Code for sample parallel section from <i>radix</i> . All non-control-flow statements are removed.                                                                                                                                             | 19      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2  | Execution time, imbalance, and thread behavior of key points in Figure 1. Points that cause load imbalance are shown with thicker lines.                                                                                                      | 20      |

| 3  | Example of clusters and leader nodes                                                                                                                                                                                                          | 26      |

| 4  | Example of final score computation                                                                                                                                                                                                            | 29      |

| 5  | Imbalance reduction of each parallel section when reported cache misses are eliminated.                                                                                                                                                       | 35      |

| 6  | LIME report for <i>lu-cb</i>                                                                                                                                                                                                                  | 37      |

| 7  | LIME report for <i>volrend</i>                                                                                                                                                                                                                | 38      |

| 8  | LIME report for <i>barnes</i> .                                                                                                                                                                                                               | 39      |

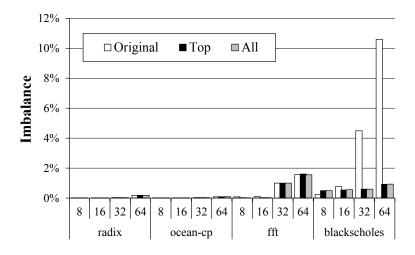

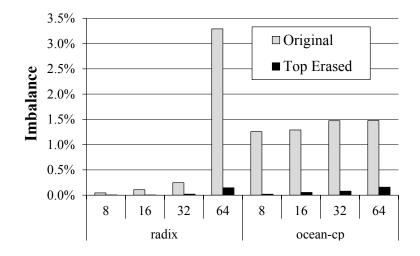

| 9  | Imbalance of <i>radix</i> and <i>ocean-cp</i> applications on smaller cache con-<br>figuration before and after we "erased" reported cache miss events<br>from LIME. Top-erased means only top reported events are treated<br>as "cache-hits" | 43      |

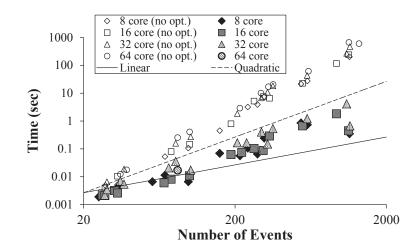

| 10 | Clustering time vs. number of events. Each point represents clustering time of one parallel section. Note the logarithmic scale markings on each of the axes.                                                                                 | 45      |

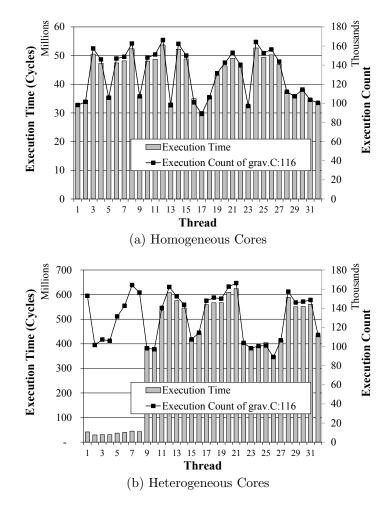

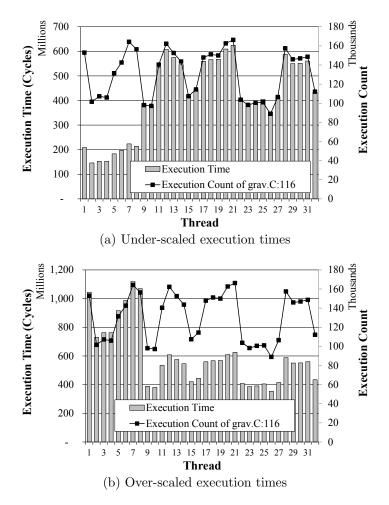

| 11 | Execution time and execution count of an event that causes load im-<br>balance ( <i>grav.C:116</i> ) from <i>barnes</i> on homogeneous and heterogeneous<br>cores                                                                             | 49      |

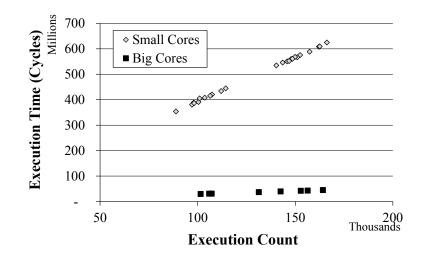

| 12 | Execution time and event count of <i>grav.C:116</i> from heterogeneous cores. Note that it is not possible to find a common trend line for both cores.                                                                                        | 50      |

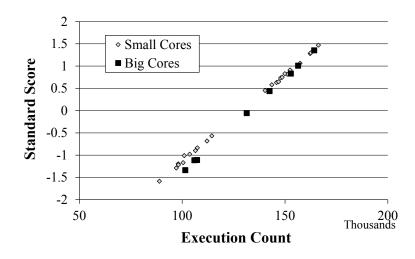

| 13 | Adjusted execution time using standard score and event count of <i>grav.C:11</i> from heterogeneous cores.                                                                                                                                    | 6<br>51 |

| 14 | Examples of improper adjustment of execution times                                                                                                                                                                                            | 52      |

| 15 | Execution time before and after scaling using standard scores. $\ldots$                                                                                                                                                                       | 53      |

| 16 | Execution time before and after scaling using min/max thread ratio                                                                                                                                                                            | 54      |

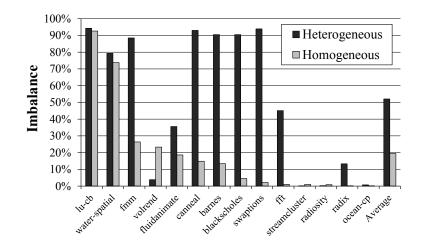

| 17 | Exacerbated load imbalance on heterogeneous cores due to the perfor-<br>mance difference.                                                                                                                                                     | 58      |

| 18 | Overall design of the TL network and TLSync transmitters and receivers.                                                                                                                                                                       | 66      |

| 19 | TLSync Barrier latency for different frequency band allocations                                                                                                                                        | 69  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 20 | Realizations of transmission lines                                                                                                                                                                     | 74  |

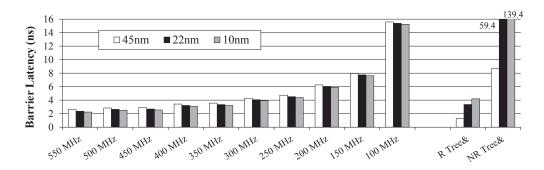

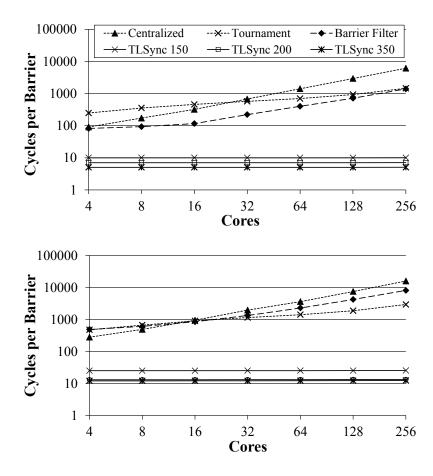

| 21 | Raw barrier latency in Small-Core (top) and Large-Core (bottom) con-<br>figurations.                                                                                                                   | 78  |

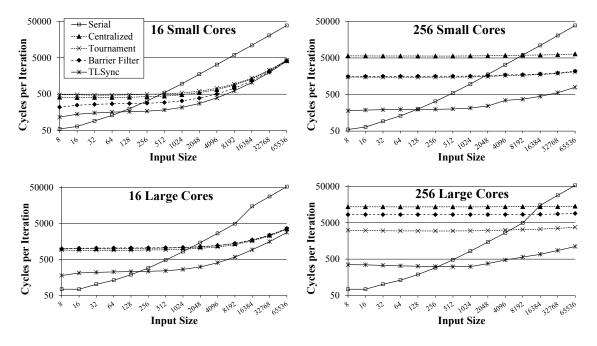

| 22 | Performance of Livermore Loop 2 for various barrier mechanisms                                                                                                                                         | 80  |

| 23 | Performance of Livermore Loop 3 with various barrier mechanisms with 16 (top) and 256 (bottom) cores.                                                                                                  | 81  |

| 24 | Performance of Livermore Loop 6 with various barrier mechanisms with 16 (top) and 256 (bottom) cores.                                                                                                  | 82  |

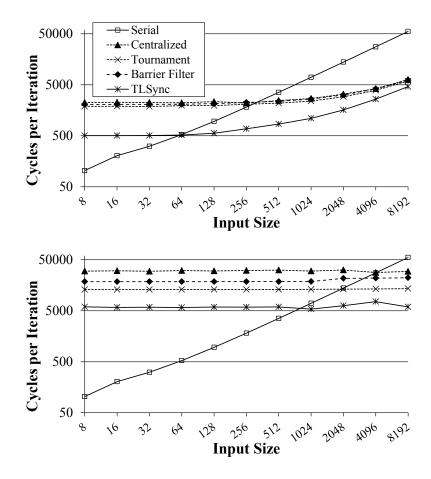

| 25 | Performance of Dithering (top) and Streamcluster (bottom) with var-<br>ious barrier mechanisms.                                                                                                        | 84  |

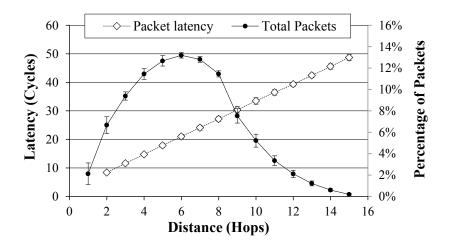

| 26 | Distribution of the number of packets and packet latency on switched interconnection for varying distances. Values are averaged for all the tested applications and shown with 95% confidence interval | 89  |

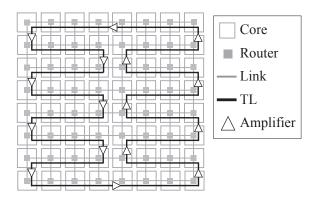

| 27 | TL-based ring with packet-switched network                                                                                                                                                             | 90  |

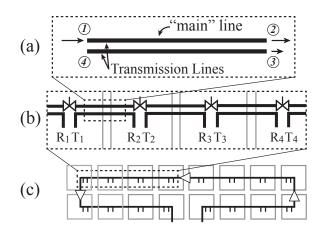

| 28 | Connecting UTL couplers into a ring                                                                                                                                                                    | 92  |

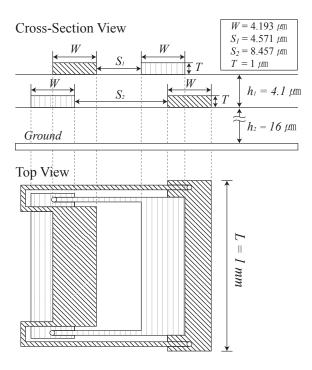

| 29 | Cross-section and top view of the coupler.                                                                                                                                                             | 93  |

| 30 | Transmitter and receiver design for TL ring                                                                                                                                                            | 94  |

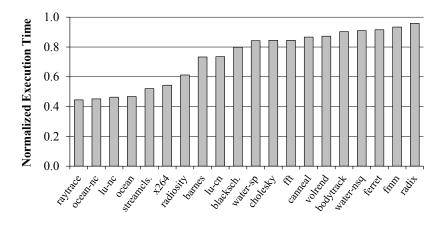

| 31 | Normalized execution time with infinite throughput on-chip intercon-<br>nect (single cycle latency)                                                                                                    | 105 |

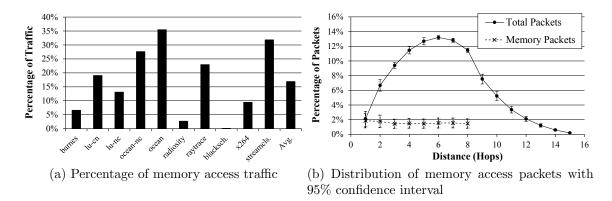

| 32 | Total packets and memory access packets on switched on-chip intercon-<br>nect with 95% confidence interval. 8 memory controllers are located<br>above the top row of the mesh network                  | 106 |

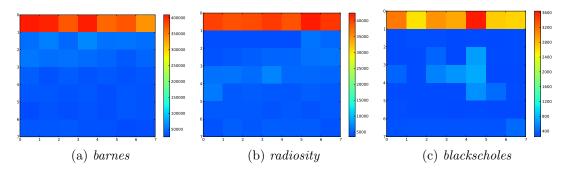

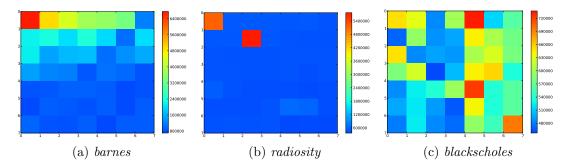

| 33 | Heatmap of the memory traffic. The value means the number of pack-<br>ets a corresponding core generates or receives                                                                                   | 106 |

| 34 | Heatmap of the overall traffic. The value means the number of packets a corresponding core generates or receives.                                                                                      | 107 |

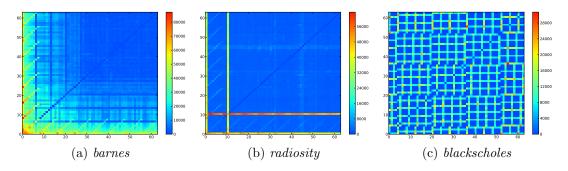

| 35 | Heatmap of the communication pattern. The value on $(x, y)$ is the number of packets going from $y$ to $x$                                                                                             | 107 |

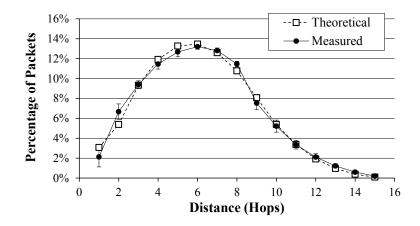

| 36 | Distribution of traffic for varying packet distance from real applica-<br>tions (Measured). Theoretical random distribution is also depicted<br>(Theoretical)                                          | 108 |

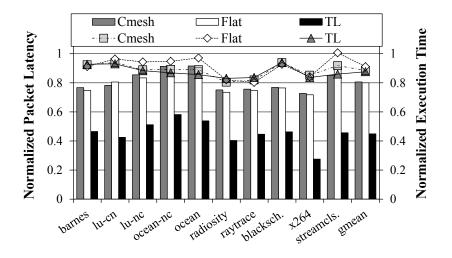

| 37 | Normalized packet latency to the baseline mesh (left axis) of concen-<br>trated mesh (Cmesh), flattened butterfly (Flat) and TL ring with ex-<br>ecution time (right axis)                                                                       | 109 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

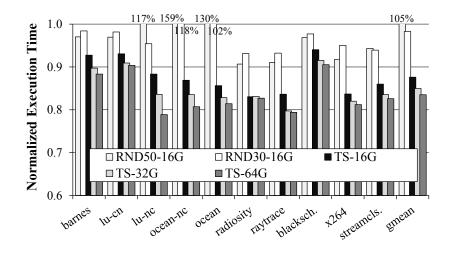

| 38 | Normalized execution time of traffic steering (TS) with varying TL ring bandwidth, random (RND)                                                                                                                                                  | 111 |

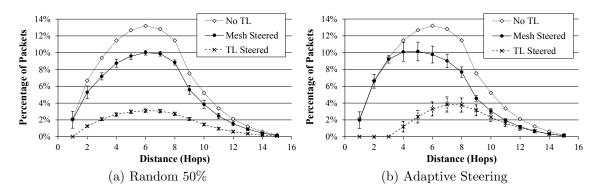

| 39 | Distribution of packets steered to TL ring and switched network with<br>Random Steering (left) and Adaptive Steering (right). Dotted line<br>denotes the distribution of packets with switched network only. 95%<br>confidence interval is shown | 112 |

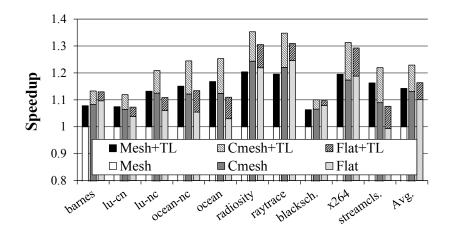

| 40 | Speedup over baseline mesh when TL ring (16 Gb/s) is used with concentrated mesh network (Cmesh) and flattened butterfly (Flat). $\ .$                                                                                                           | 113 |

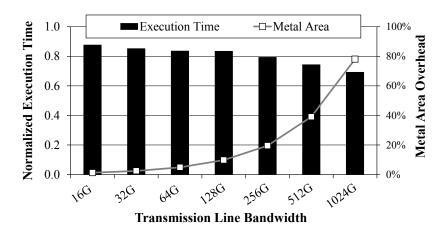

| 41 | Normalized execution times (averaged for all benchmarks) for config-<br>urations with various TL ring bandwidth                                                                                                                                  | 114 |

#### SUMMARY

Software frameworks and hardware techniques that address scalability limiters can cooperatively improve the performance of parallel applications on many-core processors.

In recent years, the number of available cores in a processor are increasing rapidly while the pace of performance improvement of an individual core has been lagged. It led application developers to extract more parallelism from a number of cores to make their applications run faster. However, writing a parallel program that scales well with the increasing core counts is challenging. Consequently, many parallel applications suffer from *performance bugs* caused by *scalability limiters*.

We expect core counts to continue to increase for the foreseeable future and hence, addressing scalability limiters is important for better performance on future hardware. With this thesis, I propose both software frameworks and hardware improvements that I developed to address three important scalability limiters: load imbalance, barrier latency and increasing on-chip packet latency.

First, I introduce a debugging framework for load imbalance called LIME. The LIME framework uses profiling, statistical analysis and control flow graph analysis to automatically determine the nature of load imbalance problems and pinpoint the code where the problems are introduced.

Second, I address scalability problem of the barrier, which has become costly and difficult to achieve scalable performance. To address this problem, I propose a transmission line (TL) based hardware barrier support, called TLSync, that is orders of magnitude faster than software barrier implementation while supports many (tens) of barriers simultaneously using a single chip-spanning network.

Third and lastly, I focus on the increasing packet latency in on-chip network, and propose a hybrid interconnection where a low-latency TL based interconnect is synergistically used with a high-throughput switched interconnect. Also, a new adaptive packet steering policy is created to judiciously use the limited throughput available on the low-latency TL interconnect.

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Multi-core Era and Parallel Applications

In recent years, the number of available cores in a processor is increasing rapidly while the pace of performance improvement of an individual core has been lagged. As a result, application developers are now required to extract more parallelism and leverage the abundant number of cores to make their applications run faster. In the single-core era, the improvement in core performance is translated into a speedup of an application without any change on the application. However, the increasing core counts barely contribute to performance gain of a parallel application unless written specifically to *scale*, and writing a scalable parallel program is a challenging task, putting aside the problem of writing a correct program. Many parallel applications have suffered from *performance bugs* caused by *scalability limiters*. These prevent performance from improving as much as it should with more cores.

Since we expect core counts to continue to grow for the foreseeable future, addressing scalability limiters is crucial for software development in order to obtain better performance on future hardware. However, managing scalability limiters is not a straightforward task because numerous factors can lead to various types of scalability limiters that are either software- or hardware-related ones, or both. For example, a program may not scale with more cores because the algorithm implemented in the program is unable to offload proper workload to the additional cores, causing softwarerelated scalability limiters [72]. It is also possible that the application interacts with underlying hardware in a biased way, causing an unbalanced progress between cores. This may incur stall at synchronization point and deteriorates scalability. In that case, the scalability limiter is related to both hardware and software.

Thus, in this work, I propose both a software framework and hardware improvements that I developed to identify and manage important scalability limiters. Specifically, I target three limiters: load imbalance, barrier latency and increasing on-chip packet latency.

#### 1.2 Scalability Limiters

#### 1.2.1 Load Imbalance and Debugging Framework

Load imbalance is one of the key scalability limiters in parallel applications. Ideally, a parallel application assigns an equal amount of work to all available cores, keeping all of them busy for the parallel section delimited by global synchronization points (i.e., barriers). Load imbalance occurs when some cores run out of work and must wait for the remaining cores to finish their work.

One characteristic of load imbalance is that is relatively easy to detect—one can watch for threads waiting at the end of a parallel section or at a thread-join point, but it is much more difficult to diagnose the cause of load imbalance. In particular, to help programmers decide what changes to make to the application to resolve the imbalance, the cause of load imbalance should be identified with sufficient precision. However, it may be difficult to diagnose the cause of load imbalance because of the wide range of candidates. For instance, load imbalance can be caused by assigning an unfair proportion of tasks to a thread, or by assigning too many long tasks to the same thread—both of these manifest as control flow differences between threads. Diagnosing causes for imbalance becomes even harder when it occurs due to interactions between the application and the underlying hardware (e.g., threads having different numbers of cache misses). Such causes cannot be easily detected through code inspection or static analysis. Reducing load imbalance has long been an active research topic. The most common approach to reducing load imbalance is to use customized software stack that supports dynamic task scheduling, such as OpenMP [75] and TBB [42]. Dynamic task scheduling involves partitioning the parallel work into many more tasks than threads, and using a run-time system to assign tasks to threads on-demand. Dynamic scheduling significantly reduces load imbalance, but introduces considerable runtime overheads, both from executing scheduling code and from the loss of cache locality among tasks. These overheads increase with the number of cores/threads, and can dominate performance [57].

Because load imbalance is a major issue in debugging the performance of parallel programs, and because existing approaches do not satisfactorily address this problem, there is a need for tools to help programmers efficiently find what causes load imbalance in their code. Therefore, I propose a framework for debugging load imbalance, called LIME. This framework uses profiling, statistical analysis, and control flow graph analysis to automatically determine the nature of load imbalance problems and pinpoint the code where the problems are introduced. The framework does not aim to automatically exploit or reduce load imbalance unlike prior approaches. Instead, LIME provides highly accurate information to programmers about what causes the imbalance and where in the code it is introduced, with the goal to minimize trialand-error diagnosis and the programming effort needed to alleviate the performance problem in parallel applications.

#### **1.2.2** Barrier Latency and TL-based Hardware Barriers

Second scalability limiter I am addressing is the barrier. Barrier synchronization is useful building block for parallel programming that makes it possible to implement "meeting-point" between multiple or all threads. However, with growing numbers of cores within a chip and increasing wire latencies, barrier synchronization becomes increasingly challenging to achieve scalable performance.

The barrier problem is closely related with the load imbalance, the first scalability limiter presented in previous section. Ironically, as one gets more successful to reduce the load imbalance using the proposed LIME framework, the time to complete a barrier, i.e., barrier latency in the application becomes worse with non-scalable barriers. This is because the load imbalance reduction makes threads that used to arrive the barrier at different times (and hence caused load imbalance) arrive at similar times without much stall. That balanced arrival increases contention at the non-scalable barrier, resulting longer barrier latency.

Simplistic software-only implementations that maintain global arrival counter is the example of the non-scalable barrier. They suffer from serialization in accessing the global counter, so the barrier latency increases in proportion to the number of cores. Hierarchical barriers can reduce this contention, but require multiple rounds of point-to-point synchronization between cores and an inefficient broadcast via a shared memory location.

Hardware barrier networks provide much lower barrier latency and scalability but require a dedicated chip-spanning network whose wire latency has an undesirable technology-scaling trend. Worse, future many-core chips are likely to execute several parallel applications, virtual machines, etc., each of which may need a separate barrier network to synchronize its threads. Because the number of barrier networks (and their total cost) is a design-time decision, designers must decide between a) providing multiple expensive barrier networks that may be unused and b) not providing enough of them and potentially forcing applications to fall back to a much slower software barrier implementation. To address the latency problem of software barrier and multiple-barrier support issues faced by traditional hardware barrier networks, I propose a new hardware barrier system that exploits the advantages of "transmission lines". Transmission lines have been proposed as a low-latency solution for on-chip interconnects, e.g. for express links in the on-chip network [21, 53] or for connecting distant banks in large caches [9]. In addition to providing much lower signaling latencies than traditional wires, transmission lines can be used to transmit multiple modulated signals at different RF frequencies. These advantages are tempered by increased cost and significant signal processing delays for demodulation and decoding of RF signals.

In this thesis, I propose a hardware barrier network, called TLSync, that allocates a relatively small part of the transmission line's available spectrum to each barrier group, allowing a single chip-spanning transmission-line network to support many (tens) of barriers simultaneously. In this barrier implementation, signal processing latencies are minimized by not relying on data transmission. Instead, TLSync barrier uses a simple signal presence test to determine when all cores in the group have arrived to the barrier. In essence, a TLSync barrier performs a wired-AND operation using the presence/absence of a "tone" at the barrier's allocated frequency to replace the traditional signaling using high and low voltage level on a wire. Each core transmits into the transmission line a low-power "tone" at its barrier's allocated frequency and stops transmitting when it finally arrives to the barrier. The receiver in each core is a simple tone detector tuned to the barrier's frequency, and a core can exit the barrier when this receiver no longer detects a "tone" at the barrier's frequency.

I provide an analysis of how the underlying chip-spanning transmission-line network can be designed to obtain accurate latency estimates for the proposed mechanism. This analysis offers several important insights on the tradeoffs that I face in using transmission lines (TLs) for on-chip transmission of RF signals. The key finding is that the end-to-end latency of RF transmission is dominated by fundamental signal processing delays that must be accounted for, and that careful modeling of TLs is necessary to account for severe signal weakening and degradation when multiple transmitters and/or receivers are connected along one transmission line.

#### 1.2.3 Increasing On-chip Latency and Hybrid TL Interconnect

The last scalability limiter I explore in this thesis is the increasing packet latency in on-chip network. With the steadily growing number of on-chip cores, a shared bus has reached the point where it no longer provides sufficient bandwidth for the coherence traffic. As a result, many-core chip recently adopts a packet-switched network-on-chip (NoCs), e.g. a mesh or torus [26] that provides better throughput.

In such NoCs, each link is short and its length scales down with technology, so latency and energy consumption scale well if most traffic is local. Further, the aggregate bandwidth of all the links scales with the number of cores. However, switched networks come at a significant latency cost for traffic between far-apart cores—these messages traverse more switches when the core count grows, in addition to longer wire delays due to technology scaling. This increasing on-chip latency can be a serious obstacle to achieve good scalability performance for parallel applications because in usual, scalable applications try to fully utilize all cores in a chip, incurring communications between far-apart cores that cause significant latency disadvantage.

One viable solution for the worsening NoC latency is to use transmission lines in packet transmission. As denoted in TLSync, the signals propagation is close to the speed of light. However, TLs consume far more metal area than traditional wires, so the same-area TL-based NoC typically either provides far less throughput or requires very sophisticated signaling to improve this throughput.

I overcome this physical limitation of TL using an observation that the latency advantage of TLs over wires is the greatest for long-distance packets. Local traffic (which often represents the majority of the traffic) sees a relatively low latency even in a traditional mesh based NoC and it has little benefit from using costly TLs. Guided by this insight, a low-cost unidirectional TL (UTL) ring interconnect is designed. The UTL ring provides very low maximum propagation latency (e.g. 2 ns for a 64-core chip), uses simple signaling and has a very efficient and simple arbitration mechanism. However, this ring has limited throughput, so I use it *together* with a traditional switched NoC, by judiciously steering each packet to the ring or the packet-switched interconnect. Evaluation shows that the TL hybrid interconnect can help parallel applications to run faster with more cores, improving execution time by 12.4% on average compared to the case where the mesh interconnect is used alone.

#### 1.3 Thesis Statement

With the accelerating technology improvements, the number of available cores in a processor steadily increases. As a result, it is inevitable for application developers to exploit parallelism for better application performance. However, writing a fast parallel application is challenging due to many obstacles called *scalability limiters*.

This thesis addresses the scalability limiters to assist development of well-performing parallel applications. The scalability limiters occur from a variety of reasons, such as a defect in application design and incapability of the underlying hardware that executes the application. To effectively address those limiters, custom-built approach that deals with both software and hardware is necessary. Thus, I propose both a software framework and hardware improvements that are specifically devised to address three important scalability limiters: load imbalance, barrier latency and increasing on-chip packet latency.

This thesis proposes an initial exploration of collective approaches that are specifically targeted to address performance problems of parallel applications on many-core processors. The thesis proposes the following statement: Software frameworks and hardware techniques that address scalability limiters can cooperatively improve the performance of parallel applications on many-core processors.

# 1.4 Thesis Overview

Chapter 3 explains the first software framework, *LIME*, that addresses load imbalance. The LIME framework is extended to incorporate applications running on heterogeneous cores in Chapter 4. Then, in Chapter 5, a new TL-based hardware barrier *TLSync* is proposed as a solution to current barriers that limits scalability. Further exploiting a transmission line design, I propose a new hybrid interconnect that explores the third scalability limiter, i.e., increased latency of switched on-chip networks in Chapter 6. I conclude in Chapter 7.

## CHAPTER II

# BACKGROUND AND RELATED WORK

#### 2.1 Load Imbalance Debugging

Load imbalance has been one of the most serious problems in parallel and distributed systems. Load imbalance is described as the amount of wasted resource due to a lagging thread or machine, and many imbalance metrics have been proposed to characterize the load imbalance. One common metric is to define the imbalance as the difference between resource utilization of each entities using standard deviation between measured utilizations [5, 100]. Since this standard deviation depends on the measurement unit, often, coefficient of variation which is the ratio of the standard deviation over the mean value is used. This metric tells that if it is well load balanced, the dispersion of the measured utilization will be small, resulting smaller coefficient of variation. In [41], the load balance of parallel region is defined as the ratio between average and maximum efficiency across all processors. Likely to the first metric, this ratio denotes how the load is well distributed between different processors.

Performance debugging has long been studied in distributed systems. Much work focuses on finding the causal trace, or the trace with the longest path through a distributed system; this is analogous to the slowest thread in this study. The causal trace naturally tells programmers where to focus optimization efforts. LIME shares the same goal as this work, but works in a different domain. One notable study is the performance debugging method proposed by Aguilera et al. [3]—they use a black box approach that finds the causal trace without any knowledge of the system, and a signal processing technique called convolution to infer causal relationships. LIME collects profile data without a programmer's intervention, and uses clustering and regression analysis to infer causal relations between events and load imbalance.

A number of tools exist to detect and measure parallel overheads and inefficiency (i.e., idleness). One recent example is from Tallent et al. [92]. Their goal is to pinpoint where parallel bottlenecks occur, and classify bottlenecks as overhead or idleness. Gamblin et al. [34] proposes load balance measurement framework for largescale systems. To avoid excessive overhead and perturbation associated with the system-wide measurement, they exploit wavelet analysis to compact profiled data.

This work is largely orthogonal to those tools—once a programmer knows that a problem exists, they can use this framework to help find the cause for the bottlenecks they have detected. Tallent et al. also analyzed lock contention [93]. This study shares a lot in common with LIME framework since they try to detect the cause of lock contention and identify the lock holder to blame. LIME focuses on barriers rather than locks and provides more direct information about where in the code the problem arises.

Also, many studies have tried to optimize performance and energy in the presence of load imbalance. Thrifty Barrier [60] predicts how much slack (i.e., idle time) each thread will have using a history-based predictor and save power by putting noncritical threads into a sleep state. Meeting Points [18] uses a different predictor that counts thread deviation at checkpoints called meeting points. It delays non-critical threads using dynamic voltage and frequency scaling to save power. It also attempts to accelerate the critical thread by prioritizing it.

The Thread Criticality Predictor [12] similarly predicts thread criticality based on adjusted cache miss rates, and prioritizes threads based on the prediction.

The automatic detection and prioritization of critical threads saves programmers effort, yet it only reduces load imbalance by a limited amount. Instead, LIME help programmers find and permanently fix imbalance problems in applications regardless of how severe the problems are; this can (and usually does) have a dramatic performance impact.

#### 2.2 Hardware Support for Barriers

Researchers have long acknowledged the importance of efficient barrier mechanisms in highly-parallel systems, and many past supercomputer or massively parallel multicomputer systems had dedicated fast barrier hardware. Examples include a combining omega-switch network for fast fetch-and-add (barrier counter increment) in the NYU Ultracomputer [37], a single-stage combining network [40], and a dedicated bus for test-and-set messages in Sequent systems [8], dedicated networks in CM-5 [59] and Cray T3D [24], router extensions to support a virtual barrier tree in Cray T3E [86], and "global interrupt network" wired-OR in Blue Gene/L [4]. In the chipmultiprocessor arena, the MIT Multi-ALU processor [49] has a single-cycle barrier instruction implemented using global wires (that still had single-cycle latencies at the time). These dedicated barrier networks can only support one barrier at a time, whereas future many-core systems will likely execute several (potentially many) multithreaded applications, each with its own barrier synchronization. Virtual barrier networks, such as the one in T3E, possibly bolstered with additional express links [84], are the exception to this—they can provide multiple virtual barrier trees, albeit at a cost of increased contention and latency. Beckmann and Polychronopolous [10] proposed a dedicated global interconnect for barriers that uses a register with zero-detect logic. However, the extension of this design for multiple concurrent barriers replicates much of the cost for each supported barrier, an approach that does not scale to large number of cores that may need many (ten or more) concurrent barriers. Sampson et al. introduce Barrier Filter [80], a lightweight barrier mechanism that uses cache invalidation as a barrier arrival signal and starves the cache fill until all threads arrive to the barrier. Unfortunately, the invalidation traffic to the centralized filter (which determines when all cores have arrived) can be a problem in many-core processors.

For future many-core chips, all these barrier networks also face the problem of increasing latencies for global wires. A barrier network spans the entire chip, so the wire length traversed by arrival and notification signals is expected to slowly increase as the total chip size increases, while the wire latency per unit distance quickly gets worse [43].

#### 2.2.1 Transmission Lines

With growing numbers of cores per chip and increasing wire latencies, barrier synchronization becomes increasingly challenging even with the dedicated hardware supports. This is because the signal in traditional wires changes the potential of the entire wire whose capacitance is proportional to its length. Furthermore, future technology scaling trends [43] are expected to significantly increase the delays per unit length which are already long.

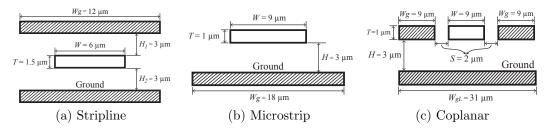

Transmission lines (TLs) have been proposed as a low-latency alternative to traditional global wires. In contrast to the traditional wire, TLs propagate signals as electromagnetic waves, at speeds that are close to the speed of light in the conductor material. This allows signals to cross the entire chip with sub-nanosecond propagation latencies, at least an order of magnitude faster than with traditional wires. This makes TLs very attractive for on-chip communication. However, TLs have several constraints that limit their usability: 1) they are more expensive than traditional wires because they are much wider (often by an order of magnitude or more) and occupy several (two or three) metal layers, 2) design of TLs requires much more modeling and planning because high frequency signals are significantly affected by the TL's shape (e.g., bends and turns) and implementation (e.g., material and thickness of the metal and insulator), 3) TLs require more sophisticated circuitry to transmit and receive their signals—instead of directly connecting logic gate inputs to a wire, TL receivers range from sense amplifiers to complete radio-frequency (RF) demodulation and decoding, depending on the type of the signal that is being used, and 4) data rates that can be achieved with relatively simple receivers (e.g., sense amplifiers) are limited.

That said, TLs will unlikely replace the entire global wires. Instead, TLs are likely to be used strategically, e.g. to provide low-latency global connections for cache banks in very large caches [9], "express" long-distance network-on-chip (NoC) links [21, 53], or as a chip-wide frequency-multiplexed bus [20].

Recently, a global network of TLs with baseband (non-modulated) signals has been proposed for barrier synchronization [1]. This hardware barrier has a lower latency than one built out of traditional wires. However, this scheme can still support only one barrier group at a time. Considering the large cost of TLs, it is unlikely that future chips will include multiple such global networks in order to support multiple barriers.

#### 2.3 On-chip Network: Topologies and Latencies

Ever since more than one core is packed in one chip, various types of networks have been proposed for on-chip interconnects. Generally, the networks can be classified into three categories: unswitched (typically bus-based), packet-switched, and hybrid interconnects that exploit both. Unswitched interconnects broadcast all traffic on a shared medium, allowing simpler design than switched interconnects. However, as the number of cores and connections increases, the resulting contention becomes a major performance issue [38, 62]. Traditional buses also suffer from unfavorable wire delay and power trend as technology scales [32, 44, 90, 98].

In contrast, a packet-switched network typically employs short links between adjacent cores, which is efficient and has low-latency for local traffic. However, packets traveling to far-apart destinations have to go through many such links and on-chip routers. These routers are typically pipelined, which improves throughput, but further increases per-hop latency. This latency is somewhat alleviated by techniques such as lookahead routing [33], where routing calculation is performed one hop ahead to shorten the router's pipeline, or aggressive speculation [68] which also reduces pipeline length by speculatively performing switch allocation early. However, even with these advanced router microarchitectures, each traversed node still adds several cycles to the latency of a packet.

Hop count can be reduced by more advanced network topology. In a concentrated mesh [7], several nodes share each router, so fewer routing hops are necessary than the ones in a traditional mesh. In a flattened butterfly [50], hop count is reduced by providing richer physical connectivity to non-adjacent nodes. However, even with these efforts, growing core counts still lead to increase hop counts and wire latency, causing latencies of tens of cycles between far-apart cores.

The per-hop routing delays can be eliminated either by using a separate link for each pair of cores, which is extremely expensive for a large number of cores, or by using an unswitched interconnect. Unfortunately, as noted earlier, traditional unswitched interconnects (buses) suffer from both contention and poor scaling trends.

#### 2.3.1 On-chip Transmission Lines

The latency and energy problems of wires in unswitched interconnects can be addressed with transmission lines (Section 2.2.1). For the specific TL-based design I use (Section 6.2.1), electromagnetic simulations show 7.5 ps/mm propagation speed, compared to ITRS projections [44] of 140 ps/mm for optimally repeated wires in 22 nm, and 150 ps/mm in 10 nm technology. However, TLs do not address the throughput problem of unswitched interconnects—in fact, they make it worse because the metal area occupied by a single TL is equivalent to tens of wires. Thus, a TL-based interconnect tends to have less throughput than the same-cost wire-based one.

#### 2.3.2 Hybrid Interconnect and Steering

In contrast to my approach, where both networks are fully capable of delivering any message from its source to its destination, most prior work with multiple networks uses them hierarchically. Bourdaus [17] proposes hierarchical rings connecting local meshes to reduce global hop count. Local buses with global meshes are another hierarchical interconnect [27, 94] that can improve latency and power efficiency through communication locality. However, these hybrid proposals still incur significant routing delays for cross-chip packets in many-core processors, and growing wire delays are still a problem. In contrast, my approach combines a (traditional or advanced) switched NoC with a low-cost UTL ring that provides extremely low latency for selected (e.g. cross-chip) packets.

Other approaches to improve latency of many-core interconnect include attempts to hierarchically split chip-spanning bus into multiple local buses connected with point-to-point links [56]. Filtering broadcasts between segmented global and local buses further improves bus throughput [95] and the use of hierarchical (local and global) rings shows performance close to the packet-switched interconnect with improved scalability [32]. However, these interconnects still show strain in high-traffic applications, so they may only delay the transition to more scalable switched interconnects. In contrast, I embrace the transition to more scalable NoCs, but add TL ring to provide extremely low latency when needed. Furthermore, advances in scalable switched interconnects in terms of latency [39, 54] and power efficiency [31] may still result in significant latency differences depending on hop count.

Ring interconnects have been widely used in many systems for its simplicity with trivial routers and manageable latency with short point-to-point wires. IBM Power5 [89] and IBM Cell Architecture [47] exploits ring structure to connect multiple on-chip computing units with ring. Similarly, my approach with Transmission Line adopts ring structure to ease the implementation with simple architecture. However, unlike the traditional ring structure, TL ring allows seamless signal propagation with novel couplers and pass-gates. When a pass-gate is in connected states, no delay is incurred to relay the signal. Using this, the ring can form a fast chain that starts and ends at the sending node. The coupler works like a ring resonator in nanophotonic interconnects [97] and allows every node on the chain to observe and relay the transmitted signal at the same time.

Steering messages in heterogeneous networks was explored in [22]. The heterogeneous network implements multiple interconnects with different characteristics in latency, bandwidth and power-efficiency by adjusting wire and repeater spacing. Then, coherence traffic is optimized to steer messages into different networks according to their properties (criticality, size, etc.). In contrast to steering between NoCs that are similar in nature, my approach steers between NoCs with very different latency, throughput and latency/hop characteristics.

Transmission lines (TLs) have been used for fast communications, e.g. low-latency barriers [1, 73], long-distance "express" links [21, 53] and connections between distant banks in large caches [9]. Shared-medium broadcast TL interconnects in [20] use optimizations to reduce on-chip traffic. While these optimizations defer the scalability problem, growth in core counts still inevitably leads to saturation of broadcast-type interconnects. In contrast, I rely on a switched network to provide throughput scaling, and use TL ring only for packets that benefit the most from it.

Alternative emerging approaches for low-latency interconnection include nanophotonics [23, 51, 76, 97] and on-chip wireless communications [35]. Nanophotonic NoCs can address the power and latency problem of the traditional NoC, though they require further investigation in their suitability to replace existing metal-based NoC architecture [101]. The application of TL to augment the existing NoCs differ with their approach in that I exploit already mature technologies and can ease the burden of installation. Hybrid wireless NoC expedites long-range communication but requires routing scheme and communication protocol that consume power and area overhead. Also, it has to overcome reliability and integration challenges.

Finally, a recent proposal describes a NoC composed of TL buses, with various optimizations to increase throughput [19]. However, such all-TL approaches increase throughput by using more TLs, complex encoding/decoding to embed more bits in the signal, and/or signaling at extremely high frequencies. My work is based on the insight that TLs provide little benefit for a large portion of the traffic (e.g. local traffic). That leads us to a low-cost approach of minimizing the total TL length and using binary pulse signaling at frequencies for which the required circuitry has already been demonstrated in existing CMOS technology [16, 74]. I then use the UTL ring to provide low latency for packets that can benefit from it while relying on a traditional scalable NoC for throughput requirement.

## CHAPTER III

# A FRAMEWORK FOR DEBUGGING LOAD IMBALANCE

#### 3.1 Overview of LIME

In this chapter, I present LIME, a framework for debugging Load Imbalance for Multithreaded Executions. This framework utilizes statistical analysis in conjunction with control flow graph analysis on profiled data to *automatically* determine the nature of load imbalance problems and pinpoint the code where the problems are introduced.

To help explain LIME framework and the scalability limiter it addresses, I use the code example in Figure 1. This is an actual parallel section from SPLASH-2's *radix* benchmark [99]. The SPLASH-2 benchmark suite was extensively optimized over a decade ago by experts in both parallel programming and multi-processor hardware, and has been used to evaluate parallel performance of multi-processor and multi-core machines ever since.

This parallel section begins and ends with barriers, where each thread waits for all others to arrive before proceeding further. Any load imbalance will result in threads arriving at the end barrier (line 598) at different times, forcing early-arriving threads to wait (i.e., be idle) until the longest-running thread arrives.

Within the parallel section, each thread uses its private *MyNum* and *offset* values to decide which part of the parallel computation it should perform. Depending of these values, the threads may have different execution times, either by executing different code (due to differences in control flow) or by taking different amounts of time to execute the same code (due to differences in how the executed code interacts with

```

534

BARRIER(...);

535

if (MyNum != (...)) {

540

while ((offset & 0x1) != 0) { ... }

while ((offset & 0x1) != 0) { ... }

549

557

for (i = 0; i < radix; i++) \{ ... \}

560

} else {

562

}

566

while ((offset & 0x1) != 0) { offset=... }

575

for(i = 0; i < radix; i++) { ... }

578

while (offset != 0) {

579

if ((offset & 0x1) != 0) {

582

for (i = 0; i < radix; i++) \{ ... \}

585

}

589

}

590

for (i = 1; i < radix; i++) \{ ... \}

594

if ((MyNum == 0) || (stats)) \{ ... \}

598

BARRIER(...);

```

**Figure 1:** Code for sample parallel section from *radix*. All non-control-flow statements are removed.

the hardware). In Figure 1, there are several examples of possible control flow differences: if-then-else blocks at lines 535, 579, and 594 may cause only a subset of threads to execute the if-path (and for line 560, other threads to execute the else-path); loops at lines 540, 549, 557, 575, 578, 582, and 590 could all execute a different number of iterations for different threads. Nesting of loops and conditionals (e.g., line 582) can compound these differences. Additionally, threads may have differences in interacting with the system, such as branch predictor performance (some threads might have more predictable branch decision patterns than others) or cache performance (e.g., threads that access data already in the cache may have more cache hits). These differences are too numerous to point out even in this small example code because every branch, jump, load, store, etc. instruction in the compiled code may be, at least in theory, a potential source of these performance differences.

It may seem that a trained programmer can inspect the source code to identify potential causes of imbalance and repair them. However, this is a very labor-intensive and error-prone endeavor because of the sheer number of potential causes, and because

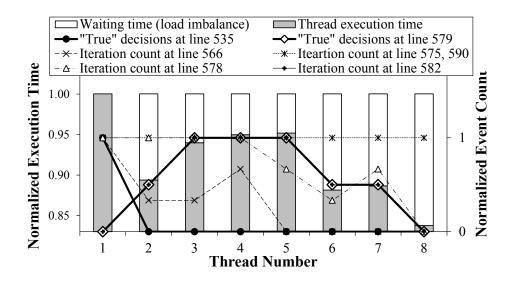

**Figure 2:** Execution time, imbalance, and thread behavior of key points in Figure 1. Points that cause load imbalance are shown with thicker lines.

of the complexity of understanding each cause and determining whether or not each is responsible for imbalance (and then repairing those that are).

An actual example of the threads' execution times for one dynamic instance of this parallel section is shown in Figure 2. The shaded part of each bar represents the useful execution time of each thread, normalized to the overall execution time of the parallel section. The white part of each bar represents the thread's waiting time at the end of the parallel section (line 598). Due to this waiting time, we have load imbalance of 0.051 according to our first definition in Section 2.1 (coefficient of variation, CoV) and 0.918 in second definition (ratio between average and maximum execution time). Note that the load imbalance shrinks as CoV decreases as well as the ratio increases.

Here, the discussion of possible causes of imbalance included two types of control flow causes—iteration counts of loops and decision counts of if-then-else blocks. These event counts are also shown in Figure 2, with each event's counts normalized to the maximum count for that event among all threads. From visual inspection of the graph, the decision at line 535 appears to cause imbalance between the first thread and the others. The differences in "true" decisions at line 579 appears to account for the remaining imbalance (note how well the useful execution time tracks this factor for threads 2 through 8). The loops at lines 575 and 590 have identical iteration counts in all threads, and thus cannot be causing any imbalance—code inspection reveals the same insight, because the value of *radix* is constant and the same for all threads. The loops at lines 566 and 578 do produce different iteration counts in different threads but this does not seem to correspond to actual imbalance. Finally, loop iteration counts at lines 540, 549, and 557 (not shown) have the same relationship with the imbalance that decision count at line 535 has, and loop iteration count at line 582 has the same behavior as the decision count for line 579.

LIME framework performs this kind of analysis automatically and quantitatively. For each thread in each parallel section, LIME measures execution time and various *event counts*. The event counts are dynamic decision counts for all static control flow decision points (control flow events), as well as dynamic counts for each static code location that causes machine-interaction events<sup>1</sup> (hardware events). Using this data, LIME's analysis framework determines how much imbalance exists, which control flow decisions and machine interaction events are related to the imbalance, and assigns scores that help programmers decide which cause of the imbalance to "attack" first.

The initial implementation of LIME includes two different profiling environments. The first implementation uses a cycle-accurate hardware simulator called SESC [79] that can be relatively easily extended to collect any desired machine-interaction event count; however, since it performs detailed simulation of a computer system, it is very slow and can only be used for parallel sections that execute quickly (e.g., with carefully designed small input sets). To overcome the speed limit, I implemented LIME with Pin [63], which is fast but can only accurately collect data for analysis of control

<sup>&</sup>lt;sup>1</sup>Among machine-interaction events, I only experimented with cache misses because I expected them to be the only machine-interaction event that plays a significant role in creating load imbalance. As will be shown in Section 3.4.4, this turned out to not always be true. However, LIME's analysis treats all hardware events in the same way and I expect it to readily extend to other events (as long as they can be counted efficiently).

flow causes of imbalance. The simulator-based implementation was designed to let us experiment with collecting different events, and the Pin-based one to let us test LIME on larger input sets. For practical use, a purpose-built profiler could be employed to collect control flow events and key hardware performance counters more efficiently.

The analysis part of the framework processes profiling data from either profiling environment. It first clusters together events whose counts are highly correlated to each other. The purpose of this step is to group together events that seem to be related to the same potential cause of imbalance. For example, this step puts the decision count from line 535 and the iteration counts from lines 540, 549, and 557 in the same cluster because they are linearly related to each other (they have zero counts in all threads but one, so one of these event counts is equal to a constant times the execution count of another). Similarly, the iteration count from line 582 and the number of cache misses at lines 580–585 are in the same cluster as the "true" decision count from line 579 (this would not be true if threads had differing cache miss rates for lines 580–585).

Next, LIME finds the "leader" of each cluster. The purpose of this step is to identify the event that corresponds to "introducing" a potential cause of imbalance. In the two example clusters, the "true" decision counts from lines 535 and 579 are found to be the leaders of their respective clusters.

The next step in LIME uses multiple regression to find which cluster leaders are related to the imbalance in a statistically significant way, and to find the strength of that relationship. In this example, the "true" decision counts from lines 535 and 579 are the only cluster leaders to have a statistically significant relation to the load imbalance.

Finally, LIME ranks and reports the cluster leaders that are related to the imbalance. The report includes the score, the location in the code, and the corresponding cause of imbalance. In the example, LIME reports only two causes, both with relatively high scores: (1) threads take different paths at line 535, and (2) threads have different biases ("true" vs. "false" decision) for the if-then-else at line 579.

The following section provides a detailed description of the analysis framework. Subsequent sections describe the two profiling implementations, and an experimental evaluation of LIME's accuracy with examples that provide more intuition about how LIME works and how its results can be used by the programmer to reduce load imbalance.

# 3.2 LIME Analysis Framework

LIME's analysis starts with data gathered by one of the profiling implementations (see Section 3.3). The profiling data consists of 1) per-thread control flow event counts for each edge in the static control flow graph and 2) per-thread hardware event counts for each static instruction that can cause such an event.

### 3.2.1 Causality Analysis for Hardware Events

Before entering the main analysis routine, LIME conducts preprocessing on collected hardware events in order to establish causal relationships between related events. For example, an L1 cache miss can occur only when a memory access instruction is executed, an L2 cache miss can occur only when an L1 cache miss happens, etc. If the dynamic count for a particular hardware event differs among threads, this hierarchy among events allows us to split the "blame" for the difference between that event itself and the events that must precede it. For instance, when threads have different numbers of L1 misses at a particular static instruction, this may due to some threads executing that instruction more times (and thus having more L1 miss opportunities) or due to how the application interacts with the L1 cache. In the preprocessing step, LIME removes from subordinate hardware events (e.g. L1 misses) the contribution from their "superior" events (e.g. instruction's execution count) using the Gram-Schmidt process [36], leaving each event count only with the event's own contribution to variations among threads. This adjusted hardware event count is used instead of the naïve one throughout the LIME analysis.

### 3.2.2 Hierarchical Clustering

The second step in the LIME analysis is to cluster related events together. There are two commonly used clustering algorithms: hierarchical clustering and K-means clustering [45]. I use hierarchical clustering because it can automatically find an appropriate number of clusters for a given separation principle (clustering threshold) between clusters, whereas K-means yields a predetermined number of clusters. For the same reason, many projects on workload characterization [14, 48, 78] rely on hierarchical clustering to find benchmarks that have similar behavior.

Hierarchical clustering is performed in steps. Each step merges the two clusters that are "closest" according to a distance metric. Clustering ends when the distance between the two closest clusters is larger than a preset threshold.

In LIME, each event (control flow event or hardware event) is initially a cluster. I then compute a proximity matrix in which an element (i, j) represents the distance between 'cluster *i*' and 'cluster *j*'. At each step, I merge the two closest clusters and update the proximity matrix accordingly. The distance metric LIME uses is Pearson's correlation between the event's per-thread counts, because it effectively captures similarity in how the event count behaves in different threads. For linkage criteria, I used average linkage (UPGMA [70]), but other methods (single/completelinkage) produced similar results.

LIME stops clustering when the largest correlation is <0.9. This threshold value provides the best results in most parallel sections I tested. The exceptions are *fmm* and *fluidanimate*, where I used threshold values of 0.8 and 0.6, respectively. A poorly chosen threshold affects the usefulness of the report—too-high of a threshold prevents merging of correlated event clusters, while too-low of a threshold results in clusters that contain unrelated events.

Clustering provides several benefits for further analysis:

- It results in a major reduction in the number of subjects for further analysis.

- It gathers highly co-linear events into one cluster, which improves accuracy of regression<sup>2</sup> in Section 3.2.5.

- It helps identify significant decision points in the program structure (e.g., branches where control flow differs between threads), as I explain in Section 3.2.4.

#### **3.2.3** Classification of Clusters

Clusters are classified into two types: those that contain control flow events (controlflow clusters), and those with only hardware events (hardware event clusters).

For hardware event clusters, the absence of highly correlated control flow events indicates that different threads suffer the hardware events differently for the same code. Therefore, if any load imbalance is eventually attributed to the cluster, all the hardware events in the cluster are reported as contributing to that portion of the imbalance.

#### 3.2.4 Finding Cluster Leaders

Within a control-flow cluster, control flow events are typically interdependent. To improve the usefulness of reported results, for each cluster, LIME discovers a *leader* node—a control flow instruction that steers program execution into the cluster. Intuitively, if the cluster is related to the imbalance, the leader node represents the code point where this imbalance is introduced.

<sup>&</sup>lt;sup>2</sup>Statistical regression works poorly with collinear vectors.

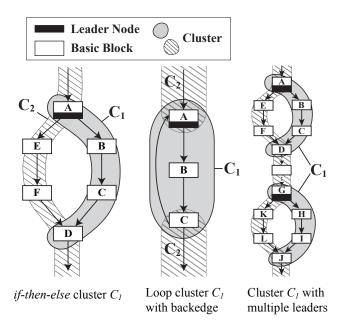

Figure 3: Example of clusters and leader nodes

Leader nodes are important because they are the decision points that change thread execution characteristics. They are the points in the program of most interest to the programmer: by inspecting the code that affects the leader node's decision, the programmer can typically find the high-level reason for the imbalance.

To formally define a leader node, assume a control flow graph of a program has vertices V and edges E. The leader node of a cluster C is a vertex v in the control flow graph such that all incoming edges to v except backedges have source vertices outside the cluster, i.e.,  $v \in C$  such that  $\forall (s, v) \in E, s \notin C$ .

Examples of typical clusters and their leader nodes are shown in Figure 3. The leftmost example shows a cluster whose leader is an *if*-statement. The middle example shows why a backedge restriction is needed in the leader definition—it allows a loop cluster to have a leader (the loop entry point). The rightmost example shows a cluster with two leaders (A and G)—this typically occurs when the same control flow decision is made in more than one code point.

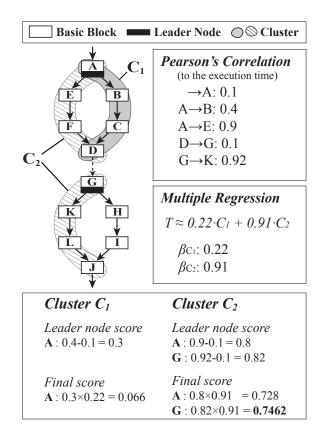

After finding leader nodes for each cluster, each leader node is assigned a score according to its significance in creating load imbalance. First, LIME computes, for each edge, the Pearson's correlation coefficient between that edge and the execution time. The score of a leader node is the *difference* in this correlation between the node's incoming and outgoing edges (again, ignoring backedges). For example, if nthreads have execution times  $T = (t_1, t_2, \dots, t_n)$  and a leader node v has incoming edge counts  $ie_{v_1}, ie_{v_2}, \dots, ie_{v_i}$ , and outgoing edge counts  $oe_{v_1}, oe_{v_2}, \dots, oe_{v_j}$ , the score  $s_v$  of the leader node v is

$$s_v = \max_x \left( corr\left( oe_{v_x}, T \right) \right) - \max_y \left( corr\left( ie_{v_y}, T \right) \right) \tag{1}$$

where corr(a, b) is the Pearson's correlation coefficient between vectors a and b.