# SOFTWARE-ORIENTED DATA ACCESS CHARACTERIZATION FOR CHIP MULTIPROCESSOR ARCHITECTURE OPTIMIZATIONS

by

## Yong Li

B.S. Telecommunication Engineering, Chongqing University, 2005M.S. Computer Engineering, University of Pittsburgh, 2010

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

University of Pittsburgh

2013

## UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Yong Li

It was defended on

Oct. 29th 2013

and approved by

Alex K. Jones, Ph.D., Associate Professor, Department of Electrical and Computer Engineering Rami Melhem, Ph.D., Professor, Department of Computer Science

Hai Li, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Yiran Chen, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Zhihong Mao, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Dissertation Advisors: Alex K. Jones, Ph.D., Associate Professor, Department of Electrical and

Computer Engineering,

Co-Advisor, Rami Melhem, Ph.D., Professor, Department of Computer Science

## SOFTWARE-ORIENTED DATA ACCESS CHARACTERIZATION FOR CHIP MULTIPROCESSOR ARCHITECTURE OPTIMIZATIONS

Yong Li, PhD

University of Pittsburgh, 2013

The integration of an increasing amount of on-chip hardware in Chip-Multiprocessors (CMPs) poses a challenge of efficiently utilizing the on-chip resources to maximize performance. Prior research proposals largely rely on additional hardware support to achieve desirable tradeoffs. However, these purely hardware-oriented mechanisms typically result in more generic but less efficient approaches. A new trend is designing adaptive systems by exploiting and leveraging applicationlevel information. In this work a wide range of applications are analyzed and remarkable data access behaviors/patterns are recognized to be useful for architectural and system optimizations. In particular, this dissertation work introduces software-based techniques that can be used to extract data access characteristics for cross-layer optimizations on performance and scalability. The collected information is utilized to guide cache data placement, network configuration, coherence operations, address translation, memory configuration, etc. In particular, an approach is proposed to classify data blocks into different categories to optimize an on-chip coherent cache organization. For applications with compile-time deterministic data access localities, a compiler technique is proposed to determine data partitions that guide the last level cache data placement and communication patterns for network configuration. A page-level data classification is also demonstrated to improve address translation performance. The successful utilization of data access characteristics on traditional CMP architectures demonstrates that the proposed approach is promising and generic and can be potentially applied to future CMP architectures with emerging technologies such as the Spin-transfer torque RAM (STT-RAM).

## TABLE OF CONTENTS

| PRI | PREFACE xiv                                          |    |

|-----|------------------------------------------------------|----|

| 1.0 | INTRODUCTION                                         | 1  |

|     | 1.1 CMP Challenges                                   | 1  |

|     | 1.1.1 Architecture Scaling                           | 2  |

|     | 1.1.2 Technology Challenges                          | 2  |

|     | 1.2 Proposed Solutions                               | 3  |

|     | 1.3 Background and Context                           | 5  |

|     | 1.4 Contributions                                    | 7  |

|     | 1.5 Overview                                         | 9  |

| 2.0 | RELATED WORK                                         | 10 |

|     | 2.1 Compiler Optimizations                           | 10 |

|     | 2.2 CMP Enhancements                                 | 12 |

|     | 2.2.1 Coherent Caches                                | 13 |

|     | 2.2.2 Network-on-chip                                | 14 |

|     | 2.2.3 Address Translation and TLBs                   | 15 |

|     | 2.2.4 Application-aware Optimizations                | 15 |

|     | 2.3 Emerging Memories in CMPs                        | 17 |

| 3.0 | COMPILER ANALYSES FOR DATA CLASSIFICATION            | 19 |

|     | 3.1 Basic Analyzing Approaches                       | 20 |

|     | 3.2 Data Classification                              | 21 |

|     | 3.2.1 Motivation: The Concept of Practically Private | 21 |

|     | 3.3 Data Classification Detection                    | 24 |

|     | 3.3.1 Thread-Identifying Variables                              | 26 |

|-----|-----------------------------------------------------------------|----|

|     | 3.3.2 Programs with Dynamic Parallelism                         | 29 |

|     | 3.3.3 Data Classification for Other Parallel Programming Models | 31 |

|     | 3.3.4 Data Classification Algorithm                             | 32 |

|     | 3.4 Evaluation                                                  | 34 |

|     | 3.4.1 Compiler-based Data Classification                        | 35 |

| 4.0 | DATA CLASSIFICATION AWARE CACHE ARCHITECTURE                    | 38 |

|     | 4.1 Customized Memory Allocator                                 | 38 |

|     | 4.2 Data Classification Aware Caching                           | 39 |

|     | 4.2.1 Classification Aware Coherence Protocol                   | 41 |

|     | 4.2.2 Addressing False Sharing for Private Data                 | 44 |

|     | 4.3 Evaluation                                                  | 45 |

|     | 4.3.1 Effect on Coherence Traffic                               | 47 |

|     | 4.3.2 Performance Evaluation                                    | 47 |

|     | 4.3.2.1 Miss Rate                                               | 47 |

|     | 4.3.2.2 Latency                                                 | 48 |

|     | 4.3.2.3 Performance Improvement                                 | 50 |

| 5.0 | TLB OPTIMIZATION USING DATA CLASSIFICATION                      | 52 |

|     | 5.1 Motivation                                                  | 54 |

|     | 5.2 Background and Context                                      | 56 |

|     | 5.2.1 Background                                                | 56 |

|     | 5.2.1.1 Address Translation Architecture                        | 57 |

|     | 5.2.1.2 Address Translation Basics                              | 57 |

|     | 5.2.1.3 Address Translation Consistency                         | 58 |

|     | 5.2.2 Comparison with Prior TLB Proposals                       | 58 |

|     | 5.3 Partial Sharing TLB                                         | 60 |

|     | 5.3.1 Sharing TLB Entries                                       | 61 |

|     |                                                                 | 62 |

|     | 5.3.2.1 Translation/Page Classification Support                 | 63 |

|     | 5.3.3 Basic Translation Operations on PS-TLB                    | 64 |

|     |                                                                 |    |

|     |           | 5.3.3.1 Parallel Translation Lookup                     | 64 |

|-----|-----------|---------------------------------------------------------|----|

|     |           | 5.3.3.2 Translation Classification Aware Fill/Placement | 65 |

|     | 5.3.4     | Optimized TLB Shootdown                                 | 65 |

|     | 5.3.5     | Optimized TLB Flush                                     | 67 |

|     | 5.3.6     | Atomicity and Race Conditions                           | 67 |

|     | 5.3.7     | Discussion                                              | 68 |

|     |           | 5.3.7.1 Scalability                                     | 68 |

|     |           | 5.3.7.2 Multi-program Workloads                         | 68 |

|     |           | 5.3.7.3 Thread Migration                                | 68 |

|     | 5.4 Evalu | ation                                                   | 69 |

|     | 5.4.1     | Impact of Classification Mechanisms                     | 70 |

|     | 5.4.2     | Comparison with Shared TLB                              | 72 |

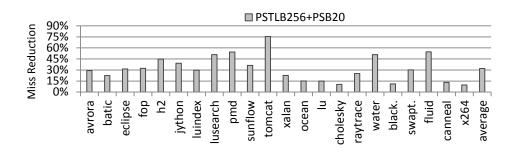

|     |           | 5.4.2.1 Translation Miss Rate                           | 72 |

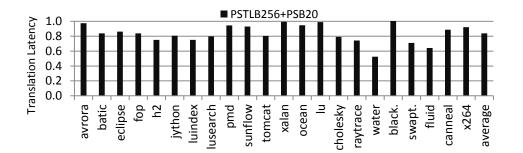

|     |           | 5.4.2.2 Translation Latency                             | 73 |

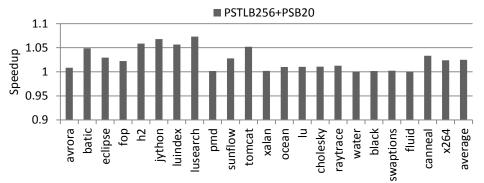

|     |           | 5.4.2.3 Overall Performance Impact                      | 73 |

|     | 5.4.3     | Comparing with Prefetching Mechanism                    | 74 |

|     | 5.4.4     | Sensitivity Analyses                                    | 76 |

|     | 5.4.5     | Additional Benefits from PS-TLB                         | 78 |

|     |           | 5.4.5.1 Shootdown                                       | 79 |

|     |           | 5.4.5.2 Context Switching                               | 79 |

| 6.0 | COMPII    | LER-BASED DATA PARTITIONING AND COMMUNICATION PAT-      |    |

|     | TERN A    | NALYSES OF PRACTICALLY PRIVATE DATA                     | 81 |

|     | 6.1 Over  | view                                                    | 82 |

|     | 6.2 Multi | i-threaded Memory Access Pattern Analysis               | 83 |

|     | 6.2.1     | Array Access Regions                                    | 83 |

|     | 6.2.2     | Multi-threaded Array Analysis                           | 84 |

|     |           | 6.2.2.1 Thread-Identifying Structures                   | 84 |

|     |           | 6.2.2.2 Multi-threaded Memory Access Patterns           | 86 |

|     | 6.2.3     | MMAP generation                                         | 87 |

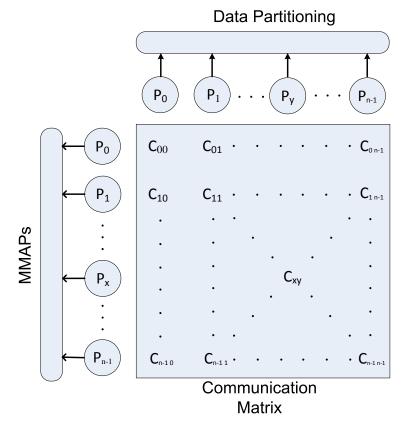

|     | 6.3 Gene  | rating Data Partitioning and Communication Pattern      | 90 |

|     | 6.3.1 Data Partitioning                                  |

|-----|----------------------------------------------------------|

|     | 6.3.2 Granularity of Data Ownership                      |

|     | 6.3.3 Calculating Communication Patterns                 |

|     | 6.4 Evaluation                                           |

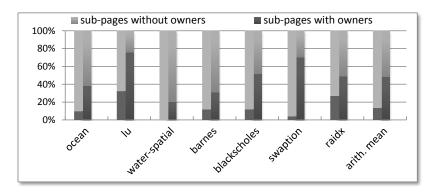

|     | 6.4.1 Capability in Discovering Ownership                |

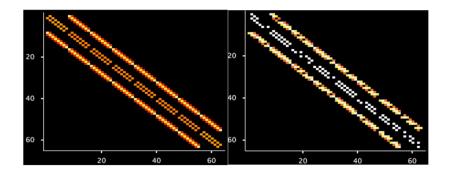

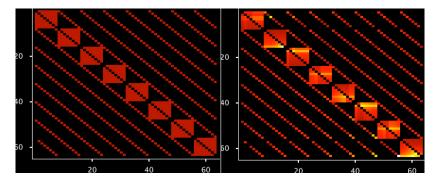

|     | 6.4.2 Compiler Communication Pattern Accuracy            |

| 7.0 | UTILIZING COMPILER DETERMINED DATA PARTITIONING AND COM- |

|     | MUNICATION PATTERN IN CMPS                               |

|     | 7.1 Related Work                                         |

|     | 7.1.1 Relevant Runtime Cache Enhancements                |

|     | 7.1.2 Relevant Reconfigurable Networks                   |

|     | 7.2 System Support                                       |

|     | 7.3 Evaluation                                           |

|     | 7.3.1 Simulation Environment                             |

|     | 7.3.2 Compiler-Assisted Partitioning Performance         |

|     | 7.3.2.1 Impact on Cache Performance                      |

|     | 7.3.2.2 Overall Performance                              |

|     | 7.3.2.3 Impact of Partition Granularity                  |

|     | 7.3.3 Impact of Compiler Assisted Network Configuration  |

| 8.0 | <b>OPTIMIZING STT-RAM CACHES</b>                         |

|     | 8.1 STT-RAM Technology Trends and Design                 |

|     | 8.1.1 Write Optimizations                                |

|     | 8.1.2 Read Optimization Using Differential Sensing       |

|     | 8.2 Compiler Data Reuse Analysis                         |

|     | 8.2.1 Data Reuse Analysis for Arrays                     |

|     | 8.2.1.1 Basic Data Reuse Analysis                        |

|     | 8.2.1.2 Consecutive Read (CR) Analysis                   |

|     | 8.2.1.3 CTR Analysis                                     |

|     | 8.2.1.4 CSR Analysis                                     |

|     | 8.2.2 Data Reuse Analysis for Linked Structures          |

|     |                                                          |

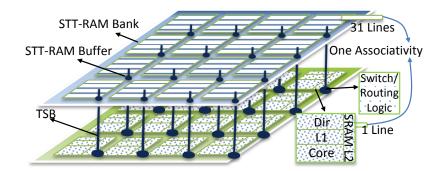

| 8.3 Hybrid SRAM/STT-RAM Cache Design             |

|--------------------------------------------------|

| 8.3.1 3-D Stacked Architecture with Hybrid Cache |

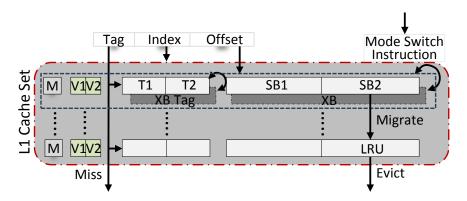

| 8.4 Dual-mode Cache Design                       |

| 8.4.1 C1C Architecture                           |

| 8.4.2 Design Considerations                      |

| 8.5 Evaluation                                   |

| 8.5.1 Hybrid Cache Evaluation                    |

| 8.5.1.1 Performance and Power Evaluation         |

| 8.5.2 C1C Evaluation                             |

| 8.5.2.1 Effectiveness of the Threshold Analysis  |

| 8.5.2.2 Performance and Power Evaluation         |

| <b>9.0 CONCLUSION AND FUTURE WORK</b>            |

| <b>BIBLIOGRAPHY</b>                              |

### LIST OF TABLES

| 1  | Benchmarks                                                                                                                                                                           |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | Architecture configurations                                                                                                                                                          |

| 3  | Benchmarks                                                                                                                                                                           |

| 4  | Architecture configurations                                                                                                                                                          |

| 5  | Benchmarks                                                                                                                                                                           |

| 6  | Benchmark description                                                                                                                                                                |

| 7  | Peripheral circuitry and read latency for two L1 cache examples at 22nm technology 114                                                                                               |

| 8  | Hybrid cache architecture configurations                                                                                                                                             |

| 9  | Benchmarks                                                                                                                                                                           |

| 10 | Overheads for ocean with different $T$ values $\ldots \ldots \ldots$ |

| 11 | C1C architectural parameters (The read/write latency for LLC shown in this table                                                                                                     |

|    | is the raw access time excluding the network traversal latency)                                                                                                                      |

## LIST OF FIGURES

| 1  | Overview of compiler- and OS-oriented architecture optimizations                      | 4  |

|----|---------------------------------------------------------------------------------------|----|

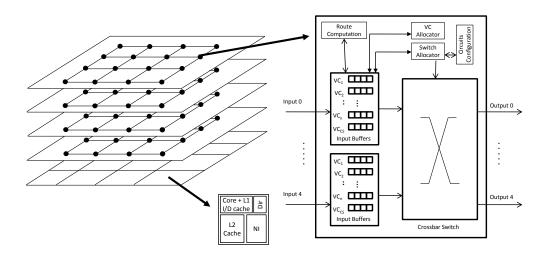

| 2  | Scalable chip multiprocessor architecture                                             | 5  |

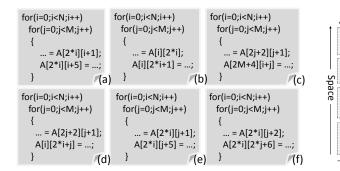

| 3  | Serial and parallel computation for matrix multiplication                             | 22 |

| 4  | Different scenarios for practically private data                                      | 24 |

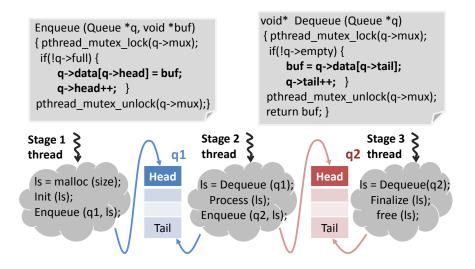

| 5  | Pointer analysis example for data classification                                      | 26 |

| 6  | Detecting TI variable passed as parameters                                            | 27 |

| 7  | Detecting TI variable by directives                                                   | 27 |

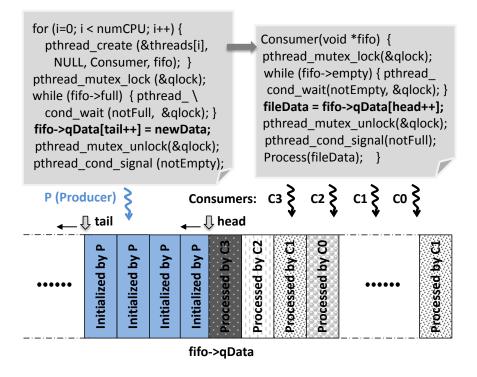

| 8  | Practically private data in a program applying the producer-consumer parallel model   | 30 |

| 9  | Practically private data in a program applying the pipeline parallel model            | 31 |

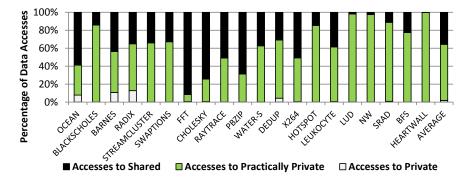

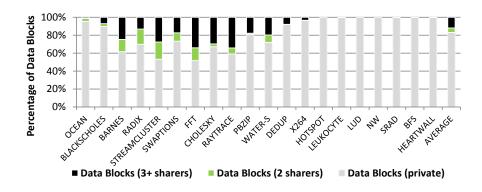

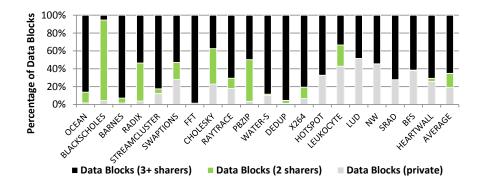

| 10 | Percentage of accesses classified by the compiler as shared, practically private, and |    |

|    | private                                                                               | 35 |

| 11 | Percentages of data blocks classified as practically private that are accessed by one |    |

|    | core (private), two cores, or three or more cores                                     | 36 |

| 12 | Percentages of accesses to the data blocks classified as practically private that are |    |

|    | accessed by one core (private), two cores, or three or more cores                     | 36 |

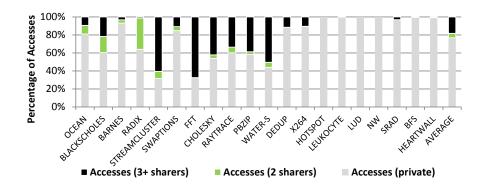

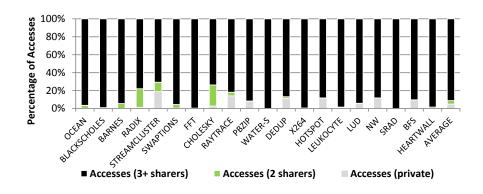

| 13 | Percentages of data blocks classified as shared that are accessed by one core (pri-   |    |

|    | vate), two cores, or three or more cores                                              | 37 |

| 14 | Percentages of accesses to the data blocks classified as shared that are accessed by  |    |

|    | one core (private), two cores, or three or more cores                                 | 37 |

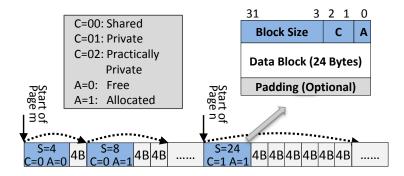

| 15 | Data blocks maintained by the memory allocator                                        | 39 |

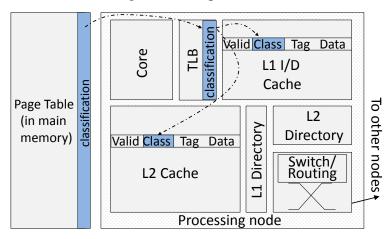

| 16 | Architecture organization for data classification aware caching                       | 40 |

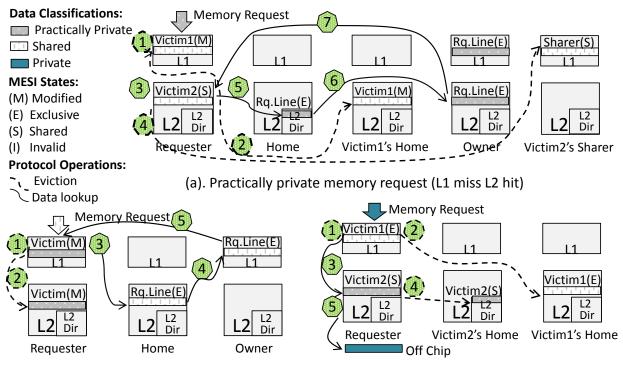

| 17 | Examples of data flow and the coherence protocol for different data classifications . | 42 |

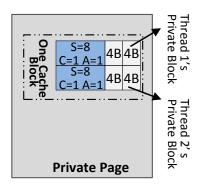

| 18 | False sharing in a private page                                                        | 44 |

|----|----------------------------------------------------------------------------------------|----|

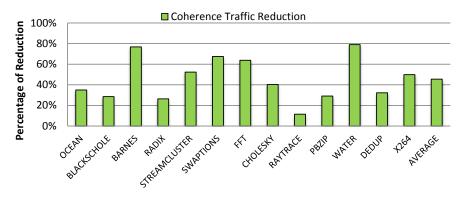

| 19 | Percentage of coherence traffic reduced compared to private caches                     | 47 |

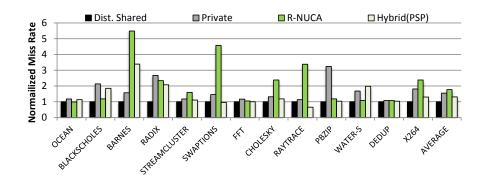

| 20 | Miss rate for the shared-averse configuration                                          | 48 |

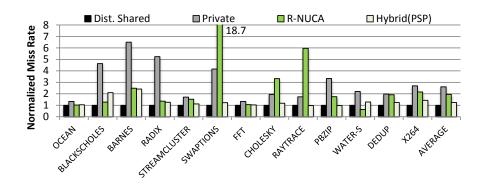

| 21 | Miss rate for the private-averse configuration                                         | 48 |

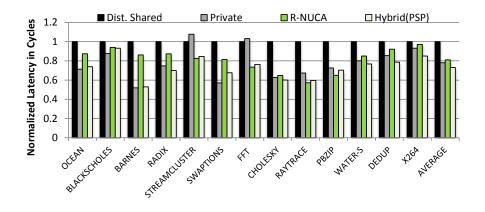

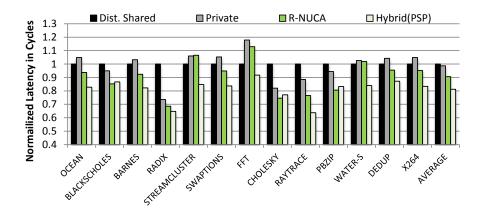

| 22 | Average memory access latency for the shared-averse configuration                      | 49 |

| 23 | Average memory access latency for the private-averse configuration                     | 49 |

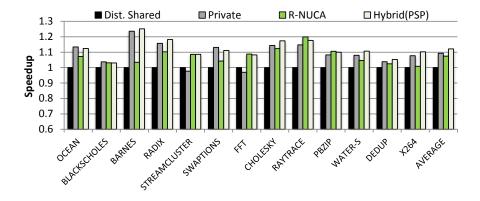

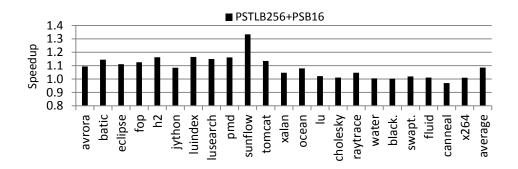

| 24 | Application speedup for the shared-averse configuration                                | 51 |

| 25 | Application speedup for the private-averse configuration                               | 51 |

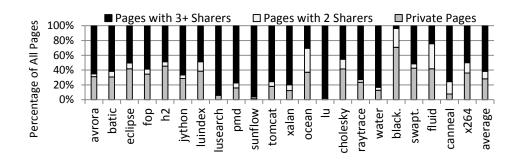

| 26 | Application page sharing characteristics                                               | 54 |

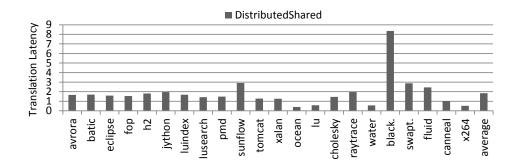

| 27 | Translation latency for a L2 TLB using a non-uniform access shared TLB model           |    |

|    | compared with a centralized shared approach for 16 cores (normalized to central-       |    |

|    | ized shared)                                                                           | 55 |

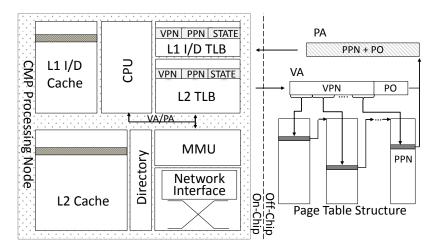

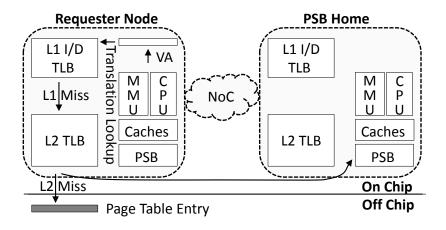

| 28 | Baseline architecture with 2-level TLB translation and a hierarchical page table       | 57 |

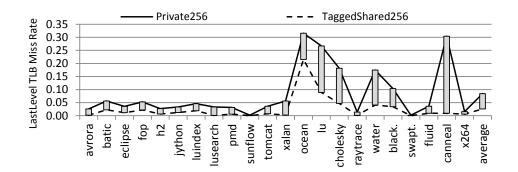

| 29 | Last level TLB miss rate for private vs tagged shared TLB with 256 TLB entries/core    | 61 |

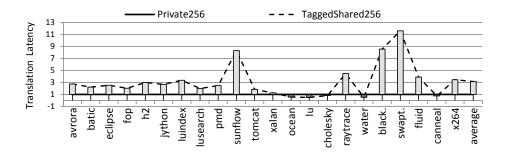

| 30 | Latency for private vs tagged shared TLB with 256 entries/core (normalized to private) | 61 |

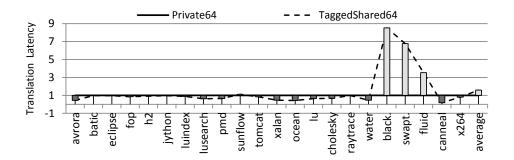

| 31 | Latency for private vs tagged shared TLB with 64 entries/core (normalized to private)  | 62 |

| 32 | Partial sharing TLB organization and translation lookup                                | 63 |

| 33 | Structures for virtual address, TLB entry, PSB entry and page table entry(PTE)         | 63 |

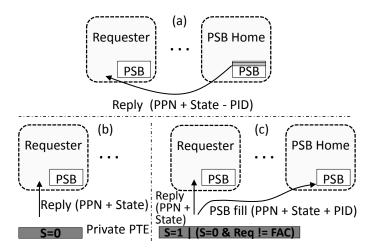

| 34 | Translation reply and fill on PS-TLB ((a):Hit a PSB entry(b):PSB miss of a private     |    |

|    | PTE (c):PSB miss of a shared PTE                                                       | 66 |

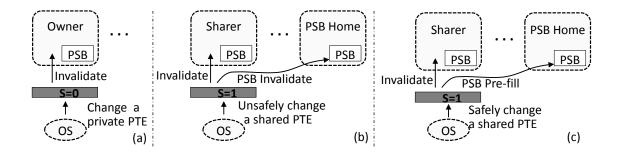

| 35 | TLB shootdown process on PS-TLB                                                        | 67 |

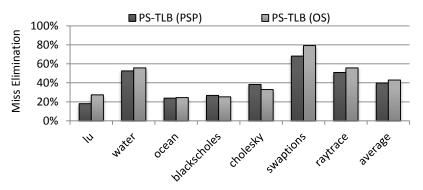

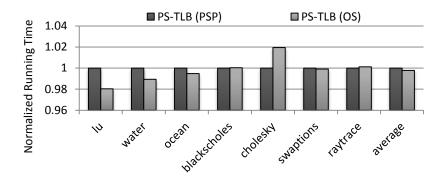

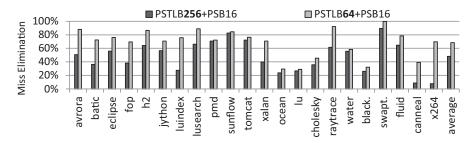

| 36 | TLB miss elimination on PS-TLB with different page classification schemes              | 71 |

| 37 | PS-TLB performance comparison with different page classification schemes               | 71 |

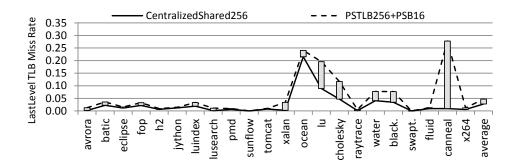

| 38 | Miss rate comparison of the PS-TLB with a PSB size of 16 entries compared with         |    |

|    | a centralized shared TLB                                                               | 73 |

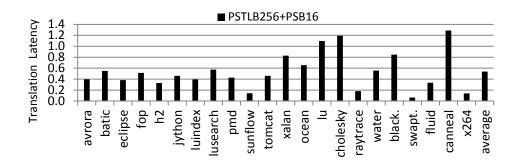

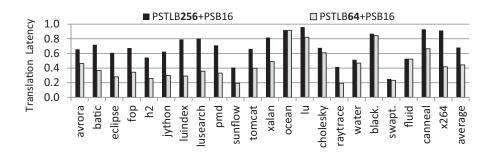

| 39 | Translation latency (normalized to centralized shared)                                 | 73 |

| 40 | Speedup over a centralized shared TLB                                                  | 74 |

| 41 | Percentage of last-level TLB miss reduction compared to prefetching scheme             | 75 |

| 42 | Translation latency compared to prefetching scheme                                     | 75 |

| 43 | Speedup over prefetching scheme                                                        | 76 |

| 44 | Percentage of last-level TLB miss elimination for a PS-TLB with 64 TLB entries/core          | 76  |

|----|----------------------------------------------------------------------------------------------|-----|

| 45 | Translation latency of a PS-TLB with 64 TLB entries/core (normalized to zero PSB)            | 77  |

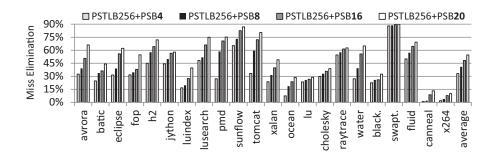

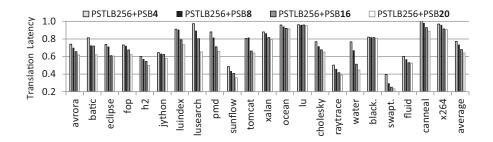

| 46 | Percentage of last-level TLB miss elimination for a PS-TLB with different PSB sizes          | 77  |

| 47 | Translation latency of a PS-TLB with different PSB sizes (normalized to a zero PSB)          | 78  |

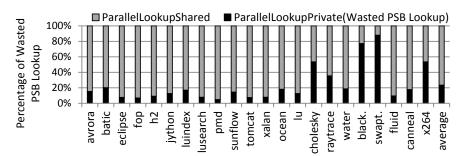

| 48 | Unnecessary (wasted) PSB lookups after a L2 TLB miss                                         | 78  |

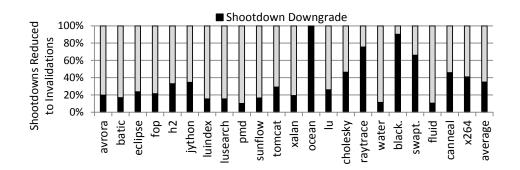

| 49 | Estimation of TLB shootdown downgrade savings                                                | 79  |

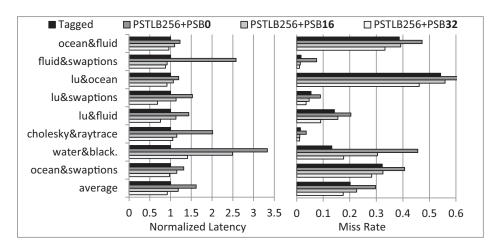

| 50 | Latency and miss rate saving during context switches                                         | 80  |

| 51 | Experimental compiler framework                                                              | 82  |

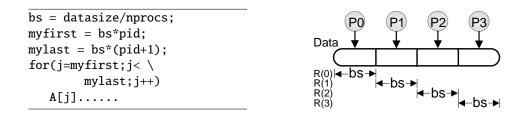

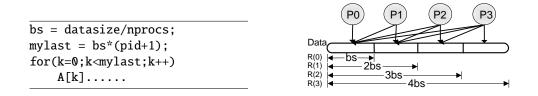

| 52 | Example TI structure and the corresponding block pattern ( $nprocs = 4$ )                    | 85  |

| 53 | Example TI structure and the corresponding nested pattern $(n procs = 4)$                    | 85  |

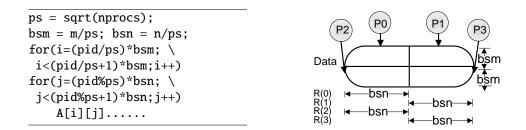

| 54 | Example TI structure and the corresponding grid pattern ( $nprocs = 4$ )                     | 86  |

| 55 | Example TI structure and corresponding interleaved pattern $(0 \le pid \le 3) \ldots \ldots$ | 86  |

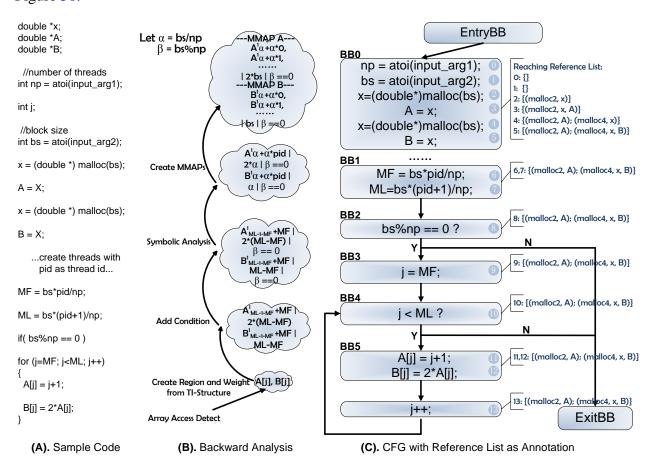

| 56 | MMAP generation flowgraph                                                                    | 88  |

| 57 | Example code                                                                                 | 91  |

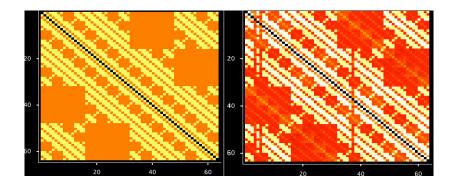

| 58 | Communication matrix                                                                         | 94  |

| 59 | Percentage of sub-pages with owners for (smaller working set on left)                        | 96  |

| 60 | Static vs dynamic communication pattern for OCEAN                                            | 96  |

| 61 | Static vs dynamic communication pattern for LU                                               | 97  |

| 62 | Static vs dynamic communication pattern for WATER-SPATIAL                                    | 97  |

| 63 | System overview                                                                              | 98  |

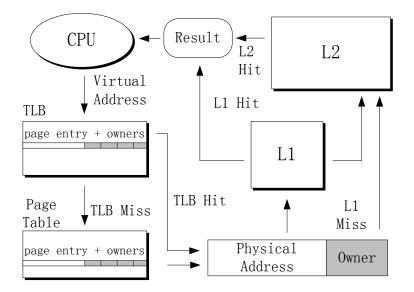

| 64 | Retrieving ownership during address translation                                              | 102 |

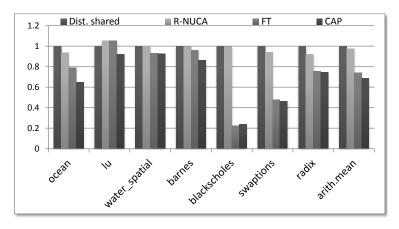

| 65 | Cache miss rate (normalized to dist. shared)                                                 | 104 |

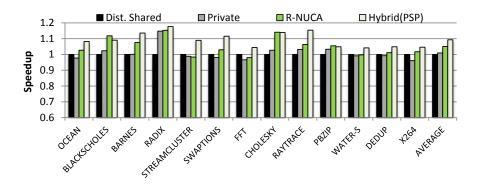

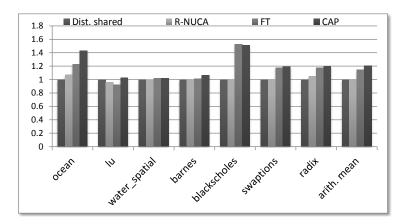

| 66 | Average memory access latency (normalized to dist. shared)                                   | 105 |

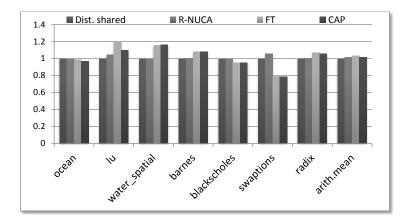

| 67 | Speedup (normalized to distributed shared)                                                   | 106 |

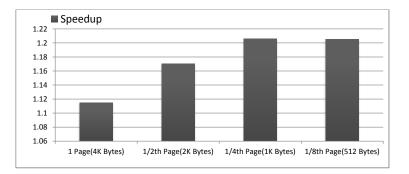

| 68 | Average speedup of CAP over distributed shared for various block sizes                       | 106 |

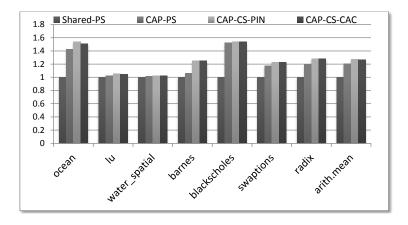

| 69 | Comparison of application speedup (normalized to Shared-PS)                                  | 107 |

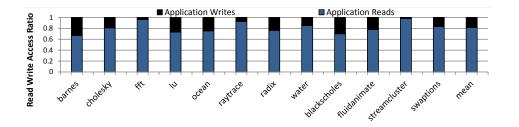

| 70 | Application read vs writes                                                                   | 108 |

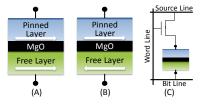

| 71 | Illustration of an MTJ and STT-RAM cell                                                      | 111 |

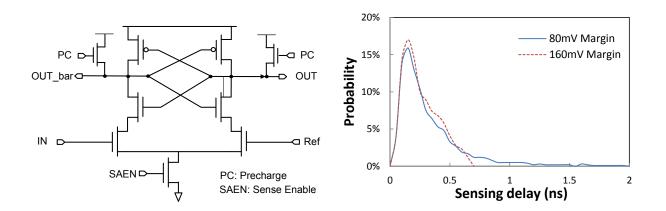

| 72 | Sense amplifier design                                                                       | 113 |

| 73 | Sense speed distribution                                                                     | 113 |

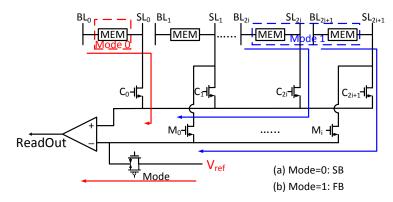

| 74 | Configurable SB/FB memory circuit                                                      |

|----|----------------------------------------------------------------------------------------|

| 75 | Array accesses and the corresponding matrix representations (a): array accesses (b):   |

|    | matrix representation                                                                  |

| 76 | CTR and CSR code examples                                                              |

| 77 | CTR and CSR access patterns                                                            |

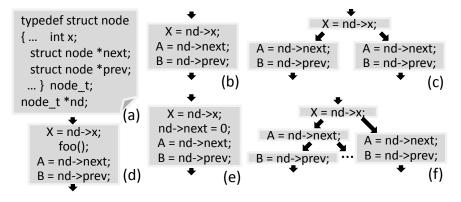

| 78 | Code and control flow graph examples for spatial reuse identification (T=3). (a):      |

|    | type definition code (b): spatial reuse in the same basic block (c): spatial reuse     |

|    | across one basic block and all its successors (d): spatial reuse broken by function    |

|    | call (e): spatial reuse broken by write (f): spatial reuse broken by one successor 123 |

| 79 | 3-D Architecture with hybrid SRAM/STT-RAM caches                                       |

| 80 | Configurable L1 cache architecture (C1C)                                               |

| 81 | Sparc V9 prefetch instruction format                                                   |

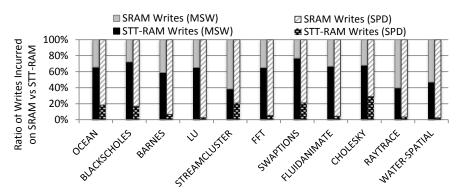

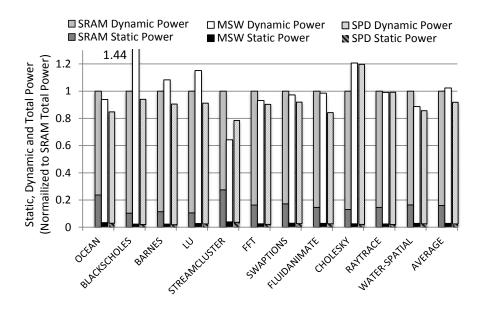

| 82 | Ratio of writes on SRAM vs STT-RAM for MSW and SPD                                     |

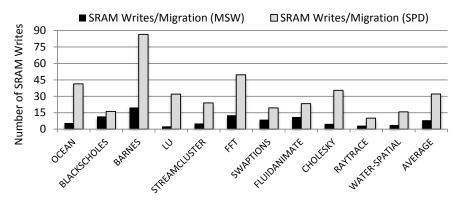

| 83 | Number of SRAM writes per dispatch (migration)                                         |

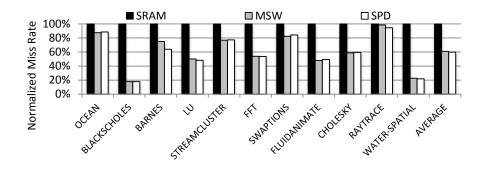

| 84 | Normalized off-chip miss rate                                                          |

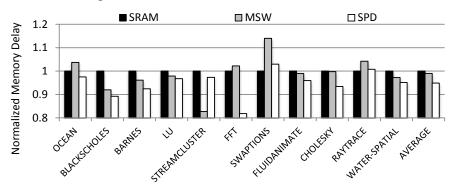

| 85 | Normalized memory access delay                                                         |

| 86 | Normalized power consumption                                                           |

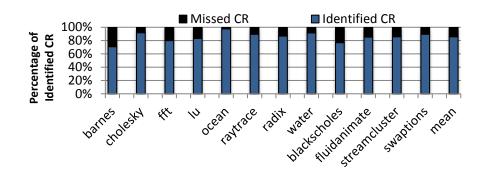

| 87 | Percentage of identified consecutive read reuse                                        |

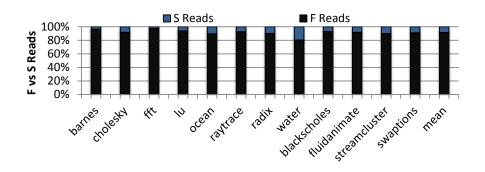

| 88 | Reads in different modes (optimized reads)                                             |

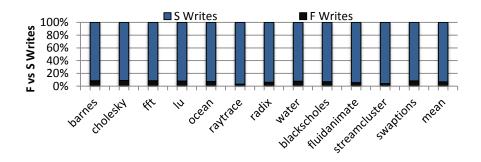

| 89 | Writes in different modes (write overhead)                                             |

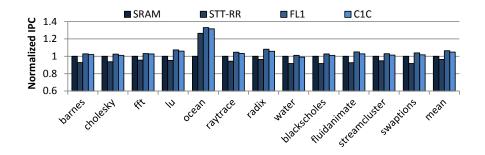

| 90 | Performance (IPC) comparison (norm. to SRAM)                                           |

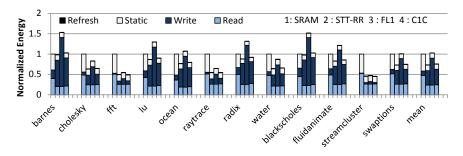

| 91 | Energy consumption (norm. to SRAM)                                                     |

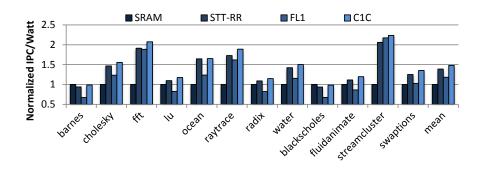

| 92 | Performance per watt comparison (norm. to SRAM)                                        |

#### PREFACE

Among many people who helped me with this work, I first thank my advisor, Dr. Alex Jones, for his relentless support throughout the entire duration of my graduate research, which forms the foundation of this dissertation. It was him who invited me to his excellent research group in which I initiated my first research project and have been actively participated during my PhD program. His instructive advice helped me to build my research experiences from ground up and follow the right direction since then. His strong enthusiasm motivates me to concentrate on my high performance computing research. Without his help, I could have never done this work.

Second, I would like to thank Dr. Rami Melhem, who has co-advised my research work for over five years of my graduate study. His encouragement at the early stage of my work made me feel warm and helped me through the hard times. It was from his words I gained the confidence to pursue a PhD degree. His patient guidances and directions not only helped me to conquer the difficulties I have experienced in my research work but also equipped me with valuable capabilities necessary for conducting research. From him I have learned many useful techniques including presentation/reasoning skills, academic paper writing, research idea formulating, etc.

I also thank Professor Yiran Chen, Professor Hai Li and Professor Zhihong Mao for being on my program committee and giving me constructive advice on this dissertation. I highly appreciate their time spent on reviewing the dissertation.

Thanks are also given to Ahmed Abousamra, my research group mate, for his suggestions and collaborative work. It was him who helped me to get a quick start on conducting research experiments.

Finally, I owe a thank you to my wife, Ruoxin Zhang, for her constant care and support during my entire PhD program. Her contribution to the family has enabled me to concentrate on my research work.

#### **1.0 INTRODUCTION**

The chip-multiprocessor (CMP) paradigm is now a prevalent platform to harness the increasing amount of on-chip transistors and offer massively parallel computing power that can be leveraged by a set of diverse applications. With the scaling of computing power available on a single die, effectively using resources is becoming increasingly important for designing high-performance, low-power and cost-efficient CMPs. To better apply these resources for today's diverging application requirements, new demands arise for "smarter" computer architectures that are more efficient and adaptive to application characteristics and deliver higher performance per watt. This dissertation work explores extracting application-level information that can be used by modern computer architecture components (e.g., caches, networks-on-chip and translation lookaside buffers (TLBs)) for optimized performance, scalability and efficiency. This chapter opens by introducing several challenges in building scalable and efficient modern CMP systems. Limitations of prior approaches and a brief introduction of the proposed solutions are also discussed in this chapter.

#### 1.1 CMP CHALLENGES

The increasing amount of computing capabilities integrated on chip requires both architectural innovation and consideration of the impact from technology scaling. While the performance continues to increase, the system suffers from many scaling induced issues including prolonged remote data access latency, more expensive communication overheads, increased leakage power, etc. The following two subsections discuss specific issues of architecture and technology scaling that motivate many CMP system optimizations including the proposed work.

#### 1.1.1 Architecture Scaling

Architectural resources in modern parallel computing platforms such as cache memories and interconnects are constantly evolving at a rapid pace to drive the computing capabilities and satisfy the increasing performance and scalability requirements. Unlike traditional computing processors in which a small number of cores are tightly integrated on a bus, current and future computers tend to have a larger number of integrated cores with local as well as shared resources connected using a distributed network-on-chip (NoC).

Organizing multiple processing cores in a distributed manner increases the inter-core communication bandwidth and mitigates the contention issue when handling data communication for a large number of cores. However, a well know issue associated with the distributed NoC is the multi-hop communication latency for accessing remote data. On the widely used non-uniform cache architecture (S-NUCA) [55] in which data blocks are interleaved across multiple cores, data communication latency due to remote accesses is significant. The increase in core count also complicates cache coherence operations typically required in multi-core systems to maintain data consistency. As a result, more storage resources and coherence messages are required to track and maintain the coherence states among multiple cores. In addition to the aforementioned issues, architecture scaling also challenges many other aspects of CMP designs, such as the virtual to physical address translation mechanism.

#### 1.1.2 Technology Challenges

Technology scaling is another driving force of modern CMP computing platforms. In particular, the shrinking transistor size and decreasing gate voltage of smaller technology process enable the designing of more powerful and energy-efficient CMP systems. The downside of this scaling trend is a variety of challenges (e.g., increased leakage power and reliability) that must be addressed before the technology process can become an overall competitive solution. One particular scaling issue this dissertation targets is the reduced sensing margin and consequently degraded read performance due to the process scaling in Spin-transfer torque RAM (STT-RAM), which has been been actively studied as a low leakage alternative for conventional memory technologies such as SRAM and DRAM. As the technology scales, the supply voltage, transistor size, and transistor

gate voltage of an STT-RAM cell decrease. Additionally, process variation [60] at smaller technology nodes begins to show a significant impact on device operations and result in a distribution of various electronic properties. As a result, data read performance suffers from larger sense amplifier delays for detecting increasingly small sense margins which is further exacerbated by the process variation.

#### **1.2 PROPOSED SOLUTIONS**

To address the issues presented in Section 1.1, this dissertation proposes various cross-layer optimizations to mitigate the coherence penalty, data access latency, communication overheads and improve address translation efficiency in scalable architectures. The proposed approaches leverage application-level information including data access classification, memory access patterns and data reuse behaviors in multi-threaded programs to optimize different architectural components such as caches, interconnect and TLBs.

In order to achieve a desirable utilization of the data access behaviors of a certain application in different scenarios, it is necessary to consider the information from either the compiler or OS, depending on the optimization target. Compiler techniques can be applied in many cases to extract fine-grained data access information and provide a method to examine an application's "future" characteristics *a priori*. OS-based mechanisms are good complements to a compiler approach and can efficiently retrieve page-level characterization when fine-grained information is not necessary. To gain an understanding of the behavior of today's parallel applications, various multithreaded benchmarks from the SPLASH [5], PARSEC [15] and RODINIA [21] benchmark suites are studied. Many of them exhibit regular data access patterns that can be statically extracted by a compiler or dynamically captured by an OS and used for cross-layer optimizations. This dissertation proposes techniques for characterizing data accesses in multi-threaded applications. The data access characterizations are used for a variety of optimizations including data placement among NUCA [55] caches, data-classification-aware caching, communication pattern prediction, circuit scheduling in network-on-chip (NoC), address translation acceleration and emerging memory configuration.

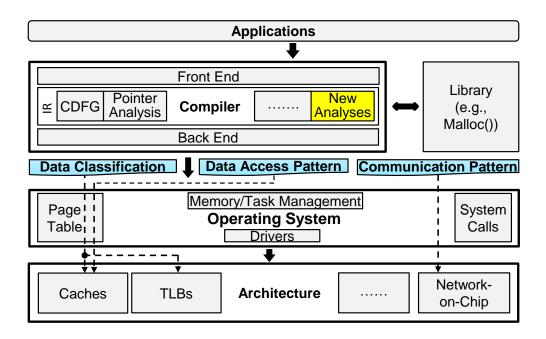

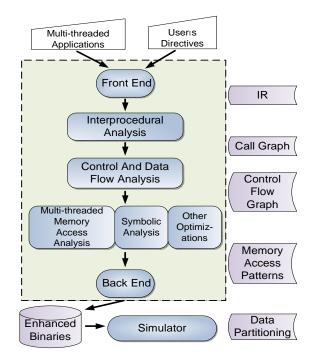

Figure 1: Overview of compiler- and OS-oriented architecture optimizations

Figure 1 illustrates a high-level overview of the proposed system with four layers: application, compiler, operating system (OS) and architecture. In the system the input applications are first processed by the compiler's front end and transformed into an intermediate representation (IR), on which a series of program analyses are performed. Many traditional compiler analyses are leveraged, and new compiler analyses are developed to extract useful application information that can be used by various system components at the architecture level. The compiler interacts with a customized library that can assist in passing the information to the OS or the underlying architecture. Finally, the extracted program characteristics are passed to the architecture at runtime. One example from this dissertation is data classification information discovered from the compiler analyses is first instrumented with a memory allocation routine (e.g., *malloc()*) and then passed through the page table to caches and TLBs for architecture optimizations. A second example is that data access pattern and communication pattern information can be passed to on-chip caches and NoCs through the OS page table [69] in a similar fashion to guide the cache data distribution and NoC configuration. Further, the instruction set architecture (ISA) can be extended with new instructions dedicated for architecture configuration, which is also discussed in this work.

#### **1.3 BACKGROUND AND CONTEXT**

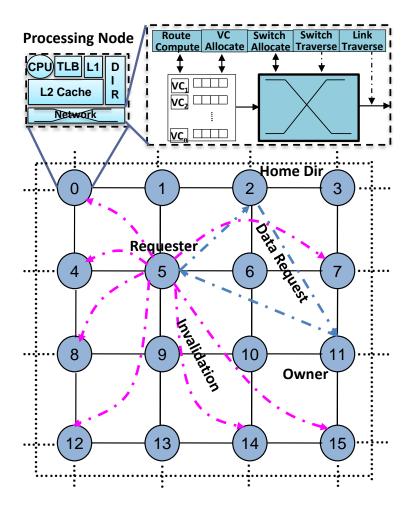

Figure 2: Scalable chip multiprocessor architecture

Figure 2 shows an example CMP architecture discussed as a baseline throughout the dissertation. The architecture contains several processing nodes and each node is composed of a processing core, a cache hierarchy (L1 and L2 caches), a TLB, a cache coherence directory (DIR) and a network switch. The network switch is pipelined in stages including route computation, virtual channel (VC [59]) allocation, switch allocation, switch traversal and link traversal. The cache coherence is maintained by a directory-based coherence protocol such as the MESI protocol [30]. In such an organization, a *requester* (e.g., node 5 in Figure 2) that accesses a datum not in the

local cache may need to consult a non-local *home* directory (node 2), which provides the state information of the datum and forwards the request to the *owner* (node 11). The datum is finally returned to the requester from the *owner* and this results in multi-way communications over the NoC. If the requester issues a write on a data item, multiple invalidation messages must be sent out to all the nodes that cache that data item. All of these operations can lead to expensive multi-hop communications, long access latencies, complicated coherence operations and high power consumption. The situation deteriorates as the architecture scales to larger core counts.

To mitigate the problems raised by architecture scaling, many runtime approaches have been proposed [112, 61, 20, 114, 94] to achieve fast memory accesses, reduced coherence overhead and communication latency. These schemes typically rely solely on hardware and are not aware of distinct application behaviors, resulting in more generic but often less efficient solutions in many scenarios. For example, Sun *et al.* [94] proposed a hybrid SRAM/STT-RAM cache in which hardware counters are used to keep track of runtime write access patterns and guide data migrations between the two types of memory. Recently, systems that adapt to certain application data access behaviors have been proposed [116, 29, 42, 48, 53] to further enhance performance and scalability by efficiently managing the on-chip components including caches, interconnect and TLBs. For example, Hardavellas *et al.* [42] proposed an OS based page-level data classification mechanism to guide the data placement in multiple last level cache (LLC) banks so that both private and shared data pages are placed as if in their favored LLC organizations (i.e., private and distributed shared, respectively).

The aforementioned mechanisms improve system performance and scalability by leveraging application runtime information. However, these mechanisms can mislead the hardware in certain scenarios and result in configuration thrashing due to a lack of knowledge about the overall data access characteristics. In other words, runtime based approaches rely on "local" application behavior typically extracted from a small time window rather than more reliable "global" information. Consider the data classification mechanism [42] that classifies a page as either private or shared based on the number of cores that have accessed the page. In such a runtime scheme a single access from a second core to a page results in the page being classified as shared, even if all the subsequent accesses are all private. This mechanism provides a simple and efficient solution when only coarse-grained classification information is needed (e.g., address translation discussed in Chapter 5). For

situations where finer grained data access information is required, the OS-page level mechanism can lead to inaccurate data classification. Tracking write access behaviors using hardware counters for data migration [94] can also result in problematic configuration and migration decisions. For example, a transient write access behavior can cause an unnecessary data migration if the detected behavior no longer persists after the migration.

An inherent drawback of the above mentioned approaches is that the runtime detected application characteristics may not be persistent to benefit an architecture configuration, resource scheduling, or a data distribution decision. A significant distinction that sets this dissertation work apart from the prior runtime based approaches is that in the enclosed solutions, relatively stable program behaviors are detected by compiler techniques and used by customized architecture designs that are aware of the detected information. By leveraging the compiler's capability in analyzing program characteristics over a larger execution window (e.g., global data flow information, intraand inter-procedure analyses, etc.), the proposed solutions avoid temporally misleading program behaviors and manage CMP resources more efficiently.

#### **1.4 CONTRIBUTIONS**

This dissertation work shows that how a variety of data characterizations including access patterns, data classification, sharing characteristics and reuse behavior can be leveraged for different architecture optimization goals. The proposed approaches are demonstrated on a cluster of novel designs and systems that are aware of certain application data access characteristics, particularly from the compiler or OS, to enhance various aspects of CMP architectures:

• Compiler-assisted Data Classification for Cache and TLB Optimization: This dissertation introduces a fairly simple but generic compiler analysis that can classify data into different categories including private and shared style memory accesses. In addition, to address several issues raised by runtime data classification mechanisms, a data classification termed *practically private* is introduced. The concept of practically private implies a situation where the compiler cannot prove that a data block is only accessed by one processor but speculatively determines that private style access is highly probable. Practically private classification also covers scenar-

ios where most elements of a data block are private or a data block is mostly accessed privately. Based on the data classification two architecture optimizations are proposed:

- By designing a cache coherence protocol that is aware of the data classification discovered by the compiler, the system achieves fast data accesses, efficient utilization of the on-chip LLC capacity, reduced communication latency and coherence overhead.

- The private-shared data classification is also used in the designing of a novel TLB architecture to provide translation sharing while keeping translation latency low. The new TLB design is based on traditional private TLBs but in addition provides a shared buffer to accommodate shared translations dictated by a page-level data classification mechanism. Since translation data is cached in TLBs at the OS page granularity, both the compiler and a simple and efficient OS-based approach are considered to provide the classification support for the proposed TLB design. The proposed TLB is demonstrated to outperform state-of-the-art translation solutions.

- Compiler-assisted Data Partitioning and Communication Pattern Analyses: Compiler techniques are proposed to determine multi-threaded memory access patterns and data partitioning in parallel programs that exhibit compile-time deterministic data access locality. Based on the detected data partitioning, each block is assigned an owner, which is the thread/core that accesses the block most frequently. Given the multi-threaded memory access patterns and data partitioning the compiler further determines communication pattern in an application. The data ownership and communication pattern can be used for efficient CMP architecture design:

- Ownership information is instrumented with memory allocation and passed to an architecture with an ownership-aware NUCA cache organization. Data blocks are distributed across NUCA banks based on the ownership information for improving locality and reducing remote data accesses.

- The communication patterns are used to guide circuit establishment to improve the circuit utilization and reduce circuit scheduling overhead in a hybrid packet/circuit-switching NoC [1].

- **Compiler-guided Configurable STT-RAM L1 Cache:** Finally, this dissertation work demonstrates that data access characteristics are important in designing next generation computer architectures leveraging emerging memory technologies. In particular a configurable STT-RAM

cache architecture designed to operate in two modes is studied. One mode is slower in servicing read accesses but has high density and low energy advantages. The other mode offers faster read accesses at the expenses of high dynamic write power and reduced memory density. Compiler techniques are demonstrated to identify consecutive data accesses to help the mode configuration to achieve optimized tradeoff between read speed, density and write power.

The evaluation demonstrates that the compiler-assisted data classification mechanism reduces an average of 46% coherence traffic and achieves around 10% speedup over the shared caching scheme for a set of tested parallel applications. The access-pattern-guided data placement scheme achieves a 20% speedup over traditional shared cache and leveraging communication patterns for network configuration provides an additional 5.1% performance gain. By leveraging data classification in address translation, the TLB can achieve a nearly 50% reduction in off-chip misses and 45% improvement in translation latency. Finally, the compiler-assisted configurable STT-RAM cache brings 5% performance gain over SRAM and 10% performance improvement with less than 2% dynamic power increase over STT-RAM designs without read optimizations at 22nm technology.

#### **1.5 OVERVIEW**

The rest of the dissertation is organized as follows: Chapter 2 describes the background and related research efforts. Chapter 3 introduces the compiler-assisted data classification mechanism. Chapter 4 presents an data-classification-aware coherence cache design to reduce remote data accesses and coherence overhead. Chapter 5 presents an advanced TLB design leveraging the data classification information to improve TLB sharing and reduce translation misses. Chapter 6 elaborates the proposed compiler techniques for analyzing data partitioning and communication patterns. An architecture with customized cache and NoC designs to utilize the data partitioning and communication pattern information is detailed in Chapter 7. In Chapter 8, the configurable architecture based on STT-RAM that leverages compiler-extracted consecutive reuse information is discussed. Finally, Chapter 9 summarizes the dissertation work.

#### 2.0 RELATED WORK

The proposed approaches in this dissertation are cross-layer and leverage system-level software such as compilers for optimizing a variety of architectural components including caches, NoCs and TLBs. This chapter is dedicated to introducing a general background and prior arts related to the work presented in this dissertation. More specific and detailed background relevant to each optimized component will be addressed in the subsequent chapters.

#### 2.1 COMPILER OPTIMIZATIONS

Compiler analyses and optimizations have been proven to be critical to improve code efficiency, reduce resource utilization, and expose optimization opportunities. Some of the proposed data characterization approaches are dependent on a series of conventional compiler analyses including control and data flow analysis, symbolic analysis, etc.

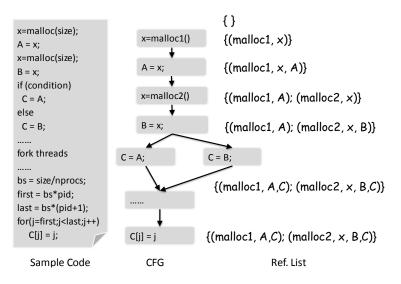

A control flow graph (CFG) [3] is a directed graph built on top of the intermediate code representation abstracting the control flow behavior of a function that is being compiled. In a CFG, each vertex represents a basic block <sup>1</sup> and each edge represents a possible transfer of control flow from one basic block to another. Since the CFG logically represents the relationship among different components of a program, it forms the basis for a large number of compiler analyses and optimizations such as pointer analysis, reaching definition, liveness analysis, dead code elimination, loop transformation, constant propagation, branch elimination, instruction scheduling, etc.

For data flow analyses, each basic block is further represented as a data flow graph (DFG) [49]. A DFG, which is also a directed graph, carries the data dependencies within the code between

<sup>&</sup>lt;sup>1</sup>A basic block is a continuous sequence of code with only one entry point and only one exit

control points. In a DFG, each node represents an operator (e.g. addition, logical shift, etc.) or an operand (e.g. constant, variable, array element, etc.). Each directed edge indicates a data dependency that denotes the transfer of a value.

Based on a combination of basic compiler optimization approaches, one can perform various high-performance oriented compile-time optimizations including dependence analysis, data reuse analysis, data access analysis, loop transformation, auto-parallelization [37, 40, 39], as have been done by many researchers.

Some early attempts have been made to analyze data accesses in a nested loop and find a data or loop partitioning among parallel threads. Ramanujam and Sadayappan [77] used a matrix representation to formulate an optimized data partitioning applied to shared memory multiprocessors without caches. Ju and Dietz [51] attempt to determine a data layout (row or column major) for a memory block in a uniform memory access (UMA).

In the PARADIGM compiler [38], data usage in parallelizable Fortran 77 and HPF (high performance Fortran) code was analyzed and partitioned across machines with distributed memories. Optimized communication operations were generated for the parallelized code. Another similar effort has been made by Kremer *et al.* [54], in which an automatic data layout specification was produced using 0-1 integer programming.

In the work from Lam's group at Stanford [105], data dependence was studied using a special case of the integer programming approach. Leveraging features of well formatted programs, their analysis results in a polynomial time algorithm. For data that carries no dependence, they distributed loop iterations across multiple processors. In another attempt, Barua *et al.* [11] developed a heuristic method to handle data partitioning in a way that avoids NP-complete linear programming.

There are also a number of efforts made to represent memory access patterns within singlethreaded programs with the intent of assisting compiler transformations. Tu and Padua [100] approximated memory accesses by representing each array access subscript using a triplet notation. Li and Yew proposed a representation named *atom image* [68] to capture the coefficients of indices and loop bounds in a program. A more precise notation is *convex region* [99, 28], which expresses the geometrical shape of array accesses. Paek introduced the concept of the *array access region* that uses span-stride pairs [73] with an abstract access form to represent memory accesses within a program phase such as a nested loop. Note that the array access region theory forms the foundation of the multi-threaded data access pattern analysis presented in this dissertation (see Chapter 6).

Based on array access regions, Paek and Padua [74] presented an advanced compiler framework to achieve automatic parallelization and communication generation for a machine that does not employ automated cache coherence. Chu *et al.* adopted a profiling based scheme [27] for determining affinity relationships between memory accesses and computation operations. Data accesses and computations are partitioned across data caches of each core to avoid memory stalls and improve computation parallelism. In another attempt from the same research group [26], a compiler-directed approach was proposed to cooperatively partition data objects and the associated computation across multiple clusters to achieve improved locality and reduced communication. Shao *et al.* proposed complier analyses to identify communication patterns in MPI-based parallel applications. The identified patterns are used to configure on-chip networks to avoid circuit establishment overheads and improve communication speed.

In another recent attempt [70], a polyhedral model is used to perform localization analysis based on the Farkas Lemma and Fourier-Motzkin algorithm. The goal of this analysis is to find a data layout transformation to promote locality of accesses which would otherwise be destroyed by finely interleaving data among the tiled banks. This work targets array accesses in sequential programs and restructures the array indexing such that a distributed shared cache policy is retained, but most of the addresses accessed by a particular thread are mapped to the tile on which that thread runs. It assumes a fixed way of partitioning the iteration space (hence the data space) among parallel threads and works in a similar way to that of some conventional paralleling compilers.

#### 2.2 CMP ENHANCEMENTS

There is a large body of research approaches proposed to optimize different CMP components including coherent caches, NoCs and TLBs. Most of these approaches target one CMP component and are generic in that they are independent of other architectural features and characteristics of applications. This section introduces relevant research efforts at architecture level. In particular, Section 2.2.4 discusses related work leveraging program characteristics for CMP optimizations.

#### 2.2.1 Coherent Caches

Ever since the concept of the static non-uniform cache access architecture (S-NUCA) [55] was proposed, extensive research has been conducted to mitigate the impact of poor data proximity associated with this scheme often by adopting different variations of a private caching [19]. However, private caches, due to the replication of shared data, do not utilize cache capacity as effectively as a distributed shared S-NUCA cache<sup>2</sup>. Several hybrid approaches have been proposed [111, 58] starting either with shared or private cache organizations to achieve an optimized design. Specifically, Zhang and Asanovic [114] proposed the victim replication cache scheme based on a shared L2 cache structure. In their work, the local L2 cache slice is used as a place to hold victim cache lines from local as well as remote L1s. Hammoud *et al.* designed a cache organization in which the unique copy of a data block is placed at the "center of gravity" of its requesters [41] to simplify coherence operation, save directory entries and reduce average access latency for multiple processing cores.

Chang and Sohi [20] designed cooperative caching based on private caches. They enlarged the effective cache capacity by evicting cache lines which have multiple copies prior to those with only a single copy. They also studied optimizations such as cache-to-cache transfer of clean data, replication-aware data replacement and global replacement of inactive data. Dybdahl [34] tried to combine the advantages of both shared and private caches by dividing cache banks into shared versus private partitions. The size of each partition changes dynamically depending on the miss rate of the corresponding bank. Other attempts have been made to mitigate the cache coherence overhead by designing more efficient directory structure [112] or adopting policies that simplify the coherence states such as the self-eviction policy [82].

Unlike the proposed techniques, which leverage software-extracted application characteristics, the above runtime cache optimizations rely on dedicated hardware to collect data access and sharing information. The collected information typically reflects only application behaviors in a small time window thus can result in frequent but inefficient cache reconfigurations.

<sup>&</sup>lt;sup>2</sup> In this work "shared" is used as a short term to refer to distributed shared S-NUCA.

#### 2.2.2 Network-on-chip

Interconnect communication is also becoming a major factor limiting CMP performance and scalability and has received significant research attention. Conventionally, interconnect is either packet or circuit switching. In traditional packet switching, packets must undergo several pipelined stages including decoding at input ports, buffering in virtual channels, computing routes, arbitrating/allocating switch resources and traversing the switch links. Communicating a message from a source to a destination typically involves multiple hops and thus the latency is high. By contrast, in circuitswitching networks circuits are established between source and destination nodes to achieve direct communication. However, the circuit establishment overhead is high and circuits are sparse resources that should be utilized carefully.

Recently, there have been several attempts to create configurable and hybrid networks to leverage the benefits of both packet and circuit switching techniques. For example, Peh's group at Princeton has developed the concept of Express Virtual Channels (EVCs) [62, 59]. EVCs provides a flow control mechanism that allows data packets to bypass arbitration and routing stages in a pipelined switch. With predefined virtual express paths (fast paths), packets can skip virtually the entire router pipeline at intermediate nodes along their paths and thus the communication delay approaches that of a dedicated wire interconnect. Jerger *et al.* [47] proposed a hybrid circuit switching, a technique that removes the circuit establishment overhead by intermingling packet-switched flits with circuit-switched flits. A prediction-based coherence protocol is also designed to leverage the existence of circuits and promote circuit reuse between sharer cores. Abousamra *et al.* [1] use a runtime system to determine the most beneficial fast paths to establish based on runtime collected traffic statistics. The fast paths, once established, are pinned for a predetermined period of time to promote locality and avoid expensive overheads due to frequency circuit establishments.

Many other strategies for reducing communication latency for traversing the network rely on methods for reducing the global hop count [57, 8, 18, 31]. For example, Kim *et al.* [57] proposed an flattened bufferfly network topology using high-radix routers to reduce the diameter of the network and hence the communication latency. They also exploited two dimensional network layout and channel bypass to further optimize on-chip communication. In another attempt [31], a hybrid topology that combines the bus and low-radix mesh was proposed to improve communication

efficiency. The bus is used for local communication among a few number of nodes while the mesh topology is used for global communication. Variants of the mesh-based network [8, 18] have also been demonstrated to have benefits over traditional mesh networks. These approaches adapt traditional mesh network based on traffic patterns to improve link utilization.

#### 2.2.3 Address Translation and TLBs

The TLB is another important CMP component on the critical path of memory accesses which has recently received considerable attention. Traditional TLBs are designed as private to each processing core in CMP systems to avoid long access latency. However, providing sharing for TLBs offers potential benefits of reduced TLB misses, enlarged TLB capacities and optimized TLB operations (e.g., TLB flush).

In particular, Bhattacharjee *et al.* recently presented a study of TLB sharing characterization [13] that motivated a number of research efforts including Synergistic TLBs [93] (detailed in Section 5.2.2). Based on the study of TLB sharing behavior, Bhattacharjee *et al.* proposed a TLB prefetching scheme [14] to reduce TLB misses. Using a technique called *leader-follower*, when a tile misses in the local TLB it becomes the "leader." The fetched TLB entry is sent to the prefetch buffer of other "following" cores that frequently utilize the leader's pages. A second technique, *distance-based cross-core*, matches the historical distance between TLB misses and predicts/prefetches TLB entries based on pattern matching. The system records the two distances between three successive TLB misses in a *distance table*. When two misses in any core match the first distance, the page matching the second distance is prefetched into the prefetch buffer.

A more detailed discussion of TLB related work and their comparison with the proposed TLB optimization can be found in Section 5.2.2.

#### 2.2.4 Application-aware Optimizations

A number of mechanisms have been recently proposed to utilize application data access characteristics to efficiently optimize various hardware components of CMPs such as caches, interconnects, coherence directories, etc. As these approaches are highly relevant to the proposed work, a summary of these approaches is provided below. **Cache:** In reactive NUCA (R-NUCA) [42], data accesses are classified as private, shared, and read-only at the page granularity. Data is assumed to be private until a second core accesses the data (signaled by a TLB miss). Data lines from private pages are cached locally to improve access latency while lines from shared pages are cached using S-NUCA style [56, 55] (i.e., distributed shared data placement) to improve capacity.

Another relevant effort is Jin and Cho's software oriented shared (SOS) cache management [48]. They classify data accesses to a range of memory locations (returned by a memory allocation function such as malloc()) into several categories such as Even Partition, Scattered, Dominant Owner, Small-Entity, and Shared. Applications are profiled and memory accesses are matched to one of the above categories. Hints are provided to the memory allocation functions based on the matched access patterns. Pages within the memory ranges are assigned to cache tiles indicated by these hints.

Cuesta et al. [29] recently presented an efficient cache coherence directory based on a runtime data classification scheme similar to the one used in R-NUCA. The proposed scheme saves more than 50% coherence directory entries by distinguishing shared data blocks from private ones and maintaining directory entries for only the shared data blocks. When the classification of a data page experiences a transition from private to shared, as detected by the OS, a coherence recovery process is invoked to recover the coherence states.

R-NUCA and SOS are both techniques that leverage execution history and profiling to detect the data access pattern. In addition, the two techniques extract information at the OS page granularity. Consequently, they have a higher probability of one data access pattern being polluted by another compared to a technique that utilizes application information at a finer granularity such as a cache line or an element of a data-structure.

**Interconnect:** Several attempts have been made to understand the communication characteristics of parallel programs [7, 43, 35, 89, 86, 103, 9, 79]. Most of these attempts, however, reveal only coarse properties of communication behaviors such as "point-to-point" and "collective". They do not provide accurate descriptions of communication patterns. The work in [86] uses a compiler to discover the communication behavior for MPI-based (message passing interface) programs and uses a matrix to describe the communication among multiple processors. The compiler is extended to include a phase partitioning algorithm and a scheduling methodology to configure a hybrid electronic packet-switched and optical circuit-switched interconnect [88]. However, these efforts only focus on explicit communications in MPI-based programs, omitting the implicit communication patterns implied by a shared-memory cache system.

#### 2.3 EMERGING MEMORIES IN CMPS

STT-RAM has been proposed for use in CMP cache hierarchies as a potential replacement for SRAM, particularly for LLC. STT-RAM caches can leverage both non-volatility for reduced leakage power and increased density and capacity over SRAM. Previous conventional wisdom for STT-RAM is that writes are slower and require more power than their conventional SRAM counterparts, although recent research efforts [115, 60, 72, 110] demonstrate that read performance becomes a new bottleneck as technology scales down to 45nm and below (detailed in Chapter 8). This section mainly discusses several techniques proposed at different levels (i.e., device, architecture and compiler levels) to mitigate the STT-RAM write challenges.

According to Smullen *et al.*, the excessive long write delay can be significantly reduced by relaxing the non-volatility [91] or reducing data retention time [96] with dynamic data refresh support to retain data. The write energy can be also saved by adopting early write termination [117], which avoids unnecessary writes in STT-RAM cells.

There are similar techniques proposed for combating write related penalties in phase-change memory (PCM). Qureshi *et al.* [76] recently proposes PreSET, a scheme aimed to improve read/write performance by leveraging the asymmetry in writing different logic values. Their earlier effort [75] attempts to alleviate the penalty of pending reads caused by long write delays using write cancellation and write pausing.

STT-RAM optimizations have also been substantially studied at architecture level. Guo *et al.* [36] use STT-RAM to re-design a number of non-write-intensive micro-architectural components. They also adopt a subbank write buffering policy with read-write bypassing to increase write throughput and hide the high write latency. Wu *et al.* [108] proposed a region-based hybrid cache architecture (RHCA) and a level-based hybrid cache architecture (LHCA) by combining disparate memory technologies including SRAM, STT-RAM and phase change memory (PCM). Dedicated

hardware units are used to collect data write intensity information and distribute data blocks to appropriate types of memories to reduce access latency and power consumption. Rasquinha *et al.* [78] proposed new promotion and insertion policies that operate differently for read versus write operations. The high write energy of STT-RAM was addressed by adopting a new replacement policy that increases the residency of dirty lines at higher cache levels (e.g., L1) at the expense of a higher data miss rate.

Li *et al.* [65] proposed a compiler-assisted technique to improve the performance and energy efficiency for embedded systems with STT-SRAM hybrid caches by reducing the migration overhead. In particular, the work identifies migration-intensive memory blocks through compiler analysis and give those blocks higher priority to be placed in the SRAM component to avoid frequent migration and long write latency on STT-RAM.

Chen *et al.* [23] developed a compiler pass that provides data placement hints to reduce STT-RAM write frequency on a customized hardware that can correct the compiler hints based on runtime cache behavior. In their solution a compiler technique is proposed to leverages the concept of memory reuse distance. However, the reuse distance concept used in their work is similar to the conventional reuse analysis and not aware of the read-write interleaving patterns. Thus, it cannot identify optimization opportunities brought by consecutive reads.

#### 3.0 COMPILER ANALYSES FOR DATA CLASSIFICATION

For multi-threaded applications running on CMPs, an important and commonly used approach for characterizing accesses to a data block is to examine how many cores/threads access that data block, based on which the block can be classified as private (accessed by one core) or shared (accessed by more than one core). This chapter presents how private versus shared data accesses can be detected using lightweight compiler analyses. To further reduce the compilation complexity and avoid the downside of a runtime data classification mechanism such as data classification pollution (see Section 3.2.1), a new data classification termed *practically private* is introduced. Practically private indicates that the compiler cannot easily prove that the memory is accessed privately (e.g., exclusively by one thread/core) but speculatively determines that private access is highly probable and any sharing is minimal. Due to the speculative nature of the practically private concept, the complexity of the compiler analysis required to capture data sharing information is greatly reduced, resulting in a simple and effective approach.

The practically private data classification promotes access proximity for many data blocks used by parallel applications that would be treated as shared in many run time schemes. Moreover, the proposed classification is helpful in designing a more efficient coherence protocol that distinguishes practically private versus shared data, which have remarkably distinct sharing and coherence behaviors. This chapter demonstrates that practically private data is ubiquitous across a variety of applications and a high percentage of practically private data is dominated by local accesses. The following two chapters demonstrate that the detected application data classification information can be used to optimize coherent caches and TLBs.

#### 3.1 BASIC ANALYZING APPROACHES

The proposed compilation methodology requires the use of several known compiler techniques that are well understood. This section discusses a few of these optimization passes and their applications in order to provide a background for the compiler methodology described in the following sections. In particular, the existing libraries available in the parallel compiler infrastructures SUIF [105] such as the dependence test, data flow framework [98], aliasing analysis, etc., are helpful in the development of the target compiler-based analysis and data classification.

In programs that utilize dynamically allocated objects, the starting addresses of memory blocks returned by malloc() are usually assigned directly to pointers. Other pointers can point to the same memory block through pointer assignments. To address the memory disambiguation problem, one necessary compilation technique is pointer analysis, which can be used to track memory access information of dynamically allocated memory. As such, the following definitions are introduced:

**Definition 1.** A pure pointer is a pointer that has been directly assigned the return value of a heap memory allocation routine such as malloc().

**Definition 2.** A derived pointer is a pointer that is derived from a pure pointer either directly or indirectly based on a pointer assignment.

**Definition 3.** A reference list for an allocated memory block is a collection of pointers that can be used to refer to that block.

To accomplish this analysis, a variant of Andersen's point-to analysis [4] was implemented. Instead of keeping a series of point-to pairs, a reference list is used to include all the pointers that may point to a particular memory block. By using the pointer analysis, array accesses can be resolved back to their pure pointers to simplify subsequent compiler analyses. A detailed example of the reference list based pointer analysis is shown in Section 3.3.

#### 3.2 DATA CLASSIFICATION

A study of multi-threaded code from a variety of program domains such as scientific computing, multimedia, image processing and financial processing reveals that data structures can be used in quite different ways. It is also observed that the way data is usually used by multiple threads can be implied by information such as where in the virtual memory space the data is allocated and how the references of data are handled. For example, instructions and globally allocated data such as synchronization structures are typically shared by all threads. In contrast, stack and heap objects allocated within a thread usually have very few sharers. From the system performance point of view, the access characteristics of these data objects are so different that each of them should be treated using a customized design. This section describes the approach to classify and identify the data classification at compile time. Since a variety of multi-threaded benchmarks feature extensive usage of dynamic memory allocation for managing computed data, emphasis is given to analyzing data blocks allocated through memory allocators such as malloc(). The analysis approach can be extended to other memory allocation routines such as new.

#### 3.2.1 Motivation: The Concept of Practically Private

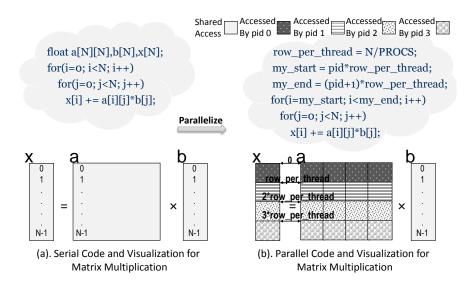

Understanding the data access behavior in multi-threaded programs is essential to deliver high performance on CMPs. Parallel applications tend to exhibit flexible and diverse data access patterns. This poses a challenge for compiler to detect and describe these patterns. However, the study shows that there are several representative patterns/classifications that exist in a variety of parallel applications and they dominate the entire program execution. Consider the matrix multiplication example in Figure 3. The code in Figure 3(a) computes the product of matrix *a* and vector *b* and stores the result in *x*. Figure 3(b) shows a typical parallelized version of the same problem using POSIX threads, assuming the number of available threads is four (*PROCS* = 4). Both the source code and the illustration in Figure 3(b) imply a clear data classification: *a* and *x* are partitioned across the 4 threads and thus can be classified as private while *b* should be classified as shared since it is entirely shared by all threads. This example will be revisited in more detail in Section 3.3 to show how the data classification can be formally identified from source code.

Figure 3: Serial and parallel computation for matrix multiplication

Generally, the classification of data must meet certain criteria to improve data access latency, save coherence directory entries or reduce network traffic. In particular:

- Different classifications within an application exhibit remarkable disparity in terms of locality, storage requirements, and access latency and as such must be treated differently.

- Classifications are practical for the compiler to identify.

- Classifications are representative for a wide spectrum of parallel applications.

A straightforward method is to classify data blocks into two distinct access categories: private versus shared, as shown in the above example. Private data is accessed by only one processor and thus is suitable to be placed locally to reduce access latency and promote locality. Coherence directory [113] size can also be reduced by eliminating entries for private data [29]. Conversely, shared data is accessed by more than one processor and should be optimized using different methods than private data. Shared data can be placed at a fixed location indexed by its address or at the "center of gravity" of its requesters [41] to reduce coherence traffic, save directory entries and simplify searching of data, especially when the data exhibits frequent/heavy sharing.

As a compiler-assisted data classification approach, the analyses must remain conservative when identifying private data to guarantee correctness. Unfortunately, identifying data privacy requires complicated and NP-complete compiler analyses (e.g., inter-procedural analysis, memory disambiguation, etc.), which drastically increase the compilation overhead and may still fail to guarantee data privacy in some complicated cases such as calling procedures by function pointers and accessing memory through pointer arithmetic. To avoid these complications and expensive analyses, the private-shared classification is extended with the third category, *practically private*. Leveraging practically private greatly reduces the burden of compiler analysis for ensuring data privacy and forms a data classification space the compiler can handle. The resulting three data categories are described as follows:

• **Private:** In multi-threaded applications, a data block (such as one returned by malloc()) is defined to be *private* if every element in it is accessed by only one thread in the parallel program segment. This is the case when multiple threads in the program partition a data block exclusively without overlap.

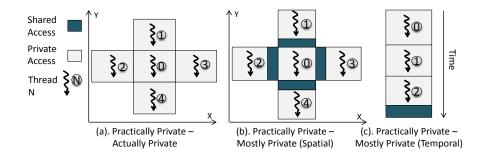

## • Practically Private:

For data that appears to be private but is not provably so from the compiler analysis, the data is classified as *practically* private. There are two scenarios that this classification covers. First, data that is *probably* private can practically be treated as private. Probably private data is frequently entirely private at runtime, as depicted in Figure 4(a), but safeguards are required to deal with cases when sharing occurs. Second, if the practically private data is not entirely private, typically it is still *mostly* private, as illustrated in Figure 4(b) and Figure 4(c). Figure 4(b) indicates mostly private data where each thread operates largely on exclusive data regions with shared boundaries (i.e., spatial perspective). Figure 4(c) illustrates mostly private (i.e., temporal perspective) where multiple threads operate exclusively on the data most of the time (e.g., data is shared only at the beginning or the end when threads are forked/joined). Typically, mostly private data has a low degree of sharing in terms of sharers and frequency of sharing, making it suitable for private treatment in practice.