# **VIDAS**

## PTDC/EEA-TEL/75217/2006

## Deliverable D4.1

## VLC Modulation Schemes

# Instituto de Telecomunicações Pólo de Aveiro

Aveiro, July 31st, 2010

## Deliverable D 4.1:

## **Modulation Schemes**

**Authors:** Navin Kumar

Mónica Figueiredo

Luis Nero Alves

Rui L. Aguiar

Source: Instituto de Telecomunicações - Pólo de Aveiro

No. of pages: 94

Version: 1

**Date:** March 31<sup>st</sup>, 2011

#### This deliverable reports to:

Activity D4.1: Modulation Schemes for outdoor visible-light communication systems

# **Contents**

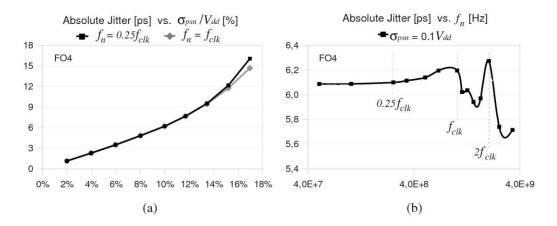

| Sumn    | 3.1.1 BER for OOK Modulation.       9         3.2 Pulse Position Modulation (PPM)       10         3.2.1 Bit Error Rate of L-PPM       11         3.2.2 Inverted – PPM (I-PPM)       12         3.2.2.1 Bit Error Rate of I-LPPM       13         Direct Sequence Spread Spectrum       15         4.1 Introduction       15         4.2 DSSS Modulation in VLC System       18         4.2.1 Introduction       18         4.2.2 Basic Principle       18         4.2.3 Sequence Inverse Keying Modulator       19         4.2.3.1 Frequency Domain Analysis       19         4.2.3.2 The Corresponding Time Domain Analysis       22         4.3 SNR and BER of SIK Modulator with AWGN       23         4.4 SNR and BER of SIK Modulator with AWGN       23         4.5 Matlab Simulink Model For DSSS SIK       24         4.5.1 Integrate and Dump Decorrelator Receiver       25         4.5.2 PN Matched Filter Correlator Receiver       25         4.5.2 PN Code Generator       28         Uncertainty in Clock Repeaters       31         5.1 Clock Repeaters       31         5.2 Simulation Framework       36 |            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.Intr  | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Techniques |

| 2.Base  | Baseband Data Transmission in White Gaussian Noise and Probability of Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| 3.Basi  | ic Modulation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7          |

| 3.1     | On-off Keying – Non Return to Zero (NRZ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7          |

| 3.1     | 1.1 BER for OOK Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9          |

| 3.2     | Pulse Position Modulation (PPM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10         |

|         | v .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 3.2     | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|         | 3.2.2.1 Bit Error Rate of I-LPPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| 4.Dire  | ect Sequence Spread Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15         |

| 4.1     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15         |

| 4.2     | DSSS Modulation in VLC System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 4.2     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 4.3     | SNR and BER of SIK Modulator with AWGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23         |

| 4.4     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 4.5     | Matlab Simulink Model For DSSS SIK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 4.5     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|         | 4.5.2.1 PN Code Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28         |

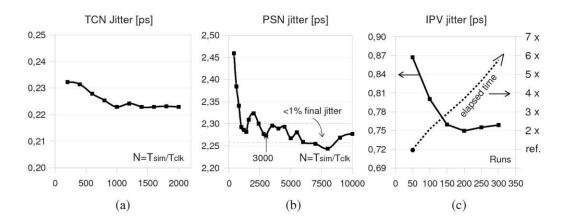

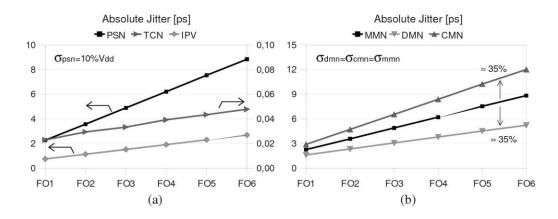

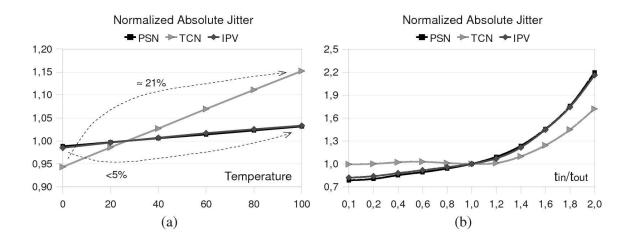

| 5.Unc   | ertainty in Clock Repeaters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31         |

| 5.1     | Clock Repeaters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31         |

| 5.2     | Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36         |

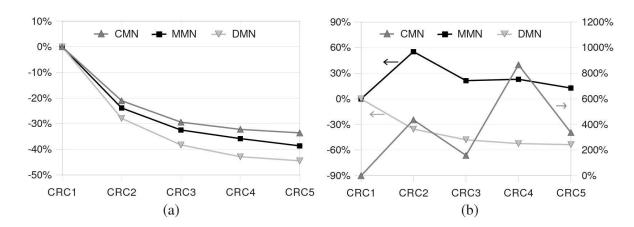

| 5.3     | Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41         |

| 6.Unc   | ertainty in Cascaded Clock Repeaters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45         |

| 6.1     | Digitally Controlled Delay Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45         |

| 6.2     | Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47         |

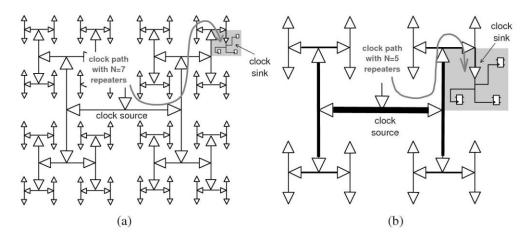

| 6.3     | Clock Distribution Trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50         |

| 7.Jitte | er Accumulation Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54         |

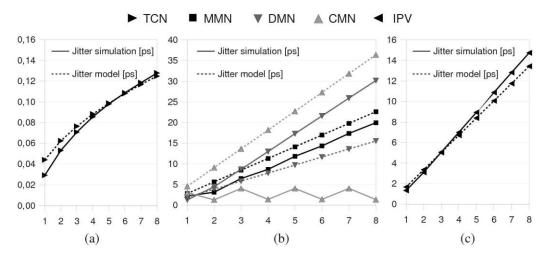

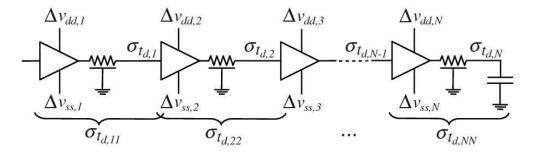

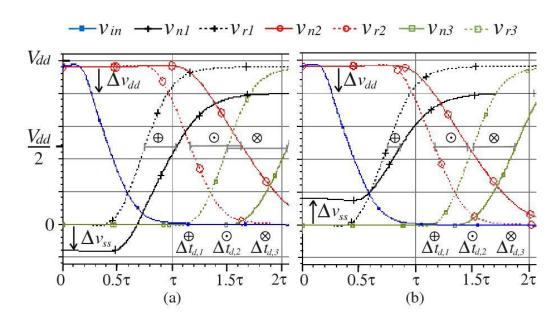

| 7.1    | Dynamic Jitter in Cascaded Repeaters | 54 |

|--------|--------------------------------------|----|

| 7.2    | Bounds for Jitter Accumulation       |    |

| 7.3    | Simulation Results                   | 58 |

| 8.Perf | formance Results                     | 62 |

| 9.Con  | cluding Remarks                      | 68 |

| Refere | ences                                | 69 |

#### **Modulation Schemes**

**Project VIDAS: Deliverable D4.1**

PTDC/EEA-TEL/75217/2006

#### **Summary**

This report presents the analysis of different modulation schemes D4.1 for VLC systems of the VIDAS project.

Considering the final prototype design and application, the deliverable D4.1 was projected. The detail analysis of various modulation schemes are carried out and a robust technique based on direct sequence spread spectrum (DSSS) is followed. DSSS technique though necessitates use of high bandwidth while minimizing the effect of noise. Since the final application does not require very high data rate of transmission but robustness against the noise (external lights) becomes necessary. The analysis is followed by model development using Matlab/Simulink. The performance of both of these systems are compared and evaluated. Some of the simulation results are presented.

# Section 1

#### 1. Introduction

Modulation is one of the key processes in communication system. Appropriate and robust modulation techniques allow enhanced performance of the system. The performance of VLC systems is likely to be impaired by the significant high path loss and the shot noise induced by natural and artificial lights. High path loss leads to the use of considerably high optical power levels. In addition, they are also suffered from the speed of optoelectronic devices (LEDs and PIN photodiodes). System performance varies depending on the environment conditions, data rate, technical solutions and implementation of a particular system.

In the application of traffic information broadcast system, the data is received by the receiver installed on moving vehicles. The amount of data received will depend on the data transmission rate, velocity of vehicles and the road length (service area) in which data is receivable. This is given by the relation:

$$Received\ data[bit] = \frac{Transmission\ Rate[bits/sec]*Service\ Area[m]}{Velocity\ of\ Vehicle[kmph]} \tag{1}$$

That is, the received data increases with the distance (increase in service area). However, the possibility of interference also increases with distance. Assuming, a vehicle approaching traffic point at a speed of 60kmph will cover 16.6m of distance each second. Considering data rate 100kbps, vehicle speed of 60kmph and a service area between 2.5m to 70m of road length, the amount of received data comes to be approximately 150kbits to 420kbits. Furthermore, a text message in A4 size of paper with 20 font size of Times New Roman Font which can comfortably be read by driver contains approximately 10kbits of data. This means that each second 15 to 42

times of 10kbits of data can be sent by VLC broadcast transmitter and receiver is expected to reliably receive the information. If the transmitted information is repeated a number of times, the driver will have little over 4 seconds to read the message before crossing the service area when green signal remains on (the worst case condition). However, if vehicle needs to stop for green signal there will not be problem in receiving and reading the information.

The above scenario is applicable in normal conditions i.e. when line-of-sight (LoS) channel is free from other disturbances such as fog, rain and dense dust. But under these conditions the channel behavior will vary and thus service area will be affected (as discussed in R3.1). Therefore, a robust modulation technique is needed for this system. DSSS based modulation has been widely used in Radio system and considered robust system especially in noisy environment. However, requirement of transmission bandwidth increases thereby affecting data rate. But, in road safety applications of traffic information broadcast, the data rate is not an important issue. Minimizing the effect of external noise is the most important.

In this report, we focus on one of the most robust modulation technique based on DSSS. The choice for the method is also supported for the low data rate application. The primary measure of system performance for digital data communication system is the probability of error  $P_E$  [1]. Therefore, we derive a generic expression for  $P_E$  and SNR for baseband data transmission on AWGN channel.

# Section 2

# 2. Baseband Data Transmission in White Gaussian Noise and Probability of Error

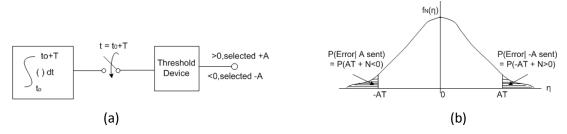

Consider the binary digital data communication system with transmitted signal consists of a sequence of constant amplitude pulses of either A or -A units in amplitude and T seconds duration. Considering a detector with integrate and dump (Fig. 1a), the performance can be evaluated with probability of error in the received signal. The output of the integrator at the end of a signaling interval is:

$$V = \int_{\tau_0}^{\tau_0 + T} [s(t) + n(t)]$$

(2)

$$= \begin{cases} +AT + N & if + A \text{ is sent} \\ -AT + N & if - A \text{ is sent} \end{cases}$$

(3)

where *N* is a random variable defined as:

$$N = \int_{\tau_0}^{\tau_0 + T} n(t) dt \tag{4}$$

Since *N* results from a linear operation on a sample function from a Gaussian process, it is a Gaussian random variable. It has the mean:

$$E\{N\} = E\left\{ \int_{\tau_0}^{\tau_0 + T} n(t)dt \right\} = \int_{\tau_0}^{\tau_0 + T} E\{n(t)\}dt = 0$$

(5)

**Fig.1:** a) Receiver structure with Integrate-and-dump receiver; b): Illustration of error probabilities for Binary Signalling

since n(t) has zero mean. Its variance is therefore,

$$var\{N\} = E\{N^{2}\} = E\left\{ \left[ \int_{\tau_{0}}^{\tau_{0}+T} n(t)dt \right]^{2} \right\}$$

$$= \int_{\tau_{0}}^{\tau_{0}+T} \int_{\tau_{0}}^{\tau_{0}+T} E\{n(t)n(\sigma)\}dt \, d\sigma$$

$$= \int_{\tau_{0}}^{\tau_{0}+T} \int_{\tau_{0}}^{\tau_{0}+T} \frac{1}{2} N_{0} \delta(t-\sigma)dt \, d\sigma$$

(6)

where we have made the substitution  $E\{n(t)n(\sigma)\} = \frac{1}{2} [N_0 \delta(t - \sigma)]$ . Using the shifting property of the delta function, we obtain:

$$var = \frac{1}{2} \left( N_0 T \right) \tag{7}$$

Thus the probability density function (pdf) of N is:

$$f_N(\eta) = \frac{e^{-\eta^2/N_0 T}}{\sqrt{\pi N_0 T}} \tag{8}$$

where  $\eta$  is used as the dummy variable for N to avoid confusion with n(t).

If +A is transmitted, an error occurs if AT + N < 0, that is if N < -AT. The probability of this event is:

$$P(error|A\ sent) = P(E|A) = \int_{-\infty}^{-AT} \frac{e^{-\eta^2/N_0 T}}{\sqrt{\pi N_0 T}} d\eta \tag{9}$$

Which is the area to the left of  $\eta = -AT$  in Fig. 1b. Letting:  $u = \frac{-\sqrt{2}\eta}{\sqrt{N_0 T}}$ , we can write this as:

$$P(E|A) = \int_{\sqrt{A^2 T/N_0}}^{\infty} \frac{e^{-u^2/2}}{\sqrt{2\pi}} \ du \ \triangleq Q\left(\sqrt{\frac{2A^2 T}{N_0}}\right)$$

(10)

which is the area to the right of  $\eta = AT$  in the Fig. 1b. The average probability of error is

$$P_{E} = P(E|+A) P(+A) + P(E|-A) P(-A).$$

(11)

As P(+A) + P(-A) = 1, we obtain:

$$P_E = Q\left(\sqrt{\frac{2A^2T}{N_0}}\right) \tag{12}$$

We can interpret the ratio  $A^2T/N_0$  in two ways. First, since the energy in each signal pulse is:

$$E_b = \int_{t_0}^{t_0 + T} A^2 dt = A^2 T \tag{13}$$

we see that the ratio of signal energy per pulse to noise power spectral density is:

$$SNR = \frac{A^2T}{N_0} = \frac{E_b}{N_0} \tag{14}$$

where  $E_b$  is called the energy per bit because each signal pulse (+A or -A) carries one bit of information. Second, we recall that a rectangular pulse of duration T seconds has amplitude spectrum AT sinc Tf and that  $R_b = 1/T$  is a rough measure of its bandwidth. Thus,

$$SNR = \frac{A^2}{N_0 R_b} \tag{15}$$

can be interpreted as a function of bandwidth (data rate).

Next, we examine the performance of various modulation techniques. We start with most common, based on intensity modulation with direct detection (IM/DD), on-off keying.

# Section 3

## 3. Basic Modulation Techniques

The choice of modulation technique in the design of VLC system remains one of the most important technical issues. Background from IR technology suggests the use of modulation techniques such as OOK, L-pulse position modulation (L-PPM), subcarrier phase shift keying (SC-PSK) and these have been discussed and proposed [2-4]. Utilization of equalization techniques for IR as well as indoor short range VLC has also been proposed by authors in [5, 6]. The use of equalizers substantially increases the receiver complexity while OOK and L-PPM though simple to implement causes interference because of artificial and other sources of light.

In the following sections, we discuss various modulation techniques. We start with OOK, which forms the basic standard for evaluation.

### 3.1 On-off Keying – Non Return to Zero (NRZ)

On-Off-Keying is the simplest form of amplitude-shift keying (ASK) modulation that represents digital data as the presence or absence of a carrier wave. In its simplest form, the presence of a carrier for a specific duration represents a binary one, while its absence for the same duration represents a binary zero. Some more sophisticated schemes vary these durations to convey additional information. It is analogous to unipolar encoding line code.

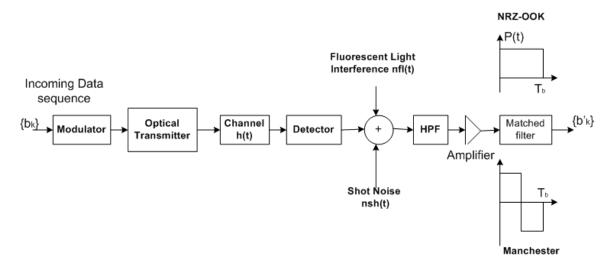

The block diagram of a typical receiver system employing IM/DD is shown in Fig. 2. Information bits are the inputs to the modulator (NRZ or Manchester) at a bit rate of  $R_b$  (bit per second (bps)). Pulse waveforms produced by the modulator for each bit drive the optical

transmitter. The intensity-modulated optical signal passes through a time-dispersive multipath channel that is fully characterized by its impulse response  $h_c(t)$ . However, multipath channel can be ignored in this application. The incoming optical signal is converted to an electrical signal by the photodiode by using direct detection. This electrical signal is comprised of a distorted replica of the transmitted signal and shot noise,  $n_{sh}(t)$ , as well as fluorescent light periodic interference,  $n_{fl}(t)$ . The high pass filter (HPF) at the receiver front end, after the photodiode, is modeled as a first-order RC filter with a cut-off frequency of  $f_o$ . Matched filtering using Integrate and dump filter is assumed for both modulation schemes. The impulse response of the matched filter for both modulation schemes is also depicted in Fig. 2. In the absence of fluorescent light and inter symbol interference (ISI), this corresponds to the optimum maximum-likelihood (ML) receiver [7].

The peak amplitude of the received signal pulses is A and is directly proportional to the optical power, i.e.,  $A = 2R P_{opt}$ , where R is the photodetector responsivity and  $P_{opt}$  is the average received optical power [2, 8]. The power spectral density (PSD) of the Gaussian shot noise  $n_{sh}$  (t) is denoted by  $N_0$ . The shot noise PSD is dependent on the total DC-generated photocurrent, i.e.,  $N_0 2e(I_B + i_b)$ , where  $I_B$  is the DC photocurrent generated by stationary ambient lighting and  $i_b$  is the DC level of the fluorescent light interference. For both modulation schemes the transmitted signal waveform can be described as an infinite series of time delayed replicas of the basic pulse waveform p(t):

$$S(t) = \sum_{k=-\infty}^{\infty} a_k p(t - kT_b)$$

(16)

where p(t) is the rectangular pulse of duration  $T_b = 1/R_b$ . However, if signal is Manchester, the p(t) is the alternating pulse of the same duration with mid-bit transition.

Fig. 2: Block diagram of a Typical IM/DD Receiver

Ignoring noise components, the received signal pulse r(t) at the input of the matched filter will be:

$$r(t) = h_F(t) * p(t) \tag{17}$$

where  $h_F(t)$  is the impulse response of the HPF and \* denotes convolution.

#### 3.1.1 BER for OOK Modulation

On-Off-Keying transmitter emits a rectangular pulse of duration  $1/R_b$  and of intensity 2P to signify a one bit, and no pulse to signify a zero bit. The bandwidth required by OOK is roughly  $R_b$ . The BER is given in terms of minimum distance between two bits. In this type of receiver design, the receiver will choose that signals from the set of known signals that is closest to the received signal. Since the receiver observes which of the possible signals is closest to the received signal, it stands to reason that it is less likely to make an error due to noise or other errors when the other signals are further away.

For the case of OOK the BER is given as:

$$BER_{OOK} = Q\left(\frac{RP_{av}}{\sqrt{N_0 R_b}}\right) \tag{18}$$

Also, in terms of error function<sup>1</sup>, it is given as:

$$BER_{OOK} = \frac{1}{2}erfc\left(\frac{P_{av}R\sqrt{T_b}}{\sqrt{2N_0}}\right)$$

(19)

Power required by OOK to achieve a given BER is:

$$P_{OOK} = \sqrt{N_0 R_b} \ Q^{-1}(BER) \tag{20}$$

For any other modulation scheme to achieve the same error probability, the required power is approximately:

$$P = \left(\frac{d_{OOK}}{d_{min}}\right) P_{OOK} \tag{21}$$

\_

$<sup>^{1}</sup>Q(z) = \int_{z}^{\infty} \frac{1}{2\pi} e^{-\frac{y^{2}}{z}} dy$ , and also,  $Q(z) = \frac{1}{2} \left[ 1 - erf\left(\frac{z}{\sqrt{2}}\right) \right] = \frac{1}{2} erfc\left(\frac{z}{\sqrt{2}}\right)$

#### 3.2 Pulse Position Modulation (PPM)

Higher average power efficiency can be achieved by employing pulse modulation schemes in which a range of time dependent features of a pulse carrier may be used to convey information.

PPM has been used widely in optical communication systems. It is a scheme where the pulses of equal amplitude are generated at a rate controlled by the modulating signal's amplitude. During PPM transmission, signal pulses are fixed width and amplitude, but the actual number is represented by pulse position in time.

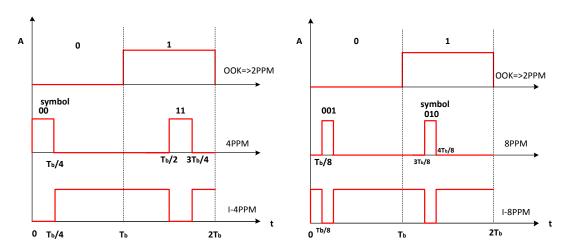

L-PPM utilizes symbols consisting of L time slots (chip). A constant power L.P is transmitted during these chips and zero during remaining (L-1) chips. Hence, encoding  $log_2L$  bits in the position of the high chip. If the amplitude of transmitted waveform is A, average transmitted power of 2PPM is A/2, that of 4PPM is A/4, and for L-PPM is A/L. For any L greater than 2, PPM requires less optical power than OOK. In principle, the optical power requirement can be made arbitrarily small by making L suitably large, at the expense of increased bandwidth.

For a given bit rate, L-PPM requires more bandwidth than OOK by a factor of  $L/log_2L$  i.e. 16-PPM requires four times more bandwidth (BW) than OOK. The bandwidth required by PPM to achieve a bit rate of  $R_b$  is approximately the inverse of one chip duration, B = L/T [9]. In addition to the increased bandwidth requirement, PPM needs (compared to OOK) more transmitted peak power and both slot and symbol-level synchronization [10].

In the absence of multipath distortion, L-PPM yields an average–power requirement that decreases steadily with increasing L; the increased noise associated with a  $(L/log_2L)$ -fold wider receiver noise BW is out weighted by the L-fold increase in peak power.

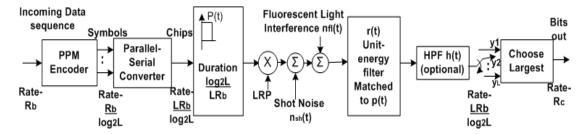

Fig. 3 shows the block diagram of the L-PPM system. Input bits, at rate  $R_b$ , enter a PPM encoder, producing L-PPM symbols at rate  $R_b/Log_2L$ . Each symbol contains a single sample of unit amplitude and (L-1) samples of zero amplitude. The PPM symbols are converted to a serial sequence of chips at rate  $LR_b/log_2L$  and passed to a transmitter filter whose impulse response p(t) is a unit-amplitude rectangular pulse of duration  $log_2L/LR_b$ . The chips are scaled by the peak detected photocurrent LRP and shot noise n(t) and fluorescent-light interference  $n_{fl}(t)$  are added. The receiver employs a unit- energy filter r(t) matched to p(t) which is followed by high pass filter h(t). The filtered signal is sampled at rate  $LR_b/log_2L$  and passed to a comparator that determines which sample in each L-length block has the largest value thus yielding the output bit sequence. Without fluorescent light and high pass filtering the receiver is ML receiver.

Fig. 3: Block diagram of L-PPM System

In this type, each signal is orthogonal of the form:

$$X_{m} = [0, 0, \dots, b_{h}, 0, 0]$$

(22)

where the non-zero term is in the m-th position. Thus, every signal is the same distance from every other signal. Fig. 4 illustrates the waveforms from pulse modulators.

#### 3.2.1 Bit Error Rate of L-PPM

For L orthogonal signals, there are (L-1) other signals at the minimum distance, and the error probability is independent of which signal is transmitted. Symbol error rate can be derived from minimum Euclidian distance  $(d_{min})$ :

$$d_{min}^2 = \min \int_{i \neq i} \left( x_i(t) - x_j(t) \right)^2 dt \tag{23}$$

where d<sub>min</sub> for L-PPM is given as:

$$d_{min} = \sqrt{\frac{2R^2LP_{av}^2\log_2L}{R_b}}$$

(24)

Hence, the symbol error rate for L-PPM is given as:

Fig.4: Illustration of L-PPM and I-LPPM waveforms

$$SER_{L-PPM} = Q\left(\sqrt{\frac{2R^2LP_{av}^2\log_2L}{N_0R_b}} \cdot \frac{1}{2}\right)$$

(25)

$$SER_{L-PPM} = Q\left(\sqrt{\frac{R^2LP_{av}^2\log_2L}{2N_0R_b}}\right) \tag{26}$$

*BER* - We assume that symbol '1' (corresponding to chip sequence  $b_k$  of a single one followed by (L-1) zeros) was transmitted and we assume k = L. Therefore, probability of bit error can be approximated as:

$$P[bit\ error\ \because\ transmit\ symbol\ 1]\ pprox rac{L/2}{(L-1)} \left[ Q\left(rac{d_{min}}{2\sqrt{N_0}}

ight)

ight]$$

(27)

So that,

$$BER_{L-PPM} = \frac{L/2}{L-1} Q\left(\sqrt{\frac{R^2 L P_{av}^2 \log_2 L}{2N_0 R_b}}\right)$$

(28)

The average optical signal power required to achieve a given SER for an L-PPM system can be found by solving for  $P_{av}$ :

$$P_{req} = \frac{\sqrt{N_0 R_b}}{\sqrt{\frac{1.L \log_2 L}{2}}} Q^-(BER)$$

(29)

$$P_{req} = \frac{P_{OOK}\sqrt{2}}{\sqrt{L.\log_2 L}} \tag{30}$$

That is, L=2 yields a sensitivity for 2-PPM that is identical to OOK. We see that, for any L greater than two, the optical power required by L-PPM is smaller than that required by OOK.

It can also be noted that, 2-PPM has the same power efficiency as OOK but requires twice the bandwidth. It is apparent that 4-PPM is particularly attractive because it has the same bandwidth requirement as 2-PPM but requires 3.8dB less optical power. As L increases from 4 to 16, the bandwidth requirement increases from  $2R_b$  to  $4R_b$ , while the sensitivity increases from 3dB better than OOK to 7.5dB better than OOK.

For a given transmitter power, background illumination power, and bit rate, it is desirable to maximize the allowable distance between transmitter and receiver, which is equivalent to maximizing the power efficiency.

#### 3.2.2 Inverted – PPM (I-PPM)

In the case of conventional PPM, we set only one pulse among L sub intervals. Average transmitted power, i.e. LED brightness, falls to 1/L when the peak amplitude is not changed. Of course, LED brightness can be made to equal with other modulation methods if we increase the

amplitude L times (practical limitation with power constraint). I-PPM yields higher brightness than conventional PPM. Inverting the pulse position of conventional PPM, we obtain I-PPM (as shown in Fig. 4. The optical intensity is 'off' during the 1-th sub-interval and 'on' everywhere else. For example, in case of 4-PPM light is on equivalent to 3-chip duration, making the LED three times as bright as conventional 4PPM. When amplitude of the transmitted waveform is A, average transmitted power of I-4PPM is 3A/4. That is, the average transmitted power of I-L-PPM is (L-1)A/L.

This modulation technique is particularly suitable in the indoor environment for the reason that illumination is better.

#### 3.2.2.1 Bit Error Rate of I-LPPM

In the case of inverted multilevel PPM, the symbol error rate for the inverted L-PPM is given as:

$$SER_{I-LPPM} = Q\left(\sqrt{\frac{2R^2LP_{av}^2\log_2L}{(L-1)^2N_0R_b}} \cdot \frac{1}{2}\right)$$

(31)

$$SER_{I-LPPM} = Q\left(\sqrt{\frac{R^2LP_{av}^2\log_2L}{2(L-1)^2N_0R_b}}\right)$$

(32)

and the BER is therefore;

$$BER_{I-LPPM} = \frac{L/2}{L-1} Q\left(\sqrt{\frac{R^2 L P_{av}^2 \log_2 L}{2(L-1)^2 N_0 R_b}}\right)$$

(33)

The average optical signal power required to achieve a given SER for an I-LPPM system can be found by solving for  $P_{av}$ :

$$P_{req} = \frac{\sqrt{N_0 R_b (L-1)Q^{-1}(BER)}}{R\sqrt{\frac{1}{2}L \log_2 L}}$$

(34)

$$P_{req} = \frac{(L-1)\sqrt{2} P_{OOK}}{R\sqrt{L Log_2 L}} \tag{35}$$

From the simulation results it is observed that L-PPM forms of modulation techniques are power efficient and can increase the data transmission rate. However, that may result in intersymbol interference and increased bandwidth. On the other hand, I-LPPM is suitable for indoor scenario where power is not a constraint that is required illumination remains to be in place. This means, they are not power efficient. However, the effect of noise on the systems remains an issue and in VLC systems the noise effect needs to be minimized. This implies that a different approach must be considered. From the background on RF technology we know the bandwidth

spreading can minimize the effect of noise on the channel. In the next section, this issue is discussed in detail using DSSS technique.

# Section 4

## 4. Direct Sequence Spread Spectrum

#### 4.1 Introduction

In a direct sequence spread spectrum communication system [11], the spectrum spreading is accomplished before transmission through the use of a spreading code that is independent of the data sequence. The same spreading code is used in the receiver (operating in synchronism with the transmitter) to de-spread the received signal so that the original data may be recovered. The information-bearing signal is multiplied by a spreading code so that each information bit is divided into a number of small time increments. These small time increments are commonly referred to as chips. In this process the narrow bandwidth of the information-bearing signal is spread over a wide bandwidth with a factor L which equals the length of the spreading sequence.

Spread-spectrum communication techniques may be very useful in solving different communication problems. The amount of performance improvement that is achieved through the use of spread-spectrum, relative to an unspread system, is described in terms of a so-called processing gain (PG) factor. In spread-spectrum modulation an information-bearing signal is transformed into a transmission signal with a much larger bandwidth. The transformation is achieved by encoding (spreading) the information bearing signal with a spreading code signal. This process spreads the power of the original data signal over a much broader bandwidth, resulting in a lower power spectral density than the unspread information signal. When the spectral density of the resultant spread spectrum signal starts to merge with or fall below the background noise level, the DSSS communication signal enters a state of low visibility or

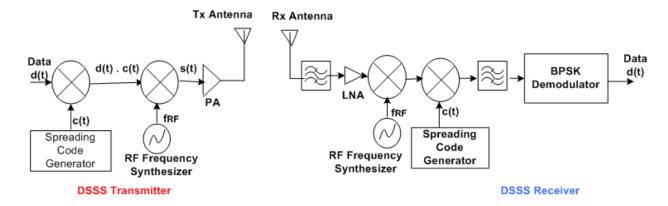

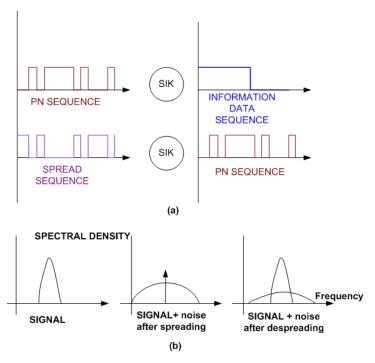

Fig. 5(a): Conceptual Block Diagram of DSSS

**Fig. 5(b):** Conceptual Block Diagram of DSSS Transmitter Receiver

perception, making it hard to locate or intercept. This communication mode is commonly referred to as low probability of interception (LPI), and offers a form of security, which has previously been exploited for military applications, but are presently increasingly applied to a host of commercial applications. The PG of the spread-spectrum system can be defined as the ratio of transmission bandwidth to information bandwidth:

$$PG = \frac{B_T}{B_B} = \frac{T_b}{T_c} = \frac{R_c}{R_b} = L \tag{36}$$

where  $B_T$  is the transmission bandwidth,  $B_B$  is the bandwidth of information-bearing signal,  $T_b$  is the one bit period of the data signal,  $T_c$  is the one chip period of the spreading code,  $R_c$  is the chip rate of the spreading sequence,  $R_b$  is the bit rate of the data signal and L is the length of the spreading code.

The receiver correlates the received signal with a synchronously generated replica of the spreading code signal to recover the original information-bearing signal. This implies that the receiver must know the spreading sequence or code used to spread or modulate the data.

The basic spreading process in a direct sequence spread-spectrum system is illustrated in the conceptual block diagram of a DSSS transmitter and receiver in Fig. 18a and Fig. 18b. The information-bearing signal d(t) is multiplied by the spreading code c(t) and modulated onto a RF carrier frequency to obtain a final spread output signal s(t);

$$s(t) = d(t)c(t)cos(2\pi f_{RF}t)$$

(37)

where  $f_{RF}$  is the carrier frequency.

The incoming signal is received by the RF front-end consisting of basically a noise reject band pass filter, a low noise amplifier (LNA) and a mixer to down-convert the RF signal to intermediate frequency (IF). This DSSS IF signal is de-spread and band pass filtered, where after the de-spread signal is demodulated by means of a binary phase shift keying (BPSK)

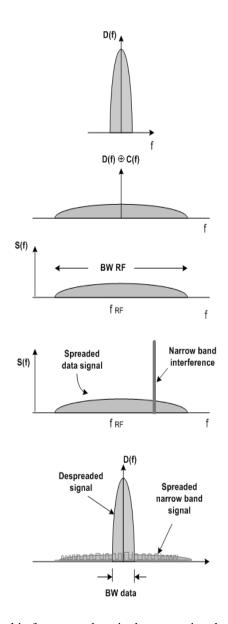

demodulator to recover the original information-bearing signal d(t). The process of spreading and dispreading signal in frequency domain is shown in Fig. 6.

A DSSS system employing complex spreading sequences may include several advantages, such as offering perfectly constant envelope output signal including the possibility to generate a single side band (SSB) DSSS signal with theoretically up to 6dB more PG than offered by conventional double side band (DSB) system while exhibiting comparable auto and improved cross correlation properties compared to any other binary (DSSS) presently employed [11].

Fig.6: Signal in frequency domain demonstrating the spreading-

#### 4.2 DSSS Modulation in VLC System

#### 4.2.1 Introduction

Spread spectrum modulation technique can minimize the affect of interference according to the processing gain advantage. While the additional bandwidth requirement of a spread-spectrum modulation scheme reduces the system bandwidth efficiency, the processing gain of the spread spectrum technique helps to combat artificial light interference effects and multipath dispersion (if any) without the need for extra circuitry such as equalizers. A form of DSSS technique called sequence inverse-keying (SIK) [12] is able to combat these two important channel impairments and is a potential modulation format for the low rate VLC in the outdoor.

#### 4.2.2 Basic Principle

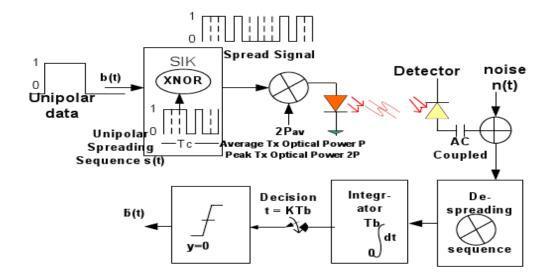

The use of DSSS to an OW system is based on the basic principle of unipolar-bipolar correlation [13]. In radio systems, DSSS uses bipolar spreading sequences that cannot be used as such in the all-positive (unipolar) optical medium. The technique called unipolar-bipolar sequencing that allows the same spreading codes of radio systems to be used in optical systems are employed instead. Unipolar-bipolar sequencing, which involves transmission of a unipolar spreading sequence and correlation with a bipolar version of the same spreading sequence, preserves the correlation properties of bipolar-bipolar sequencing although with the introduction of a fixed dc offset.

At the transmitter, a unipolar spreading sequence is modulated by binary data such that the sequence is transmitted for a binary '1' while the inverse (complement) sequence is transmitted for a binary '0'. This type of modulation is called as SIK. The resulting spread spectrum signal, which uses a rectangular NRZ chip waveform, intensity modulates the visible light source (LEDs), by on-off keying. At the receiver, the optical signal is detected and processed. The spread signal may be AC coupled prior to de-spreading in order to remove the unwanted DC signal components introduced by the optical channel. AC coupling does not alter the correlation properties of the spreading sequence, thus de-spreading can use the bipolar version of the unipolar spreading sequence. For single correlator detection, the de-spread signal is integrated over the data bit period  $T_b$  and sampled at intervals of  $t = T_b$ . The sample value at the correlator output is zero-threshold detected such that either a positive or a negative sample results a binary '1' or '0' estimate of the transmitted data bit, respectively.

Fig .7: SIK Modulation for VLC

#### 4.2.3 Sequence Inverse Keying Modulator

Fig. 7 shows the schematic diagram of the transmitter and receiver of SIK system. The modulator part basically performs digital operation of X-NOR where incoming data bit is modulated by a pseudo noise random data of many times higher bit rate than the data bit. Thus, the transmitted data is said to be spread. A similar operation is needed at the receiver to despread the incoming sequence from channel. For better understanding, frequency domain analysis is presented followed by equivalent time domain analysis.

### 4.2.3.1 Frequency Domain Analysis

A frequency domain analysis of the operation of DSSS SIK is presented to give a better understanding. Let us consider:

- $\triangleright$  Information data: B(t)

- $\triangleright$  Unipolar spreading signal: s(t)

- > Chip period: *Tc*

- $\triangleright$  Impulse response of the channel: h(t)

- $\triangleright$  Interference due to light sources: f(t)

The pseudo noise (PN) generator s(t) may be written as:

$$s(t) = \sum_{i=0}^{N-1} a(i)p(t - iT_C); \qquad a(i)\epsilon[1,0]$$

(38)

where a(i) is the unipolar PN sequence, p(t) is the pulse shape, N is the code length, so that each bit has N chips (N \*  $T_c = T_b$ ) with  $T_b$  is the period of data bit. B(t) is combined with spreading sequence s(t) to spread the transmitted signal which is given as:

$$x(t) = \sum_{j=-\infty}^{\infty} \sqrt{\rho} \ B(t) \oplus s(t - jT)$$

(39)

where  $\rho$  is the energy of a pulse and ' $\oplus$ ' is the SIK operator i.e. PN sequence is transmitted for data '1' and inverse of PN sequence for data '0'. The PSD of x(t) is given as:

$$\Phi_{\mathcal{X}}(f) = \frac{1}{T} |S(f)|^2 \Phi_b(f) \tag{40}$$

where S(f) is the Fourier Transform (FT) of s(t) and  $\Phi_b(f)$  is the PSD of the information data bits B(t). Before de-spreading, the received signal r(t) is:

$$r(t) = x(t) * h(t) + n(t) + f(t)$$

(41)

The PSD of the signal r(t) is given as:

$$\Phi_r(f) = \Phi_x(f)|H(f)|^2 + \Phi_n(f) + \Phi_f(f)$$

(42)

where,

H(f) = the F.T of the channel impulse response, h(t)

$\Phi_n(f)$  = the PSD of the Gaussian Noise,

$\Phi_f(f)$  = the PSD of interference caused by light sources.

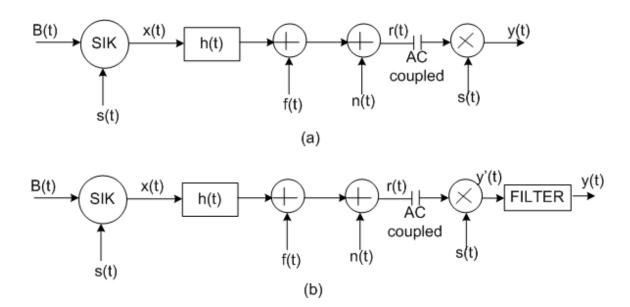

We consider first, the light source as artificial consisting of mainly incandescent and fluorescent lamps. Therefore, the PSD of the output signal y(t) after de-spreading and without filter as in Fig. 8a is given as:

$$\Phi_{y}(f) = \frac{1}{T} |S(f)|^{2} \{ \Phi_{x}(f) |H(f)|^{2} + \Phi_{n}(f) + \Phi_{f}(f) \}$$

(43)

And the desired signal power is therefore,

$$P_{req} = \frac{R^2}{T^2} \int_{-\infty}^{\infty} |S(f)|^4 |H(f)|^2 \Phi_b(f) df$$

(44)

The Gaussian distributed noise power is given as:

$$P_{awgn} = \frac{R^2}{T} \int_{-\infty}^{\infty} |S(f)|^2 \Phi_n(f) df$$

(45)

where,

$$\int_{-\infty}^{\infty} \Phi_n(f) df = 2qR P_{inf} B_n \tag{46}$$

with q is the electronic charge, R being the responsivity of the photo diode receiver,  $P_{inf}$  is the interference power (optical background) and  $B_n$  is the bandwidth.

The light interference power is given as:

$$P_{inf} = \frac{R^2}{T} \int_{-\infty}^{\infty} |S(f)|^2 \Phi_f(f) df \tag{47}$$

The light interference power can be calculated (for example, using Moreira's model) as:

$$\int_{-\infty}^{\infty} \Phi_f(f) df = \frac{R^2 P_f^2}{N^2} \left\{ \frac{1}{2K_1^2} \sum_{i=1}^{20} (a_i^2 + b_i^2) + \frac{1}{2K_2^2} \sum_{j=1}^{11} (d_j^2 + d_0^2) \right\}$$

(48)

where  $P_f$  is the average optical power of interference signal and N is the spreading gain. Therefore, the signal to interference ratio is given as:

$$SINR = \frac{P_{req}}{P_{inf} + P_{awgn}} \tag{49}$$

The operation of DSSS modulation and demodulation and the spectral results are shown in Fig. 9. However, when a filter is added (as shown in Fig. 8b) to the output before passing it through decision making device (integrator, not shown), the PSD can be given as:

$$\Phi_{yF} = \frac{1}{\tau} |S(f)|^2 |H'(f)| \left\{ \Phi_x(f) |H(f)|^2 + \Phi_n(f) + \Phi_f(f) \right\}$$

(50)

where the H'(f) is the response of the filter.

A low pass digital filter is included so that only signal of interest is allowed. This is expected to enhance the performance of DSSS receiver.

Fig. 8: a): DSSS SIK System b) DSSS SIK System with Filter

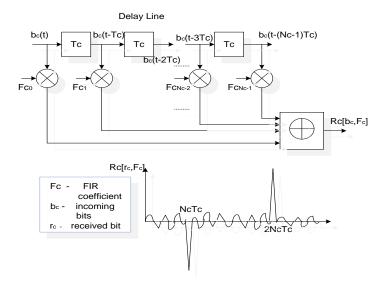

Fig.9: a): DSSS SIK Modulation and Demodulation Operation; b) Spectral Density Illustration

#### 4.2.3.2 The Corresponding Time Domain Analysis

The unipolar binary data b(t) from traffic information source given as:

$$b(t) = \sum_{k=-\infty}^{\infty} b_k(t)$$

(51)

for  $b_k \in \{0,1: -\infty \le k \le \infty\}$ .  $b_k$  is XNORed with unipolar spreading sequence s(t):

$$s(t) = \sum_{n=0}^{N-1} s_n(t)$$

(52)

where,  $s_n \in \{0,1: n = 0,1, .....N-1\}$ , where N is the sequence length,  $T_c$  is the chip duration and  $T_b = NT_c$ . The duration of N chips in one period of the spreading sequence is equal to the bit duration. In fact, the XNOR function realizes the SIK modulation format. The spread data is then convolved with the transmit pulse wave [xt(t)] and the resulting signal is used to intensity modulate the LED light source. The optical signal is characterized by an average optical power P and a peak pulse power P. The light propagates through free space channel, get added with noise and then detected by photodiode. The photodiode responsivity is given by (R=A/W). The detected photocurrent for the LoS case can be given as:

$$r_n(t) = 2RP_{av}b(t) \oplus s(t) + f(t) + n(t)$$

(53)

where,  $P_{av}$ ; is the mean optical power of the LOS signal impinging the photocurrent, f(t); is the interfering signal at the output of the photodiode due to ambient light n(t); is the channel noise process (including amplifier thermal noise and shot noise) and considering additive white Gaussian noise with power spectral density  $N_0$ . The operator  $' \oplus '$  is the SIK function given as:

$$b(t) \oplus s(t) = \frac{\left[1 + b'(t)s'(t)\right]}{2} \tag{54}$$

where, b'(t) and s'(t) are the bipolar version of b(t) and s(t).

The f(t) as discussed in [14] has the DC component  $R.P_f$  and AC component  $R.P_f$  f'(t) with P<sub>f</sub> as the average interfering power from other sources of light. Substituting these values in received signal results in:

$$r_x(t) = 2RP_{av}b(t) s(t) + RP_f + RP_f f'(t) + n(t)$$

(55)

This received signal is AC coupled and so the DC term will be removed. The signal is then given as:

$$r_n(t) = 2RP_{av}b(t)s(t) + RP_ff'(t) + n(t)$$

(56)

This signal is now multiplied by s(t) and then integrated over one data bit duration and threshold detected which is set to zero. Therefore, the correlator output becomes:

$$z(T_b) = \frac{1}{T_b} \int_0^{T_b} RP_{av} b(t) s(t) s(t) dt + \frac{1}{T_b} \int_0^{T_b} RP_f f'(t) s(t) dt + \frac{1}{T_b} \int_0^{T_b} n(t) s(t)$$

$$= bRP_{av} + \frac{RP_f}{T_b} \int_0^{T_b} f'(t) s(t) dt + n(T_b)$$

(57)

$$z(T_b) = bRP_{av} + \frac{RP_f}{T_b} f'(T_b) + n(T_b)$$

(58)

where,  $b \in \{1, -1\}$  denotes the present data bit which is desired signal term. The second term is the interference by light while the third term is the noise.

#### 4.3 SNR and BER of SIK Modulator with AWGN

Considering only AWGN channel, the BER from (58) can be written as:

$$BER_{SIK} = Q\left(\frac{RP_{av}}{\sqrt{N_0R_b}}\right) \tag{59}$$

That is, the performance of SIK in an AWGN channel has the same theoretical performance as OOK.

#### 4.4 SNR and BER of SIK Modulator in the Presence of External Noise

The mean  $(\mu_z)$  and the variance  $\sigma_z^2$  of  $z(T_b)$ , at the correlator output from equation (58) can be given as:

$$\mu_c = bRP_{av} \tag{60}$$

$$\sigma_z^2 = \left(\frac{\sigma_m R P_f}{N}\right)^2 + \frac{N_0}{T_b} \tag{61}$$

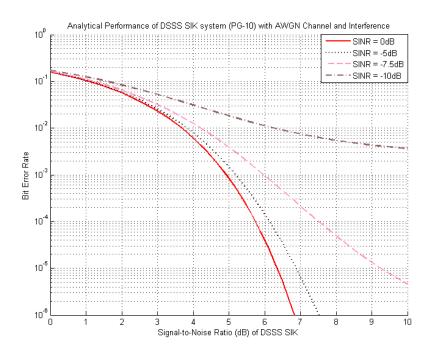

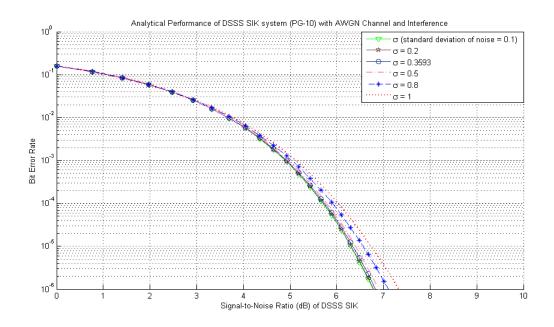

where  $\sigma_m$  is the standard deviation of f'(t) and the same as the RMS value. The value given in [15] is around 0.3593. The SNR at the output of correlator is given as:

$$SNR = \frac{R^2 P_{av}^2}{\left(\frac{\sigma_m R P_f}{N}\right)^2 + N_0 R_b} \tag{62}$$

Or

$$SNR = \frac{1}{\left(\frac{\sigma_m P_f}{NP}\right)^2 + \left(\frac{\sqrt{N_0 R_b}}{P}\right)^2} \tag{63}$$

where P is the optical power. If  $\sqrt{(N_0R_b)} = R.P_n$  denote a noise equivalent optical power. The second term in the denominator can also be written as  $1/SNR_{opt}$  which is the optical signal-to-noise power ratio. Thus equation (62) can be written as:

$$SNR = \frac{1}{\left(\frac{\sigma_m P_f}{NP}\right)^2 + \left(\frac{1}{SNR_{out}}\right)^2} \tag{64}$$

We also define signal-to-interference ratio (SINR) as:

$$SINR = \frac{P}{P_f} \tag{65}$$

Substituting this in above equation results in:

$$SNR = \frac{1}{\left(\frac{\sigma_m}{N.SINR}\right)^2 + \left(\frac{1}{SNR_{opt}}\right)^2} \tag{66}$$

when we assume data bit '+1' and '-1' to be equiprobable, the BER will be:

$$BER = Q[\sqrt{(SNR)}] \tag{67}$$

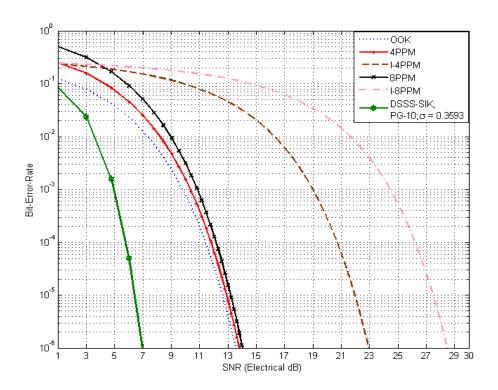

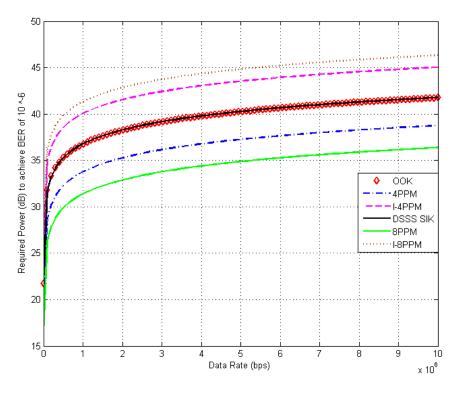

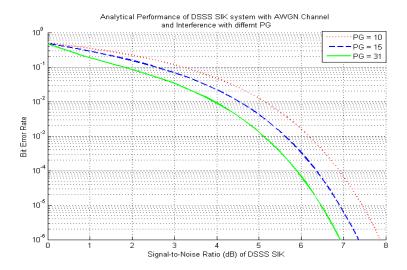

The performance parameters in terms of BER and SNR, data rate and power requirements are analyzed and simulated. The simulation results show that DSSS SIK modulation is an effective method for countering the effect of noise, especially interference noise from the artificial light sources. They also show that increase in PG improves the system's performance. However, more PG implies a lengthy pseudo noise (PN) sequence which limits the data rate. Therefore, a compromise value of PG between 10-31 can be used.

The following sections present description of system models using Matlab/Simulink and their validity through simulation.

#### 4.5 Matlab Simulink Model For DSSS SIK

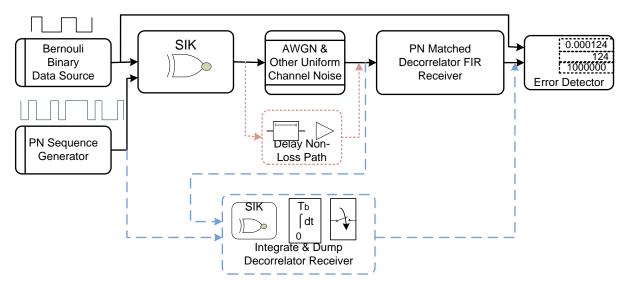

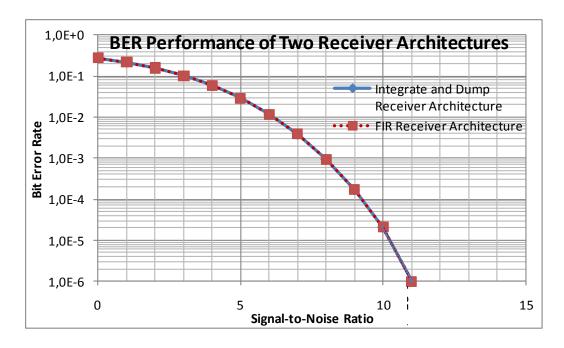

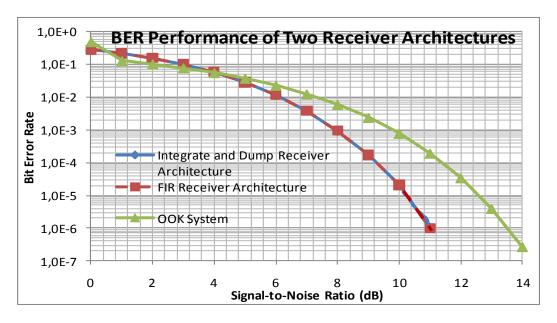

As simulation exercise, Matlab models are developed in Simulink. We have developed two decorrelator receiver architectures for dispreading spread spectrum signals: integrate and dump filter, also called as active correlator and PN matched filter. They are optimum from a

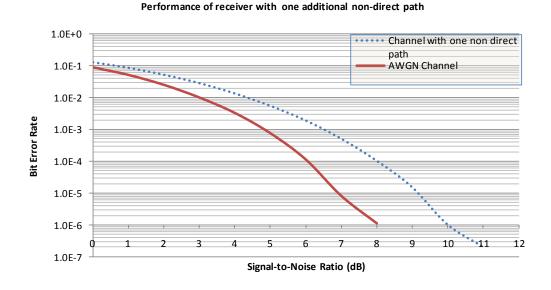

SNR point of view. The motivations behind the study are: (i) to compare the performance of DSSS SIK using both of these receiver architectures, and (ii) implement the architecture that is most suitable in FPGA. In addition, we have also introduced a delay network in the channel to simulate simultaneous reception of a strong reflected or non-direct ray. The gain of this secondary ray is set to one fourth of the direct ray. In the study, it is observed that as the gain of the secondary ray increases, the BER performance decreases. Behavior of both the architectures because of secondary non-LoS ray is found to be the same.

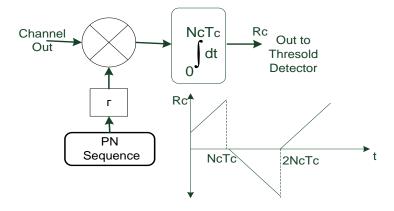

#### 4.5.1 Integrate and Dump Decorrelator Receiver

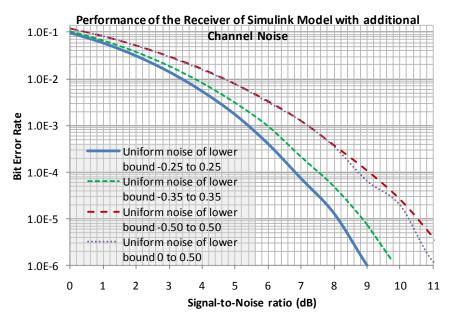

This receiver operates correctly only when the local PN sequence is accurately matched and correctly timed, with respect to the spreading code within the received signal. Synchronization becomes difficult too and it is very slow process. Fig.10 shows the basic structure of integrate and dump filter decorrelator. The Simulink model structure is shown in Fig.11. The receiver block connected by dashed lines are the integrate and dump decorrelator while the receiver block connected by solid lines shows the discrete FIR based PN matched decorrelator. Different functionalities were achieved using different blocks. Here we have considered both the conditions; DSSS SIK with AWGN channel only and with additional noise in the model. The model consists of Bernouli binary generator as data source, PN sequence generator as spreading code, SIK subsystem to obtain the SIK function, data format converters, AWGN channel, uniform noise generator, Integrate and Dump filter, threshold detector and error detection block.

The integrate and dump block creates a cumulative sum of the discrete-time input signal, while resetting the sum to zero according to a fixed schedule. When simulation begins, the block discards the number of samples specified in the Offset parameter. After this initial period, the

Fig. 10: Active Decorrelator Receiver

block sums the input signal along columns and resets the sum to zero every N input samples, where N is the Integration period (one data bit) parameter value. The reset occurs after the block produces its output at that time step. This blocks also results in a delay of one bit. The parameters setting are shown in Table 1.

**TABLE 1:** Simulink Model Simulation Parameter Settings

| Block                            | Parameter(s) and Value                                                                                                                                 |  |  |

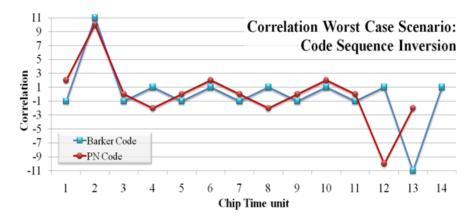

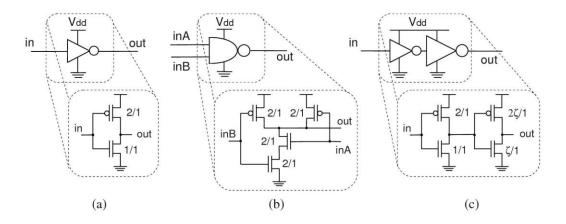

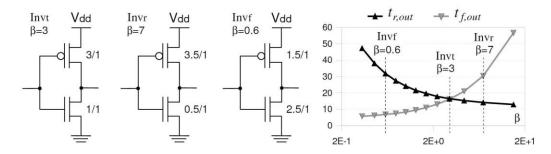

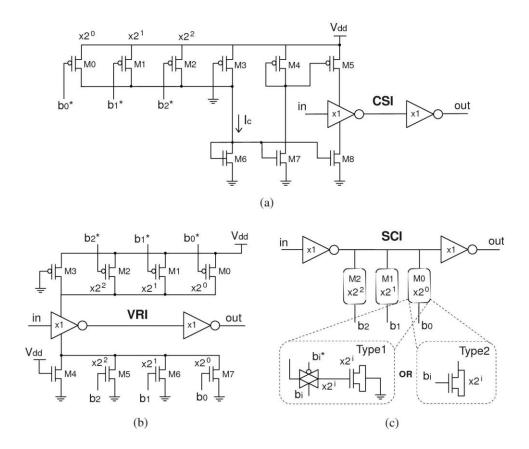

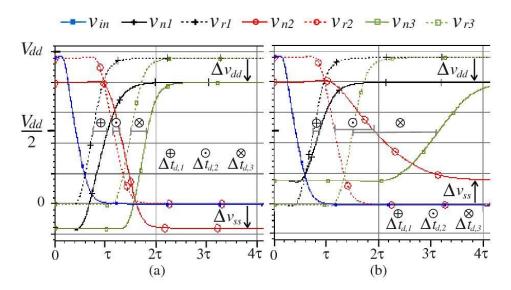

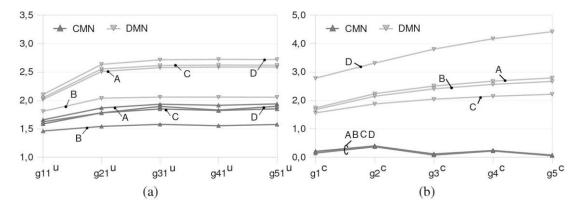

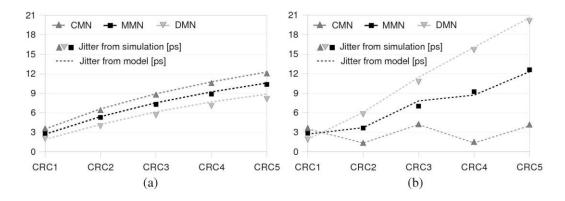

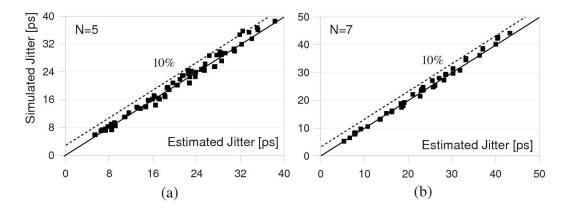

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|