Active and Passive Elec. Comp., 1998, Vol. 20, pp. 215-224 Reprints available directly from the publisher Photocopying permitted by license only © 1998 OPA (Overseas Publishers Association) Amsterdam B.V. Published under license under the Gordon and Breach Science Publishers imprint. Printed in India.

# FABRICATION AND CHARACTERIZATION OF MULTILAYER CAPACITORS BURIED IN A LOW TEMPERATURE CO-FIRED CERAMIC SUBSTRATE

## Y. C. CHAN\* and G. Y. LI

Department of Electronic Engineering, City University of Hong Kong, 83 Tat Chee Avenue, Kowloon, Hong Kong

(Received 25 September 1997; In final form 3 November 1997)

Multilayer ceramic capacitors designed to be embedded in a low temperature co-fired ceramic substrate have been successfully fabricated. Low and high value capacitors were respectively embedded in the low K multilayer substrate and high K dielectric layer. The buried capacitor has a capacitance density range (1 kHz) from about 220 pF/cm<sup>2</sup> to 30 nF/cm<sup>2</sup>. The design took material compatibility and shrinkage characteristics specifically into account. The effects of heating rate and peak temperature holding time on the densification of the laminate were studied. The scanning electron micrograph revealed no evident cracking in the fired components. The electrical properties of the buried capacitors such as dissipation factor, insulation resistance and breakdown voltage were studied and found to be good for device application. The temperature dependence of the dissipation factor and coefficient of capacitance for the buried capacitor was also studied.

Keywords: Capacitor; embedded; low temperature co-fired ceramic

### **INTRODUCTION**

The current trend in the microelectronics industry is to reduce the overall size of electronic packages. This means that more complex packages have to be made with higher interconnect density, smaller components but with the same or greater reliability. Low temperature co-fired ceramic (LTCC) technology has the ability to integrate passive

<sup>\*</sup>Corresponding author.

components such as resistors, capacitors and inductors into a monolithic package [1-4], thereby freeing valuable circuit surface area for active components. Additional advantages include reducing failure associated with surface mounting and minimising inductance through closer placement of capacitors to the IC. Another benefit, which has evolved to become much more important to EMC engineers, is its ability to reduce high frequency power distribution noise and radiated and/or conducted emissions [5].

Sintering of LTCC packages containing various passive components is very complex and not fully understood with little information published in the literature. The major technical problems for the development of such components are shrinkage match between high Kdielectric and low K substrate and thermal expansion. Due to the complexity of the fabrication process and materials interaction during firing, it is a challenging task to develop embedded cofireable passive components. This paper reports the development of cofireable embedded capacitors for a LTCC system.

### DEVELOPMENT

Our co-fired materials system for embedded capacitors consists of three components: the high K capacitor dielectric, the capacitor electrode material and the substrate tape. Designs for embedded capacitors must include compatibility of system materials. With special respect to shrinkage characteristics, thermal expansion, and chemical compatibility. The sintering temperatures and thermal expansion coefficients of high K materials are generally higher than those of standard LTCC substrate materials. During firing, differential shrinkage rates of the system materials result in distortion of the fired part. System materials must design to shrink at similar temperatures, rates and magnitudes in order to obtain an acceptable surface topography. To meet the above requirements, DuPont 704 BT tape was used for compatibility with both the DuPont 951 Low Temperature Co-fireable Ceramic (LTCC) Green Tape<sup>TM</sup> System and the Dupont silver conductor system.

The main composition (analyzed by Energy Dispersive X-ray) and fired properties of DuPont 951 tape is summarised in Table I. The

|                          | SiO <sub>2</sub>                | 31.3 wt%           |

|--------------------------|---------------------------------|--------------------|

| Main Composition         | PbO                             | 11.9               |

| (Relative concentration) | K <sub>2</sub> O                | 1.1                |

|                          | CaO                             | 5.4                |

|                          | $Al_2O_3$                       | 50.3               |

|                          | Dielectric Constant (@ 10 MHz)  | 7.8                |

|                          | Dissipation Factor (@ 10 MHz)   | 0.15%              |

|                          | Insulation Resistance (@ 100 V) | $> 10^{12} \Omega$ |

| Fired Properties         | Thermal expansion (ppm/°C)      | 5.8                |

| -                        | Density (g/cm)                  | 3.1                |

|                          | Thermal conductivity (W/m.k)    | 3.0                |

|                          | Flexural Strength (MPa)         | 320                |

| TABLE I | Main comp | osition and | properties | of DuPont 951 | LTCC substrate |

|---------|-----------|-------------|------------|---------------|----------------|

|         |           |             |            |               |                |

|                        | TABLE II | Silver conductor system |                  |

|------------------------|----------|-------------------------|------------------|

| Conductors             |          | Silver                  | Silver/Palladium |

| Inner layer (Co-fired) |          | 6142D                   |                  |

| Via-fill(Co-fired)     |          | 6141D                   |                  |

| Top layer (Co-fired)   |          |                         | 6146D            |

| Top layer (Post-fired) |          |                         | 6134D            |

conductor system is shown in Table II. For the conductor system, all pastes consist of four generic ingredients: the functional conductor, a solvent a temporary binder, and a permanent binder. Ag and Ag/Pd serve as internal and fired-on functional conductor. The glasses or fluxes are used as inorganic binders. Their main functions are to enhance the adhesion between the metal and ceramic, and to provide lower sintering temperatures for the metal, and control (or usually minimize) the metal sintering shrinkage in firing and thermal expansion mismatch. Adhesion is not often a problem for internal conductors. The purpose of an inorganic binder is to minimize the shrinkage mismatch. A polymeric and a solvent is used as vehicle. The chief function of the vehicle is to maintain the inorganic particulates in a desirable state of dispersion and to allow easy transfer of the paste spreading. The composition of 704BT is based on BaTiO<sub>3</sub>, which provides the high dielectric constant. Addition of a frit constituent to the high K dielectric formula provides shrinkage compatibility with 951 Green Tape<sup>TM</sup>. The frit does not result in the dielectric constant degradation.

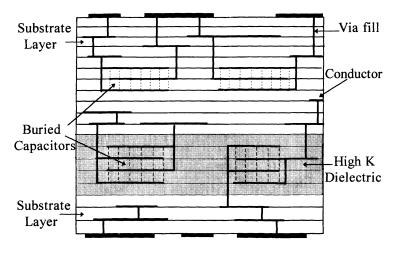

FIGURE 1 Structure of multilayer ceramic substrate with embedded capacitors.

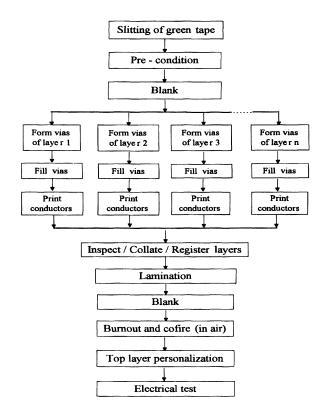

The structure of multilayer ceramic substrate with buried capacitor is shown in Figure 1. A high K tape sheet with screen printed electrodes is sandwiched between low K LTCC tape sheets forming the high-value embedded capacitors layer. Electrodes are directly printed on the low K substrate layer to form the low-value buried capacitors. In this work, 4 electrodes have been designed for both high-value and low-value test capacitors. The manufacturing process is illustrated in Figure 2. This process is similar to MLC manufacturing [6]: i.e., the unfired or green ceramic sheets are punched with via holes, screened with conductor, stacked with excellent precision, then laminated into a monolithic three-dimensional structure, and fired in a furnace. The ceramic and the conductor are both sintered simultaneously in the same fired cycle. Many chemical and physical processes occur as the parts traverses the time-temperature profile. Minimizing the sintering shrinkage mismatch between the conductor, ceramic substrate and high K dielectric is very important for eliminating process flaws, such as delaminations bowing, blistering, and crazing. The shrinkage mismatch may include the mismatch at the onset of sintering temperature, the densification rate, and the total shrinkage between conductor, ceramic substrate and dielectric. Usually the metal film

FIGURE 2 Manufacturing process of multilayer ceramic substrate with embedded capacitors.

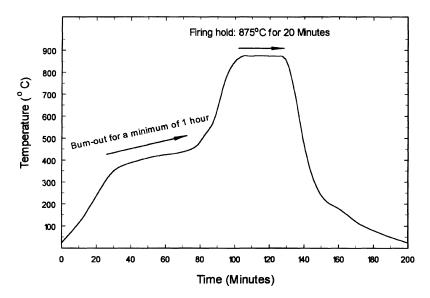

starts to sinter at low temperatures, and the densification rapidly reaches a considerable extent. However, the ceramic tape and dielectric generally sinter at higher temperatures, and most shrinkage occurs at soaking temperatures. Therefore, the temperature rate controlling is very important. During heating, the majority of the solvent evaporates in the temperature range from about 50 to  $200^{\circ}$ C. Organic burnout takes place at temperature between  $200^{\circ}$ C and  $500^{\circ}$ C. To remove organics completely and minimize the shrinkage mismatch, our studies show that the parts must be soaked within this temperature range for a minimum of one hour. The peak sintering temperature (densification) was  $875^{\circ}$ C. Except for the particle size (or surface area of the

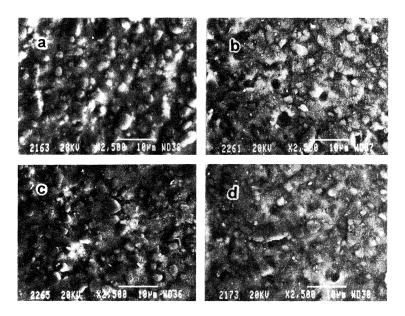

FIGURE 3 Microstructure of fired ceramic substrate for different hold time: a) 0 minute; b) 20 minutes; c) 60 minutes; d) 240 minutes.

powders), the hold time of the peak sintering temperature is a most important factor to get the proper densification of the laminates. Generally, the longer the hold time the denser the fired ceramic becomes. Figure 3 shows the microstructure of fired 951 tape for different hold time of peak sintering temperature. Considering the necessary densification and sintering characteristics of the conductor, the range of hold time from 15 to 20 minutes is appropriate. The firing profile is shown in Figure 4. After co-firing is completed, the electrical properties and microstructure of the sample are studied.

## PERFORMANCE OF BURIED CAPACITORS

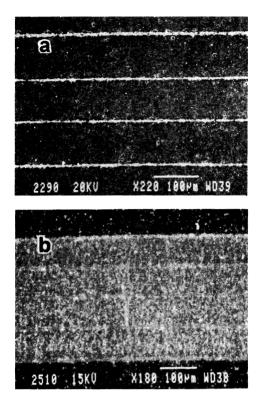

The microstructure of the embedded capacitors was studied by Scanning Electron Microscopy (SEM). Figure 5 shows the microstructure of the cross sections of high-value and low-value buried

FIGURE 4 Typical firing profile used to fire buried capacitors.

capacitors. No cracking and delamination are evident in the low K substrate, high K layer and conductor layer. The electrical properties of the embedded capacitors were measured by using an HP 4194A Impedance/Gain Phase Analyzer and an HP 4284A LCR meter. Typical electrical properties are summarized in Table III. The results show that the embedded capacitors have a good dissipation factor, insulation resistance and breakdown voltage values. No evident structural distortion is found due to the presence of embedded capacitors.

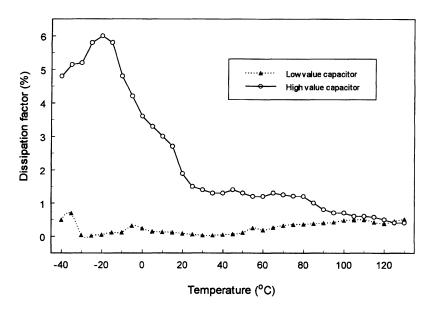

The temperature dependence of the dissipation factor is shown in Figure 6. The dissipation factor of the low value capacitor is about 0.5%. For the high value capacitor, dissipation factor is within 1.5% when the temperature is above room temperature. When the temperature drops, the dissipation factor goes up and encounter a turning point at a temperature of about  $-20^{\circ}$ C. The dissipation factor has a Maximum of about 6%. The temperature coefficient of capacitance (TCC) for the embedded capacitors is within X7R requirements, which corresponds to within  $\pm$  15% of the room temperature capacitance value between  $-50^{\circ}$ C and  $+125^{\circ}$ C.

FIGURE 5 Microstructure of cross sections of embedded capacitors: a) low-value embedded capacitor; b) High-value embedded capacitor: the dark regions above and below are the low K substrate, the dark region between is the high K dielectric layer.

| Dimensions and characteristics   | High-value<br>capacitor     | Low-value<br>capacitor      |

|----------------------------------|-----------------------------|-----------------------------|

| Area of electrode                | 1.44 cm×1.44 cm             | 1.3 cm×1.3 cm               |

| Number of electrodes             | 4                           | 4                           |

| Capacitance density<br>(1 kHz)   | $30 \text{ nF/cm}^2$        | $215 \text{ pF/cm}^2$       |

| Dissipation factor               | 1.5%                        | 0.5%                        |

| (1 kHz)<br>Insulation resistance | $1.7 \times 10^{11} \Omega$ | $1.9 \times 10^{12} \Omega$ |

| (100 V DC)                       |                             |                             |

| Breakdown voltage                | > 1000 V                    | > 1000 V                    |

TABLE III Dimension and characteristics of embedded capacitors

FIGURE 6 Temperature dependence of dissipation factor of buried capacitor.

#### CONCLUSIONS

Buried Capacitors have been successfully developed for integration into a low temperature cofired ceramic substrate, capable of increasing the available space for integrated circuits and improving circuit board performance. The design took material compatibility and shrinkage characteristics specifically into account. The effects of process parameters such as heating rate and peak temperature holding time on the densification of the laminate were studied. The laminates must be soaked at temperature between 200°C and 500°C for a minimum of one hour to remove organics completely and minimize the shrinkage mismatch. The range of hold time of peak sintering temperature from 15 to 20 minutes is appropriate. The embedded capacitors exhibit no evident microstructural defects, and have capacitance densities from about  $220 \,\mathrm{pF/cm^2}$  to  $30 \,\mathrm{nF/cm^2}$ , with temperature characteristics within X7R requirements, and have good dissipation factors (< 2%), insulation resistances (> $1.7 \times 10^{11} \Omega$ ), and breakdown voltages (> 1000V).

#### **Acknowledgements**

The authors would like to acknowledge the financial support of University Grants Council (project no. 9040106) for this work.

#### References

- John L. Sprague (1990). "Multilayer ceramic packaging alternatives", IEEE Transactions on Components, Hybrid, and Manufacturing Technology, 13(2), 390-396.

- [2] Goldberg, Lee (1995). "Multilayer, Low-fire, ceramic substrates sport embedded components, new packaging solutions", *Electronic Design*, 34, pp. 40-42.

[3] Yuhaku, S., Hakotani, Y., Nakatani, S. and Tsukamoto, M. (1993). "Multilayer

- [3] Yuhaku, S., Hakotani, Y., Nakatani, S. and Tsukamoto, M. (1993). "Multilayer ceramic substrate with buried capacitors", *National Technical Report*, 39(2), 197– 203.

- [4] Alexander, J. (1993). "Cofirable resistors for low temperature ceramic tape", Proceedings of the SPIE - The International for Optical Engineering, 2105, pp. 204-208.

- [5] Mason, Hu and James, Howard (1995). "Distributed and discrete capacitors EMI performance comparison", Proceedings of the Technical Program, NEPCON West '95, 2, pp. 756-765.

- [6] Young, W. S. and Knickerboker, S. H. "Multilayer ceramic technology", in Ceramic Materials for Electronics, Properties, and Application, second edition, New York, Marcel Dekker Inc.

Rotating Machinery

Journal of Sensors

International Journal of Distributed Sensor Networks

Journal of Electrical and Computer Engineering

International Journal of

Aerospace

Engineering

International Journal of Chemical Engineering

Advances in Civil Engineering

International Journal of Antennas and Propagation

Hindawi

Submit your manuscripts at http://www.hindawi.com

Active and Passive Electronic Components

Shock and Vibration

Advances in Acoustics and Vibration