# Research Article A Statistic-Based Calibration Method for TIADC System

### Kuojun Yang,<sup>1,2</sup> Shulin Tian,<sup>1</sup> Peng Ye,<sup>1</sup> Peng Zhang,<sup>1</sup> and Yuanjin Zheng<sup>2</sup>

<sup>1</sup>School of Automation Engineering, University of Electronic Science and Technology of China, Chengdu 611731, China <sup>2</sup>School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798

Correspondence should be addressed to Kuojun Yang; kuojunyang@gmail.com

Received 7 July 2014; Accepted 22 December 2014

Academic Editor: Marcelo M. Cavalcanti

Copyright © 2015 Kuojun Yang et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Time-interleaved technique is widely used to increase the sampling rate of analog-to-digital converter (ADC). However, the channel mismatches degrade the performance of time-interleaved ADC (TIADC). Therefore, a statistic-based calibration method for TIADC is proposed in this paper. The average value of sampling points is utilized to calculate offset error, and the summation of sampling points is used to calculate gain error. After offset and gain error are obtained, they are calibrated by offset and gain adjustment elements in ADC. Timing skew is calibrated by an iterative method. The product of sampling points of two adjacent subchannels is used as a metric for calibration. The proposed method is employed to calibrate mismatches in a four-channel 5 GS/s TIADC system. Simulation results show that the proposed method can estimate mismatches accurately in a wide frequency range. It is also proved that an accurate estimation can be obtained even if the signal noise ratio (SNR) of input signal is 20 dB. Furthermore, the results obtained from a real four-channel 5 GS/s TIADC system demonstrate the effectiveness of the proposed method. We can see that the spectra spurs due to mismatches have been effectively eliminated after calibration.

#### 1. Introduction

In the past decades, modern electronic systems have been revolutionized with fast developing of digital signal processing techniques which offer unprecedented performance and adaptivity. However, the application of DSP is hindered by difficulty in capturing ultrafast signal in high speed electronic systems. The capturing of ultrafast electrical signals is a difficult problem that requires high speed analog-to-digital converters (ADCs). Because of the limitation of fabrication technology, maximum achievable sampling rate of single ADC is limited. Thus, time-interleaved technique proposed by Black and Hodges [1] that results in a time-interleaved ADC (TIADC) is widely used to increase sampling rate.

Ideally, TIADC is formed by M identical parallel ADCs (sub-ADC or channel). Each ADC should have the same gain and offset and should be operating at the equally displaced sampling time instants. However, due to fabrication dispersion, mismatch errors in TIADC system are inevitable. Channel mismatches, such as gain mismatch, offset mismatch, and timing skew mismatch, will result in distortion of sampled

waveform and degrade the performance of TIADC. This has been proved in some contributing works [2–5].

A lot of methods have been proposed to calibrate the mismatches in TIADC [6-20]. Blind calibration techniques have been researched in [7-11]. The attractive advantage of blind calibration is that it does not require a dedicated calibration period. However, blind methods typically require a very high computational cost. In [12], a FFT-based gain and offset error calibration method is proposed, but as we know, many multipliers and other resources are needed in FFT (fast Fourier transform). An adaptive calibration method is proposed in [13], where a reference signal is introduced to identify mismatch parameters. In [14], a synthesis calibration method is proposed. This method can calibrate three mismatches simultaneously, but the calibration process is too complex, and it takes a long time for calibration. Some digital compensation methods for timing skew calibration, such as fractional delay filters [15], multichannel filters [16], Lagrange polynomial interpolation [17], and perfect reconstruction [18], are presented, but timing skew must be estimated before these methods are employed to compensate timing skew.

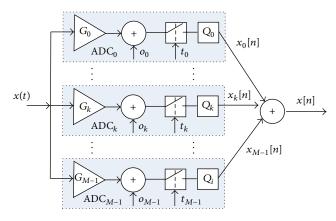

FIGURE 1: Mismatch model of TIADC system.

A code-density based timing skew detection method is proposed in [19], where an auxiliary circuit is added to detect timing skews. A timing skew calibration method based on zero-crossing is proposed in [20], where a zero-crossing detector is added for calibration.

A very easy calibration method is proposed in this paper. Compared with the previous methods, it has the following contributions. Firstly, this method can obtain gain and offset error accurately by simple addition operation. Secondly, the identification of timing skew is not required. This avoids the complicated measurement or estimation of timing skew. Finally, no auxiliary hardware circuits and filters are added for calibration. Thus, the implementation cost is reduced.

This paper is organized as follows. Section 2 gives the model and impact of TIADC mismatch. The calibration method is derived and explained in Section 3. In Section 4, the implementation of proposed calibration method is given. Section 5 shows the simulation results, and experiments results obtained from real four-channel 5 GS/s TIADC system are presented to validate the proposed method. Section 6 is dedicated to the conclusion of our work.

#### 2. Model and Impact of TIADC Mismatch

In this section, to propose the calibration method, the mismatch model of TIADC is depicted first. Then, the output of sub-ADC is derived. Finally, the output spectrum of TIADC is also calculated to demonstrate the impact of TIADC mismatches.

As shown in Figure 1, a TIADC system consists of M parallel ADCs. Each ADC operates with a sampling frequency of  $f_s/M$  and samples the input in turn, so the TIADC system has a sampling frequency of  $f_s$ . For a nonideal TIADC, mismatches are inevitable, each ADC has different gain and offset, and the sampling time intervals between adjacent ADC are not equal. Therefore, in Figure 1, gain, offset, and sampling instant of ADC<sub>k</sub> are denoted by  $G_k$ ,  $O_k$ , and  $t_k$ , respectively.

As we know, for an ideal TIADC, the sampling instant of  $ADC_k$  is

$$t_k = (nM + k)T_s,\tag{1}$$

$\times$  Real samples

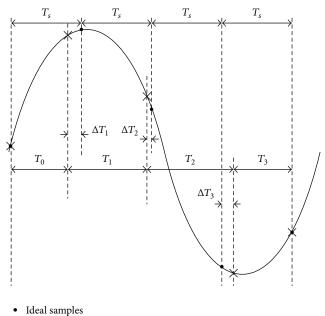

FIGURE 2: Timing skew in a four-channel TIADC.

where  $T_s$  refers to the sample period of TIADC system. Considering the relative timing skew  $\Delta t_k$  in ADC<sub>k</sub>, sampling instant of ADC<sub>k</sub> can be denoted as

$$t_k = \left(nM + k + \Delta t_k\right)T_s.$$

(2)

Thus, for a sinusoidal x(t), the output of TIADC will be

$$\begin{aligned} x_k \left[ n \right] &= G_k \sin \left( 2\pi f_{\rm in} \left( nM + k + \Delta t_k \right) T_s + \phi \right) + O_k \\ &= G_k \sin \left( \omega_0 \left( nM + k + \Delta t_k \right) + \phi \right) + O_k, \end{aligned} \tag{3}$$

where  $f_{in}$  refers to input signal frequency and  $\omega_0$  refers to the normalized angular frequency. In the following part of this paper, we assume that x(t) is a sinusoidal signal, and  $x_k[n]$  shown in (3) will be utilized.

Figure 2 shows the timing skew in a four-channel TIADC. As shown in Figure 2,  $\Delta T_k$  refers to the absolute timing skew of channel k and  $T_k$  refers to the sampling time interval between channel k and channel k + 1. These notations will be used in the following description.

According to the principle of TIADC, the sampling impulse of TIADC can be represented as

$$P(t) = \sum_{n=-\infty}^{\infty} \delta\left(t - kT_s - nMT_s\right).$$

(4)

Thus, considering mismatches in TIADC, the output signal of TIADC is

$$\widehat{x}(t) = \sum_{k=0}^{M-1} \left( \Delta g_k x \left( t - \Delta T_k \right) + \Delta o_k \right) \\ \times \sum_{n=-\infty}^{\infty} \delta \left( t - k T_s - n M T_s \right),$$

(5)

where  $\Delta g_k$  and  $\Delta o_k$  refer to gain error and offset error, respectively. The Fourier transform of (4) is

$$P(j\Omega) = \frac{2\pi}{MT_s} \sum_{n=-\infty}^{\infty} \delta\left(\Omega - n\frac{2\pi}{MT_s}\right) e^{-jnk(2\pi/M)}, \quad (6)$$

and the Fourier transform of  $x_k(t) = \Delta g_k x(t - \Delta T_k) + \Delta o_k$ gives

$$\widehat{X}_{k}(j\Omega) = \Delta g_{k}X(j\Omega)e^{j\Omega\Delta T_{k}} + \Delta o_{k}2\pi\delta(\Omega); \qquad (7)$$

thus, the Fourier transform of (5) can be calculated as

$\widehat{\mathbf{x}}(\cdot \mathbf{o})$

$$X (j\Omega)$$

$$= \sum_{k=0}^{M-1} \frac{1}{2\pi} \widehat{X}_{k} (j\Omega) * P (j\Omega)$$

$$= \frac{1}{MT_{s}} \sum_{k=0}^{M-1} \sum_{n=-\infty}^{\infty} \left[ \Delta g_{k} X \left( j \left( \Omega - n \frac{\Omega_{s}}{M} \right) \right) e^{j(\Omega - n(\Omega_{s}/M))\Delta T_{k}} + \Delta o_{k} 2\pi \delta \left( \Omega - n \frac{\Omega_{s}}{M} \right) \right] e^{-jnk(2\pi/M)},$$

(8)

where  $\Omega_s = 2\pi/T_s$ . From (8), we can see that if offset error is not zero, spectrum spurs will appear at  $n\Omega_s/M$ . For a sinusoidal x(t) whose angular frequency is  $\Omega_0$ , spectrum spurs due to gain and timing skew will appear at  $n\Omega_s/M \pm \Omega_0$ . What is more, amplitudes of spectrum spurs due to gain error are only relative to the value of gain error, while the amplitudes of spurious peaks introduced by timing skew are determined by both the value of timing skew and the input frequency.

#### 3. Statistic-Based Calibration Method for TIADC

In this section, offset, gain, and timing mismatch calibration methods are introduced separately.

3.1. Offset Mismatch Calibration. Assuming that infinite sampled points of  $x_k[n]$  are obtained, it is easy to see from (3) that the average value of these points is

$$E\left[x_{k}\left[n\right]\right] = O_{k}.\tag{9}$$

Considering N sampling points are obtained, the average value of these points can be written as

$$E_{N}[x_{k}[n]] = \frac{1}{N} \sum_{n=0}^{N-1} (G_{k} \sin(\omega_{0}(nM + k + \Delta t_{k}) + \phi) + O_{k}).$$

(10)

When N is large enough,  $E_N[x_k[n]]$  approaches  $E[x_k[n]]$ ; thus,

$$E_N\left[x_k\left[n\right]\right] = O_k. \tag{11}$$

From (11), we can know that the offset of each ADC can be obtained by calculating the average value of sampling points. In general, one chooses channel 0 as a reference and then matches all other channels to this reference channel. Therefore, offset mismatch can be calculated as

$$\Delta o_k = E_N \left[ x_k \left[ n \right] \right] - E_N \left[ x_0 \left[ n \right] \right]$$

=  $\frac{1}{N} \sum_{n=0}^{N-1} x_k \left[ n \right] - \frac{1}{N} \sum_{n=0}^{N-1} x_0 \left[ n \right].$  (12)

3.2. Gain Mismatch Calibration. For convenience, a simple sinusoidal signal  $A \times \sin(t)$  is used in the following derivations. Supposing that the analog signal  $A \times \sin(t)$  is sampled with a sampling period  $T_s$ , the sampling points will be  $A \times \sin(nT_s)$  (n = 0, 1, 2, ...). Let us assume that  $N_h$  sampling points are obtained in a half cycle of the sinusoidal signal; thus,

$$N_h = \frac{\pi}{T_s}.$$

(13)

The summation of these  $N_h$  sampling points can be written as

$$\sum_{n=0}^{N_h-1} A \times \sin\left[nT_s\right] = A \times \frac{N_h}{\pi} \sum_{n=0}^{N_h-1} \sin\left[nT_s\right] \times \frac{\pi}{N_h}.$$

(14)

When  $N_h$  is very large,  $\pi/N_h$  approaches zero. For this case, according to the definition of integral, the summation can be changed to integral. Therefore, we have

$$\sum_{n=0}^{N_h - 1} \sin \left[ nT_s \right] \times \frac{\pi}{N_h} = \int_0^{\pi} \sin \left( x \right) dx = 2.$$

(15)

Finally, from (13)-(15), we can get

$$\sum_{n=0}^{N_h-1} A \times \sin\left[nT_s\right] = \frac{2A}{T_s}.$$

(16)

Furthermore, for  $N_t$  sampling points which include one cycle of the sinusoidal signal, it can be obtained that

$$S_{t} = \sum_{n=0}^{N_{t}-1} \left| A \times \sin \left[ nT_{s} \right] \right| = 2 \times \sum_{n=0}^{N_{h}-1} A \times \sin \left[ nT_{s} \right] = \frac{4A}{T_{s}},$$

(17)

where  $|\cdot|$  represents the absolute value. It is clear that the initial phase of the sinusoidal signal does not affect  $S_t$ . Therefore, from (3) and (17), it gives that

$$S_{k} = \sum_{n=0}^{N-1} \left| x_{k} \left[ n \right] - O_{k} \right| = \frac{4G_{k}}{M\omega_{0}} \times \frac{N}{N_{t}},$$

(18)

where  $O_k$  is calculated as (11). From (18), it can be seen that the gain is relative to  $S_k$ . Without loss of generality, we choose channel 0 as a reference; thus, the gain error can be calculated as

$$\Delta g_k = \frac{S_k}{S_0} = \frac{\sum_{n=0}^{N-1} |x_k[n] - O_k|}{\sum_{n=0}^{N-1} |x_0[n] - O_0|}.$$

(19)

It is noted that the premise of (15) is that  $N_h$  is large enough. Considering that the frequency of input signal is  $f_{in}$ and the TIADC system has a sampling frequency of  $f_s$  and Mchannels, for one subchannel we can obtain that

$$N_h = \frac{f_s}{2Mf_{\rm in}}.$$

(20)

Thus, to make  $N_h$  large enough, the sampling rate should be much larger than signal frequency. However, if  $N/N_h$  is large enough, the sampling points will cover many cycles of the signal. Assuming

$$f_{\rm in} \neq \frac{f_s}{Mn}$$

$n = 1, 2, 3, \dots,$  (21)

the sampling points obtained in different cycles will be different. Then, as random equivalent sampling, we can use the sampling points obtained from different cycles to reconstruct one cycle of the input signal. Therefore, as long as  $N/N_h$  is large enough and (21) is satisfied, the gain error can be estimated accurately by (19).

*3.3. Timing Mismatch Calibration.* After offset and gain mismatches are calibrated, we can assume that  $O_k = 0$  for any k, and the gain of each channel is G. Under this assumption, the product of two adjacent channels can be written as

$$C_{k,k+1}(n) = x_k[n] \cdot x_{k+1}[n]$$

=  $G \sin \left( \omega_0 \left( nM + k + \Delta t_k \right) + \phi \right)$  (22)

$\cdot G \sin \left( \omega_0 \left( nM + k + 1 + \Delta t_{k+1} \right) + \phi \right).$

By using the product-to-sum formula, (22) is changed to

$$C_{k,k+1}(n) = \frac{1}{2}G^{2}\cos\left(\omega_{0}\left(1 + \Delta t_{k+1} - \Delta t_{k}\right)\right) - \frac{1}{2}G^{2}\cos\left(\omega_{0}\left(2nM + 2k + 1 + \Delta t_{k} + \Delta t_{k+1}\right) + 2\phi\right).$$

(23)

When sampling point number approaches infinity, the average value of the second part of (23) will be zero. Therefore, the average value of  $C_{k,k+1}(n)$  is

$$E\left[C_{k,k+1}(n)\right] = \frac{1}{2}G^{2}\cos\left(\omega_{0}\left(1 + \Delta t_{k+1} - \Delta t_{k}\right)\right).$$

(24)

If there is no timing skew in all channels, for any k ( $0 \le k \le M - 1$ ),  $E[C_{k,k+1}(n)]$  will be  $(1/2)G^2 \cos \omega_0$ . According to the Nyquist criterion, the range of  $\omega_0$  is  $[0, \pi]$ . In this range, cosine is a monotone decreasing function. Thus, if  $E[C_{k,k+1}(n)]$  is larger than  $(1/2)G^2 \cos \omega_0$ , it implies that the sampling interval between channel k and channel k + 1 is smaller than standard value  $T_s$ . Conversely, it means that the sampling interval is larger than  $T_s$ . Therefore,  $E[C_{k,k+1}(n)]$  can be used as a metric to calibrate timing skew.

Assuming that N sampling points are used to calculate  $E[C_{k,k+1}(n)]$ , the estimated value of  $E[C_{k,k+1}(n)]$  is

$$E_{N}\left[C_{k,k+1}\left(n\right)\right] = \frac{1}{2}G^{2}\cos\left(\omega_{0}\left(1 + \Delta t_{k+1} - \Delta t_{k}\right)\right) + R_{k,k+1},$$

(25)

where

$$R_{k,k+1} = \frac{G^2}{2N} \sum_{n=0}^{N-1} \cos\left(\omega_0 \left(2nM + 2k + 1 + \Delta t_k + \Delta t_{k+1}\right) + 2\phi\right).$$

(26)

In order to get an accurate estimation value of  $E[C_{k,k+1}(n)]$ , suitable *N* and  $\omega_0$  are needed to make  $R_{k,k+1}$  approach zero. Firstly, *N* must be large enough. Secondly, when the angular frequency of  $\cos(\omega_0(2nM + 2k + 1 + \Delta t_k + \Delta t_{k+1}) + 2\phi)$  is  $2n\pi$  (n = 1, 2, 3, ...),  $R_{k,k+1}$  will not approach zero. Thus,

$$\omega_0 \neq \frac{n\pi}{M}$$

(*n* = 1, 2, 3, ...). (27)

As mentioned above,  $E_N[C_{k,k+1}(n)]$  is utilized to calibrate timing skew. When there is no timing skew, the reference value of  $E_N[C_{k,k+1}(n)]$  is  $(1/2)G^2 \cos \omega_0$ . However, it is not easy to get *G* accurately, so we cannot calibrate timing skew simply by adjusting  $\Delta t_k$  and  $\Delta t_{k+1}$  to make  $E[C_{k,k+1}(n)]$ approach  $(1/2)G^2 \cos \omega_0$ . An iterative method is proposed here.

First,  $E_N[C_{k,k+1}(n)]$  for each k are calculated as

$$E_{N}\left[C_{k,k+1}\left(n\right)\right] = \frac{1}{N} \sum_{k=0}^{N-1} x_{k}\left[n\right] x_{k+1}\left[n\right].$$

(28)

Then,  $\Delta t_k$  is adjusted to make  $E_N[C_{k,k+1}(n)]$  (k = 1, 2, ..., M-2) be equal to  $E_N[C_{0,1}(n)]$ .  $\Delta t_k$  is adjusted as

$$\Delta t_k^{(m+1)} = \Delta t_k^{(m)} + d \times \Delta u, \qquad (29)$$

where  $\Delta t_k^{(i)}$  represents the residual timing skew of channel k after i times iteration,  $\Delta u$  refers to the adjustment step, and d refers to the adjustment direction. If  $E_N[C_{k,k+1}(n)]$  is larger than  $E_N[C_{0,1}(n)]$ , d is +1; otherwise, d is -1.  $\Delta u$  is decided by the adjustment method of timing skew. There are two methods to adjust  $\Delta t_k$ . One method is adjusting the sampling clock of channel k directly. This method needs digital control delay element (DCDE) in ADC or clock generation circuit. The other method is making use of fraction delay filters [15]. After this step, all  $T_k$  except  $T_{M-1}$  are equal. What is more, when  $E_N[C_{k,k+1}(n)]$  is equal to  $E_N[C_{0,1}(n)]$ , it is obtained from (24) that

$$\Delta t_{k+1} - \Delta t_k = \Delta t_1 - \Delta t_0. \tag{30}$$

By substituting  $\Delta t_0 = 0$  into (30) and after some recursive derivations, we can get

$$\Delta t_k = k \times \Delta t_1. \tag{31}$$

Furthermore,  $\Delta t_k$  is adjusted to make  $T_{M-1}$  be equal to other  $T_k$ . It is clear that  $\Delta t_{M-1}$  should be adjusted. However,

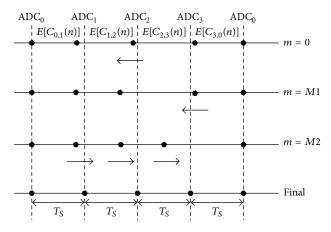

FIGURE 3: Illustration of calibration process in a four-channel TIADC.

once  $\Delta t_{M-1}$  is modified, not only  $T_{M-1}$  but also  $T_{M-2}$  is changed. Therefore, considering the residual timing skew shown in (31), to keep all  $T_k$  except  $T_{M-1}$  equal in this calibration step, each  $\Delta t_k$  is adjusted as

$$\Delta t_k^{(m+1)} = \Delta t_k^{(m)} + k \times d \times \Delta u.$$

(32)

If  $E_N[C_{M-1,0}(n)]$  is larger than other  $E_N[C_{k,k+1}(n)]$ , it means that  $T_{M-1}$  is smaller than other  $T_k$ ; thus,  $\Delta t_{M-1}$  should be decreased to increase  $T_{M-1}$  and d is -1. Conversely,  $T_{M-1}$ should be decreased, and  $\Delta t_{M-1}$  should be increased and dis +1. When all  $E_N[C_{k,k+1}(n)]$  (k = 0, 1, ..., M - 1) have the same value, the calibration is finished.

The calibration process of four-channel TIADC can be shown as in Figure 3. At the beginning of calibration, it is assumed that the timing skews are [0, -0.02, -0.01,0.01]. Because  $E[C_{1,2}(n)]$  is smaller than  $E[C_{0,1}(n)]$ ,  $\Delta t_2$  is decreased. After *M*1 iterations,  $E[C_{0,1}(n)]$  and  $E[C_{1,2}(n)]$ are equal, and the timing skews are [0, -0.01, -0.02, 0.01]. Then,  $\Delta t_3$  is also decreased since  $E[C_{2,3}(n)]$  is smaller than  $E[C_{0,1}(n)]$ . After *M*2 iterations,  $E[C_{2,3}(n)]$  and  $E[C_{0,1}(n)]$  are equal, and the timing skews are [0, -0.01, -0.02, -0.03]. Finally,  $E[C_{0,1}(n)]$  and  $E[C_{3,0}(n)]$  are compared. Because  $E[C_{0,1}(n)]$  is larger than  $E[C_{3,0}(n)]$ ,  $\Delta t_1$  is increased by  $\Delta u$ . To keep  $E[C_{1,2}(n)]$  and  $E[C_{2,3}(n)]$  be equal to  $E[C_{0,1}(n)]$ ,  $\Delta t_2$  and  $\Delta t_3$  are increased by  $2 \times \Delta u$  and  $3 \times \Delta u$ , respectively. When  $E[C_{0,1}(n)]$  and  $E[C_{3,0}(n)]$  are equal, the iteration is stopped and the calibration finishes.

#### 4. Implementation

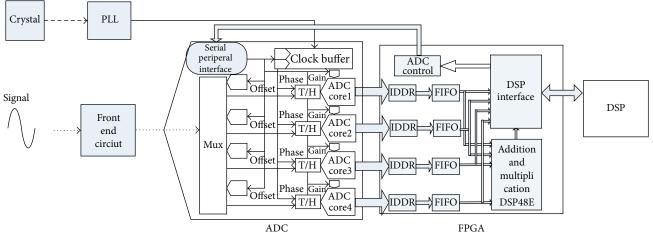

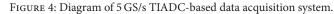

The proposed calibration method is implemented in a 5 GS/s TIADC-based data acquisition system (DAS), whose diagram is shown in Figure 4. The whole system is composed of front end circuits of ADC, clock generation circuits which include crystal and phase locked loop (PLL), ADC, field programmable gate array (FPGA), and digital signal processor (DSP). FPGA is employed for sampled data receiving and storage. In FPGA, the sampled data from ADC are received by input double data rate (IDDR) elements firstly. Then, the sampled

data are stored in FIFO (fist in fist out) which is built by memory in FPGA. At last, the sampled data are transmitted to DSP. Because the calculation speed of FPGA is faster than DSP, the addition and multiplication operation needed for calibration are also implemented in FPGA. DSP48E elements in Xilinx FPGA are utilized to implement addition and multiplication operation. The whole system is controlled by DSP.

The part number of 5 GS/s ADC is EV8AQ160, which consists of four 1.25 GS/s ADC cores. The simplified block diagram of this ADC is also shown in Figure 4. It can be seen that there are offset, gain, and phase adjustment elements in ADC. These adjustment elements are controlled by digital control word (DCW), which is sent from FPGA by serial peripheral interface (SPI). The adjustment steps of offset, gain, and phase are 0.2 LSB, 0.14%, and 110 fs, respectively.

The calibration process is conducted as follows.

First, the average value of sampled data of each channel is calculated, and offset error is obtained by (12). After the offset error is obtained, it is corrected by sending DCW to offset adjustment element. The DCW is calculated as

$$DCW_{offset}^{N} = DCW_{offset}^{O} - \frac{\Delta o_{k}}{0.2},$$

(33)

where the superscripts N and O refer to new DCW and original DCW, respectively.

Secondly, (19) is utilized to obtain gain error. Gain error is corrected by gain adjustment element, whose DCW is calculated as

$$DCW_{gain}^{N} = DCW_{gain}^{O} + \frac{1 - \Delta g_k}{0.14\%}.$$

(34)

Finally, timing skew is calibrated. Phase adjustment element is used to adjust timing skew in the process of iteration. The calibration of timing skew has been discussed in Section 3. Timing skew is adjusted by phase adjustment element, and the adjustment step is 110 fs. When all  $E[C_{k,k+1}(n)]$  are equal, the calibration is finished.

#### 5. Experimental Results

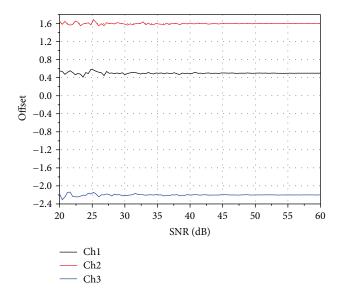

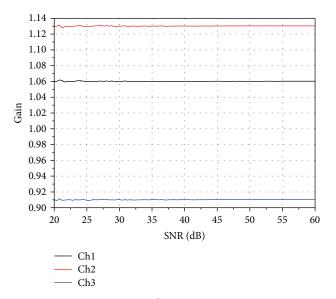

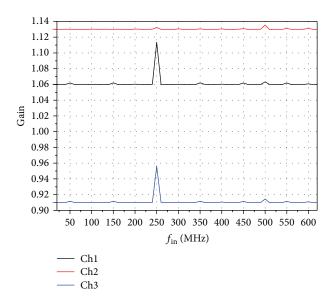

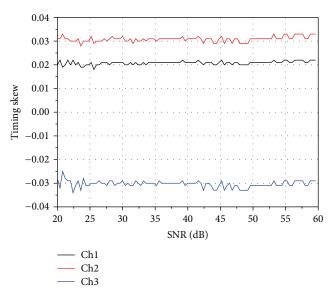

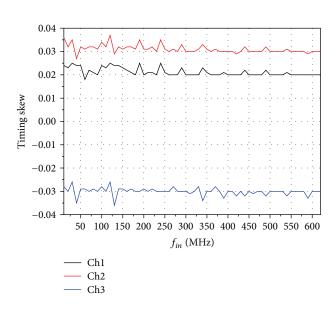

5.1. Simulation. A four-channel 5 GS/s TIADC system is simulated to present the performance of proposed method in the following part of this section. Zero-mean Gaussian white noise is added to each channel. The offset, gain, and timing skew errors are set as  $\Delta o_{0,1,2,3} = [0, 0.5, 1.6, -2.2]$ ,  $\Delta g_{0,1,2,3} = [1, 1.06, 1.13, 0.91]$ , and  $\Delta t_{0,1,2,3} = [0, 0.02, 0.03, -0.03]$ , respectively. The number of sampling points used for calibration mismatches is selected to be 20000.

First, two experiments are carried out to demonstrate the estimation accuracy of offset and gain error. One experiment is to evaluate the impact of noise on the estimation accuracy of the proposed method. The signal frequency is set to 600 MHz. As shown in Figures 5 and 6, the proposed method can estimate offset and gain error accurately in a wide SNR range from 20 dB to 60 dB. The other experiment aims at evaluating the impact of signal frequency on the estimation accuracy of the proposed method. The SNR is set to 45 dB. From Figures 7 and 8, it is shown that the proposed method has high

1.6 1.2 0.8 0.4 0.0 Offset -0.4-0.8 -1.2-1.6 -2.0-2.4 50 100 150 200 250 300 350 400 450 500 550 600  $f_{\rm in}$  (MHz) Ch1 - Ch2 - Ch3

FIGURE 5: Estimated offset error versus SNR.

FIGURE 6: Estimated gain error versus SNR.

FIGURE 7: Estimated offset error versus signal frequency.

FIGURE 8: Estimated gain error versus signal frequency.

FIGURE 9: Estimated timing skew versus SNR.

FIGURE 10: Estimated timing skew versus signal frequency.

estimate accuracy in a wide frequency range from 10 MHz to 620 MHz except for some special frequencies shown in (21). It should be noted that Figures 5 to 10 are obtained by some discrete points. In Figures 5, 6, and 9, the step of SNR is 0.4 dB. The step of frequency in Figures 7, 8, and 10 is 10 MHz.

Secondly, the performance of timing skew calibration is demonstrated. Although timing skew is calibrated directly without estimation, after the calibration is finished, the estimated timing skew  $\Delta \hat{t}_k$  can be calculated as

$$\Delta \hat{t}_k = \Delta t_k^{(P)} + \Delta t_k^{(0)}, \qquad (35)$$

where P refers to the iteration times when calibration is finished. We calibrate timing skew after offset and gain errors are corrected by the proposed method. As offset and gain error, the impacts of SNR and signal frequency on calibration

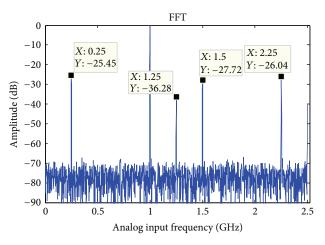

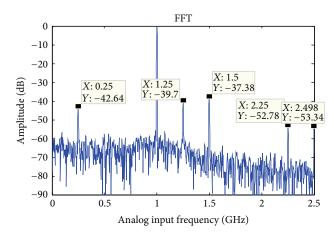

FIGURE 11: The spectrum of TIADC output without calibration.

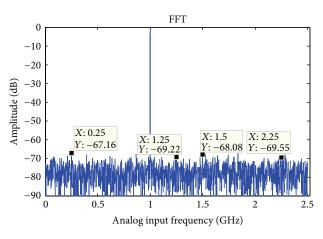

FIGURE 12: The spectrum of TIADC output with calibration.

performance are researched, respectively. The estimated timing skews versus SNR and signal frequency are shown in Figures 9 and 10, respectively. From Figure 9, where the signal frequency is set to 600 MHz, it can be seen that  $\Delta \hat{t}_k$  is very close to real timing skew  $\Delta t_k$  in a wide SNR range from 20 dB to 60 dB. Thus, it is concluded that the proposed method can calibrate timing skew accurately in a wide SNR range. Similarly, it is seen from Figure 10 that timing skew can be calibrated with different signal frequency. It should be noted that the proposed method does not work well at some frequencies as shown in (27). Because Figure 10 is obtained by discrete points with a step of 10 MHz, these frequencies are not shown.

Finally, the spectra before and after calibration are shown in Figures 11 and 12. It is shown that after calibration, the spectrum spurs due to mismatches are degraded greatly. This proves the good performance of the proposed method.

*5.2. Testing Result of 5 GS/s TIADC System.* In this part, the experiment results got from a real 5 GS/s TIADC system, whose diagram is shown in Figure 4, are shown to demonstrate the effectiveness of the proposed calibration method. Figure 13 shows the experiment board of 5 GS/s TIADC. The

FIGURE 13: Experiment board of 5 GS/s TIADC.

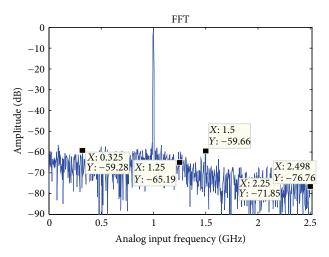

FIGURE 14: The spectrum of real 5 GS/s TIADC output before calibration.

proposed method is implemented in this system. The main chips which include ADC, FPGA, and DSP are marked in Figure 13. The signal is input by a pair of SMA (Sub-Miniature-A) connectors and then sampled by ADC. The main function of FPGA is sampled data storage. All sampled data are stored in FIFO built by Block RAM (random access memory) of FPGA. In addition, as mentioned in Section 4, the proposed calibration method is also implemented in FPGA. The main function of DSP is system control. ADC and IDDR modules shown in Figure 4 are all controlled by DSP. Moreover, when the FIFO in FPGA is full, the sampled data are transmitted to DSP for analysis.

Since the real mismatches in the system are unknown, the spectra before and after calibration are utilized to prove the effectiveness of the proposed method. From the comparison of Figures 14 and 15, we can clearly see that the spectrum spurs due to the mismatches have been effectively eliminated. These experimental results prove that the proposed method works very well in real system.

#### 6. Conclusion

The mismatches in TIADC degrade the performance of the system. In particular, in high speed TIADC system, small mismatches will introduce big spectrum spurs. A new calibration method is proposed for a four-channel 5 GS/s TIADC in

FIGURE 15: The spectrum of real 5 GS/s TIADC output after calibration.

this paper. It can calibrate mismatches accurately with different SNR and signal frequency. This method can be easily realized in a real system with low cost. It especially suits high speed digital storage oscilloscope and other systems where TIADC-based high speed data acquisition is used.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### Acknowledgments

This work was supported by the National Natural Science Foundation of China (no. 61301263 and no. 61301264), the Specialized Research Fund for the Doctoral Program of Higher Education of China (no. 20120185130002), and the Fundamental Research Fund for the Central University of China (nos. A03007023801217 and A03008023801080).

#### References

- W. C. Black and D. A. Hodges, "Time interleaved converter array," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 6, pp. 1022–1029, 1980.

- [2] A. Petraglia and S. K. Mitra, "Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer," *IEEE Transactions on Instrumentation and Measurement*, vol. 40, no. 5, pp. 831–835, 1991.

- [3] S.-P. U, S.-W. Sin, and R. P. Martins, "Exact spectra analysis of sampled signals with jitter-induced nonuniformly holding effects," *IEEE Transactions on Instrumentation and Measurement*, vol. 53, no. 4, pp. 1279–1288, 2004.

- [4] C. Vogel, "The impact of combined channel mismatch effects in time-interleaved ADCs," *IEEE Transactions on Instrumentation* and Measurement, vol. 54, no. 1, pp. 415–427, 2005.

- [5] N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, "Explicit analysis of channel mismatch effects in time-interleaved ADC systems," *IEEE Transactions on Circuits*

*and Systems I: Fundamental Theory and Applications*, vol. 48, no. 3, pp. 261–271, 2001.

- [6] P. Ye, H. Pan, H. Zeng, M. Li, and W. Huang, "A self-adaptive frequency response compensation method for a TIADC system," *Mathematical Problems in Engineering*, vol. 2013, Article ID 613025, 7 pages, 2013.

- [7] S. Huang and B. C. Levy, "Adaptive blind calibration of timing offset and gain mismatch for two-channel time-interleaved ADCs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 6, pp. 1278–1288, 2006.

- [8] S. Huang and B. C. Levy, "Blind calibration of timing offsets for four-channel time-interleaved ADCs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 4, pp. 863– 876, 2007.

- [9] J. Elbornsson, F. Gustafsson, and J.-E. Eklund, "Blind equalization of time errors in a time-interleaved ADC system," *IEEE Transactions on Signal Processing*, vol. 53, no. 4, pp. 1413–1424, 2005.

- [10] P. Satarzadeh, B. C. Levy, and P. J. Hurst, "Adaptive semiblind calibration of bandwidth mismatch for two-channel timeinterleaved ADCs," *IEEE Transactions on Circuits and Systems. I. Regular Papers*, vol. 56, no. 9, pp. 2075–2088, 2009.

- [11] Y. X. Zou and X. J. Xu, "Blind timing skew estimation using source spectrum sparsity in time-interleaved ADCs," *IEEE Transactions on Instrumentation and Measurement*, vol. 61, no. 9, pp. 2401–2412, 2012.

- [12] J. M. D. Pereira, P. M. B. S. Girão, and A. M. C. Serra, "An FFTbased method to evaluate and compensate gain and offset errors of interleaved ADC systems," *IEEE Transactions on Instrumentation and Measurement*, vol. 53, no. 2, pp. 423–430, 2004.

- [13] S. J. Liu, P. P. Qi, J. S. Wang et al., "Adaptive calibration of channel mismatches in time-interleaved ADCs based on equivalent signal recombination," *IEEE Transactions on Instrumentation* and Measurement, vol. 63, no. 2, pp. 277–286, 2014.

- [14] H. Pan, S. Tian, and P. Ye, "An adaptive synthesis calibration method for timeinterleaved sampling systems," *Metrology and Measurement Systems*, vol. 17, no. 3, pp. 405–414, 2010.

- [15] H. Johansson and P. Löwenborg, "Reconstruction of nonuniformly sampled bandlimited signals by means of digital fractional delay filters," *IEEE Transactions on Signal Processing*, vol. 50, no. 11, pp. 2757–2767, 2002.

- [16] Y. C. Lim, Y.-X. Zou, J. W. Lee, and S.-C. Chan, "Time-interleaved analog-to-digital-converter compensation using multichannel filters," *IEEE Transactions on Circuits and Systems. I. Regular Papers*, vol. 56, no. 10, pp. 2234–2247, 2009.

- [17] Y. X. Zou, S. L. Zhang, Y. C. Lim, and X. Chen, "Timing mismatch compensation in time-interleaved ADCs based on multichannel lagrange polynomial interpolation," *IEEE Transactions on Instrumentation and Measurement*, vol. 60, no. 4, pp. 1123–1131, 2011.

- [18] L. Zhao, X. Hu, C. Feng, S. Tang, S. Liu, and Q. An, "A 1.6-gsps high-resolution waveform digitizer based on a time-interleaved technique," *IEEE Transactions on Nuclear Science*, vol. 60, no. 3, pp. 2180–2187, 2013.

- [19] L. Xia, J. Wang, W. Beattie, J. Postman, and P. Y. Chiang, "Sub-2-ps, static phase error calibration technique incorporating measurement uncertainty calcellation for multi-gigahertz timeinterleaved T/H circuits," *IEEE Transactions on Circuits and Systems. I. Regular Papers*, vol. 59, no. 2, pp. 276–284, 2012.

- [20] C.-Y. Wang and J.-T. Wu, "A multiphase timing-skew calibration technique using zero-crossing detection," *IEEE Transactions on*

Circuits and Systems. I. Regular Papers, vol. 56, no. 6, pp. 1102–1114, 2009.

Journal of Probability and Statistics

(0,1),

International Journal of

Advances in Mathematical Physics

## Journal of Optimization