## IMPERIAL COLLEGE LONDON DEPARTMENT OF COMPUTING

## Software Performance Engineering using Virtual Time Program Execution

Nikolaos Baltas

Submitted in part fullment of the requirements for the degree of Doctor of Philosophy in Computing of Imperial College London and the Diploma of Imperial College London

To my mother Dimitra for her endless support

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

### Abstract

In this thesis we introduce a novel approach to software performance engineering that is based on the execution of code in virtual time. Virtual time execution models the timing-behaviour of unmodified applications by scaling observed method times or replacing them with results acquired from performance model simulation. This facilitates the investigation of "what-if" performance predictions of applications comprising an arbitrary combination of real code and performance models. The ability to analyse code and models in a single framework enables performance testing throughout the software lifecycle, without the need to to extract performance models from code. This is accomplished by forcing thread scheduling decisions to take into account the hypothetical time-scaling or model-based performance specifications of each method. The virtual time execution of I/O operations or multicore targets is also investigated.

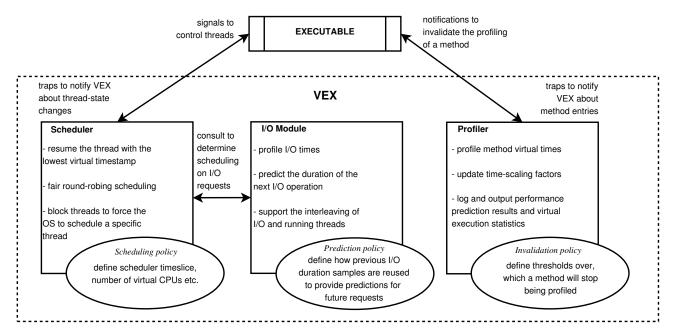

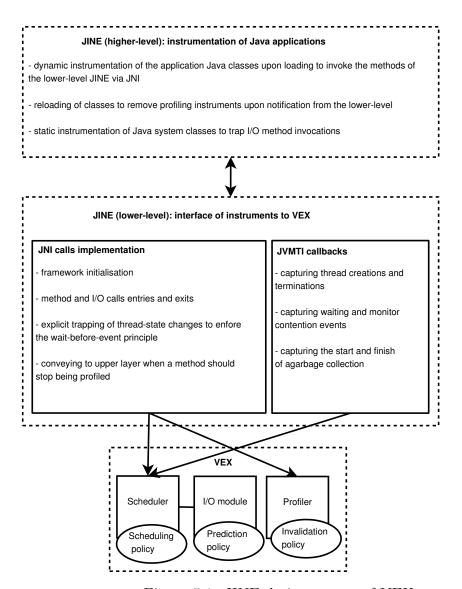

We explore these ideas using a Virtual EXecution (VEX) framework, which provides performance predictions for multi-threaded applications. The language-independent VEX core is driven by an instrumentation layer that notifies it of thread state changes and method profiling events; it is then up to VEX to control the progress of application threads in virtual time on top of the operating system scheduler. We also describe a Java Instrumentation Environment (JINE), demonstrating the challenges involved in virtual time execution at the JVM level.

We evaluate the VEX/JINE tools by executing client-side Java benchmarks in virtual time and identifying the causes of deviations from observed real times. Our results show that VEX and JINE transparently provide predictions for the response time of unmodified applications with typically good accuracy (within 5-10%) and low simulation overheads (25-50% additional time). We conclude this thesis with a case study that shows how models and code can be integrated, thus illustrating our vision on how virtual time execution can support performance testing throughout the software lifecycle.

## Acknowledgements

I would like to express my sincerest gratitude to my supervisor, Tony Field, whose knowledge, perceptiveness and positive attitude has supported, guided and inspired me throughout the course of this thesis. He has been a remarkable tutor and working with him has been an absolute privilege. I would also like to thank Paul Kelly for presenting to me the opportunity to work on this project and Alexander Wolf for bringing me in contact with the wider performance modelling community in a Dagstuhl seminar. I am grateful to my examiners Stephen Jarvis and Will Knottenbelt for their insightful comments and suggestions that have significantly improved the quality of this thesis.

I would like to particularly thank Andrew Cheadle for all the technical support and research guidance that he offered in the early stages of the project, as well as for helping us envision how our approach could be used in performance engineering. I would like to thank all the students who have been involved with the virtual time execution project: Richard Bounds, Damola Adeagbo, Andreas Matsikaris, James Greenhaulgh and Cyrus Lyons. They comprise the community that has used the virtual time execution framework and their feedback has contributed to the further improvement of the tool.

I am especially grateful to my office colleagues and friends Wolfram Wiesemann, Phoebe Vayanos, Angelos Georgiou, Raquel Fonseca and Adil Hussain for all the fun, interesting and stimulating discussions we have held over the years and for the great experience of sharing my time at the college with them.

Finally, I would like to thank my family and friends for being there for me in the better and tougher times of the research effort. I would also like to express my deepest gratitude to Delia for standing by me throughout this journey; for her constant encouragement and unconditional support.

## Contents

| 1        | Intr | oductio | on                                            | <b>25</b> |

|----------|------|---------|-----------------------------------------------|-----------|

|          | 1.1  | The ide | ea                                            | 26        |

|          | 1.2  | Contrib | outions                                       | 27        |

|          | 1.3  | Publica | ations and Statement of Originality           | 29        |

| <b>2</b> | Bac  | kgroun  | ${f d}$                                       | 30        |

|          | 2.1  | Softwar | re Performance Engineering (SPE)              | 30        |

|          |      | 2.1.1   | Model-based SPE                               | 32        |

|          |      | 2.1.2   | Measurements                                  | 36        |

|          | 2.2  | Simula  | tion                                          | 41        |

|          |      | 2.2.1   | Execution-driven simulation                   | 42        |

|          |      | 2.2.2   | Network emulation                             | 50        |

|          |      | 2.2.3   | Real time simulation                          | 52        |

|          |      | 2.2.4   | Controlling program execution in Virtual Time | 53        |

|          | 2.3  | Java V  | irtual Machine overview                       | 55        |

|          |      | 2.3.1   | Java                                          | 55        |

|          |      | 232     | INI                                           | 55        |

|   |      | 2.3.3   | JVMTI                               | 55 |

|---|------|---------|-------------------------------------|----|

|   |      | 2.3.4   | Java instrumentation                | 56 |

|   | 2.4  | Pthrea  | ads                                 | 56 |

|   | 2.5  | I/O .   |                                     | 57 |

|   |      | 2.5.1   | I/O in Linux                        | 57 |

|   |      | 2.5.2   | I/O in execution-driven simulation  | 58 |

|   |      | 2.5.3   | Prediction methods                  | 60 |

| 3 | Virt | tual Ti | me Execution                        | 62 |

|   | 3.1  | Schedi  | ıler                                | 66 |

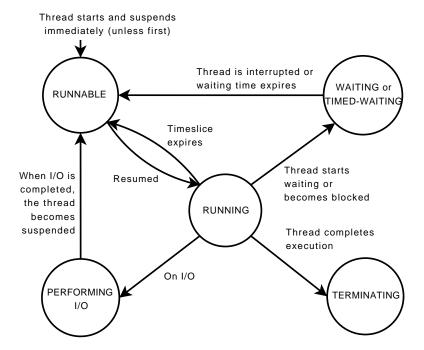

|   |      | 3.1.1   | VEX states                          | 67 |

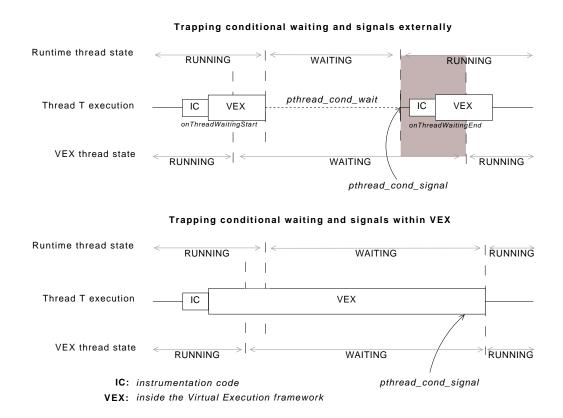

|   |      | 3.1.2   | Controlling threads in virtual time | 69 |

|   |      | 3.1.3   | Implementation issues               | 71 |

|   | 3.2  | Profile | er                                  | 75 |

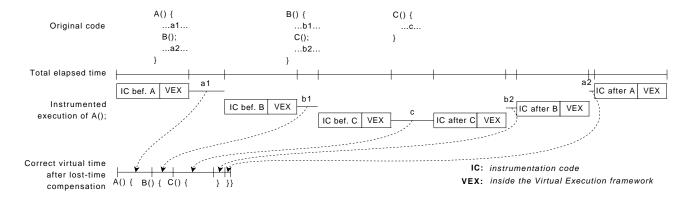

|   |      | 3.2.1   | Measuring virtual time              | 76 |

|   |      | 3.2.2   | Logging method times                | 78 |

|   |      | 3.2.3   | Compensating for observer effects   | 79 |

|   |      | 3.2.4   | Simulation output                   | 82 |

|   | 3.3  | Evalua  | ation                               | 87 |

|   |      | 3.3.1   | Validation                          | 87 |

|   |      | 3.3.2   | Overhead                            | 90 |

|   |      | 3.3.3   | Limitations                         | 93 |

| 4 | I/O        | in vir  | tual time                             | 95  |

|---|------------|---------|---------------------------------------|-----|

|   | 4.1        | I/O in  | VEX                                   | 97  |

|   |            | 4.1.1   | Requirements                          | 97  |

|   |            | 4.1.2   | Methodology                           | 98  |

|   |            | 4.1.3   | Misprediction handling                | 103 |

|   |            | 4.1.4   | I/O scaling                           | 105 |

|   |            | 4.1.5   | I/O exclusion                         | 107 |

|   | 4.2        | Empir   | rical I/O prediction parameters       | 108 |

|   |            | 4.2.1   | Measurement aggregation               | 109 |

|   |            | 4.2.2   | Prediction methods                    | 110 |

|   | 4.3        | Evalua  | ation                                 | 113 |

|   |            | 4.3.1   | Benchmarks                            | 114 |

|   |            | 4.3.2   | Optimal configuration investigation   | 117 |

|   |            | 4.3.3   | Investigating I/O effects             | 123 |

|   |            | 4.3.4   | Database prediction                   | 125 |

| 5 | Java       | a Instr | rumentation Environment               | 131 |

|   | <b>-</b> 1 | ъ.      |                                       | 100 |

|   | 5.1        | Design  | n and implementation                  | 132 |

|   |            | 5.1.1   | System initialisation and termination | 132 |

|   |            | 5.1.2   | Thread monitoring                     | 134 |

|   |            | 5.1.3   | Method handling                       | 142 |

|   |            | 5.1.4   | Instrumentation techniques            | 144 |

|   |            | 5.1.5   | Usage                                 | 146 |

|   |     | 5.1.6       | Summary                                  |

|---|-----|-------------|------------------------------------------|

|   | 5.2 | Challe      | nges in Java virtual time execution      |

|   |     | 5.2.1       | Implementation note: Deadlocks in JVM    |

|   |     | 5.2.2       | Native waiting threads                   |

|   |     | 5.2.3       | Safepoint synchronisation                |

|   |     | 5.2.4       | Leaps forward in virtual time            |

|   |     | 5.2.5       | Heuristics for countering premature VLFs |

|   |     | 5.2.6       | Java system threads                      |

|   |     | 5.2.7       | JIT compilation                          |

|   |     | 5.2.8       | Garbage collection                       |

| 6 | Res | ${ m ults}$ | 160                                      |

|   | 6.1 | M/M/        | 1 simulation                             |

|   | 6.2 | JGF s       | ingle-threaded                           |

|   | 6.3 | JGF n       | nulti-threaded                           |

|   |     | 6.3.1       | Basic results                            |

|   |     | 6.3.2       | Thread and time scaling                  |

|   | 6.4 | SPEC        | jvm2008                                  |

|   |     | 6.4.1       | Single-threaded                          |

|   |     | 6.4.2       | Multithreaded                            |

| 7 | Mu  | lticore     | VEX 193                                  |

|   | 7.1 | Metho       | dology                                   |

|   |     | 7.1.1       | Multiple core simulation                 |

|     | 7.1.2                    | Synchronisation                                                                                                                           | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2 | Extens                   | sions for VEX thread handling                                                                                                             | 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.2.1                    | I/O                                                                                                                                       | 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.2.2                    | Native waiting                                                                                                                            | 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.3 | Evalua                   | ation                                                                                                                                     | 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.3.1                    | JGF investigation of scaling                                                                                                              | 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.3.2                    | SPEC investigation                                                                                                                        | 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.3.3                    | Simulating a large number of CPUs                                                                                                         | 08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4 | 111                      |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Mod | del int                  | egration 2                                                                                                                                | <b>14</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8.1 | Integra                  | ation of models and code                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.1.1                    | Merging the notion of time                                                                                                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.1.2                    | Merging workloads                                                                                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.1.3                    | Guaranteeing functional consistency                                                                                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.1.4                    | Merging resource contention                                                                                                               | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.2 | Integra                  | ating open Queueing Networks with VEX                                                                                                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.2.1                    | Defining method-level performance models                                                                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.2.2                    | Assumptions                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.2.3                    | Simulating models in VEX                                                                                                                  | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.3 | Applic                   | eation in performance engineering                                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.4 | Case s                   | tudy                                                                                                                                      | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

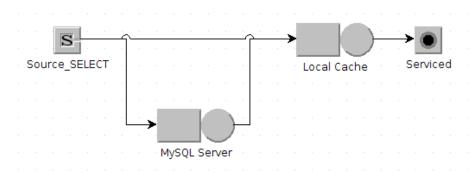

|     | 8.4.1                    | Pure model                                                                                                                                | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 8.4.2                    | Client-thinking implemented                                                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 7.3<br>Mod<br>8.1<br>8.2 | 7.2.1 7.2.2 7.3 Evalua 7.3.1 7.3.2 7.3.3  Model interes 8.1.1 8.1.2 8.1.3 8.1.4 8.2 Integra 8.2.1 8.2.2 8.2.3 8.3 Applic 8.4 Case s 8.4.1 | 7.2 Extensions for VEX thread handling       2         7.2.1 I/O       2         7.2.2 Native waiting       2         7.3 Evaluation       2         7.3.1 JGF investigation of scaling       2         7.3.2 SPEC investigation       2         7.3.3 Simulating a large number of CPUs       2         Model integration       2         8.1 Integration of models and code       2         8.1.1 Merging the notion of time       2         8.1.2 Merging workloads       2         8.1.3 Guaranteeing functional consistency       2         8.1.4 Merging resource contention       2         8.2 Integrating open Queueing Networks with VEX       2         8.2.1 Defining method-level performance models       2         8.2.2 Assumptions       2         8.2.3 Simulating models in VEX       2         8.3 Application in performance engineering       2         8.4 Case study       2         8.4.1 Pure model       2 |

|              |      | 8.4.3  | Partially-complete code                   | 233 |

|--------------|------|--------|-------------------------------------------|-----|

|              |      | 8.4.4  | Complete code                             | 234 |

|              |      | 8.4.5  | Cache study                               | 235 |

| 9            | Con  | clusio | n                                         | 238 |

|              | 9.1  | Summ   | ary of Thesis Achievements                | 238 |

|              | 9.2  | Open   | Questions                                 | 240 |

|              |      | 9.2.1  | Performance prediction quality            | 240 |

|              |      | 9.2.2  | Evaluation on large scale applications    | 241 |

|              |      | 9.2.3  | I/O modelling                             | 242 |

|              |      | 9.2.4  | Full integration in the JVM source        | 243 |

|              |      | 9.2.5  | Optimisation choice selection             | 243 |

|              | 9.3  | Future | e Work                                    | 244 |

|              |      | 9.3.1  | Lower-level virtual time executions       | 244 |

|              |      | 9.3.2  | Native code integration                   | 245 |

|              |      | 9.3.3  | Distributed VEX                           | 245 |

|              |      | 9.3.4  | Integration of other modelling techniques | 245 |

| $\mathbf{A}$ | Exp  | erime  | ntal machines                             | 246 |

|              | A.1  | Table  | of machines                               | 246 |

| В            | Ben  | chmar  | k descriptions                            | 247 |

| $\mathbf{C}$ | Frai | newor  | k usage                                   | 249 |

|              | C.1  | Buildi | ng and Options                            | 250 |

| Bibliography |      |      | 250 |

|--------------|------|------|-----|

| C.1.2        | JINE | <br> | 250 |

| C.1.1        | VEX  | <br> | 250 |

## List of Tables

| 3.1 | VEX actual scheduler timeslices according to requested timeslices: lower re-          |

|-----|---------------------------------------------------------------------------------------|

|     | quested timeslices are inexact, because the OS schedules other processes after        |

|     | the expiry time. Reported values are for Host-1 (see Appendix A). The means           |

|     | and COVs refer to all samples gathered from a single run with the requested           |

|     | timeslice. Lower timeslices from asynchronous scheduler notification are not          |

|     | taken into account                                                                    |

| 3.2 | Method instrumentation overheads for different CPU-timer selections 90                |

| 3.3 | Prediction errors for trivial short methods without any overhead compensation.        |

|     | Results from 100 measurements on Host-1 are shown                                     |

| 3.4 | Major page fault effect on VEX prediction accuracy                                    |

| 4.1 | Virtual Time I/O prediction methods                                                   |

| 4.2 | Parameters used for Disk I/O benchmark                                                |

| 4.3 | Results for the Disk I/O benchmark without an I/O threshold. "Correct" pre-           |

|     | dictions are defined to be within a $20\%$ (absolute) error of the observed I/O real  |

|     | time. Means of 15 measurements shown                                                  |

| 4.4 | Results for the Disk I/O benchmark using an I/O threshold of $50\mu s$ . Means of     |

|     | 15 measurements are shown                                                             |

| 4.5 | Issues in virtual time I/O with and without an I/O threshold. "Low" times are         |

|     | supposed to hit the cache and run sequentially, while "High" ones are expected        |

|     | to perform an I/O with DMA and allow other threads to make progress in parallel $120$ |

16 LIST OF TABLES

| 4.6 | Effect of prediction aggregation on the "No Memory" I/O benchmark, when the list is always read directly from disk                                                                                                                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7 | Effect of chain size in the <i>markov</i> prediction policy for the Disk I/O benchmark with memory-loaded file list. Means and standard deviations of 9 measurements on Host-1                                                                                                                                          |

| 4.8 | Effect of chain size in the <i>markov</i> prediction policy for the Disk I/O benchmark with disk loaded file list. Means and standard deviations of 9 measurements on Host-1                                                                                                                                            |

| 4.9 | Average prediction errors for the MySQL database experiment with and without the use of an I/O threshold as a function of the average think time $Z$ 126                                                                                                                                                                |

| 5.1 | Reference table on how JINE interfaces with VEX                                                                                                                                                                                                                                                                         |

| 6.1 | Code profile for the single-threaded JGF benchmarks as returned by JINE 168                                                                                                                                                                                                                                             |

| 6.2 | Results for the single-threaded JGF. Means of 3 runs are shown for the full profile and 30 runs for the adaptive profiling mode                                                                                                                                                                                         |

| 6.3 | Results for the single-threaded JGF with the -Xint flag. Means of 3 runs are shown                                                                                                                                                                                                                                      |

| 6.4 | Results for the multi-threaded JGF benchmarks with 8 threads. The results of the stress tests are throughputs of events, while the rest are in seconds. The count of invocations to the Thread.yield() is shown to demonstrate the effect on prediction accuracy and simulation overhead. Means of 3 runs are shown 173 |

| 6.5 | Code profile for the SPECjvm2008 benchmarks as returned by JINE 176                                                                                                                                                                                                                                                     |

| 6.6 | SPECjvm2008 benchmark results with a single workload-driving thread and no time scaling                                                                                                                                                                                                                                 |

| 6.7 | SPECjvm2008 benchmark results for 4 threads with VEX scheduler timeslices of 100ms (default) and 10ms. Means of 3 runs are shown                                                                                                                                                                                        |

LIST OF TABLES 17

| 6.8  | SPECjvm2008 benchmark results for 4 threads with stack-trace level profiling and an I/O threshold of $50\mu s$ (using the $max$ prediction method). Means of 3 measurements are shown                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.9  | SPECjvm2008 benchmark results for 4 threads with the Concurrent-Mark-Sweep garbage collector or a 2GB large heap. Means of 3 measurements are shown 183                                                                                         |

| 6.10 | SPECjvm2008 benchmark results for 4 threads with the $-XX:+AggressiveOpts$ optimisation options enabled. Means of 3 measurements are shown                                                                                                      |

| 6.11 | SPECjvm2008 benchmark results for 4 threads executed by the IBM JVM.  Means of 3 measurements are shown                                                                                                                                         |

| 6.12 | SPECjvm2008 results for 4 threads with time scaling factors of 1.0 and 2.0.  Means of 3 runs are shown                                                                                                                                          |

| 6.13 | SPECjvm2008 benchmark results for 1 - 16 threads executing in various modes: adaptive profiling (AP), no profiling (NP) and no scheduling (NS) 190                                                                                              |

| 7.1  | Multicore VEX predictions for the multi-threaded JGF benchmarks executed by 8 threads on 2 (physical and virtual) cores. Scaling results are compared to the predictions of uniprocessor VEX presented in Table 6.4. Means of 10 runs are shown |

| 7.2  | Multicore SPECjvm2008 predictions for 4 threads on 2 (physical and virtual) cores. Means of 3 runs are shown                                                                                                                                    |

| 7.3  | Multicore VEX predictions for the ratio $\frac{T}{m}$ with $T$ threads and $m$ virtual cores . 209                                                                                                                                              |

| 7.4  | Multicore VEX predictions and overheads for "Normal" and time-scaled (accelerated by $50\%$ ) executions of $T$ threads on $m$ virtual cores                                                                                                    |

| 8.1  | Parameter values and distributions used in the modelling case study                                                                                                                                                                             |

| 8.2  | Total times of performance tests in the different development stages of case study using the modelling integration feature of VEX (30 runs per result)                                                                                          |

| A.1  | Experiment hosts                                                                                                                                                                                                                                |

| B.1 | DHPC sequential JGF benchmark descriptions | 247 |

|-----|--------------------------------------------|-----|

| B.2 | JGF multi-threaded benchmark descriptions  | 247 |

| В.3 | SPECjvm2008 benchmark descriptions         | 248 |

| C.1 | VEX options                                | 251 |

| C.2 | JINE options                               | 252 |

# List of Figures

| 2.1  | The role of the Virtual Time execution in Software Performance Engineering                                                                                                                                                              | 31 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Linux kernel components involved in block I/O (Based on [20])                                                                                                                                                                           | 59 |

| 3.1  | Real- vs Virtual Time Execution                                                                                                                                                                                                         | 64 |

| 3.2  | VEX design                                                                                                                                                                                                                              | 66 |

| 3.3  | Model of VEX thread state transitions                                                                                                                                                                                                   | 68 |

| 3.4  | Difference between trapping synchronisation events externally and within VEX .                                                                                                                                                          | 73 |

| 3.5  | Lost time and overhead compensation                                                                                                                                                                                                     | 80 |

| 3.6  | Per stack-trace profile visualisation                                                                                                                                                                                                   | 83 |

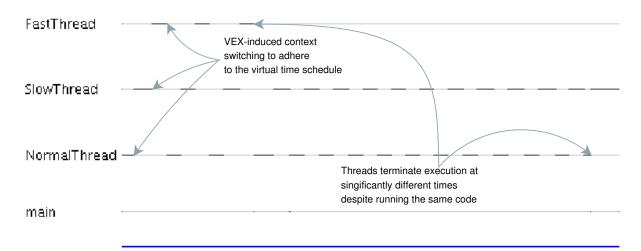

| 3.7  | Visualiser snapshot: all threads apart from main execute the same code with different virtual specifications and progress accordingly on a uniprocessor machine.  The dashes signify timeslices that a thread is in the "Running" state | 85 |

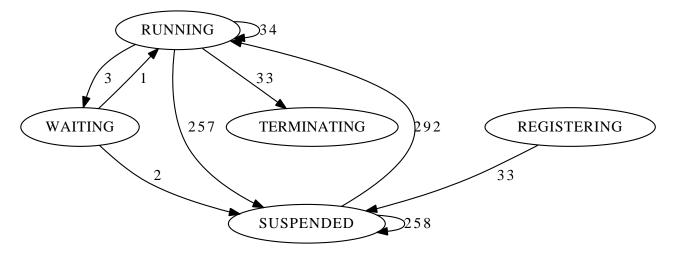

| 3.8  | A sample automatically generated state transition graph                                                                                                                                                                                 | 86 |

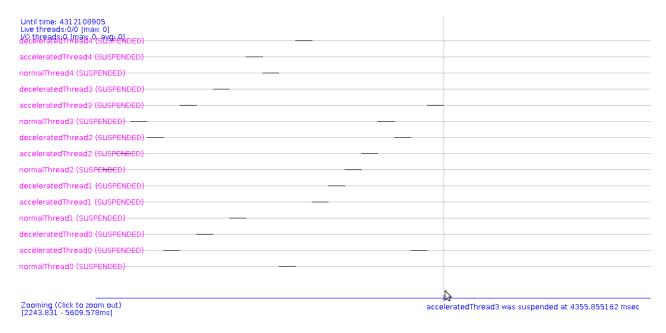

| 3.9  | Zoomed in visualisation of the scheduling sequence test as output by the VEX visualiser                                                                                                                                                 | 88 |

| 3.10 | C++ presentation of the random program executioner. The next element of execution is either a sub-method or a loop-based calculation                                                                                                    | 89 |

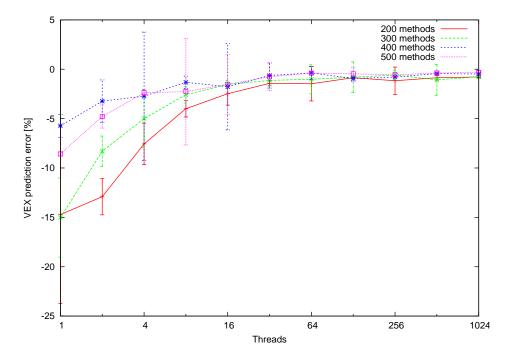

| 3.11 | Average prediction error of 10 measurements on Host-1 for 1 to 1024 threads and 200 to 500 random methods with approximate $95\%$ confidence intervals <sup>1</sup>                                                                     | 90 |

20 LIST OF FIGURES

| 3.12 | Demonstrating the effect of a single nanosecond in the lost time compensation scheme in the prediction error of VEX for three trivial short methods and two different compilation options. Results are from 100 measurements on Host-1 and                                                |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      |                                                                                                                                                                                                                                                                                           | 92  |

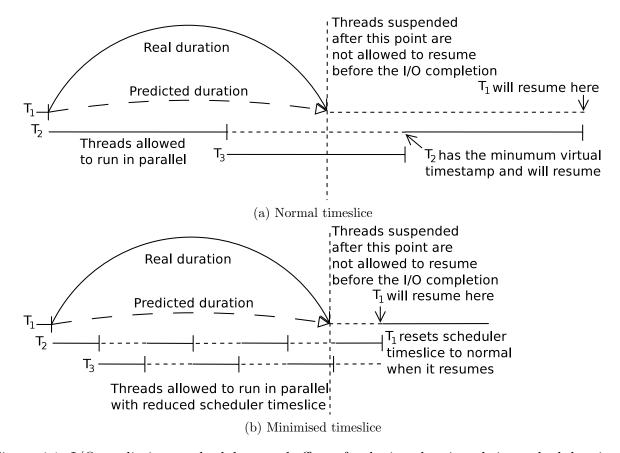

| 4.1  | I/O prediction methodology and effect of reducing the virtual time scheduler timeslice to simulate priority boosting                                                                                                                                                                      | .01 |

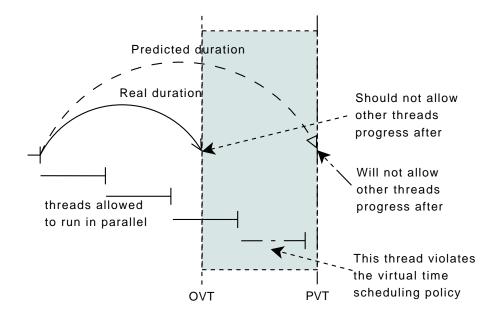

| 4.2  | I/O overprediction showing the frame where the virtual scheduling policy might be violated                                                                                                                                                                                                | .04 |

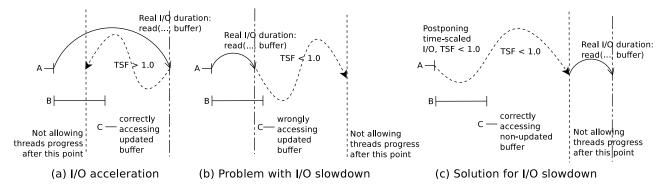

| 4.3  | Correct I/O scaling in virtual time                                                                                                                                                                                                                                                       | .06 |

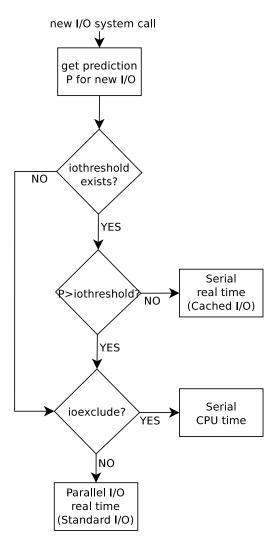

| 4.4  | Flowchart of I/O in VEX depending on user-defined parameters $\dots \dots 1$                                                                                                                                                                                                              | .08 |

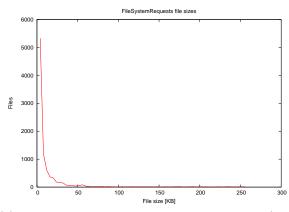

| 4.5  | Measurements on the workload of the Disk I/O benchmark                                                                                                                                                                                                                                    | 15  |

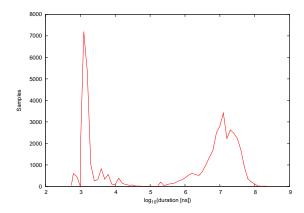

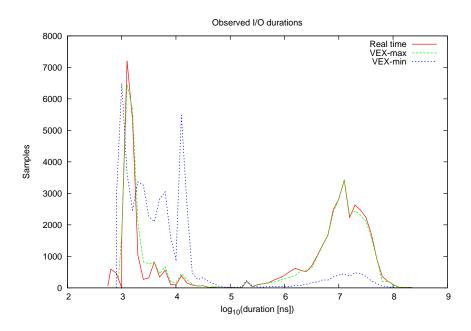

| 4.6  | Histograms of the <i>observed</i> I/O durations in the real execution and in the virtual time executions with the $max$ and $min$ prediction policies                                                                                                                                     | .19 |

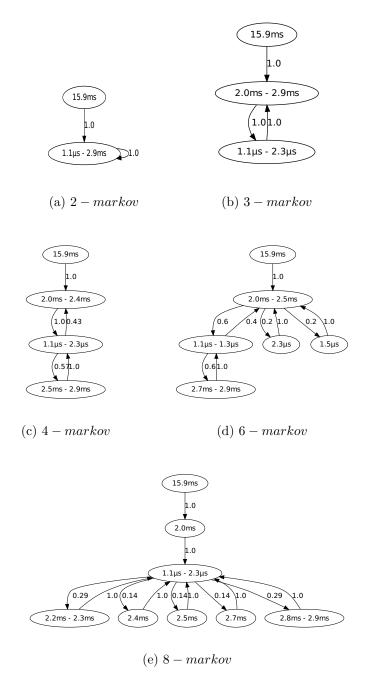

| 4.7  | Visualisation of the effect of $M$ in modelling I/O durations in a particular buffer set of $B=16$ measurements with the $M-markov$ prediction method 1                                                                                                                                   | .28 |

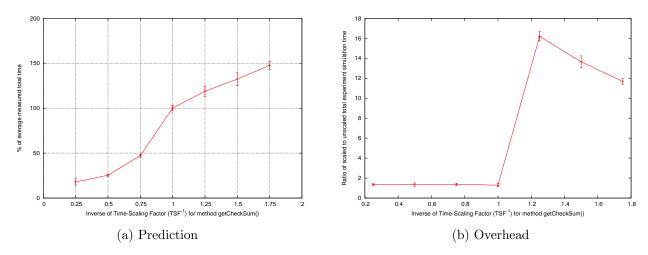

| 4.8  | Virtual time prediction as a rate to the (unscaled) real execution and overhead of the Disk I/O "memory" benchmark for various time-scaling factors $(TSF)$ . Means and (approximately) 95% confidence intervals of 7 measurements are shown 1                                            | .29 |

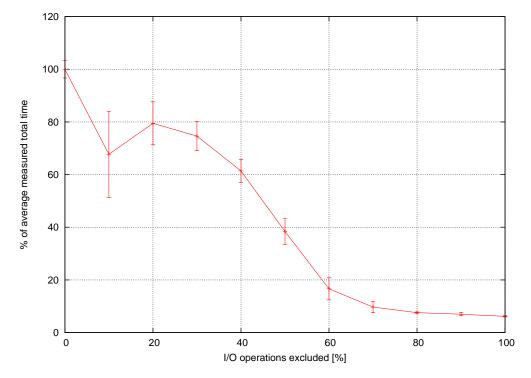

| 4.9  | Effect of I/O-exclusion in the Disk I/O "memory" benchmark (with a threshold of $50\mu s$ ). The x-axis is the percentage of recognised I/O operations, whose duration is set to be replaced by CPU-time. Means and (approximately) 95% confidence intervals of 10 measurements are shown | .29 |

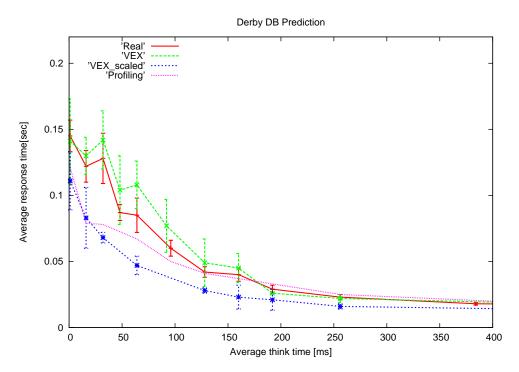

| 4.10 | Derby DB results comparing the observed average response time to the VEX prediction and the time acquired by manually scaling the results of a profiler to time-scaled VEX simulation. Means of 10 measurements with approximately 90% confidence intervals are shown                     | .30 |

LIST OF FIGURES 21

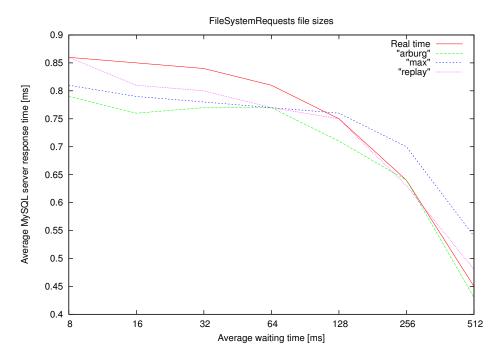

| 4.11 | MySQL DB average response times for the real-time execution and the VEX simulation with the $arburg$ , $max$ and $replay$ I/O prediction policies 130                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | JINE design on top of VEX                                                                                                                                                                                                                                                                                                                                          |

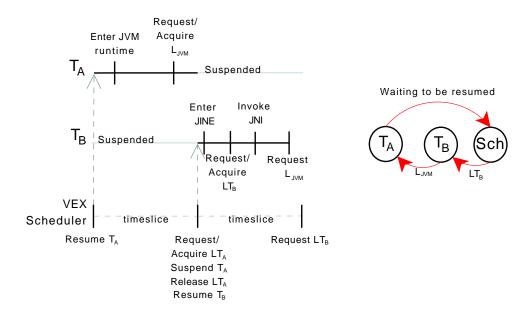

| 5.2  | Deadlock as a result of VEX scheduling and JNI invocation from JINE 149                                                                                                                                                                                                                                                                                            |

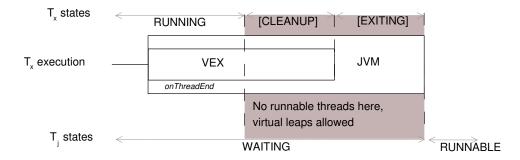

| 5.3  | Handling of joining threads in VEX to avoid virtual time leaps                                                                                                                                                                                                                                                                                                     |

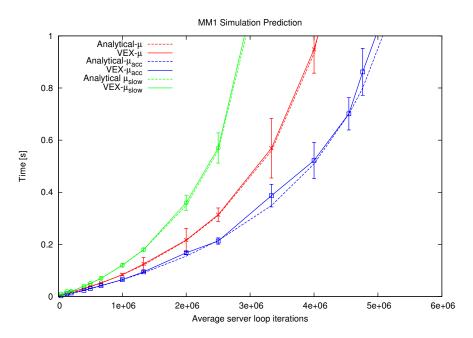

| 6.1  | M/M/1 simulation results with approximately 90% confidence intervals 167                                                                                                                                                                                                                                                                                           |

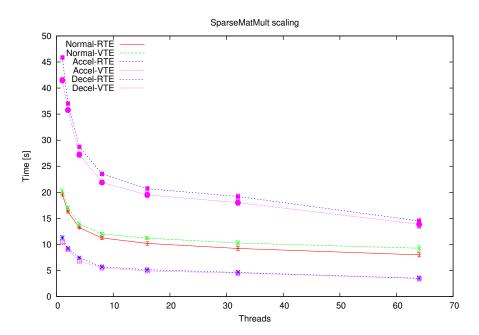

| 6.2  | Thread and time scaling results for the <i>SparseMatMult</i> benchmark of the multi-threaded JGF suite. Means of 3 measurements per thread are shown with 95% confidence intervals                                                                                                                                                                                 |

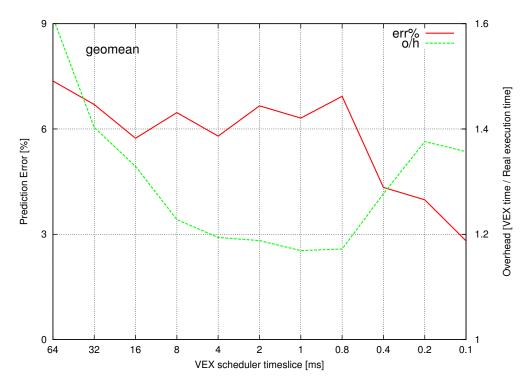

| 6.3  | Effect of the VEX scheduler timeslice on the prediction error and simulation overhead of the SPECjvm2008 benchmarks with four benchmark threads. The geometric mean of all benchmark results (using absolute values for prediction errors) are shown                                                                                                               |

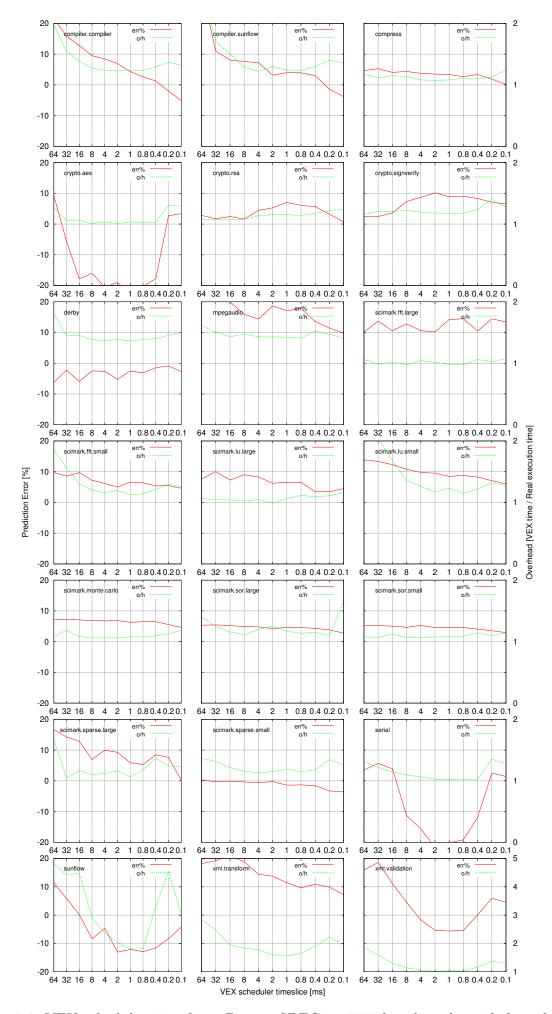

| 6.4  | VEX scheduler timeslice effect on SPECjvm2008 benchmarks with four threads . $189$                                                                                                                                                                                                                                                                                 |

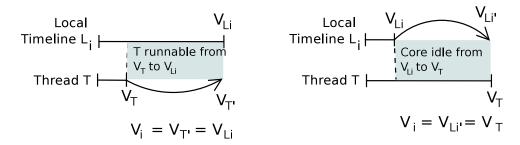

| 7.1  | The two cases of resuming thread $T$ on the local timeline $L_i$ of virtual core i 194                                                                                                                                                                                                                                                                             |

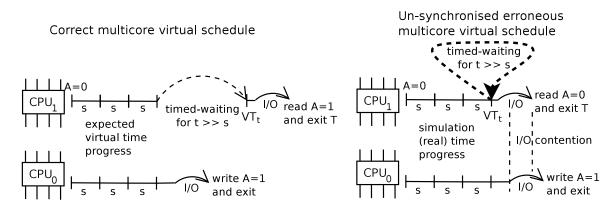

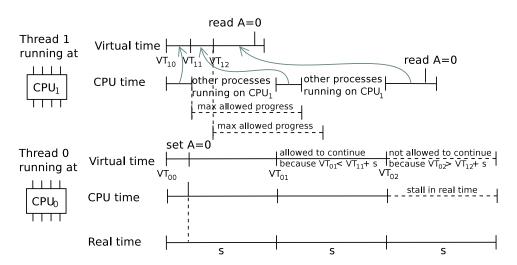

| 7.2  | Demonstration of an erroneous simulation (wrong result and artificial I/O contention), due to lack of synchronisation in multicore VEX. The thread $T$ executing at $CPU_1$ performs a virtual leap forward by $t$ : without any synchronisation mechanism this violates the correct order of execution by progressing instantaneously the virtual time of $CPU_1$ |

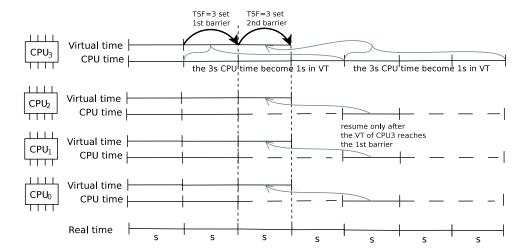

| 7.3  | Time-scaling in Lax synchronisation policy on 4 cores. By using a barrier mechanism, the accelerated thread of $CPU_3$ executes 3 times as many timeslices as the threads of the other cores, while remaining synchronised with them in virtual time                                                                                                               |

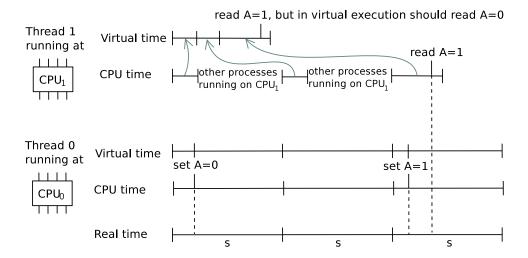

| 7.4  | Problem with lack of synchronisation between two virtual cores on a dual-core machine with background load on $CPU_1$ and the solution of $SPEX \dots 200$                                                                                                                                                                                                         |

22 LIST OF FIGURES

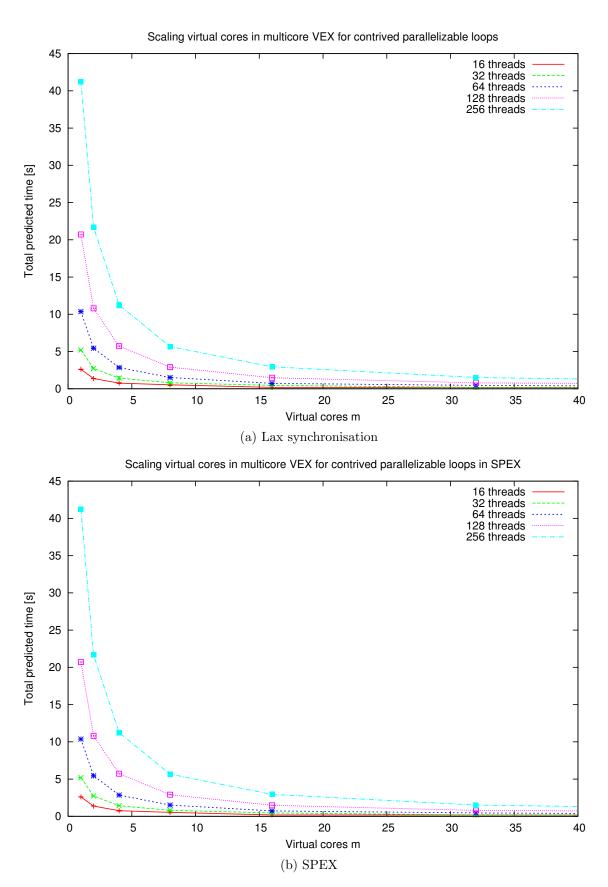

| 7.5  | Scalability of multicore VEX in terms of virtual cores $m$ on a toy example with simple loops with approximately 95% confidence intervals (3 runs)                                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

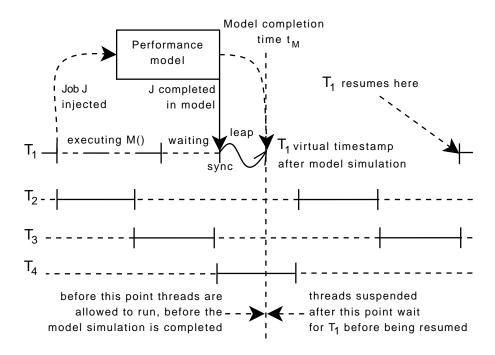

| 8.1  | Simultaneous execution of methods body and performance model (shown in real time). Thread $T_1$ triggers the arrival of a new job in the model describing method $M$ and continues to execute the body of $M$ . Other simulation threads are scheduled according to the sample method execution time, as determined by the model |

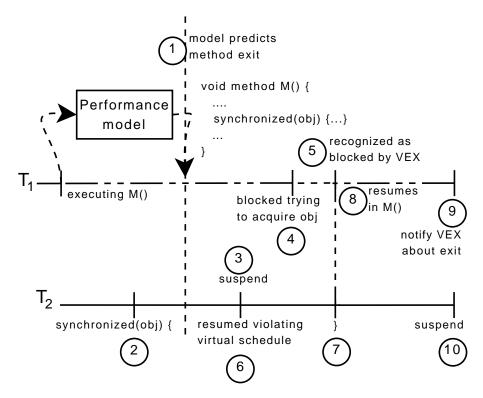

| 8.2  | Description of the scenario, where the body of a model-simulated method leads the executing thread to block: the thread is recognised as blocking by the VEX scheduler and another thread is allowed to make progress                                                                                                            |

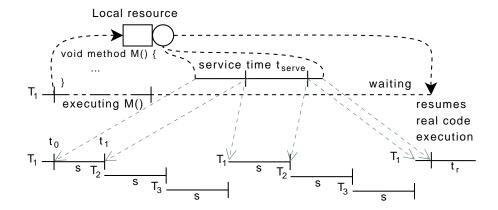

| 8.3  | Local resource simulation: $T_1$ enters a local resource and its job is scheduled in a round-robin fashion with threads $T_2$ and $T_3$ that are executing real code. The scheduling of the job concerns subtracting a timeslice from the model-estimated service time                                                           |

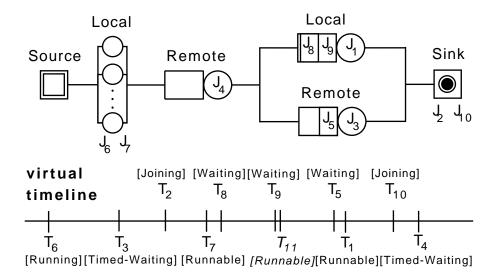

| 8.4  | Matching of VEX thread-states to the states of their jobs in a sample queueing model                                                                                                                                                                                                                                             |

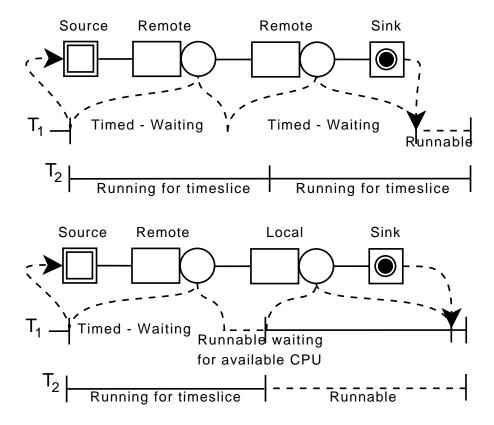

| 8.5  | Differences in virtual time scheduling after a remote resource, depending on whether the next node belongs to a local or a remote resource                                                                                                                                                                                       |

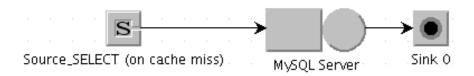

| 8.6  | demo_select.jsimg: Queueing network for the Pure model version                                                                                                                                                                                                                                                                   |

| 8.7  | Code for unimplemented select() method                                                                                                                                                                                                                                                                                           |

| 8.8  | Code for $select()$ method with implemented cache. Note that the value returned by the DB server is arbitrary (here 53 as shown)                                                                                                                                                                                                 |

| 8.9  | demo_select_only_db.jsimg: Queueing network for remote server only                                                                                                                                                                                                                                                               |

| 8.10 | Code for the implemented $select()$ method invoking method $getMySqlServerResponse$ of class $SqlDriverInfo$                                                                                                                                                                                                                     |

| 8.11 | Implementation of SqlDriverInfo.getMySqlServerResponse that makes the request to the MySQL server                                                                                                                                                                                                                                |

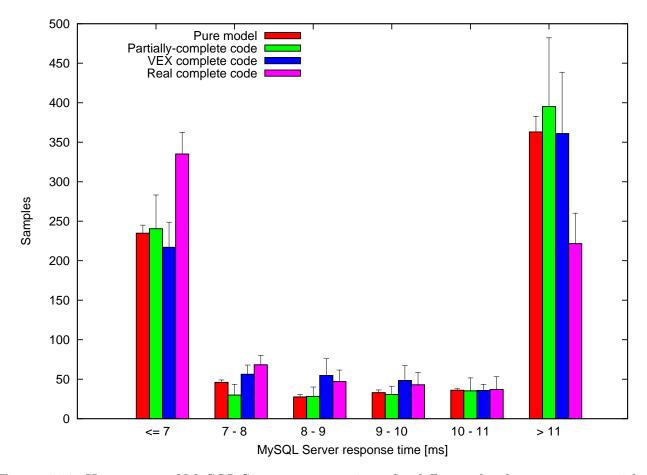

| 8.12 | Histograms of MySQL Server response times for different development stages      |

|------|---------------------------------------------------------------------------------|

|      | with 95% confidence intervals (10 runs) showing consistent results for VEX sim- |

|      | ulations and lower response times for real executions                           |

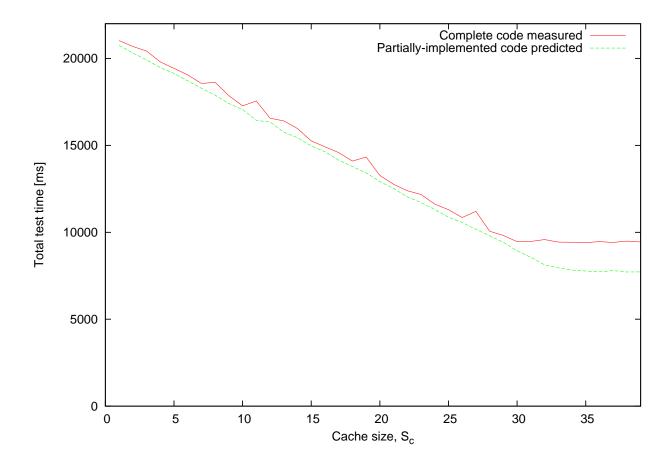

| 8.13 | Effect of cache size in VEX simulation of partially-complete code and complete- |

|      | program execution. The mean of 10 runs per $S_c$ is shown                       |

## Chapter 1

### Introduction

Software Performance Engineering (SPE) [125] regards the activities involved towards analysing, estimating and meeting performance goals for a software development project. Performance engineers identify critical use-case scenarios from software specifications and determine, together with the management and clients, the initial performance requirements of the project. At this early stage predictions on whether these objectives can be accomplished or not, rely on performance models like Queueing Networks, Generalised Stochastic Petri Nets and Stochastic Process Algebras, properly parameterised based on the expertise of the performance engineering team. Throughout the software lifecycle measurements are used to refine the model parameters to better match the implemented code and more accurately identify discrepancies with the designated performance targets. Ideally, a well-planned and continuously performance engineered software would always reach its performance goals.

Alas, SPE is not widely used in practice: a recent survey amongst IT managers [30] shows that half of them claimed to have had performance problems with at least 20% of the applications they had deployed and attributed them to poor performance engineering strategy. Due to the significant effort and cost in model selection, design, simulation and validation, performance analysis is often delayed for after the implementation completion, thus rendering SPE a post-development exercise.

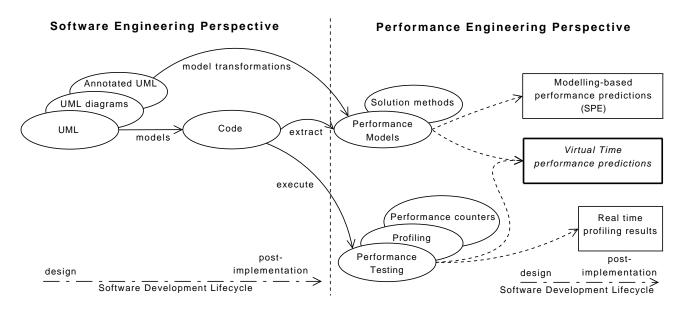

Research efforts over the last decade (as surveyed by [31], [8] and [146]) have focused on fa-

cilitating the SPE process by automatically analysing performance information and extracting performance from software engineering models (UML diagrams), appropriately extended to include non-functional attributes (like estimated response times). This approach simplifies the adoption of SPE by utilising existing architectural models, but assumes the availability of such models, a clear mapping of measurements to their components and an in-depth understanding of the application at hand.

Another common practice in performance engineering is the use of testing and profiling to identify bottlenecks in a completed system. More appropriate algorithms, caching and buffering mechanisms, code and compilation optimisations or system tuning, are then typically employed to improve the performance of critical paths, in the process of software performance optimisation. The likely effects of such optimisations on the overall performance of the software rely on the expertise of performance engineers to analyse the software behaviour, diagnose the causes of bottlenecks and suggest solutions.

Despite the many significant advances in performance modelling techniques and tools the model-based SPE methodology is currently not part of mainstream software engineering. This is in contrast to performance profiling which represents the de facto method for understanding the performance behaviour of a system, but at the post-development stage. The objective of this thesis is to develop a novel approach for lightweight integration of performance models and profiling measurements throughout the software lifecycle. Crucially, our approach facilitates the application of performance testing techniques on partially-complete software and constitutes a first step towards a new performance engineering methodology, where models and code can be used interchangeably.

### 1.1 The idea

The main idea that underpins this thesis is to simulate the execution of partially-implemented or completed programs in *virtual time*. Under the auspices of *execution-driven simulation* [32], our approach determines the progress of a program's execution, whilst profiling its performance

1.2. Contributions 27

in virtual time. Virtual time is accounted for either as a measurement of the native execution of code on the simulation host (simulating the normal execution of the program), or as a transformation of that duration (e.g. simulating time-scaling optimisation effects) or as the time predicted by a performance model. The total virtual time of the program is the performance prediction for its duration, whilst the behaviour of the application is linked to its progress in virtual time. Using dynamic instrumentation techniques, our approach is able to offer both profiling and optimisation capabilities at the method-level. No changes to the source code of the simulated program are needed, nor does the approach require the extraction of models from code or transformations of the program source code. However, we do propose an empirical prediction scheme that compensates for I/O operations and DMA behaviour.

A key objective is to avoid the need for low-level system models, such as CPU [6, 149], memory [26, 118] or I/O [2, 101] models. We are thus concerned with the understanding of the application's performance on a given host platform, essentially using the available code itself as a "model". Since one of our key contributions is a system for integrating code and models it would be straightforward in principle to integrate models of the underlying (host) system. This, however, is a whole different exercise that lies beyond the scope of this thesis.

The objective of this research is to frame our work on the SPE map, present the virtual time execution idea, create a prototype simulator, investigate the trade-offs between accuracy and overhead and evaluate the potential for future research based on this approach.

Our thesis is that the virtual execution paradigm can be used as a new software performance engineering approach, that integrates performance models and code in order to provide performance predictions of typically good accuracy and low overhead via high-level execution-driven simulation throughout the software lifecycle.

### 1.2 Contributions

In this thesis we explore the feasibility of the virtual time execution idea for software performance engineering. We introduce this methodology using a bottom-up approach: from the

scheduling and profiling aspects of virtual time execution, to the application interface and the concepts of defining and including performance models. Each chapter presents the corresponding prototype systems, elaborating on the implementation details that highlight the features and challenges of virtual time execution. Our specific contributions are as follows:

- We introduce the virtual time program execution methodology and its prototype in a language-independent Virtual time Execution (VEX) core that enforces a round-robin schedule on the threads of an existing application, as if they were executed under user-defined time-scaling specifications at the method-level. This is presented in Chapter 3.

- We describe a methodology to include I/O in virtual time, by estimating I/O durations to reproduce thread-parallelism due to DMA in virtual time. This is elaborated in Chapter 4 together with the investigation of empirically-based runtime prediction approaches for I/O durations in the VEX prototype.

- We present a system for interfacing VEX's functionalities to unmodified Java applications, called Java Instrumentation Environment (JINE). The design and implementation of the JINE and the Java-related problems encountered are elaborated in Chapter 5.

- We verify and validate VEX and JINE as measured by their ability to predict real execution times of unmodified small and medium size Java benchmarks; this is presented in Chapter 6

- We describe an extension to VEX that simulates multicore architectures, by synchronising the timelines of the virtual cores and its validation on synthetic and real benchmarks (Chapter 7)

- We propose a SPE methodology and system prototype that offers continuous performance testing throughout the lifecycle by integrating executable code and performance models (Chapter 8).

### 1.3 Publications and Statement of Originality

I declare that this thesis was composed by myself, and that the work that it presents is my own, except where otherwise stated.

The following publications arose from work conducted during the course of this PhD:

- Modelling Analysis and Simulation of Computer and Telecommunication Systems 2011

(MASCOTS) [10] discusses the idea of executing programs in virtual time as a means to

investigate the overall effect of optimising specific methods. The methodology and part

of the results presented in Chapters 3 to 6 are based on this paper.

- Quantitative Evaluation of Systems 2012 (QEST) [11] presents our approach for integrating performance models and code in virtual time. Chapter 8 is largely based on this paper.

## Chapter 2

## Background

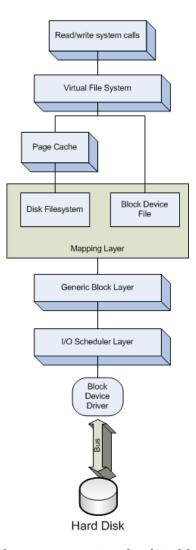

The virtual time execution approach lies at the intersection of the Software Performance Engineering (SPE) and the simulation research areas. This chapter discusses related work in these fields. As our virtual time execution requires an I/O prediction module, we present work on the black-box modelling of the I/O subsystem. A brief overview of Java, on which our virtual time implementation focuses, is also provided.

### 2.1 Software Performance Engineering (SPE)

Performance is the result of the interaction of system behaviour with resources ([146]), where by resources we refer to CPU, memory, network bandwidth, buffers and locks, threads and processes. The limited number of such resources results in the contention for their usage, which in turns leads to performance problems (bottlenecks). These can be quantified in terms of various metrics like response time, throughput or resource utilisation.

Performance analysis deals with two aspects of a system: responsiveness and scalability. The response time and the throughput constitute the main points of interest for the former, while their variations as the system load increases determine the latter. Moreover, since resource consumption affects system responsiveness and scalability, finding the optimal solution for each

Figure 2.1: The role of the Virtual Time execution in Software Performance Engineering.

system in order to satisfy the designated performance requirements, comprises a challenging task for performance engineers.