Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2012, Article ID 565827, 9 pages doi:10.1155/2012/565827

## Research Article

# **Analysis of Kink Reduction in SOI MOSFET Using Selective Back Oxide Structure**

## M. Narayanan, H. Al-Nashash, Baquer Mazhari, Dipankar Pal, and Mahesh Chandra

- <sup>1</sup> Department of Electrical Engineering, American University of Sharjah, P.O. Box 26666, Sharjah, UAE

- <sup>2</sup> Department of Electrical Engineering, Indian Institute of Technology, Kanpur 208016, India

- <sup>3</sup>NERIST, Nirjuli, 791109, Itanagar, India

Correspondence should be addressed to M. Narayanan, mnarayanan@aus.edu

Received 1 March 2012; Accepted 9 May 2012

Academic Editor: Daisaburo Takashima

Copyright © 2012 M. Narayanan et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

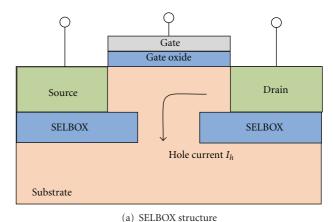

This paper presents a complete analysis of the kink effect in SOI MOSFET and proposes a method for eliminating kink effect observed in the current-voltage output characteristics of a partially depleted SOI MOSFET device. In this method, back oxide for the device is introduced at selected regions below the source and drain and not continuously as in an SOI device giving rise to what is termed a "SELBOX" structure. Selective back oxide structure with different gap lengths and thicknesses was studied. Results obtained through numerical simulations indicate that the proposed structure can significantly reduce the kink while still preserving major advantages offered by conventional SOI structure. Although the new structure is capable of eliminating kink, for narrow gaps the device may still exhibit some kink effect. A device model that explains the kink behavior of the structure for varying gap lengths is also developed.

#### 1. Introduction

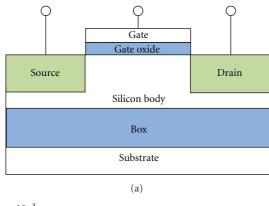

Silicon on insulator (SOI) MOSFET is fabricated on wafers consisting of a film of crystalline silicon separated by a layer of SiO<sub>2</sub> from the bulk substrate as shown in Figure 1(a). SOI MOSFETs offer several advantages as compared to bulk MOSFETs such as excellent lateral and vertical isolation, improved latch up free operation, reduced leakage current, reduced short channel effects, and improved switching speeds due to reduction in the drain-body capacitance [1]. SOI MOSFETs are divided into partially and fully depleted-SOI devices. The depletion region of the partially depleted (PD) SOI devices does not reach through the entire silicon channel/body region. PD SOI devices have silicon thickness greater than  $\sim 0.15 \,\mu\text{m}$ . The depletion region extends into the body of the device under the gate at the source body and drain-body junctions and does not deplete all of the charges in the body, resulting in the name partially depleted SOI. Partially depleted devices are often labeled as thick film. In case of fully depleted (FD) SOI devices, the silicon thickness is thinner than the silicon thickness of the partially depleted devices. The background doping of the channel

region is lower than the partially depleted devices. Usually the thickness is in the range of few tens of nanometers. These devices are called as thin film [2].

In PD SOI devices, the thickness of top Si layer is around 300 nm. The fabrication process for such devices is totally compatible with that of the bulk silicon technology. As a result, the design for bulk silicon devices can be easily transferred to PD SOI technology [3]. Fabrication of FD SOI devices involves development of ultrathin body and, therefore, needs more sophisticated technology. The threshold voltage in PD SOI devices is relatively less sensitive to the uniformity in the silicon film thickness. In FD SOI device, the threshold voltage depends on the Si film thickness [4]. It is difficult to control the thickness of the ultra thin film body in FD SOI MOSFETS, and as a result, the film thickness becomes nonuniform across the wafer. For these reasons, there has been a growing interest in PD SOI MOSFETS.

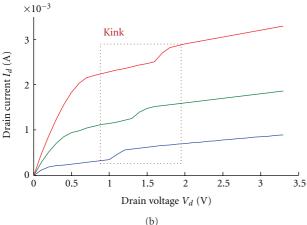

In spite of these benefits, PD-SOI MOSFET devices are accompanied with certain undesirable effects such as kink [3] in the output current-voltage characteristics as given in Figure 1(b). The kink effect is observed in partially depleted

<sup>&</sup>lt;sup>4</sup> Birla Institute of Technology, Mesra, 835 215 Ranchi, India

FIGURE 1: (a) SOI MOSFET structure and (b) Kink effect in Output characteristics.

SOI MOSFET devices. In these devices, the electric field near the drain region will be high due to relatively higher drain voltages. Consequently, the channel electrons in the high electric field acquire high energy and create electronhole pairs by impact ionization mechanism. The generated electrons are collected by the drain and the holes accumulate in the floating body. The accumulation of the holes in the floating body leads to an increase in the body potential, and the associated drop in the threshold voltage leads to a sharp increase in the drain current [2]. The increase in drain current further leads to an increase in the number of holes generated. This cumulative process will continue until the body source junction is forward biased, allowing the holes to exit the device. Consequently, the device will not be suitable for linear applications due to the nonlinearity created by the kink effect.

The second observation is that SOI devices are thermally insulated from the substrate by the buried insulator with very low thermal conductivity. As a result, removal of excess heat generated within the device is less efficient than in bulk devices [3]. This leads to a substantial elevation of device temperature and a reduction in the channel mobility.

A classical remedy for the problems due to floating body is to provide a body contact or a body tie in these devices [2]. Even though body tie can eliminate the kink effect, it will be at the cost of die area [2]. Further, effectiveness

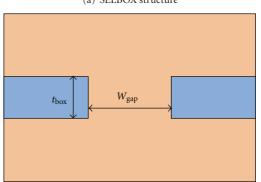

(b) Back oxide gap parameters, ( $t_{box}$ ): SELBOX Thickness, ( $w_{gap}$ ): Gap length

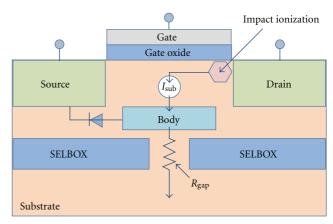

FIGURE 2: SELBOX MOSFET structure.

of body tie is much less pronounced as these contacts will introduce body charge and discharge time constants. Another method to reduce the floating body effect involves controlling the carrier lifetime in the floating body region of an SOI MOSFET by high-dose silicon implantation. The carrier lifetime in polysilicon is much shorter than that in the single crystal silicon. Ion implantation leads to amorphization of the silicon and creates recombination centers below the channel region close to the interface between the Si layer and the BOX layer. These recombination centers reduce the lifetime of excess carriers generated due to impact ionization during device operation and minimize the hole accumulation in NMOSFET device thus suppressing the kink effect. But, in this method, the drive current is reduced, due to reductions in the channel mobility resulting from the lattice damage [5].

An alternative solution for eliminating the floating body effect is the use of selective back oxide (SELBOX) structure [6] as shown in Figure 2(a). In this structure, the buried oxide covers the channel partially. It offers the prospect of combining the advantages of SOI and bulk devices. With a proper selection of oxide gap length, the kink effect and self-heating effect can be greatly reduced. The structure discussed here can provide enhanced performance by using SELBOX gap  $(w_{\rm gap})$  and back oxide thickness as an additional degree of freedom for device optimization. Figure 2(b) indicates the back oxide gap parameters. Oxide thickness  $(t_{\rm box})$  is the

thickness measured in the *y*-direction. Distance between the oxide block edges in the horizontal direction is taken as the gap length ( $w_{gap}$ ).

The feasibility of the fabrication of MOS devices with SELBOX structure and simulation has been already reported [6–8]. Simulation studies demonstrate the improvements in the threshold voltage roll-off with the SELBOX structure [8]. The present work describes the effectiveness of the SELBOX structure for reducing the kink in the output characteristics of a SOI MOSFET device. In addition, a device circuit model that explains the kink behavior of the SELBOX structure is also proposed.

The paper is divided into five sections. Section 1 explains some of the limitations of the SOI MOS devices and introduces SELBOX MOSFET as a solution to overcome these limitations. The method of implementation of the structure is discussed in Section 2. Observations and results obtained from the studies of the new structure are included in Section 3. Section 4 explains the details of a proposed model for the SELBOX structure. Finally, conclusion and future work is included in Section 5.

## 2. Methodology

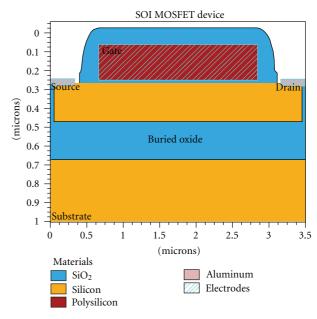

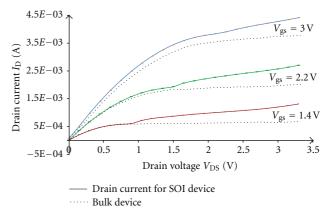

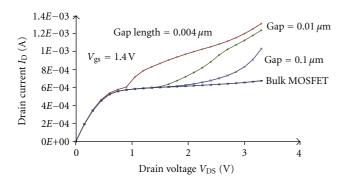

A schematic of partially depleted SOI MOSFET structure that was simulated is shown in Figure 3. The dimensions and doping concentration for the device structure considered for simulation are selected on the basis of a typical SOI device with channel length of 2.0  $\mu$ m and gate oxide thickness of 0.01 µm [9]. The p-type substrate is doped with doping concentration of  $\sim 2 \times 10^{17} \, \text{cm}^{-3}$  and source and drain regions of  $\sim 10^{19} \, \text{cm}^{-3}$ . The total device length including source, channel, and drain is 3.5 µm. Device dimensions and doping concentrations are selected according to the values available in the published work [9] in order to compare and verify the results. Silvaco tools are used for process and device simulation. Silvaco athena provides an easy way to use platform to simulate semiconductor fabrication processes, while Silvaco atlas is used to simulate the electrical characteristics of the semiconductor device under study. Numerical simulation was carried out using athena and atlas tools from Silvaco [10]. Based on literature for SOI devices, field-dependent mobility model, Shockley-Read-Hall recombination, and impact ionization model from Selberherr [11] are used for the simulation. Numeric methods chosen for simulation are Gummel and Newton methods. Figure 4 illustrates a typical output characteristics obtained for partially depleted SOI MOSFET device using atlas simulations. For bulk MOSFET with identical device dimensions and doping concentration, the simulated output characteristics is shown in Figure 4 with dotted lines.

Presence of kink in the output characteristics for SOI structure is clearly visible. The onset of kink takes place at a kink voltage ( $V_{\rm kink}$ ) of 1.5 V for gate-source voltage of 2.2 V.

The simulated output characteristics for a SELBOX device, the structure of which is explained with Figure 2, is given in Figure 5. This structure is identical to the bulk MOSFET device with the only difference being the presence of back oxide partially covering the channel. The SELBOX

FIGURE 3: SOI MOSFET structure.

FIGURE 4: Output characteristics of MOSFET and SOI MOSFET.

thickness is  $0.4 \,\mu\text{m}$ . The kink can be effectively reduced even with a small gap in the back oxide. To study the effect of changes in the gap length on the kink voltage, the gap lengths are chosen as  $0.004 \,\mu\text{m}$ ,  $0.01 \,\mu\text{m}$ , and  $0.1 \,\mu\text{m}$ . The kink voltage is found to be increasing with increase in the gap length. It is noticed that the plot for a gap length of  $0.3 \,\mu\text{m}$  and that of bulk structure coincide and the kink completely disappears.

### 3. Results

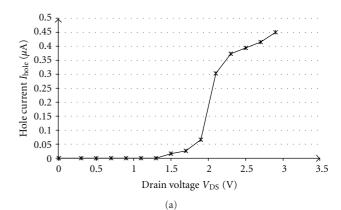

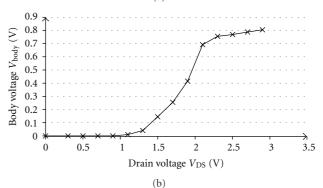

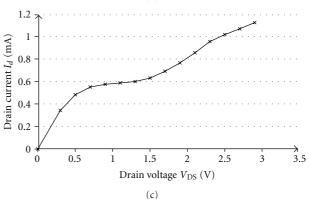

3.1. Kink Effect in SELBOX MOSFETs. The basic mechanism that leads to the kink in the output characteristics of a SELBOX structure with a gap length of  $0.02\,\mu\mathrm{m}$  and back oxide thickness of  $0.4\,\mu\mathrm{m}$  is illustrated below in Figure 6. The simulation is carried out for  $V_{\rm gs} = 1.4\,\mathrm{V}$  by atlas device simulator, and the results are given in Figures 6(a), 6(b), and 6(c). Figure 6(a) shows the hole current through the gap to the substrate, Figure 6(b) shows the body voltage

FIGURE 5: SELBOX output characteristics for  $V_{\rm gs}=1.4\,{\rm V}$  with varying gap lengths.

across the gap resulting from the hole current through the gap resistance, and Figure 6(c) shows the kink in the output characteristics, which results due to the increase in the body voltage. At higher drain voltages, the channel electrons acquire energy in the high electric field zone near the drain. These high energy electrons generate electron hole pairs through impact ionization in the region close to the drain [12]. The electrons generated will be collected by the drain, and the holes move towards the substrate through the back oxide gap. Figure 6(a) shows that the hole current starts increasing for a drain voltage close to 1.5 V indicating that the impact ionization starts for  $V_{\rm DS}$  close to 1.5 V. The hole current is measured from the hole current density in the SELBOX gap region and by subsequent integration of the current density. For narrow gap lengths, the resistance of the gap for the hole current will be much higher than the lateral channel resistance from drain to the gap. For the hole transport from the region close to drain to the substrate through the gap, the resistance in the device body region is negligibly small compared to the resistance of the narrow gap. The flow of holes through the gap resistance leads to the development of a potential across the gap, which leads to an increase in the body potential as indicated in Figure 6(b). The body potential is measured across the BOX gap. For extremely narrow gap lengths as the gap resistance is large, the hole current through the gap will be associated with a rise in the body potential, which will be sufficient to give rise to a kink in the drain current as indicated in Figure 6(c). This increase in the body potential continues till the body-source junction gets forward biased for the body voltage close to 0.7 V as shown in Figure 6(b).

3.2. Effect of Changes in Gap Length on Kink Voltage. The output characteristics of a SELBOX structure for varying gap lengths for a gate to source voltage  $V_{\rm gs}=1.4\,\rm V$ . is depicted in Figure 5. The increase in the gap length from  $0.004\,\mu\rm m$  to  $0.1\,\mu\rm m$  results in an increase in the kink voltage. For increased gap lengths, the kink occurs at a higher drain voltage because an increase in the gap length leads to a decrease in the gap resistance. Consequently, the body voltage can rise to the level required for the occurrence of kink for a larger hole current  $(I_h)$  only, and this is possible at a higher drain voltage. Eventually, for larger values of gap lengths, the kink will completely disappear.

FIGURE 6: Kink effect in SELBOX MOSFET.

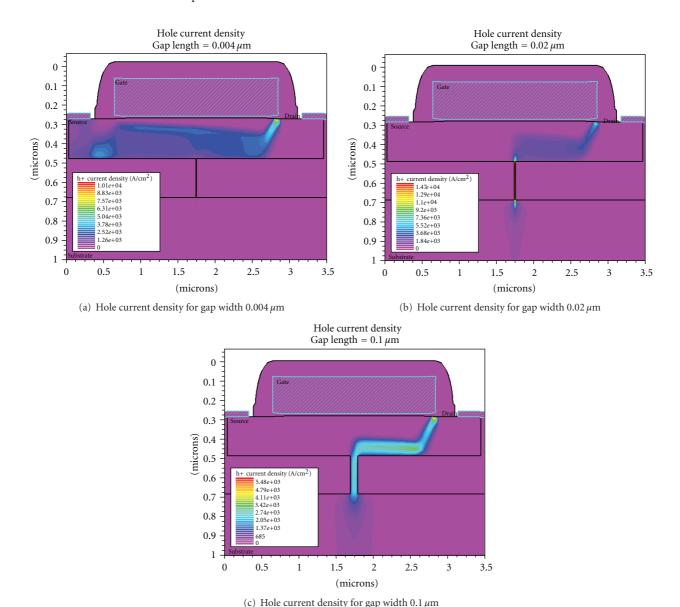

The mechanism that leads to the kink in the output characteristics of a SELBOX structure is illustrated with the hole current density (blue shade) as shown in Figure 7(a). The oxide thickness in all cases in Figure 7 is  $0.2 \,\mu\text{m}$ . For narrow gap lengths, the device still behaves like an SOI device because the narrow gap is inadequate to drain the holes to the substrate. Therefore, the accumulation of holes in the body region will continue till the body source p-n junction gets forward biased. With increased gap length, the number of holes getting drained to the substrate increases, which results in an increased kink voltage. This is illustrated in Figure 7(b). For still higher gap lengths as in Figure 7(c), majority of the holes are getting drained to the substrate and hence the kink will be minimum.

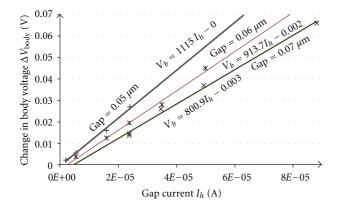

For a SELBOX MOSFET, a plot of change in body voltage  $\Delta V_b$  versus hole current  $I_h$  through the gap for different

FIGURE 7: Silvaco simulation results indicating the hole current density in SELBOX MOSFET through the oxide gap for varying gap lengths.

gap lengths is given in Figure 8. The coefficient of  $I_h$  in the equations for the lines indicates the gap resistance. The plot illustrates that with increase in the gap length the slope of the line decreases, which is an indication for a proportional reduction in the gap resistance. With decrease in the gap resistance, the rise in the body voltage due to the flow of holes generated during impact ionization is expected to reduce. This is the principle behind the elimination of kink effect with the proposed structure.

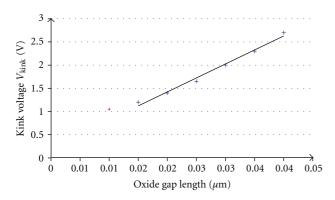

Simulation results indicate that the kink voltage increases with increase in the gap length and completely vanishes for higher gap lengths. The dependence of kink voltage on back oxide gap length was investigated keeping all other parameters constant at a gate-source voltage 1.4 V. Figure 9 shows that kink voltage increases with increase in the gap length implying a reduction in the kink effect. The kink voltage becomes larger than 3 V for a gap length of  $0.1 \,\mu m$ .

This indicates that with oxide underneath all of source, drain, and more than 95% of the channel, kink effect can be virtually suppressed. For further increase in gap length, the device remains kink-free, tends to look more like a bulk MOSFET and thus less likely to have other advantages associated with SOI.

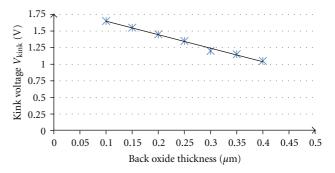

3.3. Effect of Changes in Back Oxide Thickness on Kink Voltage. The kink voltage is found to have a significant dependence on the thickness of the back oxide in a SELBOX structure. Figure 10 shows the dependence of kink voltage on back oxide thickness for a fixed gap length of  $0.03 \, \mu \text{m}$ . Keeping the gap length constant, if we vary the back oxide thickness we can expect a change in the gap resistance. For the estimation of gap resistance, back oxide thickness  $(t_{\text{box}})$  is the length of the resistance and the gap length  $(w_{\text{gap}})$  is the width of the gap resistance. As we increase the back oxide thickness keeping

FIGURE 8: Plot of  $\Delta V_b$  versus  $I_h$ .

FIGURE 9: Dependence of kink voltage on gap between the oxide regions. (SELBOX thickness is  $0.4 \, \mu m$ ).

the gap length ( $w_{\rm gap}$ ) constant, the effective gap resistance increases. This will lead to an increase in the body potential. Consequently, the body potential at which kink occurs will be reached at a lower drain voltage. With reduced oxide thickness, the back oxide gap resistance also reduces and the rise in the body voltage will be reduced. In this case, the body voltage needed to cause the kink will occur at a higher drain voltage and hence the kink voltage will be higher. Therefore, a device with thinner back oxide is more bulk-like and will be less susceptible to kink phenomenon.

Even though a very small gap length is required to virtually eliminate kink phenomenon from the device characteristics, producing a small gap length can be technologically challenging [9]. Fabrication of devices with large gap length is likely to be easier. But, with increase in the gap length, the device tends to become more bulk-like and thus lose the associated advantages of SOI such as reduced source-body and drain-body capacitances.

## 4. Device Circuit Model

In this section, we introduce device model that explain the mechanism which leads to the rise in the body potential within the SELBOX structure, which leads to the kink in the output characteristics. Figure 7 indicates the possible directions for hole current through the SELBOX structure.

FIGURE 10: Dependence of kink voltage on oxide thickness. (SELBOX Gap is 0.03 µm).

FIGURE 11: Device model units.

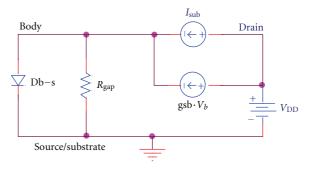

When the SELBOX gap is sufficiently wide, the majority of the generated holes will leave the body to lower substrate region through the oxide gap as shown in Figure 7(c). The device under such circumstances behaves like a bulk device as far as the kink is concerned. The events following the impact ionization inside the SELBOX device are shown in Figure 11. The diode between the body region and source represents the body-source p-n junction. The current source  $I_{\text{sub}}$  represents the hole current generated due to the impact ionization, and  $R_{\text{gap}}$  indicates the back oxide gap resistance. A gradual reduction in the gap length  $(w_{gap})$  keeping the gap thickness constant leads to an increase in the gap resistance. Consequently, a proportionate increase in the body voltage is expected for the same  $V_{\rm gs}$  and impact ionization current. For larger gap resistance resulting from extremely narrow gap lengths, the rise in the body voltage will be sufficient enough to forward bias the body-source diode, and a portion of the impact ionization holes will pass through the forward biased *p-n* diode to the source terminal.

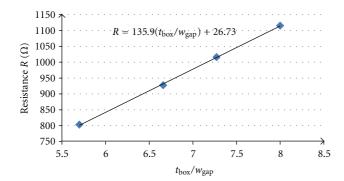

A plot of gap resistance against  $(t_{\text{box}}/w_{\text{gap}})$  for the SELBOX structure is given in Figure 12. The coefficient K of the ratio  $(t_{\text{box}}/w_{\text{gap}})$  is a characteristic for a given device and represents the gap resistivity. K is the slope of the line given in Figure 12. The value of K for the device is extracted from the graph, and the value depends on the device dimensions and doping concentration. It has unit in  $\Omega$ .

FIGURE 12: Plot of *R* versus  $(t_{\text{box}}/w_{\text{gap}})$ .

FIGURE 13: Plot of  $\ln \left[ I_{\text{sub}} / \left\{ I_d^* (V_{ds} - V_{d \text{ sat}}) \right\} \right]$  versus  $\left[ 1 / (V_{ds} - V_{d \text{ sat}}) \right]$ .

Table 1: SELBOX parameters.

| Oxide thickness $[t_{\text{box}}]$                  | 0.4 μm                          |

|-----------------------------------------------------|---------------------------------|

| Oxide gap length $[w_{gap}]$                        | $0.04\mu\mathrm{m}$             |

| Estimated gap resistance $R_{\text{gap}}$ using (2) | $1346\Omega$                    |

| g <sub>sb</sub> from Figure 14                      | $3 \times 10^{-5} \mathrm{A/V}$ |

In the present case, ( $t_{\rm box}$ ) is maintained at 0.4  $\mu$ m and the gap length is varied from 0.07  $\mu$ m to 0.05  $\mu$ m. K for the device is found to be 135.9 $\Omega$ . The term 26.73 appearing in the expression for R in the graph is due to the nonuniform distribution of the current density at the edges of the gap and also within the gap. It represents an error varying between 2.4–3.3% of the resistance value.

Figure 11 also explains the kink behavior of the device with the variations in the gap length. The hole current through the gap to the substrate results in the development of a voltage across the gap say  $\Delta V_b$ . This change in the body voltage  $\Delta V_b$  across the gap due to the hole current  $I_h$  is

$$\Delta V_b = R_{\rm gap} I_h, \tag{1}$$

where  $R_{\text{gap}}$  is the gap resistance.

Equation (1) helps us to interpret the kink behavior of the SELBOX structure. For large gap lengths ( $w_{\rm gap}$ ) in the back oxide, the gap resistance  $R_{\rm gap}$  will be very small and the substrate current will not lead to considerable rise in the body potential. As the body voltage remains fairly constant

FIGURE 14: Plot for dependence of substrate current on body voltage.

FIGURE 15: Device circuit model.

TABLE 2: Voltage values.

| Applied $V_{\rm ds}$ | Applied $V_{\rm gs}$ | Measured voltage across gap (From simulation results) |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| 2.48 V               | 1.4 V                | 0.015 V                                               |  |

in this case, the device behaves like a bulk MOSFET. If the gap length  $(w_{\rm gap})$  is reduced, the hole transport to the substrate through the gap rises the body voltage. The change in the body voltage  $\Delta V_b$  leads to the kink in the output characteristics. Gradual reduction in the gap lengths  $(w_{\rm gap})$  while maintaining  $(t_{\rm box})$  constant will result in an increase in  $R_{\rm gap}$  and the kink will occur at lower drain voltages. This can be seen in Figure 9.

For a certain  $V_{\rm gs}$ , the resulting hole current is constant at a certain drain voltage. An increase in the gap length  $(w_{\rm gap})$  leads to a decrease in the gap resistance  $R_{\rm gap}$ . The kink will therefore occur at larger drain voltages. In the same way, equation (1) can explain the nature of plot given in Figure 10 for variations in the kink voltage with thickness variations  $(t_{\rm box})$ . Increasing values of  $(t_{\rm box})$  indicate an increase in  $R_{\rm gap}$ . Therefore, the body voltage required for the occurrence of kink can result from a lower substrate current or in other words the for a lower drain voltage. Hence the kink results at a lower drain voltage.

Table 3: Hole current through the gap  $I_{\text{sub}}$ .

| Estimated $I_{\text{sub}}$ using (4) | Estimated $\Delta I_{\text{sub}}$ due to body voltage from the graph given in Figure 14 | Estimated $I_h$ from gap voltage and gap resistance using (1) | Gap current $I_{\text{sub}}$ (from simulation results) |

|--------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|

| 10.16 μΑ                             | $0.45\mu\mathrm{A}$                                                                     | 11.14 μΑ                                                      | 11.9 μΑ                                                |

For a SELBOX structure with a known dimension, we can estimate gap resistance  $R_{gap}$  with the following expression:

$$R_{\rm gap} = K \frac{t_{\rm box}}{W_{\rm gap}}.$$

(2)

The estimated resistance of the back oxide gap can be further used to find the change in body voltage for a given change in the substrate current.

The body to source diode shown in Figure 11 behaves like a normal p-n diode.

The diode current for the body to source diode is given by [13]

$$I_D = I_S e^{(V_{bs}/nV_t)}. (3)$$

$I_s$  for the body to source diode existing in the SELBOX structure used for simulation is found to be  $1.3 \times 10^{-15}$ ; A from simulation and value of n is found to be 1.3. This device will be forward biased, and conduction through this p-n junction will only be for extremely narrow gaps.

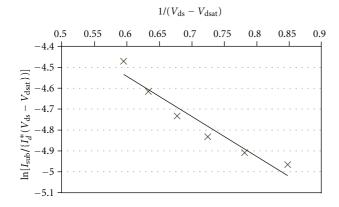

The substrate current  $I_{\text{sub}}$  generated due to impact ionization near the drain is empirically related to the drain voltage  $V_{\text{ds}}$  as given by [14]

$$I_{\text{sub}} = C_1 [V_{\text{ds}} - V_{d \, \text{sat}}] I_d \exp \left[ \frac{-C_2}{(V_d - V_{d \, \text{sat}})} \right],$$

(4)

where  $V_{d\,\text{sat}}$  is the drain saturation voltage and  $C_1$  and  $C_2$  are empirical constants [15]. The units of  $C_1$  and  $C_2$  are  $V^{-1}$  and V, respectively. Values of  $C_1$  and  $C_2$  are extracted from the characteristics of the device.  $C_1$  is a function of oxide thickness  $t_{\text{ox}}$ , substrate doping concentration  $N_{\text{sub}}$ , and junction depth  $X_j$ .  $C_2$  is obtained from the slope of the line in Figure 13.  $C_1$  is derived from the y-intercept of the line in the plot given in Figure 13, which can be also obtained from the equation for the line.

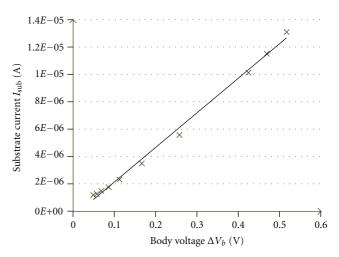

Equation (4) shows the dependence of  $I_{\rm sub}$  on the drain voltage. The impact ionization leading to the generation of  $I_{\rm sub}$  depends on the electric field near the drain. In addition to the drain voltage, the body voltage of the device will also contribute to the overall electric field near the drain, which determines the impact ionization. The dependence of impact ionization on the body voltage can be estimated in terms of the change in the substrate current due to the body voltage while keeping the other voltages in the device constant. A plot for the change in the substrate current for known changes in the body voltage is given in Figure 14. The slope of the line in the graph  $g_{\rm sb}$  can be used to estimate the changes in the substrate current for body voltage variations. For the device under study,  $g_{\rm sb}$  is found to be  $3 \times 10^{-5}$  A/V.

The above device analysis led to the development of circuit model shown in Figure 15. The current generated by impact ionization is represented by the source  $I_{\text{sub}}$ . The body

voltage-dependence of the substrate current is shown by the voltage dependent current source  $g_{sb} \cdot v_b$ , the diode represents the body-source p-n junction, while  $R_{gap}$  is the gap resistance.

For oxide gap with small dimensions, the channel resistance will be negligibly small compared to the gap resistance. As the hole current resulting from impact ionization is a function of the drain voltage, for a certain drain voltage the hole current generated will be fixed. For increased values of  $(w_{gap})$ , there will be a corresponding decrease in  $R_{gap}$ . Therefore, the required value of body voltage across  $R_{\text{gap}}$ that can lead to a kink will result at a higher drain voltage. Consequently, the kink voltage increases with gap length  $(w_{\rm gap})$  as given in Figure 9. In a similar fashion keeping  $(w_{\rm gap})$ constant if  $(t_{box})$  is increased, we can expect an increase in  $R_{\rm gap}$ . With increase in  $(t_{\rm box})$  as  $R_{\rm gap}$  increases, the required body voltage for the occurrence of kink can result even from smaller hole currents or at lower drain voltages as indicated in Figure 10. Therefore, the drain voltage at which kink occurs reduces with increase in the values of  $(t_{\text{box}})$ .

Results obtained from the verification of the circuit model for the SELBOX structure are summarized in Tables 1, 2, and 3.

The estimated substrate current  $I_{\rm sub}$  and the increment in the substrate current due to the changes in the body voltage  $\Delta I_{\rm sub}$  is 10.6  $\mu$ A. This is very close to the substrate current obtained by using the gap voltage and gap resistance  $I_h$  (11.14  $\mu$ A) and the  $I_{\rm sub}$  (simulation) obtained from the device simulation.

## 5. Conclusion

Partially depleted SOI MOSFET devices exhibit a nonlinearity in the output current voltage characteristics. This abrupt rise in the drain current known as kink results because of the changes in the body voltage of the device due to the accumulation of holes on the floating body. The effectiveness of SELBOX structure in eliminating the kink in the output characteristics of a partially depleted SOI MOSFET device is investigated. Simulation of SELBOX structure using Silvaco Athena and Atlas was performed. It is found that the kink in the output characteristics for a  $0.4\,\mu\mathrm{m}$  thick partially depleted SOI MOSFET can be virtually eliminated with a very narrow gap of  $\sim 0.1\,\mu\mathrm{m}$  in back oxide. This indicates that with oxide underneath all of source, drain, and more than 95% of the channel, kink effect can be virtually suppressed.

The effect of gap length, SELBOX thickness and body voltage on the kink voltage was investigated. A device model is proposed, which explains the basic mechanism that leads to the presence of kink even with SELBOX gap. The model includes the modulation effects of body voltage on the impact ionization and generation of holes. For a given drain voltage, the substrate current generated by impact ionization

and the estimated gap current are found to be agreeing well with those found from simulation.

The SELBOX structure has several advantages over the bulk MOS and SOI devices. It is verified in this paper that the kink effect can be completely eliminated while preserving the advantages of SOI. The preliminary results on the frequency response of the SELBOX structure demonstrate that the transition frequency  $f_T$  of these devices is larger than that of the bulk MOS devices with similar dimensions. Further, investigations on the thermal characteristics indicate that the peak temperature of SELBOX structures during the device operation is considerably lower than the SOI devices with similar dimensions. However, SELBOX structure has limitations. With increasing gap length, the device will be kink-free but tends to behave more like a bulk MOSFET, and hence, less likely to have other associated advantages of an SOI like reduced drain to substrate and source to substrate capacitances. Introduction of high quality BOX layer below the source and drain regions with narrow gaps under a single MOSFET will require additional process steps. With higher process complexity, there will be an associated increase in the cost as well. Work is in progress on the self-heating effects and frequency characteristics of SELBOX device.

#### References

- [1] J. B. Kuo and S. C. Lin, Low-Voltage SOI CMOS VLSI Devices and Circuits, John Wiley & Sons, 1st edition, 2001.

- [2] A. marshall and S. Natarajan, SOI Design: Analog, Memory and Digital Techniques, Kluwer Academic Publishers, 2001.

- [3] K. Bernstein and j. Norman, SOI Circuit Design Concepts, Kluwer Academic Publishers, 2000.

- [4] J. Chen, R. Solomon, T. Y. Chan, P. K. Ko, and C. Hu, "Threshold voltage and C-V characteristics of SOI MOSFET's related to Si film thickness variation on SIMOX wafers," *IEEE Transactions on Electron Devices*, vol. 39, no. 10, pp. 2346–2353, 1992.

- [5] J. Z. Ren and C. A. T. Salama, "1 V SOI NMOSFET with suppressed floating body effects," *Solid-State Electronics*, vol. 44, no. 11, pp. 1931–1937, 2000.

- [6] B. A. Chen, A. Hirsch, S. K. Iyer, N. Rovedo, H. -J. Wann, and Y. Zhang, "Patterned Buried Insulator," US Patent no. 6429091 B1, 2002.

- [7] Y. Dong, M. Chen, J. Chen et al., "Patterned buried oxide layers under a single MOSFET to improve the device performance," *Semiconductor Science and Technology*, vol. 19, no. 3, pp. L25– L28, 2004.

- [8] C. Pal, B. Mazhari, and S. S. K. Iyer, "Simulation of MOSFET devices and circuits fabricated on selective buried oxide (SEL-BOX) substrates," in *Proceedings of IEEE Conference on Electron Devices and Solid-State Circuits (EDSSC '05)*, pp. 559–562, Hong Kong, December 2005.

- [9] M. Y. Hammad, "Analytical modeling of the partially-depleted SOI MOSFET," *IEEE Transactions on Electron Devices*, vol. 48, no. 2, pp. 252–258, 2001.

- [10] ATHENA User's Manual Device Simulation Software, Silvaco International, Santa Clara, Calif, USA, 2004.

- [11] ATLAS User's Manual Device Simulation Software, Silvaco International, Santa Clara, Calif, USA, 2004.

- [12] J.-P. Colinge, Silicon-On-Insulator Technology: Materials to VLSI, Springer, 3rd edition, 2004.

- [13] D. A. Neamen, *Microelectronics*, McGraw-Hill, 3rd edition, 2006.

- [14] I. M. Hafez, G. Ghibaudo, and F. Balestra, "Analysis of the kink effect in MOS transistors," *IEEE Transactions on Electron Devices*, vol. 37, no. 3, pp. 818–821, 1990.

- [15] T. Y. Chan and P. K. Ko, "A simple method to characterize substrate current in MOSFET's," *IEEE Electron Device Letters*, vol. EDL-5, no. 12, p. 506, 1984.

Submit your manuscripts at http://www.hindawi.com