Hindawi International Journal of Photoenergy Volume 2017, Article ID 2383872, 8 pages https://doi.org/10.1155/2017/2383872

# Research Article

# Modeling and Modulation of NNPC Four-Level Inverter for Solar Photovoltaic Power Plant

# Xiaoqiang Guo, Xuehui Wang, Ran He, and Mehdi Narimani

<sup>1</sup>Department of Electrical Engineering, Yanshan University, Qinhuangdao, China

Correspondence should be addressed to Xiaoqiang Guo; yeduming@163.com

Received 17 January 2017; Accepted 8 May 2017; Published 30 July 2017

Academic Editor: Matthias Auf der Maur

Copyright © 2017 Xiaoqiang Guo et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Photovoltaic (PV) power plant is an attractive way of utilizing the solar energy. For high-power PV power plant, the multilevel inverter is of potential interest. In contrast to the neutral-point clamped (NPC) or flying capacitor (FC) multilevel inverter, the nested neutral point clamped (NNPC) four-level inverter has better features for solar photovoltaic power plant. In practical applications, the common mode voltage reduction of the NNPC four-level is one of the important issues. In order to solve the problem, a new modulation strategy is proposed to minimize the common mode voltage. Compared with the conventional solution, our proposal can reduce the common mode voltage to 1/18 of the DC bus voltage. Moreover, it has the capability to balance the capacitor voltages. Finally, we carried out time-domain simulations to test the performance of the NNPC four-level inverter.

#### 1. Introduction

In recent years, the grid-connected wind and PV power systems have attracted considerable interests around the world [1-4]. Many industrialized nations have installed significant solar power capacity into their electrical grids, providing an alternative to conventional energy sources. While an increasing number of less developed nations have turned to solar to reduce dependence on expensive imported fuels. Different from most building-mounted and other domestic solar power applications which are mainly for the low-voltage local users [5, 6], the high voltage is necessary to integrate the solar photovoltaic power plant into utility. In this case, the multilevel inverters are of potential interest for PV plants [7–11]. In practice, however, there are leakage currents and EMC issues in high-power photovoltaic plants [12]. The leakage currents and electromagnetic interferences have potential safety problems [13, 14]. Therefore, it must be eliminated before connecting them into grid. For this aim, the solutions based on the interesting topologies and modulation strategies have been developed in recent years. Typically, there are three classical topologies of the multilevel inverters such as the flying capacitor (FC) topology, cascade H-bridge topology, and neutral point clamped (NPC) topology [15–18]. Compared with the conventional two-level inverter, the multilevel inverter has unique features such as reduced voltage stress, less dv/dt and high waveforms. In contrast to the existing topologies, a novel nested neutral point clamped (NNPC) inverter is proposed in [19], it is of great interest for medium-voltage power conversion, especially for solar PV plant applications. In practice, however, the common mode voltage may arise, resulting in the leakage current. In order to solve the problem, a new modulation strategy is proposed to minimize the common mode voltage. Compared with the conventional solution, our proposal can reduce the common mode voltage to 1/18 of the DC bus voltage. Meanwhile, it has the capacitor balancing capability. Finally, the timedomain performance tests are carried out. The results verify the effectiveness of the proposed solution.

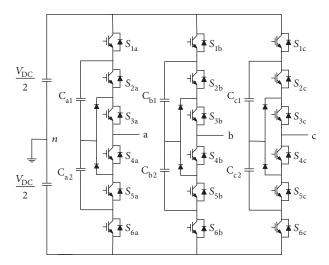

## 2. Analysis of Four-Level NNPC Inverter

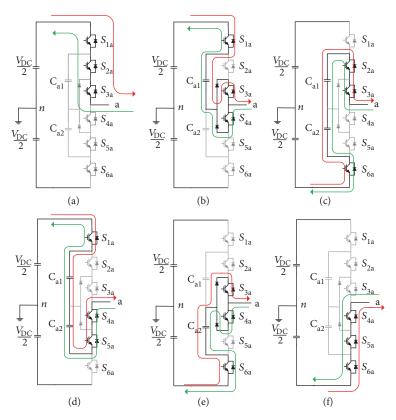

The schematic diagram of the novel four-level NNPC inverter is illustrated in Figure 1, where each phase includes 6 switches, 2 diodes, and 2 flying capacitors, which has fewer number of components and complexity than four-level NPC

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada

FIGURE 1: Schematic diagram of the four-level NNPC inverter.

$V_{\underline{a}\underline{n}}$  $V_{\underline{\mathrm{Cal}}}$  $V_{\underline{\text{Ca2}}}$ Level  $S_{1a}$  $S_{2a}$  $S_{3a}$  $S_{4a}$  $S_{5a}$  $S_{6a}$ 3 1 1 1 0 0 0  $V_{\rm DC}/2$  $C(i_a > 0)$ 0 1 0 0 2A 1  $D(i_a < 0)$ 2  $V_{\rm DC}/6$  $D\left(i_{a}>0\right)$  $D(i_a > 0)$ 2B 0 1 1 0  $C(i_a < 0)$  $C(i_a < 0)$  $C(i_a > 0)$  $C(i_a > 0)$ 0 0 0 1A 1 1 1  $D(i_a < 0)$  $D(i_a < 0)$ 1  $-V_{\rm DC}/6$  $D(i_a > 0)$ 0 0 1B 0 1 1 1  $C(i_a < 0)$

1

1

Table 1: States, switching states, and flying capacitors voltage of four-level NNPC inverter.

C: charging; D: discharging.

0

or FC inverter. Take phase A for example, there are six operation states of a phase, as shown in Table 1.

0

0

0

When the switch turns on, it corresponds to the state "1" in Table 1, while when the switch turns off, it corresponds to the state "0." The four levels of phase voltage are labeled as 3, 2, 1, and 0, which correspond to the topology of  $V_{\rm DC}/2$ ,  $V_{\rm DC}/6$ ,  $-V_{\rm DC}/6$ , and  $-V_{\rm DC}/2$ . Different from the conventional four-level NPC inverter, there are two kinds of redundant states on "1" and "2" levels of NNPC topology. "1" level corresponds to 1A and 1B, while "2" level corresponds to the 2A and 2B in Table 1. It should be noted that the flying capacitor is used in the NNPC inverter. So the capacitor voltage balancing should be considered. The impact of switching states on the capacitor voltage is shown in Table 1.

As shown in Figure 2, only the flying capacitor  $C_{\rm a1}$  is charged or discharged during the state "2A," remaining the flying capacitor  $C_{\rm a2}$  unaffected, while both the flying capacitors  $C_{\rm a1}$  and  $C_{\rm a2}$  will be charged or discharged during the state "2B." It is worth noting that if the current direction is different, the capacitor charging or discharging is also different. Take the state "2A" for example, when the current  $i_{\rm a} > 0$ , the capacitor  $C_{\rm a1}$  is charged, and while the current  $i_{\rm a} < 0$ , the

capacitor  $C_{a1}$  discharged. The details regarding the capacitor voltage balancing will be presented in the following section.

# 3. Common Mode Voltage of Four-Level NNPC Inverter

The common mode voltage is one of the important issues for power converters [20]. The common mode voltage of the NNCP inverter can be expressed as (1), where  $v_{\rm cm}$  is the common voltage, and  $v_{\rm an}$ ,  $v_{\rm bn}$ , and  $v_{\rm cn}$  represent the three-phase voltages, respectively.

$$v_{\rm cm} = \frac{v_{\rm an} + v_{\rm bn} + v_{\rm cn}}{3}.$$

(1)

$-V_{\rm DC}/2$

There are 4 switching states in each phase. So there are 64 switching states for NNPC inverter. The relationship between the common mode voltage and switching state is shown in Table 2. Taking "000" in Table 2 for example, it is indicated that the a phase output is 0 level, the b phase output is 0 level, and the c phase output is 0 level.

From Table 2, it can be observed that there are 10 kinds of values, including  $\pm V_{\rm DC}/2$ ,  $\pm 7V_{\rm DC}/18$ ,  $\pm 5V_{\rm DC}/18$ ,  $\pm V_{\rm DC}/6$ ,

FIGURE 2: Six switching states of NNPC inverter: (a) switching state 3; (b) switching state 2A; (c) switching state 2B; (d) switching state 1A; (e) switching state 1B; and (f) switching state 0.

Table 2: Switching states and common mode voltage of four-level NNPC inverter.

| Common mode voltage | Switch states                                              |  |

|---------------------|------------------------------------------------------------|--|

| $-V_{\rm DC}/2$     | 000                                                        |  |

| $-7~V_{ m DC}/18$   | 001, 010, 100                                              |  |

| $-5~V_{\rm DC}/18$  | 002, 011, 020, 101, 110, 200                               |  |

| $-V_{ m DC}/6$      | 003, 021, 012, 030, 102, 111, 120, 201, 210, 300           |  |

| $-V_{ m DC}/18$     | 013, 022, 031, 103, 112, 121, 130, 202, 211, 220, 301, 310 |  |

| $V_{ m DC}/18$      | 023, 032, 113, 122, 131, 203, 212, 221, 230, 302, 311, 320 |  |

| $V_{ m DC}/6$       | 033, 123, 132, 213, 222, 231, 303, 312, 321, 330           |  |

| 5 $V_{ m DC}$ 18    | 133, 223, 232, 313, 322, 331,                              |  |

| $7~V_{ m DC}/18$    | 233, 323, 332                                              |  |

| $V_{ m DC}/2$       | 333                                                        |  |

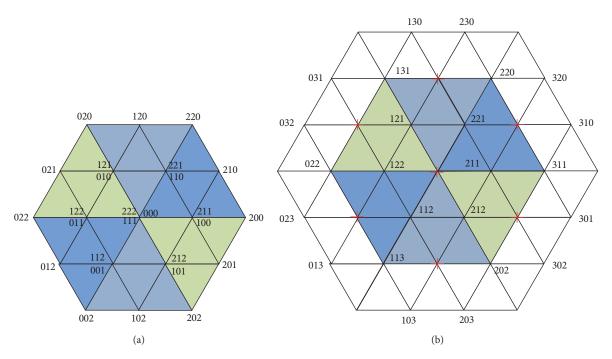

and  $\pm V_{\rm DC}/18$  regarding the common mode voltage of the NNPC inverter. Obviously, the common mode voltage would be very high if all switching states are involved. In order to reduce the common mode voltage, two groups of switching states can be utilized. In this way, the common mode voltage can be reduced to 1/18 of the DC bus voltage. The space vector diagram is as shown in Figure 3.

# 4. Proposed Modulation Strategy

As discussed above, the common mode voltage can be significantly reduced to  $\pm V_{\rm DC}/18$  by selecting the specified vectors and switching states. In order to achieve the objective, a new modulation strategy is proposed in this paper. Firstly, the desired level arrangement is generated by the modulation strategy. Secondly, select the redundant state to balance the flying capacitor voltage.

As shown in Figure 3, the vectors of the selected 24 switching states are similar to those of three-level vectors. If the outermost four-level vectors (e.g., 130 and 230) are not considered, the other four-level vectors are associated with the three-level vectors. Taking the sector of A1 as an example, the three-level vector of 000 in Figure 3(a) (redundant vectors 111 and 222) corresponds to the virtual vector (red cross presents the virtual vector) in Figure 3(b), while the three-level vector of 211 (redundant vectors 100) corresponds to the four-level vector of 211. Other relationship can also be derived, as shown in Table 3.

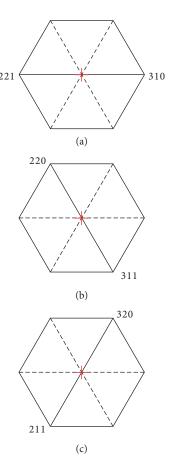

For the virtual vector, it can be achieved by vector synthesis. Taking the virtual vector of sector A1 for example, it can be synthesized through (1) vectors 221 and 310, (2) vectors 220 and 311, and (3) vectors 320 and 211. The vector synthesis diagram is shown in Figure 4.

Based on the above analysis, a novel modulation method is proposed in this paper. Firstly, comparing two triangle waves with sine wave, the three-level vectors can be

Figure 3: Space vector diagram (a) three-level inverter and (b) four-level inverter  $v_{\rm cm}$  =  $\pm$   $V_{\rm DC}/18$ .

Table 3: Relationship between three-level inverter voltage vector and four-level inverter voltage vector.

| Three-level vector | Four-level vector |

|--------------------|-------------------|

| 211, 100           | 211               |

| 200                | 311               |

| 210                | Virtual vector    |

| 221, 110           | 221               |

| 220                | 220               |

| 120                | Virtual vector    |

| 121, 010           | 121               |

| 020                | 131               |

| 021                | Virtual vector    |

| 122, 011           | 122               |

| 022                | 022               |

| 012                | Virtual vector    |

| 112, 001           | 112               |

| 002                | 113               |

| 102                | Virtual vector    |

| 212, 101           | 212               |

| 201                | Virtual vector    |

| 202                | 202               |

| 000, 111, 222      | Virtual vector    |

generated, as shown in Table 3. With the logical transformation, these vectors can be linked to the four-level vectors. The synthesis method is shown in Table 4.

For the selection of the carrier modulation, the inphase disposition (IPD) modulation is used due to the following advantages.

FIGURE 4: Virtual vector synthesis diagram.

Table 4: Relationship between virtual and synthesis vectors.

| Virtual vector | Synthetic vector           |

|----------------|----------------------------|

| 210            | Sector A1∩B1 221 and 310   |

| 210            | Sector A1∩B2 211 and 320   |

| 120            | Sector A2∩B2 121 and 230   |

| 120            | Sector A2∩B3 221 and 130   |

| 021            | Sector A3 ∩ B3 122 and 031 |

| 021            | Sector A3 ∩ B4 121 and 032 |

| 012            | Sector A4∩B4 112 and 023   |

| 012            | Sector A4∩B5 122 and 013   |

| 102            | Sector A5∩B5 212 and 103   |

| 102            | Sector A5∩B6 112 and 203   |

| 201            | Sector A6∩B6 211 and 302   |

| 201            | Sector A6∩B1 212 and 301   |

- In IPD modulation, voltage vector complies with the "near three vector principle," that is, there no longer exists jumping of the two levels on the corresponding four-level vector.

- (2) In the A1 sector, for example, in a switching period of IPD modulation, the vector 210 (i.e., three-level vector corresponding to the four-level virtual vector) has the same effect time in the first half and the second half switching periods. Therefore, it is easy to realize the vector synthesis in Table 4 (in the first Ts/2 with a synthetic vector, after Ts/2 with another synthetic vector).

As discussed above, the desired level can be generated by means of carrier modulation and logical transformation. Note that there are redundant states about "1" or "2" level (see Table 1) of the NNPC inverter. The capacitor voltage balance can be achieved with the redundant states. Taking one phase as an example, the variation of the flying capacitor voltage is defined as (2), where  $V_{ci}$  is the flying capacitor voltage, i = 1, 2. The capacitor voltage can be balanced if  $\Delta V_{ci}$  is close to 0.

$$\Delta V_{ci} = V_{ci} - \frac{V_{DC}}{3} \tag{2}$$

The capacitor voltage balancing mechanism is shown in Table 5. The balance of the capacitor  $C_1$  can be achieved only by selecting the redundancy state of "2" level, while the balance of the capacitor  $C_2$  can be achieved by selecting the redundancy state of "1" level.

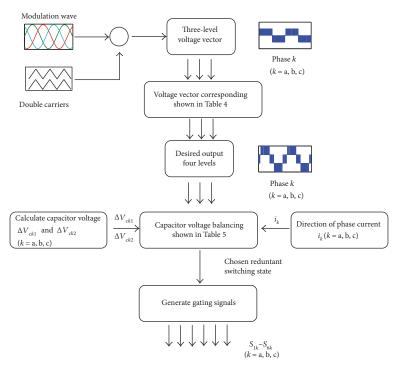

The control block diagram is shown in Figure 5. In this way, the output four-level voltage can be achieved. Meanwhile the common mode voltage can be significantly reduced to  $\pm V_{\rm DC}/18$ . Aside from that, the capacitor voltage balancing can be achieved.

#### 5. Simulation Results

In order to verify the effectiveness of the proposed solution, the time-domain simulations are carried out in MATLAB/

TABLE 5: Mechanism of capacitor voltage balancing.

| Level | $\Delta V_{\mathrm{C}i}$  | Phase current ia | Redundancy state |

|-------|---------------------------|------------------|------------------|

|       | $\Delta V_{\rm CI}$ < 0   | <0               | 2B               |

| 2     |                           | ≥0               | 2A               |

| 2     | $\Lambda W > 0$           | <0               | 2A               |

|       | $\Delta V_{\rm C1} \ge 0$ | ≥0               | 2B               |

| 1     | AV <0                     | <0               | 1B               |

|       | $\Delta V_{\rm C2} < 0$   | ≥0               | 1A               |

|       | A.V. > 0                  | <0               | 1A               |

|       | $\Delta V_{\rm C2} \ge 0$ | ≥0               | 1B               |

Simulink. The type of simulation model we use is a real circuit with power switches, instead of a transfer function or mathematical description model. The simulation parameters are listed in Table 6.

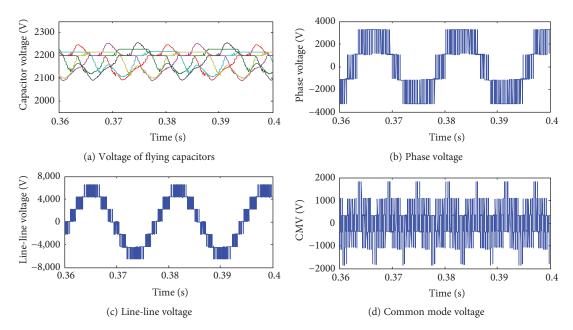

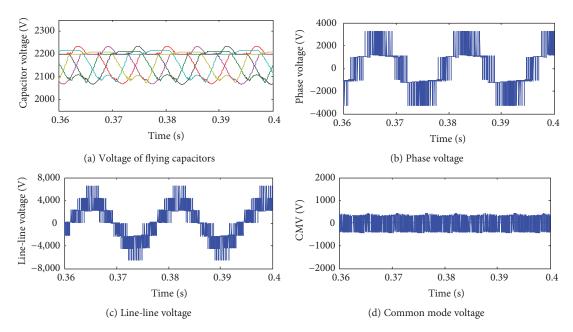

The simulation results are shown as follows. From Figures 6 and 7, it can be observed that the flying capacitor voltages can be well balanced around 2200 V ( $V_{\rm DC}/3$ ), and the ripple is less than 7.5% of the rated voltage. The output phase voltage is four-level waveform, while the line voltage is seven-level waveform. On the other hand, the common mode voltage of the conventional solution is as high as  $\pm 5V_{\rm DC}/18$ , while the common mode voltage of the proposed solution is significantly reduced to  $\pm V_{\rm DC}/18$ .

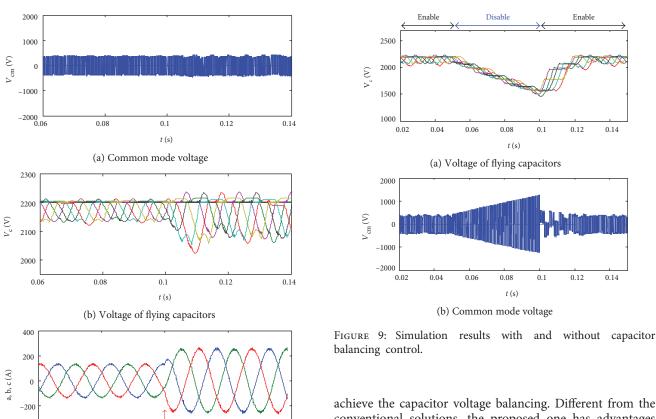

In order to verify the dynamic performance of the proposed solution, the simulations are carried out with a step change from half to full loads at 0.1 s. As shown in Figure 8, it can be seen that the current increases from half to full loads, and the waveform quality of current is kept well all the time. Note that the fluctuation of capacitor voltage after heavy loading increases, but it is still less than 7.5% of the rated voltage. So the system has a good dynamic performance. At the same time, the common mode voltage, before and after the load step, remains around  $\pm V_{\rm DC}/18$ .

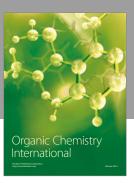

In order to further verify the effectiveness of the capacitor voltage balancing scheme, the balancing control is enabled, then disabled, and finally enabled, as shown in Figure 9.

From Figure 9, it can be observed that when the balancing control is disabled, the capacitor voltage tends to diverge. Meanwhile, the common mode voltage is negatively impacted with higher amplitude; that is, the capacitor voltage balancing has an impact on common mode voltage. After the balancing control is recovered at  $t = 0.1 \, \text{s}$ , common mode voltage and capacitor voltage can be quickly restored to normal operation state, which verifies the effectiveness of the proposed solution.

### 6. Conclusion

This paper has presented the modeling and analysis of a novel four-level NNPC inverter for PV power plant applications. It is concluded that the proposed solution can significantly reduce the common mode voltage to  $V_{\rm DC}/18$ . Also, it can

Figure 5: The controller diagram of the four-level NNPC inverter.

Table 6: Simulation parameters.

| Parameters       | Value               |

|------------------|---------------------|

| DC voltage       | 6.6 kV              |

| Output frequency | 60 Hz               |

| Output inductor  | 5 mH                |

| Output resistor  | $7.5\Omega$         |

| Flying capacitor | $2200\mu\mathrm{F}$ |

| Modulation index | 0.95                |

FIGURE 6: Simulation results (conventional solution).

0.14

0.14

FIGURE 7: Simulation results (proposed solution).

0.14

(c) Output current FIGURE 8: Simulation results from half to full load.

0.1

t (s)

0.12

0.08

-400 └ 0.06

achieve the capacitor voltage balancing. Different from the conventional solutions, the proposed one has advantages such as easy implementation with no need of complex space vector modulation. Therefore, it is of great potential interest for solar plant applications, where the common mode EMI is a major concern. It should be noted that the CMV and EMI reductions of the four-level NNPC inverter are focused for PV power plant. Other issues such as grid synchronization, control, and protection [21-26] are beyond the scope of the paper.

#### **Conflicts of Interest**

The authors declare that there is no conflict of interests regarding publication of this paper.

# Acknowledgments

This work was supported by the Science Foundation for Hundred Excellent Innovation Talents Support Program of Hebei Province (SLRC2017059) and Science Foundation for Returned Scholars of Hebei Province (CL201622).

#### References

- [1] J. Hu, L. Sun, X. Yuan, S. Wang, and Y. Chi, "Modeling of type 3 wind turbine with df/dt inertia control for system frequency response study," *IEEE Transactions on Power Systems*, 2016.

- [2] J. Hu, S. Wang, W. Tang, and X. Xiong, "Full-capacity wind turbine with inertial support by optimizing phase-locked loop," *IET Renewable Power Generation*, vol. 11, no. 1, pp. 44–53, 2017.

- [3] D. Zhang, Y. Wang, J. Hu, S. Ma, Q. He, and Q. Guo, "Impacts of PLL on the DFIG-based WTG's electromechanical response under transient conditions: analysis and modeling," CSEE Journal of Power and Energy Systems, vol. 2, no. 2, pp. 30–39, 2016.

- [4] X. Guo, "A novel CH5 inverter for single-phase transformerless photovoltaic system applications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, 2017.

- [5] W. Li, G. Yunjie, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 7, pp. 4537–4551, 2015.

- [6] X. Guo, "Three phase CH7 inverter with a new space vector modulation to reduce leakage current for transformer-less photovoltaic systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 2, pp. 708–712, 2017.

- [7] S. Kouro, M. Malinowski, K. Gopakumar et al., "Recent advances and industrial applications of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2553–2579, 2010.

- [8] H. Nademi, A. Das, R. Burgos, and L. E. Norum, "A new circuit performance of modular multilevel inverter suitable for photovoltaic conversion plants," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 2, pp. 393– 404, 2016.

- [9] S. Essakiappan, H. Krishnamoorthy, P. Enjeti, R. S. Balog, and S. Ahmed, "Multilevel medium-frequency link inverter for utility scale photovoltaic integration," *IEEE Transactions on Power Electronics*, vol. 30, no. 7, pp. 3674–3684, 2015.

- [10] M. Hamzeh, A. Ghazanfari, H. Mokhtari, and H. Karimi, "Integrating hybrid power source into an islanded MV microgrid using CHB multilevel inverter under unbalanced and nonlinear load conditions," *IEEE Transactions on Energy Conversion*, vol. 28, no. 3, pp. 643–651, 2013.

- [11] L. Liu, H. Li, Y. Xue, and W. Liu, "Decoupled active and reactive power control for large-scale grid-connected photo-voltaic systems using cascaded modular multi-level converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 176–187, 2015.

- [12] R. Araneo, S. Lammens, M. Grossi, and S. Bertone, "EMC issues in high power grid-connected photovoltaic plants," *IEEE Transactions on Electromagnetic Compatibility*, vol. 51, no. 3, pp. 639–648, 2009.

- [13] X. Guo, B. We, T. Zhu et al., "Leakage current suppression of three phase flying capacitor PV inverter with new carrier modulation and logic function," *IEEE Transactions on Power Electronics*, 2017.

- [14] X. Guo, R. He, J. Jian, Z. Lu, X. Sun, and Z. Lu, "Leakage current elimination of four-leg inverter for transformerless three-phase PV systems," *IEEE Transactions on Power Electronics*, vol. 31, no. 3, pp. 1841–1846, 2016.

- [15] X. Guo and X. Jia, "Hardware-based cascaded topology and modulation strategy with leakage current reduction for transformerless PV systems," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 12, pp. 7823–7832, 2016.

- [16] C. Hu, X. Yu, D. Holmes et al., "An improved virtual space vector modulation scheme for three-level active neutralpoint-clamped inverter," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7419–7434, 2017.

- [17] Z. Shao, X. Zhang, F. Wang, R. Cao, and H. Ni, "Analysis and control of neutral-point voltage for transformerless three-level PV inverter in LVRT operation," *IEEE Transactions on Power Electronics*, vol. 32, no. 3, pp. 2347–2359, 2017.

- [18] H. Geng, S. Li, C. Zhang, G. Yang, and L. Dong, "Hybrid communication topology and protocol for distributed-controlled cascaded H-bridge multilevel STATCOM," *IEEE Transactions on Industry Application*, vol. 53, no. 1, pp. 576–584, 2017.

- [19] M. Narimani, B. Wu, Z. Cheng, and N. Zargari, "A new nested neutral point clamped (NNPC) converter for medium-voltage (MV) power conversion," *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6375–6382, 2014.

- [20] X. Guo, D. Xu, and B. Wu, "Common-mode voltage mitigation for back-to-back current-source converter with optimal spacevector modulation," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 688–697, 2016.

- [21] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid interfaced converters in distributed utility networks," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 4, pp. 1194–1204, 2011.

- [22] Z. Shuai, Y. Hu, Y. Peng, T. Chunming, and Z. J. Shen, "Dynamic stability analysis of synchronverter-dominated microgrid based on bifurcation theory," *IEEE Transactions on Industrial Electronics*, 2017.

- [23] Z. Shuai, W. Huang, C. Shen, G. Jun, and Z. John Shen, "Characteristics and restraining method of fast transient inrush fault currents in synchronverters," *IEEE Transactions on Industrial Electronics*, 2017.

- [24] X. Guo, W. Liu, and Z. Lu, "Flexible power regulation and current-limited control of grid-connected inverter under unbalanced grid voltage faults," *IEEE Transactions on Industrial Electronics*, 2017.

- [25] X. Guo, W. Liu, X. Zhang, X. Sun, Z. Lu, and J. M. Guerrero, "Flexible control strategy for grid-connected inverter under unbalanced grid faults without PLL," *IEEE Transactions on Power Electronics*, vol. 30, no. 4, pp. 1773–1778, 2015.

- [26] L. Chen and S. Mei, "An integrated control and protection system for photovoltaic microgrids," *CSEE Journal of Power and Energy Systems*, vol. 1, no. 1, pp. 36–42, 2015.

Submit your manuscripts at https://www.hindawi.com