Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2016, Article ID 4237350, 27 pages http://dx.doi.org/10.1155/2016/4237350

## Research Article

## Modelling and Automated Implementation of Optimal Power Saving Strategies in Coarse-Grained Reconfigurable Architectures

## Francesca Palumbo,<sup>1</sup> Tiziana Fanni,<sup>2</sup> Carlo Sau,<sup>2</sup> Paolo Meloni,<sup>2</sup> and Luigi Raffo<sup>2</sup>

<sup>1</sup>POLCOMING, Information Engineering Unit, University of Sassari, Sassari, Italy <sup>2</sup>Department of Electrical and Electronic Engineering (DIEE), University of Cagliari, Cagliari, Italy

Correspondence should be addressed to Tiziana Fanni; tiziana.fanni@diee.unica.it

Received 18 April 2016; Accepted 14 September 2016

Academic Editor: Wen B. Jone

Copyright © 2016 Francesca Palumbo et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

This paper focuses on how to efficiently reduce power consumption in coarse-grained reconfigurable designs, to allow their effective adoption in heterogeneous architectures supporting and accelerating complex and highly variable multifunctional applications. We propose a design flow for this kind of architectures that, besides their automatic customization, is also capable of determining their optimal power management support. Power and clock gating implementation costs are estimated in advance, before their physical implementation, on the basis of the functional, technological, and architectural parameters of the baseline design. Experimental results, on 90 and 45 nm CMOS technologies, demonstrate that the proposed approach guides the designer towards optimal implementation.

#### 1. Introduction

Electronic devices on the market rely on the execution of computation-intensive applications on complex heterogeneous systems. Coarse-grained reconfigurable (CGR) platforms combine the high performance levels provided by Application Specific Integrated Circuit (ASIC) designs with an increased flexibility, allowing the execution of a larger set of applications over the same substrate [1, 2]. However, in the dark silicon era, due to the limited available power budget, a gap exists between the number of transistors that can be placed within a die and the number that can be actually active during execution [3, 4]. Therefore, systems are also required to be energy efficient and CGR designs must integrate specific power management techniques of the functional logic regions constituting them.

Several effective techniques for power monitoring [5] and reducing [6] have been presented at the state of the art. Among them, voltage/frequency scaling [7, 8] and power shut-off schemes [9, 10] can be extremely beneficial. However, their integration requires manual intervention of the

designer, resulting in a complex, error prone, and time consuming process. While commercial synthesizers [11] allow the automatic implementation of low overhead saving strategies at the gate level, such as fine-grained clock gating, they only provide implementation-level instruments to apply more complex strategies, like power gating. In the CGR systems field, the Multi-Dataflow Composer tool (MDC), combining the dataflow-based system specification approach with the coarse-grained reconfigurable design paradigm, is capable of automatically generating run-time reconfigurable multifunctional systems, featuring flexibility and area minimization [12]. MDC was originally meant to address reconfigurable codec implementations and was conceived to be exploited within MPEG Reconfigurable Video Coding (MPEG-RVC) studies. However, it was successfully adopted also in different resource and power-constrained scenarios [13, 14], where only microprogrammed solutions have been used so far, either exploiting single-core digital signal processors [15] or custom multicore embedded processors [16]. MDC design suite is composed of different extensions. The work presented

in this paper is related to MDC power management extension, which has been previously addressed in [17, 18]. MDC tool identifies in the generated CGR system the minimum set of disjointed functionally homogeneous logic areas of the system, called logic regions. These latter are exploited to automatically implement dynamic power management strategies, applying indistinctly to all of them either clock [17] or power gating methodologies [18].

The work we are presenting in this paper intends to propose a power modelling methodology and to improve the MDC power management extension by integrating such methodology within its automated flow. We introduce in this paper an algorithm that analyses the identified logic regions and, on the basis of one single synthesis and a minimal set of simulations (one for each scenario of the multifunctional problem), is capable of optimally characterizing the power management support. This flow, in a separate manner for each logic region of the CGR design, is capable of assessing both clock and power gating management costs and of determining which is the optimal power saving strategy (if any) prior to any physical system implementation. The algorithm is based on detailed static and dynamic power consumption models that take into account functional, architectural, and technological parameters to define the potential overhead and benefits of the considered solutions. As a future perspective, besides its application within the MPEG-RVC scenario, the proposed modelling strategy may also be extended to support other complex autonomous computing systems [19], where the number of involved resources may change at runtime.

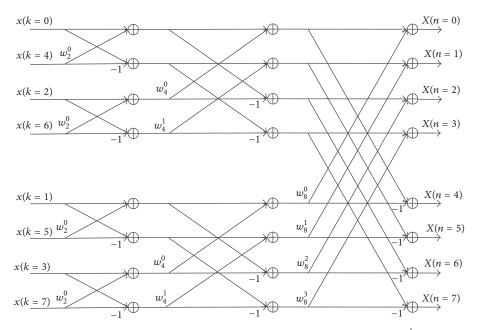

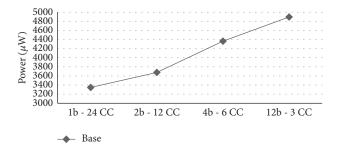

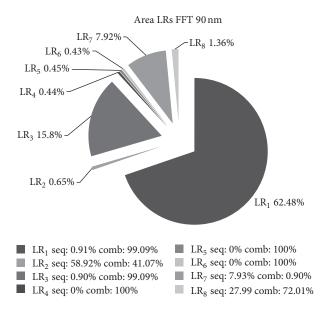

The rest of this paper is organized as follows. Section 2 reports the background of this work. Section 3 describes the operation of MDC: in particular, Section 3.1 focuses on the base operation, while Section 3.2 details the proposed power estimation models and their integration within the tool. Section 4 presents the designs under test used to validate the proposed approach: Section 4.1 involves a FFT use case targeting a 90 nm CMOS technology, while Section 4.2 presents the experimental results conducted to assess the enhanced MDC flow on a zoom coprocessor (targeting both 90 nm and 45 nm CMOS technologies). Finally, Section 4.4 details the benefits of the proposed models, before concluding with some final remarks in Section 5.

### 2. Background

This work presents a model of power consumption for CGR systems. The model is capable of estimating the system power dissipation since the early stages of the design flow and it has been integrated within an automated flow that decides which power saving technique, between clock gating and power gating, has to be applied to each portion of the design.

This section provides an overview of the state of the art in the field of power-aware optimization and, in more detail, on the main aspects involved in the proposed approach. Section 2.1 introduces the distinctive features of CGR systems and the main architectural trends for such a kind of devices. Section 2.2 deals with power issues in digital system, with

a particular emphasis on modelling strategies and design automation.

2.1. Coarse-Grained Reconfigurable Systems. Reconfigurable architectures are usually conceived as collections of functional units (FUs) whose functionality and connections can be configured at run time, to adapt them to different applications or operating modes. Such systems can be classified according to the granularity of the FUs. Fine-grained approaches, typically exploiting FPGA devices as underlying technology, involve bit-level FUs, resulting in a higher flexibility but requiring long configuration time (due to the configuration bitstream size). Coarse-grained reconfigurability, on the other hand, provides word-level FUs, thus providing less flexibility while guaranteeing faster configuration phases. CGR architectures are usually exploited to design flexible ASICs, making them capable of switching among a finite set of functionality. In such design cases, high efficiency in terms of area obstruction of the designed system can be easily obtained, but not all the resources are evenly involved in the computation. Dedicated power management techniques are needed to reduce the overhead, in terms of power consumption, related to resources that are not involved in each operating mode [17]. CGR architectures already demonstrated being suitable to address application scenarios that require flexibility along with strong area, power, and execution efficiency [13, 20].

One of the main issues of CGR architectures is their complex mapping and programming [21, 22]. Several works tried to automate the mapping of applications and computational kernels onto CGR and multicore systems [23-25]. The mapping problem requires specific knowledge of the considered kernels that usually have to be identified and specified by means of hardware description languages. The mapping effort is directly proportional to the number of involved kernels [26]. Recently, dataflow models demonstrated to be very useful in this scenario [27, 28]. Dataflows describe programs through a graph whose nodes are processing elements (actor) linked by point-to-point unidirectional channels managed according to a FIFO protocol. Actors encapsulate their own state and communicate only through atomic packets of data (tokens). Due to their intrinsic modularity, dataflows favour hardware and software components definition and reuse. Furthermore, they are natively capable of highlighting the intrinsic parallelism of the specified applications. The Multi-Dataflow Composer (MDC) tool, adopted within the presented work, relies on dataflows (RVC-CAL formalism by MPEG is currently supported) to solve the CGR mapping problem. It exploits the characteristics of such kind of models to provide several advanced features (e.g., power management [17, 18] or coprocessing units automatic generation [29]).

2.2. Power Management. Power consumption in digital devices is composed mainly of two different contributions: dynamic and static. The former is due to capacitance charging/discharging when logic transitions occur (i.e., switching activity). The latter is due to leakage currents and it is consumed also when no circuit activity is present. Modern

designers need to consider both terms when conceiving smart management strategies. Several techniques (clock gating, multifrequency, operand isolation, multithreshold, multisupply libraries, power gating, etc.) exist and, in some cases, they are automatically implemented by commercial synthesis/ place-and-route tools. In custom computing systems, some advanced design tools support the designers in the application-driven customization of the hardware architectures [30, 31]. However, generally speaking, invasive techniques (requiring insertion of additional logic and target technology support (such as the availability of dedicated cells and processes on the implementation stack)) still need tools to be guided with significant manual effort by the designer.

Clock gating is an example of quite noninvasive technique. It may reduce the dynamic power consumption due to the clock tree and to sequential logic up to the 40% [32]. It consists in shutting off the clock of the unused synchronous logic, by means of simple AND gates. Clock gating has been deeply automated and it is available on most of the commercial synthesizers. In the MPEG-RVC community, recent studies [33] presented an extension of a High-Level Synthesis tool, Xronos, to selectively switch off clock signal for parts of the circuit that are idle due to stalls in the pipeline, to reduce power consumption. Moreover, as mentioned, the MDC tool has the capability of identifying, by means of a graph-based analysis of the input dataflow specifications, independent circuitry regions. These logic regions can be clock gated to dynamically adapt power consumption when switching between different functionalities [17, 18]. From the technical point of view, in ASIC designs AND gates can be used directly on the clock to disable it, while in FPGA designs the clock network cannot be modified by the insertion of any custom logic and dedicated cells are required (Xilinx boards, e.g., are equipped with dedicated blocks (BUFGs), whose outputs can drive distinct regions of logic powering down different design portions (when enabled)). Clock gating can be applied at different granularities: fine-grained approaches act on single registers, whereas coarse-grained ones are referred, as in [17, 18, 33], to a set of resources. Commercial synthesizers normally can automate only fine-grained strategies.

Power gating is quite invasive. The main idea behind it is as follows: if a specific portion of the design is not used in a given computation mode, then it can be completely switched-off by means of a sleep transistor. This technique, as the clock gating one, is applicable at different granularities: fine-grained approaches require driving a different sleep transistor for every cell in the system, while coarse-grained ones, again, operate on a set of resources instantiating one sleep transistor to drive different cells connected to a shared power network. MDC, as discussed in [18], supports also automatic power gating for CGR architectures. Each identified logic region in the CGR system is implemented (no matter of its nature or characteristics) as a different power domain (PD) that, in order to be managed, requires to insert and drive the following resources:

(i) The *sleep transistor* between the gated region and the main power supply to switch on/off the derived power supply

- (ii) The *isolation logic* between the gated region and normally-on cells to avoid the transmission of spurious signals in input to the normally-on cells

- (iii) The *state retention logic* to maintain, where needed, the internal state of the gated region

MDC, besides defining the power gated design netlist, provides also the automatic definition of the power format file. This file specifies the shut-off, isolation, and state retention rules (if you have 10 PD you are required to define 3 \* 10 = 30 interfaces), along with their respective enable signals ([1 \* shut-off + 1 \* isol. + 2 \* reten.] \*10 = 40 signals) and a dedicated Power Controller to properly drive them. The power format file automatically created by MDC is compliant with the Silicon Integration Initiative's Common Power Format (CPF), whose definition is driven mainly by developers using Cadence [34] tools.

2.2.1. Modelling. To the best of our knowledge, literature does not treat the problem of modelling power gating and clock gating costs in CGR designs. Some approaches only partially address the issue. For example, [35] focusses on low-power techniques and power modelling for FPGAs. In [36], only clock gating is taken into account: different power states (on the basis of the clock enable signals) are defined and their consumption is characterized by low-level Power Analysis results. [37] focusses on estimating the leakage reduction for power gating and reverse body bias.

The CASPER simulator for shared memory many-core processors [38] includes precharacterized libraries containing power dissipation models of different hardware components, enabling accurate power estimation at a high-level exploration stage. In particular the authors implement Chipwide Dynamic Voltage, Frequency Scaling, and Performance Aware Core-Specific Frequency Scaling. The FALPEM framework [39] provides power estimations at preregister transfer level (RTL) stage, specifically targeting the power consumed by clock network and interconnect, but power and clock gating costs are not defined. Other approaches perform an estimation that considers different components. Li et al. [40] propose an architecture-level integrated power, area, and timing modelling framework for multicore systems, which evaluates system building blocks (CPU, buses, etc.) for different technology nodes, providing also power gating support. Finally, the work presented in [41] focuses on onchip networks.

# 3. Design Suite for Coarse-Grained Power-Aware Systems

This section discusses the proposed technique for modelling the power consumption of a CGR system when clock gating or power gating are applied. These models, combined in a selection algorithm, can be exploited for developing an automated design flow for power-efficient CGR systems, where the optimal saving strategy is selected for each identified working set of resources.

In this work, we have embedded these models and the algorithm in the Multi-Dataflow Composer (MDC) tool,

a framework capable of CGR systems characterization. MDC provides a comprehensive design suite automating several development tasks of the synthesis and development of CGR systems, within design flows targeting both FPGA [29] and ASIC. The tool provides extensive support to dynamic power management [17, 18], addressing power-constrained design cases scenarios, completely automating implementation and control of clock gating and power gating strategies in the final CGR platform. Nevertheless, such techniques are not currently addressed in a hybrid manner, the users must choose the approach to be used in the design without an a priori automated analysis process. Such an unsupported selection may easily lead to suboptimal implementations on the final platform.

In the following, Section 3.1 provides an overview of the MDC baseline functionality and of the current power management support. Section 3.2 discusses the proposed power models and automated selection algorithm identifying optimal power management strategy in CGR systems. In both sections, step-by-step examples are presented to clarify the methodology.

3.1. The Multi-Dataflow Composer Tool. MDC automates generation and management of CGR systems, facing the complex mapping of multiple applications onto a single reconfigurable architecture. It automates the mapping process and guarantees the minimization of hardware resources, allowing for significant area/energy savings [12, 42]. In literature, this problem is known as datapath merging and it deals with the combination of a set of input datapaths, described by means of graphs, onto a single reconfigurable datapath. It aims at maximally sharing (among the different input graphs) both processing nodes and connections.

MDC is naturally compliant with the RVC-CAL formalism and natively supports Dataflow Process Network (DPN) models as input. Currently, it is interfaced with the Open RVC-CAL Compiler, Orcc [43]. The Orcc front-end is responsible for parsing, one-by-one, the high-level DPN specifications of the different datapaths that MDC will merge within the CGR system. Please note that MDC can be interfaced with other graph parsers, so that it will be able to be easily adapted to any other dataflow-based modelling environment.

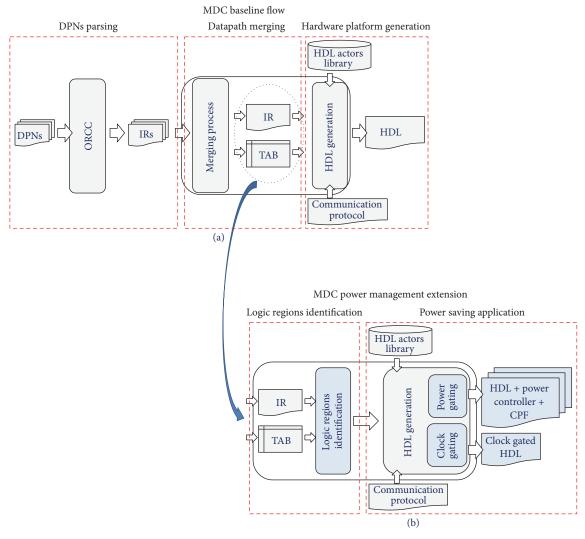

As depicted by Figure 1, the MDC baseline flow involves three main phases:

- (1) The input *DPNs parsing*, performed by the Orcc front-end, translates the RVC-CAL specifications into Java Intermediate Representations (IRs), which are basically directed graphs.

- (2) The *datapath merging*, performed by the MDC frontend, combines the IRs into a reconfigurable IR, inserting (where necessary) special switching actors (responsible for properly distributing the token flow among the different merged DPNs) keeping trace of the system programmability through a dedicated *Configuration Table* (TAB in Figure 1).

- (3) The hardware platform generation, performed by the MDC back-end, leads to the creation of the RTL

that describes the CGR system itself, where each actor of the reconfigurable IR is mapped onto a different hardware FU. In this phase, the hardware communication protocol and the *HDL* (*Hardware Description Language*) components library (providing the RTL descriptions of the required FUs, manually or automatically generated) are provided as input to the tool.

At the hardware level, reconfiguration takes place in a single clock cycle. It is achieved through low overhead switching elements (SBoxes) that allow the sharing of common resources among different input DPNs. SBoxes are simple combinatorial multiplexers and demultiplexers, whose configuration is stored into dedicated Look-Up tables that, according to the *Configuration Table*, compute the selectors necessary for the correct data forwarding in order to implement the requested functionality.

3.1.1. Automated Power Management. Dealing with reconfigurable architectures, and in particular with CGR systems, the power consumption has to be carefully taken into consideration. Such a kind of systems is affected by resource redundancy, mainly due to the FUs that are not shared among different functionalities. Thus, when a certain functionality is executed, part of the design (not involved in the computation) is in an idle state and can uselessly consume precious power. Fortunately the unused resources, for each implemented functionality, depend on the input specifications and, therefore, are fixed at design-time.

Given these considerations, then, a CGR system can be characterized by a set of disjointed *logic regions* (LRs), grouping the resources that are always active/inactive at the same time. The MDC power management extension is capable of automatically identifying LRs. It performs the *LRs identification* at a high-level of abstraction, on the reconfigurable IR, by exploiting the intrinsic modularity of the dataflow graphs. Once the LRs have been identified, the MDC dynamic power manager automatically applies, according to the user selection, either clock gating [17] or power gating [18] on the resulting CGR hardware platform. The identification of the minimal number of LRs is guaranteed, to minimize the power overhead of the extra logic needed to implement the selected power saving strategies. An overview of the power management extension is provided by Figure 1.

For each input DPN  $G_i$ , the currently available algorithm determines the set  $V_i'$ , which contains all the resources of the reconfigurable IR activated by  $G_i$ . These are the original sets of LRs that represent the starting point for the algorithm to find the final LRs by iteratively comparing two  $V_i'$  sets at a time, determining their possible overlapping. If overlapping is found, its resources are removed by the two considered sets and a new  $V_j'$  (corresponding to a new LR) involving these shared resources is issued.  $V_j'$  groups resources that are shared among different input DPNs, while the remaining resources in the two  $V_i'$  will uniquely belong to the originally considered DPNs. This compare and split identification process guarantees that the number of LRs found by the MDC dynamic power manager is the minimum achievable one.

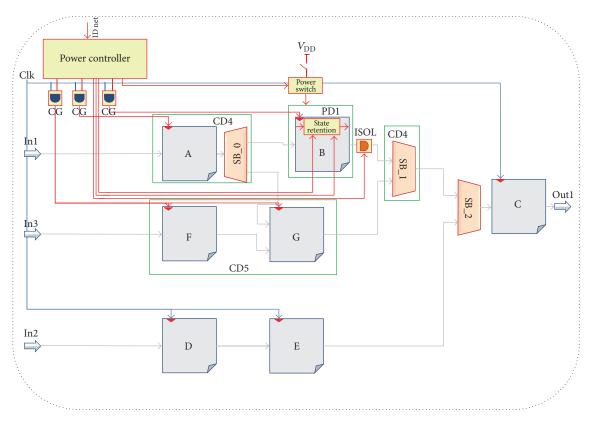

FIGURE 1: MDC design suite: baseline flow (a) and corresponding power extension (b).

If this number is still too high for the considered target platform, as it can happen if FPGAs are the target devices (in FPGA devices the number of hardware blocks that can drive the different LRs is limited; e.g., 32 BUFG units are available in Xilinx boards for clock management purposes), a LRs merging process has to be applied. MDC users are required to specify the target technology and the maximum number of implementable LRs. This latter is compared with the number of LRs determined by the compare and split identification process and, if necessary, the LRs merging process is applied. Two LRs at a time are unified (details on how to merge different LR sets can be found in [17], where two merging strategies (a power-aware one and a number-aware one) are presented) until the constraint fixed by the user is met. This process leads to a suboptimal system implementation: each DPN, while activating its corresponding LRs, may also activate some resources that do not contribute to its computation, leading to extra unnecessary power consumption.

MDC power management extension, during the HDL generation phase, provides also the implementation of the

chosen power management strategy upon the identified LRs. It blindly applies the selected strategy to all the identified LRs, without any warranty on the approach effectiveness. Clock gating acts only on the dynamic contribute of the power consumption and requires a minimum logic overhead on the final platform. Indeed, the simplest implementation is achieved by means of one AND gate for each LR plus one unique Enable Generator to properly set the enable signals of the AND gates according to the desired functionality. On the contrary, power gating is able to reduce both power contributions, static and dynamic, by shutting off the power supply of the region. However, it is quite more invasive, since it requires one power switch for each LR, one state retention cell for each Flip-Flop whose state has to be kept also when the corresponding LR is off, and one isolation cell for each bit-wise wire that goes from a disabled LR to an enabled one. A different clock gating cell (again an AND gate) is required for each LR, according to the switching-off protocol for the proper operation of the retention cells (details on the power gating switch on/off protocol can be found in [11]). Furthermore,

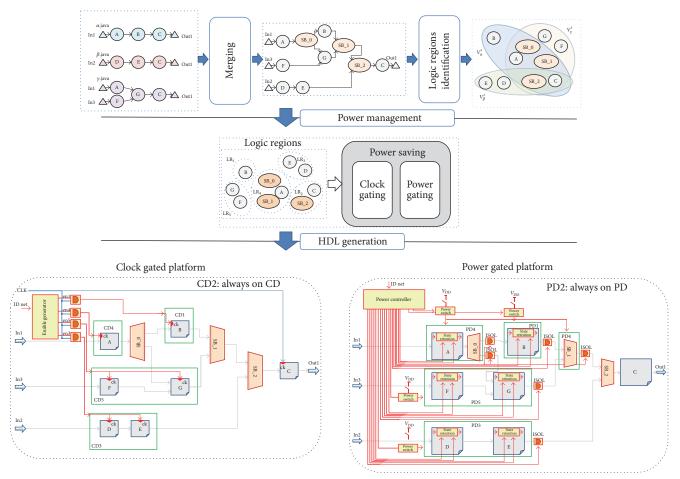

FIGURE 2: Step-by-step example of the MDC baseline and dynamic power management features. Saving strategies are blindly applied by the dynamic power manager on each identified LR.

one *Power Controller* block (involving a different finite state machine for each LR) is needed to properly drive the inserted *power switch*, *state retention* and *isolation* cells.

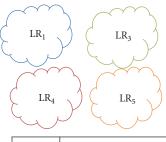

3.1.2. Step-by-Step Example. In order to clarify the features provided by MDC baseline functionality and its related dynamic power manager extension, this section describes a step-by-step example of the whole flow. Three different input functionalities, labelled  $\alpha$ ,  $\beta$ , and  $\gamma$ , are considered and modelled as DPNs. As first step of the baseline MDC functionality, the DPNs are parsed by the Orcc font-end and translated into Java IR graphs. Figure 2 depicts an overview of the whole flow starting from these input IRs ( $\alpha$ . java,  $\beta$ . java, and  $\gamma$ . java). At this level, MDC combines the dataflows into a reconfigurable IR inserting the SBox actors (SB in Figure 2). Three SBoxes are required to share actor A between  $\alpha$  and  $\gamma$  and actor C among all the three functionalities.

Once the reconfigurable IR has been derived, the dynamic power manager can identify the corresponding LRs. The starting  $V_i'$  sets are

(i)

$$V'_{\alpha} = \{A, B, C, SB_0, SB_1, SB_2\};$$

(ii)

$$V'_{\beta} = \{D, E, C, SB_2\};$$

(iii)

$$V'_{\gamma} = \{A, F, G, C, SB_0, SB_1, SB_2\}.$$

The compare and split identification process produces five different LRs:

(i)

$$LR_1 = \{B\}.$$

(ii)

$$LR_2 = \{C, SB\_2\}.$$

(iii)

$$LR_3 = \{D, E\}.$$

(iv)

$$LR_4 = \{A, SB_0, SB_1\}.$$

(v)

$$LR_5 = \{F, G\}.$$

LR<sub>4</sub> and LR<sub>2</sub> involve shared resources, being activated, respectively, by  $\alpha$  and  $\gamma$  and by  $\alpha$ ,  $\beta$ , and  $\gamma$ , while the remaining LRs involve nonshared resources. LR<sub>1</sub> is activated only by  $\alpha$ , LR<sub>3</sub> only by  $\beta$ , and LR<sub>5</sub> only by  $\gamma$ .

At this point, the selected power saving strategy is applied during the CGR system HDL generation. Figure 2 shows both the final designs resulting from the application of clock gating and power gating.

The clock gated platform is shown in the bottom left corner of Figure 2. In this case, the identified LRs become the Clock Domains (CDs) of the resulting architecture, meaning that the involved actors are all driven by the same gated clock. SBoxes are not included in any CD since they are fully

combinatorial modules. It can be noticed by Figure 2 that the clock gating overhead is limited to four AND gates (LR $_2$  is activated by all the implemented functionalities and does not need to be turned off) and one  $Enable\ Generator$  that properly assigns the clock enable values.

The power gated platform is depicted in the bottom right corner of Figure 2. LRs define the architecture power domains (PDs) where, in this case, also SBoxes are taken into consideration. Power gating turns off the whole PD power supply and it has effect also on combinatorial blocks. Figure 2 clearly shows that the logic overhead of power gating is larger than the clock gating one. In the power gated platform *power switches, state retention* cells, *isolation* cells, and one *Power Controller* are inserted. Please note that clock gating cells are not reported for simplicity. Again the logic necessary to switch off LR<sub>2</sub> is avoided since this region is an always on one (being activated by all the input DPNs).

3.2. Automated Power Management with Hybrid Clock and Power Gating. To overcome the limits of a blindly applied unique power management strategy, we propose, in this paper, a power estimation flow capable of (1) characterizing, at a high-level of abstraction, the LRs identified by the MDC power extension, and of (2) autonomously applying the optimal power reduction technique for each LR. Power and clock gating overhead are estimated, based on LRs characteristics, before any physical implementation. This strategy is meant for ASIC technologies, which allow hybrid power and clock gating support over the same CGR design.

The estimation is based on two sets of models that determine the static and dynamic consumptions of each LR when clock gating or power gating are applied. The proposed models are derived after a single logic synthesis of the baseline CGR system generated by MDC, carried out with commercial synthesis tools from the analysis of the power reports obtained after netlist simulation. Such a synthesis constitutes the only implementation effort required for the designer, besides the characterization of technique-specific blocks such as the *Enable Generator* or the *Power Controller*. Models are technology-dependent since they include parameters that are characteristic of the chosen target technology library, as it will be discussed in Section 3.2.4.

3.2.1. Power Gating: Static Power Consumption Model. Static power can be estimated on the basis of the leakage contributes provided, for each cell, by the targeted ASIC library. Given any hardware FU (uniquely corresponding to an actor of the reconfigurable IR) its static power can be obtained by summing up the single contributions of the adopted cells. The static power consumption term is tightly related to the LR area: the more cells are included in the considered region, the more is its corresponding static dissipation.

The proposed model for the static power consumption is defined as follows:

$$\begin{aligned} P_{\text{lkg}}\left(\text{LR}_{i}\right) &= P_{\text{lkgON}}\left(\text{LR}_{i}\right) + \text{Ext\_Over}_{\text{lkg}}\left(\text{LR}_{i}\right) \\ &= \sum_{\text{actors} \in \text{LR}_{i}} \left[P_{\text{lkg}}\left(\text{cmb}\right) + P_{\text{lkg}}\left(\text{RC}\right) * \text{\#rtn} \right] \end{aligned}$$

$$\begin{split} &+P_{lkg}\left(\text{reg}\right)*\frac{\#\text{reg}-\#\text{rtn}}{\#\text{reg}}\right]*\text{Ti}_{ON}+\left[P_{lkg}\left(\text{ISO}_{ON}\right)\right.\\ &*\text{Ti}_{ON}+P_{lkg}\left(\text{ISO}_{OFF}\right)*\text{Ti}_{OFF}\right]*\#\text{iso}\\ &+\left[P_{lkg}\left(\text{Contr}_{ON}\right)*\text{Ti}_{ON}+P_{lkg}\left(\text{Contr}_{OFF}\right)\right.\\ &*\text{Ti}_{OFF}\right]+\left[P_{lkg}\left(\text{CG}_{ON}\right)*\text{Ti}_{ON}+P_{lkg}\left(\text{CG}_{OFF}\right)\right.\\ &*\text{Ti}_{OFF}\right]. \end{split}$$

Dealing with a prospective power gating implementation, the static estimation (1) for each LR involves two terms:  $P_{\rm lkgON}({\rm LR}_i)$  corresponds to the static consumption when the LR is active and  ${\rm Ext\_Over}_{\rm lkg}({\rm LR}_i)$  refers to the power overhead due to the additional power gating logic. This second term does not consider the *power switch* overhead, since it is not included in the prelayout netlist. Power gating prevents, by definition, any static dissipation on the LR when disabled; therefore, (1) does not present any  $P_{\rm lkgOFF}({\rm LR}_i)$ .

$P_{\text{lkgON}}(LR_i)$  is obtained as the multiplication of the LR activation time Ti<sub>ON</sub> and the sum of leakage power of the involved actors, considering separately combinatorial and sequential logic. The former,  $P_{\rm lkg}$  (cmb), is equal to the leakage of the combinatorial cells within the considered LR. The latter is related to the number of registers (#reg) within the LR and their need (according to the implemented functionality) of preserving or not their status, by means of state retention cells, when the region is inactive. Then it involves, in turn, two terms. The first one refers to the registers whose state can be lost and it is estimated on the basis of the static consumption of the sequential cells ( $P_{lkg}(reg)$ ), as an average on the number of registers that are not retained. The second one refers to the retention cells and it is estimated starting from the number of registers whose state has to be maintained (#rtn) multiplied by the leakage of a single state retention cell ( $P_{lkg}(RC)$ ), whose value is retrieved from the target ASIC library.

$\operatorname{Ext-Over}_{\operatorname{lko}}(\operatorname{LR}_i)$  is composed of three terms: the first one is related to the isolation cells (#iso), the second one to the Power Controller, and the third one to the clock gating cell (the power gating switch off protocol requires applying clock gating at the region level, before retaining the registers value). Note that, unlike  $P_{lkgON}$ , for the three abovementioned terms,  $\mathsf{Ext\_Over}_{\mathsf{lkg}}$  characterizes the LR static consumption in both its on and off states. In the on state, the model accounts for the static consumption in the on state (e.g.,  $P_{\rm lkg}({\rm ISO_{ON}}))$ multiplied by the activation time Ti<sub>ON</sub> and by the overall number of cells within the LR (e.g., #iso). In the off state, the model accounts for the static consumption in the off state (e.g.,  $P_{\rm lkg}({\rm ISO}_{\rm OFF})$ ) multiplied by the inactive time  ${\rm Ti}_{\rm OFF}$ and by the overall number of cells within the LR (e.g., #iso). Please note that there is just one Power Controller for all the LRs and one clock gating cell per LR, but an a priori characterization phase would be required to the designer, since their consumption values cannot be retrieved directly from any ASIC library.

3.2.2. Power Gating: Dynamic Power Consumption Model. Estimating the dynamic power is more complex than estimating the static one, since this term strongly depends on the nodes switching activity. Frequently, commercial tools (e.g., Cadence Encounter Digital Implementation System) consider dynamic power as composed of two main terms, as depicted by (2): a net contribution due to the power dissipated throughout the wires linking the cells, and an internal contribution due to the dissipation occurring inside the cells [44]:

$$\begin{split} P_{\rm dyn} &= P_{\rm net} + P_{\rm int} \\ &= \frac{1}{2} f V_{DD}^2 \sum_{\rm net_i} C_{\rm load_j} SW_j + f \sum_{\rm cell_i} P_i SW_i. \end{split} \tag{2}$$

The operating frequency, f, influences both terms.  $P_{\text{net}}$  accounts for the load capacitance of each  $\text{net}_j$  (bearing a specific capacitance  $C_{\text{load}_j}$ ) and the related switching activity  $(SW_j)$ , whereas  $P_{\text{int}}$  depends on the power per MHz dissipated by each cell  $(P_i)$  and the related switching activity  $(SW_i)$ .

Currently, the developed model is able to estimate only the  $P_{\text{int}}$  contribution that can be expressed for each single LR as follows:

$$\begin{split} P_{\text{int}}\left(\text{LR}_{i}\right) &= P_{\text{intON}}\left(\text{LR}_{i}\right) + \text{Ext\_Over}_{\text{int}}\left(\text{LR}_{i}\right) \\ &= \sum_{\text{actors} \in \text{LR}_{i}} \left[P_{\text{int}}\left(\text{cmb}\right) + P_{\text{int}}\left(\text{RC}\right) * \#\text{rtn} \right. \\ &+ P_{\text{int}}\left(\text{reg}\right) * \frac{\#\text{reg} - \#\text{rtn}}{\#\text{reg}}\right] * \text{Ti}_{\text{ON}} + \left[P_{\text{int}}\left(\text{ISO}_{\text{ON}}\right) \right. \\ &* \text{Ti}_{\text{ON}} + P_{\text{int}}\left(\text{ISO}_{\text{OFF}}\right) * \text{Ti}_{\text{OFF}}\right] * \#\text{iso} \\ &+ \left[P_{\text{int}}\left(\text{Contr}_{\text{ON}}\right) * \text{Ti}_{\text{ON}} + P_{\text{int}}\left(\text{Contr}_{\text{OFF}}\right) \right. \\ &* \text{Ti}_{\text{OFF}}\right] + \left[P_{\text{int}}\left(\text{CG}_{\text{ON}}\right) * \text{Ti}_{\text{ON}} + P_{\text{int}}\left(\text{CG}_{\text{OFF}}\right) \right. \end{split}$$

Considering a prospective power gating implementation, the different parts of (3) basically reflect the ones of (1). The main difference among the static power model and the dynamic one is that this latter requires accurate data in terms of nodes switching activity. For this reason, the netlist of the baseline CGR system is not sufficient to retrieve accurate values from the power reports and one different simulation of the netlist for every implemented functionality is required. Thus, dynamic power model takes into consideration the real system switching activity provided by the hardware simulations.

The  $P_{\rm net}$  term of (2) is not currently addressed in our model. Nevertheless, as demonstrated further on in this work (please see Tables 8, 9, 12, and 14) neglecting this term seems not to affect the optimal identification of the region to be gated. We have already planned to extend the proposed methodology to include the nets contribution in a near future.

3.2.3. Clock Gating: Static and Dynamic Power Consumption Models. Clock gating static and dynamic models are less complicated than the power gating ones, since clock gating requires a very low logic overhead and it positively acts only on the dynamic dissipation. Equations (4) and (5) report the models adopted, respectively, for the static power estimation and for the dynamic power one, referring to a clock gated design:

$$P_{lkg}(LR_{i}) = P_{lkg}(LR_{i}) + Ext\_Over_{lkg}(LR_{i})$$

$$= \sum_{actors \in LR_{i}} [P_{lkg}(cmb) + P_{lkg}(reg)]$$

$$+ [P_{lkg}(Enab_{ON}) * Ti_{ON} + P_{lkg}(Enab_{OFF}) * Ti_{OFF}]$$

$$+ [P_{lkg}(CG_{ON}) * Ti_{ON} + P_{lkg}(CG_{OFF}) * Ti_{OFF}],$$

$$P_{int}(LR_{i}) = P_{int}(LR_{i}) + Ext\_Over_{int}(LR_{i})$$

$$= P_{int}(combLR_{i}) + P_{intON}(seqLR_{i})$$

$$+ Ext\_Over_{int}(LR_{i})$$

$$= \sum_{actors \in LR_{i}} [P_{int}(cmb) + P_{int}(reg) * Ti_{ON}]$$

$$+ [P_{int}(Enab_{ON}) * Ti_{ON} + P_{int}(Enab_{OFF}) * Ti_{OFF}]$$

$$+ [P_{int}(CG_{ON}) * Ti_{ON} + P_{int}(CG_{OFF}) * Ti_{OFF}].$$

At the logic region level, (4) considers always the combinatorial and sequential contributions for both the on or off states, since clock gating does not affect the system leakage, whereas (5) considers always the combinatorial part for both the on or off states, since combinatorial logic cannot benefit from clock gating and the sequential contribution only during the LR active time. The overhead,  $\text{Ext\_Over}_{\text{int}}(\text{LR}_i)$ , is given by the clock gating cell and the *Enable Generator*. Please remember that implementing clock gating management at a coarse-grained level, just one clock gating cell per LR has to be inserted within the system. Equation (5) is pretty much the same as (4), a part from the fact that, dealing with the dynamic model, clock gating effects are estimated by omitting the contribute of sequential logic when the LR is off.

*3.2.4. Parameters Discussion.* The proposed models are determined by the intrinsic features of the LRs. In particular, they consider the following:

- (i) Architectural Parameters. LRs composition determines the amount of involved combinatorial and sequential cells.

- (ii) *Functional Parameters*. LRs behaviour defines the region activation time and if its status has to be preserved or not.

- (iii) *Technological Parameters*. Target technology has an impact on the ratio between dynamic and static power (as it will be demonstrated in Section 4.2) and on the different cells characterization.

Table 1 reports, for each parameter considered in (1), (3), (4), and (5), their classification. A deeper explanation about  $P_{\rm lkg/int}({\rm cmb})$  and  $P_{\rm lkg/int}({\rm reg})$  is necessary. They are not associated with any specific parameters class, indeed they depend on type and number of involved cells composing the considered LR and also on the system switching activity (especially for the internal contribute). These values are gathered by the reports of the baseline CGR system netlist, assuming that the amount and type of cells composing the FUs do not change as power saving strategies are applied (except for the retained registers).

3.2.5. Step-by-Step Example. The example proposed in Figure 2 shows the merging process of three DPNs in a CGR system, where five LRs have been identified. Equations (1), (3), (4), and (5) can be applied to all of them. However, as already discussed, LR2 can be discarded: being common to all the input DPNs, it is always active and does not require to be switched-off. As defined in the previous section, the parameters reported in Table 2 are extracted by the reference technology library or characterized by synthesis trials (see the definition provided in Table 1). The power consumption values in Table 3 have been extracted by the synthesis reports of the baseline (with no power saving applied) CGR platform and required three hardware simulations (one for each input kernel). These simulations are necessary to correctly estimate the internal power consumption of the different LRs, taking into account the real switching activity of the design. In practice, power values are determined as an average of those obtained according to the different switching activity profiles.

Starting from the data in Tables 3 and 2, here follows the detailed equations characterization for  $LR_5$ , which include actors F and G.

When power gating is applied, the static power consumption of  $LR_5$  is derived according (1), as follows:

$$\begin{split} P_{\text{lkg}}\left(\text{LR}_{5}\right) &= \left[\left(P_{\text{lkg}}\left(\text{comb}_{F}\right) + P_{\text{lkg}}\left(\text{RC}\right) * \#\text{rtn}F\right.\right.\\ &+ P_{\text{lkg}}\left(\text{reg}_{F}\right) * \frac{\#\text{reg}F - \#\text{rtn}F}{\#\text{reg}F}\right) + \left(P_{\text{lkg}}\left(\text{comb}_{G}\right)\right.\\ &+ P_{\text{lkg}}\left(\text{RC}\right) * \#\text{rtn}G + P_{\text{lkg}}\left(\text{reg}_{G}\right)\\ &+ \frac{\#\text{reg}G - \#\text{rtn}G}{\#\text{reg}G}\right)\right] * T5_{\text{ON}} + \left[P_{\text{lkg}}\left(\text{ISO}_{\text{ON}}\right)\right.\\ &* T5_{\text{ON}} + P_{\text{lkg}}\left(\text{ISO}_{\text{OFF}}\right) * T5_{\text{OFF}}\right] * \#\text{iso}_{5}\\ &+ \left[P_{\text{lkg}}\left(\text{Contr}_{\text{ON}}\right) * T5_{\text{ON}} + P_{\text{lkg}}\left(\text{Contr}_{\text{OFF}}\right)\right.\\ &* T5_{\text{OFF}}\right] + \left[P_{\text{lkg}}\left(\text{CG}_{\text{ON}}\right) * T5_{\text{ON}} + P_{\text{lkg}}\left(\text{CG}_{\text{OFF}}\right)\right.\\ &* T5_{\text{OFF}}\right] = \left[\left(213 + 17.15 * 128\right) + \left(273 + 17.15\right.\\ &* 64 + 1385 * 0.5\right] * 0.3 + \left[4.27 * 0.3 + 1.39\right.\\ &* 0.7\right] * 32 + \left[95.44 * 0.3 + 88.63 * 0.7\right] + \left[5.77\right.\\ &* 0.3 + 4.71 * 0.7\right] = 1509.219. \end{split}$$

(6)

The internal power consumption is given by (3):

$$\begin{split} P_{\text{int}}\left(\text{LR}_{5}\right) &= \left[\left(P_{\text{int}}\left(\text{comb}_{F}\right) + P_{\text{int}}\left(\text{RC}\right) * \#\text{rtn}F\right.\right.\\ &+ P_{\text{int}}\left(\text{reg}_{F}\right) * \frac{\#\text{reg}F - \#\text{rtn}F}{\#\text{reg}F}\right) + \left(P_{\text{int}}\left(\text{comb}_{G}\right)\right.\\ &+ P_{\text{int}}\left(\text{RC}\right) * \#\text{rtn}G + P_{\text{int}}\left(\text{reg}_{G}\right)\\ &* \frac{\#\text{reg}G - \#\text{rtn}G}{\#\text{reg}G}\right)\right] * T5_{\text{ON}} + \left[P_{\text{int}}\left(\text{ISO}_{\text{ON}}\right)\right.\\ &* T5_{\text{ON}} + P_{\text{int}}\left(\text{ISO}_{\text{OFF}}\right) * T5_{\text{OFF}}\right] * \#\text{iso}_{5} & (7)\\ &+ \left[P_{\text{int}}\left(\text{Contr}_{\text{ON}}\right) * T5_{\text{ON}} + P_{\text{int}}\left(\text{Contr}_{\text{OFF}}\right)\right.\\ &* T5_{\text{OFF}}\right] + \left[P_{\text{int}}\left(\text{CG}_{\text{ON}}\right) * T5_{\text{ON}} + P_{\text{int}}\left(\text{CG}_{\text{OFF}}\right)\right.\\ &* T5_{\text{OFF}}\right] = \left[\left(537 + 383.25 * 128\right) + \left(363 + 383.25\right)\right.\\ &* 64 + 44068 * 0.5\right] * 0.3 + \left[2.7 * 0.3 + 0 * 0.7\right]\\ &* 32 + \left[1449 * 0.3 + 1488 * 0.7\right] + \left[169 * 0.3\right.\\ &+ 292 * 0.7\right] = 30217.72. \end{split}$$

When clock gating is considered, (4) and (5) are computed as follows:

$$P_{lkg} (LR_5) = [(P_{lkg} (comb_F) + P_{lkg} (reg_F)) + (P_{lkg} (comb_G) + P_{lkg} (reg_G))] + [P_{lkg} (Enab_{ON}) + (P_{lkg} (comb_G) + P_{lkg} (reg_G))] + [P_{lkg} (Enab_{ON}) + T5_{ON} + P_{lkg} (Enab_{OFF}) * T5_{OFF}] + [P_{lkg} (CG_{ON}) + T5_{ON} + P_{lkg} (CG_{OFF}) * T5_{OFF}] = [(213 + 1232) + (273 + 1385)] + [84.51 * 0.3 + 76.54 * 0.7] + [5.77 * 0.3 + 4.71 * 0.7] = 3186.96,$$

$$P_{int} (LR_5) = [(P_{int} (comb_F) + P_{int} (reg_F) * T5_{ON}) + (P_{int} (comb_G) + P_{int} (reg_G) * T5_{ON})] + [P_{int} (Enab_{ON}) * T5_{ON} + P_{int} (Enab_{OFF}) + [P_{int} (CG_{ON}) * T5_{ON} + P_{int} (CG_{OFF}) + T5_{OFF}] + [P_{int} (CG_{ON}) * T5_{ON} + P_{int} (CG_{OFF}) + T5_{OFF}] = [(537 + 22489 * 0.3) + (363 + 44068 * 0.3)] + [1351 * 0.3 + 1320 * 0.7] + [169 * 0.3 + 292 * 0.7] = 22451.8.$$

Table 4 summarizes all the values achieved applying the proposed static and dynamic models to all the different logic regions.

3.2.6. Hybrid Clock and Power Gating Support and Integration in MDC. The discussed models (described in (1), (3), (4), and (5)) have been integrated in the MDC design flow, in order to implement a fully automated power management

|                                                                                                                                                                    |       | T      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                          | Arch. | Funct. | Tech.   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Extraction                                                                                                    |

| #reg                                                                                                                                                               | ×     |        |         | Number of sequential cells in the considered LR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Provided by the synthesis reports                                                                             |

| #iso                                                                                                                                                               | ×     |        |         | Number of estimated isolation cells in the design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Obtained by counting the number of wires that connect the different LR among each other in the dataflow model |

| Ti <sub>OH</sub>                                                                                                                                                   |       | ××     |         | Activation time<br>Off time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Found by means of a high-level (directly on the dataflow) profiling of the targeted scenario                  |

| #rtn                                                                                                                                                               |       | ×      |         | Number of retention cells in the design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Strictly related to the LR functionality and is chosen by the designer                                        |

| Plkg/int (RC) Plkg/int (ISO <sub>ON</sub> ) Plkg/int (ISO <sub>ON</sub> )                                                                                          |       |        | x x x   | Power estimation of retention and isolation cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Determined by the selected synthesis process and can be obtained without any implementation run               |

| $P_{ m kg/int}\left( m Contr_{ON} ight) \ P_{ m kg/int}\left( m Contr_{OFF} ight) \ P_{ m kg/int}\left( m Enab_{ON} ight) \ P_{ m kg/int}\left( m Enab_{ON} ight)$ |       |        | × × × × | Power estimation of PG and CG controller<br>when the LR is on or off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | It requires being characterized, according to the target technology, with dedicated synthesis trials          |

| $rac{P_{ m lkg/int}( m cmb)}{P_{ m lu} = r_{ m cm}( m reg)}$                                                                                                      | × ×   | ××     | ××      | Power consumed by combinatorial and sequential cells within the considered LR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Gathered by the reports of the baseline CGR system netlist                                                    |

| 1 lba/int (10%)                                                                                                                                                    | 4     | ٧      | ۷       | and designed or the contract of the contract o | 200000000000000000000000000000000000000                                                                       |

TABLE 2: Contributions of static and internal power consumption extracted by the reference technology library or characterized by synthesis trials.

| Parameters          | lkg power [nW] | int power [nW] |

|---------------------|----------------|----------------|

| Enab <sub>ON</sub>  | 84.51          | 1351           |

| Enab <sub>OFF</sub> | 76.54          | 1320           |

| $Contr_{ON}$        | 95.44          | 1449           |

| $Contr_{OFF}$       | 88.63          | 1488           |

| $CG_{ON}$           | 5.77           | 169            |

| $CG_{OFF}$          | 4.71           | 292            |

| $ISO_{On}$          | 4.27           | 2.7            |

| ISO <sub>OFF</sub>  | 1.39           | 0              |

| P(RC)               | 17.15          | 383.25         |

```

PG_set is empty;

CG_set is empty;

foreach LR; in set LRs do

evaluate_area(LR<sub>i</sub>, area<sub>th</sub>)

end

function: evaluate_area(LR<sub>i</sub>, area<sub>th</sub>):

calculate_LR;_area;

\textbf{if} \ area_{LR} > area_{th} \ \textbf{then}

evaluate_PG(LR_i);

else

evaluate_CG(LR<sub>i</sub>);

end

function: evaluate_PG(LR<sub>i</sub>):

estimate_PG_total_overhead;

if PG_total_overhead < 0 then

estimate_CG_total_overhead;

if PG_total_overhead < CG_total_overhead then

add LR, to PG_set;

add LR, to CG_set;

end

else

evaluate_CG(LR<sub>i</sub>);

end

evaluate_CG(LR<sub>i</sub>);

function: evaluate_CG(LR<sub>i</sub>):

estimate_CG_total_overhead;

if CG_total_overhead < 0 then

add LR<sub>i</sub> to CG_set;

end

```

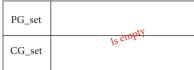

ALGORITHM 1: Automatic power saving strategy selection for CGR systems.

strategy. Designers are guided towards the optimal solution for each LR, rather than choosing a one-fit-to-all switching-off technique for all of them.

This automated selection flow is implemented as reported in Algorithm 1. For each LR, identified by the MDC power management extension, Algorithm 1 executes the following steps, embodied by different functions.

(1) Area Thresholding (See evaluate\_area Function). As previously discussed, power gating is a quite invasive technique,

requiring a lot of extra logic to be inserted in the nonswitchable always on domain. Thus, for small LRs, we can assume that it will not bring any benefit, so that power gating is not to be considered for implementation. Indeed, clock gating may still be beneficial, due to its very small additional logic amount.

(2) Power Gating Overhead Estimation (See evaluate\_PG Function in Algorithm 1). Power gating cost is estimated in order to find out if it can lead to power saving or not. The prospective power and clock gating implementations are compared on the basis of their overall consumption. Equation (1) is applied and summed to (3), if there is not total power saving the algorithm goes to the clock gating overhead estimation. On the contrary, if there is saving it has to be compared with the sum of (4) and (5) to determine whether the current LR may benefit from power gating (despite its larger overhead) or from clock gating.

(3) Clock Gating Overhead Estimation (See evaluate\_CG Function in Algorithm 1). Clock gating cost is estimated to investigate the possibility of achieving power saving with this technique. If the LR clock gating achievable saving does not counterbalance its implementation costs, the LR is discarded. This means that when the MDC back-end generates the RTL description of the CGR system, the LR logic is included in the always on domain. On the contrary, if the clock gating leads to an overall saving in terms of total power, the LR will be clock gated during the implementation.

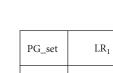

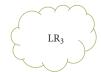

The output of Algorithm 1 is the classification of the LRs, stating which one should be power gated (see PG\_set in Algorithm 1), which one should be clock gated (see CG\_set in Algorithm 1), and which ones should be included in the always on domain.

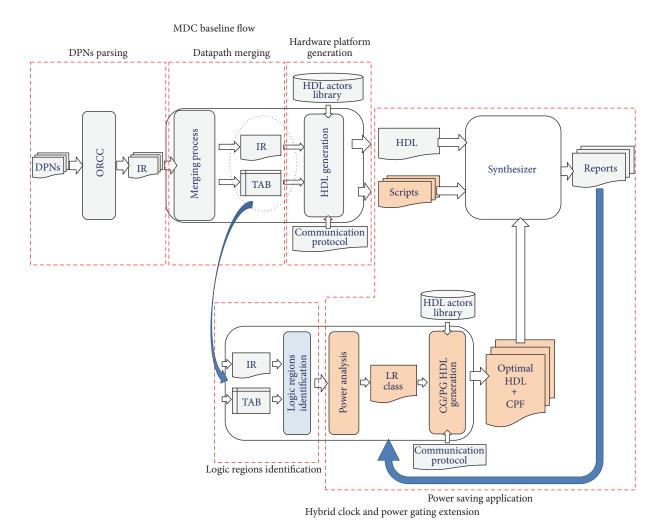

Figure 3 provides an overview of the modified design flow. As it can be noticed, the MDC tool and its power management extension are directly interfaced with the logic synthesizer. Algorithm 1 is implemented within the *Power Analysis* block. MDC baseline tool provides the HDL description of the plain CGR system and all the scripts to perform the synthesis of the CGR design and all the different hardware simulations (one for each input DPNs), as required by the proposed power estimation models. The power reports are then fed back to the MDC power management extension and parsed within the *Power Analysis* to execute Algorithm 1. The LRs classification (see LR class in Figure 3), generated by the *Power Analysis* block, is used by the *CG/PG HDL Generation* block to automatically define the hybrid, clock and power gating, power management support for the given CGR design.

Summarizing, this flow, with respect to what is discussed in Section 3.1, does not require designers to opt for a specific power management technique. On the basis of the proposed power estimation models and by linking MDC with a logic synthesis tool, the presented flow is capable of overcoming the limit of providing a one-fit-to-all solution. Each LR, in a CGR design, is supported (where necessary) with the optimal power management technique.

| Logic region          | Kernel   | $T_{ m ON}$ | Actors        | #iso      | #reg | #rtn |

|-----------------------|----------|-------------|---------------|-----------|------|------|

| $\overline{LR_1LR_1}$ | α        | 0.1         | В             | 32        | 514  | 24   |

| LR <sub>3</sub>       | β        | 0.6         | D, E          | 32        | 8    | 8    |

| $LR_4$                | α, γ     | 0.4         | A, SB_0, SB_1 | 96        | 256  | 64   |

| $LR_5$                | γ        | 0.3         | F, G          | 32        | 265  | 192  |

| Actor                 |          | P           | ower [nW]     |           |      |      |

| Actor                 | lkg seq. | int seq     | lkg comb.     | int comb. | #reg | #rtn |

| В                     | 801      | 104987      | 121411        | 3916599   | 512  | 24   |

| D                     | 48       | 1104        | 51            | 319       | 4    | 4    |

| E                     | 56       | 1437        | 53            | 198       | 4    | 4    |

| A                     | 3264     | 89238       | 0             | 0         | 256  | 64   |

| SB_0                  | 0        | 0           | 307           | 409       | _    | _    |

| SB_1                  | 0        | 0           | 225           | 350       | _    | _    |

| F                     | 1232     | 22489       | 213           | 537       | 128  | 128  |

| G                     | 1385     | 44068       | 273           | 363       | 128  | 64   |

Table 3: Parameter and power consumption of each LR, extracted by the synthesis reports of the baseline CGR platform.

TABLE 4: Resulting power consumption of the different LRs when the proposed models are applied.

| Logic region    | lkg PG [nW] | int PG [nW] | lkg CG [nW] | int CG [nW] |

|-----------------|-------------|-------------|-------------|-------------|

| LR <sub>1</sub> | 1240.69     | 404358.71   | 122294.15   | 3928700.60  |

| LR <sub>3</sub> | 342.67      | 3884.44     | 294.67      | 3599        |

| $LR_4$          | 2062.11     | 38705.08    | 3880.86     | 5598.6      |

| LR <sub>5</sub> | 1509.58     | 30712.72    | 3186.96     | 22451.8     |

- 3.2.7. Step-by-Step Example. In this section, a step-by-step example of the application of Algorithm 1 is presented, considering the same example proposed in Figure 2. In that case, MDC LRs identification led to determining five LRs and the user-specified power management technique is blindly applied to all of them except LR<sub>2</sub>. This region is used by all the input DPNs; thus, it is never disabled and does not require any power management support. In the following step-by-step example, shown in Figure 4, the threshold on the area (area<sub>th</sub>) is set to 5%.

- (i) LR<sub>1</sub> is processed by invoking evaluate\_area(LR<sub>1</sub>, 5).

- (a) Its area is calculated: area<sub>LR1</sub> = 52% of total area.

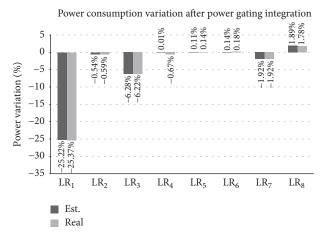

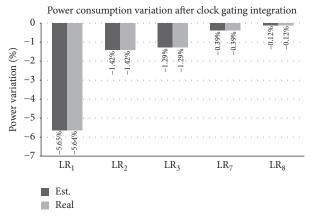

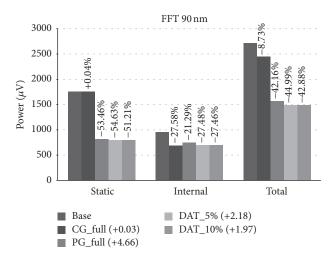

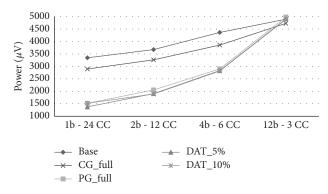

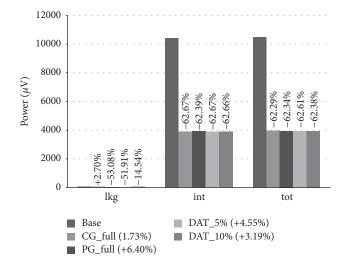

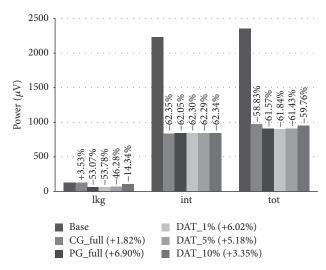

- (b) area<sub>LR1</sub> > area<sub>th</sub>, so that a prospective power gating implementation on LR<sub>1</sub> is taken into consideration by invoking evaluate\_PG(LR<sub>1</sub>).