Sede Amministrativa: Università degli Studi di Padova

Dipartimento di Ingegneria dell'Informazione

SCUOLA DI DOTTORATO DI RICERCA IN INGEGNERIA DELL'INFORMAZIONE INDIRIZZO: SCIENZA E TECNOLOGIA DELL'INFORMAZIONE CICLO XXV

# Novel Offline Switched Mode Power Supplies for Solid State Lighting Applications

Direttore della Scuola: Ch.mo Prof. Matteo Bertocco

Coordinatore di Indirizzo: Ch.mo Prof. Carlo Ferrari

Supervisore: Ch.mo Prof. Giorgio Spiazzi

**Dottorando:** Francesco Sichirollo

## Acknowledgements

"Con un sorriso sarà tutto più semplice..."

First of all I would like to thank my supervisor Prof. Giorgio Spiazzi for his invaluable support, that gave me the possibility to continuously improve my scientific and personal skills during my PhD. His wise, careful and tireless way of working have been for me an important reference in all these years.

With him, I want to thank also all the other members of the power electronics research group "PEL" of the University of Padova: Prof. Simone Buso, Prof. Paolo Mattavelli, Prof. Leopoldo Rossetto, Prof. Paolo Tenti, Dr. Luca Corradini, Dr. Marco Stellini and Mr. Renato Sartorello, who helped and encouraged me, actively contributing to my professional and personal growth.

A special thanks goes to my colleague, running mate and dear friend Dr. Alessandro Costabeber. He shared with me daily progress and stress during all these years, being an important source of suggestions and motivation.

Best of luck to all the newcomers of our research group, the PhD students Tommaso Caldognetto, Stefano Lissandron and Luca Scandola. My best wishes to all of them for an enjoyable and fruitful activity and a successful future.

I want also to express my sincere gratitude to all the people of the "CE3I2" research group of the University of Oviedo in Gijón, that I had the opportunity to join as a visiting researcher during my PhD. Their warm hospitality made me to feel at home every day of my stay. In particular, I would like to thank Prof. J. Marcos Alonso. Work with him has been for me really a great experience. His supervision, support and kind help really enriched me a lot both professionally and personally. A particular thanks goes also to his family. Their kindness and friendship further contributed to make my stay in Gijón a fantastic experience, that I will always remember with great pleasure.

With them I also want to thank all my friends and all the people that I had the opportunity to meet so far, who gave me good times, ideas and teachings. They continuously enrich my life with a lot of good memories and push me to do my best every day.

In conclusion, a heartfelt "Grazie!" goes to the most important people in my life: my family and Martina. In all these years they loved me so much to constantly encourage me to realize my projects, even if these often forced me to stay away from all of them.

It may sound obvious to keep in mind to always thank the persons to whom we owe all we have, but unfortunately it is not so. Especially when the daily grind leads us to focus on our personal needs, problems and goals.

So, I want to take this opportunity to put in writing all my gratitude to them, simply saying: "Grazie per il vostro supporto ed affetto incondizionato. Grazie per tutto quello che avete fatto e continuate a fare ogni giorno per me. Vi voglio bene!".

Padova, January 2013.

### **Abstract**

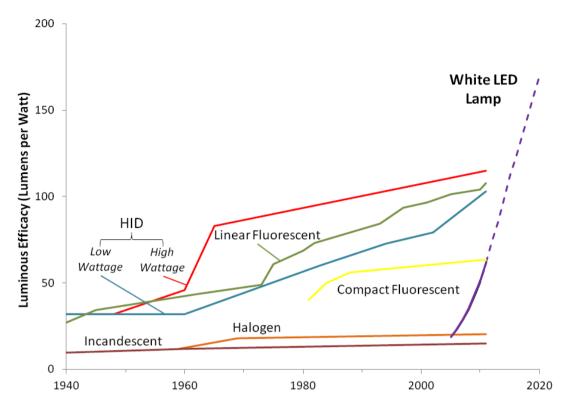

In recent years, high brightness light emitting diodes (HBLEDs) have increasingly attracted the interest of both industrial manufacturers and academic research community. Among the several aspects that make LED technology so attractive, the most appreciated characteristics are related to their robustness, high efficiency, small size, easy dimming capability, long lifetime, very short switch-on/switch-off times and mercury free manufacturing.

Even if all such qualities would seem to give to solid state lighting a clear advantage over all the other kinds of competing technologies, the issues deriving from the need of LED technology improvement, on one hand, and of the development of suitable electronic ballasts to properly drive such solid state light sources, on the other, have so far hindered the expected practical applications.

The latter problem, in particular, is nowadays considered the main bottleneck in view of a widespread diffusion of solid state technology in the general lighting market, as a suitable replacement of the still dominant solutions, namely halogen and fluorescent lamps.

In fact, if it is true that some aspects of the devices' technology (e.g. temperature dependent performance, light quality, efficiency droop, high price per lumen, etc...) still need further improvements, it is now generally recognized that one of the key requirements, for a large scale spread of solid state lighting, is the optimization of the driver.

In particular, the most important specifications for a LED lamp ballast are: high reliability and efficiency, high power factor, output current regulation, dimming capability, low cost and volume minimization (especially in domestic general lighting applications). From this standpoint, the main goal is, therefore, to find out simple switched mode power converter topologies, characterized by reduced component count and low current/voltage stresses, that avoid the use of short lifetime devices like electrolytic capacitors. Moreover, if compactness is a major issue, also soft switching capability becomes mandatory, in order

to enable volume minimization of the reactive components by increasing the switching frequency in the range of the hundreds of kHz without significantly affecting converter's efficiency.

It is worth mentioning that, in order to optimize HBLED operation, also other matters, like the lamp thermal management concern, should be properly addressed in order to minimize the stress suffered by the light emitting devices and, consequently, the deterioration of the light quality and of the expected lamp lifetime. However, being this work focused on the issues related to the research of innovative driving solutions, the aforementioned thermal management problems, as also all the topics related to the improvement of solid state devices' technology, will be left aside.

The main goal of the work presented in this thesis is, indeed, to find out, analyze and optimize new suitable topologies, capable of matching the previously described specifications and also of successfully facing the many challenges dictated by the future of general lighting.

First of all, a general overview of solid state lighting features, of the state of the art of lighting market and of the main LED driving issues will be provided.

After this first introduction, the offline driving concern will be extensively discussed and different ways of approaching the problem, depending on the specific application considered, will be described.

The first kind of approach investigated is based on the use of a simple structure relying on a single power conversion stage, capable of concurrently ensuring: compliance with the standards limiting the input current harmonics, regulation of the load current and also galvanic isolation. The constraints deriving from the need to fulfil the EN 61000-3-2 harmonics standard requirements, when using such kind of solution for low power (<15W) LED driving purposes, will be extensively discussed.

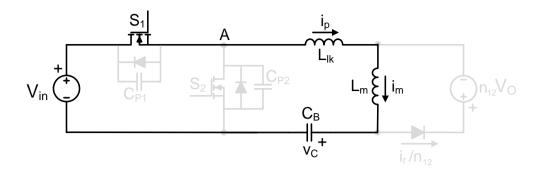

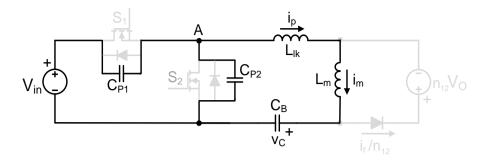

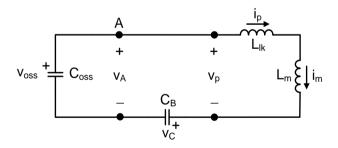

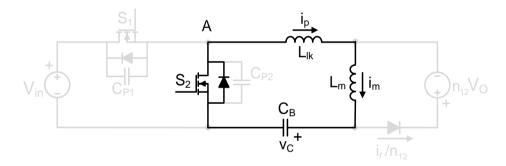

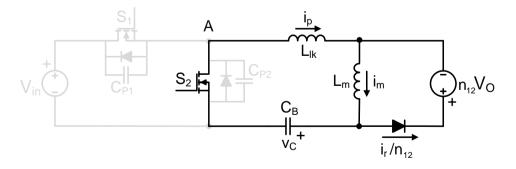

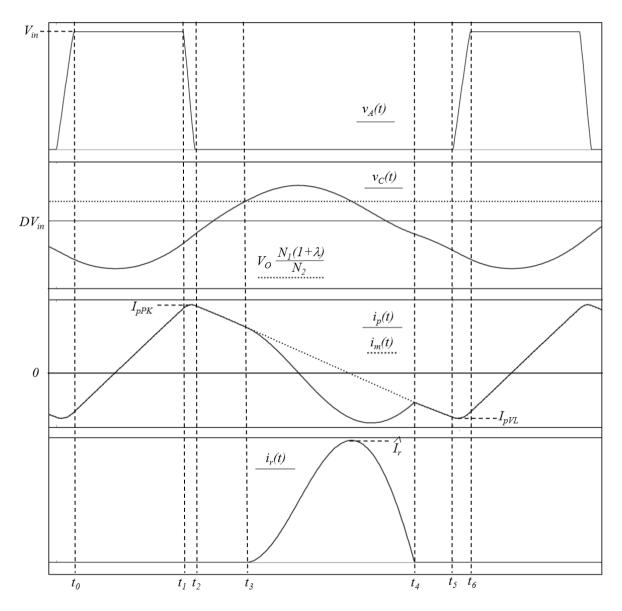

A low cost, low component count, high switching frequency converter, based on the asymmetrical half bridge flyback topology, has been studied, developed and optimized. The simplicity and high compactness, characterizing this solution, make it a very good option for CFL and bulb replacement applications, in which volume minimization is mandatory in order to reach the goal of placing the whole driving circuitry in the standard E27 sockets. The analysis performed will be presented, together with the design procedure, the simulation outcomes and the different control and optimization techniques that were studied, implemented and tested on the converter's laboratory prototype.

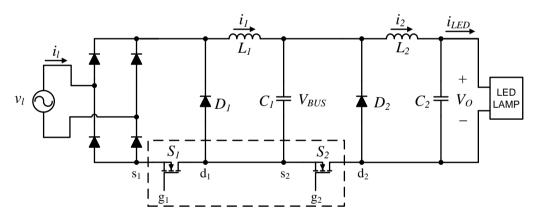

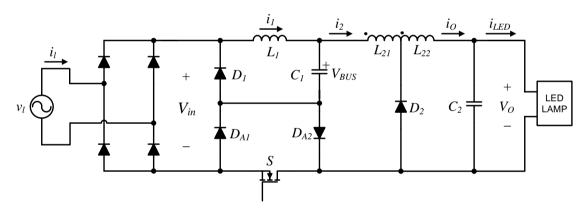

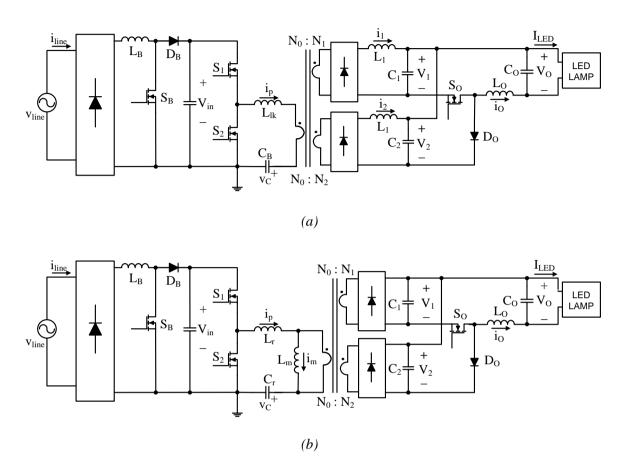

Another interesting approach, that will be considered, is based on the use of integrated topologies in which two different power conversion stages are merged by sharing the same power switch and control circuitry.

In the resulting converter, power factor correction and LED current regulation are thus performed by two combined semi-stages in which both the input power and the output current have to be managed by the same shared switch. Compared with a conventional two-stages configuration, lower circuit complexity and cost, reduced component count and higher compactness can be achieved through integration, at cost of increased stress levels on the power switch and of losing a degree of freedom in converter design. Galvanic isolation can be provided or not depending on the topologies selected for integration. If non-isolated topologies are considered for both semi-stages, the user safety has to be guaranteed by assuring mechanical isolation throughout the LED lamp case.

The issue, deriving from the need of smoothing the pulsating power absorbed from the line while avoiding the use of short lifetime electrolytic capacitors, will be addressed. A set of integrated topologies, used as HBLED lamp power supplies, will be investigated and a generalized analysis will be presented. Their input line voltage ripple attenuation capability will be examined and a general design procedure will be described.

Moreover, a novel integrated solution, based on the use of a double buck converter, for an about 15W rated down-lighting application will be presented. The analysis performed, together with converter design and power factor correction concerns will be carefully discussed and the main outcomes of the tests performed at simulation level will be provided.

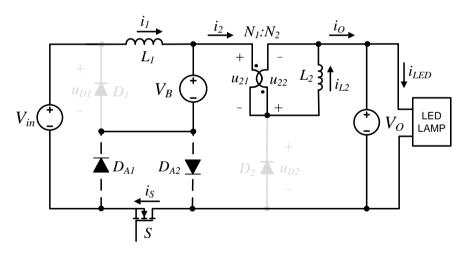

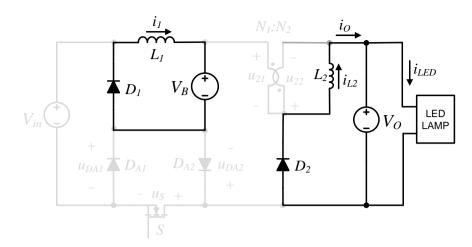

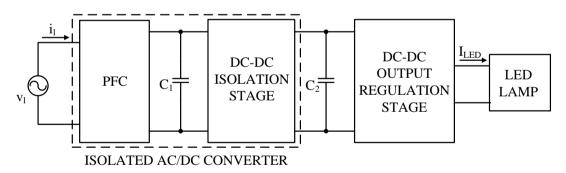

The last kind of approach to be discussed is based on a multi-stage structure that results to be a suitable option for medium power applications, like street lighting, in which compactness is not a major concern.

By adopting such kind of solution it is, indeed, possible to optimize converter's behavior both on line and on load side, thereby guaranteeing both an effective power factor correction at the input and proper current regulation and dimming capability at the output. Galvanic isolation can be provided either by the input or the output stage, resulting in a standard two stage configuration, or by an additional intermediate isolated DC-DC stage

(operating in open loop with a constant input/output voltage conversion ratio) that namely turns the AC/DC converter topology into a three stage configuration. The efficiency issue, deriving from the need of multiple energy processing along the path between the utility grid and the LED load, can be effectively addressed thanks to the high flexibility

guaranteed by this structure that, relaxing the design constraint, allows to easily optimize each stage.

A 150W nominal power rated ballast for street solid state lighting applications, based on the latter (three stage) topology, has been investigated. The analysis performed, the design procedure and the simulations outcomes will be carefully described, as well as the experimental results of the tests made on the implemented laboratory prototype.

#### **Abstract**

Negli ultimi anni i dispositivi LED di potenza ad elevata luminosità (HBLED) hanno attirato in misura sempre crescente l'interesse della comunità scientifica, sia all'interno del mondo accademico che di quello industriale. Tra le varie caratteristiche, che rendono questo tipo di tecnologia interessante, le qualità più apprezzate sono certamente: la robustezza, l'elevata efficienza, le piccole dimensioni, la facilità di modulazione dell'intensità luminosa, il lungo tempo di vita, l'estrema rapidità di accensione e spegnimento e l'assenza di mercurio.

Nonostante tutti questi aspetti sembrino dare alla tecnologia a stato solido un netto vantaggio rispetto alle tecnologie concorrenti, l'utilizzo dei LED di potenza nel campo dell'illuminazione rimane a tutt'oggi abbastanza limitato. La necessità di ulteriori progressi nella tecnologia dei dispositivi, da un lato, e dello sviluppo di soluzioni in grado di garantirne il corretto ed efficiente pilotaggio, dall'altro, ne hanno, infatti, fino ad ora frenato la diffusione rispetto alle attese.

Quest'ultimo aspetto, in particolare, è al giorno d'oggi considerata il vero "collo di bottiglia" in vista dell'impiego su larga scala della tecnologia a stato solido, in sostituzione delle soluzioni, tutt'ora dominanti nel mercato dell'illuminazione, basate sull'utilizzo di lampade alogene e a fluorescenza.

Se, da un lato, infatti, è vero che alcuni aspetti della tecnologia dei dispositivi (e.g. variabilità delle prestazioni con la temperatura, qualità della luce, calo dell'efficienza luminosa con l'aumentare della corrente, elevato costo per lumen, ecc...) necessitano di essere ulteriormente perfezionati, dall'altro è ormai universalmente riconosciuto che l'elemento chiave per l'ampia diffusione dell'illuminazione a stato solido è proprio l'ottimizzazione dello stadio di alimentazione.

In particolare, le specifiche più importati che un ballast per lampade a LED è tenuto a soddisfare sono: elevata affidabilità ed efficienza, elevato fattore di potenza, capacità di regolazione della corrente di uscita e di modulazione del flusso luminoso, basso costo e

minimo ingombro (soprattutto nell'illuminazione domestica). L'obiettivo principale è, quindi, riuscire ad ideare soluzioni basate sull'utilizzo di topologie semplici, caratterizzate da ridotto numero di componenti e limitati livelli di stress di corrente e tensione, che non prevedano l'impiego di componenti con breve tempo di vita come i condensatori elettrolitici. Inoltre, nelle applicazioni in cui la compattezza è considerata uno degli aspetti di maggior rilievo, anche la capacità di operare in soft-switching diviene una specifica indispensabile. Ciò è infatti necessario al fine di permettere la minimizzazione del volume delle componenti reattive, tramite l'aumento della frequenza di commutazione nel range delle centinaia di kHz, senza compromettere l'efficienza del convertitore.

Per completezza, vale la pena di ricordare che, per ottimizzare il funzionamento dei LED ad elevata luminosità, andrebbero presi in considerazione anche altri aspetti, come ad esempio le problematiche legate alla gestione del calore dissipato dalla lampada, importanti al fine di limitare gli stress termici subiti dai dispositivi e, di conseguenza, migliorare la qualità della luce emessa e massimizzare il tempo di vita della lampada.

Tuttavia, essendo il lavoro presentato in questa tesi centrato sulle questioni relative allo stadio di alimentazione, i suddetti problemi di gestione termica, come anche gli aspetti relativi allo sviluppo della tecnologia dei dispositivi non verranno esaminati.

L'obiettivo principale del lavoro che verrà descritto nel corso dei prossimi capitoli, è, infatti, la ricerca di soluzioni innovative per il pilotaggio da rete elettrica di lampade basate su tecnologia a stato solido. Verranno pertanto approfonditamente trattate le tematiche relative ad analisi, ottimizzazione e sviluppo di topologie che siano in grado di soddisfare i requisiti precedentemente enunciati e di affrontare con successo le sfide proposte dalla continua evoluzione dello scenario del "general lighting".

Per prima cosa, sarà fornita una visione di insieme riguardante lo stato dell'arte del mercato dell'illuminazione, le caratteristiche dei dispositivi di illuminazione a stato solido ed i principali aspetti relativi al loro pilotaggio.

Dopo questa prima sezione introduttiva, la tematica relativa all'alimentazione da rete elettrica di tali dispositivi verrà approfonditamente discussa. Differenti modi di approcciare il problema, a seconda della specifica applicazione considerata, verranno discussi.

Il primo tipo di approccio che verrà esaminato si basa sull'uso di una semplice struttura, formata da un singolo stadio di conversione di potenza. Essa è in grado di fornire al contempo il rispetto degli standard che limitano il contenuto armonico della corrente di ingresso, l'isolamento galvanico e la regolazione della corrente e dell'intensità luminosa in uscita.

I vincoli, dettati dall'esigenza di garantire il rispetto della normativa EN 61000-3-2, in applicazioni di bassa potenza (<15W) prive di uno stadio dedicato alla correzione del fattore di potenza, verranno approfonditamente trattati.

Saranno, poi, illustrati i risultati dello studio, sviluppo ed ottimizzazione di un convertitore a singolo stadio, operante ad elevata frequenza di commutazione, basato sulla topologia flyback a mezzo ponte asimmetrico. La semplicità, il ridotto numero di componenti ed il basso costo, che caratterizzano tale tipo di soluzione, la rendono adatta all'alimentazione di lampade per il settore residenziale, in cui la compattezza dello stadio di alimentazione è di fondamentale importanza al fine di consentirne l'alloggiamento nei classici socket E27. L'analisi effettuata, la procedura di progetto ed risultati ottenuti in simulazione ed a livello sperimentale durante lo studio di tale topologia verranno accuratamente descritti e discussi.

Un altro interessante tipo di approccio che verrà considerato si basa sull'utilizzo di topologie integrate, nelle quali due diversi stadi di conversione vengono uniti tramite la condivisione dello stesso interruttore di potenza e della relativa circuiteria di comando.

Nel convertitore che ne risulta, la correzione del fattore di potenza e la regolazione della corrente nei LED saranno dunque garantite dalla combinazione dei due semi-stadi, il cui interruttore comune dovrà essere in grado di gestire sia la potenza di ingresso che la corrente di uscita.

Rispetto alla configurazione a due stadi convenzionale, la soluzione ottenuta tramite l'integrazione consente una minore complessità circuitale, un ridotto numero di componenti e, di conseguenza, una maggiore compattezza ed un minor costo. Tutto ciò viene guadagnato a scapito di un maggiore livello di stress nei componenti e della perdita di un grado di libertà nel progetto del convertitore. L'isolamento galvanico può essere garantito o meno a seconda del tipo di topologie che vengono selezionate per l'integrazione. Se la scelta ricade su topologie non isolate, la sicurezza dell'utente andrà comunque garantita isolando meccanicamente l'involucro della lampada.

I problemi legati alla necessità di smorzare la componente alternata della potenza assorbita dalla rete, evitando al contempo l'utilizzo di componenti con basso tempo di vita, come i condensatori elettrolitici, verranno discussi. A tal proposito si studieranno le caratteristiche di un insieme di topologie integrate, al fine di fornirne un'analisi ed una procedura di design generalizzate. Se ne esaminerà, inoltre, la capacità di attenuare la componente ondulatoria della tensione di ingresso che viene trasferita al carico, dove si traduce in un'oscillazione della corrente di alimentazione fornita ai LED.

Verrà proposta, poi, una soluzione basata su una topologia derivante dall'integrazione di due convertitori di tipo step-down (abbassatori di tensione), per applicazioni di "downlighting", dimensionata per una potenza di circa 15W. Se ne discuteranno, in particolare, i dettagli di maggiore interesse relativi all'analisi effettuata, alla procedura di progetto ed ai risultati dei test effettuati in ambiente di simulazione.

L'ultimo tipo di approccio considerato prevede, infine, l'utilizzo di una topologia multistadio, ritenuta una scelta appropriata soprattutto per applicazioni lighting di potenza elevata (>60W), come l'illuminazione stradale, in cui la compattezza dell'alimentatore non è ritenuta un aspetto di primaria importanza.

Tramite questo tipo di soluzione è, infatti, possibile ottimizzare le prestazioni del convertitore sia dal lato della rete che dal lato del carico. Si riescono a garantire, in tal modo, un'efficace correzione del fattore di potenza, un adeguato controllo della corrente di uscita ed un'appropriata modulazione del flusso luminoso emesso dalla lampada.

L'isolamento galvanico può essere fornito dallo stadio di ingresso o da quello di uscita o da un aggiuntivo stadio DC-DC intermedio, operante a catena aperta con rapporto di conversione di tensione costante. In quest'ultimo caso la struttura del convertitore, si trasforma, dalla classica configurazione a due stadi, in una topologia a triplo stadio.

Il problema che nasce dalla necessità di assicurare un elevato livello di efficienza del sistema, nonostante l'interposizione di ripetuti stadi di conversione dell'energia tra la rete ed il carico a LED, può essere efficacemente risolto grazie alla flessibilità che caratterizza tale tipo di struttura. L'aumento del numero dei gradi di libertà in fase progettuale permette, infatti, di ottimizzare con semplicità ogni singolo stadio.

Per comprovare limiti e potenzialità di tale tipo di approccio, si è deciso di studiare un ballast (dimensionato per una potenza nominale di 150W) basato sulla topologia a triplo stadio precedentemente menzionata, per applicazioni nell'ambito dell'illuminazione stradale. L'analisi condotta, la procedura di progetto ed i risultati delle simulazioni effettuate verranno discussi nel dettaglio, così come i risultati sperimentali dei test di laboratorio effettuati sul prototipo costruito.

# **Contents**

| ABSTRACT                                                        | 3  |

|-----------------------------------------------------------------|----|

| CHAPTER 1:SOLID STATE LIGHTING                                  |    |

| 1.1 Introduction                                                | 15 |

| 1.2 Lighting                                                    | 19 |

| 1.2.1 The Long Debate on the Nature of Light                    | 19 |

| 1.2.2 The Electromagnetic Spectrum and Visible Light Perception | 21 |

| 1.2.3 The "Quality" of Light                                    | 26 |

| 1.3 The Lighting Market                                         | 29 |

| 1.3.1 Lighting Applications                                     | 29 |

| 1.3.2 State of Art of Lighting Market                           | 30 |

| 1.4 Solid State Lighting                                        | 37 |

| 1.4.1 The History of Lighting - a Brief Review                  | 37 |

| 1.4.2 LEDs: Operating Principles an White Light                 | 40 |

| 1.4.3 Solid State Lighting: Issues and Benefits                 | 44 |

| 1.5 Solid State Lighting Driving                                | 49 |

| 1.5.1 LED Driving Issues                                        | 49 |

| 1.5.2 Offline LED Driving Solutions                             | 54 |

#### CHAPTER 2: THE SINGLE STAGE APPROACH

| 2.1   | Introduction                                                 | 59  |

|-------|--------------------------------------------------------------|-----|

| 2.    | 1.1 Line Side Harmonic Injection                             | 61  |

| 2.2   | The AHB-Flyback Converter                                    | 67  |

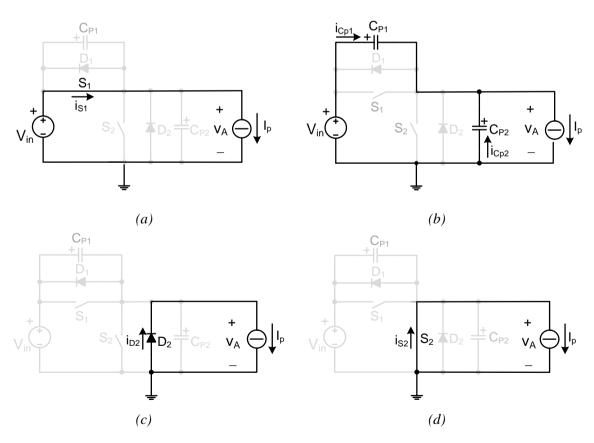

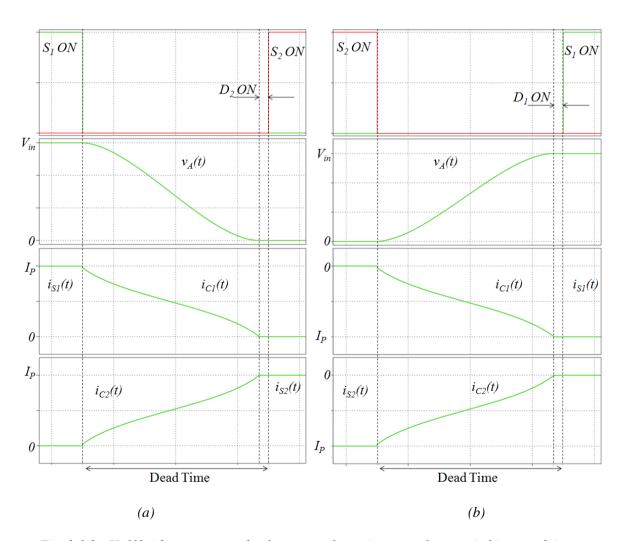

| 2.3   | The Soft Switching Issue                                     | 76  |

| 2.4   | Main Converter Design Issues                                 | 83  |

| 2.5   | AHB-Flyback Converter Control.                               | 90  |

| 2.6   | Optimization Techniques                                      | 100 |

| 2.    | 6.1 Switching Frequency Modulation                           | 102 |

| 2.    | 6.2 Magnetizing Inductance Modulation                        | 104 |

| 2.7   | Experimental Results                                         | 108 |

| СНАРТ | TER 3: THE DOUBLE INTEGRATED STAGE APPROACH                  |     |

| 3.1   | Introduction                                                 | 117 |

| 3.    | 1.1 The Integration Technique                                | 118 |

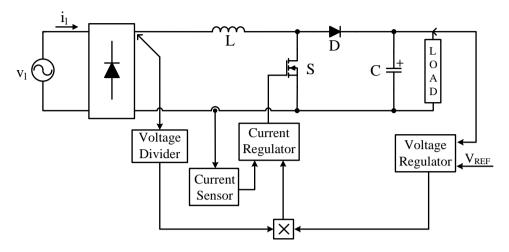

| 3.2   | Input Stage: the PFC Issue                                   | 121 |

| 3.    | 2.1 Ideal Power Factor Correctors                            | 124 |

| 3.    | 2.2 Quasi Power Factor Correctors                            | 126 |

| 3.3   | Output Stage: the Load Current Ripple Reduction Issue        | 129 |

| 3.4   | Integrated Topologies for Solid State Lighting Applications: |     |

|       | a General Design Approach                                    | 133 |

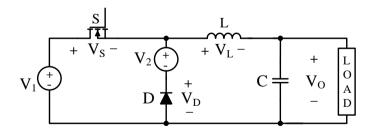

| 3.5   | The Integrated Double Buck Offline Converter                 | 141 |

| 3.6    | Performance of the Input and Output Semi-Stages | 148 |

|--------|-------------------------------------------------|-----|

| 3.7    | Integrated Double Buck Converter Design         | 155 |

| 3.8    | Converter Simulation Outcomes                   | 163 |

| СНАРТ  | TER 4: THE MULTIPLE STAGE APPROACH              |     |

| 4.1    | Introduction                                    | 167 |

| 4.     | 1.1 Multi-Stage Power Supply Features           | 168 |

| 4.2    | Half Bridge Converter                           | 173 |

| 4.3    | LLC Resonant Converter                          | 179 |

| 4.4    | The Soft Switching Issue                        | 185 |

| 4.5    | Multi-Stage Power Supply Design                 | 194 |

| 4.6    | Main Converter Implementation Issues            | 202 |

| 4.7    | Simulation Outcomes and Experimental Results    | 208 |

| CONCI  | LUSIONS                                         | 217 |

| BIBLIC | OGRAPHY                                         | 221 |

# Chapter 1 Solid State Lighting

#### 1.1. Introduction

In the last decades, many issues related to global warming and to the increasing economic and environmental cost of the energy have started gaining a center stage in the public debate.

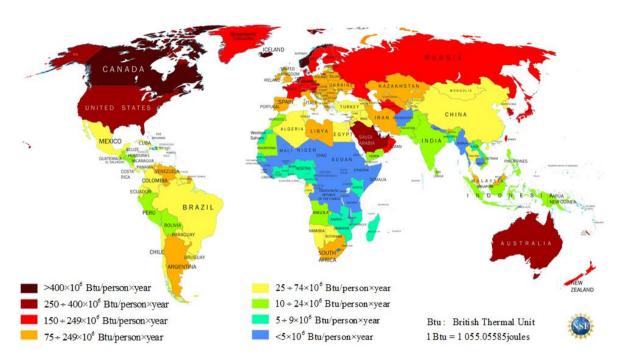

Every year, indeed, a huge amount of energy is used to support human activities worldwide, as can be noticed by observing the reference picture shown in Fig. 1.1.1. The obvious consequences are the continuous impoverishment of natural resources and the massive emission of  $CO_2$  and other gasses, that actually increase pollution level and favor the greenhouse effect.

Moreover, in order to fully understand the significance of such problem, another fundamental aspect should be taken into account, that is the impressive growth rate of the so-called developing countries.

Fig. 1.1.1 – Average annual energy consumption per capita by country (year 2009). Source: United States Central Intelligence Agency.

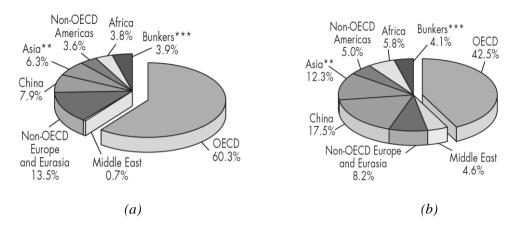

As a suitable reference of this concern, can be considered the data reported Fig. 1.1.2 (a) and (b), describing the contributions of the different world regions to the global energy consumption, referred to the years 1973 and 2010 ([1], [2]).

As it can be observed, in the last forty years, the non-OECD member countries (see the notes in Fig. 1.1.2 for details) essentially reversed the course, rising from about 40% to about 60% of the overall energy consumptions.

This clearly forces a substantial rethinking of the way in which energy is generated and used in order to meet the world growing demand for energy.

In an effort to address such problem, concerns like green power, sustainability, and energy saving have become therefore a matter of priority for the international scientific community, with the aim of optimizing the use of available resources and protect the environment.

From this perspective, the main target is to relieve the dependence on fossil fuels, through a larger use of renewable resources, while improving, at the same time, the efficiency of the daily used electrical equipments, thus reducing global consumptions.

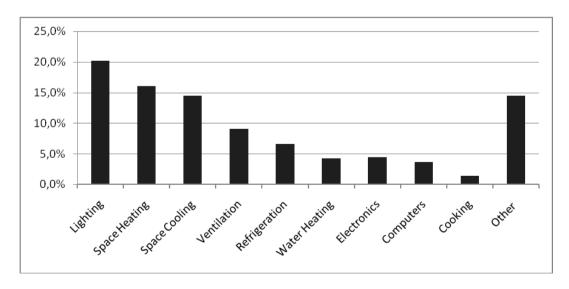

In particular, as concerns the latter issue, it may be worth to consider, as a reference, the distribution of the electrical power demand by application, concerning the U.S. commercial buildings, whose relating data, reported in [3] has been summarized in Fig. 1.1.3.

Fig. 1.1.2 – World total energy consumption, by region, in the years (a)1973 and (b) 2010.

Source: International Energy Agency: "Key World Energy statistics", released in 2012 Notes:

- the region "Asia" excludes the data relative to the People's Republic of China and Hong Kong;

- the term "Bunkers" includes international aviation and international marine bunkers;

- the countries members of the Organization for Economic Co-Operation and Development (OECD) are: Australia, Austria, Belgium, Canada, Chile, the Czech Republic, Denmark, Estonia, Finland, France, Germany, Greece, Hungary, Iceland, Ireland, Israel, Italy, Japan, Korea, Luxembourg, Mexico, the Netherlands, New Zealand, Norway, Poland, Portugal, the Slovak Republic, Slovenia, Spain, Sweden, Switzerland, Turkey, the United Kingdom, the United States (Estonia and Slovenia from 1990).

As it can be observed, about 20% of the electrical energy consumed, is transformed into artificial light. It can be therefore consequently inferred how a strong innovation effort in this field, aimed at improving light sources efficiency, would actually produce substantial benefits in terms of energy saving and reduction of CO<sub>2</sub> emissions.

Fig. 1.1.3 – Distribution of electrical energy demand by application in U.S. commercial buildings. Source: U. S. Department of Energy: "Building energy data book" 2011.

As a matter of facts, given the relevance of lighting in the worldwide energetic scenario, it is clearly strategic to move towards the use of more efficient light sources. For this reason the European Union, together with many other countries, in 2009 decided to start the phase-out of incandescent light bulbs [4].

Such light sources, invented in the late nineteenth century, are indeed capable of converting only less than 5% of the supplied energy into visible light, while dissipating the whole remaining amount of energy into heat.

From this perspective, nowadays, the most promising technology is represented by solid state lighting (SSL) in which energy is directly converted into light by manipulating the electrons in a solid, at room temperature. Unlike the case of conventional lighting, namely based on incandescent and fluorescent light sources, in which light is instead generated through an indirect process (electricity is used at first to produce heat and gas discharges) that actually limits conversion efficiency.

The beneficial effects deriving from the replacement of conventional lighting with solid state lighting sources, in terms of energy saving, will be presented in paragraph 1.4.3.

However, besides the higher conversion efficiency, with respect to the other light sources, there are many other advantages actually characterizing the solid state lighting technology. In particular, among the others it is worth to mention the long lifetime (about 50000 hours), the robustness to shocks and vibrations, the very fast turn-on and turn-off speed, the dimming capability, the very low radiation in the infra-red spectrum, the highly directional light emission, the compactness, etc...

However, despite their many widely recognized positive characteristics, the widespread of LED lamps currently still find it hard to occur.

As an example, it can be considered that, according to the lighting market characterization, released in 2012 by the U.S. Department of Energy, [5]., over the last decade the total number of LED lamps, installed in the U.S.A., has grown from 1.6 million (in 2001) to 67 million lamps (in 2010).

Although this corresponds to an increase equal to 4000%, the actual datum is that, in 2010, LED lamps still represented approximately only 1% of the whole installed lamps.

In order to support a large scale spread of solid state lighting, it is fundamentally important to improve the overall reliability and efficiency of such light sources. Actually the main way to reduce their cost per lumen and compensate for their high initial price, as it that will be better explained in the following paragraphs.

#### 1.2. Lighting

#### 1.2.1. The Long Debate on the Nature of Light

A long lasting debate has permeated the study of light nature along the past centuries, mainly due to the conflict between two main different competing models.

Two contrasting early theories, indeed, were developed since the late seventeenth century, aimed to physical modeling light nature on one hand as a collection of fast-moving particles and on the other hand as a propagating wave.

The first detailed wave theory of light was formally formulated in 1690 in the "Traité de la Lumiere" (i.e. Treatise on Light) by the Duch astronomer Christiaan Huygens. He was the first to describe light as a composition of waves perpendicularly vibrating with respect to light direction, being also able to derive the laws of reflection and refraction.

Almost in the same years, however, another brilliant scientist was carrying out his research activity on light properties, sir Isaac Newton. Differently from Huygens, to explain the phenomena he observed during his studies, Newton theorized that light is composed by a stream of particles ("Optiks", 1704). In order to meet the law of refraction, he made the hypothesis that transparent objects exert an attractive force on such corpuscles, consequently increasing light speed with respect to light transfer in vacuum.

Newton also asserted that particles of different colors have slight mass differences resulting in different speeds in transparent media and therefore in different refraction angles.

Because of the great authority Isaac Newton had in the scientific community, his corpuscular model resisted until the early nineteenth century when the evidences of the wave nature of light became overwhelming.

In particular, Thomas Young experiments on light interference phenomena (1803), then mathematically formalized by Augustin Fresnel in 1815, that significantly bolstered Huygens theory.

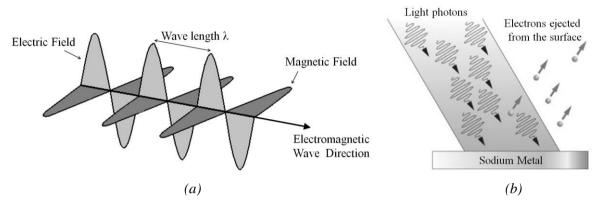

However, notwithstanding the many theoretical and experimental proofs, the actual behavior of the light wave remained almost unknown until 1860, when J.C. Maxwell was actually able to described the electromagnetic radiation as a wave of coupled electric and magnetic fields propagating through the space.

He also proposed a careful mathematical formulation of his physical inferences. In its modern form it is expressed through four fundamental equations, that relate the electric and magnetic fields to their source and still represent the basis of the classical electromagnetism.

Given the highly convincing theoretical and experimental evidences supporting the wave nature of light, at the end of the nineteenth century the conflict between the wave and corpuscular nature of light seemed to have been definitively resolved.

Together with the mechanics and thermodynamics theory of Newton, Maxwell formulation of electromagnetism was adopted as a foundational element of physics.

However in the very early twentieth century, new studies about the blackbody radiation, along with new experimental methods improving the investigation at atomic level, opened the way to quantum physic and led to a substantial departure from classical theories.

In 1900 Planck proposed the idea that the electromagnetic radiation can be emitted and absorbed only in finite packets, called "quanta" whose energy is proportional to the radiation frequency:

$$E = h \cdot f \tag{1.2.1}$$

according to a constant of proportionality ( $h = 6.626 \cdot 10^{-34} js$ ) that was experimentally derived and it is worldwide known with the name of Planck's constant.

This theory substantially revolutionized physics, however Planck did not provide a physical basis to its proposal, offering essentially only a mathematical construct, aimed at meeting the experimental observations he made on the black body spectrum.

A physical interpretation of such theory was first provided in 1905 by Albert Einstein, that, on the basis of thermodynamic arguments applied to a radiation field obeying to Planck's radiation law, inferred the granular nature of the radiation.

He proposed, in particular, a solution based on the idea that light has both wave and particles characteristic, suggesting that light is composed of energy "quanta", later called "photon", according to the term coined by G. N. Lewis. Each photon has an energy depending on the solely radiation frequency, being independent from light intensity.

Einstein supported his idea through a detailed analysis of the photoelectric effect, an already known process in which electrons are ejected from a metallic surface illuminated by light.

By means of careful experimental measurements, he finally showed that the onset of such process is related to the only frequency of the light and the makeup of the surface, concluding that a only photons with a sufficient amount of energy can induce electron emission.

Fig. 1.2.1 - (a) Maxwell description of the electromagnetic radiation, (b) photoelectric effect.

The basic principles of Einstein theory, claiming the dual nature of electromagnetic radiation, are still universally accepted by modern physic. Light diffracts, reflects off of material surfaces, refracts entering into a material with a different density and can be absorbed by the material. It is, therefore, supposed to both propagate from a place to another as an electromagnetic wave and to interact with matter via absorption and emission as a particle.

#### 1.2.2. The Electromagnetic Spectrum and Visible Light Perception

As previously mentioned, Maxwell research effort, culminated in the formulation of the electromagnetism theory, gave a fundamental contribution to the description of the wave nature of light.

Moreover it is worth to remember that on the basis of Maxwell theory, in 1888 Hertz demonstrated the existence of other electromagnetic waves in addition to those composing visible light. Although characterized by longer wavelengths, such waves resulted, indeed, to be consistent with the properties of light waves, actually demonstrating that light is only a part of a much broader set of phenomena.

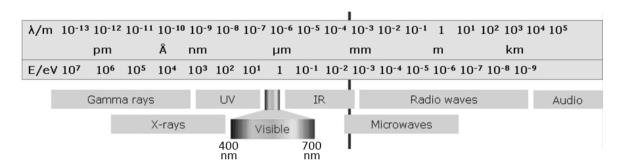

Even if there is no theoretical difference between electromagnetic waves with different wavelengths, the electromagnetic spectrum can be divided into different wavelength intervals. Such portions usually take their names from the way the wave are produced or detected, the applications in which they are used, the scientific development that led to their identification, etc.., as shown in Fig. 1.2.2.

*Fig. 1.2.2 – The electromagnetic spectrum.*

As it can be noticed, the interval of electromagnetic radiation that is detectable by human eyes, usually referred as visible light or white light, or simply light, is effectively only a small part of the spectrum, including the wavelengths approximately ranging between the 400 and the 700nm.

The human eye is provided of two kinds of receptors named rods and cones, either involved in the visual process depending on the light level. The former contribute to scotopic vision in low light condition, being essentially insensitive to colors. The latter, on the other hand, guarantee color sensitivity contributing to the so-called photopic vision in high luminance conditions. There are three different kinds of cones whose peak sensitivity lie in the violet (blue cones), green (green cones) and yellow (red cones) range, respectively.

Color perception is therefore given by the combination of physical, physiologic and psychic activities, involving the characteristics of electromagnetic radiation and of the human eye and brain, actually resulting in a complex subjective process.

Since the human eye is unable to make spectrum analysis of the radiation, electromagnetic radiations characterized by different spectral contents can be perceived in the same way.

As a consequence, a given perceived color can be the effect of light sources emitting a mixtures of different wavelengths, known as the phenomenon of metamerism. From this perspective a fundamental role is played by colorimetry, a science aimed at quantifying and physically describing the colorimetric stimulus that determines human color perception.

In order to provide suitable tools to enable a standard color evaluation and reproduction, proper standard scales and reference quantities have been established by the "Commission International de l'Eclairage" (CIE) and the "Optical Society of America" (OSA).

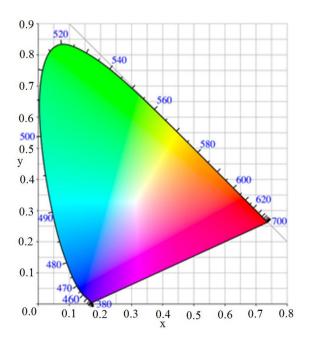

The basic idea is to conceptualize the parameters describing color sensation, the so-called "tristimulus values", related to the stimulation of the human eye cone photoreceptors, as the amount of three primary colors in a tri-chromatic additive color model ([6]).

To eliminate the dependence on the observer, due to its particular eye receptors distribution, a standard colorimetric observer has also been defined.

In the CIE color space, such tristimulus values (usually indicated with the capital letters X, Y and Z) are associated with colors by means of color-matching function, that numerically describe the chromatic response of such standard observer.

As a result, a complete plot of the whole visible color set, should be three dimensional.

However, in order to derive a practical reference to specify the different colors, two different concepts, namely brightness and chromaticity, can be distinguished.

The latter, in particular, can be specified by two of the normalized parameters, also called chromaticity coordinates:

$$x = \frac{X}{X + Y + Z} \qquad y = \frac{Y}{X + Y + Z} \qquad z = \frac{Z}{X + Y + Z}$$

(1.2.2)

being the third one linearly dependent from the others according to the relation:

$$x + y + z = 1 \tag{1.2.3}$$

The corresponding CIExy bi dimensional diagram, commonly used to specify the chromaticity of a color is shown in Fig. 1.2.3.

*Fig. 1.2.3 – Chromaticity diagram.*

Moreover, since the CIE XYZ color space was deliberately designed so that the Y parameter was a measure of the brightness, the resulting color space CIE xyY, (specified by the chromaticity parameters x, y and the brightness parameter Y) can be practically used as a reference to exhaustively specify each different color.

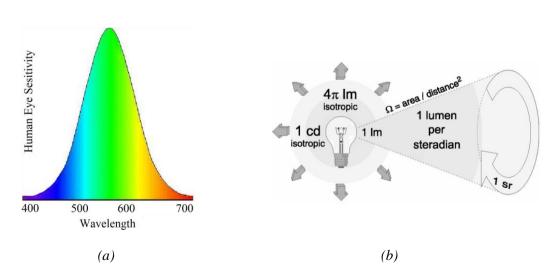

Once briefly summarized the underlying ideas of electromagnetic spectrum and color, it is worth to spend a few words on some basic light measurement parameters, that are widely used to describe light sources [7]. Namely: luminous flux, luminous intensity, illuminance, luminous efficiency and luminous efficacy.

#### Luminous Flux

The luminous flux accounts for the portion of power emitted by a light source that is actually perceived by the human eye and is measured in "lumens" (lm). It is therefore significantly different from the concept of radiant flux, that corresponds, instead, to the measure of the total power of the emitted light, despite human eye sensitivity to the different radiation wavelengths.

The luminous flux can be computed as the integral, over the visible spectrum wavelengths  $(\lambda)$ , of the product between the radiant power  $P(\lambda)$  and the CIE spectral luminosity function  $V(\lambda)$  (Fig. 1.2.4 (a)) scaled by the lumens per watt conversion factor for CIE curve (k=683 lumen/W):

$$\phi = k \cdot \int_{380 \text{nm}}^{730 \text{nm}} P(\lambda) \cdot V(\lambda) \, d\lambda \quad \text{[lumen]}$$

(1.2.4)

Fig. 1.2.4 – (a) Relative eye sensitivity (b) isotropic light source: luminous flux and luminous intensity.

#### Luminous Intensity

Since many sources are not isotropic, the luminous intensity accounts for the amount of luminous flux emitted in a specific direction into a solid angle, called steradian. The SI unit of luminous intensity is the "candela" (cd), which is defined as lumens over steradians (sr). As it can be observed from Fig. 1.2.4 (b), an isotropic light source will emit uniformly in a total volume of  $4\pi$  sr. As a result, in such case a luminous intensity of one candela will correspond to a luminous flux of  $4\pi$  lumens.

#### Illuminance

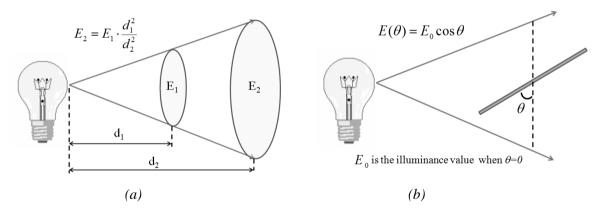

Such parameter is measured in "Lux" and expresses the photometrically corrected power (lumens) falling upon a given unity of surface area (m<sup>2</sup>)

Each luminaire can be considered a point source if the observation distance is at least five time greater than light source diameter. Now, from a point source, light will spread out, so that the illuminated surface will increase (and consequently the illuminance value will decrease) according to the inverse square law (Fig. 1.2.5 (a))

Fig. 1.2.5 – Illuminance decrease according to the (a) inverse square law, (b) cosine law.

Moreover, the illuminance also decrease according to the cosine of the angle of incidence  $(\theta)$ , as shown in Fig. 1.2.5 (b), where  $E_0$  is the illuminance corresponding to a surface normal to the incident light direction.

#### Luminous Efficacy and Efficiency

The luminous efficacy is defined as the ratio between the total luminous flux and the total radiant flux of an emitting source. In the SI, luminous efficacy has units of lumens per watt (lm/W). A related concept is that of luminous efficiency, that is usually used to evaluate the lighting efficiency of an artificial light source and is defined as the luminous flux emitted by a specific light source over the total energy it consumes in a time unit.

#### 1.2.3. The "Quality" of Light

Light plays a fundamental role in people's everyday life. Eyesight is actually considered the most important sense for the human being, since about 80% of information is acquired at visual level.

As a matter of fact darkness typically somehow causes a feeling of fear, consequently increasing our stress level; moreover, the persistence of a low light condition can influence people mood and cause some discomfort.

There are a lot of scientific evidence of the close relationship between lighting and a multitude of biological, physiological and psychological effects, that are relevant for human performance and well being. Light affects our biological clock, however there is a threshold below which light is incapable to correctly regulate human circadian system.

Nowadays people usually spend the most of their time indoor, under artificial lights, in chronobiological darkness conditions, that can cause physical disturbances of various kinds. However, it is fundamental to understand that it is not a matter of quantity, but rather of quality of lighting.

Indeed, if providing a proper light level is clearly a necessary condition to achieve a good enlightenment, it is still not sufficient, since many other characteristics like light uniformity, spectral power, glare, etc... contributes to the actual lighting quality.

So, providing "good" lighting quality is much more than just guaranteeing an appropriate quantity of light. Therefore, it cannot simply expressed in terms of photometric measurements, since light perception is influenced by a number of different physical, physiological and psychological factors.

Moreover, the idea of "good" lighting usually varies depending on the specific place, its setting, its function, the characteristics of the people it is supposed to house, etc...

As a result, provide general criteria suitable for light quality analysis and find out prediction parameters to evaluate it is not a simple concern. However, some qualitative aspects, to be considered when estimating the suitability of lighting conditions, can be easily identified, as discussed also in [8]-[11].

#### Visual Performance

It is determined by the speed and accuracy in performing visual tasks, such as writing, reading, typing, interacting with other people, view image and videos, work with specific objects, etc... Visual performance is improved with increasing luminance, until reaching a

plateau above which any further illuminance increase does not actually produce any practical improvement.

#### Visual Comfort

To realize visually comfortable environments it is actually not a straightforward task, due to the several interrelated factors that can produce visual disturbances. Visual comfort, however, can be provided through a multitude of aspects, such as: a proper lighting distribution and light level, reduced glare and veiling reflections, the absence of excessive shadows and flickering effects, etc..

#### Color Characteristics

Light color characteristics are determined by light source emission spectrum, on one hand, and by the reflectance properties of the objects' surfaces on the other hand.

Light designer action field is clearly mainly aimed at addressing the former aspect, which is usually described by two different parameters, the so-called color temperature and the color rendering index. The first one is defined as the temperature of an ideal black body radiator that radiates light of comparable hue to that of the considered light source.

The second one is, instead, a quantitative measure of the ability of a light source to faithfully reproduce a set of test colors, compared to an ideal reference source of the same color temperature.

#### Psychological Aspects

Luminance can act at psychological level triggering emotions, affecting people's mood, increasing objects attractiveness. Therefore a lighting set-up that does not meet user expectations and does not produce positive feelings can be considered inappropriate, although it provides proper visual properties.

Moreover, lighting conditions can affect on productivity performance through motivation as shown in Fig. 1.2.6. So, lighting installations should be realized so as to allow people to work efficiently, safely and comfortably while trying to improve their productivity exploiting the non-visual aspects of light.

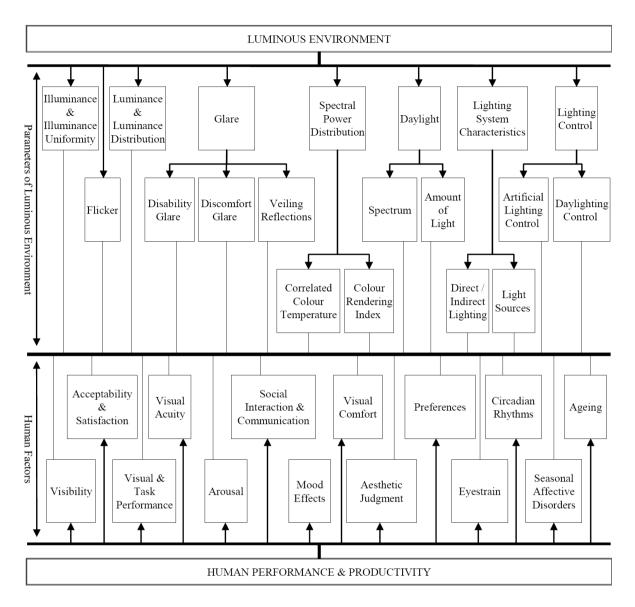

Fig. 1.2.6 – Interaction between human performance and luminous environment.

#### 1.3. The Lighting Market

#### 1.3.1. Lighting Applications

The world of lighting is characterized by a multitude of different kinds of applications, each of which has its peculiar properties and requirements that must be understood, studied and addressed. Only in this way it is, indeed, possible to meet the current market needs, enhance lighting systems and consequently improve people life quality.

As a reference, the most common lighting applications categories, are briefly reviewed here in the following, with the aim of pointing out their peculiar features.

#### Commercial Lighting

Lighting systems for commercial areas are usually aimed at creating a pleasant environment, capable of promoting positive customers feelings encouraging them to shop. In such situation light pays a fundamental role in enhancing product qualities, allowing to easily recognize the value of the brands on sale.

The most common luminaries involved in such kind of application are usually indoor spotlights, which allow the maximum positioning and set-up modification flexibility, and recessed luminaries [12], in order to hide lighting fixture and improve the aesthetics of the light source.

#### Industrial Lighting

Lighting in warehouses and industrial plants can improve safety, create flexible spaces, enhance working quality and productivity.

Due to the peculiar structure of such places, namely very large areas and high ceilings, however, the main required features in this kind of lighting application, are: long lifetime, minimum maintenance needs and high luminous efficiency, with the aim of minimizing costs. It is worth also to note that, in general, in this contest uniform lighting is not required. The typical lighting technique is indeed characterized by the use of a general low illuminance enlightenment, together with supplemental, more intense lighting concentrated in areas of specific interest such as the workstations.

#### Residential Lighting

In residential environments a multitude of different kinds of light sources are usually used, due to the huge variety of multidisciplinary activities that usually take place in such spaces.

A house, indeed, is a place where people can socialize, eat, sleep, play, study, work, relax, indulge in their hobbies, etc... For this reason, specific solutions, to match the requirements of each kind of activity, need to be adopted. As a result, in residential applications, the lighting conditions required in each particular case will be therefore achieved, from time to time, through the combined use of standard bulbs and more technical products.

#### Outdoor lighting

Outdoor lighting systems are intended to improve people safety, guaranteeing the visibility of obstacles and of potential dangerous situations, helping both vehicles and pedestrians and providing an effective contribution to the prevention of micro-criminality.

Common requirements for outdoor lighting typically call for the use of high efficiency and low maintenance cost street lamps. However, the specific needs of some urban elements (squares, monuments, parks, crossroads, etc...) must be obviously taken into account. In such cases the use of particular products like: pathway luminaries, floor-recessed luminaries, outdoor floodlights, etc... is actually recommended.

#### 1.3.2. State of Art of Lighting Market

The launching of new energy programs by the European Community and the U.S. government, together with the release of new international efficiency standards and the advent of new technologies, herald a change in the lighting market in the upcoming years. In order to better understand where the market is headed, it is worth to indentify the main characteristics of the current lighting market. A useful reference in this perspective is provided by the U.S. Department of Energy lighting market characterization report [5], released in January 2012 (DOE -LMC 2012), that illustrates the state of the art in this regard.

Such report, indeed, actually provides a snapshot of U.S. present situation making the inventory of all "lighting installed in the U.S. in stationary applications" in 2010. To this end, the market data have been split into four different sectors related to: residential, commercial, industrial buildings, and outdoor.

As it can be noticed, by observing the outcomes summarized in Table 1.3.1, about half of the electricity used for lighting is consumed in commercial buildings, while being the residential sector the second largest lighting energy consumer.

|             | Lamps         | Average Daily Operating Hours | Wattage per<br>Lamp | Annual Electricity Use (TWh) |

|-------------|---------------|-------------------------------|---------------------|------------------------------|

| Residential | 5,811,769,000 | 1.8                           | 46                  | 175                          |

| Commercial  | 2,069,306,000 | 11.2                          | 42                  | 349                          |

| Industrial  | 144,251,000   | 13.0                          | 75                  | 58                           |

| Outdoor     | 178,374,000   | 11.7                          | 151                 | 118                          |

| Total       | 8,203,700,000 | 4.7                           | 48                  | 700                          |

Table 1.3.1– Summary of U.S. lighting market characteristics in 2010. Source: DOE - LMC 2012.

It is worth to observe that the latter datum is given by the combination of the large base of installed lamps and their typically low efficiency, being incandescent lamp still the most broadly used in residential sector.

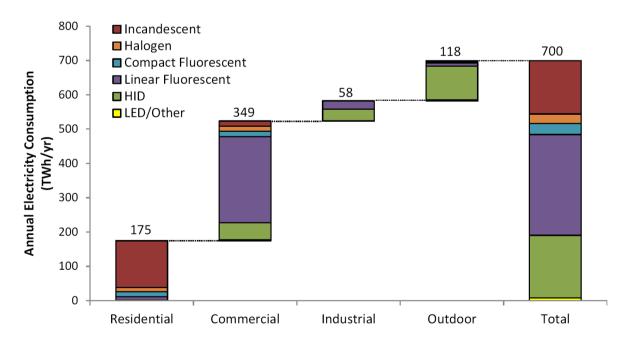

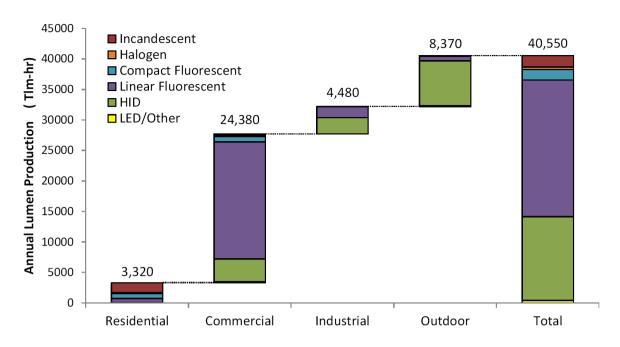

As a reference of the U.S. electricity consumption and lumen production by market segment and lamp type, the data reported Fig. 1.3.1 and Fig. 1.3.2 can be considered, respectively. Light sources have been grouped in six different lamp technology categories, that is: incandescent, halogen, compact fluorescent, linear fluorescent, high intensity discharge, and solid state/other.

Fig. 1.3.1 – U.S. lighting electricity consumption by sector and lamp type in 2010. Source: DOE - LMC 2012.

Fig. 1.3.2 – U.S. lumen production by sector and lamp type in 2010. Source: DOE - LMC 2012.

As it can be noticed, the relation between the energy consumed and the produced lumen is clearly unfavorable for incandescent lighting, while being highly beneficial in the case of efficient light sources, like HID, linear fluorescent and compact fluorescent lamps.

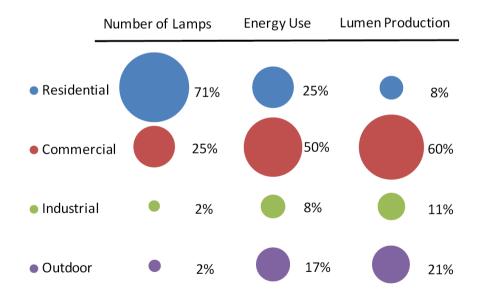

Another interesting reference is provided in Fig. 1.3.3, which shows the percentage of market share of each sector according to three different perspectives: the number of installed lamps, the energy consumption and the lumen production.

Fig. 1.3.3 – U.S. Lighting Lamp Inventory, Electricity Consumption and Lumen Production in 2010. Source: DOE - LMC 2012.

#### **CHAPTER 1: SOLID STATE LIGHTING**

As can be seen, the lighting of commercial building clearly turns out to be the main sector as concerns energy use and lumen production, while being the most of lamps actually installed in the residential environment, because of the many multidisciplinary applications characterizing such segment.

Further details concerning the current U.S. lighting market can be derived also from the analysis, of Table 1.3.2.

|                              | Residential | Commercial | Industrial | Outdoor | All Sectors |

|------------------------------|-------------|------------|------------|---------|-------------|

| Incandescent                 | 62.0%       | 3.7%       | 0.3%       | 10.0%   | 45.1%       |

| General Service - A-type     | 34.9%       | 2.1%       | 0.3%       |         | 25.3%       |

| General Service - Decorative | 16.9%       |            |            |         | 11.9%       |

| Reflector                    | 7.5%        | 0.9%       | 0.0%       |         | 5.5%        |

| Miscellaneous                | 2.8%        | 0.7%       |            | 10.0%   | 2.4%        |

| Halogen                      | 4.4%        | 2.3%       | 0.0%       | 2.3%    | 3.8%        |

| General Service              | 0.5%        | 0.0%       | 0.0%       |         | 0.3%        |

| Reflector                    | 2.9%        | 0.9%       | 0.0%       |         | 2.3%        |

| Low Voltage Display          | 0.3%        | 1.2%       |            |         | 0.5%        |

| Miscellaneous                | 0.7%        | 0.1%       | 0.0%       | 2.3%    | 0.6%        |

| Compact Fluorescent          | 22.8%       | 10.4%      | 0.3%       | 6.8%    | 18.9%       |

| General Service - Screw      | 19.3%       | 2.0%       | 0.1%       |         | 14.2%       |

| General Service - Pin        | 0.1%        | 6.6%       | 0.1%       |         | 1.7%        |

| Reflector                    | 2.0%        | 1.9%       | 0.1%       |         | 1.9%        |

| Miscellaneous                | 1.4%        |            |            | 6.8%    | 1.1%        |

| Linear Fluorescent           | 9.9%        | 80.0%      | 89.2%      | 16.3%   | 29.1%       |

| T5                           | 0.1%        | 5.2%       | 6.4%       |         | 1.5%        |

| T8 Less than 4ft             | 0.1%        | 0.7%       | 0.5%       |         | 0.2%        |

| T8 4ft                       | 1.1%        | 43.9%      | 54.4%      |         | 12.8%       |

| T8 Greater than 4ft          | 0.0%        | 1.3%       | 2.3%       |         | 0.4%        |

| T12 Less than 4ft            | 0.1%        | 0.4%       | 0.0%       |         | 0.2%        |

| T12 4ft                      | 5.7%        | 19.8%      | 16.6%      |         | 9.3%        |

| T12 Greater than 4ft         | 0.5%        | 5.3%       | 7.5%       |         | 1.8%        |

| T8 U-Shaped                  | 0.0%        | 2.2%       | 0.4%       |         | 0.6%        |

| T12 U-Shaped                 | 0.0%        | 0.5%       | 0.7%       |         | 0.1%        |

| Miscellaneous                | 2.3%        | 0.6%       | 0.3%       | 16.3%   | 2.1%        |

| High Intensity Discharge     | 0.0%        | 1.7%       | 9.8%       | 52.2%   | 1.7%        |

| Mercury Vapor                | 0.0%        | 0.0%       | 1.0%       | 2.3%    | 0.1%        |

| Metal Halide                 | 0.0%        | 1.5%       | 6.5%       | 16.5%   | 0.8%        |

| High Pressure Sodium         | 0.0%        | 0.2%       | 2.3%       | 32.5%   | 0.8%        |

| Low Pressure Sodium          |             | 0.0%       |            | 0.8%    | 0.0%        |

| Other                        | 0.9%        | 1.9%       | 0.4%       | 12.5%   | 1.4%        |

| LED                          | 0.2%        | 1.8%       | 0.4%       | 10.8%   | 0.8%        |

| Miscellaneous                | 0.8%        | 0.0%       |            | 1.7%    | 0.6%        |

| TOTAL                        | 100%        | 100%       | 100%       | 100%    | 100%        |

Table 1.3.2 – U.S. lighting market: distribution of lamps (percent of the total) by end-use Sector in 2010. Source: DOE - LMC 2012.

The data reported therein match the information accounting for the light sources distribution among the different sectors, with those related to the market shares of the different lighting technologies.

As it can be noticed, very interesting hints are provided about the strong variations in the distribution of the various lighting technologies according to the specific sector of application.

However, beside a static snapshot of present situation, it may be worth to catch also market trends. In this perspective, a suitable information, about lighting market evolution over the last decade, can be derived by comparing current data with the outcomes of the analogous DOE's report relative to the year 2001 [13].

The net result is a general decrease of average lamp wattages against an increment of lamp quantities, thanks to the use of more efficient lighting technologies.

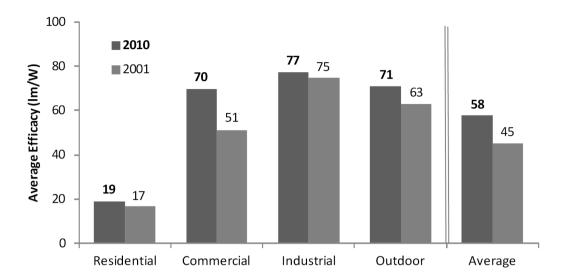

A detailed description of such matter can be easily derived by observing Table 1.3.3 and Fig. 1.3.4, reporting the comparison between the data of the years 2001 and 2010 concerning the number of lamps and the average light sources efficacy for the different sectors.

|             | Lamps<br>(million) | Average Daily Operating Hours | Wattage per Lamp | Electricity Use<br>(TWh) |

|-------------|--------------------|-------------------------------|------------------|--------------------------|

|             | 2001 2010          | 2001 2010                     | 2001 2010        | 2001 2010                |

| Residential | 4,611 -> 5,812     | 2.0 - 1.8                     | 63               | 208 175                  |

| Commercial  | 1,966 -> 2,069     | 9.9 - 11.2                    | 56 <del></del>   | 391 - 349                |

| Industrial  | 327 - 144          | 13.5 - 13.0                   | 65 <del></del>   | 108 -> 58                |

| Outdoor     | 73 -> 178          | 10.5 - 11.7                   | 205 -> 151       | 58 → 118                 |

| Total       | 6,977 -> 8,203     | 4.8 → 4.7                     | 62               | 765 → 700                |

Table 1.3.3 – Number of installed lamps by application sector. Comparison between the data collected in 2001and in 2010. Source: DOE - LMC 2012.

As it can be noticed, indeed, from 2001 to 2010 a general increment of the average light sources efficiency, in terms of the ratio between the emitted luminous flux and the dissipated power, actually involved all market sectors.

However, it is worth to observe that such improvement has been particularly noticeable in commercial building and outdoor applications, while the residential sector, despite the widespread of compact fluorescent lamps, still keeps suffering the large reliance upon incandescent light sources.

Fig. 1.3.4 – Average light sources efficacy by sector. . Comparison between the data collected in 2001 and in 2010. Source: DOE - LMC 2012.

The actual result is that the average efficacy of the entire U.S. lighting stock has increased from 45 lm/W in 2001 to 58 lm/W in 2010, considering the overall lumen production over the whole energy consumed for lighting purposes.

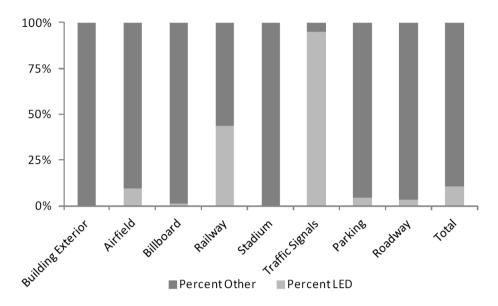

It is interesting to observe that, although there has been a considerable migration towards energy efficient lighting technologies, solid state lighting is still limited to niche applications.

As can be inferred from Table 1.3.2, LED lamps diffusion is, indeed, currently relevant only for the outdoor use (10.8%), being employed most of all for traffic light signals as shown in Fig. 1.3.5. Nevertheless, solid state lighting market share is still negligible (<1%) as concerns the cumulative lighting market datum.

In many cases, the high initial price is the major responsible in deterring the consumer from buying energy efficient lighting products, despite the perspective of lower lifecycle costs.

It is therefore evident that solid state lighting technology still need a further research commitment to improve devices performances and decrease manufacturing costs. On the other hand, international governments can play a fundamental role in supporting investments in energy efficient lighting, also through more stringent lighting regulations, and public awareness campaigns.

Only in this way, it will indeed be possible to promote a further improvement of average lighting sources efficacy and realize potential energy saving, through a massive LEDs lighting market penetration in the upcoming years.

Fig. 1.3.5 – LED prevalence in the outdoor sector. Source: DOE - LMC 2012.

# 1.4. Solid State Lighting

## 1.4.1. The History of Lighting - a Brief Review

The relationship between human life and artificial lighting is a very ancient history, started about half million of years ago with the construction of the first torches built with coniferous tree branches.

The next step was the creation of primitive lamps made of hollow rocks initially filled with moss soaked in animal fat and then with fish, olive and other vegetal oils. However, only in 3000 BC became the construction of the first candles, although very different from those commonly known nowadays.

A significant step forward was then made about four thousand years later, in the tenth century AD, with the invention of the first kerosene lamp by Zakariya al-Razi and the consequent introduction of the first street lamps.

However, only with the Industrial Revolution the lighting sector actually received a major boost. The need to extend the work activity during the night hours, indeed, strongly encouraged the research of ever more effective light sources.

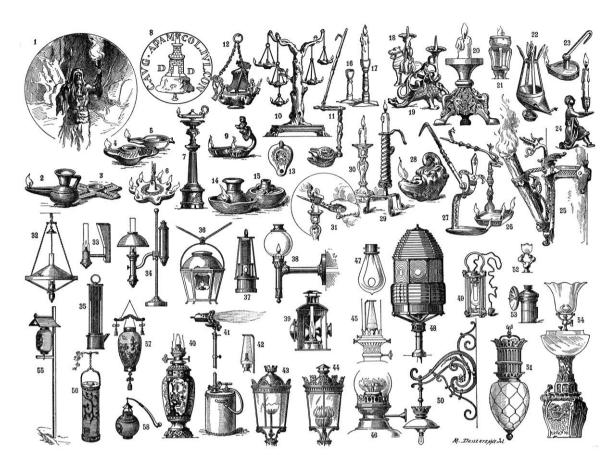

In 1780 the Swiss physicist Aimé Argand patented the Argand lamp, an oil lamp capable of emitting from 6 to 10 candela, then improved also with the addition of a glass chimney, Fig. 1.4.1 (32-34).

In the same years were carried out many studies on gas lamps, culminated with the invention of the first gas lamp by the Scottish engineer William Murdoch, in 1792.

The advent of the nineteenth and twentieth century finally brought a real lighting revolution, with a huge amount of significant advances in lighting technology. Among the many inventions, the most relevant ones are listed here in the following as useful reference.

- 1800 Carcel lamp, by Bernard Guillaume Carcel,

- 1802 Carbon arc lighting, first electric lamp, by Humphry Davy,

- 1835 first bulb based electric lighting system, demonstrated by James Bowman Lindsay,

- 1853 modern kerosene lamp, by Ignacy Lukasiewicz,

- 1867 first fluorescent lamp, demonstrated by A. E. Becquerel,

- 1875 first patented electric light bulb, by Henry Woodward,

- 1876 Yablochkov candle, the first practical carbon arc lamp for public street lighting, by Pavel Yablochkov,

Fig. 1.4.1 – Lighting through the ages, illustration by Maurice Dessertenne.

Antiquity: 1. Prehistory. - 2-3. Egyptian - 4-5. Assyrian. 6-13. Roman. - 14-15. Carthaginian. - 16-17. Merovingian period. - Middle age and modern times: 19-20. 11th century. - 21. 12th century. - 22. 13th century. - 23-24. 14th century. - 25-26-27. 15th century. - 28. 16th century. - 29. 17th century. - 30-31. 18th century. - Contemporary period: 32. (original) Argand lamp. - 33-34. (Antoine Quinquet's improved) Argand lamp. 35. Stephenson (Geordie) lamp (mines). - 36. Street light. - 37. Davy lamp. - 38. Air-fed wick lamp (theatre). - 39. Railway lamp. - 40. Carcel lamp. - 41. Gasifier. - 42. Auer (gas) lamp with gas mantle. - 43. Gas street lighting (regular burner). - 44. Gas street lighting (high intensity burner). - 45. Auer (petrol) lamp. - 46. (Air-fed) petrol lamp. - 47. Incandescent (electricity). - 48. Lighthouse (electricity). - 49. Mine lamp (electricity). - 50. Incandescent (electricity) [street light]. - 51. Arc light (electricity). - 52. Acetylene lamp (burner). - 53. Acetylene lamp (bycicle). - 54. Acetylene lamp (lamp). - Japan: 55. Street light. - 56. Transportation (rickshaw). - 57. Lantern for funerals. - 58. Portable lantern.

- 1879 first patented carbon-thread incandescent lamp, by Thomas Edison and Joseph Wilson Swan (lasted 40 hours),

- 1880 first long lasting lightbulb (1500 hours), by Thomas Edison,

- 1893 introduction of the first commercial fully enclosed carbon arc lamp, by General Electric,

- 1894 creation of the Moore tube, precursor of electric gas discharge lamps, by D.

McFarlane Moore.

#### **CHAPTER 1: SOLID STATE LIGHTING**

- 1897 incandescent lamp with solid state electrolytes, by Walther Nernst,

- 1901 mercury-vapor lamp, demonstrated by Peter Cooper Hewitt,

- 1910 neon lighting, demonstrated by Georges Claude,

- 1926 first patented fluorescent lamp, by Edmund Germer,

- 1962 first practical visible-spectrum LED, developed by Nick Holonyak Jr.,

- 1981 first Compact Fluorescent Energy Saving Lamps with integrated ballast,

- sold by Philips,

- 1991 first fluorescent light bulb using magnetic induction, invented by Philips

- 1994 first commercial sulfur lamp,

- 1995 first white LED, with blue chip and additional phosphors, invented by Shuji Nakamura at Nichia labs.

#### The Origins of Solid State Lighting

As it can be noticed, in the 19<sup>th</sup> and 20<sup>th</sup> century lighting timeline previously described, solid state lighting has been taken into account twice, namely in correspondence of the development of the first visible-spectrum LED device, in 1962, and of the invention of the first white LED in 1995.

The origins of solid state lighting history, however, are much older, dating back to the experiments of Henry J. Round, one of Marconi's assistant in England, at the beginning of the twentieth century.

In February 1907 Round published a note to the editors of the "Electrical World" to describe a curious phenomenon, resulting in a bright glow from a carborundum diode (Fig. 1.4 2) however there was not follow up publications, so that more than the inventor of the LED, Round should be actually considered the discoverer of the electroluminescence.

#### A Note on Carborundum.

To the Editors of Electrical World:

SIRS:—During an investigation of the unsymmetrical passage of current through a contact of carborundum and other substances a curious phenomenon was noted. On applying a potential of 10 volts between two points on a crystal of carborundum, the crystal gave out a yellowish light. Only one or two specimens could be found which gave a bright glow on such a low voltage, but with 110 volts a large number could be found to glow. In some crystals only edges gave the light and others gave instead of a yellow light green, orange or blue. In all cases tested the glow appears to come from the negative pole, a bright blue-green spark appearing at the positive pole. In a single crystal, if contact is made near the center with the negative

tive pole, and the positive pole is put in contact at any other place, only one section of the crystal will glow and that the same section wherever the positive pole is placed.

There seems to be some connection between the above effect and the e.m.f. produced by a junction of carborundum and another conductor when heated by a direct or alternating current; but the connection may be only secondary as an obvious explanation of the e.m.f. effect is the thermoelectric one. The writer would be glad of references to any published account of an investigation of this or any allied phenomena.

NEW YORK, N. Y.

H. J. ROUND.

Fig. 1.42 - . A note on carborundum, Henry J. Round 1907.

In the issue of Nature Photonics of April 2007, Nikolay Zheludev actually gave credit to Oleg Vladimirovich Losev for being the real inventor of LED. However, despite the debate on paternity of solid state lighting, Losev is undoubtedly one of the leading figure in the history of LEDs [14].

He was born in 1903, from a high-ranking family in Imperial Russia and, although without receiving any formal education, during his short research carrier he published a number of papers and was granted of many patents of which he was the only author.

In particular, in the 1920s Losev studied light emission from forward biased zinc oxide and silicon carbide crystal rectifier diodes. His first paper on this topic, entitled "Luminous carborundum detector and detection with crystals", published in 1927 on a Russian journal of wireless telegraphy and telephony, essentially constitutes the official discovery of solid state lighting.

During his studies, Losev was able to establish the current threshold for the onset of light emission, to record the spectrum of the emitted light and to actually provide a comprehensive study of LEDs and their applications in a total of sixteen paper published between 1925 and 1930.

Such new devices had immediately a considerable success, however, because of their low power rating, for many years their application was limited to the fields of communications and electronics. It was only in the 1990s, with the introduction of the first high brightness white light emitting diodes, designed for higher power levels, that started the use in lighting applications.

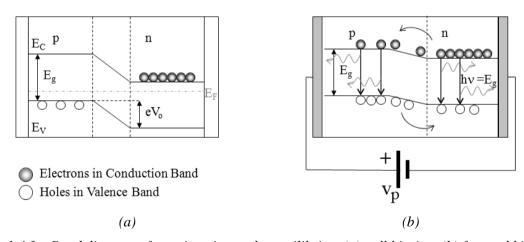

## 1.4.2. LEDs: Operating Principles and White Light

An LED is essentially a junction of semiconductor materials doped with impurities with opposite sign charge. Typically the two doped regions are indicated with the letter "n" or "p" depending on the kind of majority carriers, namely electrons or holes, respectively.

In order to reach the thermodynamic equilibrium, a charge transfer will initially occur between the two regions, with the electrons flowing from the region n (or cathode) to the region p (or anode).

When the equilibrium is reached the junction interface will be characterized by the presence of a depletion region, devoid of carrier, and of a potential barrier, hindering the charge flowing from one region to the other (Fig. 1.4.3 (a)).

If a forward biasing voltage is applied to the junction ( $v_P > 0$  in Fig. 1.4.3 (b)), the potential barrier is reduced and the depletion region will be strengthened.

So, under forward bias, majority carriers from both sides of the junction are enabled to cross the depletion region, under the action of the electric field, and entering the other side of the junction, resulting in a net transfer of majority carriers between the two regions.

This process of charge injection actually produces an excess of electrons in the conduction band of the p doped region and of holes in the valence band of the n doped region, as shown in Fig. 1.4.3 (b).

This, consequently, highly improves the probability of recombination between such careers. The process according to which an electron falls across the energy gap towards a lower energy level actually matching a hole.

Two different kind of recombination can occur, namely radiative o non radiative, depending on whether it results in the emission of a photon or of a phonon.

When the potential energy is converted into a phonon, namely a vibration of the lattice, instead that into a photon, the actual result is heat production, rather than light emission.

For an optoelectronic device, that is intended to operate as a light source, radiative recombination is therefore actually desired. The ratio of the number of photons, emitted from the active region of the semiconductor chip, to the number of electrons, injected into the active region, is called "internal quantum efficiency".

Fig. 1.4.3 – Band diagram of a pn junction at the equilibrium (a) null biasing, (b) forward biasing.

However this is not the only parameter concurring to the determination of device conversion efficiency, since a number of other power losses characterize the actual conversion process. In order to clarify this issue, the other two main contributors, to the overall LED chip efficiency, are briefly described here in the following.

The first one is the "electrical efficiency", that accounts for device ohmic losses associated with the semiconductor layers and the LED package materials. It essentially represents the

rate of the electrical charge carriers injected into the LED package that actually reach the active region of the LED.

The other important parameter is, instead, the "light extraction efficiency" which corresponds to the number of photons emitted from the semiconductor chip into the encapsulant, over the total number of photons generated in the active region. The product between the latter parameter and the internal quantum efficiency is called "external quantum efficiency".

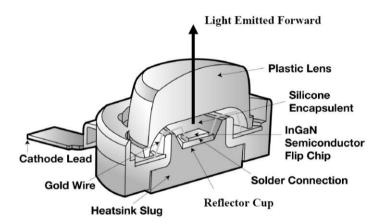

Additional efficiency losses will then occur within the LED package (whose typical structure is shown in Fig. 1.4.4) some of them will be briefly described as reference in the following.

Fig. 1.4.4 – Typical structure of a LED device.

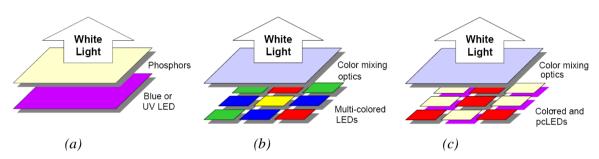

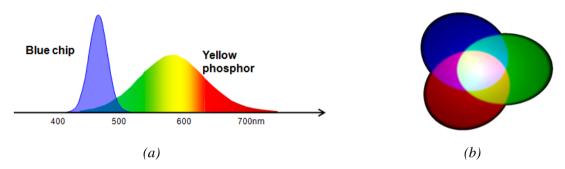

#### White Light LEDs

As previously explained, the light emitted by a solid state source is the result of radiative recombinations between majority and a minority free carriers within the semiconductor.

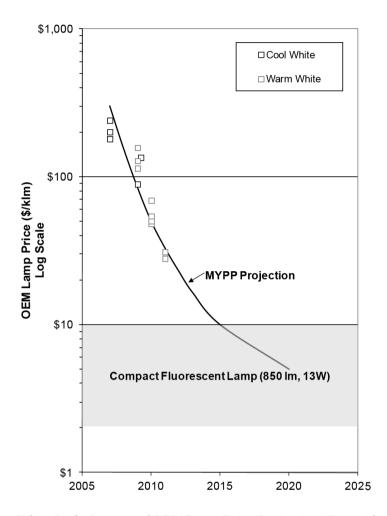

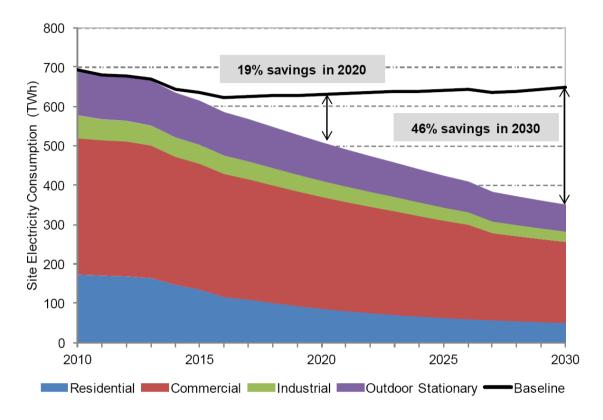

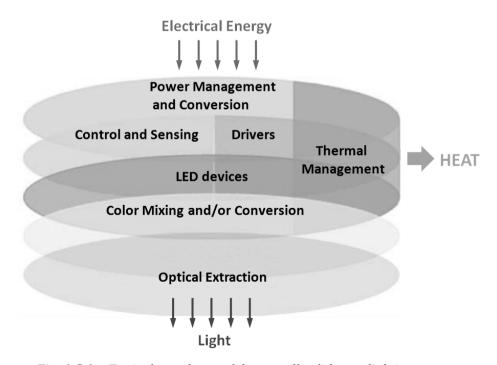

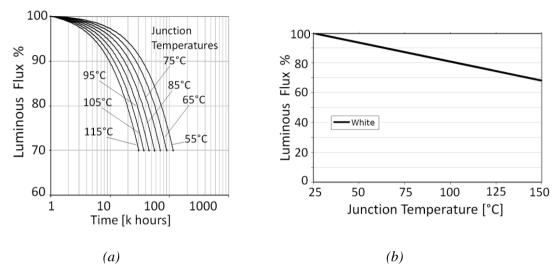

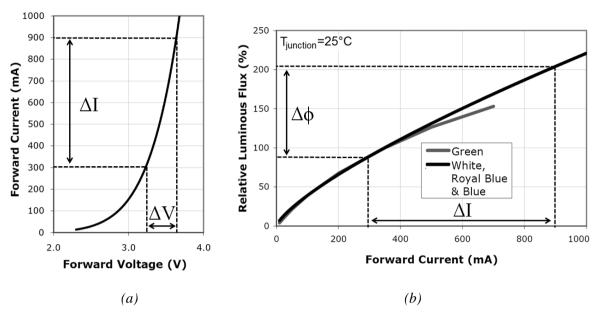

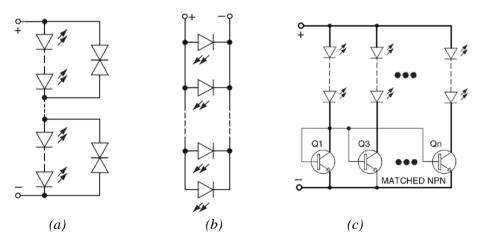

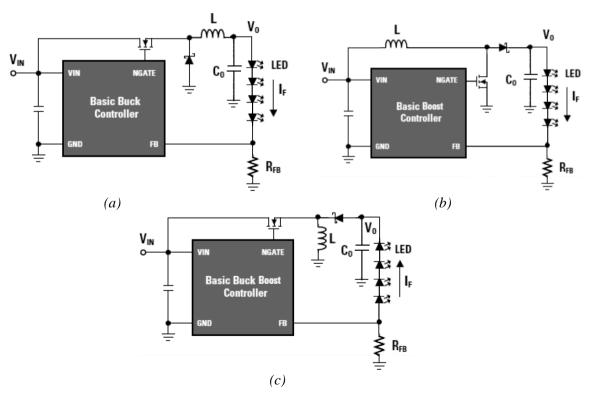

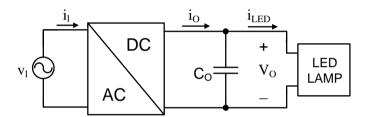

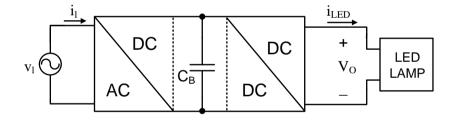

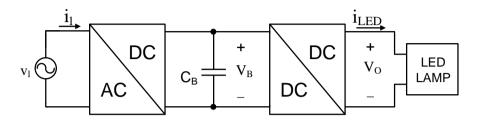

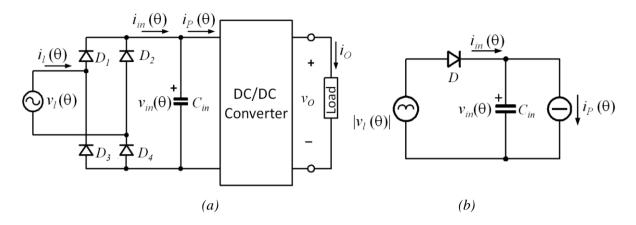

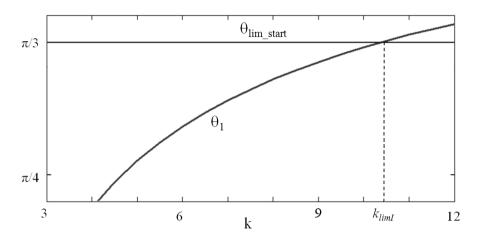

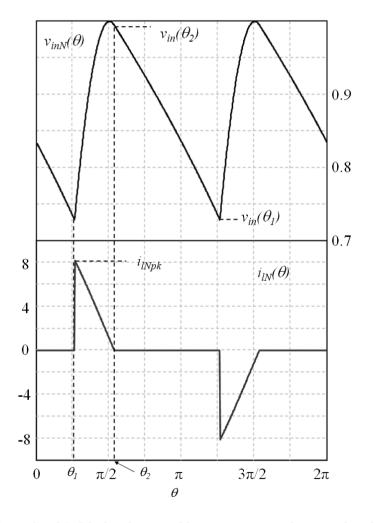

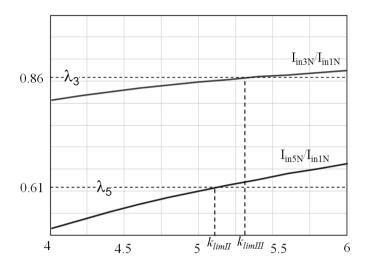

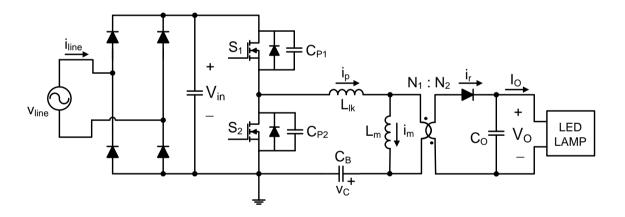

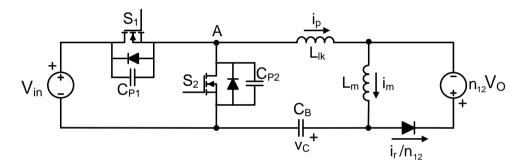

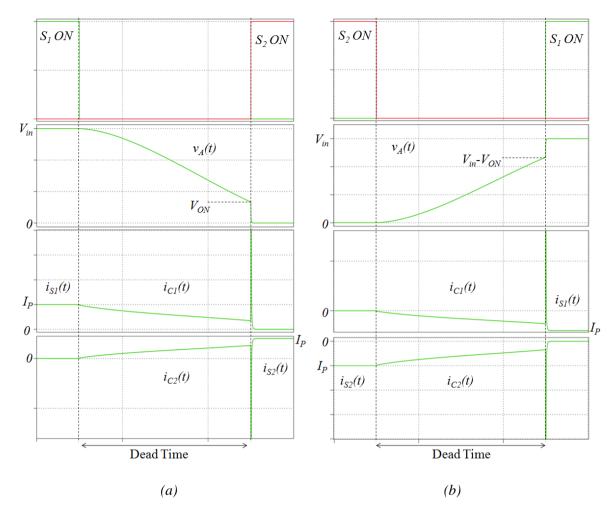

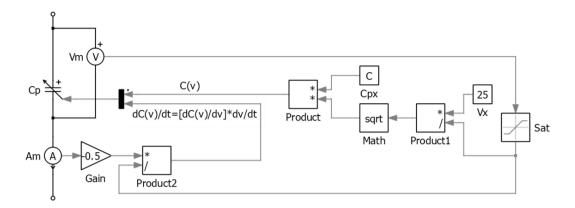

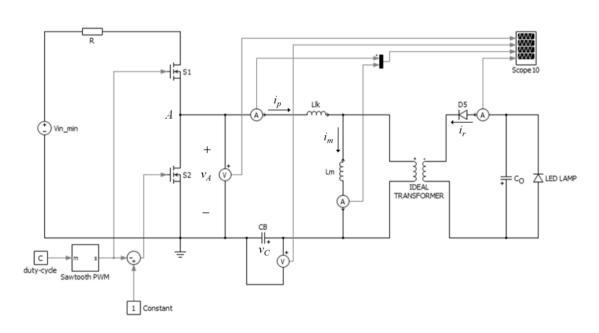

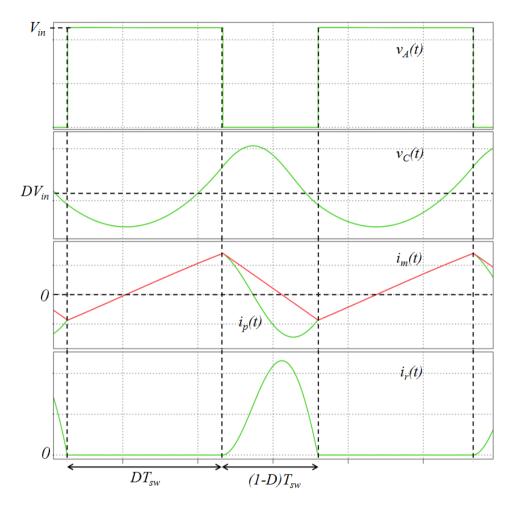

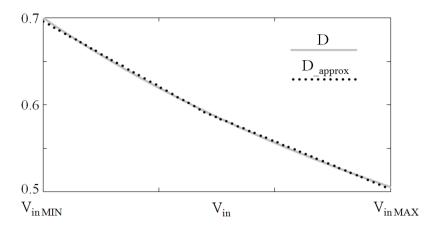

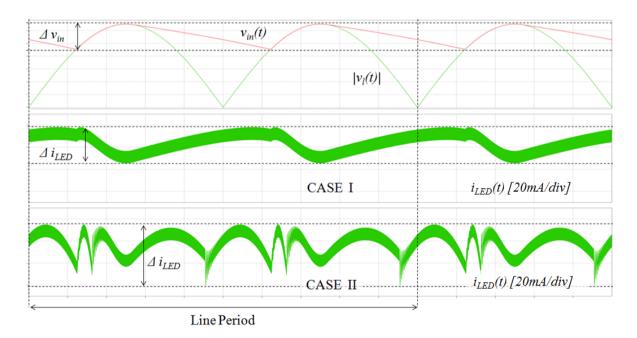

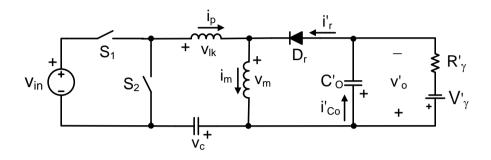

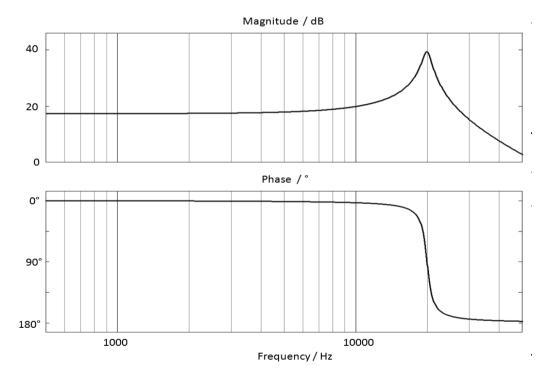

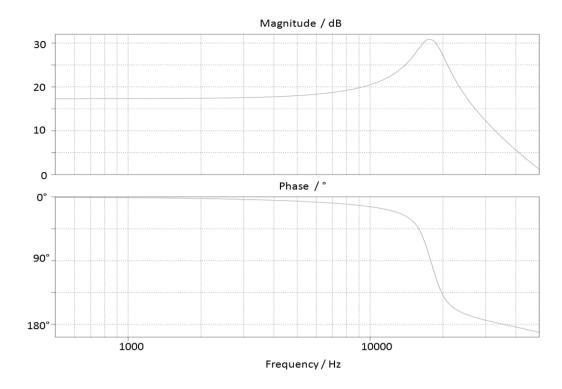

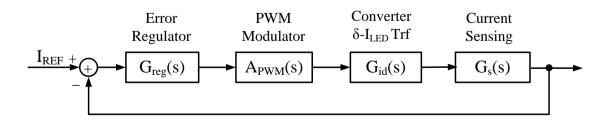

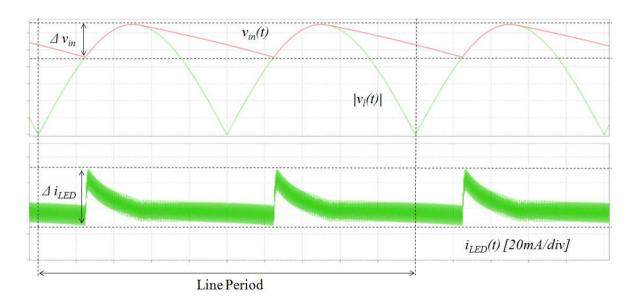

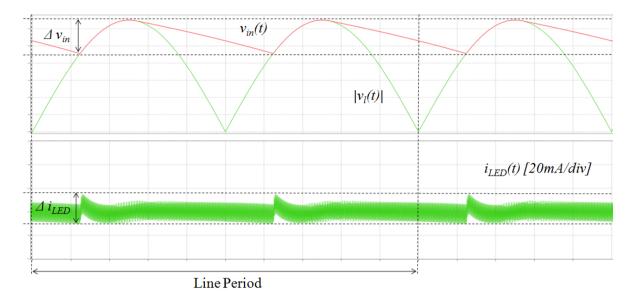

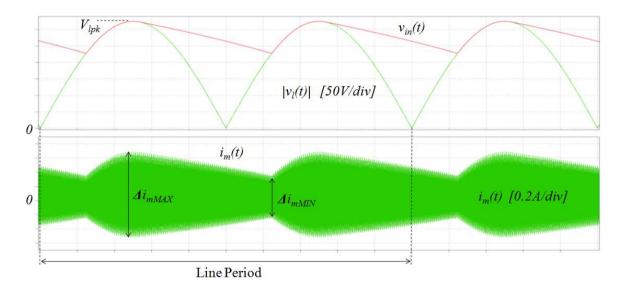

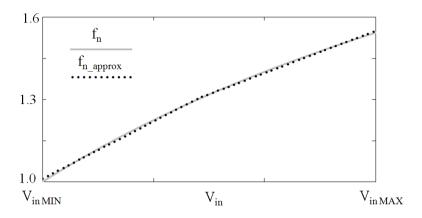

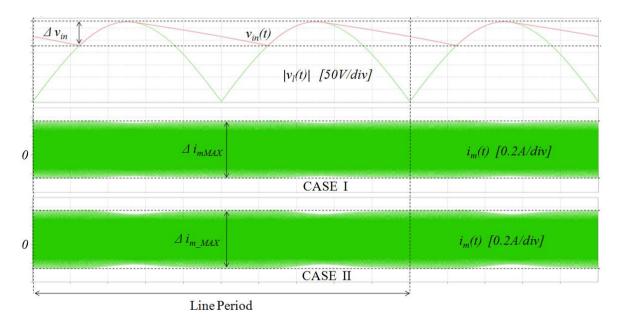

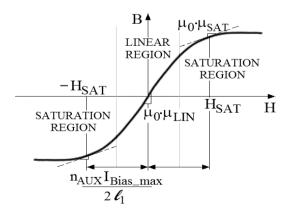

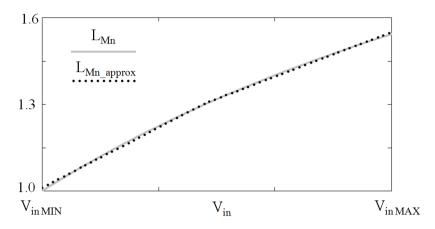

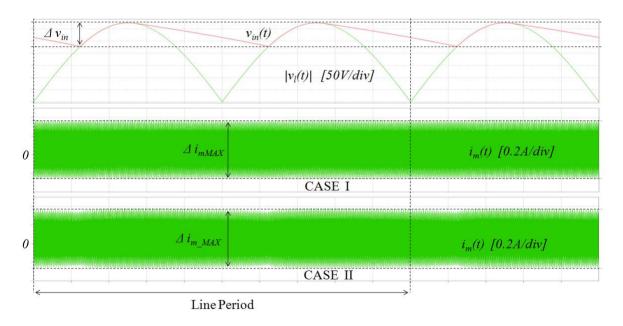

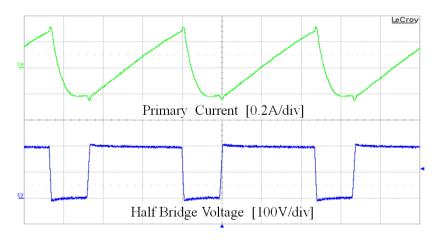

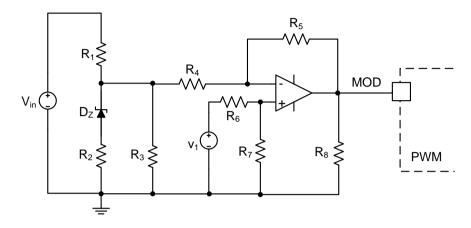

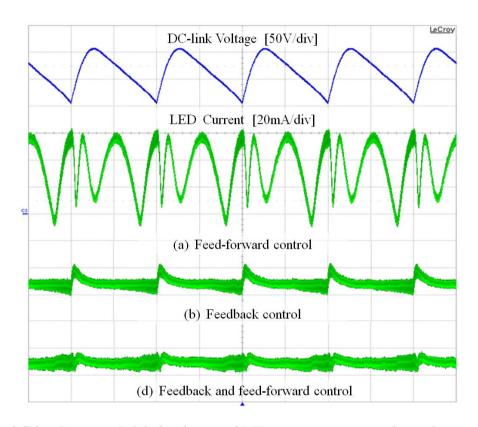

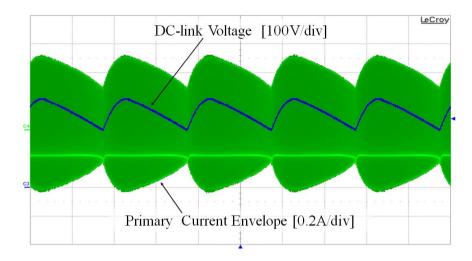

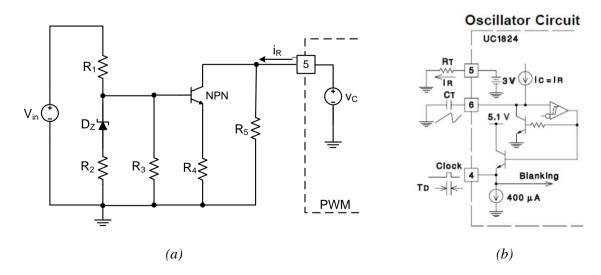

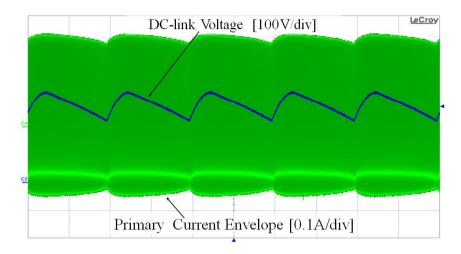

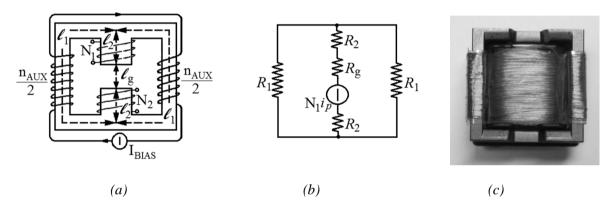

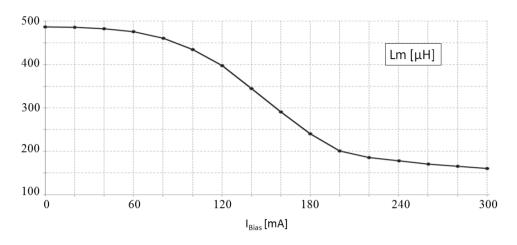

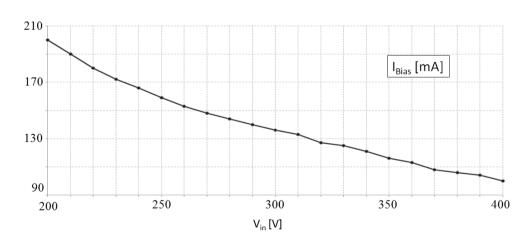

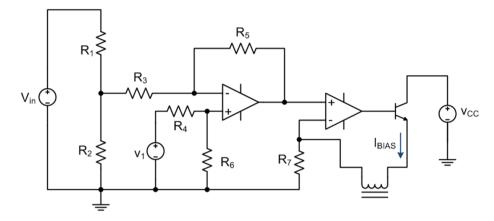

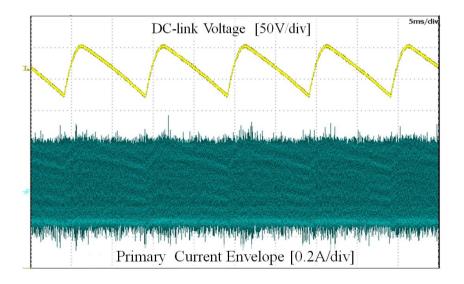

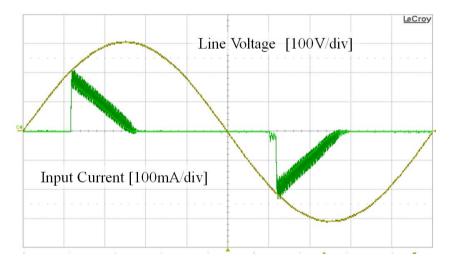

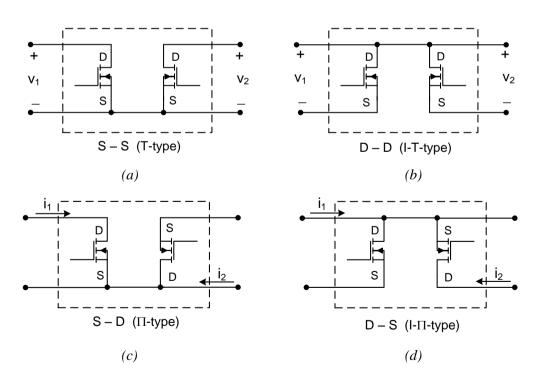

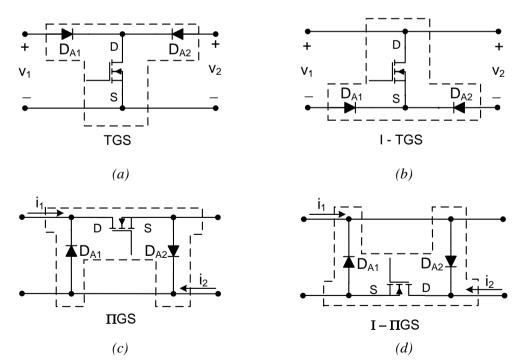

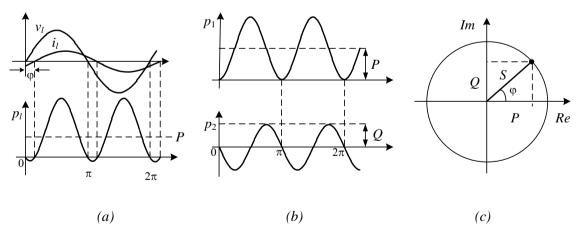

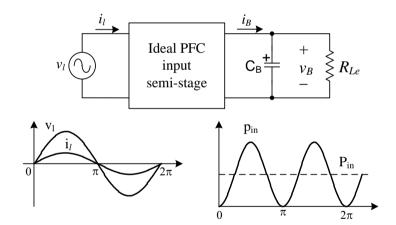

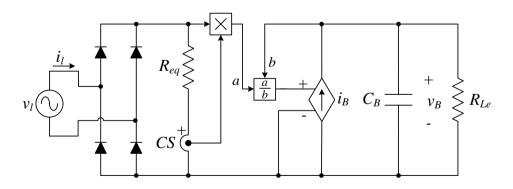

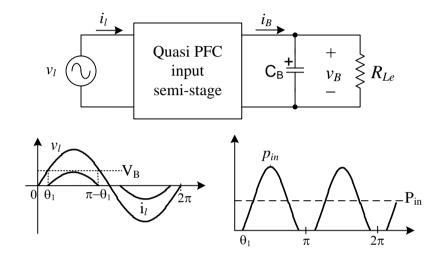

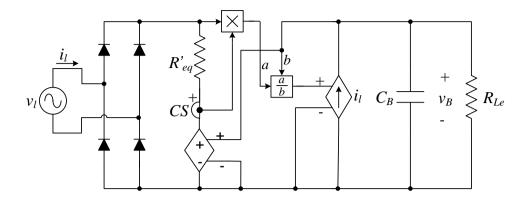

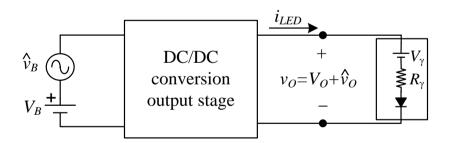

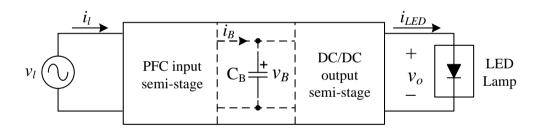

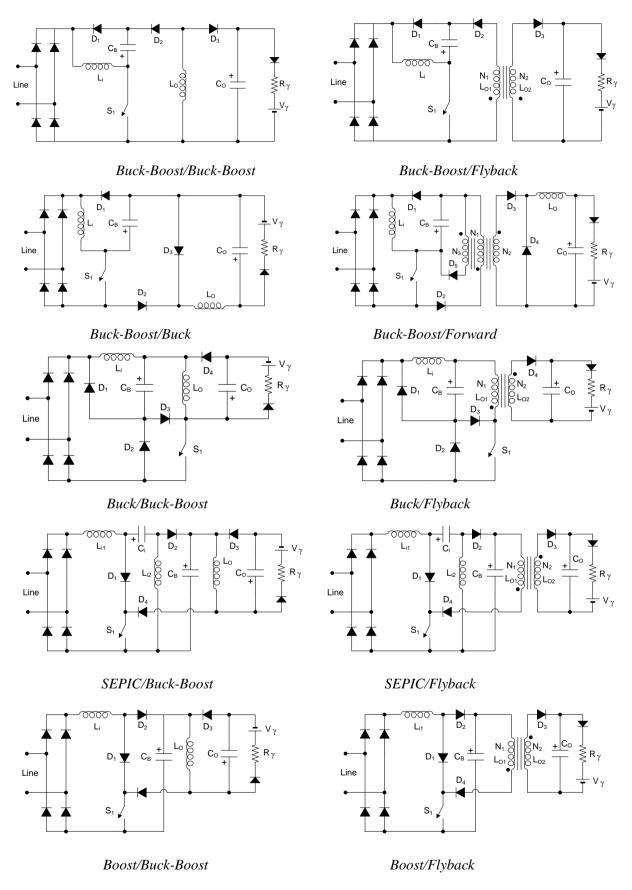

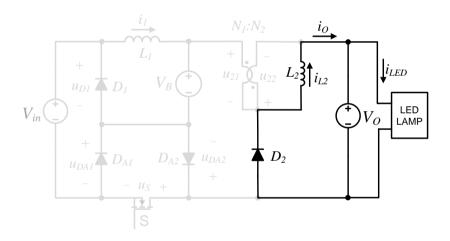

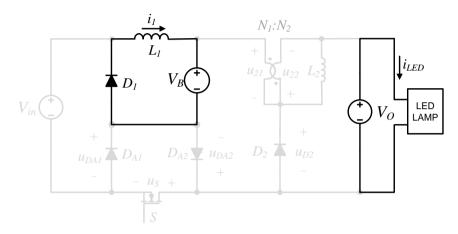

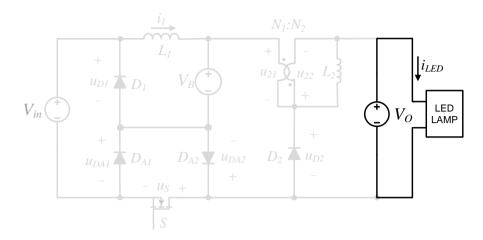

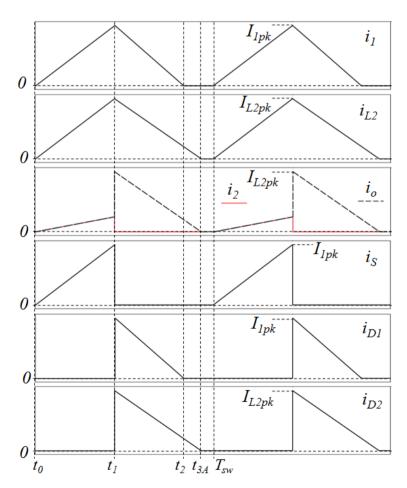

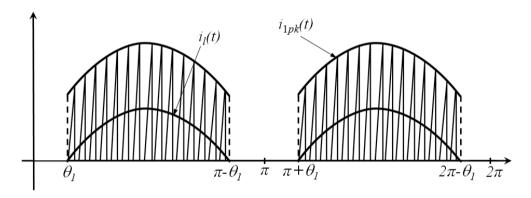

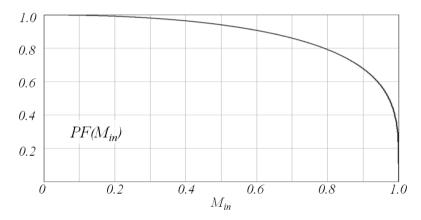

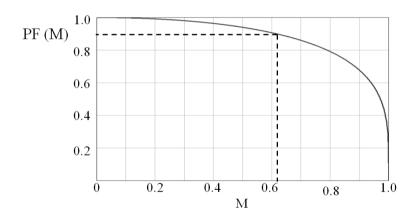

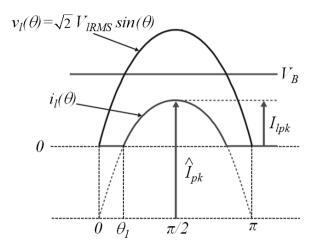

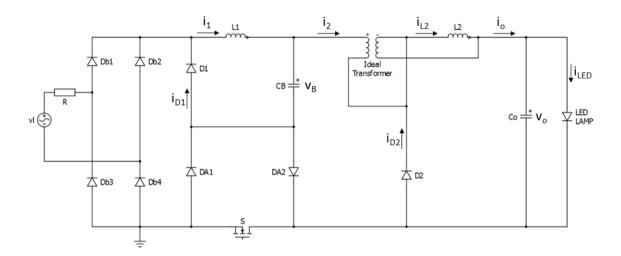

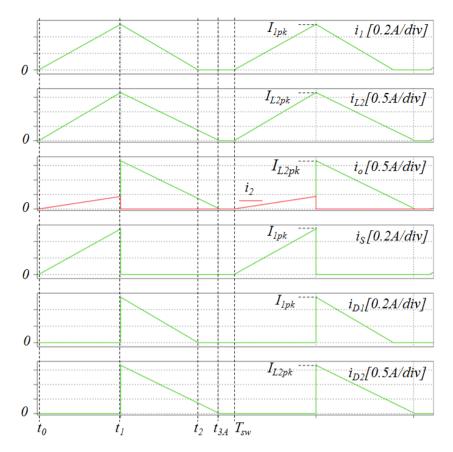

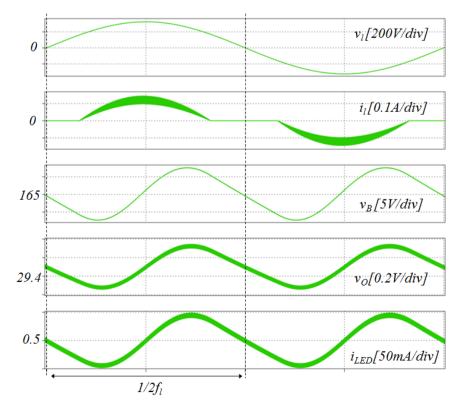

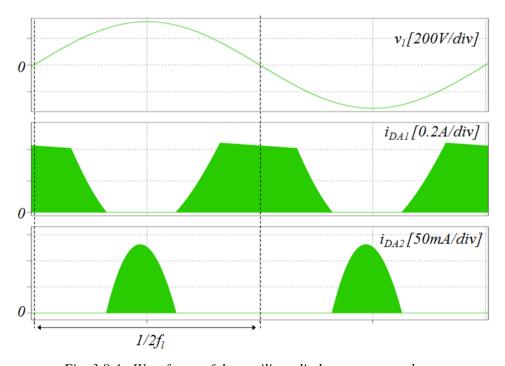

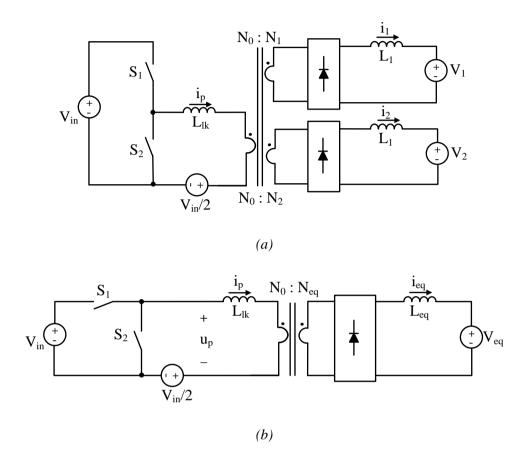

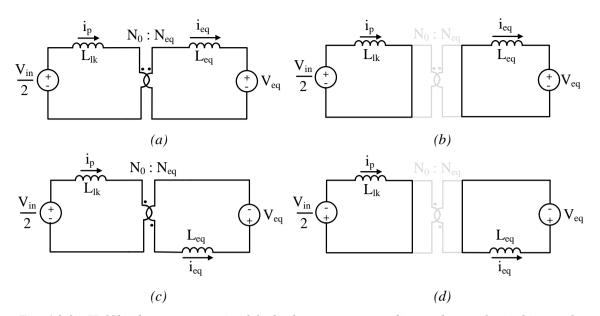

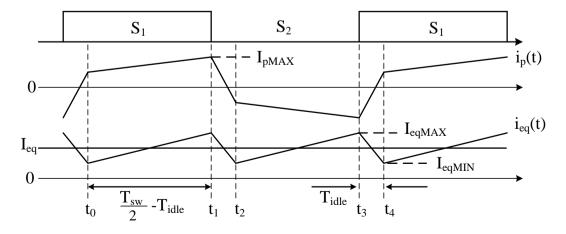

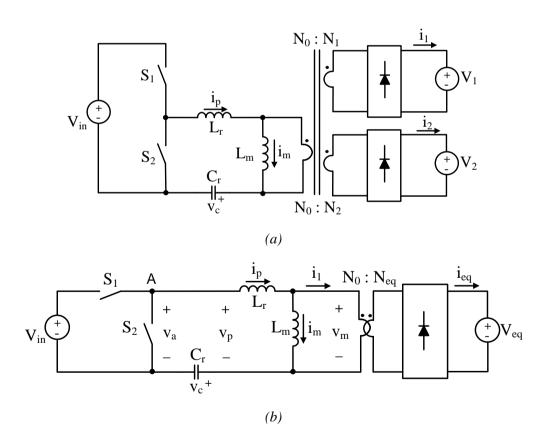

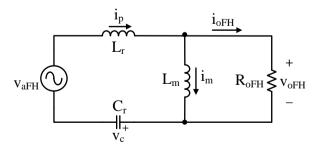

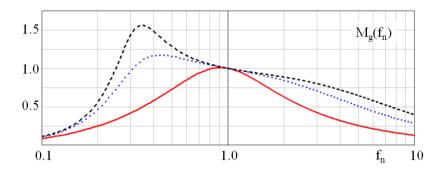

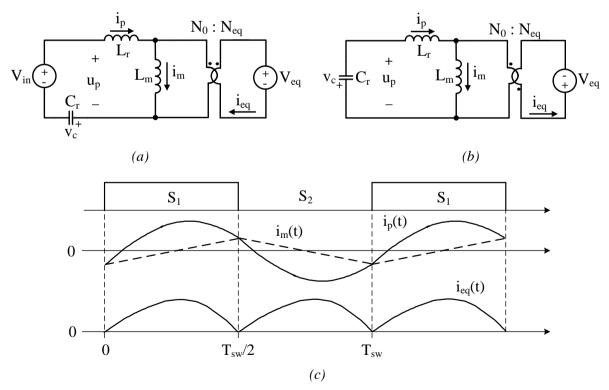

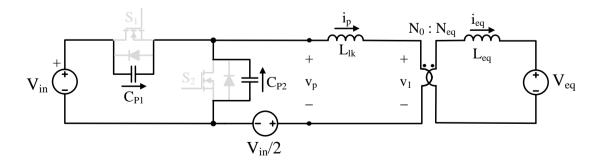

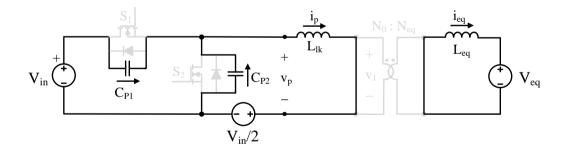

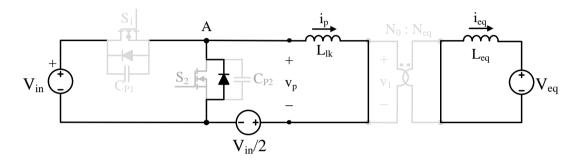

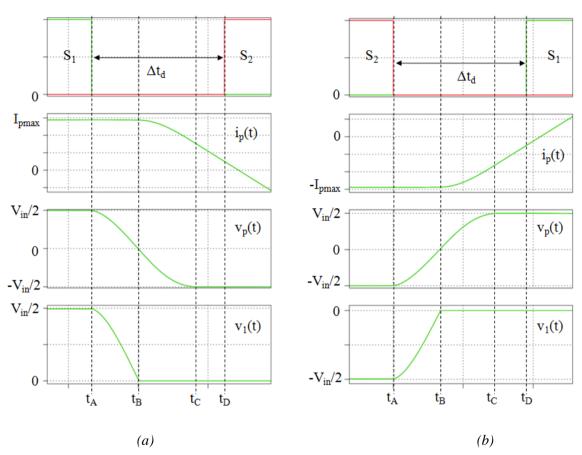

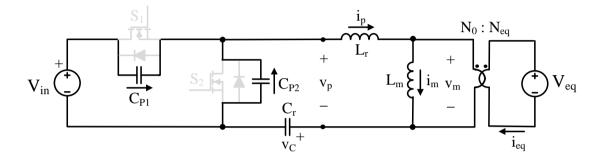

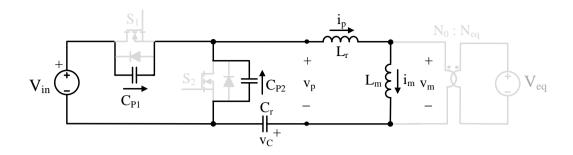

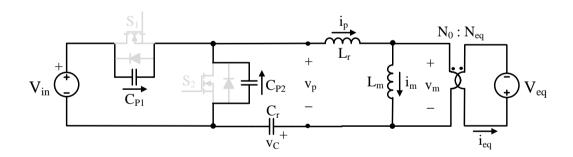

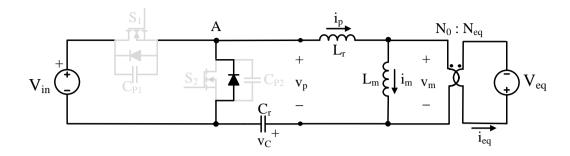

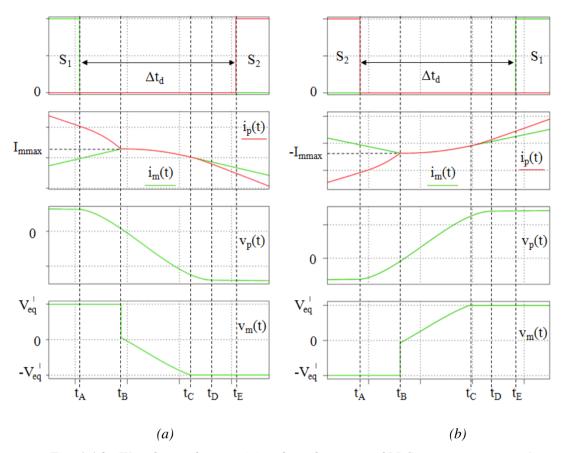

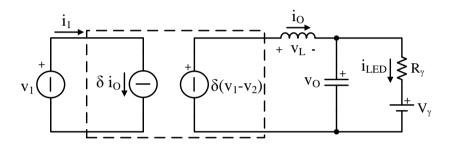

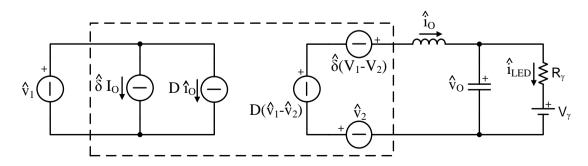

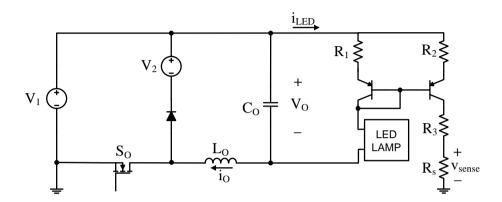

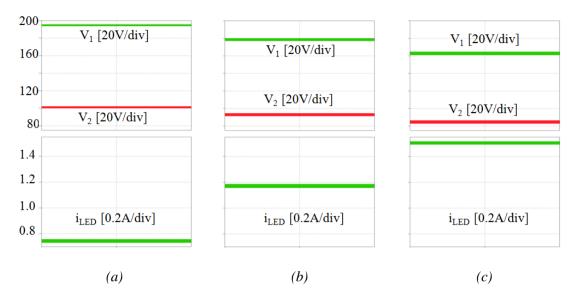

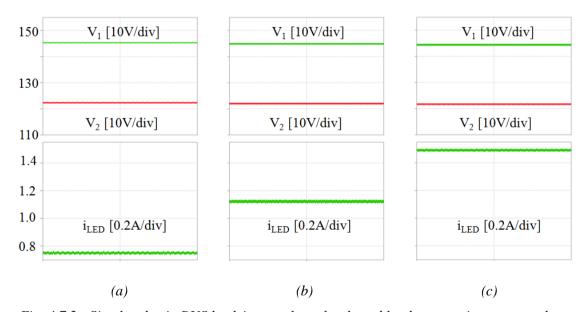

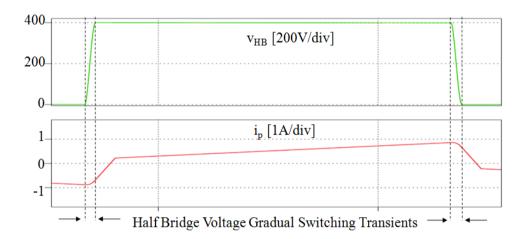

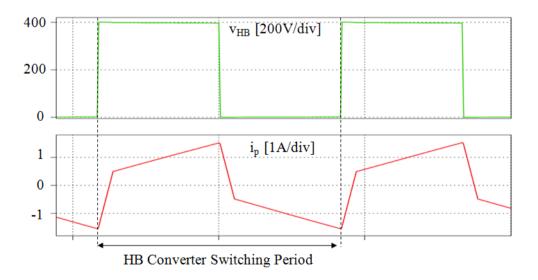

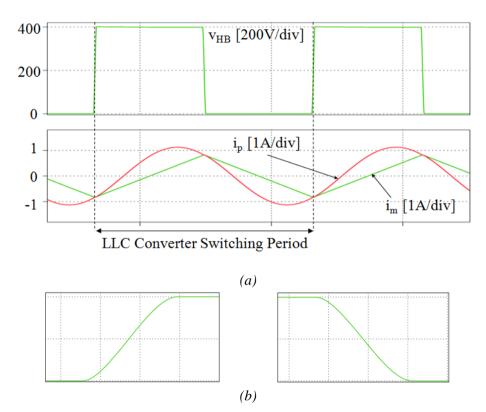

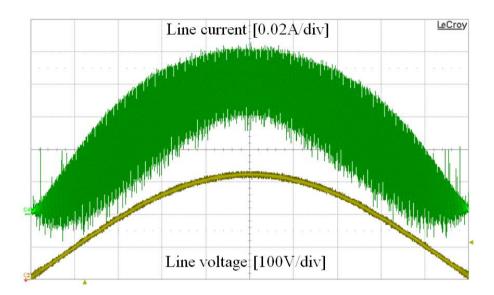

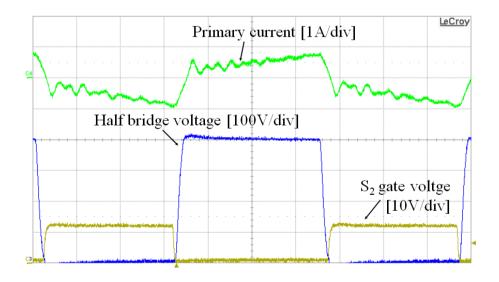

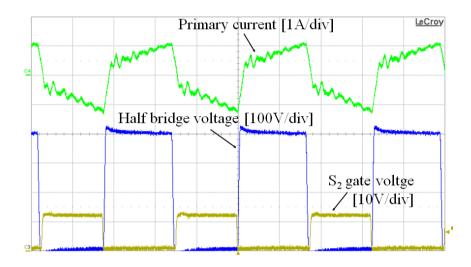

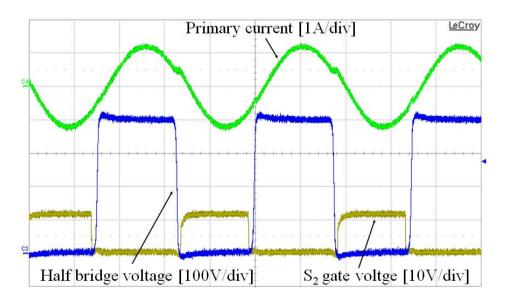

If such transitions take place between states in the conduction  $(E_c)$  and in the valence band  $(E_v)$ , the energy of the emitted photons will correspond to the chip material band gap energy  $E_g = E_c - E_v$ .