# **802.15.4 Low Intermediate Frequency Radio Receiver**

By: Sanjay Avasarala

Senior Project

**Electrical Engineering Department**

Cal Poly, San Luis Obispo

2012

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                              | i  |

|-------------------------------------------------------------------------------|----|

| LIST OF TABLES AND FIGURES                                                    | ii |

| ABSTRACT                                                                      | iv |

| DESIGN                                                                        | 1  |

| Section 1 - Introduction                                                      |    |

| SECTION 2 - BACKGROUND TECHNOLOGY REVIEW                                      |    |

| SECTION 3 - DESIGN REQUIREMENTS AND SPECIFICATIONS                            |    |

| Section 4 - Design Alternatives                                               |    |

| Section 5 - System design                                                     |    |

| Subsection 5.1 – Image Reject Filter Analysis and Design                      | 11 |

| Subsection 5.2 – BPSK Theory, Design, and Simulation                          | 20 |

| Subsection 5.3 – Modulator/Demodulator Design                                 |    |

| Subsection 5.4 – Programmable Gain Amplifier Design                           | 25 |

| Subsection 5.5 – Software/VHDL Design                                         |    |

| Software Component 5.5.1 – ADC                                                |    |

| Software Component 5.5.2 – Digital Oscillator Multiplication and Demodulation |    |

| Software Component 5.5.3 – Integration                                        |    |

| Software Component 5.5.4 – Sign Determiner                                    | 27 |

| Software Component 5.5.5 – PRBS Signal Generator                              | 27 |

| Software Component 5.5.6 – Sync Clock                                         |    |

| Software Component 5.5.7 – PGA Feedback                                       |    |

| SECTION 6 - CONSTRUCTION AND INTEGRATION                                      |    |

| Section 7 - sub system testing                                                |    |

| Subsystem 7.1 – Filter/Demodulator Testing                                    |    |

| Subsystem 7.2 – ADC Testing                                                   |    |

| Subsystem 7.3 –Instrumentation Amplifier though ADC Testing                   |    |

| Subsystem 7.4 – Modulator Testing                                             |    |

| Subsystem 7.5 – Programmable Gain Amplifier Testing                           |    |

| SECTION 8 - FULL SYSTEM TEST                                                  |    |

| Section 9 - results analysis/conclusion                                       | 47 |

| Section 10 - Bibliography                                                     | 49 |

| APPENDICES                                                                    | 50 |

| APPENDIX A - ABET SENIOR PROJECT ANALYSIS                                     | 50 |

| Appendix B - schematics                                                       |    |

| APPENDIX C - PCB LAYOUT ARTWORK                                               |    |

| APPENDIX D - VHDL PROGRAM LISTING                                             | 68 |

# ACKNOWLEDGEMENTS

I would like to thank my father for all the help he gave me during this project and my mother who motivated me to study and work hard and remain dedicated. I also want to thank my senior project advisor Professor Wayne Pilkington for the support and guidance he gave me these last two quarters.

# List of Tables and Figures

# TABLES

| <b>TABLE 3.1</b> – System specifications and requirements                                 | 7  |

|-------------------------------------------------------------------------------------------|----|

| <b>TABLE 5.1</b> – Functional description of each sub system block                        | 10 |

| TABLE 7.1.1 – Recorded values for initial filter test set up                              |    |

| TABLE 7.1.2 – Recorded values for proper individual filter test                           |    |

| TABLE 7.1.3 – Table of 5 random samples chosen from data collected for the complex filter |    |

| TABLE 7.5.1 – Selected waveforms and their respective gains and states                    | 41 |

| TABLE 8.1 – Sensitivity test results                                                      |    |

| <b>TABLE 9.1</b> – Basic top level specifications of the receiver                         | 47 |

| <b>TABLE A.1</b> – Estimated costs                                                        | 51 |

| TABLE A.2 – Actual costs                                                                  | 52 |

| <b>TABLE A.3</b> – Bill of materials                                                      | 52 |

# FIGURES

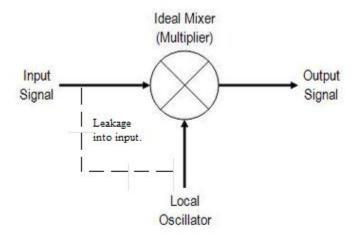

| FIGURE 1.1 – Leakage in a mixer                                                                        | 2  |

|--------------------------------------------------------------------------------------------------------|----|

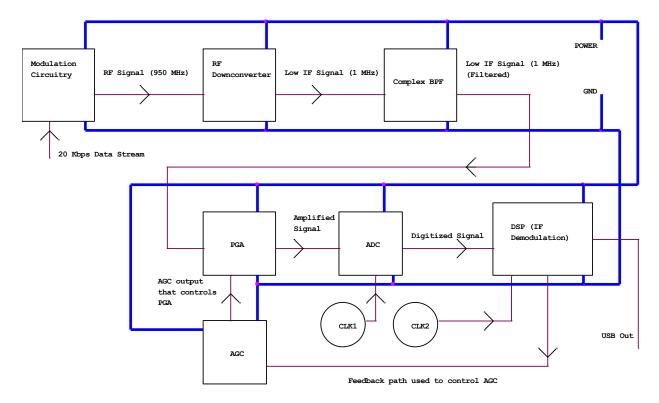

| FIGURE 5.1 – Block diagram of the entire system                                                        | 9  |

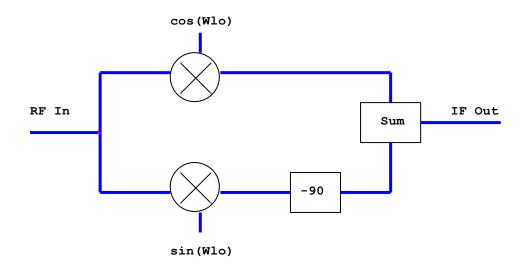

| FIGURE 5.1.1 – Simplified block diagram of an image reject system                                      | 11 |

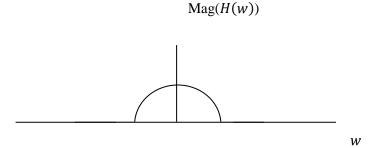

| FIGURE 5.1.2 – Magnitude response of a simple rudimentary low pass filter                              | 13 |

| FIGURE 5.1.3 – Block diagram of an image reject transfer function                                      | 14 |

| FIGURE 5.1.4 – Practical realization of a simple image reject filter                                   | 14 |

| FIGURE 5.1.5 – A more detailed look at a simple image reject filter                                    | 15 |

| FIGURE 5.1.6 – Magnitude response of a simple image reject filter                                      | 16 |

| FIGURE 5.1.7 – Ideal image reject filter using a fifth order Butterworth low pass filter               | 16 |

| FIGURE 5.1.8 – Magnitude response of a 5 <sup>th</sup> order Band pass filter (ideal)                  | 17 |

| FIGURE 5.1.9 – Magnitude response of a 5 <sup>th</sup> order Band pass filter with group delay (ideal) | 18 |

| <b>FIGURE 5.1.10</b> – Magnitude response of a 5 <sup>th</sup> order Band pass filter (non-ideal)      | 18 |

| FIGURE 5.1.11 – Completed filter schematic. This is the schematic view in LTSpice                      | 19 |

| FIGURE 5.2.1 – A BPSK system representation using a DSB-SC architecture                                | 20 |

| FIGURE 5.2.2 – Simulation showing the modulated signal.                                                | 20 |

| FIGURE 5.2.3 – Down converted low IF signal without filtering                                          | 21 |

| FIGURE 5.2.4 – Demodulated output signal                                                               | 22 |

| FIGURE 5.2.5 – Unfiltered demodulated signal with AWGN                                                 | 23 |

| FIGURE 5.2.6 – Entire simulated BPSK system in Simulink                                                | 24 |

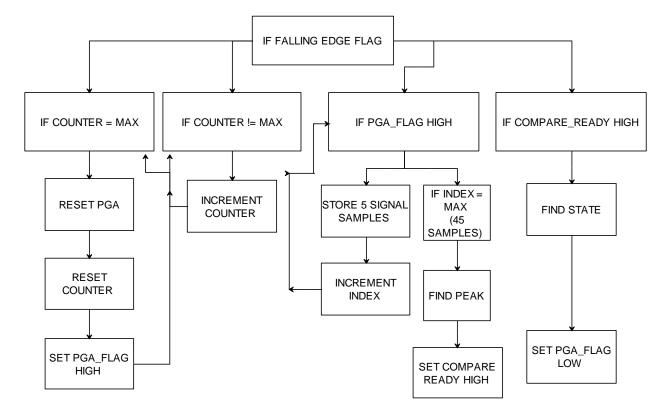

| FIGURE 5.5.7.1 – Software flow diagram for the PGA                                                     | 28 |

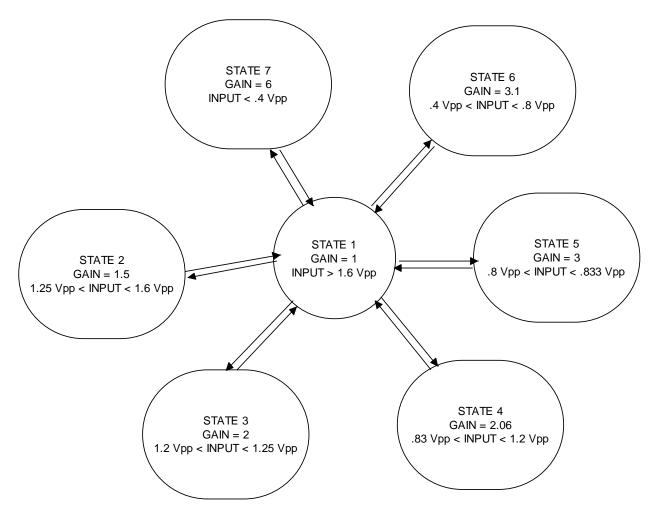

| FIGURE 5.5.7.2 – State Variable Diagram                                                                | 29 |

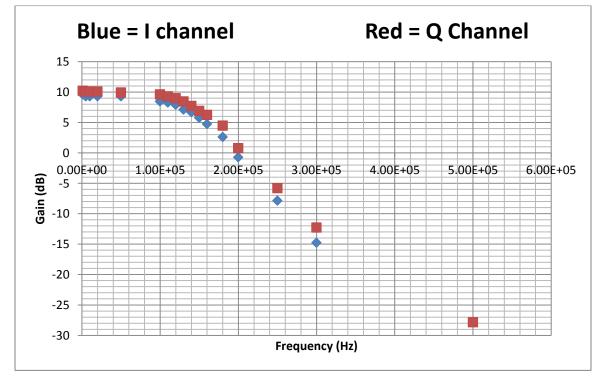

| FIGURE 7.1.1 – Plotted response for the filters                                   |    |

|-----------------------------------------------------------------------------------|----|

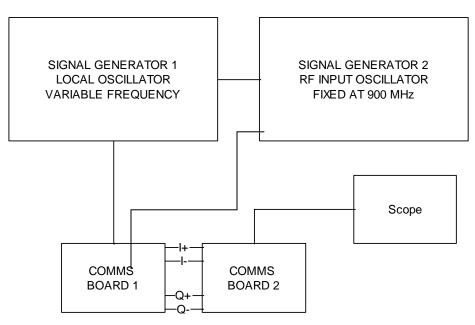

| FIGURE 7.1.2 – Test setup diagram                                                 |    |

| FIGURE 7.1.3 – I channel demodulator output                                       |    |

| FIGURE 7.1.4 – I channel differential demodulator output                          |    |

| FIGURE 7.1.5 – I and Q channel demodulator output                                 |    |

| <b>FIGURE 7.1.6</b> – $Q$ channel differential demodulator output                 |    |

| FIGURE 7.1.7 – Complex filter response with positive and negative sequences shown |    |

| FIGURE 7.2.1 – ADC Logic Analyzer output                                          |    |

| FIGURE 7.2.2 – ADC decoded output                                                 |    |

| FIGURE 7.2.3 – ADC values after being fed through the Nexys board                 |    |

| FIGURE 7.3.1 – Logic Analyzer output with the input at the IA                     |    |

| FIGURE 7.4.1 – Spectrum of the modulated 150 KHz square wave                      |    |

| FIGURE 7.5.1 – Output waveform for a .82 Vpp 2.5 CMV sin wave input               | 40 |

| FIGURE 7.5.2 – Output waveform for a .23 Vpp 2.5 CMV sin wave input               | 40 |

| FIGURE 7.5.3 – Output waveform for a 2.48 Vpp 2.5 CMV sin wave input              | 41 |

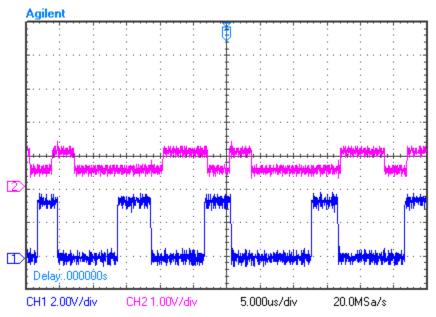

| FIGURE 8.1 – Demodulated square wave using direct conversion                      | 42 |

| FIGURE 8.2 – I channel output of the demodulator                                  | 43 |

| FIGURE 8.3 – The input and output waveforms for the filter                        | 43 |

| FIGURE 8.4 – Input data and demodulated data for a square wave                    | 44 |

| FIGURE 8.5 – Input PRBS data and the demodulated data                             | 44 |

| FIGURE 8.6 – Input data and demodulated data viewed through the Logic Analyzer    |    |

| FIGURE 8.7 – Input data and output data with the modulator LO turned off          | 45 |

| FIGURE 8.8 – Final test setup diagram                                             | 46 |

| FIGURE A.1 – Gantt Chart Timeline                                                 | 54 |

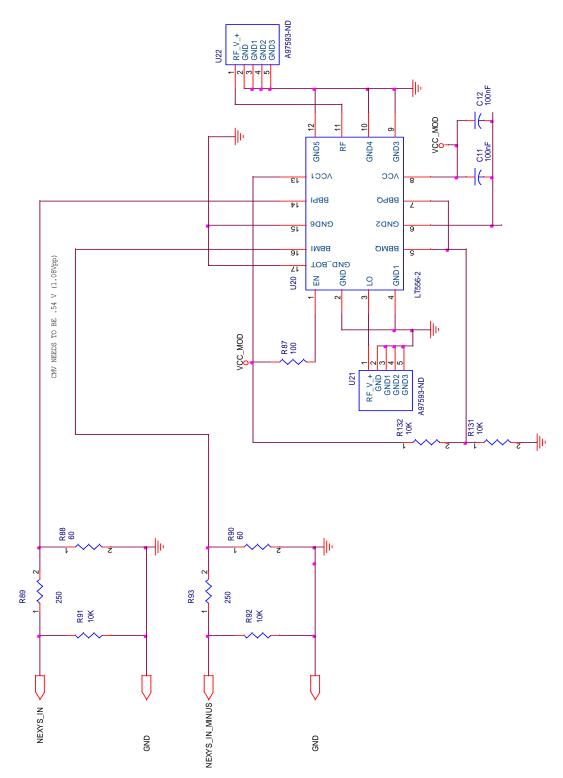

| FIGURE B.1 – Modulator Schematic                                                  |    |

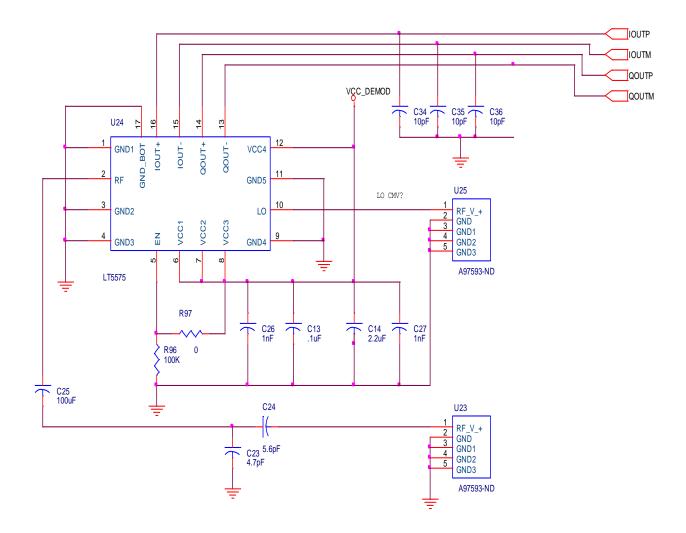

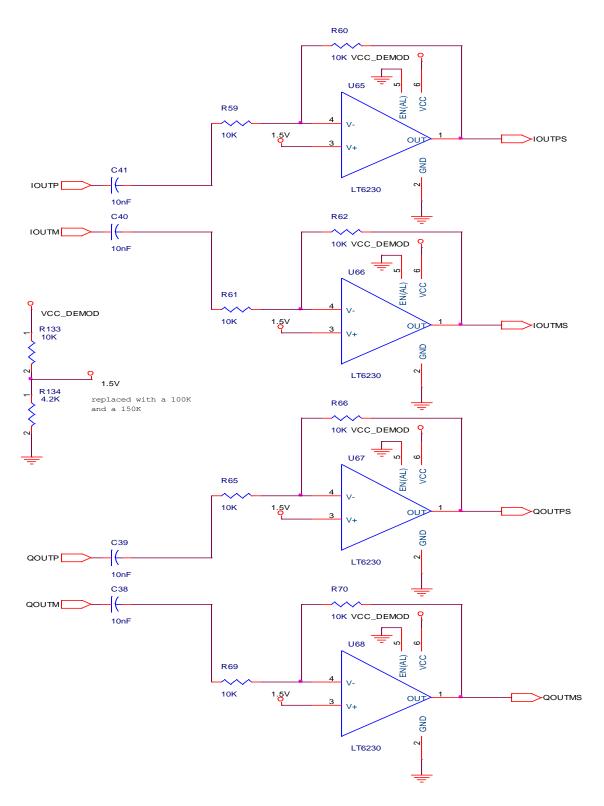

| FIGURE B.2 – Demodulator Schematic                                                |    |

| FIGURE B.3 – CMV DC Offset Shift Schematic                                        | 60 |

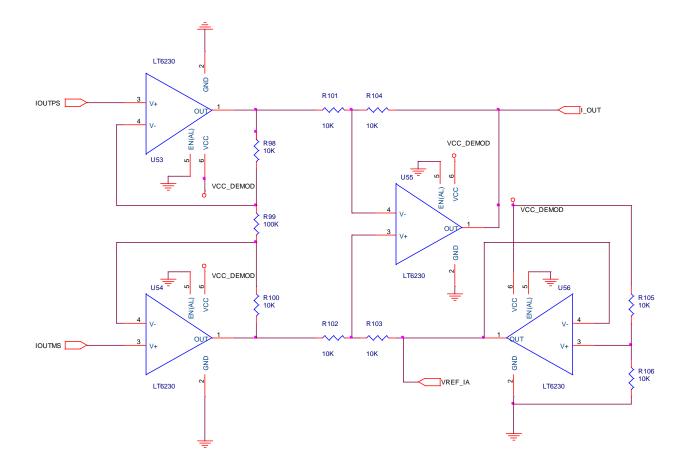

| FIGURE B.4 – Instrumentation Amplifier Schematic                                  | 61 |

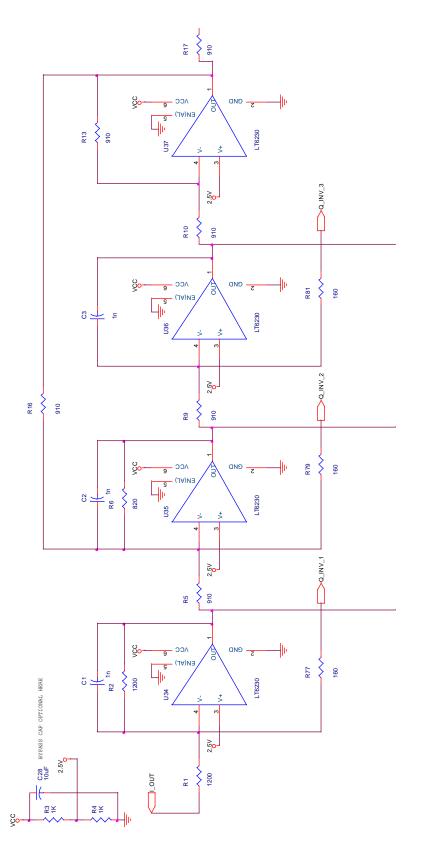

| FIGURE B.5 – Stage 1 and 2 of the I Channel for the Complex Filter                | 62 |

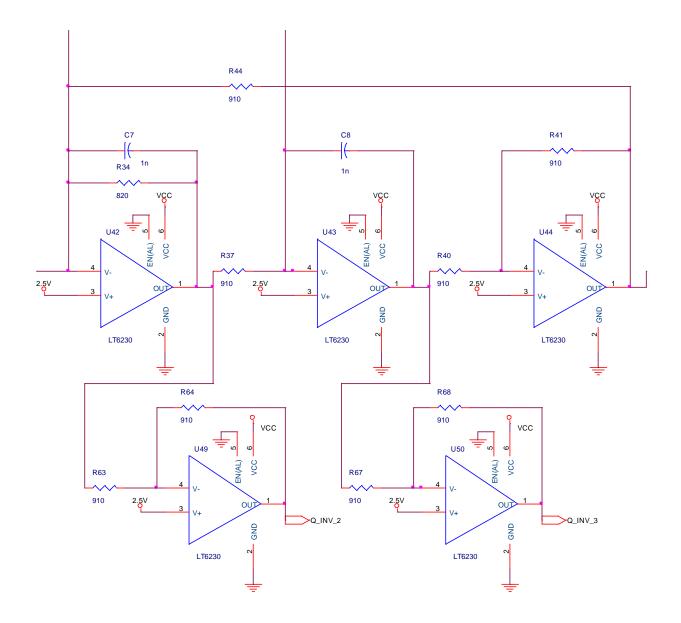

| FIGURE B.6 – Stage 2 of the Q Channel for the Complex Filter                      | 63 |

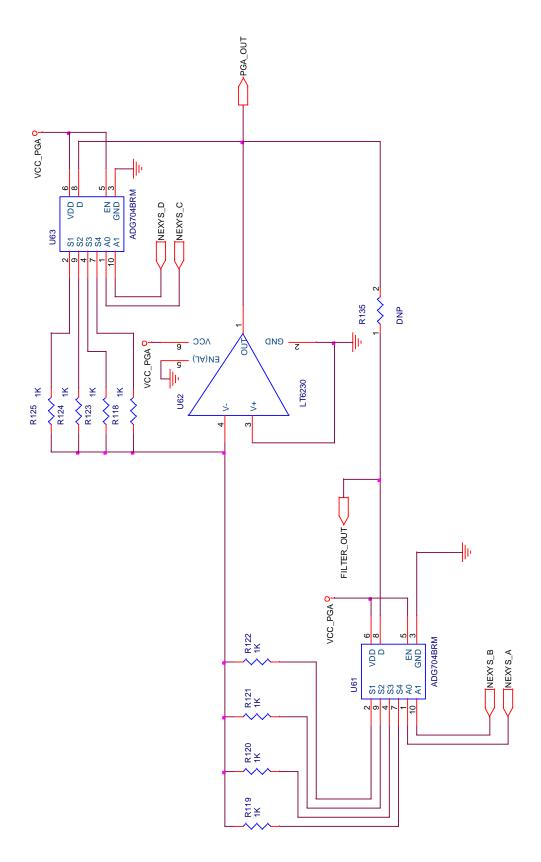

| FIGURE B.7 – PGA Schematic                                                        | 64 |

| FIGURE B.8 – ADC Interface Schematic                                              | 65 |

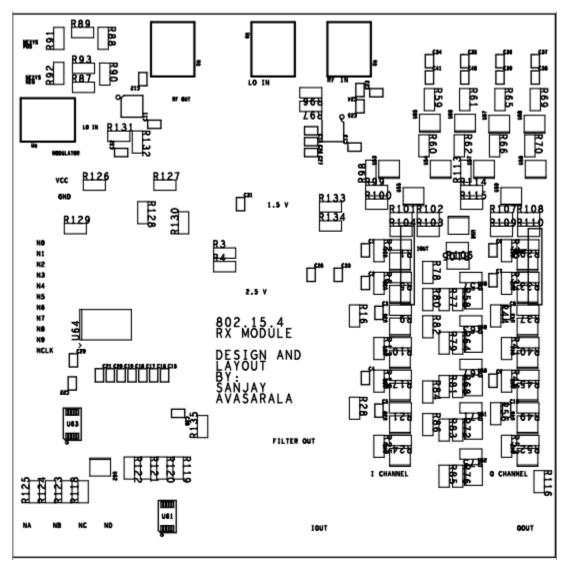

| FIGURE C.1 – Top silkscreen                                                       | 66 |

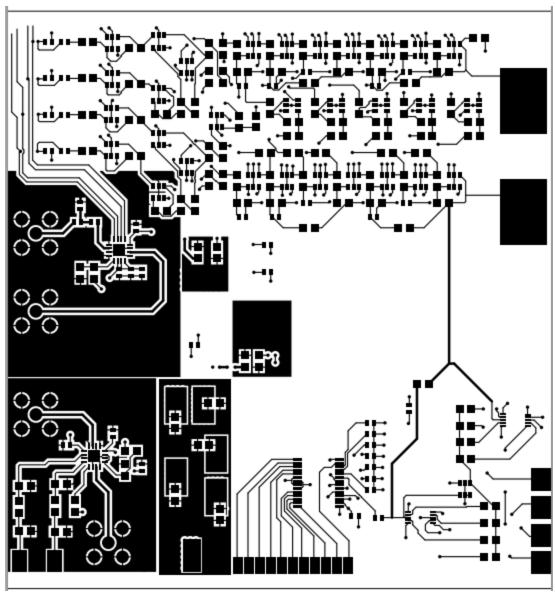

| FIGURE C.2 – Top copper layer                                                     | 67 |

# ABSTRACT

This project involves the design, building, and testing of a low intermediate frequency 802.15.4 receiver that uses an FPGA to perform final demodulation to baseband.

# Section 1. INTRODUCTION

This project will demonstrate the successful demodulation of data using a low intermediate frequency (IF) digital radio receiver. A separate modulation circuit will provide the system with BPSK modulated data at 956 MHz and an RF down converter circuit will supply the receiver with the low IF signal which contains both in phase and quadrature components.

The analog section of the receiver includes a complex band pass filter with capability of tuning both the center frequency as well as the filter bandwidth, a programmable gain amplifier (PGA), and an analog to digital converter (ADC). A digital signal processor (DSP) or field programmable gate array (FPGA) provides the final demodulation of the IF data down to base band.

The product in question is an 802.15.4 compatible receiver module that utilizes a DSP/FPGA to perform final demodulation to baseband of a low-IF signal. This type of device is not intended for consumer end markets, but rather for companies who design consumer electronics. The 802.15.4 standard is intended for low power and low data rate applications such as interfacing house hold appliances to a central node and other daily, short-range wireless applications. The module is only a receiver, and thus can either be used in conjunction with a transmitter to form a transceiver, or as a stand-alone module in applications that call for only receiving data. Because the module uses a DSP and has several features described in the specifications document, the receiver is highly customizable and immune to certain levels of interference from noise and adjacent channels. The module also does not contain any clock extraction devices for synchronization since that is beyond the scope of this project.

# Section 2. BACKGROUND TECHNOLOGY REVIEW

Note that this section offers the technology background at the highest possible system level. The theory of each sub-system operations is presented in their respective sections.

This project entails the design and creation of a low IF digital radio receiver. Currently, most receivers use three common system architectures: Direct Conversion or Zero IF (ZIF), low IF or high IF. Direct quantization and signal processing at RF frequencies is not practical and thus not used. The following describes the relative advantages and disadvantages of each architecture.

#### (Direct Conversion, or Zero IF (ZIF))

### Advantages

A. Circuit simplicity

Since direct conversion avoids the use of an IF, external IF filtering circuitry is not required. Thus, a baseband circuit has a relatively smaller area and a lower cost.

# Disadvantages

A. LO Leakage

It is possible for the LO signal to leak into the input to the RF down converter (which is as simple as just a mixer. See Fig 1.1 below).

Figure 1.1 – Leakage in a mixer.

Because the LO leaks into the input of the mixer, a DC value is present at the output (two sinusoidal waves multiplied together produce a DC term). If a high gain amplifier is present after the RF down conversion stage, it will rail with the DC offset term present. This can happen for both static self mixing and dynamic self mixing. AC coupling cannot solve this problem due to

significant levels of low frequency and DC content associated with the message signal. It is possible to design filters that account for this problem, although to do so is rather difficult.

B. Noise

A type of noise that is inversely proportional to frequency (known as 1/f noise) will be present in circuits that use active devices. A receiver that processes a signal at baseband is more susceptible to this type of noise.

# High IF

## Advantages

A. DC offset nulling

A high IF system can get rid of the DC offset problem which the baseband scheme faces by using AC coupling.

B. Image Reject

Unless proper filtering is performed at high frequencies, an image signal will be present along with the wanted signal. The image signal is any spectral power located at a frequency deviation which is the same as the wanted signal away from the local oscillator. However, the image is located on the opposite side of the carrier relative to the wanted signal. Image rejection techniques employed at high IF (using surface acoustic wave or SAW filters) is highly effective and thus high IF is used where high image rejection is needed.

## Disadvantages

A. Additional circuitry

Circuits that use a high IF require two phase locked loop (PLL) circuits to convert the signal to a low enough frequency for analog to digital conversion. There are digital signal processors (DSP) available that can handle the high frequencies of high IF (typically in the hundreds of MHz), however the amount of power and processing strength needed for this will increase the cost and current consumption. The additional circuitry needed for the high IF circuit will also make the receiver more expensive.

#### B. Bulky expensive components

As mentioned before, a SAW filter is required for filtering. A SAW filter is a bulky component that is impossible to integrate into a chip. This is the single biggest drawback to this otherwise excellent architecture.

## Low IF

#### Advantages

A. DC offset problem doesn't exist

A low IF system can ignore DC offsets in the devices by simply AC coupling the stages.

B. Circuit simplicity

As opposed to the high IF schemes, a low IF system only requires one PLL to down convert the RF signal to a low IF. The circuit requires no additional frequency conversion since a DSP/FPGA can easily handle the frequencies associated with low IF (hundreds of KHz to ones or tens of MHz).

#### Disadvantages

A. Image reject

Image rejection at a low IF is substantially harder to realize than at a high IF. It is possible, however, to use complex bandpass filters for image rejection. Amplitude and phase matching of components ultimately places a practical limit on image rejection.

## B. Data rate constraints

Another disadvantage is that the system is most suited for low data rate (low bandwidth) systems. High bandwidth systems such as Wi-Fi are not feasible with a low IF architecture, however, low data rate systems such as Zigbee and Bluetooth are.

### **Digital System Advantages**

A digital signal processor (DSP) will perform the final demodulation of the signal to baseband data. Using a DSP and mixed signal processing carries several advantages over a pure analog system.

A. Filtering

Although the radio filters the signal before A/D conversion is employed (see Figure 3), higher order filters can be realized more easily in the digital realm as opposed to analog. The only limitations to this are processing speed and memory space. One must ensure that the signal strength is optimized for quantization since signal to noise ratio degrades for lower amplitudes due to quantization error.

B. Customizable

As opposed to an analog system in which individual hardware component values are changed should any parameter change happen, a digital system allows for easy customization through the use of coding.

#### C. Improved image rejection

If the in phase and quadrature components are maintained through the receive chain, one can use a DSP to improve the image rejection quality. Image rejection relies on matched amplitude and phases in circuitry and a DSP can account for variations in the aforementioned.

# Section 3. DESIGN REQUIREMENTS AND SPECIFICATIONS

Note that the following table is derived from the EE 463 Senior Project preliminary report. The table contains both marketing requirements and engineering specifications. The following list provides a brief description of what the module must accomplish:

- Properly demodulate BPSK modulated data at 250 kbps

- Provide image rejection

- Provide a PGA

- Output data to a computer for easy visibility

| Marketing<br>Dequinements  | Engineering                                                                                                                                                       | Justification                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Requirements         2,3,4 | Specifications<br>Frequency of operation: 950 – 956 MHz,<br>capable of 250Kbps data rate. Receiver<br>must use BPSK modulation with a<br>channel spacing of 2MHz. | Must conform to the Zigbee standard<br>defined frequency allocation and bit rate<br>parameters. These specifications are taken<br>directly from the 802.15.4 standard. Note<br>that spread spectrum techniques will NOT<br>be used in this receiver. [5]                                                                                                       |

| 1                          | Use a low IF of half the channel spacing<br>of 2MHz or 1 MHz.                                                                                                     | For low data rate systems such as the<br>Zigbee standard, a low IF is desirable. A<br>low IF architecture typically costs less than<br>other types. 1 MHz is used such that the<br>adjacent channel is the only image present<br>at IF. Any other IF used over 1 MHz will<br>contain alternate channel images which<br>will be substantially harder to reject. |

| 4                          | Adjacent and alternate channel rejections<br>of 20 and 50 dB respectively.                                                                                        | The adjacent and alternate channels are<br>sometimes larger than the wanted signal.<br>Therefore these have to be rejected to<br>avoid interference (known as image<br>rejection particularly for low IF<br>architectures). These particular values are<br>more than the specified values in the<br>802.15.4 standard                                          |

| 4   | ADC resolution and sampling rate:<br>4 bits and a sampling frequency of<br>greater than the Nyquist frequency of<br>twice the bandwidth (4 MHz). Therefore<br>the sampling rate is greater than 4 MHz. | The ADC resolution is determined by the<br>SNR required by the DSP to demodulate<br>the signal to a BER of 1E-4. We assume 20<br>dB for this so that 4 bits is adequate<br>(4x6+1.78). The preceding equation is a<br>rule of thumb equation that relates signal to<br>noise ratio with a given bit resolution.<br>Excess bits will serve as headroom or<br>margin for the AGC. The sampling rate is<br>determined by the IF frequency and the<br>signal BW. |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Use an appropriate filter to achieve the<br>channel selectivity without having the<br>group delay distortion affect the BER of<br>the receiver.                                                        | For a distortion less system, a circuit<br>should have a constant or small group<br>delay variation in the passband.                                                                                                                                                                                                                                                                                                                                         |

| 4   | Use an automatic gain control system:<br>Gain control range of 50 dB                                                                                                                                   | Near/far problems and multipath will cause<br>the signal strength to vary.<br>The sensitivity of BPSK of 250Kbps<br>=-110dBm at RF. Assuming 30dB gain in<br>RF, the sensitivity at IF will be -80dBm. A<br>maximum IF signal corresponds to -20dBm<br>at RF or +10 dBm at IF. For this variation<br>of the signal the level of the signal at the<br>ADC input should be roughly constant to<br>maximize the ADC capabilities.                               |

| 2,3 | User interface                                                                                                                                                                                         | The user must physically view the<br>demodulated data stream to verify proper<br>transmission. MATLAB or LabVIEW can<br>interface with the receiver and display the<br>received data. A Logic Analyzer can also<br>export data to an excel spreadsheet for<br>analysis.                                                                                                                                                                                      |

| 2,3 | Tunable IF bandwidth. NOTE: Aftersome research, it was determined that atunable image reject filter was beyondthe scope of this project and istherefore not going to be implemented.                   | To accommodate for different bandwidths<br>associated with different data rates, a<br>tunable filter is required. The circuit<br>contains this feature for a proof of concept.                                                                                                                                                                                                                                                                               |

| 4   | A bit error rate (BER) of 1E-4 at<br>sensitivity. This in turn corresponds to a<br>packet error rate of 1% for 250 Kbps for<br>BPSK.                                                                   | This is specified in IEEE 802.15.4 [5]                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1               | Research and development costs.                                                                   | The total cost for R&D should not exceed \$450.00                                                                                                                                                                              |  |

|-----------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |                                                                                                   | \$450.00                                                                                                                                                                                                                       |  |

| 5               | PCB on which circuit is built should not<br>exceed 60 square inches or use more than<br>2 layers. | The PCB on which this circuit is built will<br>meet these specs to conform to<br>4PCB.com's academic board<br>manufacturing option. Evaluation kits for<br>the DSP, RF and TX circuitry will be<br>sourced from manufacturers. |  |

| Marketing Req   | uirements                                                                                         |                                                                                                                                                                                                                                |  |

| 1. Afforda      | •                                                                                                 |                                                                                                                                                                                                                                |  |

| 2. Easy to use  |                                                                                                   |                                                                                                                                                                                                                                |  |

| 3. Customizable |                                                                                                   |                                                                                                                                                                                                                                |  |

| 4. Seamles      | ss data transfer                                                                                  |                                                                                                                                                                                                                                |  |

| 5. Compac       | xt                                                                                                |                                                                                                                                                                                                                                |  |

| 21 Compu        | Table 2.1 Sugtan gracifications                                                                   |                                                                                                                                                                                                                                |  |

Table 3.1 – System specifications and requirements

It must be noted at this point that, although the module is meant to be a low IF receiver, a transmitter and a down converter will need to be constructed as well to provide the BPSK low IF modulated data.

# Section 4. DESIGN ALTERNATIVES

## IF Architecture

The only other alternatives for a receiver architecture include the aforementioned high IF and zero IF architectures. The disadvantages and advantages of each were discussed previously and it was determined that a low IF architecture would be the most feasible for this project given the allotted time and resources.

## Analog vs. Digital

The alternative to using DSP/FPGA for final demodulation would obviously be using analog demodulation. However, this requires the extensive use of analog filters and other sub-system components including hard limiters and additional down converters that complicate the project and add to the overall cost. A DSP/FPGA can perform final demodulation using simple coding techniques and is highly customizable and easy to change.

# DSP vs. µProcessor vs. FPGA

The alternative to using a DSP would be using a microprocessor to perform demodulation to baseband. This technique will only work if the microprocessor has sufficient memory and processing capabilities to sample and demodulate a signal (1 MHz for the project). The microprocessor needs to be able to buffer many data samples (to be determined) and possibly generate its own pseudo random binary sequence to avoid the use of two microprocessors which would require a digital PLL. The last alternative is to use an FPGA and VHDL to carry out final demodulation. The advantage of using this method is that one has direct control over any of the clocks involved in the system and can therefore alter timing constraints accordingly and with precision.

#### PCB vs. Bread boarding

Although bread boarding the system may offer more customizability and be less prone to error since any mistakes can easily be made, the system has enough components to the point where bread boarding the system may not be feasible. Creating a layout and designing the circuit on a PCB is much more compact and clean (especially for RF circuitry).

# Section 5. PROJECT DESIGN

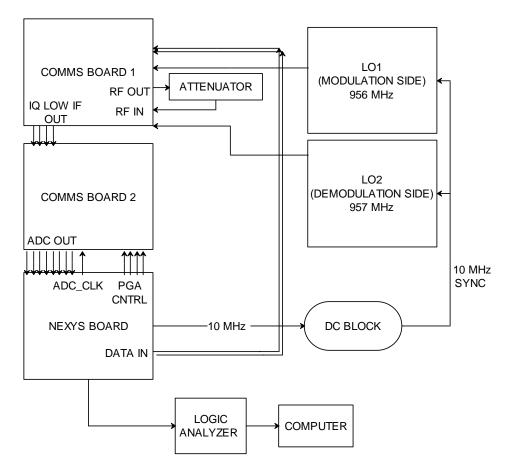

A high level block diagram of the system is shown below in Figure 5.1. Table 5.1 describes the function of each block.

Figure 5.1. – Block diagram of the entire system.

| BLOCK                                     | INPUT                            | OUTPUT                               | FUNCTION                                                                                                                                               |

|-------------------------------------------|----------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modulation<br>Circuitry                   | 250 Kbps digital<br>data stream. | Modulated 956 MHz<br>BPSK RF signal. | The modulation circuitry is what<br>will provide the BPSK modulated<br>data signal to the radio receiver at<br>956 MHz.                                |

| RF Down<br>conversion<br>circuitry        | RF 900 MHz signal                | Low IF Signal (1 MHz)                | The RF down converter will convert<br>the modulated frequency to the low<br>intermediate frequency for signal<br>processing.                           |

| BPF (Band pass<br>image reject<br>filter) | IF Signal                        | Filtered IF Signal                   | The band pass filter will only allow<br>the wanted signal in the pass band<br>and attenuate all other signals. Note<br>that this filter is complex I/Q |

| PGA               | Filtered IF Signal  | Filtered IF Signal with     | The PGA is needed for the AGC.       |

|-------------------|---------------------|-----------------------------|--------------------------------------|

| (Programmable     |                     | gain                        |                                      |

| Gain Amplifier)   |                     |                             |                                      |

|                   |                     |                             |                                      |

|                   |                     |                             |                                      |

| ADC (Analog to    | Filtered IF Signal  | Quantized output            | The ADC will convert the analog      |

| Digital           | with gain           |                             | signal to a digital value which will |

| converter)        |                     |                             | be processed by the DSP/FPGA.        |

|                   |                     |                             | The ADC resolution will depend on    |

|                   |                     |                             | the SNR requirements of the          |

|                   |                     |                             | 802.15.4 system.                     |

| CLK1              | No Input            | 5 MHz                       | The sampling rate of the ADC is      |

|                   |                     |                             | determined by this clock.            |

| CLK2              | No Input            | 50 MHz                      | Internally generated DSP/FPGA        |

|                   |                     |                             | clock.                               |

| AGC (Automatic    | DSP output signal   | Logic bus signal            | The AGC will control the PGA. The    |

| gain control)     | (logic bus)         |                             | AGC is controlled by the             |

|                   |                     |                             | DSP/FPGA.                            |

|                   |                     |                             |                                      |

| DSP (Digital      | Quantized IF signal | DSP output logic bus.       | The DSP will perform the final       |

| signal processor. |                     | USB (tentative).            | demodulation to baseband. The DSP    |

| Can be replaced   |                     | Logic analyzer (tentative). | will have a user interface (a        |

| by an FPGA)       |                     |                             | computer) such that the user can     |

|                   |                     |                             | view the demodulated bit stream for  |

|                   |                     |                             | test purposes. An FPGA can take      |

|                   |                     |                             | the place of a DSP.                  |

#### Sub-Section 1. Image Reject Filter Analysis and Design

One of the biggest problems associated with a low IF architecture is the presence of an image at the IF. An image is present due to the mathematical properties of frequency shifting when down converting. Although the image signal will be present in the negative frequencies, in all practical applications these frequencies are 'folded over' such that the image signal will indeed be present at the IF. Therefore, proper filtering must be performed to remove the image at the 'negative' frequencies. This can be done by positively shifting the magnitude response of a low pass filter such that no negative frequencies will be present in the pass band (the magnitude response of a LPF is symmetric about the y axis and therefore negative frequencies will be in the pass band). A shift in the frequency domain corresponds to multiplication by a complex number in the time domain. Hence, the type of filter used can be called a complex bandpass filter. Analysis of an IQ complex bandpass filter is shown below.

Figure 5.1.1. – Simplified block diagram of an image reject system.

First, we shall observe how an image signal is rejected using mathematical analysis. The RF Input contains two signals of interest for this analysis: the wanted signal located at  $\omega_c$  and the image signal located at  $\omega_{IM}$ . Note that for a  $\omega_{LO}$  that is greater than the wanted signal:

$$\omega_{LO} - \omega_C = \omega_{IF}$$

and

$$\omega_{LO} + \omega_{IF} = \omega_{IM}$$

The frequencies mentioned are all at RF frequencies except for  $\omega_{IF}$ . Without loss of generality, we can assume that the image and wanted signals are simple sinusoids with different amplitudes. Thus,

Message Signal =  $Acos(\omega_C t)$ Image Signal =  $Bcos(\omega_{IM} t)$  Using an IQ down-converter, the I channel yields (after being mixed by  $\cos(\omega_{LO})$ ):

$$\cos(\omega_{LO}t) * [A\cos(\omega_{C}t) + B\cos(\omega_{IM}t)] =$$

$$A\left(\cos\left((\omega_{LO} - \omega_{C})t\right) + \cos\left((\omega_{LO} + \omega_{C})t\right)\right) + B\left(\cos\left((\omega_{LO} - \omega_{IM})t\right) + \cos\left((\omega_{LO} + \omega_{IM})t\right)\right)$$

and neglecting the higher RF frequencies due to low pass filtering, we arrive at:

$$Acos((\omega_{LO} - \omega_C)t) + Bcos((\omega_{LO} - \omega_{IM})t) =$$

$$Acos(\omega_{IF}t) + Bcos(-\omega_{IF}t)$$

The Q channel yields (after being mixed by  $sin(\omega_{LO})$ ):

$$sin(\omega_{LO}t)[Acos(\omega_{C}t) + Bcos(\omega_{IM}t)] = A\left(sin((\omega_{LO} + \omega_{C})t) + sin((\omega_{LO} - \omega_{C})t)\right) + B\left(sin((\omega_{LO} + \omega_{IM})t) + sin((\omega_{LO} - \omega_{IM})t)\right)$$

and neglecting the high RF frequencies, the input to the phase shifter is:

$$Asin((\omega_{LO} - \omega_C)t) + Bsin((\omega_{LO} - \omega_{IM})t)$$

Note that the divide by 2 that occurs due to trigonometric identities is left out for simplicity. Now, since  $\omega_{LO} - \omega_{IM}$  is a negative frequency, or  $-\omega_{IF}$ , we can rewrite the above expression as:

$$Asin((\omega_{LO} - \omega_{C})t) - Bsin((\omega_{IM} - \omega_{LO})t) =$$

$$Asin(\omega_{IF}t) - Bsin(\omega_{IF}t)$$

Due to the 90 phase shift in the Q channel, the input to the summer is:

$$Asin\left(\omega_{IF}t + \frac{\pi}{2}\right) - Bsin\left(\omega_{IF}t + \frac{\pi}{2}\right) = Acos(\omega_{IF}t) - Bcos(\omega_{IF}t)$$

The output of the summer is:

$$Acos(\omega_{IF}t) + Bcos(\omega_{IF}t) + Acos(\omega_{IF}t) - Bcos(\omega_{IF}t) = Acos(\omega_{IF}t)$$

Observe that the image signal, which had an amplitude of B is now completely gone. This analysis also applies to modulated signals and images at these frequencies.

This type of image reject system can be realized using two cross coupled low pass filters. Note that the 90 degrees phase shift of the I channel is simply the Q channel. In other words, the Q channel shifts the I channel by the required 90 degrees, and feeding the Q channel into a filter along with the I channel will result in the desired output. Analysis of this filter is shown below.

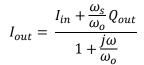

We first start with the simple low pass transfer function:

$$H(w) = \frac{1}{1 + \frac{j\omega}{\omega_o}}$$

The magnitude response of this TF resembles:

Figure 5.1.2. – Magnitude response of a simple rudimentary low pass filter

We saw how, in the previous analysis, the image signal was located in the negative frequency range. Thus, to eliminate any 'negative' frequencies, we can shift the magnitude response to the right. This will result in a new transfer function:

$$H(w) = \frac{1}{1 + \frac{j(\omega - \omega_s)}{\omega_o}}$$

where  $\omega_s$  is the shifted frequency. Applying this transfer function to only the I channel (for now) and after cross multiplying, we arrive at:

$$I_{in} = I_{out} + \frac{j\omega}{\omega_o}I_{out} - \frac{j\omega_s}{\omega_o}I_{out}$$

where  $I_{out}$  is the output of the LPF. Note that the coefficient of the last  $I_{out}$  term is a 90 degree shifted scalar multiple of  $I_{out}$ . From before, we know that the Q channel is the I channel positively shifted by 90 degrees, or j\*I. Therefore, any signal processing performed on the Q channel that is identical to the I channel will result in an output on the Q channel that is still j\*I. Therefore it is safe to represent  $I_{out}$  as  $-jQ_{out}$ . Replacing this in the above equation results in:

$$I_{in} = I_{out} + \frac{j\omega}{\omega_o} I_{out} - \frac{\omega_s}{\omega_o} Q_{out}$$

Rearranging terms results in:

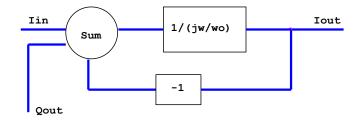

This transfer function can be realized using the following block diagram (the Q channel gain is left out for simplicity):

Figure 5.1.3. – Block diagram of an image reject transfer function.

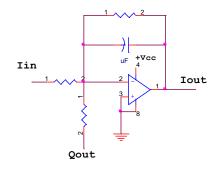

This diagram is essentially an integrator with a simple negative feedback loop. One can implement this block diagram using the following circuit.

Figure 5.1.4. – Practical realization of a simple image reject filter.

Since the entire system must be symmetric to maintain properly matched I and Q outputs, the system is cross coupled as seen in Figure 5.1.5. We can now derive what the exact transfer function of the system is and show how it resembles the shifted frequency transfer function.

Figure 5.1.5. – A more detailed look at a simple image reject filter.

We can use nodal analysis for the I channel op-amp and arrive at the equation:

$$\frac{I_{in}}{R_1} - \frac{Q_{out}}{R_3} = -I_{out}(\frac{1}{R_6} + sC_2)$$

The negative term for  $Q_{out}$  is present due to the inverter (E1) at the output of the filter on the Q channel. This inverter is here due to mathematical reasons. If it were not present, the passband would be shifted negatively as opposed to positively. Replacing s with  $j\omega$  and solving for  $I_{out}$  yields:

$$I_{out} = \frac{\left(-\frac{R_6 I_{in}}{R_1} + \frac{R_6 Q_{out}}{R_3}\right)}{1 + \frac{j\omega}{\omega_o}}$$

where

$$\omega_o = \frac{1}{R_6 C_2}$$

This transfer function is almost identical to the shifted frequency transfer function we were trying to achieve with the exception of a scalar coefficient for both  $I_{in}$  and  $Q_{out}$ . The polarity does not matter since it will result in a 180 degrees phase shift for both channels due to symmetry and thus not affect the frequency response. The  $Q_{out}$  coefficient must be set to equal  $\frac{\omega_s}{\omega_o}$  derived earlier. The values present in the schematic above are for a shift frequency of 1 MHz with the low pass filter configured for 150KHz. Simulating these values in LTSpice yields the following magnitude response shown in Figure 5.1.6.

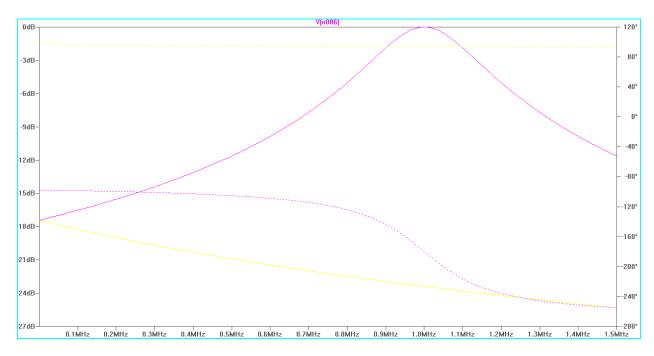

Figure 5.1.6. – Magnitude response of a simple image reject filter.

The center frequency shown in Figure 5.1.6 is indeed 1 MHz. The yellow trace on the response is the response of the frequencies at which the image would appear. Since LTSpice is incapable of plotting negative frequencies, the Q channel phase is reversed by 180 degrees such that the response is shifted left and not right. This enables us to observe the image suppression since the magnitude response has even symmetry about the magnitude axis.

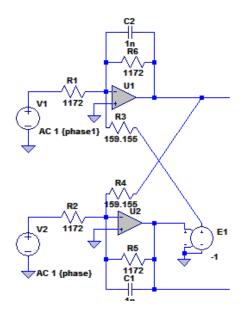

This technique of applying the output of the Q channel to the input of any integrator in the I channel will always result in a shifted frequency if all resistors are chosen accordingly. Thus, one can cascade any amount of integrators in the receive chain and achieve image rejection if the integrators are all cross coupled. We can implement a higher order filter using a cross coupled Tow Thomas bi-quad filter consisting of two complex conjugate pole pairs and a real pole. Figure 5.1.7 shows this implementation.

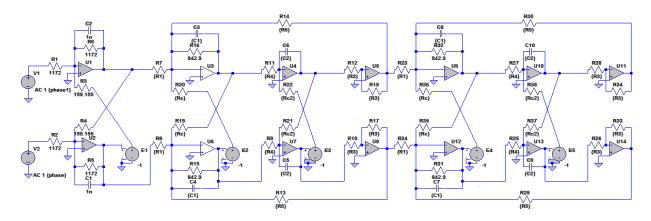

Figure 5.1.7. – Ideal image reject filter using a fifth order Butterworth low pass filter configuration.

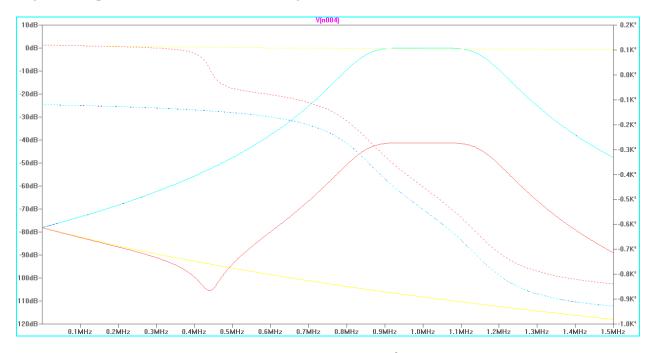

This particular filter is configured to operate as a  $5^{\text{th}}$  order Butterworth low pass filter if no coupling is present. The values for the components were generated using a program called Filter Wiz Pro. The magnitude response for this filter is shown in Figure 5.1.8.

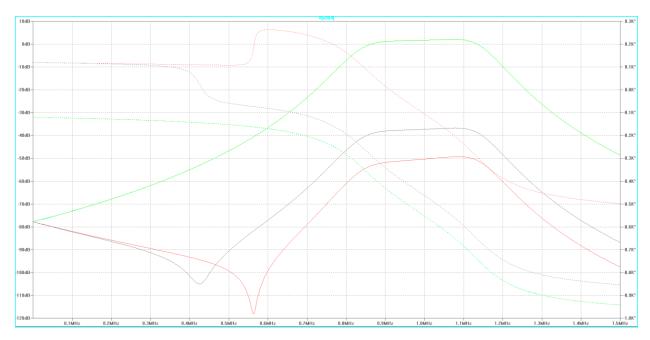

Figure 5.1.8. – Magnitude response of a 5<sup>th</sup> order BPF (ideal).

The turquoise response occurs when the filter is configured with a perfect 90 degree difference between the I and Q channels. The red trace indicates what happens if there is a 1 degree offset present between the I and Q channels. The yellow trace once again shows us the suppression of the image. The image rejection is well above the 20 and 50 dB attenuation given by the specifications. Both the I and Q channel outputs yield similar transfer characteristics. To observe the group delay in the passband, we take the derivate of the phase with respect to frequency and divide by 2\*pi.

Figure 5.1.9. – Magnitude response of a 5<sup>th</sup> order BPF with group delay (ideal).

The dotted line in Figure 5.1.9 indicates the group delay in the passband. The maximum group delay is  $4.26 \ \mu$ s. If we use standard resistor values and non-ideal op-amps with an open loop gain of 5.2K and a GBWP of 100MHz, the magnitude response is as follows:

Figure 5.1.10. – Magnitude response of a 5<sup>th</sup> order BPF (non-ideal).

The image (maroon) in Figure 5.1.10 is not as suppressed using this configuration.

For the receiver, the LT6230 op amp from Linear Technologies was chosen due to its high gain bandwidth product and fast slew rate. As this design was intended for a single supply design at 5V, the circuit was redrawn with the LT6230 and proper referencing to a common mode voltage (CMV) of 2.5V. Figure 5.1.11 shows the complete schematic with proper value components. The inverters have been replaced with inverting op amps. In a fully differential design, the inverters would not be needed due to the inverting output terminals present in a differential op amp.

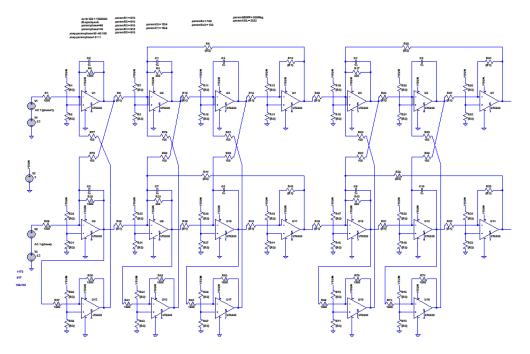

Figure 5.1.11. – Completed Filter Schematic. This is the schematic view in LTSpice.

The schematic created in OrCAD Capture can be viewed in Appendix B, Figure B.5 and Figure B.6 more clearly than the schematic in Figure 5.1.11.

# Sub-Section 2. BPSK Theory, Design, and Simulation

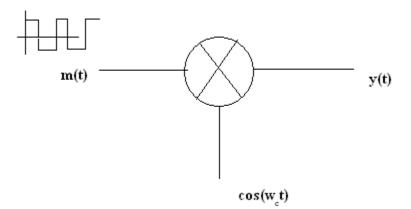

A BPSK system only has two possible states with a phase deviation of pi radians. A BPSK system can be modeled using a DSB-SC architecture with a binary message signal as shown below:

# Figure 5.2.1. – A BPSK system representation using a DSB-SC architecture.

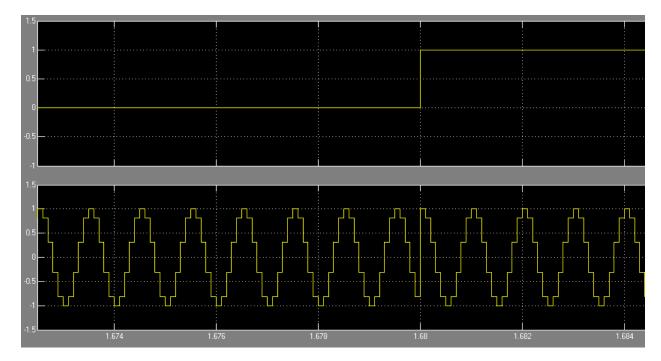

The output of the mixer is then  $y(t) = m(t) \cos(\omega_c t)$  or  $y(t) = \cos(\omega_c t + k(t))$  where k is either pi or 0 depending on the polarity of the message signal. Shown below is the waveform of the carrier signal with a modulated message signal. The simulation was performed in Simulink. The input data is not bipolar and the carrier is not smooth due to sampling limitations.

Figure 5.2.2. – Simulation showing the modulated signal. The phase changes when the message signal changes state.

To demodulate a BPSK signal down to a low IF, we can multiply the modulated signal by I and Q phased local oscillators. To down convert the signal to 1 MHz, we multiply by an LO which is 1MHz higher than the carrier frequency (high side LO injection):

$$\cos(\omega_{LO}t) * \cos(\omega_{c}t + k(t)) = \cos(\omega_{c+LO}t + k(t)) + \cos(\omega_{IF}t - k(t))$$

After image rejection and channel selection processing is performed at the IF, the signal is then down converted by mixing a sinusoid with the same frequency as the IF:

$$\cos(\omega_{IF}t) * \cos(\omega_{IF}t - k(t)) = \cos(k(t))$$

The signal is now demodulated. Higher frequencies are filtered out and are therefore neglected. A suitable filter for this system can be an integrate and dump filter which acts as a low pass filter. The down converted low IF signal is shown in Figure 5.2.3 below. High frequencies exist in the signal due to no filtering. Both the I and Q demodulation channels are shown.

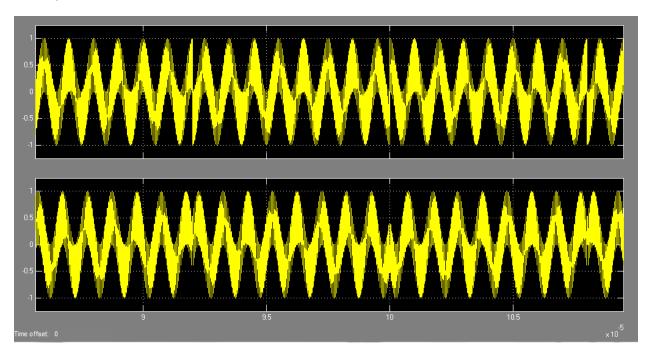

Figure 5.2.3. – Down converted low IF signal without filtering (both I and Q channels).

Figure 5.2.4 shows the final demodulated signal without filtering on the next page.

Figure 5.2.4. – Demodulated output signal (both I and Q channels).

The aforementioned signal capture is for a perfect channel. Figure 5.2.5 shows the demodulated wave with additive Gaussian noise.

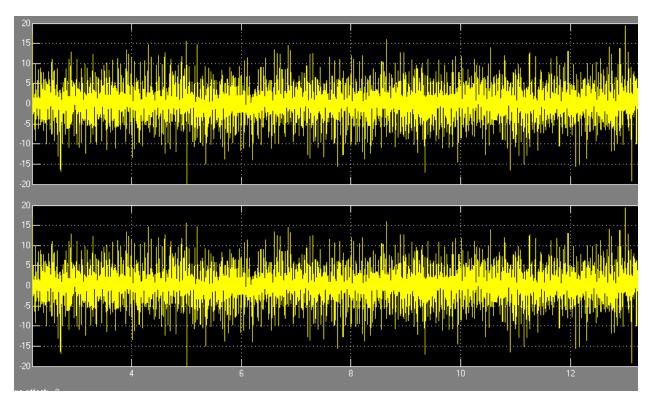

Figure 5.2.5. – Unfiltered demodulated signal with AWGN.

The previous figures were obtained using Simulink. The entire BPSK communication system was simulated in Simulink with the digital communications toolbox. The RF frequency, however, had to be reduced to 10 MHz due to computer processing limitations. The system sampling frequency had to be at least twice the Nyquist frequency, but to obtain more accurate results, a sampling frequency of 100 MHz was used. The first stage mixers, which represent the RF down converters, were set to 11 MHz. The second stage mixer, which will ultimately be performed using a DSP, was set to 1 MHz to down convert the final signal to baseband.

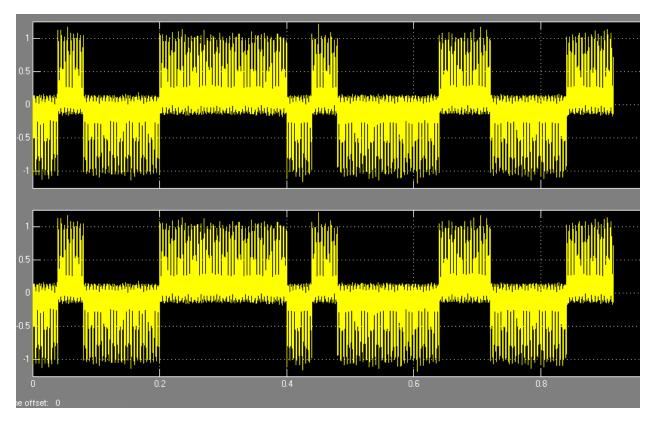

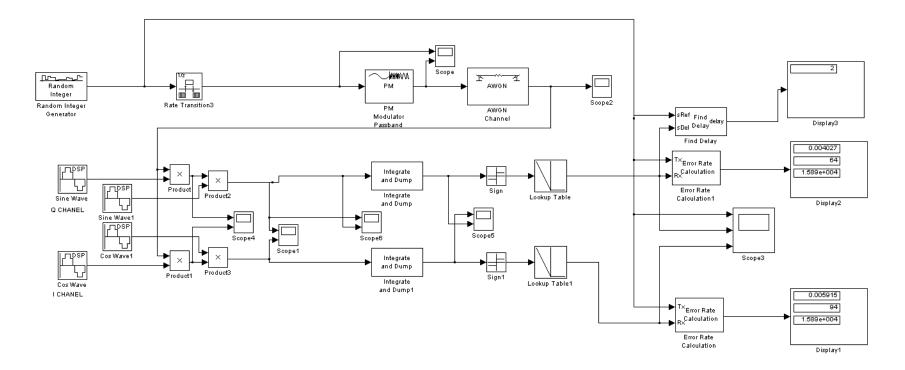

The system is shown in the next page with the error rate calculators present on the right side of the page. For the given test in the figure, Display2 represents the Q channel and Display1 represents the I channel. A total of 15890 bits were sent and the average bit errors was 77 which yields an average BER of .004971 or .49% for a given Eb/No value of 8.2 dB (Note that this value does not meet specifications. This is merely for an example case). An additive Gaussian noise channel was used to perform the simulation as can be seen in the following page. To extract data from the output of the integrate and dump filters, a sign block was used. A look up table had to be used only due to the fact that the sign block output values based upon three conditions and not two. All of the aforementioned functions can be readily implemented in a DPS/FPGA.

Figure 5.2.6. – Entire simulated BPSK system in Simulink.

#### Sub-Section 3. Modulator/Demodulator

The modulation circuitry for the receiver consisted of a basic attenuation network and the LT5568 IQ modulator. Since the system is a BPSK system, the quadrature component is not used on the modulation side and thus had its pins tied together. The inputs to the modulator are differential inputs, and therefore any data that is sent to the modulator must be in differential form. Failure to provide differential signaling can cause severe harmonic distortion. The CMV of the differential inputs to the modulator has to be .54V with a total voltage of less than 2.5V. Thus, an attenuation network was added to the input of the modulator to accommodate this specification. The modulator schematic can be seen in Appendix B, Figure B.1.

The output and LO are both connected to SMA cables for ease of testing and connectivity. The demodulation circuitry utilized the LT5575 IQ direct down conversion demodulator. This demodulator had two differential outputs for the I and Q channel. Since the filter is single ended, an instrumentation amplifier (IA) had to be utilized to convert from differential to single ended signaling. Also, all the LT6230 op amps in this design could not accept a voltage below 1.5V or above 4V. Therefore, the signals from the demodulator had to be AC coupled and centered around a reference voltage of 3V before being fed into the instrumentation amplifier. The IA was then referenced to the CMV of 2.5V which is the same CMV as the filter. Refer to Appendix B, Figure B.2 for the demodulator, Figure B.3 for the DC offset circuit, and Figure B.4 for the instrumentation amplifier.

## Sub-Section 4. Programmable Gain Amplifier

The specifications require that a PGA be used in the receive chain to correct for signal level changes caused by near-far problems. This is done by using two resistor banks controlled by multiplexer switches and an op-amp in the inverting configuration as can be seen in Appendix B, Figure B.7. The FPGA will control a switch array that adjusts the gain of the amplifier based upon which resistor is grounded. The FPGA will have an algorithm that checks the amplitude of the signal and will adjust the switches accordingly. An explanation of the PGA software can be found in Sub-Section 5, Software Component 7.

## Sub-Section 5. Software/VHDL

At this point, it must be noted that the Nexys-2 FPGA was selected as the software demodulation device. All VHDL code is listed in Appendix D.

The main blocks that need to be implemented in software include the following:

- 1) Interface to ADC the FPGA will have to interface with an ADC to input data.

- 2) A digital local oscillator/mixer this will perform the final demodulation to baseband. The local oscillator should have enough samples to offer reliable data.

- 3) Integrate and dump this block essentially acts as a low pass filter. Its main purpose is to accumulate enough data to provide the sign block information about the polarity of the signal.

- 4) Sign determiner (hard limiter) this block will output a logic '1' if the input is positive and '0' if negative. The output of this block will be a completely demodulated signal

- 5) Pseudo-Random Binary Sequence Generator random data will need to be generated by the DSP itself to avoid clock conflicts. If a different device were to be used, a digital PLL will have to be built which is beyond the scope of this project.

- 6) Sync Clock This is used to sync with the LO's.

- 7) PGA Feedback the FPGA will have to have a control system to determine the switch values for the PGA.

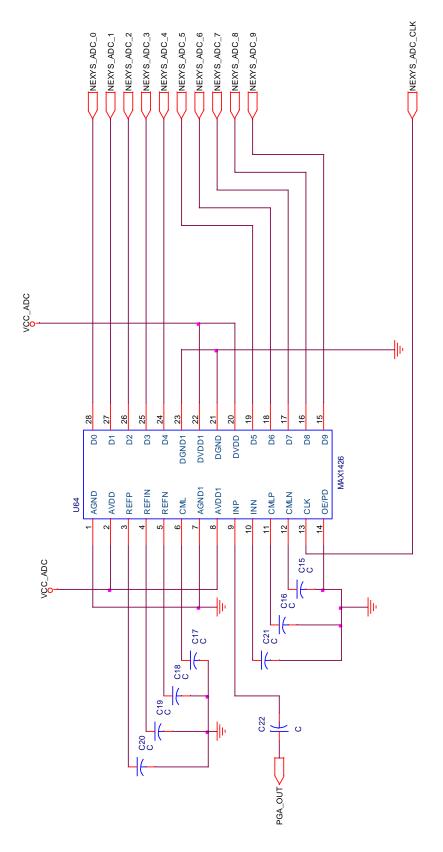

## Software Component 1. – ADC

The schematic for the ADC is shown in Appendix B, Figure B.8. The output of the PGA was AC coupled to the ADC for the easiest configuration. Although an ADC is a hardware component, it is the interface between the hardware and software realm of the project and therefore was included in the software section. The 10-bit output of the ADC was fed into the Nexys-2 board for processing. An output of the Nexys-2 board was used for the clock that was fed into the ADC. The ADC outputs parallel data for each falling edge of the clock (up to 20 MHz). The sample rate used for this project was 5 MHz. Data is delayed by 5 clock cycles and therefore has to be taken into consideration in software.

VHDL code lines 399 to 478 in Appendix D contain the ADC sampling process.

# Software Component 2. – Digital Oscillator Multiplication and Demodulation

After the data has been input into Nexys board, it needs to be multiplied by a local oscillator to shift the spectrum down to baseband. The sample rate of the ADC was set to 5 MHz. Because of this unique sampling frequency, no multiplication was necessary. This is due to the fact that separating a signal into 5 separate parts and multiplying those parts by their corresponding cosine terms results in only one of three states. Either the sample is passed through unaffected, inverted, or not passed through at all. After all the samples are complete, the data is pushed out of the process onto another set of signals for further processing.

VHDL code lines 399 to 478 in Appendix D contain the multiplication process.

# **Software Component 3. – Integration**

Since integration is essentially a Riemann sum of areas which can be composed of rectangle approximations, the integration step can be simplified to a basic addition operation with a constant scale factor. This can be further simplified by removing the scale factor because only the polarity is needed in the next step and not an actual quantitative value. Thus, no multiplication is present anywhere in the system which is highly efficient.

VHDL code lines 500 to 549 in Appendix D contain the integration process.

# Software Component 4. – Sign Determiner

This process is fairly straightforward. Since the data from the ADC and all subsequent data is in signed two's complement, only the most significant bit of the output of the integrator needs to be read to determine the polarity.

VHDL code lines 559 to 570 in Appendix D contain the sign determine process.

# Software Component 5. PSBR Signal Generator

A simple array and clock generator was used to create a PRBS sequence. Each time the allocated clock line pulled low, a signal was indexed and output differentially from the board.

VHDL code lines 321 to 382 in Appendix D contain the signal generation process.

# **Software Component 6: Sync Clock**

A 10 MHz clock had to be generated by the Nexys-2 board to synchronize it with the LO's since no clock extraction circuitry was used in this circuit. The LO's external sync inputs were 50 Ohm inputs and required an AC coupled signal. Therefore the output of the Nexys-2 board was fed to a 10 uF capacitor before the LO's. It must also be noted that it is impossible to generate a 10 MHz clock using falling edge triggered clock generation as done for the 5 MHz signal and the 250 KHz signal due to the fact that a total of 2.5 clock cycles is needed for every 1 half period of the sync clock. Therefore, Xilinx's IP Core generator had to be used to instantiate a clock divider 'black box' design. The VHDL code for this is proprietary and unknown. Only a component with a port map was provided. The clock signal was fed to the component and the 10 MHz clock was taken from the output.

VHDL code lines 296 to 302 in Appendix D contain the sync clock process

# **Software Component 7: PGA Feedback**

A software flow diagram of the PGA feedback algorithm can be found below in Figure 5.5.7.1.

Figure 5.5.7.1 - Software flow diagram for the PGA

A master *if* statement will reset the PGA and initialize a sample store and compare sequence if a counter hits a certain value. This process exists to avoid positive feedback in the system. The following scenario describes how positive feedback can occur. Suppose the signal is very weak, and the maximum gain of the PGA needs to be applied. Assuming the PGA has a gain of 1 initially, the ADC will read the signal, detect the peak, and apply the appropriate gain. Because the PGA is fed into the ADC, the ADC will now read the signal with the gain applied and assume that the signal is 'normal' in which case it will set the gain back down to 1. This will cause the signal to become small again, and the process will continue to oscillate. By resetting the PGA in the master if statement, this oscillation is avoided.

A state variable diagram is shown in Figure 5.5.7.2 for the different states a signal can exist in depending on its amplitude. Note that the bi directional paths exist because the PGA is reset upon each master *if* statement reset.

Figure 5.5.7.2. – State Variable Diagram

The gain steps of the PGA are clearly non-linear and not very ideal. However, the PGA in this project is more proof of concept than practical. Moreover, the gains can be adjusted by setting the resistor values accordingly and calibrating the code for the different states.

# Section 6. CONSTRUCTION AND INTEGRATION

Construction consisted of soldering all components onto the PCB's. No further soldering beyond this was necessary. Because all of the system was localized onto a board, there was no need for interconnects beyond the interface with the Nexys-2. Due to unforeseen circumstances, the modulator and demodulator QFN footprints used for the first revision were footprints taken from another part that had an identical footprint name. This footprint was of the incorrect size and therefore the components could not be soldered on due to the fact that RF components are near impossible to wire mod. A second revision had to be created with the correct footprint. However, since all of the complex filter components were still on the initial revision board, the two boards were jumped together to avoid the removal and replacement of all the components which would have been time consuming.

Wires were soldered onto the pads on the PCB to interface to the PMOD<sup>TM</sup> connectors on the Nexys-2 board directly. The sync clock output was sent to a separate prototype PCB with the 10uF capacitor to the LO's. The data output was a simple wire connection.

# Section 7. SUB SYSTEM TESTING

## Sub-System 1. Filter/Demodulator Testing

To properly characterize the filter, each individual chain had to be analyzed individually, and then analyzed when fully completed. At first, each filter was decoupled (I/Q cross coupling removed) and the input test signal was inserted directly at the inputs of the filters *with* the instrumentation amplifier and CMV shifting circuitry in place. This proved to be an erroneous test set up since the output data was clearly wrong (see Table 7.1.1 below). Thus, the input test signals had to be inserted at the inputs of the IA which yielded fairly accurate low pass transfer characteristics for a Butterworth response as can be seen in Table 7.1.2.

| F (Hz)   | Vpp input (V) | Vpp2 output (V) | Gain     | Gain<br>(dB) |

|----------|---------------|-----------------|----------|--------------|

| 1.00E+03 | 1E-45         | 0               | 0        | #NUM!        |

| 1.00E+04 | 0.5           | 0.5             | 1        | 0            |

| 5.00E+04 | 0.5           | 0.5             | 1        | 0            |

| 1.00E+05 | 0.62          | 0.58            | 0.935484 | -0.57927     |

| 1.10E+05 | 0.68          | 0.6             | 0.882353 | -1.08715     |

| 1.20E+05 | 0.72          | 0.62            | 0.861111 | -1.29882     |

| 1.30E+05 | 0.76          | 0.64            | 0.842105 | -1.49267     |

| 1.50E+05 | 0.84          | 0.6             | 0.714286 | -2.92256     |

| 1.60E+05 | 0.88          | 0.52            | 0.590909 | -4.56959     |

| 1.70E+05 | 0.9           | 0.5             | 0.555556 | -5.10545     |

| 1.80E+05 | 0.92          | 0.46            | 0.5      | -6.0206      |

| 1.90E+05 | 0.96          | 0.42            | 0.4375   | -7.18044     |

| 2.00E+05 | 0.96          | 0.38            | 0.395833 | -8.04975     |

| 2.20E+05 | 1             | 0.3             | 0.3      | -10.4576     |

| 2.40E+05 | 1.06          | 0.24            | 0.226415 | -12.9019     |

| 2.80E+05 | 1.12          | 0.112           | 0.1      | -20          |

| 3.00E+05 | 1.16          | 0.1             | 0.086207 | -21.2892     |

| 5.00E+05 | 1.26          | 0.08            | 0.063492 | -23.9456     |

Table 7.1.1 – Recorded values for the initial set up. The input voltage incorrectly varied with frequency. The voltage output to input *ratio* however, did yield a correct Butterworth response.

|          | Vpp   | Vpp2   |             |             | Vpp   | Vpp2   |             |             |

|----------|-------|--------|-------------|-------------|-------|--------|-------------|-------------|

|          | input | output | Gain(I-     |             | input | output | Gain(Q-     |             |

| F (Hz)   | (V)   | (V)    | Channel)    | Gain (dB)   | (V)   | (V)    | Chanel)     | Gain (dB)   |

| 1.00E+03 | 1.48  | 4.48   | 3.027027027 | 9.620325972 | 1.48  | 4.8    | 3.243243243 | 10.21959044 |

| 5.00E+03 | 1.48  | 4.32   | 2.918918919 | 9.304440628 | 1.48  | 4.72   | 3.189189189 | 10.07360566 |

| 1.00E+04 | 1.48  | 4.32   | 2.918918919 | 9.304440628 | 1.48  | 4.72   | 3.189189189 | 10.07360566 |

| 2.00E+04 | 1.48  | 4.32   | 2.918918919 | 9.304440628 | 1.48  | 4.72   | 3.189189189 | 10.07360566 |

| 5.00E+04 | 1.48  | 4.32   | 2.918918919 | 9.304440628 | 1.48  | 4.64   | 3.135135135 | 9.925125303 |

| 1.00E+05 | 1.48  | 3.92   | 2.648648649 | 8.460487033 | 1.48  | 4.48   | 3.027027027 | 9.620325972 |

| 1.10E+05 | 1.48  | 3.84   | 2.594594595 | 8.281390179 | 1.48  | 4.32   | 2.918918919 | 9.304440628 |

| 1.20E+05 | 1.48  | 3.68   | 2.486486486 | 7.911722066 | 1.48  | 4.16   | 2.810810811 | 8.976632305 |

| 1.30E+05 | 1.48  | 3.36   | 2.27027027  | 7.12155124  | 1.48  | 3.92   | 2.648648649 | 8.460487033 |

| 1.40E+05 | 1.48  | 3.2    | 2.162162162 | 6.697765258 | 1.48  | 3.6    | 2.432432432 | 7.720815707 |

| 1.50E+05 | 1.48  | 2.88   | 1.945945946 | 5.782615447 | 1.48  | 3.28   | 2.216216216 | 6.912242566 |

| 1.60E+05 | 1.48  | 2.56   | 1.72972973  | 4.759564998 | 1.48  | 3.04   | 2.054054054 | 6.252237364 |

| 1.80E+05 | 1.48  | 2      | 1.351351351 | 2.615365605 | 1.48  | 2.48   | 1.675675676 | 4.483799309 |

| 2.00E+05 | 1.48  | 1.36   | 0.918918919 | -0.73445614 | 1.48  | 1.62   | 1.094594595 | 0.785065983 |

| 2.50E+05 | 1.48  | 0.6    | 0.405405405 | -7.8422093  | 1.48  | 0.76   | 0.513513514 | -5.78896246 |

| 3.00E+05 | 1.48  | 0.27   | 0.182432432 | -14.7779590 | 1.48  | 0.36   | 0.243243243 | -12.2791842 |

| 5.00E+05 | 1.48  | 0.06   | 0.040540541 | -27.8422093 | 1.48  | 0.06   | 0.040540541 | -27.8422093 |

Table 7.1.2 – Recorded values for the individual filter test. The I channel filter results are on the left and the Q channel results are on the right.

**Figure 7.1.1 – Plotted responses for the filters.**

The filters, tested individually, yielded excellent test results and each channel had a 3 dB cut off frequency of 150Khz, which is precisely what the filters were designed for. However, there existed a slight gain difference between the I and Q channel suggesting the presence of I and Q channel mismatch. This mismatch may lead to degradation in image rejection (as can be seen later). To test the entire complex filter, the demodulator was needed. The demodulator was soldered on, and the RF and LO inputs were connected to two synchronized signal generators as can be seen in Figure 7.1.2 below.

Figure 7.1.2 – Test setup diagram.

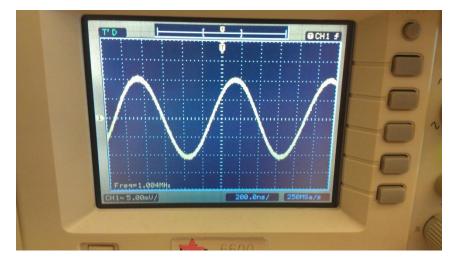

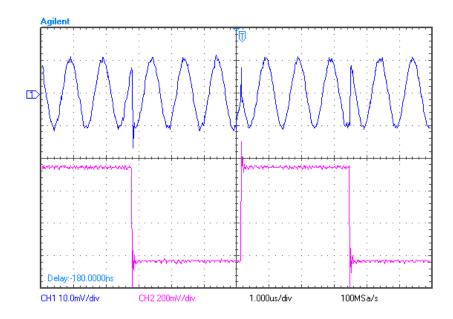

There exist two communications boards due to a manufacturing footprint error. The I and Q channels were simply jumped from one board to the other. Due to the low IF of 1 MHz, neither the line lengths nor the type of wire used was important. With the RF input set to 900 MHz and the LO set to 901 MHz, the output of the demodulator yielded a clean 1 MHz sinusoid on the I positive channel as can be seen in Figure 7.1.3 below.

Figure 7.1.3 – I channel demodulator output.

Figure 7.1.4 shows the I channel with both differential lines probed.

Figure 7.1.4 – I channel differential demodulator output.

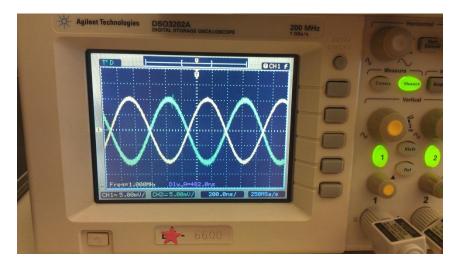

Figure 7.1.5 shows the I positive and Q positive channel. The delay between the two signals is 750 ns (or 250 ns) which is indeed a quarter of a wavelength (1us) indicating that the I and Q channels are 90 degrees apart.

Figure 7.1.5 – I and Q channel positive demodulator outputs. Notice how the signals are 90 degrees apart.

Agilent Technologis DSO3202A DITAL STORAGE OSCILLONCOPE PLANE P

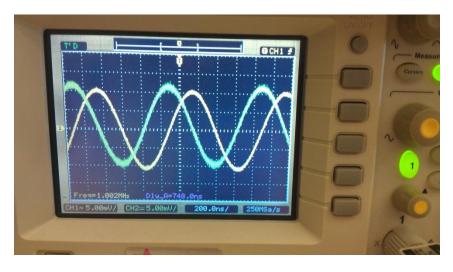

Figure 7.1.6 – Q channel differential demodulator output.

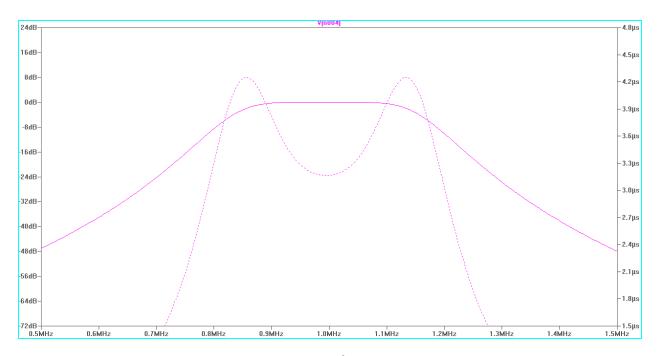

Because the inputs to the filter were completely complex, the full bandpass filter can be tested. The LO was varied from the positive sequence to the negative sequence to observe both the pass band response and the image response. Over 100 data points were taken, so Figure 7.1.3 only shows several samples.

| LO (MHz) | IF (MHz) | RF (MHz) | IF FILTER OUT<br>(Vpp) | IF FILTER OUT<br>(dB) |

|----------|----------|----------|------------------------|-----------------------|

| 901      | 1        | 900      | 1.841                  | 5.30107577            |

| 901.08   | 1.08     | 900      | 1.881                  | 5.487775911           |

| 901.42   | 1.42     | 900      | 0.084                  | -21.51441428          |

| 900.77   | 0.77     | 900      | 0.24                   | -12.39577517          |

| 899.5    | -0.5     | 900      | 0.001                  | -60                   |

| 898.8    | -1.2     | 900      | 0.108                  | -19.33152489          |

Table 7.1.3 – Table of 5 random samples chosen from the data collected from the complex filter.

# Finally, Figure 7.1.6 shows the Q channel output.

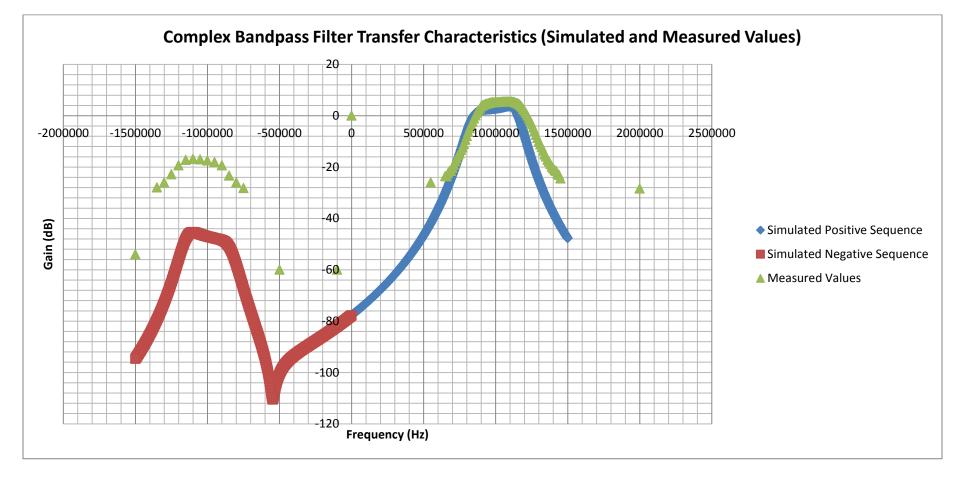

Figure 7.1.7 shows the filter response over the positive and negative sequence in addition to the simulated values.

Figure 7.1.7 – Complex filter response with positive and negative sequences shown.

The negative sequence response is rejected with a minimum attenuation of -22 dB. The negative sequence, when viewed with an oscilloscope, was indeed a 1 MHz signal. Therefore, it can be concluded that the image reject filter is working and successfully rejects an image located to the right of the local oscillator for high side LO injection. It must be noted that the image attenuation was not as simulated; this is due to I and Q channel phase offset and amplitude characteristics mismatch. However, this filter is still within specifications.

# Sub-System 2. - ADC Testing

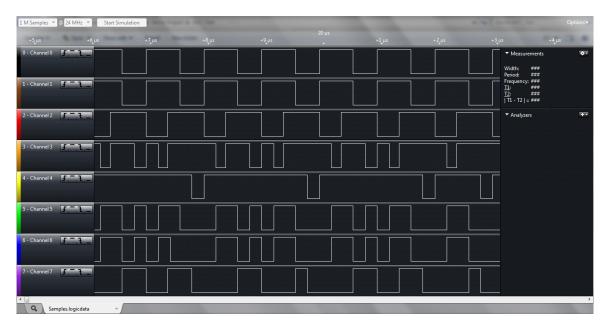

The ADC was first tested by simply feeding a 1 MHz signal into the ADC. A 5 MHz clock was fed to the ADC and the outputs were polled by a logic analyzer. The waveforms are shown in Figure 7.2.1.

Figure 7.2.1 – Logic Analyzer output with Channel 0 as the MSB. The analyzer only had 8 bits so the 2 least significant bits were left out of the test.

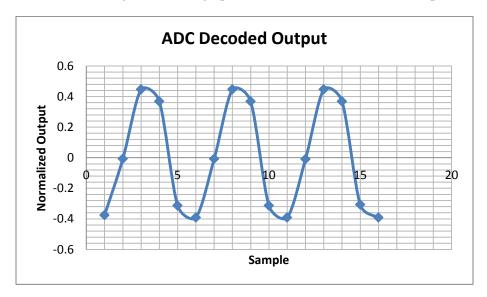

The MSB clearly indicates a 1 MHz polarity switch indicating correct operation. After decoding the output of the ADC, the following normalized graph was obtained for the first 16 samples:

Figure 7.2.2. – Observe that sampling at 5 MHz is more than enough to reconstruct the original waveform.

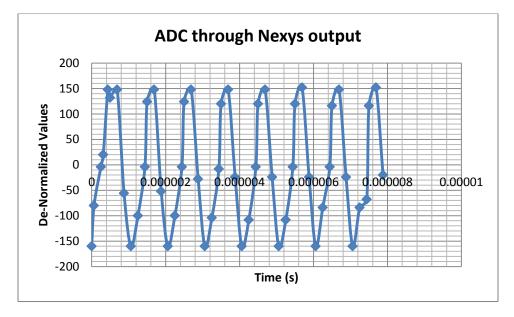

Following these tests, the ADC outputs were then fed through the Nexys board which sampled the ADC and, upon every clock falling edge in a process statement, were then fed back to the outputs of the Nexys board and sampled as can be seen in the following figure.

Figure 7.2.3 – ADC values after being fed through the Nexys board.

Some of the points in the figure above appear to deviate from their proper position. This is due to noise generated by the clock line which causes occasional bit errors. However, these errors happened relatively rarely and were ignored for the time being. The errors were most likely caused by improper routing because the clock line was routed underneath the ADC; it should have been isolated from the ADC and separate from the data and any other analog lines.

#### Sub-System 3. Instrumentation Amplifier through ADC Test

To test the IA through the ADC, only either the I or Q channel was used. Since the input is differential, one input was just tied to a CMV voltage of 1.5V and the other had a 2Vpp 100 KHz sine wave inserted into it. The output of the ADC is shown in Figure 7.3.1 on the next page.

| 1 M Samples 🔻 @ 24 MHz 🔻     | Start Simulation                                 | Oj                                                                        |

|------------------------------|--------------------------------------------------|---------------------------------------------------------------------------|

| +40 µs                       | +50 μs +60 μs +70 μs +80 μs +90 μs + 10 μs +20 μ | ıs +30 µs                                                                 |

| 0 - Channel 0 5 2 -          |                                                  | ✓ Measurements       Width:     ###       Period:     ###                 |

| 1 - Channel 1 <b>F - T _</b> |                                                  | Frequency: ###<br><u>T1</u> : ###<br><u>T2</u> : ###<br>  T1 - T2   = ### |

| 2 - Channel 2 5 2 -          |                                                  | ✓ Analyzers                                                               |

| 3 - Channel 3 📑 📜            |                                                  |                                                                           |

| 4 - Channel 4 5 2 -          |                                                  |                                                                           |

| 5 - Channel 5 5 - Channel 5  |                                                  |                                                                           |

| 6 - Channel 6 🥤 🔭 📜 🗖        |                                                  |                                                                           |

| 7 - Channel 7 📑 📜            |                                                  |                                                                           |

|                              |                                                  |                                                                           |

Figure 7.3.1 – Logic Analyzer output with the input at the IA.

The measured sign bit change is 100 KHz indicating that the ADC is reading data properly. Both channels behaved identically so the Q channel result picture has been left out.

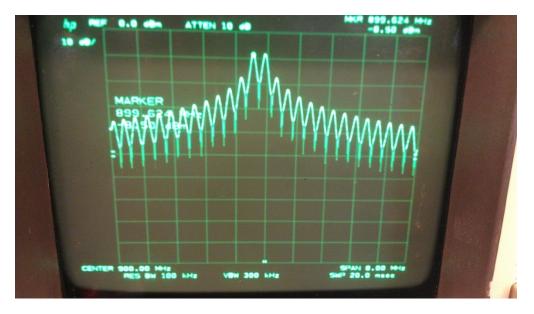

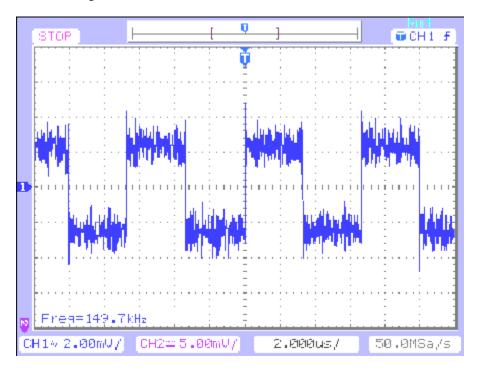

# Sub-System 4. – Modulator Testing

To test the modulator, a simple 150 KHz differential square wave was fed to the input and the RF was fed to a spectrum analyzer. The LO was set to 900 MHz at 0 dBm. Figure 7.4.1 shows the resulting spectrum.

Figure 7.4.1 – Spectrum of the modulated 150 KHz square wave.

Without pulse shaping applied to the system, the signal will occupy a large bandwidth as can be seen in Figure 7.4.1. However, Figure 7.4.1 does indeed demonstrate that the signal is being modulated to 900 MHz and that the LO is suppressed at 900 MHz. The sidebands follow a sinc function which is indeed the Fourier Transform of a 150 KHz square wave.

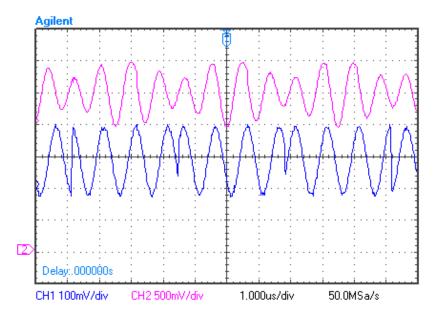

#### Sub-System 5. – Programmable Gain Amplifier Testing

To test the PGA, a sine wave signal with a 2.5 CMV was inputto the PGA and its amplitude was varied. The output of the PGA was observed in an oscilloscope. Refer to Figures 7.5.1, 7.5.2, and 7.5.3 for selected input and output waveforms. Because of the reset process described in Section 5, Sub-System 4, Software Component 7, the signal did indeed get passed through with a gain of 1 for a brief instant in time. This time depends on the time it takes for the comparator process to run.

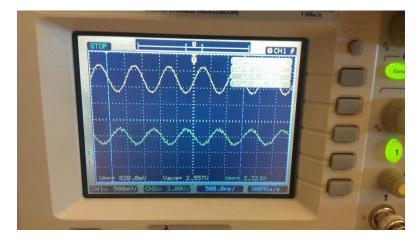

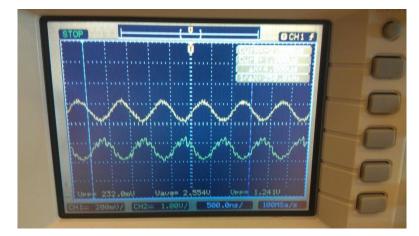

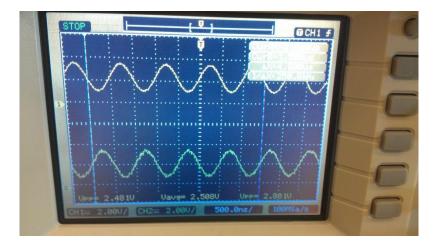

Figure 7.5.1. – Output waveform (green) for a .82 Vpp 2.5V CMV sin wave input (yellow).

Figure 7.5.2. - Output waveform (green) for a .23 Vpp 2.5V CMV sin wave input (yellow).

Figure 7.5.3. - Output waveform (green) for a 2.48 Vpp 2.5V CMV sin wave input (yellow).

Table 7.5.1 shows the gains of each of the previous waveforms and compares them to the nominal gains that correspond to the respective states given in Figure 5.5.7.2.

| Vin   | Vout  |             |       | Nominal |   |          |

|-------|-------|-------------|-------|---------|---|----------|

| (Vpp) | (Vpp) | Gain        | State | Gain    |   | % Error  |

| 0.82  | 2.32  | 2.829268293 | 5     |         | 3 | -5.69106 |

| 0.232 | 1.24  | 5.344827586 | 7     |         | 6 | -10.9195 |

| 2.48  | 2.881 | 1.161693548 | 1     |         | 1 | 16.16935 |

Table 7.5.1. – Selected waveforms and their respective gains and states compared with nominal values.

The percent errors shown for these states are relatively high. However, they are within reason and we can assume that the PGA works. It must be noted that the oscilloscope somewhat struggled to obtain a proper waveform picture because of the resetting nature of the algorithm, therefore, some measurements may be innacurate.

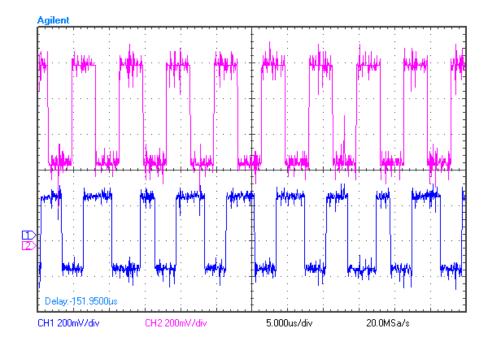

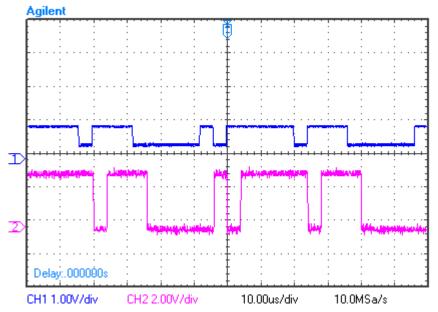

#### Section 8. FULL SYSTEM TEST

With all the sub-systems tested and working, the system was ready to be integrated and tested together. For preliminary tests, the PGA was excluded. The first test was to establish a direct demodulation communication system by simply connecting the RF\_IN and RF\_OUT ports of the modulator and demodulator and setting both LO's to 900 MHz. The 900 MHz RF carrier was used as opposed to 950 MHz for arbitrary reasons. Absolutely no discernable difference was noticed between these two frequencies. With a 150 KHz square wave differential input, the I positive output of the demodulator is shown in Figure 8.1 below.

Figure 8.1. – Demodulated square wave using direct conversion.

The noise present in the wave is the unfiltered high frequency content associated with down conversion. This test confirmed that the demodulator does indeed down convert a signal properly.