# Transmission Line Modeling for the Purpose of Analog Power Flow Computation of

# Large Scale Power Systems

A Thesis

Submitted to the Faculty

of

Drexel University

by

Aaron St. Leger

in partial fulfillment of the

requirements for the degree

of

Master of Science in Electrical Engineering

July 2005

© Copyright 2005 Aaron St. Leger. All Rights Reserved

### ACKNOWLEDGMENTS

I would like to acknowledge and thank my advisor, Dr. Chikaodinaka Nwankpa, for all his help and guidance in the research and the development of this thesis. I also thank him for the opportunity to study and conduct research in the Center of Electric Power Engineering (CEPE). The facilities, faculty and students in CEPE all contribute to an environment that is very conducive to learning and conducting research. I am ever grateful for the opportunity to be a part of this organization.

I would also like to thank Dr. Miu, Dr. Halpin and Dr. Nagvajara for serving on my thesis committee. I am appreciative for their expertise, participation in my graduate studies and their time dedicated to reviewing and commenting on this work.

Finally I would like to express gratitude to Jeffrey Yakaski, Anthony Deese, Qingyan Liu and Michael Olaleye for their help and participation in the PowerGrid research project. Their valuable work has assisted me in my research efforts and made much of the work in this thesis possible.

# TABLE OF CONTENTS

| LIST O | F TABLES                                     | vii |

|--------|----------------------------------------------|-----|

| LIST O | F FIGURES                                    | X   |

| ABSTR  | ACT                                          | xiv |

| 1 IN   | TRODUCTION                                   | 1   |

| 1.1    | OVERVIEW                                     | 1   |

| 1.2    | BACKGROUND                                   | 4   |

| 1.3    | MOTIVATION                                   | 8   |

| 1.4    | PROBLEM STATEMENT                            | 10  |

| 1.5    | ORGANIZATION OF THESIS                       | 11  |

| 2 DE   | SIGN AND BENCHMARKING ENVIRONMENT            | 12  |

| 2.1    | OVERVIEW                                     | 12  |

| 2.2    | PSPICE                                       | 12  |

| 2.3    | POWERWORLD                                   | 15  |

| 2.4    | HARDWARE                                     | 17  |

| 3 PC   | WER TRANSMISSION LINE MODELING               | 19  |

| 3.1    | OVERVIEW OF TRANSMISSION LINE MODELING       | 19  |

| 3.2    | DISTRIBUTED TRANSMISSION LINE PARAMETERS     | 20  |

| 3.3    | LUMPED TRANSMISSION LINE PARAMETERS          | 24  |

| 3.4    | LUMPED PARAMETER TRANSMISSION LINE MODELS    | 27  |

| 4 AN   | VALOG EMULATION OF A POWER SYSTEM            | 33  |

| 4.1    | INTRODUCTION                                 | 33  |

| 4.2    | ANALOG POWER SYSTEM DC EMULATION METHODOLOGY | 34  |

|   | 4.3 | POV    | WER SYSTEM EMULATION COMPONENTS |                      |

|---|-----|--------|---------------------------------|----------------------|

|   | 4.  | 3.1    | GENERATORS                      |                      |

|   | 4.  | 3.2    | TRANSMISSION LINES              |                      |

|   | 4.  | 3.3    | LOADS                           |                      |

| 5 | М   | ETHO   | DOLOGY AND DEVELOPMENT OF ANALO | OG TRANSMISSION LINE |

| В | ULD | ING BI | LOCKS                           |                      |

|   | 5.1 | INT    | RODUCTION                       |                      |

|   | 5.2 | CHA    | ARACTERIZATION OF OPERATIONAL   | TRANSCONDUCTANCE     |

|   | AMI | PLIFIE | R (OTA)                         |                      |

|   | 5.3 | POS    | SITIVE OTA VARIABLE RESISTOR    |                      |

|   | 5.  | 3.1    | SIMULATION RESULTS              |                      |

|   | 5.  | 3.2    | HARDWARE RESULTS                |                      |

|   | 5.4 | NEC    | GATIVE OTA VARIABLE RESISTOR    |                      |

|   | 5.4 | 4.1    | SIMULATION RESULTS              |                      |

|   | 5.  | 4.2    | HARDWARE RESULTS                |                      |

| 6 | V   | ERIFIC | CATION OF ANALOG LINE MODELS    |                      |

|   | 6.1 | OVI    | ERVIEW                          |                      |

|   | 6.2 | PAF    | RAMETER SCALING                 |                      |

|   | 6.3 | PRO    | DTOTYPE NETWORK MODULE          |                      |

|   | 6.4 | NET    | WORK MODULE TESTING             |                      |

|   | 6.  | 4.1    | LOSSLESS LINE MODEL             |                      |

|   | 6.  | 4.2    | LOSSY LINE MODEL                |                      |

|   | 6.  | 4.3    | PI LINE MODEL                   |                      |

| 6.5 NETWORK AND LOAD EMULATOR TESTING                           |

|-----------------------------------------------------------------|

| 7 CONCLUSIONS AND FUTURE WORK                                   |

| 7.1 CONCLUSIONS                                                 |

| 7.2 SUMMARY OF RESEARCH CONTRIBUTIONS 110                       |

| 7.3 FUTURE WORK                                                 |

| LIST OF REFERENCES                                              |

| APPENDIX A: EXAMPLES OF COMMERCIAL ANALOG COMPUTERS 115         |

| APPENDIX B: EMULATION RESULTS FOR 3 BUS LOSSLESS TRANSMISSION   |

| LINE NETWORK                                                    |

| APPENDIX C: EMULATION RESULTS FOR 3 BUS LOSSY TRANSMISSION LINE |

| NETWORK                                                         |

| APPENDIX D: PSPICE SIMULATION OF THREE BUS POWER SYSTEM         |

| EMULATION WITH PI LINE MODELS                                   |

| APPENDIX E: EMULATION RESULTS FOR NETWORK AND LOAD MODULE 133   |

vi

## LIST OF TABLES

| Table 1: Cost of System Downtime in Different Industries             | 9   |

|----------------------------------------------------------------------|-----|

| Table 2: Details on Lumped Line Models                               |     |

| Table 3: Simulation Details for Lossy Network                        |     |

| Table 4: Emulation Parameters for Lossy Transmission Lines           | 100 |

| Table 5: Emulation Bus Voltages for Lossy Transmission Line Test     | 101 |

| Table 6: Emulated Line Currents for Lossy 3 Bus Network              | 101 |

| Table 7: Offset Corrected Emulation Line Currents                    | 101 |

| Table 8: Error Analysis on Emulation Results for 3 Bus Lossy Network | 102 |

| Table 9: Power System Parameters for Pi Line HW Test                 | 103 |

| Table 10: Pi Line Emulation Parameters                               | 104 |

| Table 11: Emulation Parameters for Pi Transmission Line              | 104 |

| Table 12: Emulated Line Currents for Pi Transmission Line            | 104 |

| Table 13: Ybus and Emulation Current Injections                      | 105 |

| Table 14: Emulation Error for Pi Transmission Line HW Test           | 105 |

| Table 15: PowerWorld Parameters and Results                          | 107 |

| Table 16: Emulation Parameters and Results                           | 107 |

| Table 17: Error Analysis on Emulation with Network and Load Modules  | 107 |

| Table 18: Simulation Results for Lossless Network                    | 119 |

| Table 19: Scaling Factors for Lossless Network Testing               | 119 |

| Table 20: Emulation Parameters for Lossless Transmission Lines       | 119 |

| Table 21: Emulation Bus Voltages for Lossless Transmission Line Test | 119 |

| Table 22: Emulated Line Currents for Lossless 3 Bus Network          | 120 |

| Table 23: Emulated Current Injections for Lossless 3 Bus Network            | 120 |

|-----------------------------------------------------------------------------|-----|

| Table 24: Error Analysis on Emulation Results for 3 Bus Lossless Network    | 120 |

| Table 25: Simulation Results for Lossless Network                           | 121 |

| Table 26: Emulation Bus Voltages for Lossless Transmission Line Test        | 122 |

| Table 27: Emulated Line Currents for Lossless 3 Bus Network                 | 122 |

| Table 28: Emulated Current Injections for Lossless 3 Bus Network            | 122 |

| Table 29: Error Analysis on Emulation Results for 3 Bus Lossless Network    | 122 |

| Table 30: Simulation Results for Lossless Network                           | 123 |

| Table 31: Emulation Bus Voltages for Lossless Transmission Line Test        | 124 |

| Table 32: Emulated Line Currents for Lossless 3 Bus Network                 | 124 |

| Table 33: Emulated Current Injections for Lossless 3 Bus Network            | 124 |

| Table 34: Error Analysis on Emulation Results for 3 Bus Lossless Network    | 124 |

| Table 35: Simulation Results for Lossy Network                              | 126 |

| Table 36: Emulated Line Currents for Lossy 3 Bus Network                    | 126 |

| Table 37: Offset Corrected Emulation Results for Lossy 3 Bus Network        | 126 |

| Table 38: Error Analysis on Emulation Results for 3 Bus Lossy Network       | 126 |

| Table 39: Power World Simulation Results for Three Bus System with Pi Lines | 127 |

| Table 40: Emulation Scaling Factors                                         | 127 |

| Table 41: DC Emulation Network Parameters                                   | 128 |

| Table 42: Emulation Line Configuration for Pi Transmission Lines            | 128 |

| Table 43: Error Analysis on Emulation Results for 3 Bus Pi Line Network     | 128 |

| Table 44: PowerWorld Parameters and Results                                 | 134 |

| Table 45: Emulation Parameters and Results                                  | 134 |

| Table 46: Error Analysis on Emulation with Network and Load Modules | 134 |

|---------------------------------------------------------------------|-----|

| Table 47: PowerWorld Parameters and Results                         | 135 |

| Table 48: Emulation Parameters and Results                          | 136 |

| Table 49: Error Analysis on Emulation with Network and Load Modules | 136 |

# **LIST OF FIGURES**

| Figure 1: PSoC Development Process                                    |    |

|-----------------------------------------------------------------------|----|

| Figure 2: Analog Transmission Line Model Control Panel                | 6  |

| Figure 3: PSpice Electrical Schematic with Voltage and Current Probes | 14 |

| Figure 4: PSpice Plot of Probed Signals vs. Bias Current              | 14 |

| Figure 5: PowerWorld One Line Diagram of a 6 Bus Power System         | 16 |

| Figure 6: PowerWorld Transmission Line Options                        | 17 |

| Figure 7: Analog Emulation Hardware Test Setup                        |    |

| Figure 8: Distributed Parameter Transmission Line Model               |    |

| Figure 9: Lumped Parameter П-Equivalent Transmission Line             |    |

| Figure 10: Long Transmission Line Model                               |    |

| Figure 11: Medium Length Transmission Line Model                      |    |

| Figure 12: Short Lossy Transmission Line Model                        |    |

| Figure 13: Short Lossless Transmission Line Model                     |    |

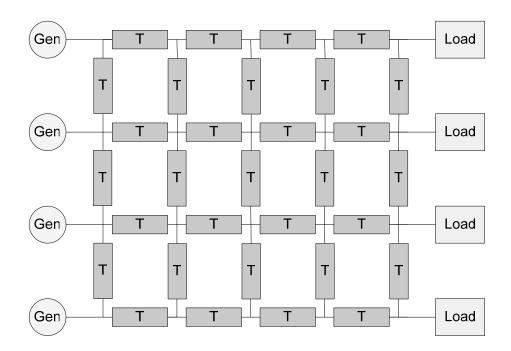

| Figure 14: Power System Emulation Network                             |    |

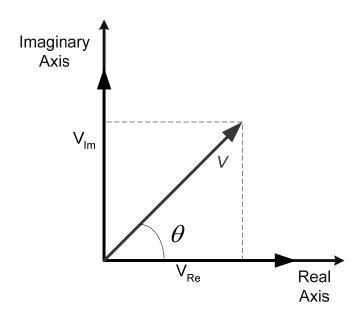

| Figure 15: Polar and Rectangular Coordinate Comparison                |    |

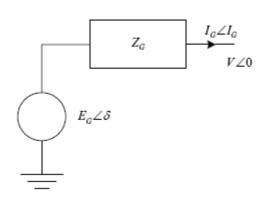

| Figure 16: Classical Generator Model                                  | 41 |

| Figure 17: Analog Generator Module for DC Emulation                   |    |

| Figure 18: Resistor Networks for a Short Lossless Transmission Line   | 45 |

| Figure 19: Resistor Networks for a Short Lossy Transmission Line      |    |

| Figure 20: Resistor Networks for a Medium Length Transmission Line    | 48 |

| Figure 21: Resistor Networks for a Long Transmission Line Model       | 49 |

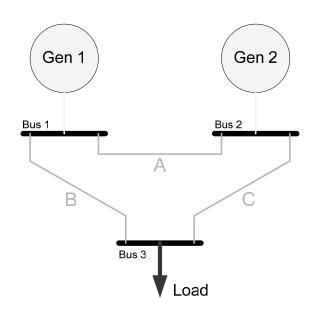

| Figure 22: Single Line Diagram of a Three Bus Power System            | 50 |

| Figure 23: Three Bus DC Emulation Topology with Short Lossless Transmission Lin | e |

|---------------------------------------------------------------------------------|---|

| Model 5                                                                         | 1 |

| Figure 24: Three Bus DC Emulation Topology with Short Lossy Transmission Lin    | e |

| Model                                                                           | 2 |

| Figure 25: Three Bus DC Emulation Topology with Medium Length Transmission Lin  | e |

| Model                                                                           | 3 |

| Figure 26: Three Bus DC Emulation Topology with Long Length Transmission Lin    | e |

| Model 5                                                                         | 4 |

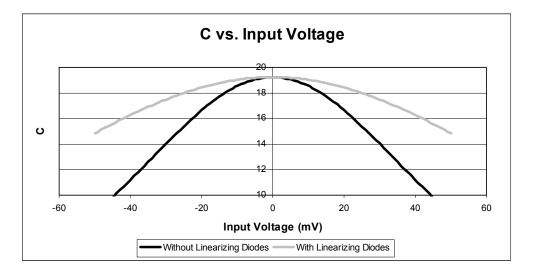

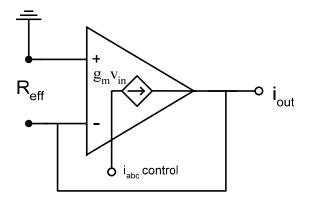

| Figure 27: Ideal OTA5                                                           | 9 |

| Figure 28: Effect of OTA Gain Factor with Linearizing Diodes                    | 1 |

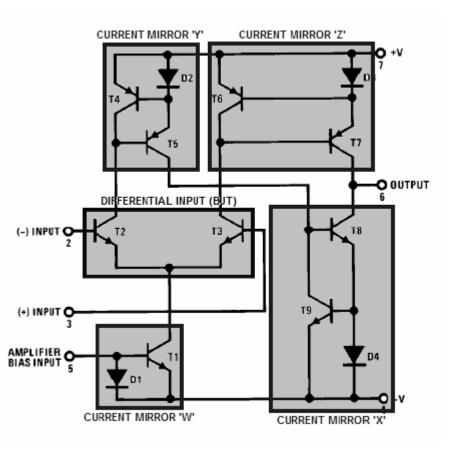

| Figure 29: Internal Structure of LM3080 OTA                                     | 4 |

| Figure 30: Basic OTA Variable Resistor                                          | 5 |

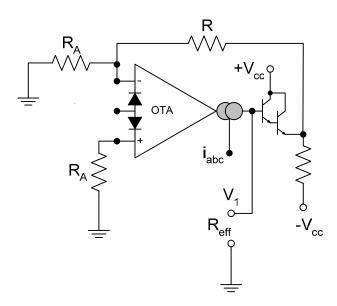

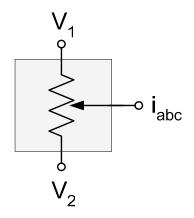

| Figure 31: Single Ended Variable Resistor with Extended Input Range             | 7 |

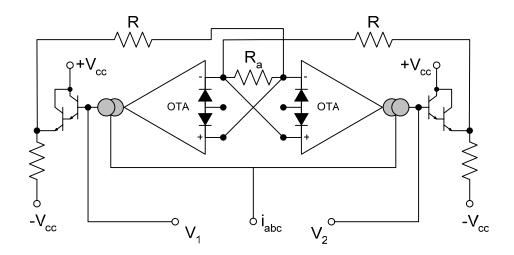

| Figure 32: OTA Based Floating Variable Positive Resistor                        | 9 |

| Figure 33: Potentiometer Relationship to OTA Variable Resistor Circuit          | 0 |

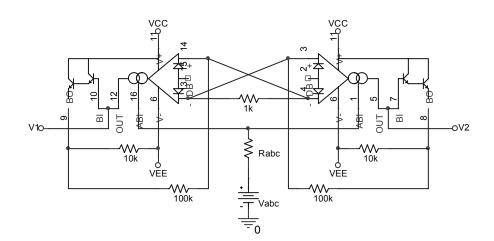

| Figure 34: PSpice Schematic for OTA Based Variable Positive Resistor            | 2 |

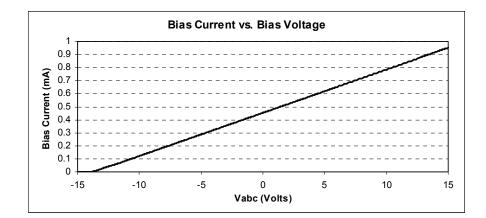

| Figure 35: Bias Current versus Bias Voltage7                                    | 3 |

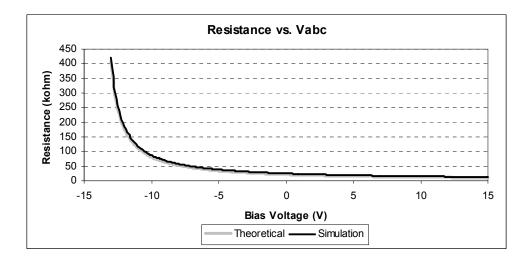

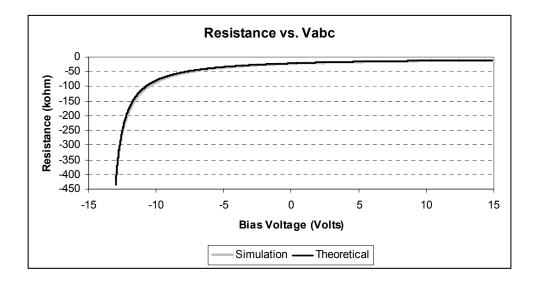

| Figure 36: Simulated and Theoretical Effective Resistance vs. Bias Voltage      | 4 |

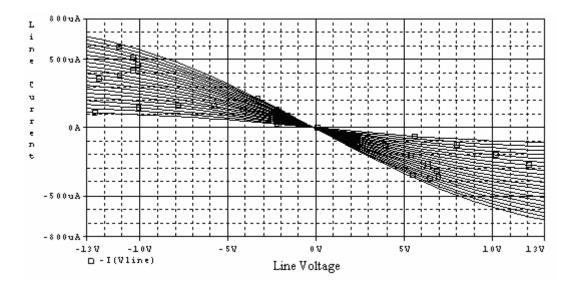

| Figure 37: SW Line Current vs. Line Voltage                                     | 5 |

| Figure 38: SW Line Current vs. Line Voltage (Linear Region)7                    | 5 |

| Figure 39: Effective Resistance from PSpice Simulation7                         | 6 |

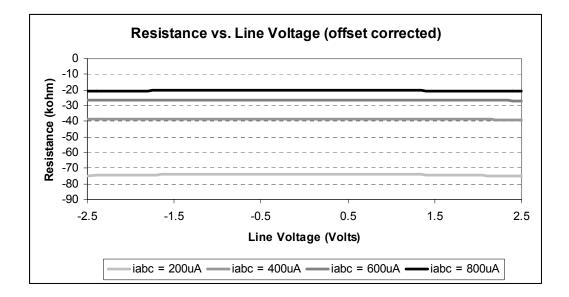

| Figure 40: SW Effective Resistance vs. Line Voltage                             | 7 |

| Figure 41: Hardware and PSpice Effective Resistance vs. Bias Voltage            | 8 |

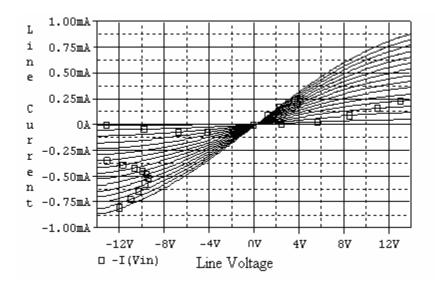

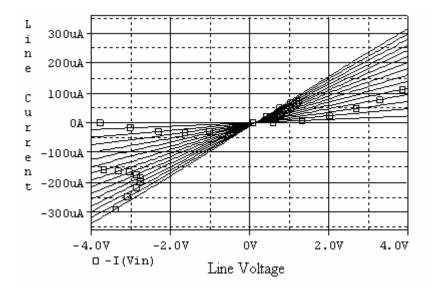

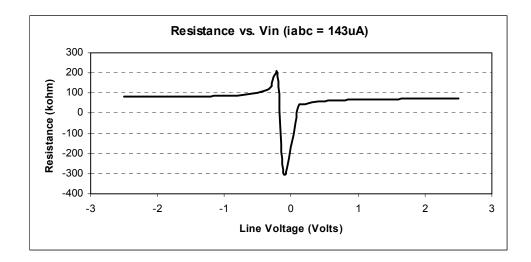

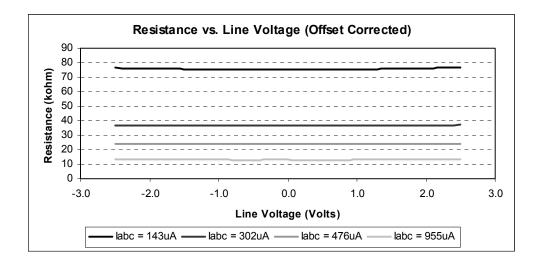

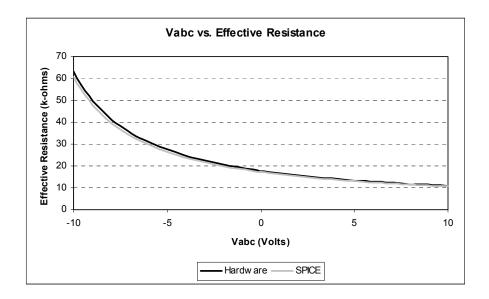

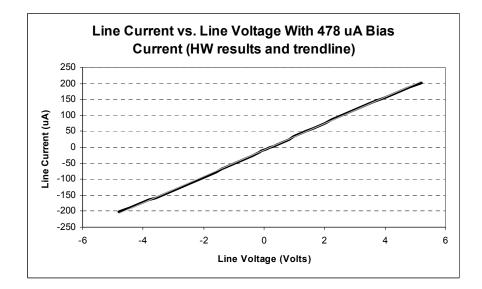

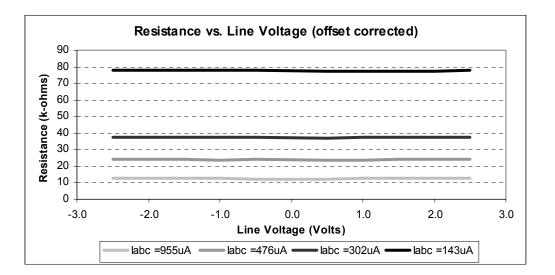

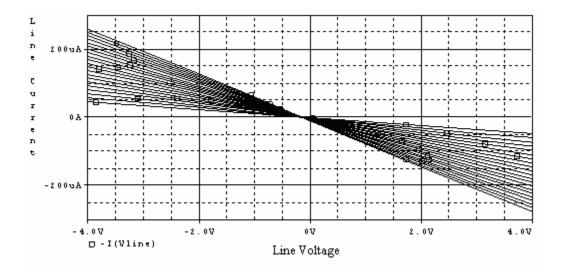

| Figure 42: HW Line Current vs. Line Voltage for Various Bias Currents      | 79  |

|----------------------------------------------------------------------------|-----|

| Figure 43: HW Line Current Linearity                                       | 79  |

| Figure 44: Hardware Effective Resistance vs. Line Voltage                  | 80  |

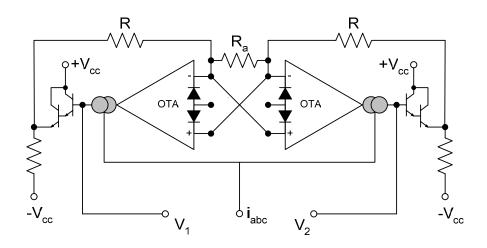

| Figure 45: Double Ended OTA Variable Negative Resistor                     | 81  |

| Figure 46: PSpice Schematic for OTA Based Variable Negative Resistor       | 83  |

| Figure 47: Simulated and Theoretical Effective Resistance vs. Bias Voltage | 84  |

| Figure 48: SW Line Current vs. Line Voltage                                | 85  |

| Figure 49: SW Line Current vs. Line Voltage (Linear Region)                | 85  |

| Figure 50: SW Effective Resistance vs. Line Voltage                        | 86  |

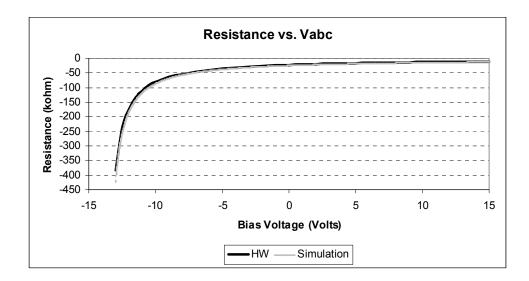

| Figure 51: Hardware and PSpice Effective Resistance vs. Bias Voltage       | 87  |

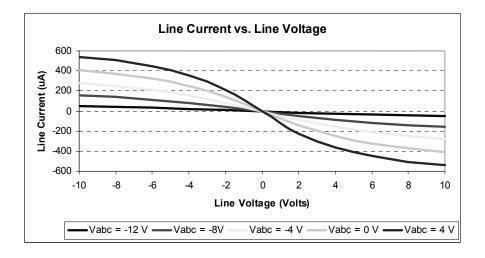

| Figure 52: HW Line Current vs. Line Voltage for Various Bias Voltages      | 88  |

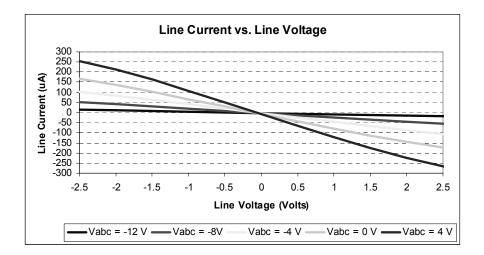

| Figure 53: HW Line Current vs. Line Voltage (Linear Region)                | 88  |

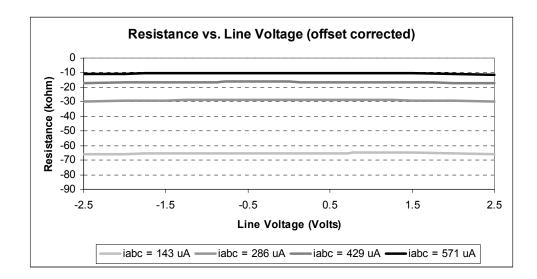

| Figure 54: Hardware Effective Resistance vs. Line Voltage                  | 89  |

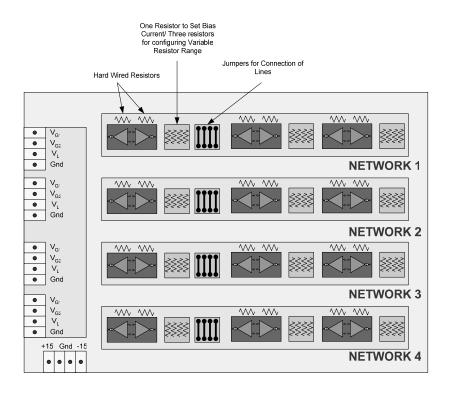

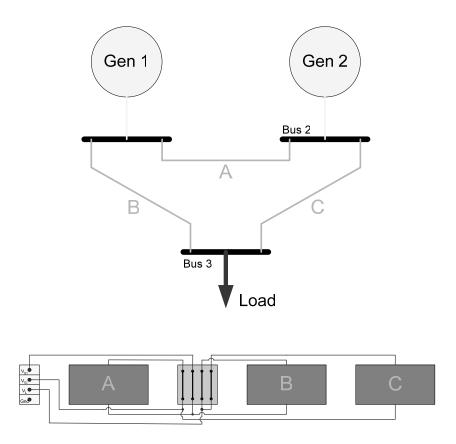

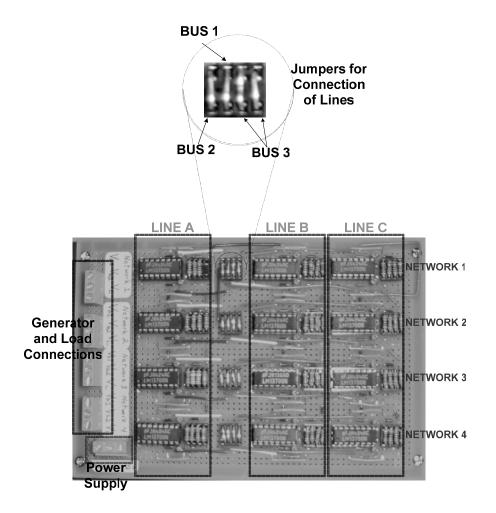

| Figure 55: Network Module Layout                                           |     |

| Figure 56: Emulation Network and a Three Bus Power System                  |     |

| Figure 57: Prototype Network Module                                        |     |

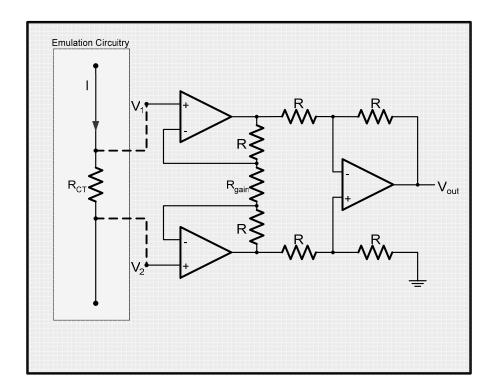

| Figure 58: Current Measurement Circuit                                     |     |

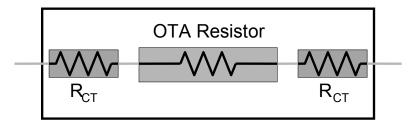

| Figure 59: OTA Variable Resistor with Current Sensing Resistors            |     |

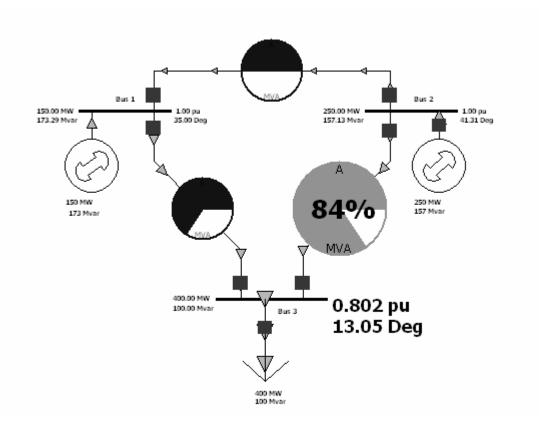

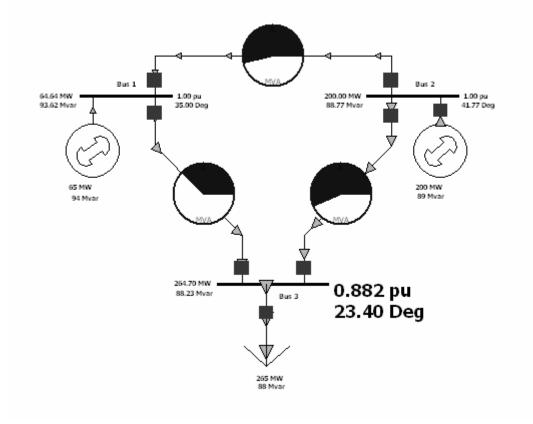

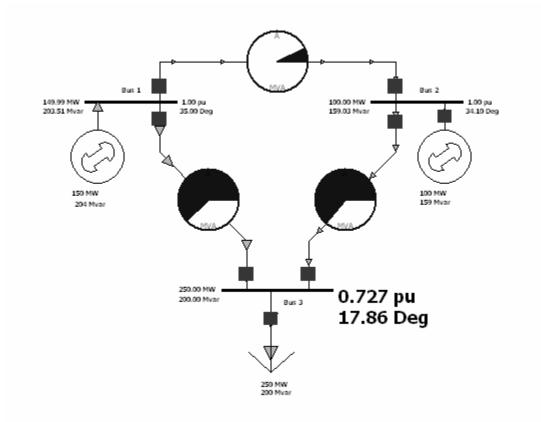

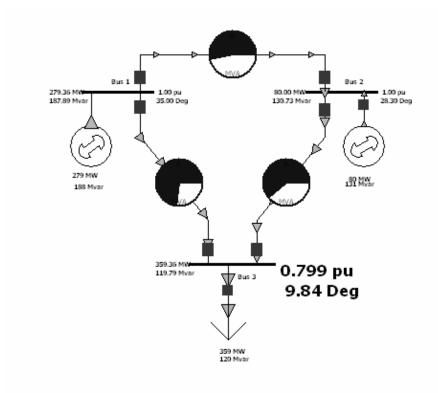

| Figure 60: PowerWorld Simulation Results with Lossy Lines                  |     |

| Figure 61: Single Pi Transmission Line HW Test Setup                       | 103 |

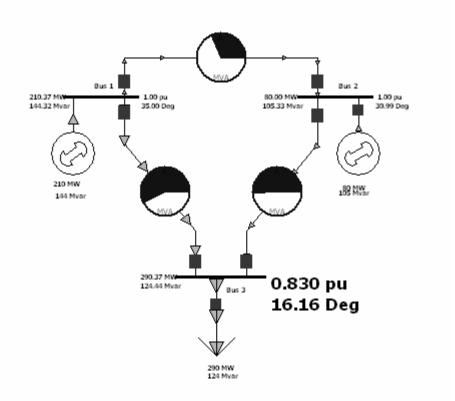

| Figure 62: PowerWorld Results for Network and Load Module Emulation        | 106 |

| Figure 64: Applied Dynamics Model # AD-1-16                                | 115 |

| Figure 65: Applied Dynamics Model # AD-256                                 | 116 |

| Figure 66: Comcor Incorporated Model # Ci 5000 1                                  | 17 |

|-----------------------------------------------------------------------------------|----|

| Figure 67: PowerWorld Simulation Results with Lossless Lines 1                    | 18 |

| Figure 68: PowerWorld Simulation Results with Lossless Lines 1                    | 21 |

| Figure 69: PowerWorld Simulation Results with Lossless Lines 1                    | 23 |

| Figure 70: PowerWorld Simulation Results with Lossy Lines 1                       | 25 |

| Figure 71: PSpice Schematic for a Single Pi Line DC Emulation Network 1           | 29 |

| Figure 72: PSpice Schematic for Three Bus Simulation with Hierarchal Blocks 1     | 30 |

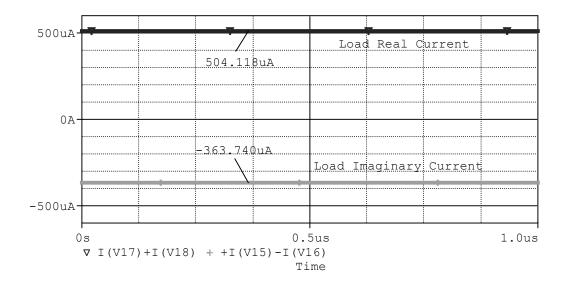

| Figure 73: Simulation Results for Generator 1 Current for 3 Bus Pi Line Network 1 | 31 |

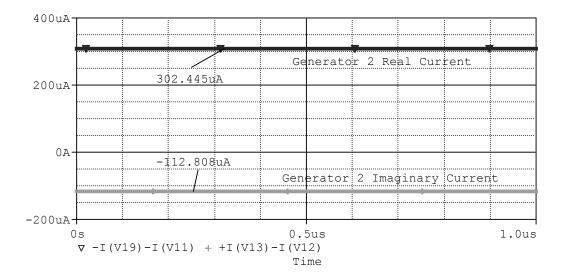

| Figure 74: Simulation Results for Generator 2 Current for 3 Bus Pi Line Network 1 | 31 |

| Figure 75: Simulation Results for Load Current for 3 Bus Pi Line Network 1        | 32 |

| Figure 76: PowerWorld Results for Network and Load Module Emulation 1             | 33 |

| Figure 77: PowerWorld Results for Network and Load Module Emulation 1             | 35 |

#### ABSTRACT

## Transmission Line Modeling for the Purpose of Analog Power Flow Computation of Large Scale Power Systems Aaron St. Leger Chikaodinaka Nwankpa, Ph.D.

This thesis proposes methods for modeling electric power transmission lines for the purpose of analog power flow computation of power system networks. Theoretical and applicable circuit models for analog transmission lines are presented with a focus on power-flow studies which concentrates on the steady state or static behavior of electrical power transmission lines. With this approach the wave propagation and reflection is not as much of a concern as the steady state line voltages and current flows. Because of this lumped circuit equivalent line models are utilized. The primary goal is to develop a computational alternative for power system analysis that overcomes obstacles currently faced by traditional digital computation methods. Analog computation is proving to be a viable alternative and has notable advantages over digital computers. In order to contrive a practical analog emulator precise models for power system components are required. Specifically this thesis develops a realization of an electric power transmission line model for such a purpose.

The transmission line model traditionally utilized in power-flow computation is a lumped parameter pi-model equivalent circuit. In digital computation the shunt elements and sometimes the series resistances are often times neglected in order to simplify the power flow equations and subsequently speed up the calculation times. Prior research in analog computation for power flow analysis also utilized these simplified line models. A fully reconfigurable pi-model is presented here for an analog computation approach. No components have been neglected resulting in a more accurate line model with fast computation times. The ability to remotely reconfigure each component on the line model makes this model universal. The design could easily be fabricated to an integrated circuit to represent a large scale network and configured to match a real world system. In addition, the model is easily expanded to form a distributed parameter line model by interconnecting multiple components in series. This allows for computational analysis of the power system states throughout the transmission line which is traditionally not done in digital power flow computation due to computational restraints.

## **1** INTRODUCTION

### **1.1 OVERVIEW**

Analog computation of power systems is a continuing field of research. Among the advantages analog computation possesses over traditional digital methods are physically realizable solutions and much faster computation times. In order to consummate this analog method as a viable tool in power system analysis accurate models of power system components are required. This thesis explores and presents various reconfigurable transmission line models for a specific analog computation methodology.

Currently power-flow computation for large power systems is time intensive. The calculations are non-linear in nature and lengthy iteration schemes are the currently preferred solution. This presents a problem as many assumptions and simplifications are required to solve the equations with digital methods in a timely manner. In addition, expansion of the power grid, increasing necessity and complexity of contingency studies and introduction of economic analyses are demanding further computational burden. Traditional digital methods are too slow to solve the aforementioned demands quickly. This affects the security, reliability and market operation of power systems. Ideally a real-time computation tool, or faster than real-time, is preferable, specifically in market activities and operation. Analog computation provides a viable alternative to traditional approaches to achieve this goal.

Analog power-flow computation has certain inherent advantages over digital computation. Conventional digital methods are expensive and slow in comparison to analog computers. The power-flow solution is obtained almost instantaneously regardless of the number of components in the network with analog circuits. Analog methods achieve true parallelism in computation, the time to find a solution is independent of network size. Effectively the solution is obtained as quickly as the system stabilizes. Experimentation has shown the ability to calculate solutions even faster than power system phenomena occur in the real world. In prior research, simulation time for a two machine system were typically 10<sup>4</sup> times shorter than the real time simulated phenomena[1]. This is following the approach of modeling generator dynamics for the purpose of transient stability evaluation. Despite that an analog approach is certainly advantageous in some regards there are also barriers in this field and reasons why its use is not widespread today as digital techniques.

The modeling and design of analog components is one obstacle that must be overcome to take advantage of above-mentioned desirable attributes of analog computation. While analog solutions are not as precise as digital methods (measurement errors, noise, etc.) they have the capability to be much more accurate through more detailed modeling in analog hardware. Without clearly defined valid models for power system components this computational method cannot be realized. In addition, these models also must cater towards computational speed. Specifically in power system operation execution of multiple runs and contingencies is required extremely quickly. A priority for these analog models is to yield valid solutions while allowing fast reconfigurability. These problems have been addressed in the design of the transmission line models presented in this thesis. The models were designed based on a previously proposed DC emulation technique of power-flow computation which is reviewed and expanded upon in this thesis. Specifically this work presents a robust analog transmission line model suitable for the development of a large scale power system emulator.

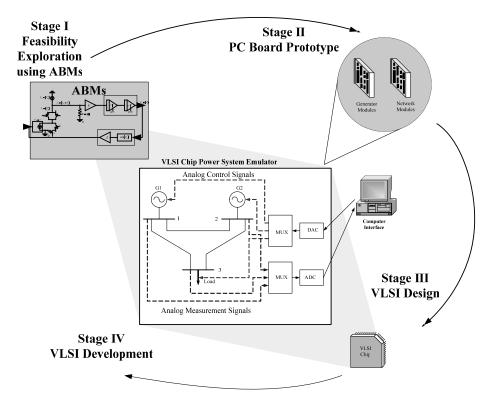

The work in this thesis is part of ongoing research efforts to develop a Power System on a Chip (PSoC). The vision is to realize this through a Very Large Scale Integrated (VLSI) circuit which is remotely configurable, or reconfigurable, and controllable. A graphical illustration for the development of a PSoC is shown in Figure 1 below[2]. Exploration into Analog Behavior Modeling (ABM), stage I, was conducted by M. Olaleye[2] and the work in this thesis concentrates on stage II and furthering development of the transmission line models for this application. The transmission line models presented here were fully developed in hardware and a prototype power system network was constructed and tested.

Figure 1: PSoC Development Process

Stage I was a study conducted to analyze the feasibility of analog computation for power system analysis without requiring development and construction of analog circuits and data acquisition. This task was accomplished through software simulation. Stage II encompasses the realization of the power system model in analog circuit form. Stages III and IV move this circuit realization into an end product of a VLSI chip.

The next section details some background, history and renewed interest of analog computational methods. In addition, inherent obstacles and limitations of analog computation are examined along with schemes to try and overcome them.

## **1.2 BACKGROUND**

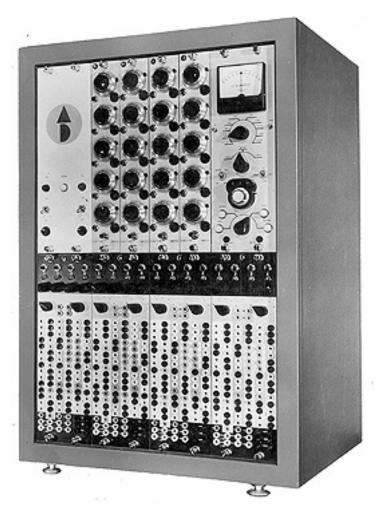

Analog computation in power systems is certainly not a new endeavor. AC Network Analyzers (NA) were first developed in the 1920's to model and solve problems associated with power distribution systems[3]. These analyzers were essentially miniaturized power systems built with passive components such as resistors, capacitors Bell Telephone Laboratories (BTL), Massachusetts Institute of and inductors Technology (MIT), and the Office of Naval Research (ONR) all actively developed and researched analog computing applications at some point in time. Development and use of analog computation grew throughout the twentieth century until digital computers came into the mainstream in the 1970's. These digital methods became so popular for good reasons. They were much more precise and were easily programmable in comparison to The analog computers at that time required manual their analog counterparts. configuration of jumpers, potentiometers and other parameters for each computation. This required manual intervention and lengthy setup time for complex problems. Despite

these shortcomings up through the 1960's analog computers were commercially available and considerably successful and efficacious. Some examples of commercial analog computers can be seen in appendix A. Although analog computing lost the commercial war to its digital counterpart there were distinct advantages in the analog world. For example the AC network analyzers used in the 1920's had the capability of real time computation of large power networks. Even the fastest digital computers today cannot claim this capability. This speed is brought about by the ability to have true parallelism in computation and is one of the reasons analog computation is still utilized in some applications today and looks to be in the future. Even recently a fully analog power system emulator, currently the largest in the world, was constructed in 1990 by the Kansai Electric Power Company (KEPCO). This system was constructed with passive elements modeling major components of the power network and consists of 30 generators, 304 transmission lines, 20 loads, HVDC transmission facilities, and static var compensators[4]. This analyzer is based on a real world system and epitomizes some current development for analog computation in the power systems field. In addition, old analog network analyzers no longer in use are being utilized for undergraduate and research efforts in power systems[5].

Current and future development of analog computation looks to take advantage of associated strengths and overcome some of, ideally all, the historically congenital obstacles. Namely some major encumbrances are large size of analog circuits, poor programmability/reconfigurability, and limited computational accuracy and measurement problems. An example of an older computational tool for power systems is shown in Figure 2[6]. This was an analog transmission line model used for computations in relay

studies. This was a very powerful tool for its time but suffered from the drawbacks previously mentioned. New technological developments are showing promise to overcome these hindrances.

Figure 2: Analog Transmission Line Model Control Panel

One approach deals with hybrid systems. These computational engines utilize both digital and analog components to try and take advantage of both methods. More recently a push is going for computational systems on a chip (SoC) which allows reconfiguration and programmability without the need of manually changing wires or settings. This push for SoC is being done with both analog and digital computational methods. The latter is trying to mimic the main strength of analog computation, true parallel computation.

With the advancement of fabrication technologies digital network analyzers are being researched and developed moving towards real time digital computation[7-10]. These analyzers show promise but are much more complex in comparison to analog network analyzers and still have problems associated with digital computation. The basic approach to achieve parallel computation in power systems with this method is to associate an independent processor or process with each power system component (transmission lines, generators, loads, etc.). An example of a real time digital analyzer for a transmission line can be seen in [7]. Other methods dedicate a processor to each bus in the power system[9]. In contrast to an analog approach these methods require a vast array of complex devices (processors) to construct and simulate a power system. In addition, these methods are approaching real time by increasing the incremental step size of computation and are not continuous mathematically as analog methods are. Analog approaches have already shown to be much faster than real time computation[1].

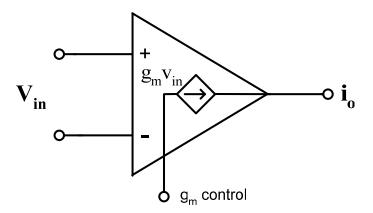

Current research in the analog field is pushing towards VLSI implementation of various analog technologies to realize a SoC and is well suited for power system analysis[1, 11-14]. Development in BiCMOS, MOST, BJT and other analog VLSI technologies are paving the way for large scale integration and accuracy for analog designs. Literally thousands of analog components can be fabricated on a wafer the size of a pushpin. In the older network analyzers the components were exceedingly large in comparison to microelectronics. Likewise as the system to be represented by the analyzer grew in size so did the analyzer itself. A realization of large systems with thousands of components is simply not feasible through a NA. VLSI is the solution. Neural network computation methods is a VLSI example being studied[15, 16] along with Evolvable Hardware (EH)[17]. In this thesis modeling of power transmission lines is accomplished with Operational Transconductance Amplifiers (OTAs) which are fundamental building blocks of VLSI circuits. OTA technology specifically lends itself well to fabrication on a large scale and allows for remote reconfiguration via a

controllable bias current allowing remote programmability in a large scale analog emulator for power systems.

### **1.3 MOTIVATION**

The main advantage of analog computational methods is speed through the pure parallelism exhibited. This technology has the potential to create a real-time or faster than real time computation engine for large complex systems, specifically in this case power systems. This can result in better planning and operation which leads to fewer power outages. Power outages are very expensive, specifically for business operations, and current computational methods do not allow full contingency analysis to be conducted during system operation. Faster computational tools can be used during system operation to help eliminate downtime and make the power grid more secure and robust.

For the most part the power grid is extremely reliable. The majority of power outages are alleviated quickly and do not result any major problems. Unfortunately the outages that are not alleviated quickly or easily tend to cause more serious problems, especially economically. In addition, with the interconnection present in the power grid cascading failures are becoming more and more common and at this time are of great concern in planning and operation stages. These failures affect large areas of power transmission and distribution systems and require more time to fix the problems and bring equipment back online. A study published in 2004 by Lawrence Berkeley National Laboratory (Berkeley Labs) estimated that power outages result in monetary losses of eighty billion dollars annually[18] in America. With economic effects of that magnitude

the motivation to push for even higher reliability of electric power is warranted. Some companies are so sensitive to power outages they build and operate their own power generation stations (cogeneration) to supplement utility power and to provide for critical loads in the event of a utility blackout. This is popular in manufacturing facilities where hours of downtime result in millions of dollars in losses of revenue. Table 1[19] details the revenue loss in dollars per hour of operation and per employee-hour for different sectors of the economy.

| INDUSTRY SECTOR              | REVENUE/HOUR | REVENUE/EMPLOYEE-HOUR |

|------------------------------|--------------|-----------------------|

| Energy                       | \$2,817,846  | \$569.20              |

| Telecommunications           | 2,066,245    | 186.98                |

| Manufacturing                | 1,610,654    | 134.24                |

| Financial institutions       | 1,495,134    | 1,079.89              |

| Information technology       | 1,344,461    | 184.03                |

| Insurance                    | 1,202,444    | 370.92                |

| Retail                       | 1,107,274    | 244.37                |

| Pharmaceuticals              | 1,082,252    | 167.53                |

| Banking                      | 996,802      | 130.52                |

| Food/beverage processing     | 804,192      | 153.10                |

| Consumer products            | 785,719      | 127.98                |

| Chemicals                    | 704,101      | 194.53                |

| Transportation               | 668,586      | 107.78                |

| Utilities                    | 643,250      | 380.94                |

| Health care                  | 636,030      | 142.58                |

| Metals/natural resources     | 580,588      | 153.11                |

| Professional services        | 532,510      | 99.59                 |

| Electronics                  | 477,366      | 74.48                 |

| Construction and engineering | 389,601      | 216.18                |

| Media                        | 340,432      | 119.74                |

| Hospitality and travel       | 330,654      | 38.62                 |

| Average                      | \$1,010,536  | \$205.55              |

Table 1: Cost of System Downtime in Different Industries

Improving grid reliability makes sense economically. While improving the infrastructure of the power system along with maintenance of the current system yield better reliability the most critical component is in power system operation. This is where faster computation can lead to improved reliability. Power system operators want to economically dispatch electrical energy while allowing for system faults (contingencies) without loss of power to any customers. This particular analysis requires massive computational efforts specifically related to contingency analysis, furthermore, this problem is growing even worse with the trend of deregulation. Prior to deregulation each utility locally operated their power system with minimal or no interaction with other utilities. The analysis was mainly limited to a single utility's power system. Now Regional Transmission Organizations (RTO), such as PJM, operate huge sections of the power grid and are required to run these analyses on systems with tens of thousands of nodes or buses. It is not feasible with current digital computation technology to run all the desired analysis while operating the system. Simplifying assumptions are made along with approximations on failure modes to speed up the processes and meet the demands of power system operation. If real-time computational tools are developed more thorough analyses could be conducted without the need for as many assumptions and shortcuts. Properly applied this increase in system analysis for real-time operations should allow better power system operation and higher reliability.

## **1.4 PROBLEM STATEMENT**

The objective was to expand upon a previously proposed DC emulation power flow technique by developing more detailed transmission line models and also to develop these line models in low-cost analog hardware. Particularly, the analog hardware should be fast, accurate, remotely reconfigurable, and scalable for large system modeling and have the capability to be easily implemented into a VLSI design.

## **1.5 ORGANIZATION OF THESIS**

The software tools utilized along with the hardware testing environment is outlined in chapter 2. Chapter 3 provides some background theory on power transmission line modeling and Chapter 4 contains an overview of a specific methodology for analog emulation of power systems and the modeling of power system components with emphasis on transmission lines. Specific details of numerous transmission line models for emulation are presented. Chapter 5 introduces the analog circuits and their associated components for the analog emulation line models with the inclusion of software and hardware verification of these circuits. Chapter 6 follows this development with verification and analysis of the analog transmission line models constructed with the analog components introduced in the preceding chapter through software simulation and hardware testing. In conclusion chapter 7 summarizes the work presented in this thesis and the progress made in this research topic with these contributions followed by recommendations for future work.

### 2 DESIGN AND BENCHMARKING ENVIRONMENT

## **2.1 OVERVIEW**

The work presented in this thesis deals with the formulation and development of transmission line models for the purpose of analog power-flow emulation. During the development of these models numerous hardware (HW) and software (SW) tools were utilized. These tools were used to aid the design process, test the designs against their desired performance, verify the analog circuit functionality and validate the results as applied to power-flow computation. In the development of a hardware prototype representing a network of transmission lines a combination of HW and SW were used for powering, actuating, acquiring data and controlling the associated circuitry. Before the hardware prototype was constructed software tools were used in design, simulation and verification of the line models. More specifically, the circuit design tool PSpice was utilized for software simulations. All emulation results, from both SW simulations and HW testing, were compared directly with commercially available power-flow packages.

## 2.2 PSPICE

PSpice is a software tool for electronic circuit analysis. It is utilized heavily in the work presented in this thesis. The acronym SPICE refers to Simulation Program for Integrated Circuits Emphasis. This software represents and analyzes circuits through a netlist and component models. A netlist is a text based file which specifies electronic components in the circuit and their interconnections. Each electrical component has an associated PSpice model which mathematically represents its input/output behavior in the

PSpice software along with other information such as pin outs and size of the physical device. With this information mathematical circuit analysis is conducted based on the component models and their interconnections. Specifically, a commercially available product OrCad Capture CIS [20] was used which is published by Cadence. This software package utilizes a PSpice backend for computation and evaluation of circuit behavior via a netlist and also includes a robust graphical user interface.

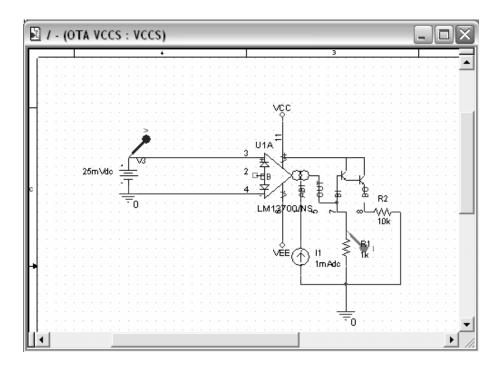

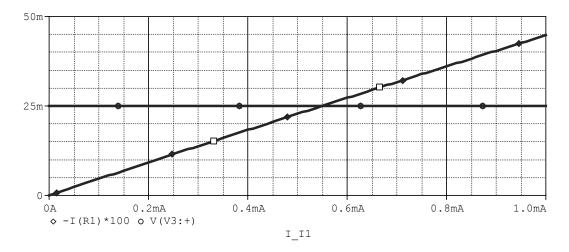

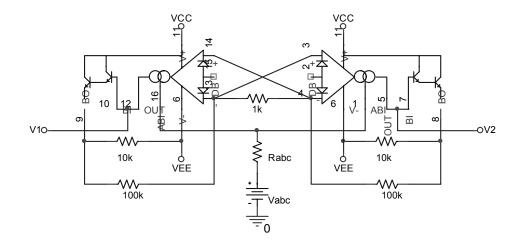

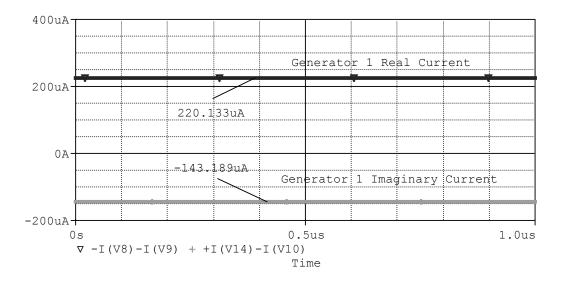

The interface allows for the construction of circuits by creation of an electrical schematic. The netlist is then automatically produced by the software based on the schematic representation of the circuit. Simulations are conducted and data analyzed by file outputs or graphically through the use of probes. These probes are graphically applied to the circuit schematic and measure the electrical signals and other characteristics which can then be visually plotted. The two basic probes measure current and voltage. In addition, the data from these probes can be processed mathematically to compute other values of interest such as power dissipation or Fourier analysis. Figure 3 shows a PSpice schematic of a simple OTA voltage controlled current source (VCCS). There is a voltage probe on the input of the device and a current probe on the output. The bias current, supplied by current source I1, is the independent variable which controls the gain of the OTA. The output current varies for a fixed input voltage with the bias current. Figure 4 is the plot generated from the probes in the circuit in Figure 3 and is an example of how signals are plotted and can then be analyzed based on probes inserted in the schematic.

Figure 3: PSpice Electrical Schematic with Voltage and Current Probes

Figure 4: PSpice Plot of Probed Signals vs. Bias Current

PSpice was utilized extensively for the design and verification of the analog transmission line models and analog circuit components in this thesis. This was useful because behavior of the circuits can be tested through the software based circuit models without the need to construct the circuits in hardware. However these models are approximations of the real device and many components are treated as ideal in the analysis. Assumptions are made to simplify both the models and the computation of their behavior. With this in mind there are inherent differences between the simulation results and the hardware results. This does not invalidate the simulations in anyway but this fact must be recognized when transferring circuits from the simulation environment into hardware. Minor discrepancies in results should be expected and drastic differences can occur if the component models are not an accurate representation of the hardware components. In an attempt to minimize such discrepancies all of the PSpice component models used in this work were obtained directly from the manufacturers of the devices. This was done as an attempt to represent the actual circuit behavior as closely as possible. The hardware prototype was built based off the designs tested through PSpice circuit simulations and include the same electrical components. For comparison to the end application of power-flow both the circuit simulations and hardware results were compared to PowerWorld power-flow solutions [21].

#### 2.3 POWERWORLD

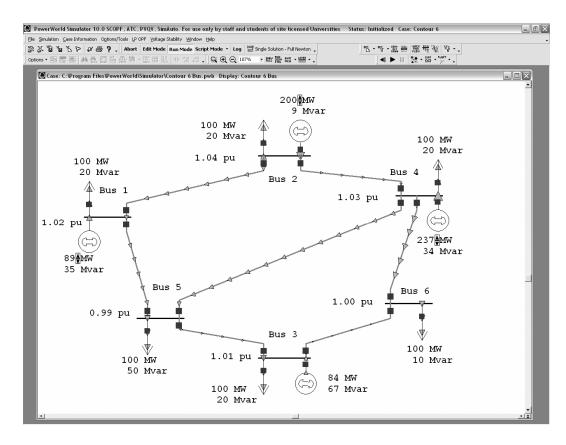

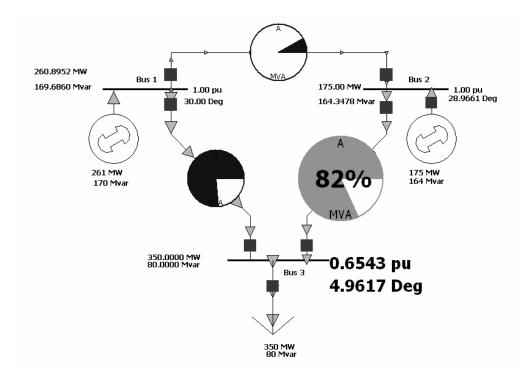

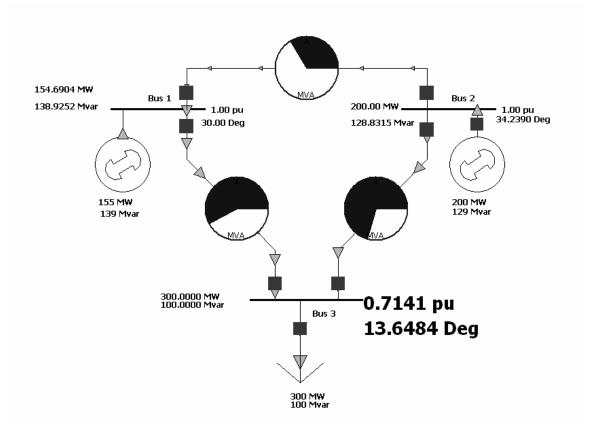

PowerWorld is a visually based software package for power system analysis. More specifically the basic application of this software is to solve static power-flow problems. The power system is represented by a single line graphical diagram consisting of power system components. Figure 5 shows a one line diagram of a six bus power system in PowerWorld. It consists of generators, transmission lines and loads. The parameters of these components are user adjustable and set to represent their real world counterparts. The dialog box for adjusting transmission line parameters and setting other options is shown in Figure 6. Adjustments and settings can be made for transmission line impedances, power-flow limits and fault parameters. The flow of power through the system is even represented graphically based on the numerical solutions obtained. This can be seen by the green arrows in Figure 5. In addition, this software has other capabilities such as optimal power-flow solvers, economic analysis and area generation control but is utilized in this work only for its static Newton-Raphson power-flow solver. The results of this solver are compared directly to the PSpice and hardware results of the analog line models for validation purposes. Error analysis is conducted on the differences between this power-flow solver and the analog emulation results.

Figure 5: PowerWorld One Line Diagram of a 6 Bus Power System

| Transmission Line/Transformer Options                                                                                                                         |                                                     |                      |                              |      |                                                 |                                 |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|------------------------------|------|-------------------------------------------------|---------------------------------|---|

| From Bus     To Bus     Circuit       Number     \$     4     1       Name     Five     Four       Nominal kV     138.0     138.0       Area Name     1     1 |                                                     |                      |                              |      |                                                 |                                 |   |

| Labels                                                                                                                                                        |                                                     |                      |                              |      |                                                 |                                 |   |

| Parameters / Display                                                                                                                                          | Series Capacitor                                    | Fault Pa             | rameters   Ow                | ners | 1                                               |                                 |   |

| Status<br>Open<br>Occosed                                                                                                                                     | Series Resistar<br>Series Reactan<br>Shunt Charging | ice (X)              | 0.04000<br>0.08000<br>0.0200 | _    | Limit A (MVA)<br>Limit B (MVA)<br>Limit C (MVA) | 100.000<br>1000.000<br>1000.000 |   |

| Line Shunts<br>Calculate Per Un                                                                                                                               |                                                     | Length               | 0.00                         | 4    | Limit D (MVA)<br>Limit E (MVA)<br>Limit F (MVA) | 0.000<br>0.000<br>0.000         | ~ |

| Convert Line to Transformer Display Pixel Thickness 3  Symbol Segment 1                                                                                       |                                                     |                      |                              |      |                                                 |                                 |   |

| Anchored                                                                                                                                                      | Line                                                | Symbol S<br>Symbol F | äize<br>Percent Length       |      | 4                                               |                                 |   |

|                                                                                                                                                               | Save                                                |                      |                              |      | X Cancel                                        | <b>?</b> He                     |   |

Figure 6: PowerWorld Transmission Line Options

With respect to the main contribution of this work, PowerWorld software was used to construct a three bus power system which was used as a basis of comparison to a three bus analog hardware prototype based on the analog line models derived within this thesis. This three bus system consisted of two generators, three transmission lines and a single load.

## 2.4 HARDWARE

Hardware tools were utilized for data acquisition, measurement, actuation/configuration, and control of an analog three bus power system prototype.

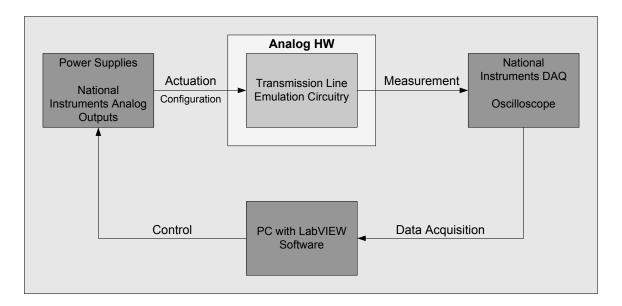

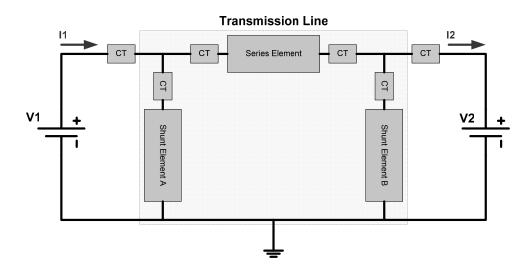

Oscilloscopes and a National Instruments Data Acquisition (DAQ) card, specifically model # NI PCI-6071E, were used for monitoring and acquiring data from the circuits. DC power supplies and a National Instruments analog output card, model # NI PCI6703, were used for actuation and control of the hardware. Specifically transmission line parameters were set and varied via PC control of the National Instruments analog output card. This control was accomplished through National Instruments LabVIEW[22] software which interfaces with the National Instruments DAQ and analog output cards. The LabVIEW software introduces a graphical programming environment to control power supplies and output cards, in this case an analog output card, and measure data from DAQ cards. Figure 7 details, through a block diagram, the hardware setup for testing of the transmission line prototype. This setup allows remote control, configuration and actuation of the transmission line circuits along with data acquisition from the analog hardware.

Figure 7: Analog Emulation Hardware Test Setup

### **3** POWER TRANSMISSION LINE MODELING

### 3.1 OVERVIEW OF TRANSMISSION LINE MODELING

The transmission line transmits electrical power from one end of the line, sending end, to another, receiving end. A common method of analyzing this behavior is through parameterization and modeling of the transmission lines with passive components. The passive components used in this modeling are resistors, capacitors and inductors. The quantity of these parameters depends mainly on the conductors used in the lines and the physical or geometrical configuration of the lines. The conductors themselves will have certain characteristics such as resistance and reactance both in series from sending to receiving ends of the line and shunt from the line to electrical ground associated with them. In addition, there is inherently mutual inductance, or coupling, of the lines with respect to each other as they are bundled together or placed in close proximity to one another in a multi-phase system. This can all be taken into account through proper analysis and parameterization of the transmission lines. This chapter does not derive the parameterization of the lines but provides an overview of steady state analysis of transmission lines after the line parameters have been obtained.

In this thesis only the sinusoidal steady state of the transmission lines is examined. No dynamic analysis or consideration is taken. The work here is geared mainly towards power-flow studies in which the steady state behavior of the transmission lines is focused on with the dynamics neglected. In a power system the dynamics of generators and loads are much more substantial in both magnitude and time duration and affect the system more than the transmission line dynamics. It is a reasonable assumption to neglect the transmission line dynamics for power-flow studies and generator/load dynamics should be introduced into power system analysis before the dynamic behavior of transmission lines is considered.

A conventional method of modeling steady state transmission lines is through either distributed or lumped parameterization. The latter is a simplification of the former. The next sections detail the derivation of the distributed line model and the methodology and justification of lumped parameter equivalent models. Most of this information was gathered from[23, 24].

### **3.2 DISTRIBUTED TRANSMISSION LINE PARAMETERS**

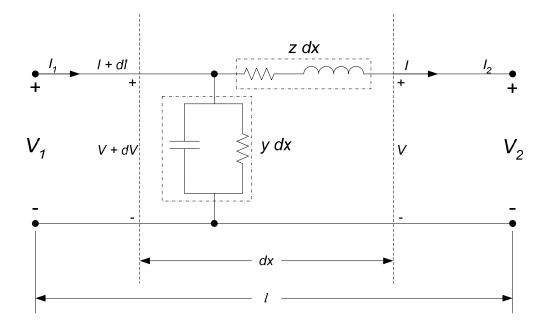

The distributed transmission line model gains its name from 'distributing' the parameters of the line equally through the line. The parameters are quantified per unit length and are additive in nature as the length of the line increases. This is effective for wave propagation analysis along the line as well as at the terminals of the line. Specifically for a power transmission line the voltage and current behavior along the line is of interest. Power transmitted through the line as well as losses can be observed and determined from these quantities. A diagram for a segment of a distributed transmission line is shown in Figure 8 [24]. The line model segment consists of a series impedance and a shunt admittance. The overall distributed transmission line model consists of a summation of these line segments.

Figure 8: Distributed Parameter Transmission Line Model

The series impedance of the line is represented by a resistance in series with an inductance. This is quantified per unit length as follows:

$$z = r + j\omega l \tag{3.1}$$

The series resistance r and the series inductance l are quantified respectively as ohms per unit length and henrys per unit length. The term  $\omega$  represents the operational angular frequency of the AC power system in radians per second. The resulting impedance of the inductor is therefore dependant on the operational frequency of the system. In this thesis lower case letters will be used for distributed parameters and upper case letters for lumped parameters. The shunt elements of the line model consist of a capacitance and a resistance in parallel with each other. The admittance of this shunt element is quantified by:

$$y = g + j\omega c \tag{3.2}$$

The capacitor admittance is also dependant on the system operational frequency.

As shown in Figure 8, the length of the whole line is denoted by l and the length of the differential segment by dx. The series impedance across a segment is zdx and the shunt segment ydx.  $V_1$  and  $I_1$  denote the voltage and current at the sending end, x = 0, and  $V_2$  and  $I_2$  at the receiving end, x = l. A voltage drop dV appears across the series element of the line and a current dI flows through the shunt element. Two first-order differential equations (3.3) quantify the voltage drop and current loss of the line[24].

$$\frac{dV}{dx} = zI$$

$$\frac{dI}{dx} = yV$$

(3.3)

This same behavior can also be represented by a single second-order linear equation in terms of either current or voltage:

$$\frac{d^2V}{dx^2} = yzV = \gamma^2 V \tag{3.4}$$

$$\frac{d^2I}{dx^2} = yzI = \gamma^2 I \tag{3.5}$$

The term  $\gamma$  is called the propagation constant. Solving the differential equations yields the following solutions [24]:

$$V = V_2 \cosh(\gamma x) + Z_c I_2 \sinh(\gamma x)$$

$$I = I_2 \cosh(\gamma x) + \frac{V_2}{Z_c} \sinh(\gamma x)$$

(3.6)

These equations yield the voltage and current at any point along the transmission line designated by x. The term  $Z_c$  is referred to as the characteristic impedance of the line and is computed by:

$$Z_c = \sqrt{z/y} \tag{3.7}$$

The terminal voltages and currents are usually of more interest and can be computed by setting x = l:

$$V_{1} = V_{2} \cosh(\gamma l) + Z_{c} I_{2} \sinh(\gamma l)$$

$$I_{1} = I_{2} \cosh(\gamma l) + \frac{V_{2}}{Z_{c}} \sinh(\gamma l)$$

(3.8)

The lumped parameter model is a simplification of the distributed model and was developed to model only the terminal relationships at the sending end and receiving end of the transmission lines. It was derived from (3.8) but contains no information of voltage and current as they propagate down the line. Voltage and current information at

any point along the line can be useful but where it is not required the simplified lumped models are adequate.

## **3.3 LUMPED TRANSMISSION LINE PARAMETERS**

Traditionally in power flow analysis the voltages and currents at the line terminals are the values of more interest as compared to points along the transmission line. Historically the wave propagation on the lines is neglected and a simplified lumped parameter model is implemented for power flow. To develop the lumped model equation (3.8) can be put in the following form [24]:

$$V_1 = AV_2 + BI_2 I_1 = CV_2 + DI_2$$

(3.9)

where:

$$A = \cosh(\gamma l)$$

$$B = Z_c \sinh(\gamma l)$$

$$C = \frac{1}{Z_c} \sinh(\gamma l)$$

$$D = \cosh(\gamma l)$$

(3.10)

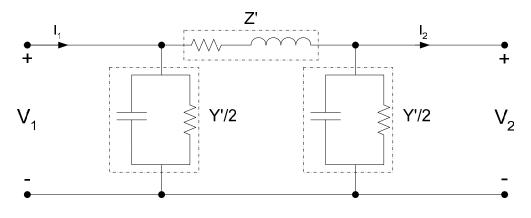

The lumped transmission line model holds the appropriate terminal behavior in equation (3.9) with lumped circuit elements. A  $\pi$ -equivalent circuit for this purpose is shown in Figure 9.

Figure 9: Lumped Parameter II-Equivalent Transmission Line

Passive elements model the series and shunt elements in this model. The effects of the distribution of impedance across the line are lumped together in quantities of ohms. They are related to the length of the line but are not in terms of unit length. By appropriately picking the values of Z' and Y'/2 the same terminal behavior of the distributed line is held. Utilization of Kirchoff's voltage (KVL) and current (KCL) laws to the lumped parameter circuit in Figure 9 yield the following results [24]:

$$V_{1} = V_{2} + Z' \left( I_{2} + \frac{Y'}{2} V_{2} \right)$$

=  $\left( 1 + \frac{Z'Y'}{2} \right) V_{2} + Z' I_{2}$  (3.11)

$$I_{1} = \frac{Y'}{2}V_{1} + \frac{Y'}{2}V_{2} + I_{2}$$

=  $Y'\left(1 + \frac{Z'Y'}{4}\right)V_{2} + \left(1 + \frac{Z'Y'}{2}\right)I_{2}$  (3.12)

Comparing (3.11) and (3.12) to (3.9) allows the quantification of the A, B, C, and D parameters for the lumped equivalent circuit.

$$A = 1 + \frac{Z'Y'}{2}$$

$$B = Z'$$

$$C = Y' \left( 1 + \frac{Z'Y'}{4} \right)$$

$$D = 1 + \frac{Z'Y'}{2}$$

(3.13)

Solving for the components Z' and  $\frac{Y'}{2}$  in Figure 9 yields:

$$Z' = Z_c \sinh(\gamma l) \tag{3.14}$$

$$\frac{Y'}{2} = \frac{1}{Z_c} \tanh\left(\frac{\gamma l}{2}\right)$$

(3.15)

The formulation here allows the quantification of parameters in a lumped  $\pi$ equivalent circuit with respect to the length, characteristic impedance and the propagation

constant of the line. Resistors, capacitors and inductors for the lumped model are sized

by (3.14) and (3.15). From there circuit analysis on the resultant RLC circuit will

maintain the appropriate terminal behavior. In a similar manner a T equivalent circuit

could be constructed with two series impedance elements and one shunt impedance

element. This is simply a transformation of the  $\pi$  model which holds the same terminal

relationship. For shorter length transmission lines this derivation may be simplified.

For lines that are not particularly long  $|\gamma l| \ll 1$ . If this is the case small angle approximations can be made to (3.14) and (3.15) to simplify the computation without

substantial loss in computational accuracy. The next section deals with this simplification along with the omission of certain passive elements to simplify the lumped model even further.

### **3.4 LUMPED PARAMETER TRANSMISSION LINE MODELS**

The prior sections introduced both distributed and lumped parameter transmission line modeling. Specifically the lumped parameter model was a  $\pi$ -equivalent circuit which incorporates shunt resistive and capacitive elements along with series resistive and inductive elements. Certain simplifying assumptions can be made to this lumped equivalent circuit based on the length of the transmission line. Four different line models are presented here based on the transmission line length. As the lines become shorter certain parameters have a minimal effect on the terminal voltages and currents of the line and can then be neglected.

For a *long transmission line* (l > 150 miles) no approximations should be made. The circuit elements for a  $\pi$ -equivalent circuit should be computed by (3.14) and (3.15). For this  $\pi$ -equivalent circuit the characteristic impedance and propagation constant are computed as follows:

$$\gamma = \sqrt{yz} = \sqrt{(g + j\omega c)(r + j\omega l)}$$

=  $\sqrt{gr - \omega^2 cl + j(\omega cr + \omega gl)}$  (3.16)

$$Z_{c} = \sqrt{\frac{z}{y}} = \sqrt{\frac{r + j\omega l}{g + j\omega c}}$$

(3.17)

With  $\gamma$  and  $Z_c$  the complex values of Z'and Y'/2 are computed. The RLC circuit elements are then sized for the equivalent circuit in Figure 10. This representation will be referred to as the *long transmission line* model.

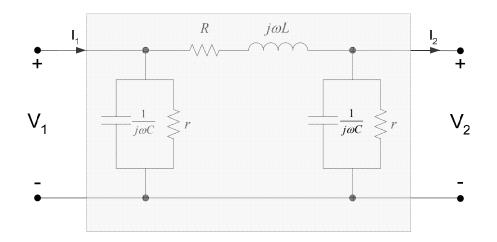

Figure 10: Long Transmission Line Model

where:

$$Z' = R + j\omega L \tag{3.18}$$

$$\frac{Y'}{2} = \frac{1}{r} + j\omega C \tag{3.19}$$

Note that "r" in (3.19) is a lumped parameter. It is in lower case here to differentiate it from the series resistive element. This shunt resistive element can be neglected if a transmission line is less than 150 miles in length. This is defined as a *medium length transmission line*.

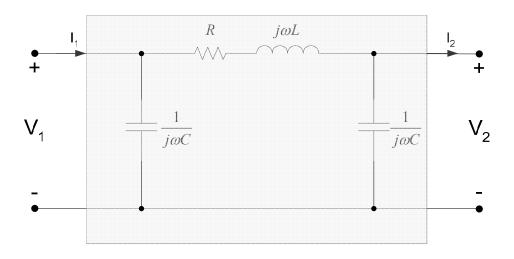

The resistive shunt current flow on a transmission line is usually very small and is proportional to the terminal voltage magnitude. This element's contribution is only significant in longer high voltage transmission lines. For medium length lines this component is neglected with little discrepancy in calculated results. If the shunt resistance of the line is neglected the lumped equivalent circuit will yield the form in Figure 11.

Figure 11: Medium Length Transmission Line Model

Further approximations are also made for this model. No longer are the propagation constant and characteristic impedances used to calculate the RLC elements in the lumped circuit. The following approximations are made:

$$Z' \approx Z = zl = R + j\omega L \tag{3.20}$$

$$\frac{Y'}{2} \approx \frac{Y}{2} = yl = -j\omega C \tag{3.21}$$

This is simpler than the long line model computation. The elements in this model can be quantified by the line length and parameters in per unit length. No hyperbolic functions are necessary. Next further approximations are made for short transmission line. A short transmission line is defined as a line less than 50 miles in length.

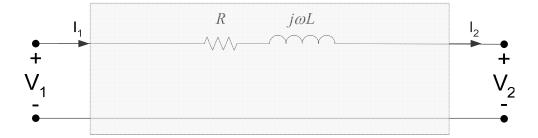

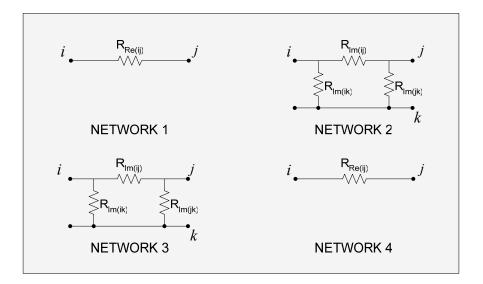

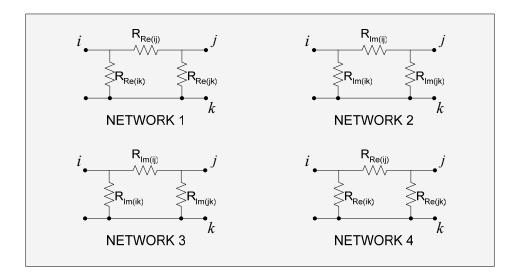

For short transmission lines all the shunt elements are neglected. The argument for this is that the shunt charging due to the shunt capacitance is negligible for short transmission lines and eliminating them from the modeling results in little inaccuracy. Two short transmission line models are represented here. One is referred to as a *short lossy transmission line* and the other *short lossless transmission line*. The lossy model incorporates both the series resistor and inductor components shown in Figure 12. The term lossy is formulated from the presence of  $I^2R$  real power losses in the model. Small angle approximations are again used and the components in this model are quantified by equation (3.20).

Figure 12: Short Lossy Transmission Line Model

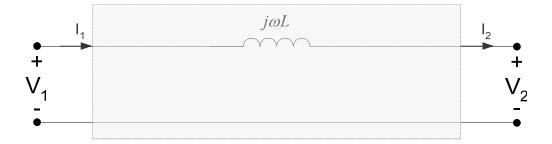

The fourth and final lumped line model considered here is the short lossless line model. This is the simplest representation of a power transmission line and is often used in distribution system line modeling and for very short lines. This is also fairly popular in power flow solvers in order to simplify and speed up calculations. This model is simply a series inductive element shown in Figure 13. The absence of the series resistor, and real power losses, is why the model is called lossless.

Figure 13: Short Lossless Transmission Line Model

The inductor in this model is sized by the following equation:

$$Z = j\omega L \tag{3.22}$$

Four lumped line models have been presented, specifically long, medium, short lossy and short lossless models. Care must be taken when to incorporate which model in calculations to prevent large errors in the results. Guidelines have been given in [24] with respect to the transmission line length. This is summarized in Table 2 and each line type is labeled by a letter. Intuition indicates that the short lossless line model should only be used in lines much less than 50 miles in length.

| Line Model | Transmission Line<br>Length | Appropriate<br>Lumped Model | Assumptions<br>Made                                                                                          |

|------------|-----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------|

| Α          | $l \ll 50$ miles            | Short Lossless              | <ul> <li>-all shunt element<br/>neglected</li> <li>-series resistance<br/>neglected</li> <li>Z'≈Z</li> </ul> |

| В          | <i>l</i> < 50 miles         | Short Lossy                 | -all shunt elements<br>neglected<br>$Z' \approx Z$                                                           |

| С          | $50 \le l < 150$ miles      | Medium Line                 | -shunt resistor<br>neglected<br>$\frac{Z' \approx Z}{\frac{Y'}{2} \approx \frac{Y}{2}}$                      |

| D          | $l \ge 150$ miles           | Long Line                   | None                                                                                                         |

Table 2: Details on Lumped Line Models

The four lumped line models presented here are the basis for the analog transmission line modeling for power flow in this thesis. Analog circuit equivalents to the four models derived are developed and tested for the analog power flow emulation. Chapter 4 details this analog power flow method and the modeling of power system components with emphasis on the transmission lines for this application.

## **4** ANALOG EMULATION OF A POWER SYSTEM

#### 4.1 INTRODUCTION

In this chapter the analog DC emulation power flow methodology is examined. The fundamental theory behind this computational approach is presented along with a characterization of the power system model employed in this emulation environment. Each power system component is identified separately in this context. The mathematical models are presented with emphasis on application to this particular emulation scheme. This DC emulation approach is utilized here but other methods have been investigated.

There are various approaches for analog computation of power systems that have been introduced over the years. Three different methods have been outlined in [12, 13], functional analog computation, DC emulation and AC emulation of the power system. More specifically, functional analog computation is similar to the old generic analog mathematical computation methods but with one key difference. It is specialized specifically to power system problems. It consists of analog computation blocks based on electrical equations. These are pieced together in a manner to solve the desired problem. In the DC emulation technique, which is utilized here, the states of the power system network are represented by DC voltages and currents in equivalent DC networks. The elements in the network are inherently frequency independent. This is discussed in more detail later. The latter approach, AC emulation, is analogous with both the old and new AC network analyzers. The emulation of the system is done in pure AC and the elements are all frequency dependant. "The main difference between the AC and DC emulation approaches is the fact that in the AC approach the computation is performed instantaneously, whereas in the DC approach it is only the signals' envelopes which are

being computed."[13] These represent three different approaches to the same problem and encompass many things in common with each other.

The prevalent common theme in the aforementioned emulation techniques is the necessity to model power system components. Whether it is an analog computation element, a DC network, or an AC network there requires behavioral representation of the real world power system components. The results of the subsequent computation will only be as precise as the system models and definitions. For the DC emulation method used here the classical power system model is utilized which contains three main components: generators, transmission lines and loads.

#### 4.2 ANALOG POWER SYSTEM DC EMULATION METHODOLOGY

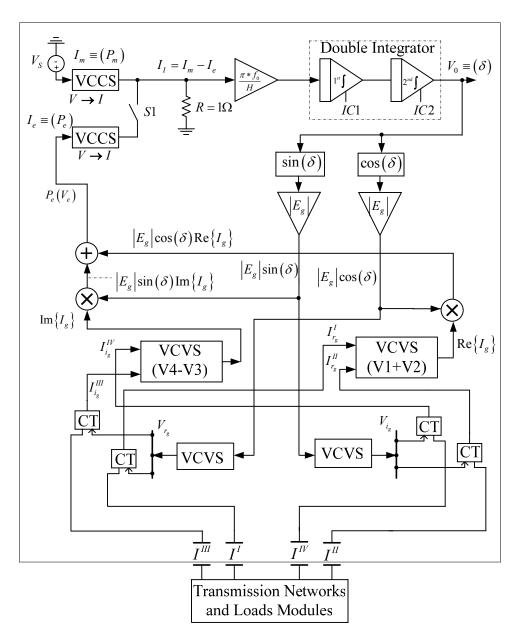

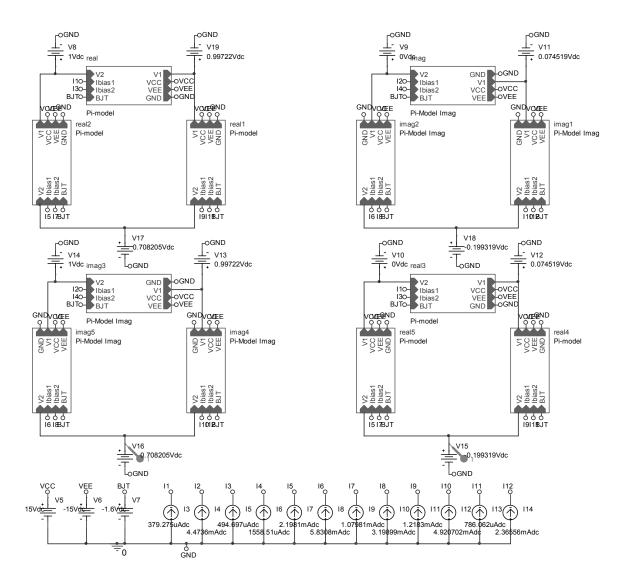

The power system network in the DC emulation technique is represented in rectangular coordinates. The power system parameters are separated into real and imaginary components and the states, voltages and currents, are also separated into real and imaginary components which are represented by DC voltage and current levels. With this method only the magnitude of the signals requires to be measured and phase can be computed later. This permits the use of DC. The power system emulation network consists of generators, transmission lines and loads and is shown in Figure 14.

Figure 14: Power System Emulation Network

Any number of transmission lines, loads and generators can be combined together to represent a power system. Switches, relays, transformers and other power system components are not modeled here but are topics of future research. The fundamental components for power generation, transmission and consumption were analyzed here.

Power system computation in many digital applications is conducted in polar coordinates. This system details the magnitude and the angle of power system states and parameters. In the analog DC emulation technique the computation in the network is performed exclusively in rectangular (Cartesian) coordinates. All power system parameters and values are represented in rectangular and/or converted from polar form to rectangular form when necessary for application in the emulator. Figure 15 is a comparison of polar and rectangular representation of a vector V on a complex plane.

Figure 15: Polar and Rectangular Coordinate Comparison

The polar form representation contains two components, a vector magnitude and phase. It can be represented in the following manner:

$$V = |V| \angle \theta \tag{4.1}$$

The Cartesian coordinate representation consists of two magnitudes. One is purely real and lies on the real axis and the other is purely imaginary and lies on the imaginary axis. This representation is related to the magnitude and phase by (4.2) where  $V_{\text{Re}}$  and  $V_{\text{Im}}$  are the real and imaginary vector components respectively.

$$V = V_{\rm Re} + jV_{\rm Im} = |V|\cos(\theta) + j|V|\sin(\theta)$$

(4.2)

The rectangular form can easily be transformed into polar form by (4.3). Note that the sign of the quotient of  $V_{\rm Im}$  and  $V_{\rm Re}$  dictates what quadrant  $\theta$  lies. If the quotient is positive  $\theta$  is located in the first quadrant and if negative  $\theta$  lies in the fourth quadrant.

$$|V| = \sqrt{V_{\text{Re}}^2 + V_{\text{Im}}^2}$$

$$\theta = \tan^{-1} \left(\frac{V_{\text{Im}}}{V_{\text{Re}}}\right)$$

(4.3)

The specifics of the previously proposed DC emulation method were first introduced in [12] and highlighted and expanded upon here. The method roots itself in solving the network matrix equation in rectangular coordinates. This equation simply relates the current flow in the network to a voltage applied to the admittance of the network:

$$[I] = [Y] \cdot [V] \tag{4.4}$$

The admittance matrix, [Y], is a nodal admittance matrix based on the power system topology and impedances of the transmission lines. Note that this is not a Y<sub>bus</sub> matrix and ground is considered a node in the construction of this matrix. With this in mind for an n-bus system this matrix would be (n+1) by (n+1) square. [I] is an (n+1) vector of the currents entering the network nodes and [V] is an (n+1) vector of the nodal voltages of the network. The multiplication of a complex admittance and a complex voltage in rectangular coordinates yields:

$$Y \cdot V = I_{\text{Re}} + jI_{\text{Im}} = (Y_{\text{Re}} + jY_{\text{Im}}) \cdot (V_{\text{Re}} + jV_{\text{Im}})$$

$$= Y_{\text{Re}}V_{\text{Re}} + jY_{\text{Re}}V_{\text{Im}} + jY_{\text{Im}}V_{\text{Re}} - Y_{\text{Im}}V_{\text{Im}}$$

$$= (Y_{\text{Re}}V_{\text{Re}} - Y_{\text{Im}}V_{\text{Im}}) \quad \{\text{real current}\}$$

$$+ j(Y_{\text{Im}}V_{\text{Re}} + Y_{\text{Im}}V_{\text{Re}}) \quad \{\text{imaginary current}\}$$

(4.5)

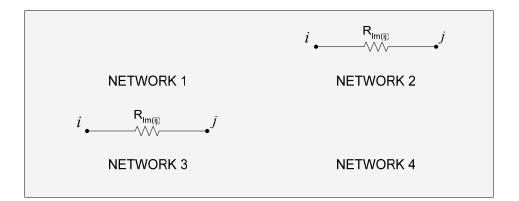

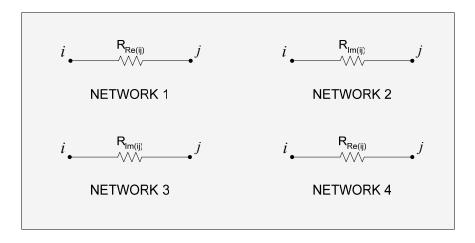

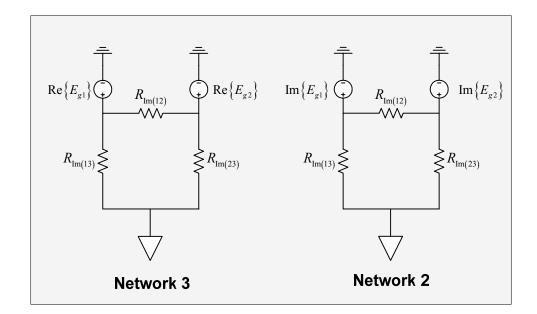

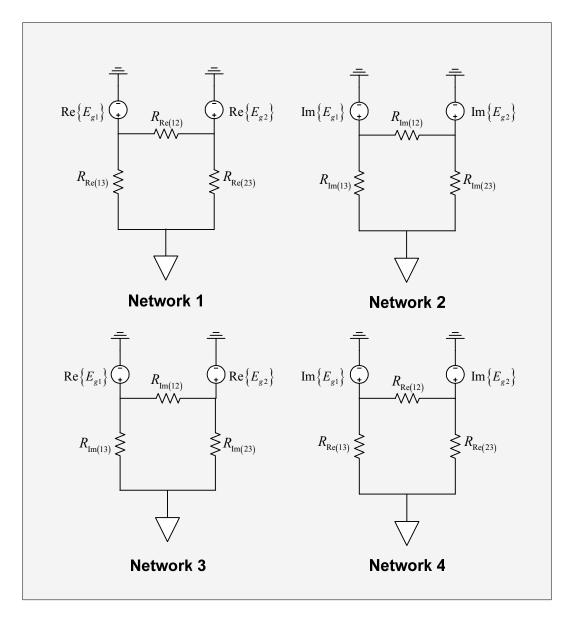

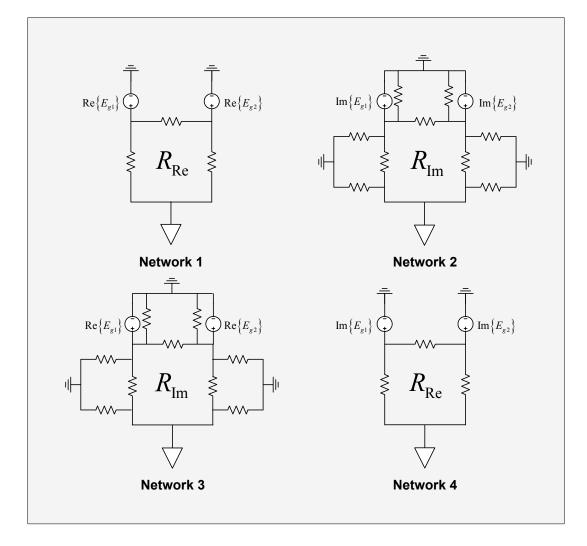

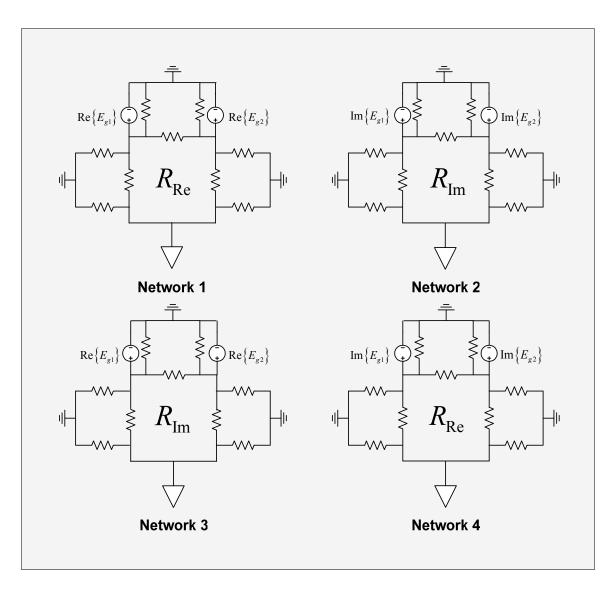

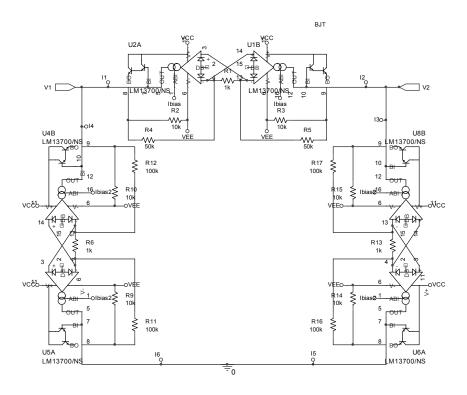

The real and imaginary components in (4.5) are labeled. For this case, with complex network impedances, there are a total of four current components. Each one is an admittance magnitude multiplied by a voltage magnitude. This behavior is identical to the resultant current flow based on a voltage drop across a resistor. This is how the DC emulation is conducted. Resistive networks represent the admittances and a voltage is applied to induce current flow. With four DC networks, one for each of the components in (4.5), the network equation can be solved. The solution to the power flow problem is specifically the voltages and currents flowing in these DC networks. This information needs to be extracted, or measured, from the analog circuits. Specifically the four networks are defined as follows:

$$I_{\text{Re}} + jI_{\text{Im}} = Y_{\text{Re}}V_{\text{Re}} \quad \text{network 1}$$

-  $Y_{\text{Im}}V_{\text{Im}} \quad \text{network 2}$

+  $jY_{\text{Im}}V_{\text{Re}} \quad \text{network 3}$

+  $jY_{\text{Re}}V_{\text{Im}} \quad \text{network 4}$  (4.6)

From a circuit viewpoint all the nodal voltages can be measured directly in rectangular coordinates, one imaginary voltage magnitude and one real voltage magnitude. Obtaining the rectangular current magnitudes is not as straight forward. Four currents must be measured and added together to obtain the branch current flow or injections in rectangular coordinates. Specifically the summation of currents in networks one and two equal the real current value and the summation of currents in networks three and four equate to the imaginary current component. More generally for any size system the current at a node i, such as a generator injection into the network, can be computed by:

$$I_{Gi} = \sum_{j=1}^{n+1} \operatorname{Re}\left\{Y_{ij}\right\} \cdot \operatorname{Re}\left\{V_{j}\right\} \text{ network 1}$$

$$-\sum_{j=1}^{n+1} \operatorname{Im}\left\{Y_{ij}\right\} \cdot \operatorname{Im}\left\{V_{j}\right\} \text{ network 2}$$

$$+j\sum_{j=1}^{n+1} \operatorname{Im}\left\{Y_{ij}\right\} \cdot \operatorname{Re}\left\{V_{j}\right\} \text{ network 3}$$

$$+j\sum_{j=1}^{n+1} \operatorname{Re}\left\{Y_{ij}\right\} \cdot \operatorname{Im}\left\{V_{j}\right\} \text{ network 4}$$

(4.7)

where  $\operatorname{Re}\{Y_{ij}\}$  and  $\operatorname{Im}\{Y_{ij}\}$  are the real and imaginary network admittances between nodes *i* and *j*, and  $\operatorname{Re}\{V_j\}$  and  $\operatorname{Im}\{V_j\}$  represent the real and imaginary voltage magnitudes at bus *j* respectively. The formulation in (4.7) is for an *n* bus system with (n+1) nodes with the inclusion of ground as a node.

The key to implementing this emulation technique is to develop accurate representation of the power system components to operate in the DC networks. The generators are modeled as PV buses and provide current injections and voltages at the generator buses, the transmission lines are passive resistive networks corresponding to the line impedances and the loads are modeled as current injections or sinks as necessary. The next section delves into the details of each power system emulation component.

#### **4.3 POWER SYSTEM EMULATION COMPONENTS**

This section outlines the three main power system components utilized in the DC emulation of power-flow. These components are representative of the classic power system model containing generators, loads and transmission lines. Each component is catered towards operation in rectangular coordinates and ideally a final circuit design would be easily scaled towards VLSI technology. Realistically a large scale implementation would be a system on a chip (SOC) application. Furthermore, the components should act as computational 'modules' and allow configuration to suit specific parameters of real world power systems. For example a generator module should be able to computationally represent any kind of generator, whether it is a nuclear plant or a smaller coal burning generating station.

# 4.3.1 GENERATORS

The generator is modeled as a constant voltage source behind internal impedance. This is sometimes referred to as the classical generator model shown in Figure 16 [25]. For the application in DC emulation the generator maintains a PV bus behavior. The real power output, P, and the generator terminal voltage, V, are specified and maintained by the model.

Figure 16: Classical Generator Model

The swing equation is solved to match the electrical power output of the generator with the specified mechanical input:

$$\overset{\bullet}{M}\overset{\bullet}{\delta} + D\overset{\bullet}{\delta} + P_e(\delta) = P_m \tag{4.8}$$

where M is the generator inertia coefficient and D is the damping coefficient of the generator. If damping is neglected solving (4.8) for the power angle results in the double integral shown in (4.9).

$$\delta = \frac{1}{M} \iint \left( P_m - P_e(\delta) \right) dt dt \tag{4.9}$$

With the solution of the power angle and a specified generator voltage magnitude the voltages to be applied to the networks can be determined in a similar manner as equation (4.2):

$$V_{\text{Re}} = |V|\cos(\delta)$$

$$V_{\text{Im}} = |V|\sin(\delta)$$

(4.10)