# Unbalanced Power Converter Modeling for AC/DC Power Distribution Systems

A Thesis

Submitted to the Faculty

of

**Drexel University**

by

Xiaoguang Yang

in partial fulfillment of the

requirements for the degree

of

Doctor of Philosophy

December 2006

# © Copyright 2006

Xiaoguang Yang. All Rights Reserved.

#### **ACKNOWLEDGEMENTS**

First, I would like to appreciate my advisor, Dr. Karen N. Miu for her guidance, encouragement, and support in the past years. Her consistent advice helps me gain invaluable knowledge and experiences through this work. I would like also to thank Dr. Halpin, Dr. Kwatny, Dr. Niebur and Dr. Nwankpa for serving on my committee.

Second, I would like to thank my friends, fellow students, and staff in CEPE for their help throughout my graduate years. I would like to knowledge Valentina Cecchi, Andrew S. Golder, Michael R. Kleinberg, Yiming Mao, Shiqiong Tong and Jie Wan for their friendship.

Finally, my special thanks to my wife Chuanhuan Zhou and my parents, for their love, patience, and understanding.

## **Table of Contents**

| LIST OF TA  | BLES   |                                                       | .vii |

|-------------|--------|-------------------------------------------------------|------|

| LIST OF FIG | URES   |                                                       | xiii |

| ABSTRACT    |        | X                                                     | viii |

| CHAPTER 1.  | INTRO  | DDUCTION                                              | 1    |

| 1.1         | Motiva | ations                                                | 1    |

| 1.2         | Object | ives                                                  | 3    |

| 1.3         | Summ   | ary of Contributions                                  | 4    |

| 1.4         | Organi | zation of Thesis                                      | 5    |

| CHAPTER 2.  | UNBA   | ALANCED CONVERTER MODELING: DIODE RECTIFII            | ER,  |

|             | THYR   | RISTOR CONVERTER AND PULSE-WIDTH-MODULAT              | ED   |

|             | (PWM   | O CONVERTER                                           | 7    |

| 2.1         | Unbala | anced Diode Rectifier and Thyristor Converter Models  | .11  |

|             | 2.1.1  | Thyristor Converter Model                             | .11  |

|             |        | 2.1.1.1 Delta-Connection Approach                     | .13  |

|             | 2.1.2  | Determine DC Current and Power in the Delta-Connected |      |

|             |        | Model                                                 | .17  |

|             |        | 2.1.2.1 Continuous Conduction                         | 20   |

|             |        | 2.1.2.2 Discontinuous Conduction                      | .22  |

|             | 2.1.3. | Participation Coefficients                            | .24  |

|             | 2.1.4. | Equivalence Transformation                            | .25  |

|             | 2.1.5  | Diode Rectifier Model                                 | .28  |

| 2.2        | Unbala | anced Puls | se-Width-Modulated (PWM) Converter Model29              |

|------------|--------|------------|---------------------------------------------------------|

| 2.3        | Three- | Phase Con  | nverter Model Under Two-Phase Operating Conditions32    |

| 2.4        | Evalua | ation of U | nbalanced AC/DC Converter Models34                      |

|            | 2.4.1  | Three-Ph   | ase Thyristor Converter Benchmark and Evaluation of the |

|            |        | Delta-Co   | onnected Model36                                        |

|            |        | 2.4.1.1    | Simulation Results of the Thyristor Converter           |

|            |        |            | Benchmark37                                             |

|            |        | 2.4.1.2    | Evaluating the Delta-Connected Thyristor Converter      |

|            |        |            | Model                                                   |

|            | 2.4.2  | Three-Pl   | nase Diode Rectifier Benchmark and Evaluation of the    |

|            |        | Delta-Co   | onnected Model44                                        |

|            |        | 2.4.2.1    | Simulation Results of the Diode Rectifier               |

|            |        |            | Benchmark44                                             |

|            |        | 2.4.2.2    | Evaluating the Delta-Connected Diode Rectifier          |

|            |        |            | Model                                                   |

|            | 2.4.3  | Three-Pl   | nase PWM Inverter Benchmark and Evaluation of the       |

|            |        | Delta-Co   | onnected Model47                                        |

|            |        | 2.4.3.1    | Simulation Results of the PWM Inverter Benchmark49      |

|            |        | 2.4.3.2    | Evaluating the Delta-Connected PWM Converter            |

|            |        |            | Model51                                                 |

| 2.5        | Comm   | nents      | 53                                                      |

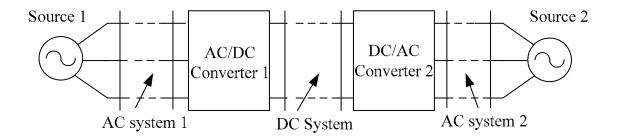

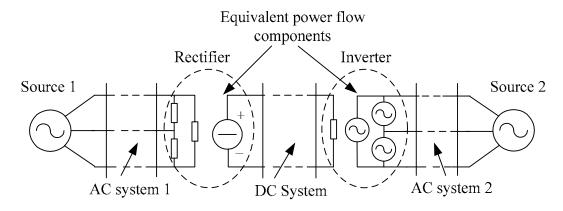

| CHAPTER 3. | THRE   | EE-PHAS    | E SEQUENTIAL DISTRIBUTION AC/DC POWER                   |

|            | FLOW   | <i>7</i>   | 55                                                      |

|            |        |            |                                                         |

| Three  | -Phase Power Flow Component Models                                              | 57            |

|--------|---------------------------------------------------------------------------------|---------------|

| 3.1.1  | Equivalencing the DC Systems to AC Power Flow                                   |               |

|        | Components                                                                      | 58            |

| 3.1.2  | Equivalencing the AC Systems to DC Power Flow                                   |               |

|        | Components                                                                      | 61            |

| AC/D   | C Power Flow Formulation                                                        | 65            |

| 3.2.1  | AC and DC System Nodal Analysis Equations                                       | 66            |

| 3.2.2  | Converter AC Bus Equations                                                      | 69            |

|        | 3.2.2.1 Thyristor Converters and Diode Rectifiers                               | 69            |

|        | 3.2.2.2 PWM Converters                                                          | 70            |

| 3.2.3  | Converter DC Bus Equations                                                      | 72            |

|        | 3.2.3.1 Thyristor Converters and Diode Rectifiers                               | 72            |

|        | 3.2.3.2 PWM Converters                                                          | 73            |

| Soluti | on Algorithm                                                                    | 74            |

| 3.3.1  | Ranking Method                                                                  | 74            |

| 3.3.2  | Backward/Forward Algorithm                                                      | 77            |

| MAT    | LAB Numerical Results                                                           | 83            |

| Comn   | nents                                                                           | 92            |

| 4. TH  | REE-PHASE UNIFIED DISTRIBUTION AC/I                                             | OC POWER      |

| FLOV   | V                                                                               | 93            |

| AC/D   | C Power Flow Formulation in MNA                                                 | 95            |

| 4.1.1  | Modified Nodal Analysis Equations for Thyristor Co                              | onverters and |

|        | Diode Rectifiers                                                                | 97            |

|        | 3.1.1 3.1.2 AC/D 3.2.1 3.2.2 3.2.3 Soluti 3.3.1 3.3.2 MATI Comm 4. TH FLOV AC/D | Components    |

|        |       | 4.1.2    | Modified Nodal Analysis Equations for PWM Converters101      |

|--------|-------|----------|--------------------------------------------------------------|

|        |       |          | 4.1.2.1 AC Current Controlled PWM Converters103              |

|        |       |          | 4.1.2.2 AC Voltage Controlled PWM Converters104              |

| 4      | 1.2   | Solution | on Algorithm106                                              |

| 4      | 1.3   | MATI     | AB Numerical Results                                         |

| 4      | 1.4   | Comm     | ents                                                         |

| CHAPT: | ER 5. | HARD     | WARE TEST BED FOR AC/DC POWER FLOW STUDIES125                |

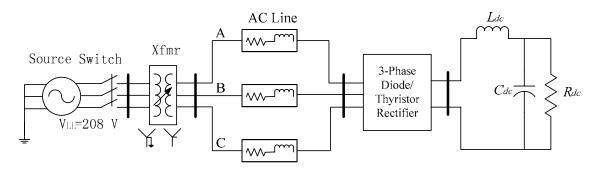

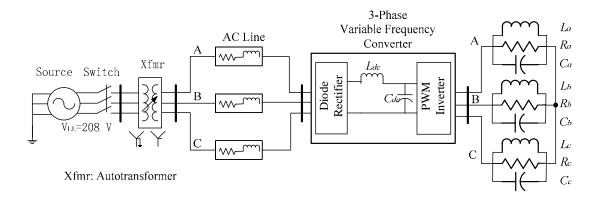

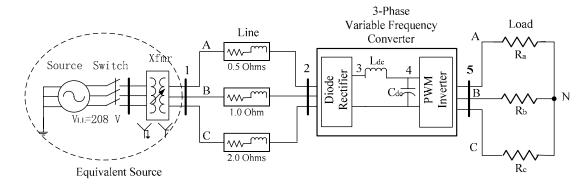

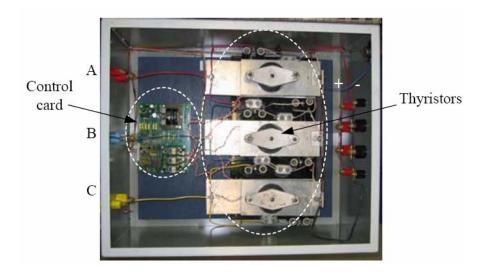

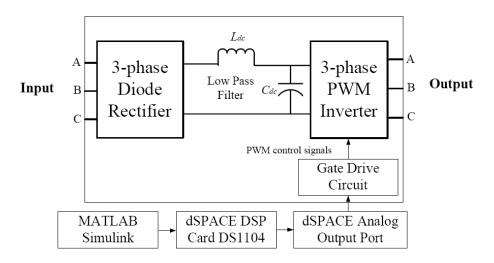

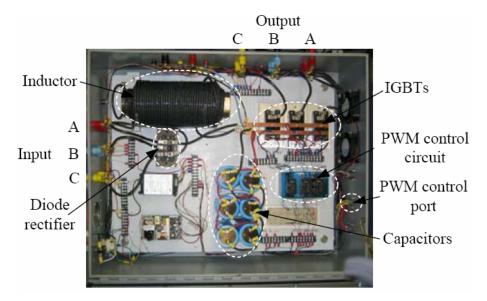

| 5      | 5.1   | Three-   | Phase AC/DC System Hardware Test Bed127                      |

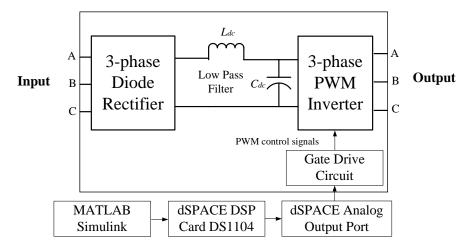

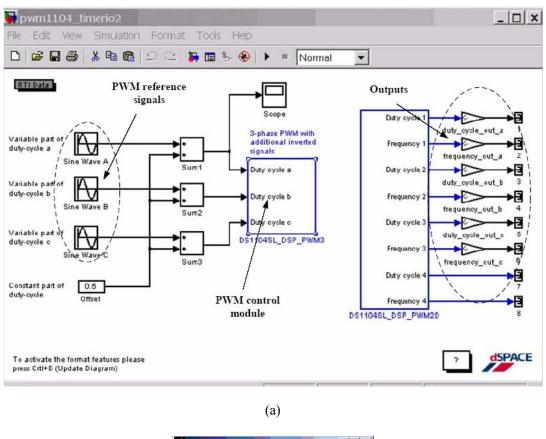

| 5      | 5.2   | Three-   | Phase Variable Frequency Converter129                        |

| 5      | 5.3   | AC/D     | C Power Flow Studies Using a Thyristor Converter and a Diode |

|        |       | Rectifi  | er132                                                        |

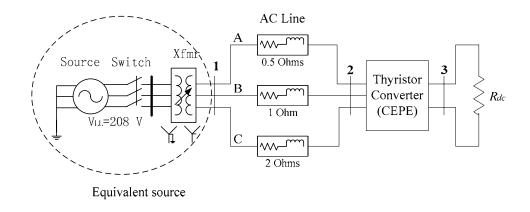

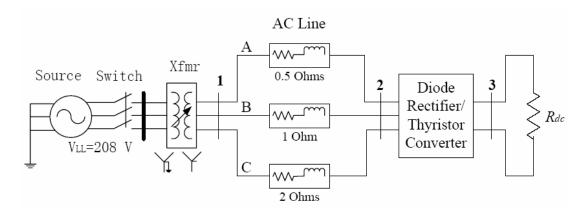

|        |       | 5.3.1    | 3-Bus Unbalanced AC/DC System with a Thyristor Converter134  |

|        |       |          | 5.3.1.1 Hardware Test Results                                |

|        |       |          | 5.3.1.2 Time Domain Simulation Results                       |

|        |       |          | 5.3.1.3 Steady-State Power Flow Analysis Results143          |

|        |       | 5.3.2    | 3-Bus Unbalanced AC/DC System with a Diode Rectifier146      |

|        |       |          | 5.3.2.1 Hardware Test Results                                |

|        |       |          | 5.3.2.2 Time Domain Simulation Results                       |

|        |       |          | 5.3.2.3 Steady-State Power Flow Analysis Results             |

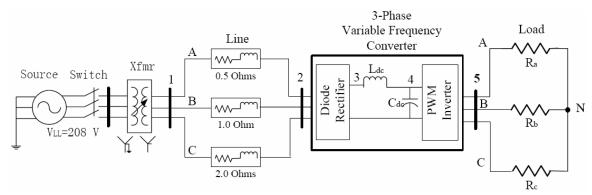

| 5      | 5.4   | AC/D0    | C Power Flow Studies Using a Variable Frequency Converter155 |

|        |       | 5.4.1    | Hardware Test Results                                        |

|        |       | 5.4.2    | Time Domain Simulation Results                               |

|        |       | 543      | Steady-State Power Flow Analysis Results 163                 |

| 5.5         | Comments                                                   | 166 |

|-------------|------------------------------------------------------------|-----|

| CHPATER 6.  | CONCLUSIONS                                                | 167 |

| 6.1.        | Contributions                                              | 167 |

| 6.2.        | Future Work                                                | 169 |

|             | 6.2.1. System Modeling and Analysis                        | 169 |

|             | 6.2.2. Application to Planning and Operation               | 170 |

|             | 6.2.3. Hardware and Software Test-Beds for Multi-Frequency |     |

|             | Systems                                                    | 170 |

| LIST OF REF | TERENCES                                                   | 171 |

| APPENDICES  | S                                                          | 175 |

| VITA        |                                                            | 204 |

## **List of Tables**

| Table 2.1 | Component parameters of the 4-bus ac/dc system with a three-phase                            |

|-----------|----------------------------------------------------------------------------------------------|

|           | thyristor converter                                                                          |

| Table 2.2 | Numerical results of the three-phase thyristor converter benchmark using                     |

|           | Simulink40                                                                                   |

| Table 2.3 | Current participation coefficients, $\lambda_{T,I}^{LL}$ , power participation coefficients, |

|           | $\lambda_{T,P}^{LL}$ , and equivalence coefficients, $K_T^{LL}$ , in the 1-phase thyristor   |

|           | converters41                                                                                 |

| Table 2.4 | The ac currents, $I_T^p$ , and ac power, $S_T^p$ in the three-phase thyristor                |

|           | converter using the $\Delta$ -connected model and the Y -connected model42                   |

| Table 2.5 | Numerical results of the three-phase diode rectifier benchmark using                         |

|           | Simulink45                                                                                   |

| Table 2.6 | Current participation coefficients, $\lambda_{D,I}^{LL}$ , power participation coefficients, |

|           | $\lambda_{D,P}^{LL}$ , and equivalence coefficients, $K_D^{LL}$ , in the 1-phase diode       |

|           | rectifiers                                                                                   |

| Table 2.7 | The ac currents, $I_D^p$ , and ac power, $S_D^p$ in the three-phase diode rectifier          |

|           | using the $\Delta$ -connected model in steady-state analysis46                               |

| Table 2.8 | Component parameters of the 4-bus ac/dc system with a three-phase PWM                        |

|           | inverter                                                                                     |

| Table 2.9 | Numerical results of the three-phase PWM inverter benchmark using                            |

|           | Simulink51                                                                                   |

| Table 2.10 | Comparison of the benchmark and the three-phase PWM inverter using      |

|------------|-------------------------------------------------------------------------|

|            | the delta-connected model in steady-state analysis                      |

| Table 3.1  | Equivalent power flow components for the DC systems59                   |

| Table 3.2  | Equivalent dc power flow components for the AC systems61                |

| Table 3.3  | A list of known and unknown parameters in AC/DC power systems65         |

| Table 3.4  | The ranks of the subsystems in the sample system76                      |

| Table 3.5  | Nominal power loads for the 12-bus system in Case 185                   |

| Table 3.6  | The subsystem ranks in Case 185                                         |

| Table 3.7  | Convergence comparison of the sequential method in Case 186             |

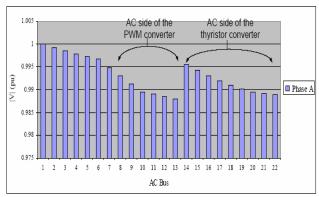

| Table 3.8  | Bus voltage magnitudes in Case 186                                      |

| Table 3.9  | Parameters of the thyristor converter in Case 1                         |

| Table 3.10 | Parameters of the PWM converter in Case 187                             |

| Table 3.11 | Nominal loads for the 12-bus system in Case 2                           |

| Table 3.12 | The subsystem ranks in Case 289                                         |

| Table 3.13 | Convergence comparison of the sequential solver in Case 289             |

| Table 3.14 | Bus voltage magnitudes in Case 290                                      |

| Table 3.15 | Parameters of the thyristor converter model in Case 290                 |

| Table 3.16 | Parameters of the PWM converter model in Case 291                       |

| Table 4.1  | Nominal loads for the 25-bus system in Case 1112                        |

| Table 4.2  | Maximum current magnitudes on the ac sides of the converters in Case 1a |

|            | with $P_{PWM,ac} = 0$ MW                                                |

| Table 4.3  | AC bus voltage magnitudes on the ac sides of the converters in Case 1a  |

|            | with $P_{PWM,ac} = 0$ MW                                                |

| Table 4.4  | Coefficients of the delta-connected thyristor converter model in Case 1a |

|------------|--------------------------------------------------------------------------|

|            | with $P_{PWM,ac} = 0$ MW114                                              |

| Table 4.5  | Maximum current magnitudes on the ac sides of the converters in Case 1b  |

|            | with $P_{PWM,ac} = 0.4 \text{ MW}.$ 116                                  |

| Table 4.6  | Bus voltage magnitudes on the ac sides of the converters in Case 1b with |

|            | $P_{PWM,ac} = 0.4 \text{ MW}$                                            |

| Table 4.7  | Coefficients of the delta-connected thyristor converter model in Case 1a |

|            | with $P_{PWM,ac} = 0.4$ MW                                               |

| Table 4.8  | AC power injected into the ac system from the three-phase converters in  |

|            | Case 1b with $P_{PWM,ac} = 0.4 \text{ MW}$                               |

| Table 4.9  | Nominal loads for the 25-bus system in Case 2                            |

| Table 4.10 | Maximum current magnitudes on the ac sides of the converters in Case 2a  |

|            | with $P_{PWM,ac} = 0$ MW                                                 |

| Table 4.11 | AC bus voltage magnitudes on the ac sides of the converters in Case 2a   |

|            | with $P_{PWM,ac} = 0.4 \text{ MW}$                                       |

| Table 4.12 | Coefficients of the delta-connected thyristor converter model in Case 2a |

|            | with $P_{PWM,ac} = 0$ MW                                                 |

| Table 4.13 | Maximum current magnitudes on the ac sides of the converters in Case 2b  |

|            | with $P_{PWM,ac} = -0.675 \text{ MW}$                                    |

| Table 4.14 | Bus voltage magnitudes the ac sides of the converters in Case 2b with    |

|            | $P_{PWM,ac} = -0.675 \text{ MW}.$                                        |

| Table 4.15 | Coefficients of the delta-connected thyristor converter model in Case 2b    |

|------------|-----------------------------------------------------------------------------|

|            | with $P_{PWM,ac} = -0.675 \text{ MW}.$ 123                                  |

| Table 4.16 | AC power injected into the ac system from the three-phase converters in     |

|            | Case 2b with $P_{PWM,ac} = -0.675 \text{ MW}$                               |

| Table 5.1  | Voltage profile in the 3-bus ac/dc system with a thyristor converter from   |

|            | hardware tests                                                              |

| Table 5.2  | Current profile in the 3-bus ac/dc system with a thyristor converter from   |

|            | hardware tests                                                              |

| Table 5.3  | Ac and dc voltages, currents, and power in the 3-phase thyristor converter  |

|            | from hardware tests                                                         |

| Table 5.4  | Voltages at bus 1 in the 3-bus ac/dc system with a thyristor converter from |

|            | hardware tests                                                              |

| Table 5.5  | Line and load impedance in the 3-bus ac/dc system with a thyristor          |

|            | converter from hardware tests                                               |

| Table 5.6  | Ac and dc voltages, currents, and power in the thyristor converter from     |

|            | time domain analysis141                                                     |

| Table 5.7  | Difference of ac and dc voltages, currents, and power on the thyristor      |

|            | converter between time domain analysis and hardware tests142                |

| Table 5.8  | Coefficients of the thyristor converter model from steady-state             |

|            | analysis143                                                                 |

| Table 5.9  | Ac and dc voltages, currents, and power in the 3-phase thyristor converter  |

|            | from steady-state analysis144                                               |

| Table 5.10 | Difference of ac and dc voltages, currents, and power in the 3-phase         |

|------------|------------------------------------------------------------------------------|

|            | thyristor converter between steady-state analysis and hardware tests145      |

| Table 5.11 | Voltage profile in the 3-bus ac/dc system with a diode rectifier from        |

|            | hardware tests                                                               |

| Table 5.12 | Current profile in the 3-bus ac/dc system with a diode rectifier from        |

|            | hardware tests                                                               |

| Table 5.13 | Ac and dc voltages, currents, and power in the diode rectifier from          |

|            | hardware tests                                                               |

| Table 5.14 | Voltages at bus 1 in the 3-bus ac/dc system with a diode rectifier from      |

|            | hardware tests                                                               |

| Table 5.15 | Line and load impedance in the 3-bus ac/dc system with a diode rectifier     |

|            | from hardware tests                                                          |

| Table 5.16 | Ac and dc voltages, currents, and power in the 3-bus ac/dc system from       |

|            | time domain analysis                                                         |

| Table 5.17 | Difference of ac and dc voltages, currents, and power in the diode rectifier |

|            | between time domain analysis and hardware tests                              |

| Table 5.18 | Coefficients of the diode rectifier model from steady-state analysis153      |

| Table 5.19 | AC and dc voltage, currents and power in the 3-phase diode rectifier from    |

|            | steady-state analysis                                                        |

| Table 5.20 | Difference of ac and dc voltages, currents, and power in the 3-phase diode   |

|            | rectifier between steady-state analysis and hardware tests154                |

| Table 5.21 | Voltage profile in the 5-bus ac/dc system with a variable frequency          |

|            | converter from hardware tests                                                |

| Table 5.22 | Current profile in the 6-bus ac/dc system with a variable frequency        |

|------------|----------------------------------------------------------------------------|

|            | converter from hardware tests                                              |

| Table 5.23 | Voltages at bus 1 in the 5-bus ac/dc system with a variable frequency      |

|            | converter from hardware tests                                              |

| Table 5.24 | Line and load impedance in the 5-bus ac/dc system with a variable          |

|            | frequency converter161                                                     |

| Table 5.25 | Current profile in the 6-bus ac/dc system with a variable frequency        |

|            | converter from time domain analysis                                        |

| Table 5.26 | Voltage difference in the 5-bus ac/dc system between time domain           |

|            | simulation and hardware tests                                              |

| Table 5.27 | Current difference in the 5-bus ac/dc system between time domain           |

|            | simulation and hardware tests                                              |

| Table 5.28 | Coefficients of the diode rectifier model in the 5-bus ac/dc system with a |

|            | variable frequency converter from steady-state analysis162                 |

| Table 5.29 | Voltage profile in the 5-bus ac/dc system with a variable frequency        |

|            | converter from steady-state analysis                                       |

| Table 5.30 | Current profile in the 5-bus ac/dc system with a variable frequency        |

|            | converter from steady-state analysis                                       |

| Table 5.31 | Voltage difference in the 5-bus ac/dc system between steady-state analysis |

|            | and hardware tests                                                         |

| Table 5.32 | Current difference in the 5-bus ac/dc system between steady-state analysis |

|            | and hardware tests                                                         |

# **List of Figures**

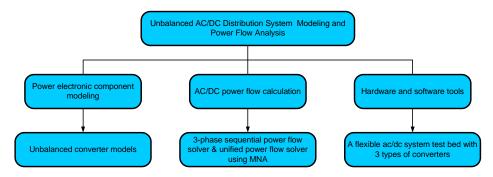

| Figure 1.1  | The framework of this thesis4                                                            |

|-------------|------------------------------------------------------------------------------------------|

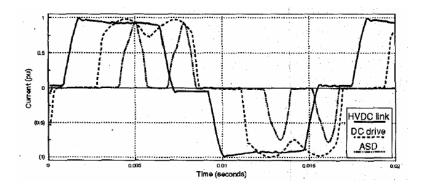

| Figure 2.1  | Typical current waveforms of HVDC links, 6-pules dc drives, and                          |

|             | adjustable speed drives                                                                  |

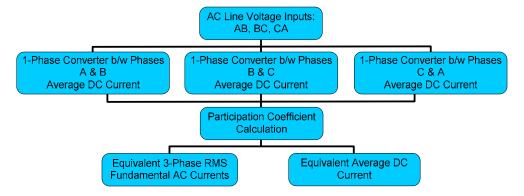

| Figure 2.2  | The unbalanced, delta-connected converter modeling approach10                            |

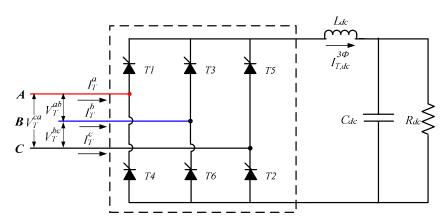

| Figure 2.3  | Three-phase line-frequency full bridge thyristor converter                               |

| Figure 2.4  | Three-phase delta-connected thyristor converter model                                    |

| Figure 2.5  | The ac and dc currents in a three-phase thyristor converter14                            |

| Figure 2.6  | The ac and dc currents in the delta-connected converter model                            |

| Figure 2.7  | Equivalent ac and dc components of the delta-connected converter                         |

|             | model                                                                                    |

| Figure 2.8  | The dc currents in a three-phase thyristor converter, $i_{T,dc}^{3\phi}$ , and the three |

|             | single-phase converters, $i_{T,dc}^{LL}$                                                 |

| Figure 2.9  | The ac equivalent component of the delta-connected converter model26                     |

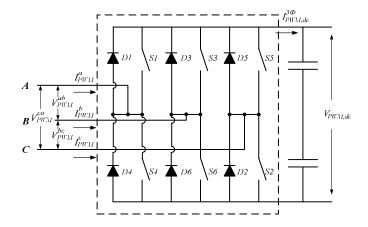

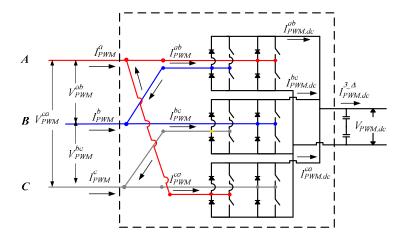

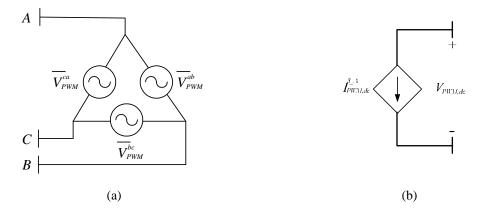

| Figure 2.10 | Three-phase PWM converter                                                                |

| Figure 2.11 | Three-phase delta-connected PWM converter model30                                        |

| Figure 2.12 | A three-phase thyristor converter under two-phase operating condition                    |

|             | with phase c open33                                                                      |

| Figure 2.13 | The equivalent model of a three-phase converter under two-phase operating                |

|             | condition with phase c open                                                              |

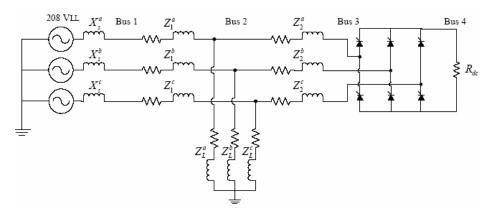

| Figure 2.14 | The circuit diagram of a 4-bus unbalanced ac/dc system with a three-phase                |

|             | thyristor converter                                                        |

|-------------|----------------------------------------------------------------------------|

| Figure 2.15 | The Simulink circuit of the 4-bus unbalanced ac/dc system with a           |

|             | three-phase thyristor converter                                            |

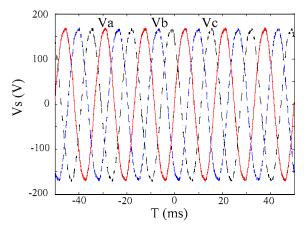

| Figure 2.16 | Line-to-neutral voltages (top) and ac currents (bottom) in the three-phase |

|             | thyristor converter benchmark                                              |

| Figure 2.17 | Dc voltage (top) and dc current (bottom) in the three-phase thyristor      |

|             | converter benchmark39                                                      |

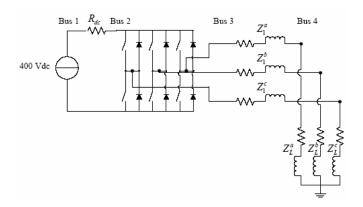

| Figure 2.18 | The circuit diagram of a 4-bus unbalanced ac/dc system with a three-phase  |

|             | PWM inverter                                                               |

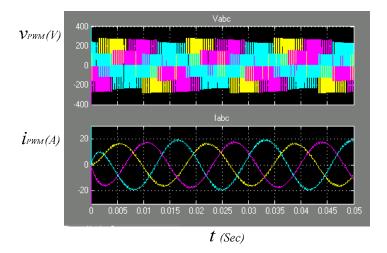

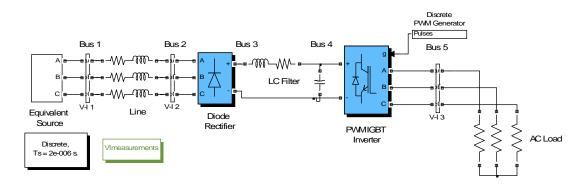

| Figure 2.19 | The Simulink circuits of the 4-bus unbalanced ac/dc system with a          |

|             | three-phase IGBT PWM inverter50                                            |

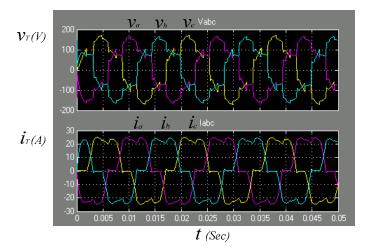

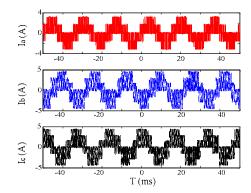

| Figure 2.20 | Line-to-neutral voltages (top) and ac currents (bottom) in the three-phase |

|             | PWM inverter benchmark51                                                   |

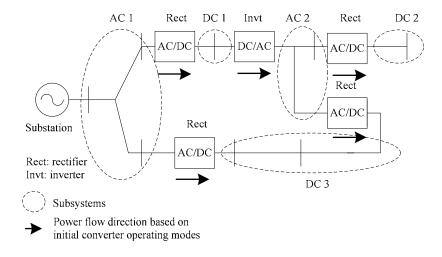

| Figure 3.1  | A sample ac/dc system55                                                    |

| Figure 3.2  | Decoupled ac and dc systems used in the sequential power flow solver58     |

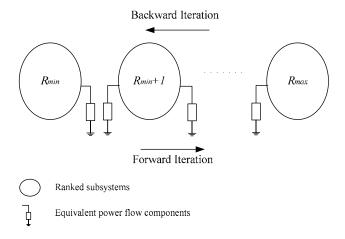

| Figure 3.3  | The one-line diagram of a sample ac/dc system with 5 subsystems76          |

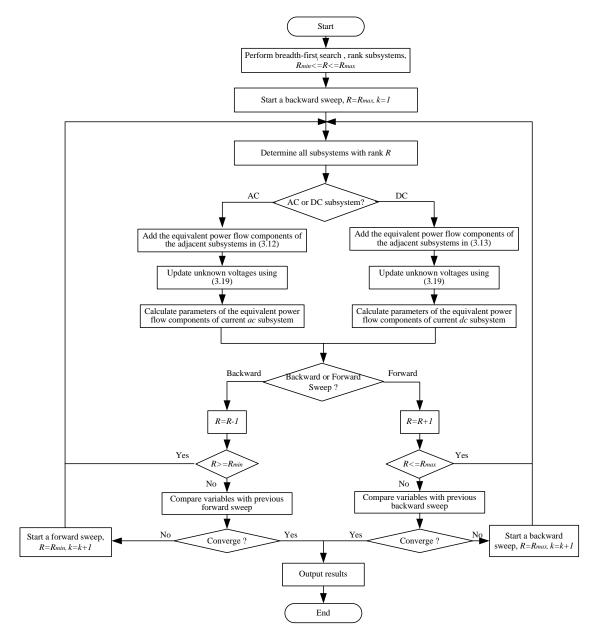

| Figure 3.4  | The backward/forward sequential ac/dc power flow77                         |

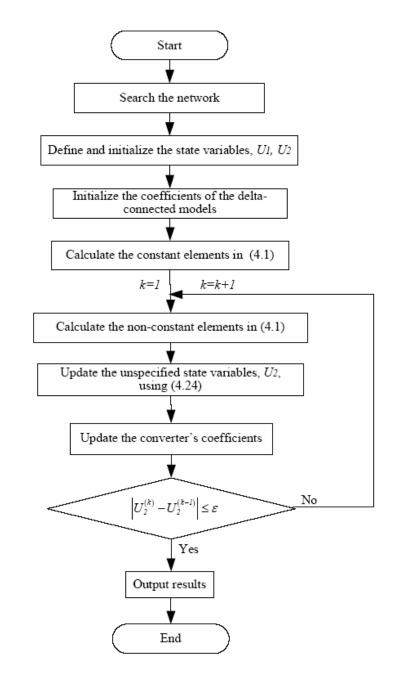

| Figure 3.5  | Flow chart of the 3-phase sequential <i>ac/dc</i> power flow solver82      |

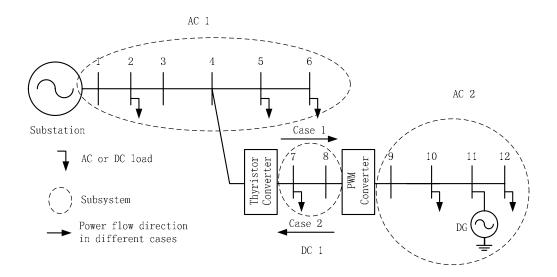

| Figure 3.6  | A one-line diagram of the 12-bus AC/DC system83                            |

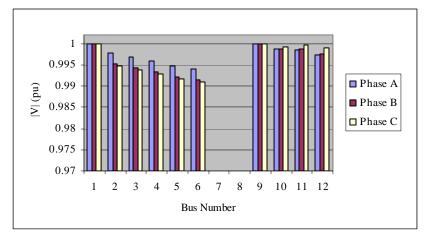

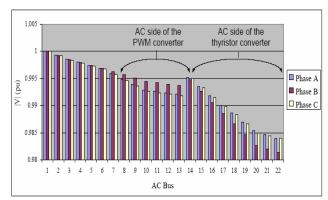

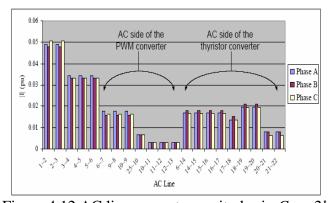

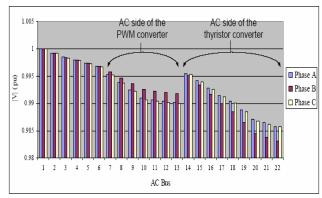

| Figure 3.7  | AC bus voltage magnitudes in Case 187                                      |

| Figure 3.8  | AC bus voltage magnitudes in Case 290                                      |

| Figure 4.1  | The equivalent ac and dc power flow components for ac/dc systems           |

|             | interconnected with three-phase thyristor converters97                     |

| Figure 4.2  | The equivalent ac (a) and dc (b) power flow components for ac/dc system      |  |  |

|-------------|------------------------------------------------------------------------------|--|--|

|             | interconnected with ac current controlled PWM converters                     |  |  |

| Figure 4.3  | The equivalent ac (a) and dc (b) power flow components for ac/dc systems     |  |  |

|             | interconnected with ac voltage controlled PWM converters102                  |  |  |

| Figure 4.4  | The flow chart of the three-phase MNA based unified ac/dc power flow         |  |  |

|             | solver                                                                       |  |  |

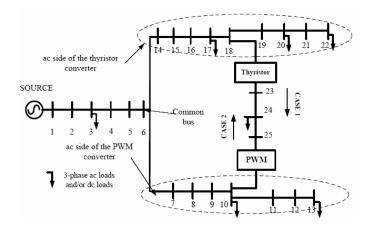

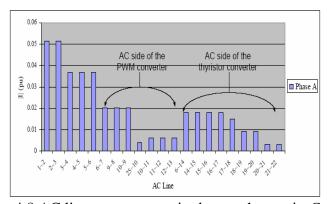

| Figure 4.5  | A one-line diagram of the 25-Bus System                                      |  |  |

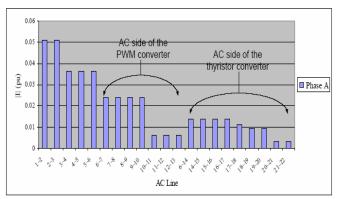

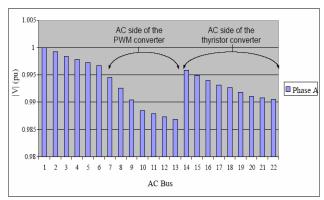

| Figure 4.6  | AC line current magnitudes on phase a in Case 1a                             |  |  |

| Figure 4.7  | AC bus voltage magnitudes on phase a in Case 1a                              |  |  |

| Figure 4.8  | AC line current magnitudes on phase <i>a</i> in <i>Case 1b</i>               |  |  |

| Figure 4.9  | AC bus voltage magnitudes on phase a in Case 1b                              |  |  |

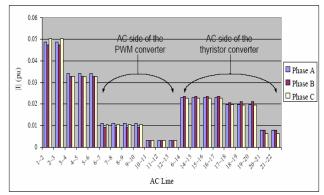

| Figure 4.10 | AC line current magnitudes in Case 2a                                        |  |  |

| Figure 4.11 | AC bus voltage magnitudes in Case 2a                                         |  |  |

| Figure 4.12 | AC line current magnitudes in <i>Case 2b</i>                                 |  |  |

| Figure 4.13 | AC bus voltage magnitudes in Case 2b                                         |  |  |

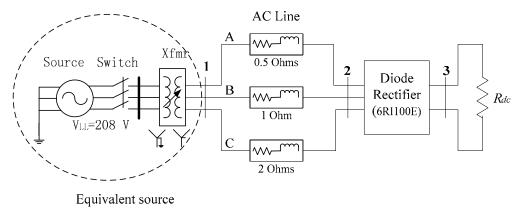

| Figure 5.1  | An ac/dc system setup with a three-phase diode rectifier/thyristor converter |  |  |

|             | on the test bed                                                              |  |  |

| Figure 5.2  | An ac/dc system setup with a three-phase variable frequency converter on     |  |  |

|             | the test bed                                                                 |  |  |

| Figure 5.3  | The block diagram of the three-phase ac/dc/ac variable frequency             |  |  |

|             | converter129                                                                 |  |  |

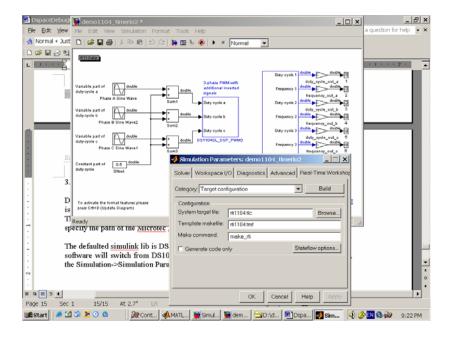

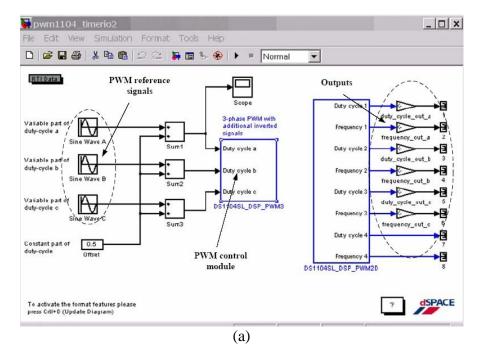

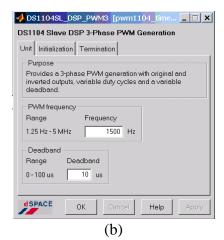

| Figure 5.4  | The PWM inverter control circuit (a) and PWM control module (b) in           |  |  |

|             | MATLAB Simulink for the dSPACE DS1104 DSP card131                            |  |  |

| Figure 5.5  | The 3-bus unbalanced ac/dc system with a three-phase thyristor                            |

|-------------|-------------------------------------------------------------------------------------------|

|             | converter                                                                                 |

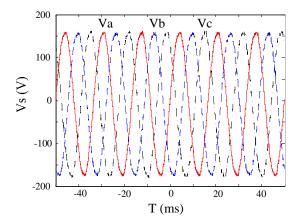

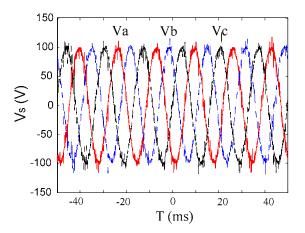

| Figure 5.6  | Waveforms of the 3-phase line-to-neutral voltages at bus 1 in the 3-bus                   |

|             | ac/dc system with a thyristor converter                                                   |

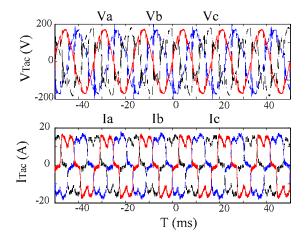

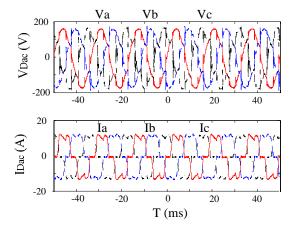

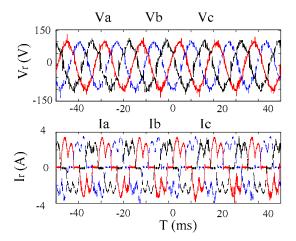

| Figure 5.7  | Waveforms of $V_T^p$ (top) and $I_T^p$ (bottom) at bus 2 in the 3-bus ac/dc system        |

|             | with a thyristor converter                                                                |

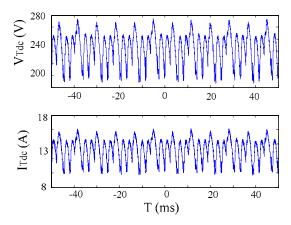

| Figure 5.8  | Waveforms of $V_{T,dc}$ (top) and $I_{T,dc}^{3\phi}$ (bottom) at bus 3 in the 3-bus ac/dc |

|             | system with a thyristor converter                                                         |

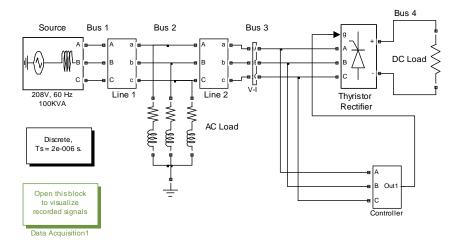

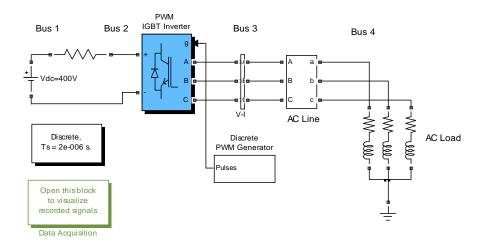

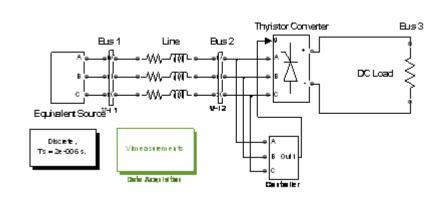

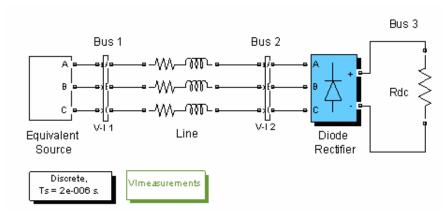

| Figure 5.9  | The Simulink circuit of the 3-bus ac/dc system with a thyristor                           |

|             | converter                                                                                 |

| Figure 5.10 | The 3-bus ac/dc system with a three-phase diode rectifier146                              |

| Figure 5.11 | Waveforms of the 3-phase line-to-neutral voltages at bus 1 in the 3-bus                   |

|             | ac/dc system with a diode rectifier                                                       |

| Figure 5.12 | Waveforms of $V_D^p$ (top) and $I_D^p$ (bottom) at bus 2 in the 3-bus ac/dc system        |

|             | with a diode rectifier                                                                    |

| Figure 5.13 | Waveforms of $V_{D,dc}$ (top) and $I_{D,dc}^{3\phi}$ (bottom) at bus 3 in the 3-bus ac/dc |

|             | system with a diode rectifier                                                             |

| Figure 5.14 | The Simulink circuit of the 3-bus ac/dc system with a diode rectifier151                  |

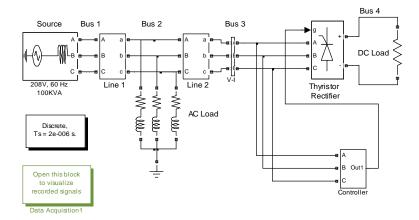

| Figure 5.15 | The 5-bus ac/dc system using the variable frequency converter155                          |

| Figure 5.16 | Waveforms of the 3-phase line-to-neutral voltages at bus 1 in the 5-bus                   |

|             | ac/dc system with a variable frequency converter156                                       |

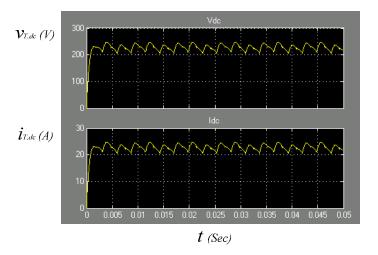

| Figure 5.17 | Waveforms of $V_D^p$ (top) and $I_D^p$ currents (bottom) at bus 2 in the 5-1                       |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------|--|--|--|

|             | ac/dc system with a variable frequency converter                                                   |  |  |  |

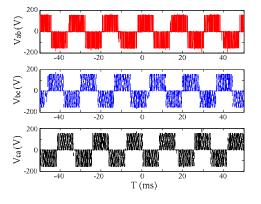

| Figure 5.18 | Waveforms of $V_{D,dc}$ , $V_{PWM,dc}$ (top) and $I_{D,dc}^{3\phi}$ (bottom) at bus 3 and bus 4 in |  |  |  |

|             | the 5-bus ac/dc system with a variable frequency converter157                                      |  |  |  |

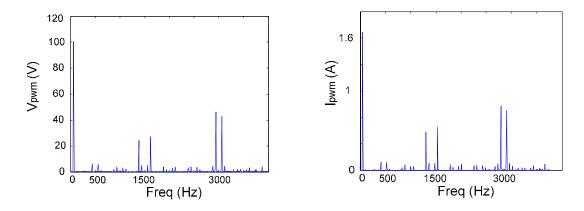

| Figure 5.19 | Waveforms of $V_{PWM}^{LL}$ (left) and $I_{PWM}^{p}$ (right) at bus 5 in the 5-bus ac/dc           |  |  |  |

|             | system with a variable frequency converter157                                                      |  |  |  |

| Figure 5.20 | FFT of $V_{PWM}^{ab}$ (left) and $I_{PWM}^{a}$ (right) at bus 5 in the 5-bus ac/dc system with     |  |  |  |

|             | a variable frequency converter                                                                     |  |  |  |

| Figure 5.21 | The Simulink circuit of the 5-bus ac/dc system with a variable frequency                           |  |  |  |

|             | converter161                                                                                       |  |  |  |

#### **ABSTRACT**

Unbalanced Power Converter Modeling for AC/DC Power Distribution Systems

#### Xiaoguang Yang

#### Karen N. Miu, Ph.D.

In power distribution systems, the installation of power electronics based equipment has grown rapidly for ac/dc system coupling, system protection, alternative energy source interface, etc. This thesis will focus on power electronic component and system modeling techniques and three-phase ac/dc power flow analysis for power distribution systems. First, mathematical models are developed for unbalanced power electronic converters, such as thyristor converters, diode rectifiers, and Pulse-Width-Modulated (PWM) converters. The modeling approach captures the imbalance of distribution systems using three, delta-connected, single-phase converters. In order to perform system analysis, these models have been incorporated into two types of ac/dc power flow solvers: (i) a three-phase backward/forward sequential solver and (ii) a threephase unified solver using the modified nodal analysis method. Both solvers have been applied to unbalanced radial and weakly meshed distribution systems. Finally, an ac/dc system hardware test bed was created to validate the mathematical models and the performance of the power flow solvers. Extensive hardware tests, time domain simulations, and steady-state analysis have been performed.

#### CHAPTER 1. INTRODUCTION

Recent developments in power electronics offer the possibility of wide-scale integration of power electronics based devices into power systems [1]. Resulting benefits would include improved control of the delivered power, high energy efficiency and high power density. In order to implement these devices into distribution systems successfully, system wide analysis should be performed in order to understand their impacts on system planning and operation. As such, appropriate mathematical models and application tools, are desired to capture the characteristics of power electronic devices. This thesis will address power electronic device modeling techniques and three-phase ac/dc power flow analysis for power distribution systems.

#### 1.1 Motivations

In power systems, *ac/dc* conversion using power converters has been developed and installed in transmission systems in past decades [2]. With a focus on power distribution systems, the implementation of power electronic devices has grown rapidly in recent years, such as in terrestrial distribution systems [3], shipboard power systems [4], and transportation systems [5]. For example, adjustable-speed drives are replacing constant speed electric motor-driven systems in industry to improve efficiency by controlling the motor speed. Power electronics have also been used as interface to transfer power from alternative energy sources, such as wind, photovoltaic, into the utility systems. In shipboard power systems, power converters introduce the potential to actively control the coupling of ac/dc systems. They can be operated faster than electromechanical devices to open/close circuits and prevent the spread of faults using zonal electrical distribution [4].

The installation of these power electronic devices may have either positive or negative impacts on the operation and control of distribution systems. To investigate the impacts of these new devices, it is essential to establish a foundation to investigate their properties and to incorporate them in planning and operation studies. Fundamental tools for power system analysis include component and system modeling and steady-state ac/dc power flow. The models and power flow have been used in many applications in planning and operation, such as protection system design, service restoration, power quality analysis, etc. The applications require appropriate models to reflect the actual behavior of system components as well as robust and efficient power flow solution algorithms.

Historically in the power industry, the main power electronics applications have been in High Voltage Direct Current (HVDC) systems, solid state VAR compensators, unified power flow controllers, and others. As a result, a number of models were created to handle these devices and implemented in power flow solvers, see for example [6-12]. In HVDC systems, large inductors are installed in the dc systems to smooth dc currents. Thus, many converter models and subsequent power flow formulations assumed the systems to be three-phase with constant dc currents. In [6-9], the network and loads are assumed to be three-phase balanced. In these models, the converter ac currents were assumed to be filtered and had sinusoidal waveforms with low distortion. The current magnitudes were calculated by performing FFT analysis on the tri-state square ac currents before filters. The dc systems were modeled as constant power ac loads in the power flow solvers.

Some three-phase, unbalanced systems, converter models have also been developed

for HVDC system analysis. In [10][11], a three-phase thyristor converter model was proposed. The imbalance of systems was captured by the conducting periods of thyristors on each phase. In [12], three-phase thyristor converters were modeled as equivalent sequence regulation transformers using modulation theory. In these three-phase models, it was still assumed that the dc currents were constant.

In contrast, power distribution systems are inherently unbalanced systems consisting of single, two and three-phase components and subsystems. Also because of limited space [13], often there are not enough filtering devices to eliminate the harmonics generated by power electronic devices. In addition, installation of large dc capacitors amplifies dc current ripples in some distribution system devices, such as Adjustable Speed Drives (ASDs), As such, the Total Harmonic Distortion (THD) in the dc currents and ac currents could be much higher, e.g. THD is among 40-60% for ASDs [13], than those in HVDC systems. For these reasons, the previous modeling approaches and power flow solvers for HVDC system analysis are not directly applicable to power distribution systems. New modeling techniques are desired to capture the properties of the power electronic devices and to be implemented in distribution system analysis tools.

Furthermore, these new mathematical models and analysis tools should be tested and validated in real-life environments. It is noted that real system data is not always accessible and it is also impractical to perform experiments on real systems for the sole purpose of validation. As such, it is desired to develop scaled-down, flexible, ac/dc system hardware test beds.

#### 1.2 Objectives

The objectives of this work are to

- (i) Investigate characteristics of power converters and develop mathematical models for distribution system analysis

- (ii) Develop new power flow solvers with appropriate mathematical models to support improved distribution system planning and operation

- (iii) Develop hardware and software tools to validate power converter models and the performance of power flow solvers

The framework of this thesis is shown in Figure 1.1.

Figure 1.1 The framework of this thesis

The work in this thesis addresses the above objectives and makes the following contributions.

#### 1.3 Summary of Contributions

This thesis provides the following contributions toward improving distribution system operation and control in the presence of power electronic devices:

- Detailed unbalanced converter models using three, delta-connected, single-phase converters for:

- Three-phase full bridge thyristor converters and diode rectifiers

- Three-phase Pulse-Width-Modulated (PWM) converters

- Three-phase ac/dc power flow solvers for uni-directional and bi-directional power flow studies in radial or weakly meshed distribution systems

- A backward/forward sequential solver using a subsystem ranking method

- A unified solver using the modified nodal analysis method

- Detailed simulation results on radial and weakly meshed three-phase distribution systems

- A flexible hardware test bed for studying ac/dc power flow and evaluating mathematical system models and analysis tools

#### 1.4 Organization of Thesis

This thesis is organized as follows. In Chapter 2, a new converter modeling approach is proposed for unbalanced power converters. The approach utilizes three, single-phase converters to model three-phase converters under unbalanced operating conditions. The models are able to capture system imbalance using the single-phase converters. The contributions of the single-phase converters to ac/dc power flow are determined by participation coefficients. By introducing equivalence criteria, the converter models become equivalent to three-phase converters with respect to both RMS fundamental ac and average dc currents. They are valid for converters operating in either rectifier mode or inverter mode. The modeling approach is applied to three types of three-phase converters: (i) thyristor converters; (ii) diode rectifiers; and (iii) PWM converters. The three converter models are validated in time domain simulation and steady- state analysis.

Using the converter models from Chapter 2, a three-phase sequential solver and a three-phase unified solver are developed in Chapter 3 and Chapter 4, respectively, for distribution ac/dc power flow studies. In the sequential solver, ac and dc power flows in

subsystems are solved using an iterative backward/forward algorithm. A subsystem ranking method is proposed to determine the sequence for solving power flow. In the unified solver, steady-state Modified Nodal Analysis (MNA) method is implemented to solve ac and dc power flow in a unified manner. Using MNA, impacts among ac and dc systems can be analyzed directly. The ac/dc power flow iterations, which may cause divergence problems, in sequential solvers are avoided. In addition, existing ac and dc nodal analysis programs can be extended to develop the unified power flow program conveniently with moderate modifications.

In order to validate the performance of the theoretical converter models and the power flow solvers, a three-phase ac/dc system hardware test bed has been developed and will be presented in Chapter 5. The test bed contains a flexible network and loads as well as three different three-phase converters: (i) a full-bridge thyristor converter; (ii) a full bridge diode rectifier; and (iii) a variable frequency converter consisting of a diode rectifier and a PWM inverter. Using the test bed, balanced or unbalanced ac/dc systems can be set up for power flow studies. Special attention is paid to the design of the variable frequency converter while the thyristor converter and diode rectifier are existing devices. Using the test bed, ac/dc power flow has been studied in a real-life environment. In addition, time domain simulations using MATLAB Simulink and power flow analysis using the solvers developed in Chapters 3 and 4 have been performed. The deltaconnected converter models and the performance of the ac/dc power flow solvers are validated by comparing the steady-state results with the hardware test results. In Chapter 6, conclusions are drawn for this work with outlined contributions. Possible future work is also discussed.

# CHAPTER 2. UNBALANCED CONVERTER MODELING: DIODE RECTIFIER, THYRISTOR CONVERTER AND PULSE-WIDTH-MODULATED (PWM) CONVERTER

In this chapter, three-phase converter models are proposed for power distribution system analysis. The models allow for converter operation with continuous and discontinuous dc currents. The following three types of converters are investigated:

- Line-frequency full bridge diode rectifiers

- Line-frequency full bridge thyristor converters

- Pulse-width-modulated (PWM) converters

These converters are modeled using three, delta-connected, single-phase converters. The models are equivalent to three-phase converters with respect to RMS fundamental ac and average dc currents. They can be used in analysis tools such as ac/dc power flow.

Unbalanced converter models are desired to capture characteristics of distribution systems. Power converter based devices, such as adjustable speed drives (ASDs), dc motor drives, flexible AC transmission system (FACTS) devices, have been used at various voltage levels in distribution systems. Distribution systems contain single-phase, two-phase, and three-phase components. As such, the ac voltages applied to and the ac currents flowing in the converters are generally unbalanced.

However, use of these devices results in distorted currents in both the ac and dc systems. Usually, installations of power electronics devices in distribution systems are

limited by physical space [13]. Consequently, the dc inductors, if present, have small inductance and may not be able to significantly reduce the harmonics in the dc currents generated by the converters. Typical ac currents in High Voltage Direct Current (HVDC) links, DC drives, and ASDs [13] are shown Figure 2.1. It can be seen that the current in the HVDC link has less distortion while the currents in the DC drive and ASD are highly distorted.

Figure 2.1 Typical current waveforms of HVDC links, 6-pules dc drives, and adjustable speed drives [13]

Traditional converter models for HVDC system studies are not directly applicable to converters in distribution systems. In HVDC systems, thyristor converters have been used for ac/dc conversion with large dc link inductors. The majority of the ac components in the dc link currents are eliminated. Then, based on pure dc currents and tri-state square-wave ac currents, single-phase [6]-[9] and three-phase [10]-[12] converter models have been proposed for HVDC power flow studies. Single-phase HVDC converter models have also been used in power flow studies for certain balanced small ac/dc systems [13][15] and transit railway power systems [16]. In the above models, it was assumed that the dc currents were constant with no harmonics. The converter ac currents

at the fundamental frequency were obtained by performing Fast Fourier Analysis (FFT) on the square-wave shape ac currents. However, the assumption of a constant dc current generally does not hold for ac/dc systems with small dc inductance or large dc capacitance and appropriate models are desired.

More recently, new three-phase converter topologies have been proposed for unbalanced distribution systems [17-19]. Time domain simulations were performed with detailed power electronic device models to verify the feasibility and efficiency of the converters. However, time domain analysis requires detailed component models and becomes complicated and time consuming for large-scale power systems. In order to implement these converters in power flow studies, frequency domain models are desired.

Unbalanced converter models using three, Y-connected, grounded, single-phase converters were proposed for distribution system power flow studies in [20]-[22]. The models used single-phase converters to capture the imbalance in the ac currents. It was assumed that the dc current was continuous and converter ac real power was balanced. In this thesis, the Y-connected models are expanded and improved by using three, delta-connected, single-phase converters. The new models relieve the above two assumptions in the Y-connected models.

The three, delta-connected, single-phase converters in the new model capture the imbalance of ac real power and the ac currents. The contributions of the single-phase converters to the dc link current are represented using participation coefficients. The delta-connected models are equivalent to three-phase converters in terms of both the

RMS fundamental ac currents entering the three-phase converters and the average dc link current. The modeling approach is illustrated in Figure 2.2. The models are:

- Applicable under significantly unbalanced operating conditions

- Valid for converters with either continuous or discontinuous dc currents

- Applicable to both rectifier and inverter operation modes

- Appropriate for both unidirectional and bi-directional power flow studies

They can be used for ac/dc power flow studies in both balanced and unbalanced distribution systems.

Figure 2.2 The unbalanced, delta-connected converter modeling approach

In the following subsections, equivalent delta-connected models are first proposed for three-phase diode/thyristor converters and PWM converters. Then, an example of the model implemented for converters operating under significantly unbalanced conditions is presented. MATLAB Simulink simulations are performed for a three-phase four-bus ac/dc system. The delta-connected models are tested and verified in both time domain and steady-state. The results are compared with those obtained from the Y-connected models [20]. Hardware tests of the models will be presented in Chapter 5.

#### 2.1 Unbalanced Diode Rectifier and Thyristor Converter Models

The diode rectifiers and thyristor converters under investigation are three-phase line-frequency full bridge converters [1]. It is noted that diode rectifiers have similar characteristics as thyristor converters with zero firing angles. As such, this subsection focuses on modeling thyristor converters. The diode rectifier model follows the same approach and will be discussed at the end of this subsection.

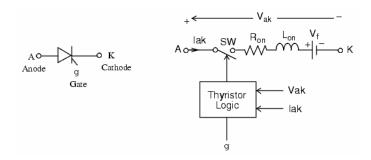

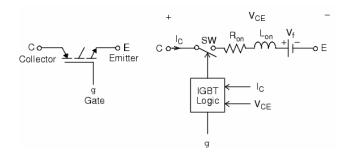

#### 2.1.1 Thyristor Converter Model

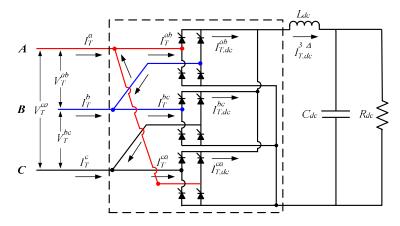

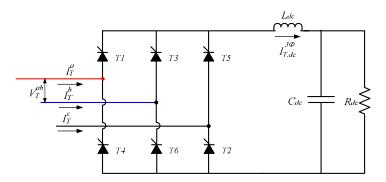

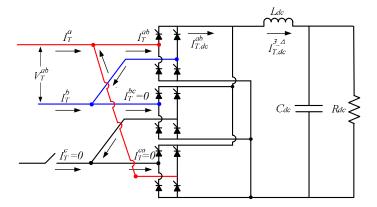

The circuit diagram of a three-phase full bridge thyristor converter is shown in Figure 2.3. Please note that the following notation is used:

$V_T^{ab}$ ,  $V_T^{bc}$ ,  $V_T^{ca}$ : the RMS line-to-line voltages on the converter ac bus

$I_T^a$ ,  $I_T^b$ ,  $I_T^c$ : the RMS ac currents entering the three-phase converters

$T_1$  to  $T_6$ : the six thyristors forming the bridge

$L_{dc}$ ,  $C_{dc}$ ,  $R_{dc}$ : the dc inductor, capacitor, and resistor respectively

$I_{T,dc}^{3\phi}$ : the average dc current through the dc link

Figure 2.3 Three-phase line-frequency full bridge thyristor converter

The following assumptions are made for the three-phase thyristor converters:

- A1. Equi-distant control is used

- A2. All firing angles are known

- A3. Commutation angles are known

- A4. The percentage of the real power loss is known and constant

The dc current of a three-phase converter is either continuous or discontinuous, depending on the network. For example, DC drives usually do not have dc link filters [13] and the dc motor inductance results in continuous dc currents. On the other hand, dc capacitors are generally installed for ac/dc/ac power conversion [1]. For example, most ASDs have large dc capacitors to sustain dc voltages. The capacitors amplify dc current ripples and cause discontinuous dc currents. In order to develop appropriate models for both conduction modes, the following assumptions are made for the dc systems:

- A5. The dc capacitor is ignored when the converter is operated in the continuous conduction mode

- A6. The dc capacitor voltage is constant when the converter is operated in the discontinuous conduction mode

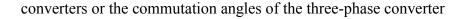

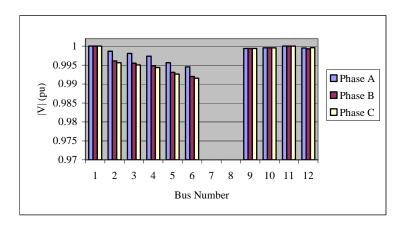

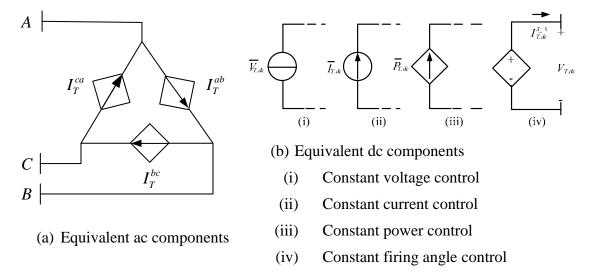

Based on these assumptions, an equivalent model is developed using three, delta-connected, single-phase thyristor converters as shown in Figure 2.4 with the following notation:

$I_{T}^{ab}$ ,  $I_{T}^{bc}$ ,  $I_{T}^{ca}$ : the RMS ac currents entering the three single-phase converters  $I_{T,dc}^{ab}$ ,  $I_{T,dc}^{bc}$ ,  $I_{T,dc}^{ca}$ : the average dc currents in the three single-phase converters  $I_{T,dc}^{3-\Delta}$ : the average dc link current

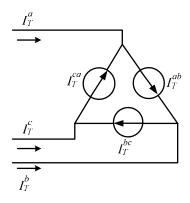

Figure 2.4 Three-phase delta-connected thyristor converter model

In the model, the ac sides of the three single-phase converters are delta-connected. Each converter contributes ac currents to two phases. The dc sides of the converters are in parallel. The sum of the dc currents in the converters gives the dc link current. The model is equivalent to three-phase converters with respect to both the RMS fundamental ac currents entering the three-phase converters and the average dc link current. Details will now be presented.

#### 2.1.1.1 Delta-Connection Approach

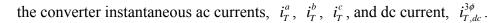

The delta-connection modeling approach can be illustrated using the following MATLAB Simulink example for a three-phase unbalanced thyristor converter in the continuous conduction mode. Using the SimPowerSystems toolbox, the converter is operated at firing angles of 10 degrees with a constant resistive dc load. Figure 2.5 shows

Figure 2.5 The ac and dc currents in a three-phase thyristor converter

From Figure 2.5, the currents in the equivalent, delta-connected thyristor converter model can be obtained through the following observations with T1 to T6 referred to thyristors in Figure 2.3:

- $i_T^{ab}(t)$  is instantaneous ac current flowing between phase a and phase b when the thyristor pair (T1, T6) or (T3, T4) conducts;

- $i_T^{bc}(t)$  is instantaneous ac current flowing between phase b and phase c when the thyristor pair (T2, T3) or (T5, T6) conducts;

- $i_T^{ca}(t)$  is instantaneous ac current flowing between phase c and phase a when the thyristor pair (T1, T2) or (T4, T5) conducts;

- $i_{T.dc}^{ab}(t)$  is instantaneous dc current in the thyristor pairs (T1, T6) and (T3, T4);

- $i_{T,dc}^{bc}(t)$  is instantaneous dc current in the thyristor pairs (T2, T3) and (T5, T6);

- $i_{T,dc}^{ca}(t)$  is instantaneous dc current in the thyristor pairs (T1, T2) and (T4, T5).

Please note that the same approach can be applied to the diode rectifier model and the

PWM converter model.

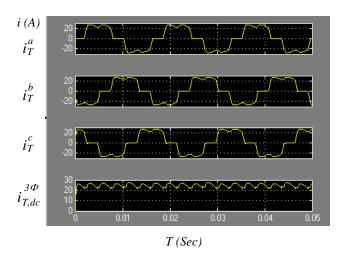

The currents in the delta-connected model are generated in MATLAB Simulink and shown in Figure 2.6. It is noted that the dc current in each single-phase converter includes nearly linear segments, which correspond to the dc currents through the single-phase converter during commutation. Compared with  $i_T^a$ ,  $i_T^b$ ,  $i_T^c$ , and  $i_{T,dc}^{3\phi}$ , it can be seen that the following relationship holds:

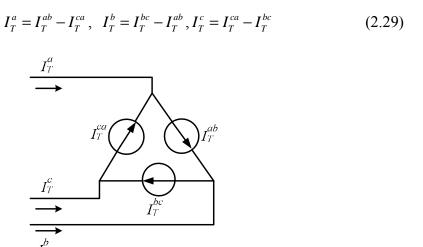

$$i_T^{a}(t) = i_T^{ab}(t) - i_T^{ca}(t), \quad i_T^{b}(t) = i_T^{bc}(t) - i_T^{ab}(t), \quad i_T^{c}(t) = i_T^{ca}(t) - i_T^{bc}(t)$$

(2.1)

$$i_{T,dc}^{3\phi}(t) = i_{T,dc}^{3-\Delta}(t) = i_{T,dc}^{ab}(t) + i_{T,dc}^{bc}(t) + i_{T,dc}^{ca}(t)$$

(2.2)

Let  $i_T^{ab}$ ,  $i_T^{bc}$ , and  $i_T^{ca}$  be the ac currents and  $i_{T,dc}^{ab}$ ,  $i_{T,dc}^{bc}$ ,  $i_{T,dc}^{ca}$  be the dc currents in the three single-phase converters. The model becomes equivalent to the three-phase converter with respect to the ac currents and dc current as shown in (2.1) and (2.2).

Figure 2.6 The ac and dc currents in the delta-connected converter model

From the above analysis, it can be seen that the single-phase converters have the following characteristics:

- (i) Each converter rectifies/inverts one line-to-line voltage;

- (ii) At each frequency, each phase current equals the difference of the ac currents entering two single-phase converters, e.g., at the fundamental frequency:

$$I_T^a = I_T^{ab} - I_T^{ca}, \quad I_T^b = I_T^{bc} - I_T^{ab}, \quad I_T^c = I_T^{ca} - I_T^{bc}$$

(2.3)

(iii) Their average dc currents add and the sum is the average dc link current:

$$I_{T,dc}^{3-\Delta} = I_{T,dc}^{ab} + I_{T,dc}^{bc} + I_{T,dc}^{ca}$$

(2.4)

(iv) Their average dc power,  $P_{T,dc}^{ab}$ ,  $P_{T,dc}^{bc}$ ,  $P_{T,dc}^{ca}$ , adds and the sum is the power through the dc link,  $P_{T,dc}^{3-\Delta}$ :

$$P_{T,dc}^{3-\Delta} = P_{T,dc}^{ab} + P_{T,dc}^{bc} + P_{T,dc}^{ca}$$

(2.5)

In the model, the ac current in a single-phase converter always flows between the two phases to which it is connected. Hence, the three single-phase converters can be treated as delta-connected current components in the ac systems. On the dc side, the dc link current is equal to the sum of the three dc currents in the single-phase converters. Equivalent ac and dc components are created as shown in Figure 2.7. Based on the equivalent circuits, three-phase converters and the model will be equivalent using participation coefficients and equivalence coefficients. The details are now presented.

- (a) The equivalent delta-connected component in ac systems

- (b) The equivalent parallel component in dc systems

Figure 2.7 Equivalent ac and dc components of the delta-connected converter model

## 2.1.2 Determining DC Current and Power in the Delta-Connected Model

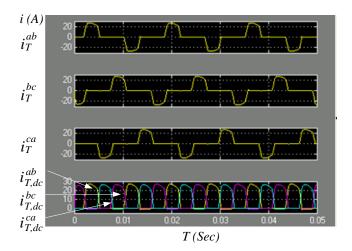

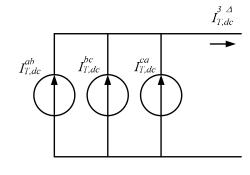

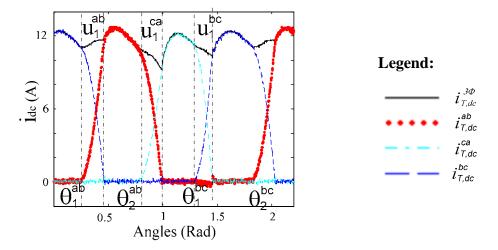

The average dc currents,  $I_{T,dc}^{LL}$ , with  $LL \in \{ab,bc,ca\}$ , and the average dc power,  $P_{T,dc}^{LL}$ , in the single-phase converters are now calculated. Figure 2.8 shows the dc currents in a three-phase thyristor converter and the three single-phase converters. It is noted that  $i_{T,dc}^{LL}$  and  $i_{T,dc}^{3\phi}$  are the same during the full conduction of the three-phase converter. The following notation is used.

$i_{T,dc}^{3\phi}$ : the instantaneous dc current in the three-phase converter

$i_{T,dc}^{LL}$ : the instantaneous dc currents in the single-phase converters

Subscript 1, 2: start and end respectively

$\theta_1^{LL}$ : the starting angles of the linear increasing periods in the single-phase converters, determined by the firing angles

$u_1^{LL}$ : the conduction angles of the linear increasing periods in the single-phase

Figure 2.8 The dc currents in a three-phase thyristor converter,  $i_{T,dc}^{3\phi}$ , and the three single-phase converters,  $i_{T,dc}^{LL}$

In order to simplify the model and preserve the real power, the following assumptions are made:

- A7.  $i_{T,dc}^{LL}$  changes linearly during commutation of the corresponding thyristors in three-phase converters.

- A8. During conduction, each single-phase converter's output voltage is equal to that of the three-phase converter. Otherwise, it is open circuit.

- A9. The percentages of the real power losses in the single-phase converters are equal to that of the three-phase converter.

Using the above assumptions, the dc current in each single-phase converter,  $i_{T,dc}^{LL}$ , consists of the following four periods: ( $\omega$ - the fundamental frequency)

•  $\theta_1^{LL} \le \omega t \le \theta_1^{LL} + u_1^{LL}$  - Linear increasing period.  $i_{T,dc}^{LL}$  increases linearly from zero when the three-phase converter is in commutation;

- $\theta_1^{LL} + u_1^{LL} \le \omega t \le \theta_2^{LL}$  Full conduction period.  $i_{T,dc}^{LL}$  is equal to  $i_{T,dc}^{3\phi}$  and the three-phase converter is in the full conduction.

- $\theta_2^{LL} \le \omega t \le \theta_2^{LL} + u_2^{LL}$  Linear decreasing period.  $i_{T,dc}^{LL}$  decreases linearly to zero when the three-phase converter is in the commutation.  $\theta_2^{LL}$  is the commutation starting angle.  $u_2^{LL}$  is the commutation angle.

- Otherwise, the dc current is equal to zero.

The conduction starting angles,  $\theta_1^{LL}$ , are dependent on the dc voltages, the firing angles, and the conduction modes. Detailed expressions will be presented in the following sections.

It is noted in Figure 2.8 that during the commutation of the three-phase converter, the dc current in one single-phase converter increases from zero while the dc current in another single-phase converter decreases to zero. As such, the following relationship holds for  $\theta_2^{LL}$  and  $u_2^{LL}$ .

$$\theta_2^{ab} = \theta_1^{ca}, \quad \theta_2^{bc} = \theta_1^{ab}, \quad \theta_2^{ca} = \theta_1^{bc}$$

$u_2^{ab} = u_1^{ca}, \quad u_2^{bc} = u_1^{ab}, \quad u_2^{ca} = u_1^{bc}$

Given the conduction angles, the average dc current in each single-phase converter is equal to the average of the instantaneous dc current in a period of  $\pi$ :

$$I_{T,dc}^{LL} = \frac{1}{\pi} \int_{0}^{\pi} i_{T,dc}^{LL}(\omega t) d(\omega t)$$

$$= \frac{1}{\pi} \left[ \int_{\theta_{1}^{LL} + u_{1}^{LL}}^{\theta_{1}^{LL} + u_{1}^{LL}} i_{T,dc}^{LL}(\omega t) \cdot d(\omega t) + \int_{\theta_{2}^{LL} + u_{1}^{LL}}^{\theta_{2}^{LL}} i_{T,dc}^{LL}(\omega t) \cdot d(\omega t) + \int_{\theta_{2}^{LL}}^{\theta_{2}^{LL} + u_{2}^{LL}} i_{T,dc}^{LL}(\omega t) \cdot d(\omega t) \right]$$

(2.6)

Based on A8, the dc voltage,  $v_{T,dc}^{ab}$ , on the single-phase converter between phase a and

phase b can be determined using the dc voltage on the three-phase converter [1]:

$$v_{T,dc}^{ab}\left(\omega t\right) = \begin{cases} \frac{1}{2} \left[v_{T}^{ab}\left(\omega t\right) - v_{T}^{bc}\left(\omega t\right)\right] & \theta_{1}^{ab} \leq \omega t \leq \theta_{1}^{ab} + u_{1}^{ab} \\ v_{T}^{ab}\left(\omega t\right) & \theta_{1}^{ab} + u_{1}^{ab} \leq \omega t \leq \theta_{2}^{ab} \\ \frac{1}{2} \left[v_{T}^{ab}\left(\omega t\right) - v_{T}^{ca}\left(\omega t\right)\right] & \theta_{2}^{ab} \leq \omega t \leq \theta_{2}^{ab} + u_{2}^{ab} \\ v_{T,dc}\left(\omega t\right) & otherwise \end{cases}$$

$$(2.7)$$

where:

$v_T^{LL}$ : the instantaneous line-to-line converter voltages

In a similar manner,  $v_{T,dc}^{bc}$  and  $v_{T,dc}^{ca}$  follow. The average dc power can be calculated by averaging the instantaneous power in a period of  $\pi$ :

$$P_{T,dc}^{LL} = \frac{1}{\pi} \int_{\theta_{l}^{LL}}^{\theta_{2}^{LL} + u_{2}^{LL}} v_{T,dc}^{LL} \left(\omega t\right) \cdot i_{T,dc}^{LL} \left(\omega t\right) \cdot d\left(\omega t\right)$$

(2.8)

The instantaneous dc currents in the single-phase converters are determined differently for the continuous and discontinuous conduction modes. Thus, the average dc current and the average dc power are different in the two conduction modes. They will be discussed respectively next.

## 2.1.2.1 Continuous Conduction

In the continuous conduction mode, the dc capacitor can be assumed to be zero from A5. During the full conduction period, the dc output voltage,  $v_{T,dc}^{LL}(\omega t)$ , is equal to the line-to-line voltage,  $v_T^{LL}(\omega t)$ , as given in (2.7). The instantaneous dc currents,  $i_{T,dc}^{LL}$ , satisfy the Kirchoff's Current Law (KCL) in the dc system:

$$v_{T,dc}^{LL}(\omega t) = L_{dc} \frac{d\left(i_{T,dc}^{LL}(\omega t)\right)}{dt} + R_{dc} \cdot i_{T,dc}^{LL}(\omega t)$$

(2.9)

It is assumed that  $\frac{L_{dc}}{R_{dc}}$  is small and then  $\frac{di}{dt}$  can be neglected. With the line-to-line voltages defined as:

$$v_T^{LL}(\omega t) = \sqrt{2} |V_T^{LL}| \cdot \sin(\omega t + \delta_{V_T}^{LL})$$

(2.10)

where:

$\left|V_{T}^{LL}\right|,~~\delta_{V_{T}}^{LL}$ : the magnitudes and phase angles of the RMS fundamental line-to-line converter voltages respectively

The dc currents can be simplified as:

$$i_{T,dc}^{LL}(\omega t) \approx \frac{v_{T,dc}^{LL}(\omega t)}{R_{dc}}$$

$$= \frac{\sqrt{2} |V_T^{LL}|}{R_{dc}} \left| \sin(\omega t + \delta_{V_T}^{LL}) \right|$$

(2.11)

During the linear conduction periods,  $i_{T,dc}^{LL}$  changes linearly and is continuous at the boundary of linear conduction periods and the full conduction period.  $i_{T,dc}^{LL}$  at  $\theta_1^{LL} + u_1^{LL}$  and  $\theta_2^{LL}$  can be determined using (2.11) and  $i_{T,dc}^{LL}$  can be represented as:

$$i_{T,dc}^{LL}(\boldsymbol{\omega}t) = \begin{cases} \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{R_{dc}} \left| \sin \left( \theta_{1}^{LL} + u_{1}^{LL} + \delta_{V_{T}}^{LL} \right) \right| \cdot \frac{\left( \boldsymbol{\omega}t - \theta_{1}^{LL} \right)}{u_{1}^{LL}} & \theta_{1}^{LL} \leq \boldsymbol{\omega}t \leq \theta_{1}^{LL} + u_{1}^{LL} \\ \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{R_{dc}} \left| \sin \left( \boldsymbol{\omega}t + \delta_{V_{T}}^{LL} \right) \right| & \theta_{1}^{LL} + u_{1}^{LL} \leq \boldsymbol{\omega}t \leq \theta_{2}^{LL} \\ \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{R_{dc}} \left| \sin \left( \theta_{2}^{LL} + \delta_{V_{T}}^{LL} \right) \right| \cdot \left( 1 - \frac{1}{u_{2}^{LL}} \cdot \left( \boldsymbol{\omega}t - \theta_{2}^{LL} \right) \right) & \theta_{2}^{LL} \leq \boldsymbol{\omega}t \leq \theta_{2}^{LL} + u_{2}^{LL} \\ 0 & otherwise \end{cases}$$

$$(2.12)$$

The average dc current,  $I_{T,dc}^{LL}$ , can be obtained by substituting (2.12) into (2.6):

$$I_{T,dc}^{LL} = \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{2\pi R_{dc} \cdot u_{1}^{LL}} \left| \sin \left( \theta_{1}^{LL} + u_{1}^{LL} + \delta_{V_{T}}^{LL} \right) \right| + \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{2\pi R_{dc} \cdot u_{2}^{LL}} \left| \sin \left( \theta_{2}^{LL} + \delta_{V_{T}}^{LL} \right) \right|$$

$$+ \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{\pi R_{dc}} \left( -\cos \left( \theta_{2}^{LL} + \delta_{V_{T}}^{LL} \right) + \cos \left( \theta_{1}^{LL} + u_{1}^{LL} + \delta_{V_{T}}^{LL} \right) \right)$$

$$(2.13)$$

The conduction angles,  $\theta_1^{LL}$ ,  $\theta_2^{LL}$ , are determined as follows. With equi-distant control from A1, the firing angle,  $\alpha_{ab}$ , is specified to control the thyristors between phase a and phase b.  $\theta_1^{ab}$  can be calculated using the line-to-line voltage  $v_T^{ca}$  at  $\theta_1^{ab} - \alpha_{ab}$ , where  $v_T^{ca}$  is equal to zero:

$$v_T^{ca} \left( \theta_1^{ab} - \alpha_{ab} \right) = \sqrt{2} \left| V_T^{ca} \right| \sin \left( \theta_1^{ab} - \alpha_{ab} + \delta_{V_T}^{ca} \right) = 0$$

(2.14)

$$\theta_1^{ab} = \theta_2^{bc} = \alpha_{ab} - \delta_{V_n}^{ca} \tag{2.15}$$

$\theta_1^{LL}$  and  $\theta_2^{LL}$  of other single-phase converters are determined:

$$\theta_1^{ca} = \theta_2^{ab} = \theta_1^{ab} + \frac{1}{3}\pi \tag{2.16}$$

$$\theta_1^{bc} = \theta_2^{ca} = \theta_1^{ca} + \frac{1}{3}\pi \tag{2.17}$$

The average power,  $P_{T,dc}^{LL}$ , in each single-phase thyristor converter can be obtained by substituting  $v_{T,dc}^{LL}$  and  $i_{T,dc}^{LL}$  in different periods into (2.8). Next,  $I_{T,dc}^{LL}$  and  $P_{T,dc}^{LL}$  are calculated for the discontinuous conduction mode.

#### 2.1.2.2 Discontinuous Conduction

In the discontinuous conduction mode, it is assumed that the dc capacitor voltage,  $V_{C_{dc}}$ , is constant. The instantaneous dc link current is equal to zero in the three-phase converter when the thyristors are fired. Hence, there is no commutation and  $u_1^{LL}$  and  $u_2^{LL}$  are equal to zero.  $i_{T,dc}^{LL}$  is equal to the dc current in  $L_{dc}$  during

the conduction period  $(\theta_1^{LL}, \theta_2^{LL})$ :

$$i_{T,dc}^{LL}(\omega t) = \frac{1}{\omega L_{dc}} \int_{\theta_{1}^{LL}}^{\omega t} \left[ \sqrt{2} \left| V_{T}^{LL} \right| \sin\left(\omega t + \delta_{V_{T}}^{LL}\right) - V_{C_{dc}} \right] d\left(\omega t\right)$$

$$= \frac{\sqrt{2} \left| V_{T}^{LL} \right|}{\omega L_{dc}} \left[ \cos\left(\theta_{1}^{LL} + \delta_{V_{T}}^{LL}\right) - \cos\left(\omega t + \delta_{V_{T}}^{LL}\right) \right] - \frac{V_{C_{dc}}}{\omega L_{dc}} \left(\omega t - \theta_{1}^{LL}\right)$$

(2.18)

Otherwise,  $i_{T,dc}^{LL}$  is equal to zero. Therefore,  $i_{T,dc}^{LL}$  can be represented as:

$$i_{T,dc}^{LL}(\omega t) = \begin{cases} A_{LL} \cdot \cos(\omega t) + B_{LL} \cdot \sin(\omega t) + C_{LL} \cdot \omega t + D_{LL} & \theta_1^{LL} \le \omega t \le \theta_2^{LL} \\ 0 & otherwise \end{cases}$$

(2.19)

where:

$$A_{LL} = \frac{-\sqrt{2} \left| V_T^{LL} \right|}{\omega L_{dc}} \cos \left( \delta_{V_T}^{LL} \right), \quad B_{LL} = \frac{\sqrt{2} \left| V_T^{LL} \right|}{\omega L_{dc}} \sin \left( \delta_{V_T}^{LL} \right),$$

$$C_{LL} = -\frac{V_{C_{dc}}}{\omega L_{dc}}, \quad D_{LL} = -A_{LL} \cdot \cos\left(\theta_1^{LL}\right) - B_{LL} \cdot \sin\left(\theta_1^{LL}\right) - C_{LL} \cdot \theta_1^{LL}$$

Then, the average dc current,  $I_{T,dc}^{LL}$ , can be obtained:

$$I_{T,dc}^{LL} = \frac{1}{\pi} \left[ A_{LL} \cdot \left( \sin \left( \theta_{2}^{LL} \right) - \sin \left( \theta_{1}^{LL} \right) \right) + B_{LL} \cdot \left( -\cos \left( \theta_{2}^{LL} \right) + \cos \left( \theta_{1}^{LL} \right) \right) \right]$$

$$+ \frac{1}{\pi} \left[ \frac{C_{LL}}{2} \cdot \left( \left( \theta_{2}^{LL} \right)^{2} - \left( \theta_{1}^{LL} \right)^{2} \right) + D_{LL} \cdot \left( \theta_{2}^{LL} - \theta_{1}^{LL} \right) \right]$$

(2.20)

Two different cases are considered to determine the conduction angles,  $\theta_1^{LL}$  and  $\theta_2^{LL}$ . In the first case, the thyristors are fired when  $v_{T,dc} \ge V_{C_{dc}}$ . The thyristors start to conduct immediately.  $\theta_1^{LL}$  is determined in (2.15) to (2.17). At  $\theta_2^{LL}$ ,  $i_{T,dc}^{LL}$  decreases to zero in (2.18).  $\theta_2^{LL}$  can be solved using the Newton method.

In the second case, the thyristors are fired when  $v_{T,dc} < V_{C_{dc}}$ . The thyristors do not conduct until  $v_{T,dc}$  becomes equal to  $V_{C_{dc}}$ :

$$v_{T,dc}^{LL}\left(\boldsymbol{\theta}_{1}^{LL}\right) = \sqrt{2}\left|V_{T}^{LL}\right| \cdot \left|\sin\left(\boldsymbol{\theta}_{1}^{LL} + \boldsymbol{\delta}_{V_{T}}^{LL}\right)\right| = V_{C_{dc}}$$

$$(2.21)$$

$\theta_1^{LL}$  can be determined:

$$\theta_{1}^{LL} = \sin^{-1} \left( \frac{V_{T,dc}}{\sqrt{2} |V_{T}^{LL}|} \right) - \delta_{V_{T}}^{LL} \qquad 0 \le \theta_{1}^{LL} \le 2\pi$$

(2.22)

$\theta_2^{LL}$  is determined in the same manner as the first case.

Since there is no commutation,  $P_{T,dc}^{LL}$ , in the discontinuous conduction mode can be determined using  $v_{T,dc}^{LL}$  and  $i_{T,dc}^{LL}$ :

$$P_{T,dc}^{LL} = \frac{1}{\pi} \int_{\theta_{l}^{LL}}^{\theta_{2}^{LL}} v_{T,dc}^{LL} \left(\omega t\right) \cdot i_{T,dc}^{LL} \left(\omega t\right) \cdot d\left(\omega t\right)$$

(2.23)

$$=\frac{1}{\pi}\int_{\theta_{1}^{LL}}^{\theta_{2}^{LL}}\sqrt{2}\left|V_{T}^{LL}\right|\cdot\sin\left(\omega t+\delta_{V_{T}}^{LL}\right)\cdot\left[A_{LL}\cdot\cos\left(\omega t\right)+B_{LL}\cdot\sin\left(\omega t\right)+C_{LL}\cdot\omega t+D_{LL}\right]\cdot d\left(\omega t\right)$$

From above, it can be seen that  $I_{T,dc}^{LL}$  and  $P_{T,dc}^{LL}$  are not balanced either in the continuous conduction mode or in the discontinuous conduction mode because of the unbalanced voltages. Hence, the contributions of the single-phase converters to the dc link current and the dc power are not equal. This difference is now captured by introducing three scalar dc current participation coefficients,  $\lambda_I^{ab}$ ,  $\lambda_I^{bc}$ ,  $\lambda_I^{ca}$ , and three scalar dc power participation coefficients,  $\lambda_P^{ab}$ ,  $\lambda_P^{bc}$ ,  $\lambda_P^{ca}$ , into the model.

## 2.1.3 Participation Coefficients

In distribution systems, ac voltages and ac currents are generally unbalanced in both magnitude and phase. Hence, each single-phase converter in the delta-connected model contributes differently to the current and the power through the dc link. It is important to determine the contribution of each single-phase converter to the total dc current and power. Three current participation coefficients,  $\lambda_{T,I}^{ab}$ ,  $\lambda_{T,I}^{bc}$ ,  $\lambda_{T,I}^{ca}$ , are introduced to capture the imbalance of the ac current magnitudes of three-phase converters.  $\lambda_{T,I}^{ab}$  is

defined as the ratio of the average dc current,  $I_{T,dc}^{ab}$ , in the single-phase converter between phase a and phase b to the sum of the average dc currents in the three single-phase converters:

$$\lambda_{T,I}^{ab} = \frac{I_{T,dc}^{ab}}{I_{T,dc}^{ab} + I_{T,dc}^{bc} + I_{T,dc}^{ca}}$$

(2.24)

In a similar manner,  $\lambda_{T,I}^{bc}$  and  $\lambda_{T,I}^{ca}$  follow.

Three real power participation coefficients,  $\lambda_{T,P}^{ab}$ ,  $\lambda_{T,P}^{bc}$ ,  $\lambda_{T,P}^{ca}$ , are introduced to capture the imbalance of ac real power in three-phase converters in terms of average dc power in the single-phase converters.  $\lambda_{T,P}^{ab}$  is defined as the ratio of the average dc power,  $P_{T,dc}^{ab}$ , of the single-phase converter between phase a and phase b to the sum of the average dc power on the three single-phase converters:

$$\lambda_{T,P}^{ab} = \frac{P_{T,dc}^{ab}}{P_{T,dc}^{ab} + P_{T,dc}^{bc} + P_{T,dc}^{ca}}$$

(2.25)

Similarly,  $\lambda_{T,P}^{bc}$  and  $\lambda_{T,P}^{ca}$  follow. Next, the delta-connected model will be made equivalent to a three-phase converter with respect to the RMS fundamental ac and the average dc currents.

# **2.1.4** Equivalence Transformation

From above, three-phase thyristor converters are modeled as three, delta-connected, singe-phase converters. The models are made equivalent with respect to the RMS fundamental ac and the average dc currents entering/leaving the three-phase converter. A dc equivalence coefficient,  $K_{T,dc}$ , is introduced to equalize the dc link currents in Figure

2.3 and Figure 2.4. It is defined as the ratio of the average dc current of a three-phase thyristor converter,  $I_{T,dc}^{3\phi}$ , to the average dc current,  $I_{T,dc}^{3-\Delta}$ , of the delta-connected model:

$$K_{T,dc} = \frac{I_{T,dc}^{3\phi}}{I_{T,dc}^{3-\Delta}} \tag{2.26}$$

$I_{T,dc}^{3\phi}$  is equal to the average of the instantaneous dc current in a period of  $2\pi$ :

$$I_{T,dc}^{3\phi} = \frac{1}{2\pi} \int_{0}^{2\pi} i_{T,dc}^{3\phi}(t) \cdot d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{2\pi} \left[ \left( i_{T,dc}^{ab}(t) + i_{T,dc}^{ca}(t) \right) + \left( i_{T,dc}^{bc}(t) + i_{T,dc}^{ab}(t) \right) + \left( i_{T,dc}^{ca}(t) + i_{T,dc}^{bc}(t) \right) \right] \cdot d(\omega t)$$

$$= I_{T,dc}^{3-\Delta}$$

$$= I_{T,dc}^{3-\Delta}$$

(2.27)

Thus,

$$K_{T,dc} = 1 \tag{2.28}$$

Now, the ac sides of the two models will be equalized with respect to the RMS fundamental ac currents. From the ac equivalent representation of the converter model in Figure 2.9, it can be seen that the phase currents entering a three-phase converter can be obtained using the ac currents entering the delta-connected single-phase converters:

Figure 2.9 The ac equivalent component of the delta-connected converter model

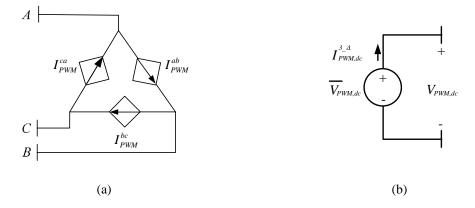

It is noted that instantaneous ac current,  $i_T^{LL}$ , is periodic and its absolute value gives the instantaneous dc current: