## Consensus Protocols Exploiting Network Programmability

Doctoral Dissertation submitted to the Faculty of Informatics of the Università della Svizzera Italiana in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> presented by Huynh Tu Dang

under the supervision of Robert Soulé and Fernando Pedone

March 2019

## Dissertation Committee

| Antonio Carzaniga | Università della Svizzera italiana                 |

|-------------------|----------------------------------------------------|

| Patrick Eugster   | Technical University of Darmstadt                  |

| Marco Canini      | King Abdullah University of Science and Technology |

Dissertation accepted on 11 March 2019

Research Advisor Robert Soulé Co-Advisor

Fernando Pedone

PhD Program Director Walter Binder I certify that except where due acknowledgement has been given, the work presented in this thesis is that of the author alone; the work has not been submitted previously, in whole or in part, to qualify for any other academic award; and the content of the thesis is the result of work which has been carried out since the official commencement date of the approved research program.

> Huynh Tu Dang Lugano, 11 March 2019

## Abstract

Services rely on replication mechanisms to be available at all time. The service demanding high availability is replicated on a set of machines called replicas. To maintain the consistency of replicas, a consensus protocol such as Paxos [1] or Raft [2] is used to synchronize the replicas' state. As a result, failures of a minority of replicas will not affect the service as other non-faulty replicas continue serving requests.

A consensus protocol is a procedure to achieve an agreement among processors in a distributed system involving unreliable processors. Unfortunately, achieving such an agreement involves extra processing on every request, imposing a substantial performance degradation. Consequently, performance has long been a concern for consensus protocols. Although many efforts have been made to improve consensus performance, it continues to be an important problem for researchers.

This dissertation presents a novel approach to improving consensus performance. Essentially, it exploits the programmability of a new breed of network devices to accelerate consensus protocols that traditionally run on commodity servers. The benefits of using programmable network devices to run consensus protocols are twofold: The network switches process packets faster than commodity servers and consensus messages travel fewer hops in the network. It means that the system throughput is increased and the latency of requests is reduced.

The evaluation of our network-accelerated consensus approach shows promising results. Individual components of our FPGA-based and switch-based consensus implementations can process 10 million and 2.5 billion consensus messages per second, respectively. Our FPGA-based system as a whole delivers 4.3 times performance of a traditional software consensus implementation. The latency is also better for our system and is only one third of the latency of the software consensus implementation when both systems are under half of their maximum throughputs. In order to drive even higher performance, we apply a partition mechanism to our switch-based system, leading to 11 times better throughput and 5 times better latency. By dynamically switching between software-based and network-based implementations, our consensus systems not only improve performance but also use energy more efficiently. Encouraged by those benefits, we developed a fault-tolerant non-volatile memory system. A prototype using software memory controller demonstrated reasonable overhead over local memory access, showing great promise as scalable main memory.

Our network-based consensus approach would have a great impact in data centers. It not only improves performance of replication mechanisms which relied on consensus, but also enhances performance of services built on top of those replication mechanisms. Our approach also motivates others to move new functionalities into the network, such as, key-value store [3] and stream processing [4]. We expect that in the near future, applications that typically run on traditional servers will be folded into networks for performance.

# Preface

The result of this research appears in the following publications:

Huynh Tu Dang, Daniele Sciascia, Marco Canini, Fernando Pedone, and Robert Soulé. 2015. NetPaxos: consensus at network speed. In Proceedings of the 1st ACM SIGCOMM Symposium on Software Defined Networking Research (SOSR '15).

Huynh Tu Dang, Marco Canini, Fernando Pedone, and Robert Soulé. 2016. Paxos Made Switch-y. SIGCOMM Computer Communication Review. 46, 2 (May 2016), 18-24.

Huynh Tu Dang, Pietro Bressana, Han Wang, Ki Suh Lee, Marco Canini, Noa Zilberman, Fernando Pedone, Robert Soulé. 2018. P4xos Consensus As A Network Service. Technical Report Series in Informatics, USI-INF-TR-2018-01.

Huynh Tu Dang, Pietro Bressana, Han Wang, Ki Suh Lee, Marco Canini, Noa Zilberman, Fernando Pedone, Robert Soulé. 2018. Partitioned Paxos via the Network Data Plane. arXiv:1901.08806 [cs.DC].

Yuta Tokusashi, Huynh Tu Dang, Fernando Pedone, Robert Soulé, and Noa Zilberman. 2019. The Case For In-Network Computing On Demand. To be appeared in Proceedings of the 14th Eurosys Conference (Eurosys'19).

Huynh Tu Dang, Jaco Hofmann, Yang Liu, Marjan Radi, Dejan Vucinic, Robert Soulé, and Fernando Pedone. 2018. Consensus for Non-volatile Main Memory. In Proceedings of the 26th IEEE International Conference on Network Protocols (ICNP), Cambridge, 2018, pp. 406-411.

# Acknowledgements

Foremost, I would like to express my sincere gratitude to my advisor Prof. Robert Soulé and my co-advisor Prof. Fernando Pedone for continuous support during my Ph.D. studies. I have learned not only how to conduct research but also invaluable knowledge under their guidance. Their sense of humor and endless encouragement have helped me to overcome many obstacles throughout my studies.

Besides my advisors, I would like to thank my thesis committee members: Prof. Antonio Carzaniga, Prof. Marco Canini, and Prof. Patrick Eugster, for their support and insightful comments. I wish to thank USI staffs for their countless assistance during my program.

My sincere thanks also go to Dr. Dejan Vucinic and Dr. Zvonimir Bandic for offering me an internship at Western Digital and guiding me through an exciting project. I want to thank Western Digital staffs who have assisted me during my internship.

This thesis would not have been possible without my co-authors: Daniele Sciascia, Theo Jepsen, Pietro Bressana, Han Wang, Ki Suh Lee, Hakim Weatherspoon, Marco Canini, Noa Zilberman, Jaco Hofmann, Yang Liu, Marjan Radi, and Yuta Tokusashi. I would particularly like to thank Daniele for sharing his experience with libpaxos, and for helping me in many unnamed tasks.

I thank my fellow labmates: Paulo Coelho, Daniele Sciascia, Leandro Pacheco, Enrique Fynn, Eduardo Bezzera, Odorico Mendizabal, Edson Camargo, Ricardo Padilha, Theo Jepsen, Pietro Bressana, Mojtaba Eslahi-Kelorazi, Vahid Lakhani, Parisa Marandi, Loan Ton, Long Hoang Le and many other open-space members for open-ended coffee talks, and for all the fun and activities we have had together in the last four years.

I want to thank my family: my parents, my sister's family, my cousins, Oanh and Vernon for their praise and support.

Last but not least, I dedicate this thesis to my wife, Xuan, for accompanying me to anywhere over the world, for delicious meals, for bearing my lovely son, Minh Khang, and most importantly, for her endless love. viii

# Contents

| Co  | onten   | ts      |                                                             | ix   |

|-----|---------|---------|-------------------------------------------------------------|------|

| Lis | st of ] | Figures |                                                             | xiii |

| Lis | st of ' | Tables  |                                                             | xv   |

| 1   | Intr    | oductio | n                                                           | 1    |

|     | 1.1     | This D  | issertation                                                 | 2    |

|     | 1.2     | Evalua  | ition                                                       | 4    |

|     | 1.3     | Resear  | ch Contributions                                            | 5    |

| 2   | Bac     | kgroun  | d                                                           | 7    |

|     | 2.1     | The Co  | onsensus Problem and The Fischer, Lynch and Patterson (FLP) |      |

|     |         | Result  |                                                             | 7    |

|     | 2.2     | The Pa  | ixos Consensus Protocol                                     | 8    |

|     |         | 2.2.1   | Asynchronous, Non-Byzantine Model                           | 8    |

|     |         | 2.2.2   | Basic Paxos                                                 | 9    |

|     |         | 2.2.3   | Implementing Fault-Tolerant Applications with Paxos         | 10   |

|     |         | 2.2.4   | Optimizations                                               | 10   |

|     |         | 2.2.5   | Performance Bottlenecks of Traditional Paxos Systems        | 11   |

|     | 2.3     | Progra  | mmable Network Hardware                                     | 13   |

|     |         | 2.3.1   | Smart Network Interface Cards (Smart NICs)                  | 13   |

|     |         | 2.3.2   | Field Programmable Gate Arrays (FPGAs)                      | 13   |

|     |         | 2.3.3   | Programmable ASICs                                          | 14   |

|     | 2.4     | Langu   | age Support for Network Programming                         | 14   |

|     |         | 2.4.1   | P4: High Level Data Plane Programming Language              | 15   |

|     | 2.5     | Kernel  | -Bypass: Accelerating Performance of Servers                | 16   |

|     |         | 2.5.1   | Methods for Power Consumption Measurement                   | 17   |

|     | 2.6     | Chapte  | er Summary                                                  | 18   |

| 3 | Net  | Paxos   |                                                              | 19 |

|---|------|---------|--------------------------------------------------------------|----|

|   | 3.1  | The Be  | enefits of Network-based Consensus                           | 19 |

|   | 3.2  | OpenF   | Flow Extensions for In-Network Consensus                     | 20 |

|   | 3.3  | Fast N  | etwork Consensus                                             | 21 |

|   |      | 3.3.1   | Protocol Design                                              | 22 |

|   |      | 3.3.2   | Evaluation                                                   | 25 |

|   | 3.4  | Summ    | nary                                                         | 28 |

| 4 | P4x  | os: Cor | nsensus As A Network Service                                 | 29 |

|   | 4.1  | P4xos   | Design                                                       | 29 |

|   |      | 4.1.1   | Paxos header                                                 | 31 |

|   |      | 4.1.2   | Proposer                                                     | 32 |

|   |      | 4.1.3   | Notation                                                     | 32 |

|   |      | 4.1.4   | Leader                                                       | 33 |

|   |      | 4.1.5   | Acceptor                                                     | 34 |

|   |      | 4.1.6   | Learner                                                      | 35 |

|   | 4.2  | Implei  | mentation                                                    | 36 |

|   | 4.3  | Absolu  | ute Performance                                              | 37 |

|   |      | 4.3.1   | ASIC Tofino                                                  | 37 |

|   |      | 4.3.2   | NetFPGA SUME and DPDK                                        | 38 |

|   | 4.4  | End-to  | o-End Performance                                            | 41 |

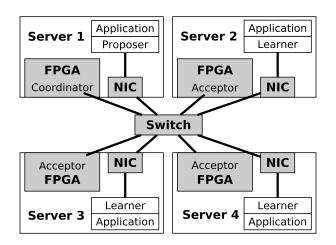

|   |      | 4.4.1   | Experiment Testbed                                           | 42 |

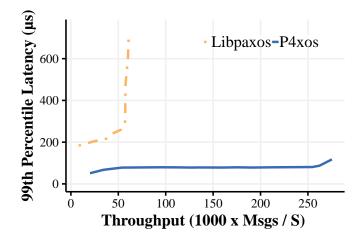

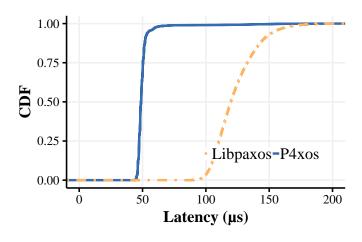

|   |      | 4.4.2   | Baseline Performance of P4xos                                | 42 |

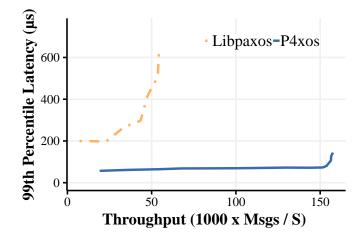

|   |      | 4.4.3   | Case Study: Replicating LevelDB                              | 44 |

|   |      | 4.4.4   | Performance Under Failure                                    | 45 |

|   | 4.5  | Discus  | ssion                                                        | 46 |

|   | 4.6  |         | er Summary                                                   | 48 |

| 5 | Part | itioned | 1 Paxos                                                      | 49 |

|   | 5.1  | Separa  | ating Agreement from Execution for State Machine Replication | 50 |

|   |      | 5.1.1   | Accelerating Agreement                                       | 51 |

|   |      | 5.1.2   | Accelerating Execution                                       | 54 |

|   | 5.2  | Evalua  | ation                                                        | 57 |

|   |      | 5.2.1   | Resource Usage.                                              | 58 |

|   |      | 5.2.2   | End-to-end Experiments                                       | 59 |

|   |      | 5.2.3   | Increase Number of Partitions                                | 63 |

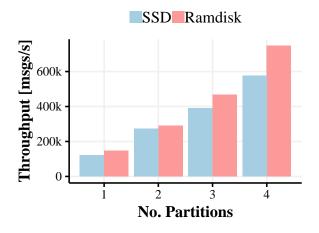

|   |      | 5.2.4   | Storage Medium                                               | 63 |

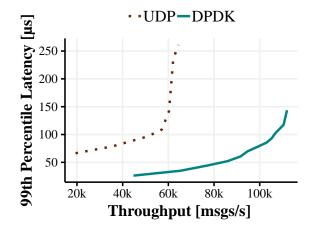

|   |      | 5.2.5   | Effect of Kernel-Bypass Library                              | 64 |

|   |      |         | Tolerance Node Failures                                      | 64 |

|   | 5.3  | Chapt   | er Summary                                               | 66  |

|---|------|---------|----------------------------------------------------------|-----|

| 6 | Enei | gy-Effi | icient In-Network Computing                              | 67  |

|   | 6.1  | The Po  | ower Consumption Concern for In-Network Computing        | 67  |

|   | 6.2  | Scope   |                                                          | 69  |

|   | 6.3  | Case S  | Studies of In-Network Computing                          | 70  |

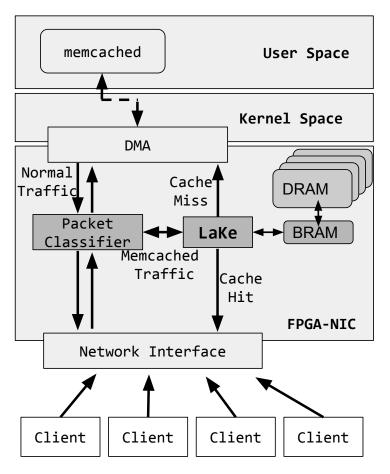

|   |      | 6.3.1   | LaKe: Key-Value Store                                    | 70  |

|   |      | 6.3.2   | P4xos: Consensus                                         | 72  |

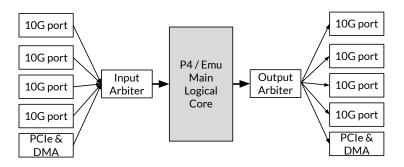

|   |      | 6.3.3   | EMU DNS: Network Service                                 | 72  |

|   |      | 6.3.4   | Applications: Similarities and Differences               | 73  |

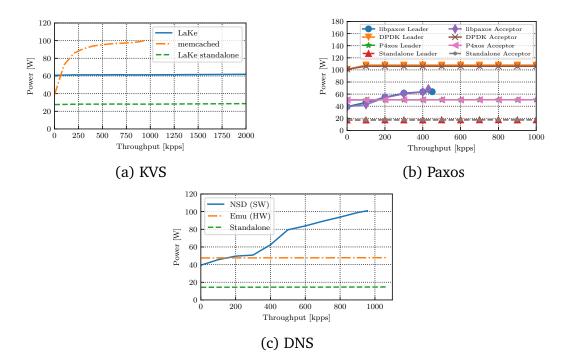

|   | 6.4  | Power   | /Performance Evaluation                                  | 74  |

|   |      | 6.4.1   | Experiment Setup                                         | 75  |

|   |      | 6.4.2   | Key-Value Store                                          | 75  |

|   |      | 6.4.3   | Paxos                                                    | 77  |

|   |      | 6.4.4   | DNS                                                      | 77  |

|   | 6.5  | Lessor  | ns from an FPGA                                          | 78  |

|   |      | 6.5.1   | Clock Gating, Power Gating and Deactivating Modules      | 78  |

|   |      | 6.5.2   | Processing Cores                                         | 79  |

|   |      | 6.5.3   | Memories                                                 | 80  |

|   |      | 6.5.4   | Infrastructure                                           | 80  |

|   | 6.6  | Lessor  | ns from an ASIC                                          | 81  |

|   | 6.7  | Lessor  | ns from a Server                                         | 82  |

|   | 6.8  | When    | To Use In-Network Computing                              | 83  |

|   | 6.9  | In-Net  | work Computing On Demand                                 | 84  |

|   |      | 6.9.1   | In-Network Computing On Demand Controller                | 85  |

|   |      | 6.9.2   | On Demand Applications                                   | 87  |

|   | 6.10 | Discus  | sion                                                     | 92  |

|   | 6.11 | Chapt   | er Summary                                               | 94  |

|   |      |         |                                                          |     |

| 7 |      |         | ased Consensus Powering Fault-Tolerance Memory           | 95  |

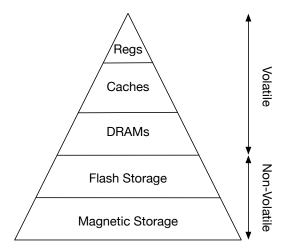

|   | 7.1  |         | ner on Computer Memory                                   | 95  |

|   |      | 7.1.1   | Limitation of Storage Class Memory                       | 97  |

|   |      | 7.1.2   | New Approach to Provide Fault-Tolerance for Non-Volatile |     |

|   |      |         | Main Memory                                              | 98  |

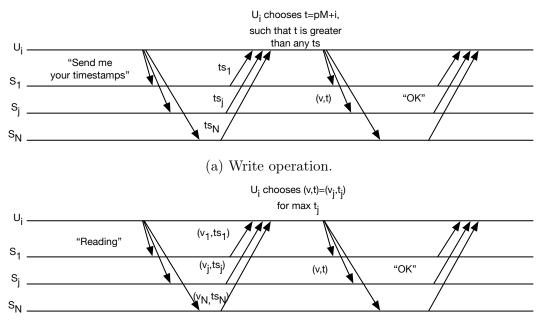

|   | 7.2  |         | ttiya, Bar-Noy, and Dolev Protocol                       | 98  |

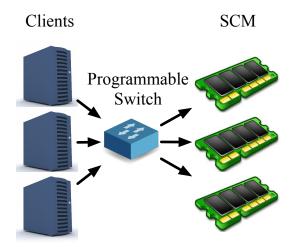

|   | 7.3  | System  | n Design                                                 | 100 |

|   |      | 7.3.1   | Memory Controller                                        | 102 |

|   |      | 7.3.2   | Switch Logic                                             | 102 |

|   |      | 7.3.3   | Failure Assumptions                                      | 103 |

xi

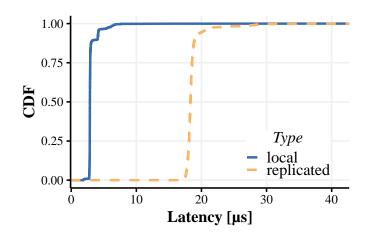

|   | 7.4<br>7.5 | 7.3.4       Implementation       104         Evaluation       104         Chapter Summary       105 |  |  |

|---|------------|-----------------------------------------------------------------------------------------------------|--|--|

| 8 |            |                                                                                                     |  |  |

|   | 8.1        | Network Support for Applications                                                                    |  |  |

|   | 8.2        | Consensus Protocols and Coordination Services 108                                                   |  |  |

|   |            | 8.2.1 State Machine Replication 108                                                                 |  |  |

|   |            | 8.2.2 Primary-Backup Replication                                                                    |  |  |

|   |            | 8.2.3 Deferred Update Replication                                                                   |  |  |

|   | 8.3        | Hardware accelerations 110                                                                          |  |  |

|   | 8.4        | In-Network Computing On Demand                                                                      |  |  |

| 9 |            | clusion 113                                                                                         |  |  |

|   | 9.1        | Limitations and Future Work 114                                                                     |  |  |

|   | 9.2        | Final Remarks 116                                                                                   |  |  |

# Figures

| 2.1 | The leader is the bottleneck in a software-based Paxos deployment.                                                                   | 11 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Besides the bottleneck at the leader, the acceptor becomes the next                                                                  |    |

|     | bottleneck as the degree of replication increases                                                                                    | 12 |

| 2.3 | P4 Workflow                                                                                                                          | 16 |

| 3.1 | NetPaxos architecture. Switch hardware is shaded grey. Other de-<br>vices are commodity servers. The learners each have four network |    |

|     | interface cards.                                                                                                                     | 22 |

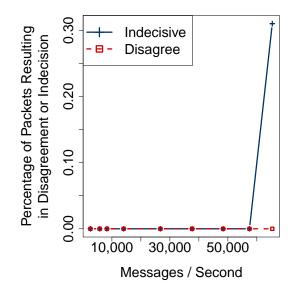

| 3.2 | The percentage of messages in which learners either disagree, or                                                                     |    |

|     | cannot make a decision                                                                                                               | 26 |

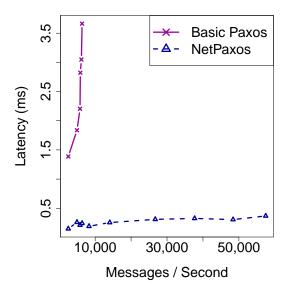

| 3.3 | The throughput vs. latency for basic Paxos and NetPaxos                                                                              | 27 |

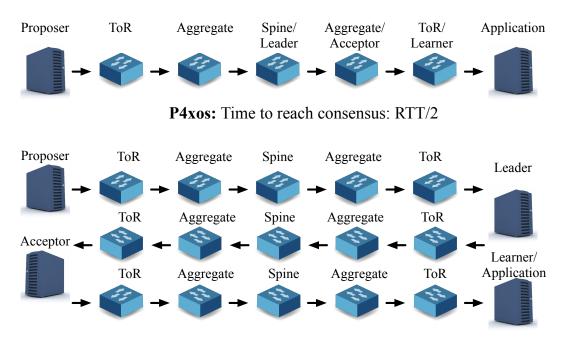

| 4.1 | Contrasting propagation delay for P4xos with server-based de-                                                                        |    |

|     | ployment                                                                                                                             | 30 |

| 4.2 | FPGA test bed for the evaluation.                                                                                                    | 41 |

| 4.3 | The end-to-end throughput vs. latency for Echo                                                                                       | 43 |

| 4.4 | The end-to-end latency CDF for Echo.                                                                                                 | 44 |

| 4.5 | The end-to-end throughput vs. latency for LevelDB                                                                                    | 44 |

| 4.6 | The end-to-end latency CDF of LevelDB                                                                                                | 45 |

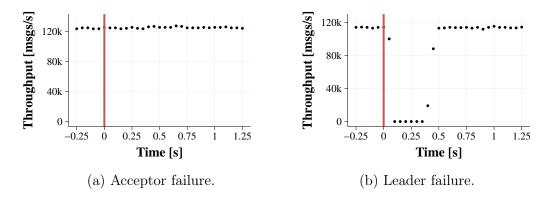

| 4.7 | P4xos performance when (a) an FPGA acceptor fails, and (b) when                                                                      |    |

|     | FPGA leader is replaced by DPDK backup                                                                                               | 46 |

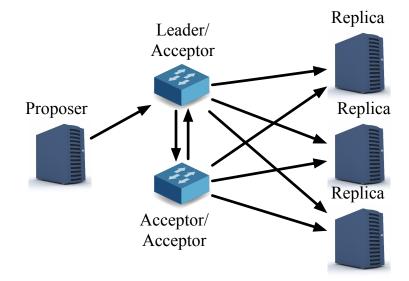

| 5.1 | Example deployment for Partitioned Paxos.                                                                                            | 52 |

| 5.2 | Partitioned Acceptor log, indexed by partition id and instance num-                                                                  |    |

|     | ber                                                                                                                                  | 53 |

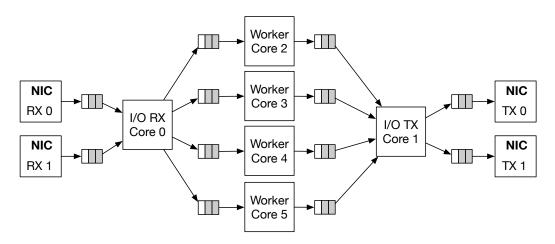

| 5.3 | Partitioned Paxos replica architecture.                                                                                              | 56 |

| 5.4 | Topology used in experimental evaluation of Partitioned Paxos                                                                        | 58 |

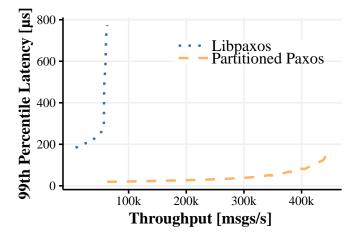

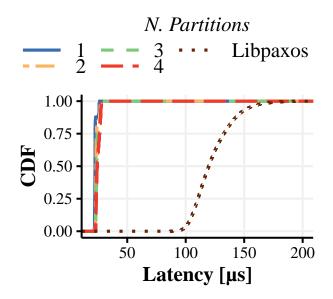

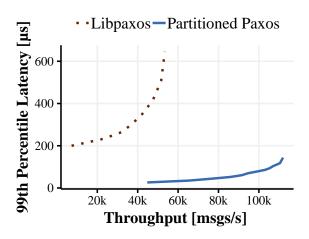

| 5.5 | Noop Throughput vs. 99 <sup>th</sup> -ile latency for libpaxos and Partitioned                                                       |    |

|     | Paxos                                                                                                                                | 59 |

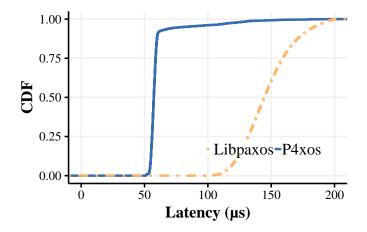

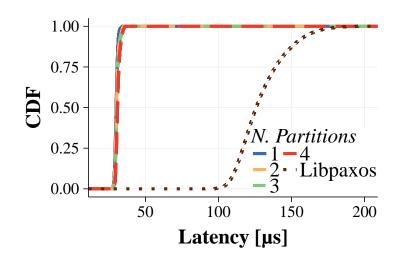

| 5.6        | Latency CDF at 50% peak throughput for libpaxos and Partitioned                                                                                                                                                                                                                          |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.7        | Paxos                                                                                                                                                                                                                                                                                    | 60       |

|            | Paxos                                                                                                                                                                                                                                                                                    | 61       |

| 5.8        | RocksDB Latency CDF at 50% peak throughput for libpaxos and Partition Paxos                                                                                                                                                                                                              | 62       |

| 5.9        | Impact of Storage Medium on Performance of Partitioned Paxos                                                                                                                                                                                                                             |          |

| 5.10       | with RocksDB                                                                                                                                                                                                                                                                             | 63<br>64 |

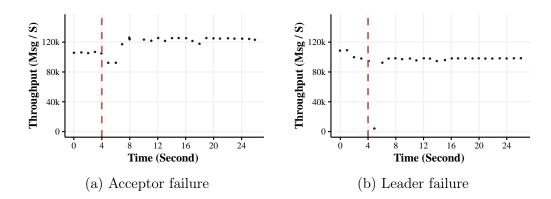

| 5.11       | Partitioned Paxos throughput when (a) a switch acceptor fails, and (b) when the switch leader is replaced by DPDK backup                                                                                                                                                                 | 65       |

| 6.1<br>6.2 | High level architecture of LaKe                                                                                                                                                                                                                                                          | 71       |

| 6.3        | on NetFPGA. The main logical core (shaded grey) is the output of<br>a program compiled from P4/C#                                                                                                                                                                                        | 73       |

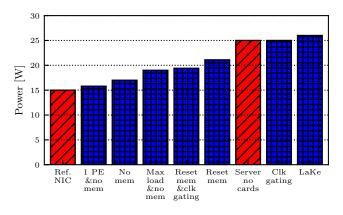

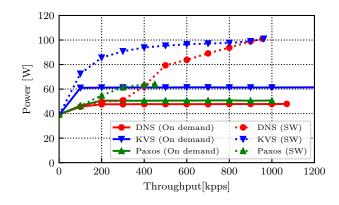

| 6.4        | <ul> <li>(c). in-network computing becomes power efficient once query rate exceeds 80Kppsm 150Kpps and 150Kpps, respectively</li> <li>The effects of LaKe's design trade-offs on power consumption.</li> <li>Blue indicates LaKe's power consumption. Red refers to NetFPGA's</li> </ul> | 76       |

| 6.5        | NIC and an i7 Server                                                                                                                                                                                                                                                                     | 79       |

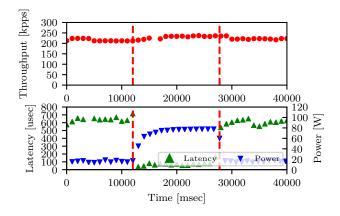

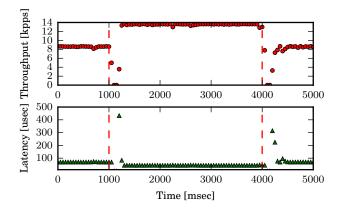

| 6.6        | demand, and dashed lines indicate software-based solutions<br>Transitioning KVS from the software to the network and back. The                                                                                                                                                           | 85       |

|            | transitions are indicated by a red dashed line                                                                                                                                                                                                                                           | 87       |

| 6.7        | Transitioning Paxos leader from the software to the network and back. The transitions are indicated by a red dashed line                                                                                                                                                                 | 90       |

| 7.1        | Memory Hierarchy                                                                                                                                                                                                                                                                         | 96       |

| 7.2<br>7.3 | The ABD protocol                                                                                                                                                                                                                                                                         | 99       |

| 7.4        | col to keep replicas consistent                                                                                                                                                                                                                                                          | 100      |

|            | replicated remote memories.                                                                                                                                                                                                                                                              | 105      |

# Tables

| 4.1 | P4xos latency. The latency accounts only for the packet processing |    |

|-----|--------------------------------------------------------------------|----|

|     | within each implementation                                         | 39 |

| 4.2 | Throughput in messages/second. NetFPGA uses a single 10Gb          |    |

|     | link. Tofino uses 40Gb links. On Tofino, we ran 4 deployments in   |    |

|     | parallel, each using 16 ports                                      | 40 |

| 4.3 | Resource utilization of P4xos on a NetFPGA SUME compiled with      |    |

|     | P4FPGA                                                             | 41 |

|     |                                                                    |    |

# Chapter 1 Introduction

Nowadays, users expect their services to be available most of the time, and hence services rely on replication mechanisms to be highly available. State machine replication (SMR) [5] is a well-known mechanism to provide high availability and consistency for services in distributed systems. Any service can be implemented as a state machine which receives user requests and produces responses. SMR replicates a service on a set of machines called replicas, and if the replicas process the same input, they are guaranteed to produce the same output. As a result, failures of a minority of replicas will not interrupt the service as there are other replicas continuing to provide the service.

To be consistent, all state machines should execute the same commands in the same order. The problem is how to provide the same sequence of commands to the state machines spread across a network where failures can happen, such as machine crashes and network partitioning. Fortunately, this problem can be solved using consensus protocols.

A consensus protocol is a procedure to achieve an agreement among processors in a distributed system involving unreliable processors. In the context of state machines, the agreement is the order of requests fed into the state machines. Existing protocols to solve the consensus problem [2, 1, 6, 7] are the foundation for building fault-tolerant systems. For example, key services in data centers, such as Microsoft Azure [8], Ceph [9], and Chubby [10] are implemented on the basis of consensus protocols [11, 5]. Moreover, other important distributed problems can be reduced to consensus, such as atomic broadcast [7] and atomic commit [12].

However, resolving consensus issues involves further processing of each request, imposing significant performance degradation, so consensus is not typically used in systems that require high performance. Over the past two decades, there have been many suggestions for optimizing performance, spanning a range of methods, including exploiting application semantics (*e.g.*, EPaxos [13], Generalized Paxos [14], Generic Broadcast [15]), strengthening assumptions about the network (*e.g.*, FastPaxos [16], Speculative Paxos [17]), or restricting the protocol (*e.g.*, Zookeeper atomic broadcast [18]). Despite these efforts, consensus performance remains an important issue that researchers are concerned about [19, 20, 21, 22, 23, 24, 25, 26, 27, 28].

Recent advances in network programmability open a new direction for speeding up consensus. We advocate moving consensus into network devices for better performance. In fact, researchers have applied a similar approach exploiting network programming capabilities to optimize data processing systems [17, 29, 28, 30]. However, these projects either provide specialized services [28, 30] rather than a general service that can be used by any off-the-shelf application, or strengthen network ordering assumptions [17, 29] that may not hold in practice. Our main objective is to provide general network-based consensus services without strengthening network assumptions.

#### 1.1 This Dissertation

This thesis addresses the issue of how to provide general-purpose, high-performance consensus services without additional overhead in power consumption. We focus specifically on the Paxos consensus protocol [1] for two reasons. First, it is one of the most widely used protocols in distributed systems [10, 31, 32]. Consequently, increasing consensus performance benefits many data center applications. Second, there exists extensive prior research on optimizing Paxos [16, 33, 34, 35], which suggests that increasing network support can significantly improve system performance.

The hypothesis is that a network-based consensus service can serve as a common substrate for distributed applications, tolerate failures, and have high performance without additional power overhead.

There are five components in this thesis that support the hypothesis:

First, this thesis explores the programmability in the network control plane to implement consensus logic. OpenFlow [36] is a standardized protocol to program the control plane of switches. The OpenFlow API can be used to configure a number of pre-defined matches and actions. A match is a tuple of the network and transport layers, and an action is a decision to forward a packet out of an egress port or a modification of some packet header field. We propose a set of sufficient operations for a network-based consensus service which can be implemented with some extensions to the OpenFlow protocol. However, the operations require some extensions to the OpenFlow API that may take years to persuade hardware vendors to support. To overcome this limitation, we propose an alternative optimistic protocol, called NetPaxos, which can be implemented without changes to the OpenFlow API but relies on two network order assumptions.

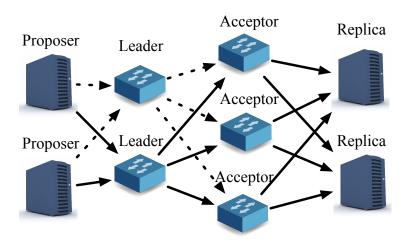

Second, we design and develop a general-purpose consensus service that exploits the network programmable data plane. A new generation of network switches [37] becomes more programmable allowing new network protocols to be deployed quickly. Furthermore, the introduction of high-level data plane programming languages (*e.g.*, P4 [38], PX [39], and POF [40]) makes network services easier to implement. Among those languages, P4 is relatively more mature than others and is widely adopted by vendors [37, 41, 42]. Therefore, we choose P4 to develop consensus services that can run on a variety of network devices. Our implementation artifact is interesting beyond presenting consensus protocols in a new syntax. It helps expose practical concerns and design decisions that have not, to the best of our knowledge, been previously addressed.

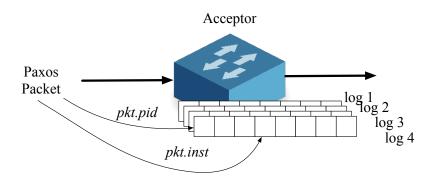

Third, this thesis discusses a technique for partitioning and parallelizing execution of consensus services. The usefulness of in-network computing becomes questionable if replicated applications cannot take advantage of the increased performance (*e.g.*, the maximum throughput of a transactional key-value store is only 5% of the throughput provided by NoPaxos [29]). Worse, network acceleration comes at a cost, regarding money, power consumption, and design time. Clearly, a better method is needed for replicated applications to exploit improved performance provided by the network-based consensus services. A potential approach for performance improvement is to partition the application state and to parallelize the state machine execution. We observe that there are two aspects of the state machine approach: agreement and execution. While agreement ensures the same order of input to the state machine on each replica, execution advances the state of a state machine. While these aspects are tightly coupled in the current projects [28, 30], we decouple execution from agreement and optimize them independently.

Fourth, this thesis justifies the use of networks to accelerate performance for data center applications. While network acceleration improves performance, it also consumes more power. The performance benefits can be disregarded by operational costs from increased power consumption. Our experiments show that offloading consensus service to the network can be extremely efficient in terms of energy. The power consumption of a software system on a commodity CPU can be improved by a factor of hundreds to thousands using FPGAs and ASICs, respectively.

Finally, as a practical use case for our approach, this thesis provides a prototype of a fault-tolerant non-volatile main memory system. Although new emerging memory technologies [43, 44, 45] offer some advantages (*e.g.*, persistence, byte-addressability, low response time and cost), they have unavoidable wear-out mechanisms resulting in finite write (and sometimes read) endurance of devices. In some scenarios, it is still feasible to replace several tiers of the traditional memory hierarchy with these non-volatile memory technologies. Our key insight is to treat the memory as a distributed storage system and rely on a network-based consensus service to keep the replicas consistent through failures.

#### 1.2 Evaluation

To verify our approach, we first estimate performance that can be accelerated by moving consensus into the network. Then, we implement the consensus protocol using programmable network devices. Next, we partition the data of applications and consensus protocols for higher performance. We provide a methodology to improve the power consumption of in-network applications. Finally, we prototype a fault-tolerant memory system which is a use case of the network-based consensus service. Details of our work are provided below.

To estimate potential gains in performance by moving consensus into the network, we implemented and compared NetPaxos with a traditional software consensus library, *libpaxos* [46]. The software library *libpaxos* has been used in many real-world deployments [28, 26, 27, 25]. Although NetPaxos has not yet implemented consensus in the network devices, but our experiments quantified the performance improvement we could get from the network-based consensus. The initial experiments showed that moving Paxos into switches would increase throughput by 9x and reduce latency by 90% for a best case scenario.

To verify the feasibility of a network-based consensus library, we developed a system called P4xos which uses network devices to implement the identified set of data plane consensus operations. P4xos can be realized in several ways, including reconfigurable ASICs [47, 48], FPGAs [49], smart NICs [42], or even x86 CPUs [50]. We used P4xos to replicate an unmodified version of LevelDB and provided a comparison with libpaxos. P4xos offers the same API as libpaxos does. The API is general-purpose and has been used by various applications, such as, Atomic Broadcast [33], Geo-Replicated Storage [25] or Key-Value Stores [27]. In the experiments, we replaced some of libpaxos processes with the P4xos counterparts, allowing us to incrementally replacing the software with hardware implementation. In terms of absolute throughput, our implementation on Barefoot Networks Tofino ASIC chip [37] can process over 2.5 billion consensus messages per second, a four order of magnitude improvement. The end-to-end result showed that P4xos achieved 4.3x throughput improvement and 3x latency improvement. In the event of failures, P4xos continues providing the service in the present of an acceptor failure and can recover quickly from a leader failure.

To verify that the partitioning technique can scale performance of replicated applications, we upgraded P4xos to Partitioned Paxos that supports state partitioning and parallelizing execution. We compared the performance of Partitioned Paxos with the traditional software consensus libpaxos. We ran an unmodified version of RocksDB on top of Partitioned Paxos and libpaxos and measured their latency and throughput. The experiments showed that application throughput is scaled linearly with the number of partitions; when running four partitions, Partitioned Paxos reached a throughput of 576K messages/second, almost 11 times the maximum throughput for libpaxos. The latency for Partitioned Paxos has little dependence on the number of partitions and it was only 18% of libpaxos's.

To justify the use of consensus in the network, we provided a detailed power analysis of network-accelerated applications and developed a methodology to flexibly switch the applications to run on servers or in networks depending on the workload. Specifically, we analyzed the energy consumption of a Key-Value Store (KVS), a consensus protocol and a Domain Name System (DNS). Our energy analysis showed that the energy consumption of servers in idle mode is lower than that of network devices. However, as the workload increases, the hardware becomes more energy efficient than the CPU. To cope with the dynamic workload, the applications are flexibly shifted between software-based and network-based implementations. Our evaluation demonstrated that in-network computing with dynamic switching is both energy-efficient and performant.

Finally, to demonstrate the consensus protocol can be applied to other classes of data center applications, we implemented a fault-tolerant persistent main memory system to tolerate arbitrary failures of a minority of memory nodes. The evaluation quantified the overhead for page fault handling via calls to remote replicated memory versus local memory. Our prototype added minimal latency overhead to conventional unreplicated memory systems.

#### 1.3 Research Contributions

Overall, this thesis makes the following contributions:

- 1. It identifies a sufficient set of features that protocol developers would need to provide for a network-based consensus service. In addition, it describes an alternative protocol which can be implemented without changes to the OpenFlow API but relies on network order assumptions.

- 2. It designs and implements a general-purpose network-accelerated consensus service which is a drop-in replacement for traditional software consensus implementations.

- 3. It explores a technique for improving network-accelerated consensus by separating agreement from execution and optimizing each of them independently.

- 4. It analyzes power consumption of network-accelerated applications and implements a methodology to dynamically shift applications between servers the network for power efficiency.

- 5. It implements a fault-tolerant service for storage class memory and provides initial evidence of the feasibility and benefits of using in-network consensus to keep SCM replicas consistent.

The rest of this dissertation is organized as follows. We present the background of this thesis (§2) and a proposition to move consensus logic into the network(§3). Next, we describe the design and implementation of P4xos(§4) and discuss the technique to partition application state and to parallelize state machine execution (§5). Following that, we present a detailed power analysis of in-network computing and an energy-efficient shifting methodology (§6). Then, we show a new approach to tolerate main memory failures using network-based consensus (§7). Finally, we cover related work (§8) and conclude the thesis by outlining our main findings and presenting directions for future research (§9).

# Chapter 2

# Background

This chapter presents the background for this thesis. we start with a definition of consensus and an important result in distributed systems (Section 2.1). Then, we review the Paxos consensus protocol and its optimized derivatives, and follow that up by discussing the performance bottlenecks in a traditional Paxos implementation (Section 2.2). We provide an overview of new programmable network hardware (Section 2.3), and language support for network programming (Section 2.4). Finally, we present an emerging technique to improve application performance (Section 2.5) and methods for power consumption measurement (Section 2.5.1). These technologies are the enablers to deploy new applications in networks.

## 2.1 The Consensus Problem and The Fischer, Lynch and Patterson (FLP) Result

In distributed systems, it is important to distinguish between synchronous and asynchronous systems. In a synchronous system, processors have access to a common clock and their processing time is bounded. Messages are also delivered within a bounded interval. Then, processors can safely tell that a processor has failed if it does not respond within an interval. On the other hand, In an asynchronous system, there are no assumptions about the speed of processors or about the interval to deliver a message, so processors cannot detect if another has failed.

Consensus is the problem of getting a set of processors in an asynchronous system to agree on a common value. It is a fundamental problem in distributed systems and is the core component of many fault-tolerant systems (*e.g.*, Microsoft

Azure [8], Ceph [9], and Google Chubby [10]). Examples of the consensus problem including atomic transaction commit, leader election and atomic broadcast.

An important result [51], published by Fischer, Lynch and Patterson in 1985, proved that "no consensus protocol can tolerate even a single unannounced process death" in asynchronous systems in which processors can fail even when the message communication is reliable. Under the asynchronous system model, a processor undetectably stops preventing any consensus protocol to reach agreement. The consensus problem cannot be solved without further assumptions about the system model.

#### 2.2 The Paxos Consensus Protocol

Paxos [1] is a protocol for solving consensus problem in a partial synchronous [52] system where the system is either synchronous or asynchronous for some periods which are not known in advance. Paxos guarantees *safety* at any time, and *liveness* whenever the system becomes synchronous in which the processing time of different processors and the time for messages to be delivered are bounded.

Safety means that no processor can choose a value which is different from the value chosen by other processors. In other words, the Paxos protocol ensures all processors choose the same value.

Liveness means that the system makes some progress by executing requests and responding to clients. Paxos guarantees liveness as long as a majority of processors are functional.

#### 2.2.1 Asynchronous, Non-Byzantine Model

The original Paxos protocol assumes any processor can delay, crash or restart. However, when a processor runs, it correctly handles the messages it received from others. It does not alter the content of messages for malicious purposes. If any processor tries to deceive the others, this act is categorized as Byzantine Failure [53]. We will not cover this type of failure in this thesis.

A processor can unicast messages to a single receiver or multicast messages to multiple receivers. The network is asynchronous in which messages can be duplicated, reordered or even lost, but they are not corrupted by the network. However, whenever the network becomes synchronous, messages are delivered in a bounded period, and received messages are exactly the same messages as the ones have been sent.

#### 2.2.2 Basic Paxos

Leslie Lamport described the original Paxos protocol [1] using an analogy of the voting process in the island of Paxos where legislators are not always present in the Chamber. Later, Lamport revised the protocol using terms that are well-known for most system builders in the "Paxos Made Simple" paper [54], so-called Basic Paxos. The Basic Paxos protocol defines the following roles depending on the actions which a processor performs: *proposers, acceptors* and *learners*.

- **Proposers** propose values to be chosen and each of the proposers tries to get a majority of acceptors to agree with it. Multiple proposers can exist but the protocol guarantees that a single value is chosen in the end.

- Acceptors vote to accept a value and remember the value they have voted for. Furthermore, the acceptors promise to reject other values if they already accepted one.

- Learners eventually find out the chosen value once it has been accepted by a majority of acceptors. The learners either learn the chosen value by receiving messages from acceptors or by contacting a majority of acceptors in case they failed before learning what has been chosen.

Paxos is resilient in the sense that it tolerates failures of up to f acceptors from a total of n = 2f + 1 acceptors. To ensure the system making progress, a majority, also known as quorum, of f + 1 acceptors must be non-faulty [19].

An instance of Paxos proceeds in two phases. In Phase 1, a proposer selects a unique round number and sends a *Prepare* request (Phase 1A) to acceptors. Upon receiving a Prepare request with a round number bigger than any previously received round number, an acceptor responds to the proposer a *Promise* message (Phase 1B) promising that it will reject future requests with smaller round numbers. If the acceptor already accepted a request for the current instance (explained next), it will return the accepted value to the proposer, together with the round number received when the request was accepted. When the proposer receives Promises from a quorum of acceptors, it proceeds to the second phase of the protocol.

In Phase 2, the proposer can select a new value to propose if none of acceptors in the quorum has accepted a value. Otherwise, the proposer must choose the highest round-value pair among those are returned in Phase 1. The proposer then sends an *Accept* request (Phase 2A) with the round number it used in the first phase and the selected value. Upon receiving an Accept request, an

acceptor acknowledges it by sending an *Accepted* message (Phase 2B) to learners, unless the acceptor has already acknowledged another request with a higher round number. When a quorum of acceptors accepts a value, consensus has been reached.

#### 2.2.3 Implementing Fault-Tolerant Applications with Paxos

A fault-tolerant application can be implemented as a system consisting of multiple servers, each of which is a state machine built on top of a replicated log. Each log entry in the replicated log is a client command. The state machine executes the commands in the order they are placed in the replicated log. Because the state machine is deterministic, all servers produce the same outputs and end up in the same state, if they apply the same log.

However, the approach above raises a question: *How do we choose which log entry for a command?* The solution is that each server keeps an instance number which is the smallest log entry with no chosen value and try to propose a value for this slot. It then keeps submitting the same value on increasing entry number until the value is selected for a particular entry. Servers can handle multiple client commands simultaneously by assigning different commands to different log entries. However, updating the state machine is sequential for consistency.

Throughout this dissertation, references to Paxos implicitly refer to multiple instances of paxos (also known as Multi-Paxos).

#### 2.2.4 Optimizations

If multiple proposers simultaneously propose values for the same instance, then no proposer may be able to complete two phases of the protocol and reach consensus. To avoid scenarios in which proposers compete indefinitely in the same instance, a *leader* can be selected to arbitrate the proposals. In this setting, proposers submit values to the leader, which executes two phases of the protocol on their behalf. If the leader fails, another proposer will be elected to be the new leader and takes over the jobs of the failed one. Paxos ensures safety despite concurrent leaders and liveness in the presence of a single leader.

If the leader is stable across instances, the protocol can be optimized by preinitializing acceptor state with previously agreed upon instance and round numbers, avoiding the need to send phase 1 messages [54]. This is possible because only the leader sends values in the second phase of the protocol. With this optimization, consensus can be reached in three communication steps: the message from the proposer to the leader, the accept request from the leader to the acceptors, and the response to this request from the acceptors to the learners.

Fast Paxos [16] is a well known optimization of Paxos. Paxos requires three message delays, including the client's message. Fast Paxos allows learners to learn the chosen value in two message delays. It save one communication step in *fast rounds* by allowing clients to send the value directly to acceptors, bypass proposers. In order to prevent the learners learning different values, fast rounds require larger quorums than classic Paxos. In case of conflicting proposals, a situation in which acceptors accept different values in the same round, Fast Paxos reverts to classic Paxos to resolve the conflict.

#### 2.2.5 Performance Bottlenecks of Traditional Paxos Systems

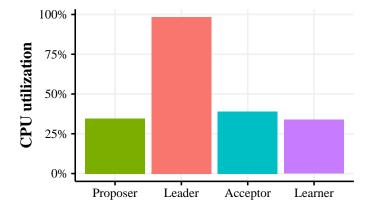

Figure 2.1. The leader is the bottleneck in a software-based Paxos deployment.

To investigate performance bottlenecks of traditional Paxos implementations, we measured the CPU usage for each of the Paxos roles when the system handles requests at peak throughput. There are, of course, many other Paxos implementations, so it is difficult to make generalizations about their collective behavior. We specifically focus on libpaxos [46], a faithful implementation of Paxos that has been extensively tested and is often used as a reference Paxos implementation (*e.g.*, [25, 26, 27, 28]). Moreover, libpaxos performs better than all the other available Paxos libraries we are aware of under similar conditions [13].

In the initial configuration, there were seven processors spread across three machines running on separate cores: one proposer that generated load, one

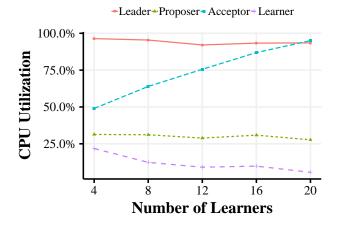

Figure 2.2. Besides the bottleneck at the leader, the acceptor becomes the next bottleneck as the degree of replication increases.

leader, three acceptors, and two learners. The processors were distributed as follows to achieve the best performance while tolerating an acceptor failure.

- Server 1: 1 proposer, 1 acceptor, 1 learner

- Server 2: 1 leader, 1 acceptor

- Server 3: 1 acceptor, 1 learner

The client application sent 64-byte messages to the proposer at the peak throughput rate of 64,949 values/sec. The results, which show the average usage per role, are plotted in Figure 2.1. They show that the leader is the bottleneck, as it becomes CPU bound.

We then extended the experiment to measure the CPU usage for each Paxos role as we increased the degree of replication by adding more learners. The learners were assigned to one of three servers in round-robin fashion, such that multiple learners ran on each machine.

The results, plotted in Figure 2.2, show that as we increase the degree of replication, the CPU usage for acceptors increases. This is expected because as the number of learners increases, the overhead of network I/O of acceptors increases. In contrast, the utilization of the learners decreases as the consensus throughput is reduced. Consequently, the learners have less messages to handle.

Overall, these experiments clearly show that the leader and acceptor are performance bottlenecks for Paxos.

## 2.3 Programmable Network Hardware

Recent advances in network programmability enable innovation in networks. With increased network programmability, system developers can tailor the network to benefit their applications. The increase in network programmability comes from various solutions, including Smart Network Interface Cards [55], FPGAs [49] and ASICs [37]. In this section, we give an overview on these programmable network devices.

#### 2.3.1 Smart Network Interface Cards (Smart NICs)

There are many definitions of SmartNICs; personally, the one from Deierling [55] is the most insightful and comprehensive. According to Deierling, "A SmartNIC is a network adapter that accelerates functionality and offloads it from the server (or storage) CPU".

SmartNICs can be manufactured with different architectures, and each of architecture exhibits different characteristics in terms of cost, programming efforts, and performance. ASIC-based SmartNICs offer the highest performance with reasonable price, but they have limited functionalities. FPGA-based SmartNICs are expensive and difficult to program, but they offer the greatest flexibility. Last but not least, (system-on-chip) SOC-based SmartNICs, which is flexible, easy to program, and offer good price performance.

Due to the flexibility and high performance of SmartNICs, many applications are offloaded to the NICs. One oblivious example is that virtual machines offload the network stack of virtual interfaces to smartNICs [56]. The SmartNICs are also used for accelerating NFV [57], Key-Value Store [58] and Consensus [59].

We also has a prototype our system using SOC-based SmartNICs [42]. This demonstrates our system can be realized on a variety of hardware. Due to a limitation of our license, we do not include the result for the SmartNICs.

#### 2.3.2 Field Programmable Gate Arrays (FPGAs)

FPGAs (Field Programmable Gate Arrays) are programmable hardware devices. The programmability of FPGAs is the ability to reconfigure logic blocks on a device after it is fabricated. Program targeting FPGAs are often written using hardware programming languages, such as Verilog and VHDL. Instead of compiling a program to the machine code like C compilers, FPGA compilers transform the program into a circuit of semiconductors and flip-flops, which implements the intended functionality.

Some FPGAs can be considered as SmartNICs as they can be implemented to offload particular system CPU tasks to configurable hardware. Unlike ASICs that have limitations on functionalities defined in the chips, FPGAs can be reprogrammed to meet different user needs. Engineers use FPGAs in designing specialized integrated circuits for faster time to market. For this advantage, vendors and open-source community have introduced FPGA compilers [41, 60, 61] for offloading applications that traditionally run on x86 CPUs [62, 63] to FPGAs.

We implement the Paxos leader and acceptors using NetFGPA SUME [49]. We use the P4FPGA compiler [60] to generate the bitstream for configuring the NetFPGA SUMEs. NetFPGA SUMEs are used to evaluate performance individual Paxos components, P4xos and our fault-tolerant memory.

#### 2.3.3 Programmable ASICs

An ASIC (application-specific integrated circuit), as its name already stated, is an electric circuit designed to perform specific tasks. The cost of design, producing and testing an ASIC chip is pretty expensive, therefore, vendors usually do not open their hardware and only provide a CLI (command-line interface) to interact with their chip. Due to the high cost of chip manufacture, it takes years to convince the hardware vendors to push new protocols onto their chips.

This is going to change with a new emerging generation of programmable ASICs [37] that adds flexibility to conventional ASICs. With the advance of the programmable ASICs, now users can develop new protocols and functionalities without buying new devices. Programmable ASICs allow users to reprogram the data plane in their switches, to remove unnecessary features or to add new functionalities as they want.

We use Tofino switches [37] to run combinations of Paxos leader and acceptors. Tofino switches are used in the evaluation of performance of individual Paxos components, Partitioned Paxos as well as our fault-tolerant memory system.

## 2.4 Language Support for Network Programming

While network devices become more programmable, there is no way to write a single program that can be cross compiled and run on variety of hardware. Although, some vendors support restricted versions of C language [64, 42], this is not an optimal solution and it still requires developers to modify the program to fit new hardware. Therefore, several high-level data plane programming languages (*e.g.*, P4[38], PX [39] has been introduced to POF [40]) make network programming easier. Among those languages, P4 is relatively more mature than others and is widely adopted by vendors [37, 41, 42].

#### 2.4.1 P4: High Level Data Plane Programming Language

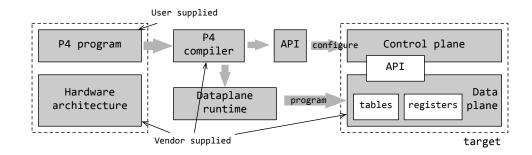

P4 [65] is designed with the following goals. First, network devices should be able to be reconfigured by a controller. Instead of being tied to specific existing protocols, a network device should be able to change its packet parser and its processing pipeline to support new protocols. Second, P4 is independent from the underlying targets. A P4 program can be compiled to run on any network devices (*e.g.*, software switches [66], Smart NICs [42], FPGAs [41] and ASICs [37]).

The language provides a common interface for programming or configuring devices of various hardware vendors. P4 provides high-level abstractions that can be tailored to the needs of packet forwarding devices: packets are parsed and then processed by a sequence of tables; tables match on packet header fields, and perform stateless actions such as forward, drop, and modify packets; actions can include some stateful operations (*e.g.*, read and write to memory).

A typical P4 program that forwarding and manipulating network packets consists the following constructs:

- *Header Types* specify the definition of the headers which are expected within a packet.

- *Parsers* specify an order of the headers within a packet and is responsible for populating values of header fields.

- *Actions* specify how to process packets and metadata. Actions can contain arguments which are supplied by the control plane at runtime.

- *Tables* associate user-defined keys with user-defined actions to transform packets and states of the device. The keys can be the header fields and/or metadata.

- *Control Flow* defines the flow of the data (packets and metadata). The flow consists of a sequence of tables and possibly some conditional branches.

Figure 2.3 shows a workflow while developing a P4 program for a general target. Programmers only need to care about their business logic instead of the architecture of underlying hardware. Different vendors may provide hardware

Figure 2.3. P4 Workflow

or software targets, or the combination of both. The target is bundled with a compiler which generates the data plane runtime to program the target, and an API to configure the program running on the target.

One feature that causes P4 to be quickly adopted is the ability to do stateful computations. P4 specification included stateful registers which can be used in traffic monitoring and general memory access. This feature attracts researchers to offloading intensive computing tasks (*e.g.*, network ordering [29], key-value store [3] and stream processing [4]) which are normally executed by the system CPUs, to network devices for performance.

Since P4 is a high-language and largely adopted by hardware vendors, we chose P4 to develop our network-based consensus services. Our implementation artifact is interesting beyond presenting consensus protocols in a new syntax. It helps expose practical concerns and design choices for the language evolution.

#### 2.5 Kernel-Bypass: Accelerating Performance of Servers

Moving consensus logic into network devices is the first half of the proposed solution. The other half is to accelerate performance of applications running on commodity servers. Bypassing the Linux kernel stack is an emerging way to increase the application performance.

Kernel bypass is a technique to eliminate the overhead of the kernel network stack in the processing pipeline of applications. A benefit of kernel bypass is performance because it avoids copying packets to intermediate buffers in the kernel space. For this benefit, many kernel bypass technologies, such as RDMA (Remote Direct Memory Access) [67], TOE (TCP Offload Engine) [68], and more recently, DPDK [69] (Data Plane Development Kit) have been used in real-world applications [27, 50, 70] to boost performance of data processing systems.

In this thesis, we focus on DPDK as it does not require upgrading network

hardware like RDMA and is more flexible than TOE which only supports TCP/IP communication. Specifically, we implement all Paxos roles (leader, acceptor and learner) using DPDK libraries for high packet processing performance. The DPDK implementation is used to evaluate performance of individual Paxos components, P4xos and Partitioned Paxos.

DPDK is an open-source project that aims at achieving high network I/O performance and reaching high packet processing rates on traditional CPUs. DPDK eliminates the overhead of the kernel networking stack by allowing user space applications to directly access network interface cards (NICs). In the user space, DPDK provides APIs to configure parameters of NICs, such as, the size of RX and TX queues, affinities between NICs and memory buses, whether to enable receiving and transmitting in batch mode, and so on. Besides, the Poll Module Driver (PMD) of DPDK accesses the NICs' RX and TX queues directly without any interrupts to quickly send and receive packets.

DPDK employs a few low-level techniques to further improve performance. We briefly mention two notable optimizations: First, by using huge pages (of 2MB or 1GB in size), DPDK needs a smaller number of memory pages and avoids dynamic memory allocation. The use of huge pages also reduces the memory access overhead as the number of Translation Lookaside Buffers (TLBs) misses is reduced. Second, all data structures in DPDK are aligned to cache lines for optimal cache use.

#### 2.5.1 Methods for Power Consumption Measurement

Aside from performance constraint, data center applications also need to deal with the power consumption issues which can rapidly exceed performance benefit. Therefore, data center operators often have to monitor performance and power consumption of their applications to enhance the efficiency of their infrastructure.

Different hardware architectures exhibit different power characteristics. While ASIC design offers better performance than general-purpose CPUs, it is deemed to consume more power. Novel computing systems are often complex and composed of hardware and software components. The power consumption is valuable information to help developers to improve energy efficiency for their systems.

There are two main methods to measure power consumptions: the hardwarebased method uses physical devices (*e.g.*, power meters) to measure the power at various test points and the software-based method estimates the power consumption from a variety of information (*e.g.*, CPU usage) [71]. A hybrid solution could be used to measure power consumption of more complex systems. In chapter 6, these three methods are used to measure power consumption for our use cases.

## 2.6 Chapter Summary

This chapter covers the necessary background for this thesis. We reviewed the Paxos protocol and some of its optimizations. We presented experiments that show performance bottlenecks of traditional Paxos implementations. We also introduced a few programmable network devices and the language support for network programming. Finally, we present the kernel bypass approach to improve performance of applications and three methods for measuring power consumption.

# Chapter 3

# NetPaxos

Network bandwidth is increased rapidly in recent years, shifting the bottleneck of applications from the network to the CPU. At the same time, network devices become more programmable, creating a possibility to offloading applications to the network. As a result, more and more services (*e.g.*, caching [3], key-value store [72], stream processing [4], etc.) are folded into networks to address the performance issue.

This chapter presents a proposition to move consensus into the network. We first elaborate on the benefits of our approach to run consensus logic directly on the network devices (Section 3.1). Second, We identify a sufficient set of data plane operations (Section 3.2) a switch would need to support for Paxos implementation. Finally, we discuss an evaluation of an optimistic protocol that can be implemented without any changes to the OpenFlow API, but it relies on network ordering assumptions (Section 3.3).

# 3.1 The Benefits of Network-based Consensus

In contrast to traditional networking, in which network devices have proprietary control interfaces, SDN (Software-Defined Networking) generalizes network devices using a set of protocols defined by open standards, including most prominently the OpenFlow [36] protocol. The standardization has led to increased "network programmability", allowing software to manage the network using the standardized APIs.

Several projects have used SDN to demonstrate that applications can benefit from improved network programmability. While these projects are important first steps, they have largely focused on one class of applications (*i.e.*, Big Data [73, 74, 75, 76]), and on improving performance via traffic engineering (*e.g.*, route

selection [74, 76], traffic prioritization [73, 76], or traffic aggregation [75]). None of these projects has considered whether application logic could be moved into the network. In other words: *how can distributed applications and protocols utilize network programmability to improve performance?*

We argue that performance of distributed applications could benefit from moving consensus logic into the network devices. Specifically, we focus on the Paxos consensus protocol [1] which is an attractive use-case for several reasons. First, it is one of the most widely deployed protocols in highly-available distributed systems, and is a fundamental building block to a number of distributed applications [10, 32, 31]. Second, there exists extensive prior research on optimizing Paxos [16, 33, 77, 78], which suggests that the protocol could benefit from increased network support. Third, moving consensus logic into network devices would require extending the SDN switches with functionality that is amenable to an efficient hardware implementation [79, 47].

Network switches could play the role of *leader* and *acceptors* and the advantages would be twofold. First, messages would travel fewer hops in the network, therefore reducing the latency for replicated systems to reach consensus. Second, throughput would be increased as the network switches processes network messages much faster than traditional servers, thus eliminating performance bottlenecks at the leader and acceptors.

# 3.2 OpenFlow Extensions for In-Network Consensus

In normal network conditions, Paxos protocol could be optimized to simplify its implementation. An optimization, inspired by Fast Paxos [16], is applied to reduce the complexity of a network-based implementation of Paxos which needs only implement Phase 2 of the Paxos protocol. Since Phase 1 does not depend on any particular value, it could be run ahead of time for a large bounded number of values. The pre-computation would need to be re-run under two scenarios: either (*i*) the Paxos instance approaches the bounded number of values, or (*ii*) the device acting as leader changes (possibly due to failure).

Unfortunately, implementing only Phase 2 of the protocol goes far beyond what is expressible in the current OpenFlow API. The API is limited to basic match-action rules, simple statistics gathering, and modest packet modification (*e.g.*, replacing MAC addresses or decrementing IP's TTL). Because the API is not expressible enough to implement Paxos, we identify a set of operations that would be sufficient for a network-based implementation of Paxos:

Generate round and sequence number. Each switch leader must be able to gen-

erate a unique round number (*i.e.*, the *c-rnd* variable), and a monotonically increasing, gap-free sequence number.

- **Persistent storage.** Each switch acceptor must store the latest round it has seen (*c-rnd*), the latest accepted round (*v-rnd*), and the latest value accepted.

- **Stateful comparisons.** Each switch acceptor must be able to compare a *c-rnd* value in a packet header with its stored *c-rnd* value. If the packet's c-rnd is higher, then the switch must update the local state with the new *c-rnd* and value, and then broadcast the message to all learners. Otherwise, the packet could be ignored (*i.e.*, dropped).

Storage cleanup. Stored state must be trimmed periodically.

We do not claim this set of operations is *necessary*. As we will see in the next section, the protocol can be modified to avoid some of these requirements.

Recent work on extending OpenFlow suggests that the functionality described above could be efficiently implemented in switch hardware [79, 47]. Moreover, several existing switches already have support of some combinations of these features. For example, the NoviSwitch 1132 has 16 GB of SSD storage [80], while the Arista 7124FX [81] has 50 GB of SSD storage directly usable by embedded applications. Note that current SSDs typically achieve throughputs of several 100s MB/s [82], which is within the requirements of a high-performance, network-based Paxos implementation. The Netronome SmartNICs [42] can flexibly perform stateful comparisons.

Also, rather than modifying network switches, a recent hardware trend towards programmable NICs [83, 84] could allow the proposer and acceptor logic to run at the network edge, on programmable NICs that provide high-speed processing at minimal latencies (tens of  $\mu$ s). Via the PICe bus, the programmable NIC could communicate to the host OS and obtain access to permanent storage.

# 3.3 Fast Network Consensus

Section 3.2 described a sufficient set of functionality that protocol designers would need to provide to completely implement Paxos logic in forwarding devices. In this section, we introduce *NetPaxos*, an alternative algorithm inspired by Fast Paxos. The key idea behind NetPaxos is to distinguish between two execution modes, a "fast mode" (analogous to Fast Paxos's fast rounds), which can be implemented in network forwarding devices with no changes to existing Open-Flow APIs, and a "recovery mode", which is executed by commodity servers.

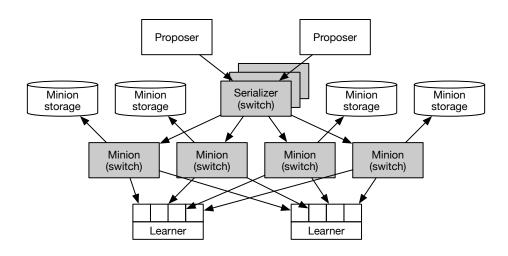

Figure 3.1. NetPaxos architecture. Switch hardware is shaded grey. Other devices are commodity servers. The learners each have four network interface cards.

Both Fast Paxos's fast rounds and NetPaxos's fast mode avoid the use of a Paxos leader, but for different motivations. Fast Paxos is designed to reduce the total number of message hops by optimistically assuming a spontaneous message ordering. NetPaxos is designed to avoid implementing leader logic inside a switch. In contrast to Fast Paxos, the role of acceptors in NetPaxos is simplified. In fact, acceptors do not perform any standard acceptor logic in NetPaxos. Instead, they simply forward all messages they receive, without doing any comparisons. Because they always accept, we refer to them as *minions* in NetPaxos.

#### 3.3.1 Protocol Design

Figure 3.1 illustrates the design of NetPaxos. In the figure, all switches are shaded in gray. Proposers send messages to a single switch called the *serializer*. The serializer is used to establish an ordering of messages from the proposers. The serializer then broadcasts the messages to the minions. Each minion forwards the messages to the learners and to a server that acts as the minion's persistent storage to record the history of "accepted" messages. Note that if switches could maintain persistent state, there would be no need for the minion storage servers. Each learner has multiple network interfaces, one for each minion.

The protocol, as described, does not require any additional functionality beyond what is currently available in the OpenFlow protocol. However, it does make two important assumptions:

- 1. Packets broadcast from the serializer to the minions arrive in the same order. This assumption is important for performance, not correctness. In other words, if packets are received out-of-order, the learners would recognize the problem, fail to reach consensus, and revert to the "recovery mode" (*i.e.*, classic Paxos).

- 2. Packets broadcast from a minion arrive all in the same order at its storage and the learners. This assumption is important for correctness. If this assumption is violated, then learners may decide different values in an instance of consensus and not be able to recover a consistent state from examining the logs at the minion storage.

Recent work on Speculative Paxos [59] shows that packet reordering happens infrequently in data centers, and can be eliminated by using IP multicast, fixed length network topologies, and a single top-of-rack switch acting as a serializer. Our own initial experiments (§ 3.3.2) also suggest that these assumptions hold with unmodified network switches when traffic is non-bursty, and below about 675 Mbps on a 1 Gbps link.

Fast Paxos optimistically assumes a spontaneous message ordering with no conflicting proposals, allowing proposers to send messages directly to acceptors. Rather than relying on spontaneous ordering, NetPaxos uses the serializer to establish an ordering of messages from the proposers. It is important to note that the serializer does not need to establish a FIFO ordering of messages. It simply maximizes the chances that acceptors see the same ordering.